### Advanced task-based programming models for scalable linear algebra operations

Antoine Jego

### ► To cite this version:

Antoine Jego. Advanced task-based programming models for scalable linear algebra operations. Other [cs.OH]. Institut National Polytechnique de Toulouse - INPT, 2023. English. NNT: 2023INPT0107. tel-04440126

### HAL Id: tel-04440126 https://theses.hal.science/tel-04440126

Submitted on 5 Feb 2024

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

Université de Toulouse

# THÈSE

En vue de l'obtention du

# DOCTORAT DE L'UNIVERSITÉ DE TOULOUSE

Délivré par :

Institut National Polytechnique de Toulouse (Toulouse INP)

**Discipline ou spécialité :** Mathématiques Appliquées

### Présentée et soutenue par :

M. ANTOINE JEGO le vendredi 15 décembre 2023

### Titre :

Modèles de programmation avancés à base de tâches pour les algorithmes d'algèbre linéaire qui passent à l'échelle

### Ecole doctorale :

Mathématiques, Informatique, Télécommunications de Toulouse (MITT)

Unité de recherche : Institut de Recherche en Informatique de Toulouse (IRIT)

### Directeur(s) de Thèse :

M. ALFREDO BUTTARI

### Rapporteurs :

M. EMANUEL RUBENSSON, UPPSALA UNIVERSITET SUEDE M. GEORGES BOSILCA, UNIVERSITE DU TENNESSEE

### Membre(s) du jury :

M. PATRICK AMESTOY, TOULOUSE INP, Président M. ALFREDO BUTTARI, TOULOUSE INP, Membre M. EMMANUEL AGULLO, INRIA CENTRE DE RECHERCHE DE BORDEAUX, Invité(e) MME AURELIE HURAULT, TOULOUSE INP, Membre M. NICOLAS RENON, MESOCENTRE CALMIP, Invité(e) M. SAMUEL THIBAULT, UNIVERSITE BORDEAUX 1, Membre

# Abstract

Writing high-performance computing packages is not an easy task given the ever-burgeoning supercomputing ecosystems. In the last decade the land-scape of supercomputers has become more complex to maintain low energy consumption and high computing power throughput. To achieve this feat groundbreaking computing chips are used such as GPUs. This hardware comes with specific low-level tools to program it and, as such, requires much expertise when building computing-intensive applications.

This thesis is focused on task-based programming models that make the adaptation of the software stack more productive and more resilient to hardware breakthroughs.

The sequential task flow (STF) model is given special care as it proposes polished interfaces that has been widely-adopted in scientific computing packages executed on shared-memory parallel machines. The adoption of this model is more disputable on distributed-memory machines; the mechanisms put in place by state-of-the-art scalable algorithms are well-established in lowlevel programming models such as the message passing interface however they are not transparently supported by the STF model. By reviewing linear algebra scalable algorithms we have identified missing features in STF that are pivotal to obtain scalability by avoiding communications.

We have implemented and validated them in the StarPU runtime system that support the STF model. The resulting extended programming model makes it possible to express state-of-the-art scalable algorithms in a portable and compact way. The first one is distributed-memory matrix-matrix multiplication for which we deliver a single elegant code that can span multiple algorithmic variants. The second one is matrix decomposition for which our implementation compactly exhibits state-of-the-art designs. These algorithms have been added to the dense routines of the qr\_mumps package.

A large experimental campaign has been carried out to validate the performance of our implementations. Performance measurements indicate compelling results with regard to other dense linear algebra packages especially on smaller problems typically harder to parallelize or when input matrices dimensions are unbalanced.

The flexibility of our implementations was instrumental to enable the use of layouts tailored for symmetric matrix multiplication when the symmetric matrix is the largest one. The resulting operation now performs comparably well to general matrix multiplication while using half the memory.

# Résumé

L'écriture de bibliothèques de calcul haute performance n'est pas une tâche aisée surtout dans des environnements de calcul en perpétuelle évolution. La dernière décennie a vu le paysage des supercalculateurs se complexifier pour maintenir une consommation d'énergie faible et une puissance de calcul élevée. Pour y parvenir des technologies avancées comme les GPU sont mises en œuvre. Ce matériel peut être programmé à l'aide d'outils bas-niveau et à ce titre une expertise est requise pour développer des applications de calcul intensif.

Cette thèse étudie les modèles de programmation à base de tâches rendant l'adaptation logicielle productive et flexible aux innovations matérielles.

On s'intéresse en particulier au modèle de programmation séquentiel en flots de tâches (STF) qui propose une interface largement adoptée par la communauté du calcul scientifique dans l'utilisation des machines en mémoire partagée. Cette adoption est cependant moins univoque dans le cadre des machines à mémoire distribuée; les méchanismes mis en place par les algorithmes de l'état de l'art qui passent à l'échelle s'appuyant plus souvent sur des interfaces bas-niveau comme celle proposée par MPI, ils ne sont pas disponibles de manière transparente dans le STF. En passant en revue les algorithmes d'algèbre linéaire qui passent à l'échelle on a pu identifié des fonctionnalités manquantes au modèle qui permettent l'évitement des communications.

On a implémenté et validé ces fonctionnalités dans le moteur d'exécution StarPU qui prend en charge le modèle STF. Le modèle étendu qui en résulte rend possible l'expression portable et compacte d'algorithmes de l'état de l'art qui passent à l'échelle. Le premier algorithme d'intérêt est la multiplication de matrices pour laquelle on fournit un unique code élégant qui balaie différentes variantes. Le second est la factorisation de matrice dont notre implémentation expose compactement des choix de conception de l'état de l'art. Ces algorithms ont été intégrés à la suite de routines denses de qr\_mumps.

Une campagne expérimentale importante a été mise en place pour valider les gains de performance réalisés. Les résultats indiquent que notre approche est compétitive face à celle mise en place par des bibliothèques de l'état de l'art, en particullier sur des problèmes de petites tailles difficiles à paralléliser ou bien des problèmes pour lesquels les dimensions sont déséquilibrées.

La flexibilité de nos implémentations a été déterminante pour permettre l'utilisation de distributions de données avancées quand la matrice symmétrique est la plus grande. L'opération qui en résulte est aussi performante que la multiplication de générale tout en utilisant moitié moins de mémoire.

### Remerciements

I would like to first thank George and Emanuel for reporting on this manuscript. Not only did they give it a thorough read which helped me improve its quality further, they have also taken the time to come to Toulouse to listen to my defense and discuss the achieved work further.

J'aimerais aussi remercier les autres membres du Jury : Aurélie, Nicolas, Patrick et Samuel. Vos perspectives multiples ont participé à améliorer la clarté de ce manuscrit. Quand bien même vous ne venez pas d'aussi loin, c'est tout autant un honneur pour moi que vous ayez pu jugé ces travaux. While the defense may supposedly be a dreadful moment, I felt really happy to answer each and every one of your questions and discuss with all of you.

Évidemment, et parce que sans eux il n'y aurait même pas une once de manuscrit à commencer à améliorer, je souhaite remercier abondament Alfredo, Abdou et Emmanuel. C'a été trois années et demi bizarroïdes en terme de rhythme avec la pandémie (en tout cas quand les institutions essayaient d'organiser sa mitigation), mais ç'a été une période pendant laquelle j'ai eu beaucoup de plaisir à faire de la recherche, à comprendre des papiers et bidouiller des logiciels. C'est un travail qui n'aurait pas été possible sans tout le temps que vous avez donné pour discuter, m'aiguiller, me modérer aussi quand j'ai pu partir dans tous les sens. Vous avez parfois dit que vous m'embêtiez pour pas grand chose mais je pense que la somme des "pas grand chose" a été très formatrice : je suis persuadé d'être extrêmement chanceux d'avoir bénéficié d'un tel cadre.

Un travail de recherche comme une thèse c'est des encadrants mais c'est aussi des équipes de recherche qui savent être accueillantes. À Toulouse au sein de l'équipe APO, j'ai eu la chance de partager la F321 avec Jean-Paul "Boris", Antoine B., Bastien, Sophie, Baptiste: même si mes horaires de sommeil ont pas toujours bien correspondu avec les horaires d'ouverture du labo je garderai de très bons souvenirs avec vous mais aussi avec le reste des doctorants dont Théo, Sadok, Peter, Rémy, Valentin, Alexandre et Matthis et des permanents de l'équipe et de l'étage. J'espére pouvoir assister, au moins à distance, à toutes vos soutenances. Merci aussi à SAM et Vanessa parce qu'une partie de l'accueil c'est aussi un super secrétariat. Quand j'ai eu l'occasion de faire des détours à Bordeaux, j'ai eu le plaisir de partager les locaux de l'équipe HIEPACS (maintenant Concace et Topal si j'ai tout suivi): ça m'a fait très plaisir d'être accueilli à 3 reprises par les doctorants là-bas. Je voudrais spéci-fiquement remercier Philippe, Romain, Mathieu, Maxime, Gwénolé et Marek qui font aussi partie du projet SOLHARIS de près ou de loin. J'aimerais aussi remercier Florent Pruvost, Nathalie Furmento et Alexandre Denis qui ont été de supers guides autour de Chameleon, StarPU et NewMadeleine respectivement.

J'aimerais aussi remercier les membres du projet SOLHARIS dans leur totalité pour avoir créé un environnement qui soit propice aux échanges et aux collaborations. C'a été très plaisant de découvrir le monde de la recherche dans cet écosystème et l'ensemble de ces membres peut largement se féliciter d'avoir créer un tel terreau.

Dans une période où y a eu moins de présentiel que d'habitude, je pense que c'est très pertinent de remercier le discord PhD students: ç'a été un endroit super sympa qui m'a permis de découvrir des horizons scientifiques diamétralement opposés. C'est un super espace sur Internet pour celleux qui préparent une thèse et je pense que quiconque y passe saura saluer l'investissement de cette communauté pour maintenir un tel endroit.

Parce qu'ils comptent beaucoup, je souhaite remercier tous les camarades toulousains et parisiens qui sont parfois eux aussi en train de préparer une thèse: Jérémy, Yann, Robin, Louis, Yohan, Grégoire et Maxime. Vous êtes de très chouettes personnes et ça me fait plaisir qu'on ait gardé notre clique depuis l'ENSEEIHT.

Même si je suis définitivement pas assez monté en Bretagne, ça me paraît très important de remercier mes parents, et mes frère et soeur Agathe et Édouard. Je suis un gros ronchon têtu et casanier mais avant de grandir scientifiquement ou quoi que ce soit il faut grandir tout court et ça c'est définitivement grâce à vous.

Pour leur soutien moral constant mais éternellement dédaigneux, je me dois de remercier Bijoux (qui a l'honneur d'être en bas de page) et Cyrano (qui aura l'honneur d'une poignée de croquettes supplémentaire). Bijoux a une santé si fragile que j'ai eu peur qu'elle ne soit plus là pour la soutenance mais elle est encore là quand j'écris ces remerciements et c'est une chose très précieuse.

Nos chats sont probablement très précieux mais il y a quelque chose de plus précieux et d'absolu encore à mon avis et c'est la famille et la maison qu'on est avec Valentine – que j'ai eu l'honneur d'épouser le lendemain de ma soutenance. Valentine a supporté les infinités de répétitions bourrées d'anglais approximatif que j'ai fait depuis le début de la thèse, et avant ça elle m'a supporté 2 ans encore. Ca fait quand même 5 années de vie commune qui ont

su être magiques ; et je peux que te remercier d'avoir reconnu, même devant l'odieux État Français – tout souverein qu'il est – qu'on est faits l'un pour l'autre. Je ne pourrai probablement jamais te remercier suffisamment pour ta patience et tout ton amour dans un seul paragraphe, je vais donc essayer dans toute une vie.

Il y a très certainement beaucoup de personnes que j'oublie dans ces remerciements ; et la profondeur de ma désolation est probablement pas assez grande pour rattraper les hauteurs à laquelle ils – les remerciements – devraient culminer. Dans le doute, pour tout le monde : merci.

# Contents

| $\mathbf{A}$  | bstra           | $\mathbf{ct}$ |                                                                | iii          |

|---------------|-----------------|---------------|----------------------------------------------------------------|--------------|

| R             | ésum            | é             |                                                                | $\mathbf{v}$ |

| R             | emer            | ciemer        | nts                                                            | vii          |

| Co            | onter           | nts           |                                                                | x            |

| Li            | st of           | Figure        | es                                                             | xiii         |

| $\mathbf{Li}$ | st of           | Table         | 5                                                              | xiv          |

| $\mathbf{Li}$ | st of           | Algor         | ithms                                                          | xv           |

| Ez            | kperi           | menta         | l platforms                                                    | xvii         |

| 1             | $\mathbf{Intr}$ | oducti        | on                                                             | 1            |

| <b>2</b>      | Bac             | kgroui        | nd                                                             | 7            |

|               | 2.1             | An eve        | er-complexifying ecosystem                                     | 8            |

|               |                 | 2.1.1         | Evolution of supercomputers hardware                           | 8            |

|               |                 | 2.1.2         | Parallel programming paradigms                                 | 13           |

|               | 2.2             | Runtir        | ne systems and their programming models $\ldots \ldots \ldots$ | 18           |

|               |                 | 2.2.1         | Features of runtime systems implementing task-based            |              |

|               |                 |               | programming models                                             | 19           |

|               |                 | 2.2.2         | The parameterized task graph (PTG) programming mode            |              |

|               |                 | 2.2.3         | The sequential task flow (STF) programming model               | 24           |

|               |                 | 2.2.4         | StarPU                                                         | 26           |

|               |                 | 2.2.5         | Summary                                                        | 29           |

|               | 2.3             |               | numerical linear algebra software and algorithms $\ldots$ .    | 29           |

|               |                 | 2.3.1         | Distributed memory dense linear algebra libraries              | 30           |

|               |                 | 2.3.2         | Scalable algorithms                                            | 33           |

|               |                 | 2.3.3         | Summary                                                        | 42           |

| C( | ONTI         | ENTS                                                 | xi       |

|----|--------------|------------------------------------------------------|----------|

|    | $2.4 \\ 2.5$ | Context of the thesis and related efforts            | 42<br>44 |

| Ι  | Sca          | lability of the STF programming model                | 45       |

| 3  | Sca          | lable STF matrix multiply                            | 47       |

|    | 3.1          | Baseline STF model                                   | 47       |

|    | 3.2          | Proposed extensions to the STF model                 | 49       |

|    | 3.3          | Scalable GEMM with the extended STF model            | 51       |

|    | 3.4          | Implementation                                       | 53       |

|    |              | 3.4.1 STF advanced features                          | 53       |

|    |              | 3.4.2 Handling the general case                      | 54       |

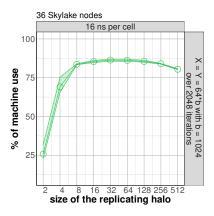

|    |              | 3.4.3 Scalability of the STF model                   | 55       |

|    | 3.5          | Experiments                                          | 57       |

|    |              | 3.5.1 Experimental setup                             | 58       |

|    |              | 3.5.2 Experimental results                           | 59       |

|    | 3.6          | Concluding remarks                                   | 65       |

| 4  | Rep          | olicating data write                                 | 67       |

|    | 4.1          | Motivation                                           | 68       |

|    | 4.2          | Enabling redundant computation within STF            | 69       |

|    |              | 4.2.1 Obtaining local data over multiple ranks       | 70       |

|    |              | 4.2.2 Transferring from alternative ranks            | 72       |

|    |              | 4.2.3 Stencil iterations over a 2D structured domain | 72       |

|    |              | 4.2.4 Summary                                        | 82       |

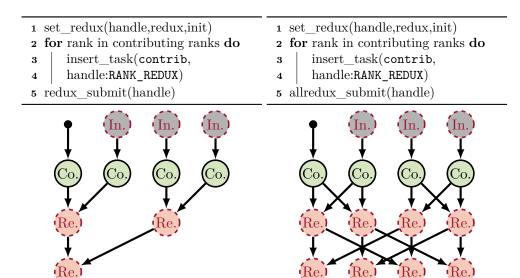

|    | 4.3          | Implementing an all<br>reduce pattern                | 82       |

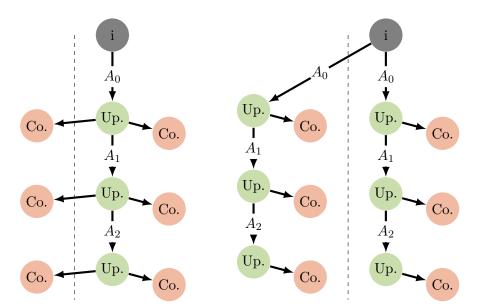

|    |              | 4.3.1 Task-based all<br>reduce STF DAG               | 83       |

|    |              | 4.3.2 3D Cholesky factorization algorithmic variants | 85       |

|    | 4.4          | Concluding remarks                                   | 93       |

| II | Syn          | nmetric operations                                   | 97       |

| 5  | Sca          | lable Symmetric Matrix-Matrix multiplication         | 99       |

| -  | 5.1          | SYMM task-based design                               | 100      |

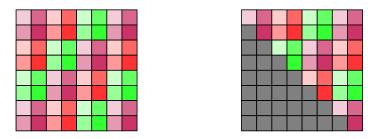

|    | 5.2          | Data distributions for SYMM                          | 101      |

|    |              | 5.2.1 Generalities                                   | 102      |

|    |              | 5.2.2 Stationary-A, general matrix multiplication    | 103      |

|    |              | 5.2.3 Stationary-A, symmetric case                   | 104      |

|    |              | 5.2.4 Summary of AI analysis                         | 110      |

|    |              | 5.2.5 3D variants                                    | 110      |

|    | 5.3          | Experiments                                          | 111      |

|    | -            | 5.3.1 Assessing the arithmetic intensity of SYMM     |          |

### CONTENTS

|                           | 5.3.2 Improving the Cholesky factorization                 | 113 |

|---------------------------|------------------------------------------------------------|-----|

| 5.4                       | Multidimensional scaling and randomized singular value de- |     |

|                           | composition                                                | 114 |

| 5.5                       | Application to RSVD-MDS                                    | 115 |

| 5.6                       | Concluding remarks                                         | 118 |

| 6 Co                      | nclusion                                                   | 119 |

| Scientific Communications |                                                            |     |

| Bibliography              |                                                            |     |

# List of Figures

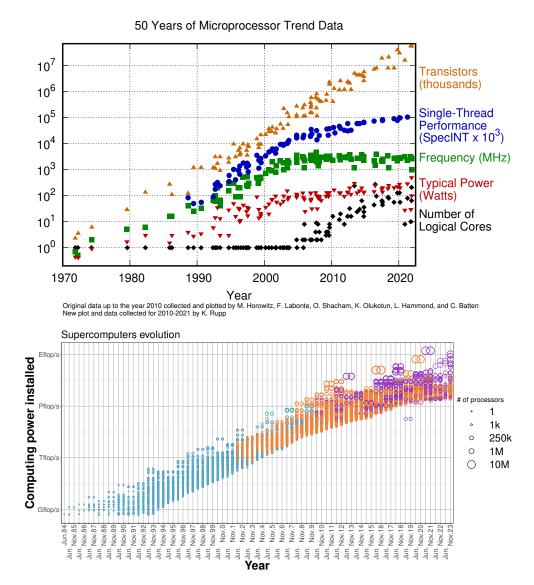

| 2.1  | Computing trends                                                         | 9  |

|------|--------------------------------------------------------------------------|----|

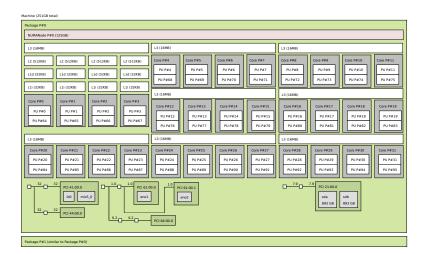

| 2.2  | The topology of a single computing node of Platform A                    | 12 |

| 2.3  | A typical HPC computing node.                                            | 14 |

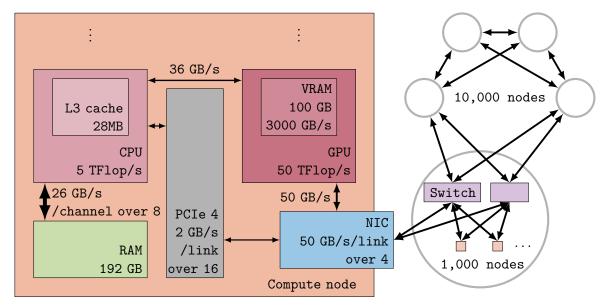

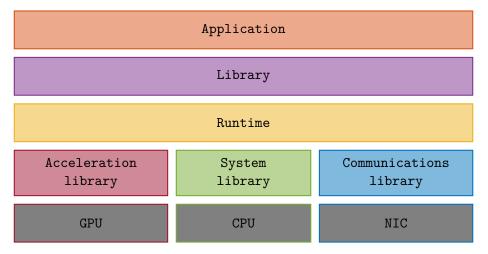

| 2.4  | Typical HPC application software stack.                                  | 19 |

| 2.5  | Diamond graph with 4 tasks.                                              | 20 |

| 2.6  | A DAG distributed over four ranks to execute a distributed mem-          |    |

|      | ory operation                                                            | 22 |

| 2.7  | A pruned DAG focusing on the operation executed by a single rank.        | 26 |

| 2.8  | The 2D Block Cyclic layout                                               | 31 |

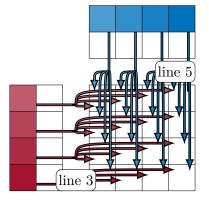

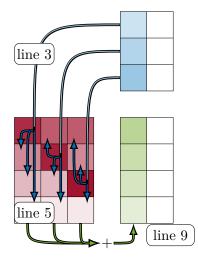

| 2.9  | Pattern of communications of Stationary-C SUMMA                          | 35 |

| 2.10 | Pattern of communications of Stationary-A SUMMA                          | 36 |

| 2.11 | Pattern of communications for the 3D stationary-C SUMMA algo-            |    |

|      | rithm                                                                    | 37 |

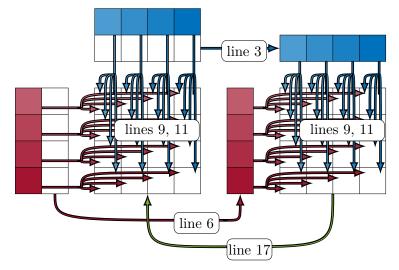

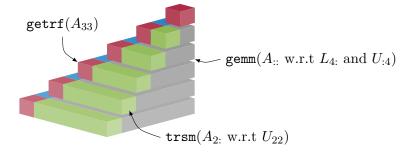

| 2.12 | GETRF algorithm at a given step                                          | 39 |

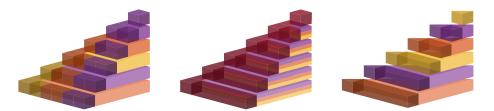

| 2.13 | 3D visualization for factorization algorithms                            | 39 |

| 2.14 | Maps for state-of-the-art factorization algorithms                       | 42 |

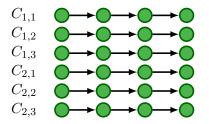

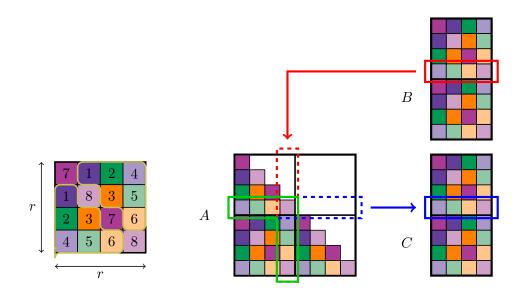

| 3.1  | DAG of the GEMM operation                                                | 48 |

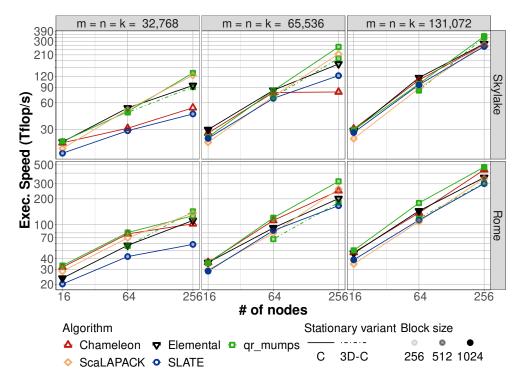

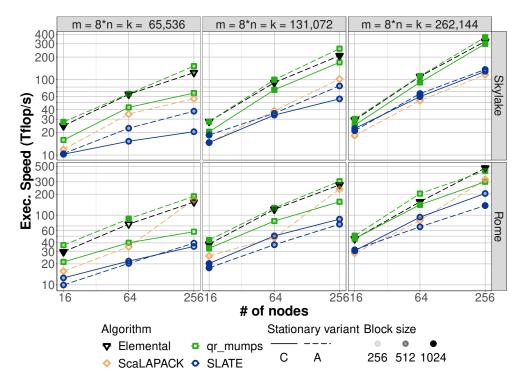

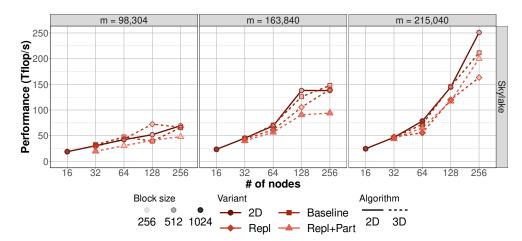

| 3.2  | pGEMM strong scalability benchmark with square matrices                  | 61 |

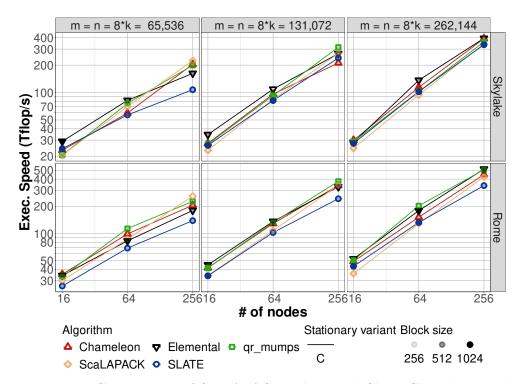

| 3.3  | pGEMM strong scalability benchmark with a larger $C$ matrix              | 62 |

| 3.4  | pGEMM strong scalability with a larger $A$ matrix $\ldots \ldots \ldots$ | 63 |

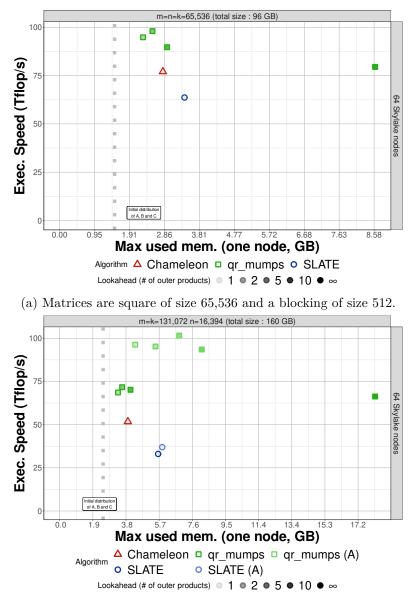

| 3.5  | Memory consumption benchmark for pGEMM                                   | 64 |

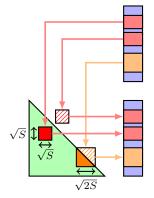

| 4.1  | A computation can be replicated to minimize transfers                    | 69 |

| 4.2  | insert_tasks simplifies the use of the SAME access mode                  | 71 |

| 4.3  | Figure 4.1 submission algorithm.                                         | 71 |

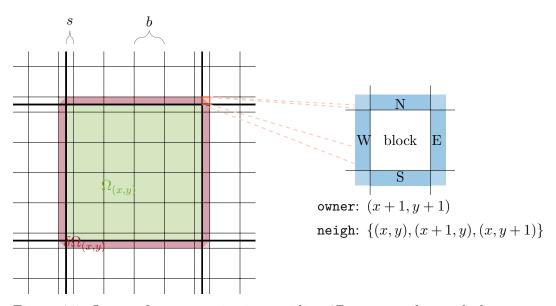

| 4.4  | Cell 2D block layout.                                                    | 74 |

| 4.5  | Layout for communication-avoiding 2D structured stencil algorithm.       | 76 |

| 4.6  | Communication-avoiding irregular update tasks.                           | 79 |

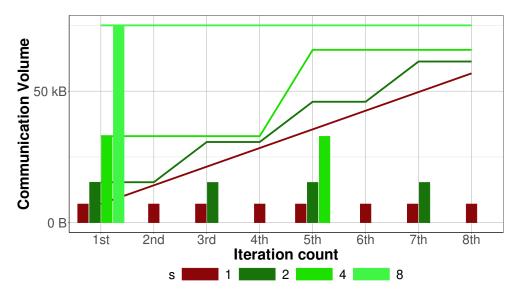

| 4.7  | Communication volume for conventional and communication-avoiding      |     |

|------|-----------------------------------------------------------------------|-----|

|      | approaches for a 2D five-points stencil                               | 81  |

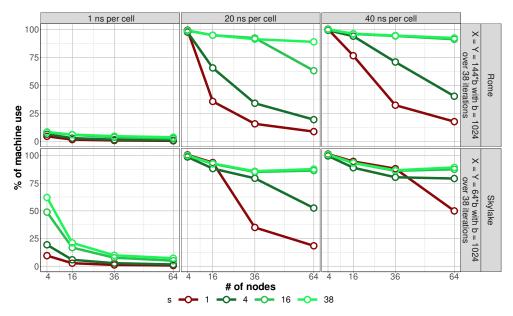

| 4.8  | Strong scalability experiment evaluating classical and communication- |     |

|      | avoiding approaches on a 2D five-points stencilfor stencil            | 81  |

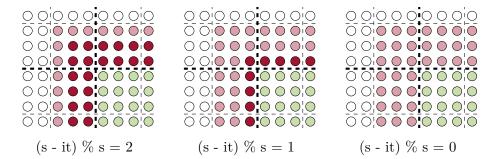

| 4.9  | Different values of $s$ for the communication-avoiding five-points    |     |

|      | stencil                                                               | 82  |

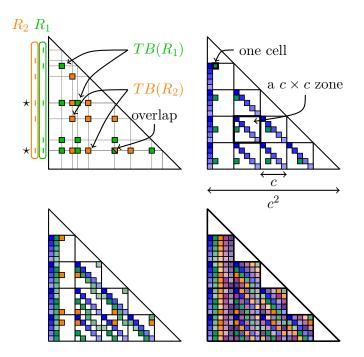

| 4.10 | STF reduce and allreduce operations                                   | 84  |

| 4.11 | 3D distributions with "large" blocks distributed in a round-robin     |     |

|      | way                                                                   | 90  |

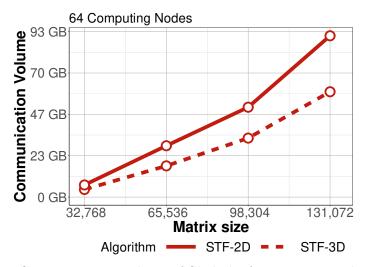

| 4.12 | Communication volume of Cholesky factorization.                       | 91  |

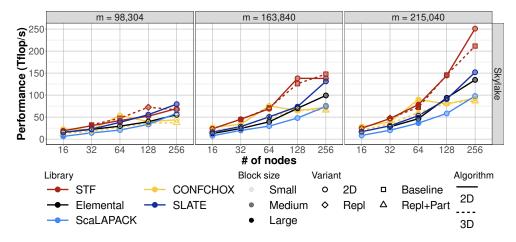

| 4.13 | Strong scalability POTRF STF benchmark                                | 93  |

| 4.14 | Strong scalability POTRF libraries benchmark                          | 93  |

| 4.15 | Double-precision GEMM single-core performance                         | 94  |

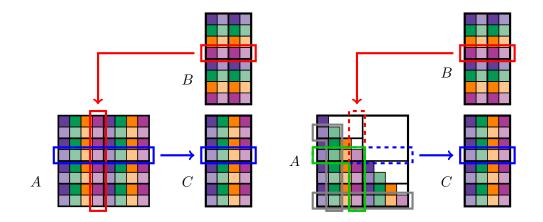

| 5.1  | Pattern of communications for GEMM and SYMM 1                         | 103 |

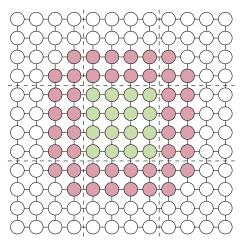

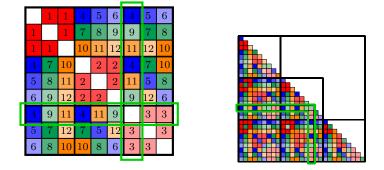

| 5.2  | Symmetric Block Cyclic distribution                                   | 105 |

| 5.3  | Key steps to build the Triangle indices for the Triangular Block      |     |

|      | Cyclic distribution                                                   | 106 |

| 5.4  | Key steps to build the Triangle Block Cyclic distribution 1           | 107 |

| 5.5  | Triangular Block Cyclic distributions                                 | 09  |

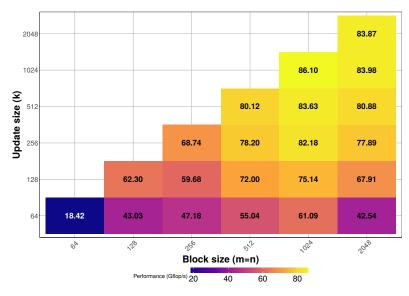

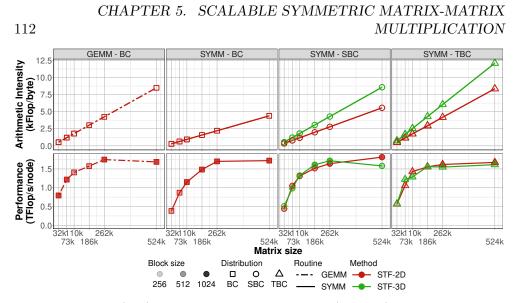

| 5.6  | Benchmark of symmetric distributions using SYMM 1                     | 12  |

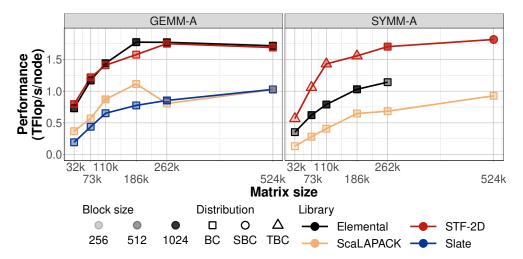

| 5.7  | Benchmark of GEMM comparing with SYMM 1                               | 13  |

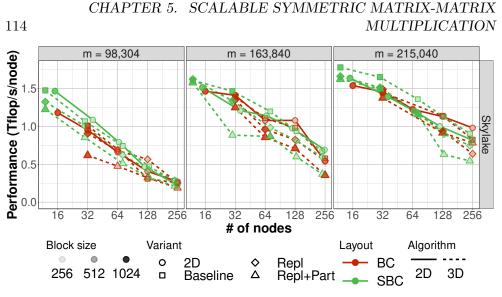

| 5.8  | Cholesky BC vs. SBC                                                   | 14  |

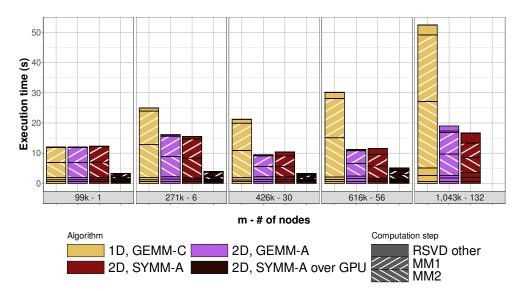

| 5.9  | RSVD benchmark                                                        | 16  |

|      |                                                                       |     |

# List of Tables

| 3.1 | The mapping of tasks and access modes on the C matrix for the stat-A, stat-B and stat-C 3D GEMM algorithms |

|-----|------------------------------------------------------------------------------------------------------------|

| 5.1 | pGEMM and pSYMM communication volume and storage require-                                                  |

|     | ments                                                                                                      |

| 5.2 | Names sample used in the dataset                                                                           |

# List of Algorithms

| 1               | PTG expression of a diamond DAG with 4 tasks                           | 23  |

|-----------------|------------------------------------------------------------------------|-----|

| 2               | STF expression of a diamond DAG with 4 tasks.                          | 24  |

| 3               | Generic statements executed by the rank <b>me</b> in a task-based dis- |     |

|                 | tributed runtime system processing a task T                            | 25  |

| 4               | Registering data with StarPU.                                          | 27  |

| 5               | Inserting user-defined tasks with StarPU.                              | 28  |

| 6               | Registering data with StarPU executed by rank me                       | 28  |

| 7               | Sequential, blocked GEMM.                                              | 34  |

| 8               | Stationary-C SUMMA algorithm as executed by the $(r, c)$ rank.         | 35  |

| 9               | Stationary-A SUMMA algorithm as executed by the $(r, c)$ rank.         | 36  |

| 10              | 3D stationary-C SUMMA algorithm as executed by the $(r, c, h)$         |     |

|                 | rank                                                                   | 37  |

| 11              | Right-Looking 2DBC Cholesky Factorization                              | 40  |

| 12              | Right-Looking 3D Cholesky Factorization                                | 41  |

|                 |                                                                        |     |

| 13              | Parallel GEMM using the baseline STF model                             | 48  |

| 14              | Parallel GEMM using the improved STF model                             | 51  |

| 15              | PA1 executed from the process of rank $r$                              | 74  |

| 16              | Conventional STF implementation of a 5-points stencil.                 | 77  |

| 17              | 5-points stencil STF implementation without replication exe-           | • • |

| 11              | cuted by rank $r$                                                      | 77  |

| 18              | 5-points stencil STF implementation with replication executed          | • • |

| 10              | by rank $r$                                                            | 78  |

| 19              | STF allreduce subgraph submission.                                     | 84  |

| 20              | STF-3D POTRF.                                                          | 87  |

| $\frac{20}{21}$ | STF-3D with diagonal computation replication POTRF.                    | 88  |

| 22              | STF-3D with diagonal computation replication POTRF and par-            | 00  |

|                 | tition of the results of the TRSM.                                     | 89  |

|                 |                                                                        | 00  |

| 23              | STF blocked SYMM                                                       |     |

| 24              | Scalable STF block stationary-A SYMM                                   |     |

| 25              | TBC(c) pattern, on $P = c(c+1)$ nodes                                  | 109 |

# **Experimental platforms**

- A. **Irène-Rome** partition of dual processor AMD Rome 7H12 2.6 GHz (64 cores each, 128 cores per node) hosted by the CEA for GENCI.

- 2,292 nodes with Infiniband HDR100 interconnect

- $R_{\text{peak}} = 11.75 \text{ PFlop/s}$

- 256GB DDR4 RAM per node

- Intel MKL 21.3.0, GCC 12.2.0, OpenMPI 4.1.1

- B. **Irène-Skylake** partition of dual processor Intel Skylake 8168 2.7 GHz (24 cores each, 48 cores per node) hosted by the CEA for GENCI.

- 1,656 nodes with Infiniband EDR interconnect

- $R_{\text{peak}} = 6.86 \text{ PFlop/s}$

- 192GB DDR4 RAM per node

- Intel MKL 21.3.0, GCC 12.2.0, OpenMPI 4.1.1

- C. Jean Zay partition of dual processor Intel Cascade Lake 6248 2.5 GHz (20 cores each, 40 cores per node) hosted by IDRIS for GENCI

- 2,140 nodes, 351 of them with quad GPU Nvidia Tesla V100 16GB, 261 of them with quad GPU Nvidia Tesla V100 32GB

- $R_{\text{peak}}^{\text{CPU}} = 4.87 \text{ PFlop/s } R_{\text{peak}}^{\text{GPU}} = 17.14 \text{ PFlop/s}$

- 192GB DDR4 RAM per node

- Intel MKL 19.0.5

### Chapter 1

# Introduction

The cost of developing software is high and even more so when the objectives are to deliver performance, portability and ease of maintenance at the same time. Supercomputers are commonly employed in a large variety of applications and algorithms that require considerable computing power; these range from classical numerical simulations to data analytics and are widelyused in numerous scientific and industrial fields. The landscape of supercomputer architectures, however, is ever-changing as constructors strive to adopt state-of-the-art technological advances to obtain unprecedented performance. This makes the task of developing high-performance, portable code for highperformance computing a daunting challenge for developers.

In this thesis we are interested in task-based programming models that aim at making the production, porting and maintenance of high-performance computing software easier on existing and future supercomputers.

If typical supercomputers in the 1990s mostly consisted of clusters of singlecore machines, the machines used in the 2020s are vastly different. They host multiple manycore Central Processing Units (CPUs) which are often – but not always – accelerated with other processors such as Graphical Processing Units (GPUs). Writing software that is portable across these different machines is not simply a compilation issue. The correct sets of tools and frameworks which vary between supercomputers have to properly be used to target and extract the performance out of the hardware. One way to observe the evolution of supercomputers is to follow the Top500 semestrial reports. Every semester, the Top500 ranks the most high-performing supercomputers in the world: in 2020 the Japanese Fugaku supercomputer equipped with ARM CPU chips was the fastest supercomputer in History with 442 PFlop/s – for two years. In 2022 it was superseded by the American Frontier equipped with GPUs that reached 1.2 EFlop/s. These two supercomputers have very different architectures that seek to deliver a vast quantity of raw computing power. Their differences *partly* come from how they account for electricity supply, energy cost of cooling, *etc.*: the landscape of supercomputers keeps changing in part to accommodate these physical limits. The related emerging hardware has an impact on the software that is written to use it.

As the hardware gets increasingly complex and varied, porting scientific software over multiple architectures while maintaining performance becomes a challenging task. The programmer has to manage data transfers across processing units and across the network as well as orchestrate the scheduling of operations on the (heterogeneous) processing units. Most parts of the development efforts end up being devoted to these tasks rather than to the implementation of the application. Low-level programming models are used by the programmer to abstract the computer's components and to simplify its use. Community-wide efforts have even made it possible to structure these programming models into standards. For distributed-memory architectures, the Message-Passing Interface (MPI) provides tools to describe data transfers [107]; it is implemented both as free software through OpenMPI, MPICH, etc. as well as by several vendors like Intel. When orchestrating computation on shared-memory architectures, the OpenMP standard is favored because the modification of the code can come off as relatively inexpensive through its directive programming [34]. These standards demand a certain level of expertise to be used efficiently. Additionally their impact on the codebase can become considerable. The same standardization effort has not yet settled for the use of GPUs as many actors are involved (Nvidia [47], AMD [16]) and getting involved (Intel) in GPU manufacturing. Adapting a codebase to GPUs often takes the form of a thorough rewrite to handle data transfers between processing units.

Modernizing software cannot be sustainably achieved by incrementally updating entire codebases. A more durable option is to rely on higher-level abstractions of the computer. Using such programming models make the effort of the programmer less focused on low-level architectural details and more time can be spent expressing computation that are prone to parallelism. Among these programming models, task-based ones are becoming increasingly popular because oftentimes algorithms can be easily expressed as a collection of tasks, that is, elementary operations. Runtime systems such as StarPU [20] or PaRSEC [38] (formerly DAGue) expose an interface of these programming models to effectively discharge the programmer of data management, scheduling, etc.. Among the models proposed by runtime systems, the Sequential Task Flow (STF) model has been well integrated in multiple scientific computing packages. The sequential aspect of this model is an integral part of its accessibility. A vast body of recent literature and software demonstrates that task-based parallel programming models and runtimes allow achieving great performance and portability on shared memory, heterogeneous systems;

among these efforts, many focus on the use of the STF model for implementing mathematical software. Nonetheless, this model has seen a less pervasive adoption when dealing with distributed-memory architectures. Data management at the shared memory level is often entirely delegated to the runtime system, however this hardly translates to the distributed memory case. Managing the distributed memory comes with more challenges regarding the coherency of the system; therefore the efficient mechanisms to transfer data are more intrusive, especially when the algorithms are presented through a sequential flow of tasks. Ultimately the adoption of general purpose runtime systems is more disputable in distributed-memory environment.

Dense and sparse linear algebra software packages are extensively used in numerous high-performance computing applications. Among these, one of the most well-known and widely-used is ScaLAPACK [29]; this library that provides a wide range of dense linear algorithms has been developed at the end of the 1990s using a message passing parallel programming model relying on the MPI standard. Although ScaLAPACK is still the reference in distributedmemory parallel dense linear algebra software its rigid programming model makes it unsuitable for modern supercomputers as it lacks asynchronism, and native support for multicores and accelerators. This has prompted the High-Performance Computing (HPC) community to develop modern ScaLAPACK replacements such as SLATE [57], Elemental [95] or Chameleon [3]; these have taken over ScaLAPACK from a performance and portability point of view although they do not cover an equally large panel of algorithms. Additionally all of the above packages do not support state-of-the-art scalable algorithms. Many recent research efforts from the HPC community focused on the development of scalable algorithms for large-scale supercomputers; these are often referred to as "communication-avoiding" because they increase parallelism by carefully reducing either the volume of data transfers (i.e., the bandwidth usage) or the number of exchanged messages (i.e., the communications latency), possibly at the cost of a modest increase in the operational complexity. In some cases, for example, this is done by rearranging the computing nodes into a 3D logical grid which requires more intricate communication patterns than the standard 2D logical grids [18, 105, 102, 82]. In other cases, the latency of data transfers can be reduced by grouping more messages together which can create additional, redundant computation [70, 45]. These advanced algorithms cannot be straightforwardly implemented in the basic STF model because it lacks the necessary features; this issue can be partially overcome through carefully designed coding where data and communications are manually handled by the programmer but this, in essence, defeats the purpose of using a high productivity programming model like STF. In this work, we focus our attention on relieving programmers from such effort by providing them with a suitable programming model to develop Such a model is expected to help the programmer scalable algorithms. devote more time to the numerical intricacies of the computation they wish to implement.

The objective of this thesis is to extend the task-based programming models capabilities to improve their use in a highly-parallel distributed-memory context. The implementation of such programming models by runtime systems should grant a practical tool to programmers that seek to harness the computing power of supercomputers with millions of heterogeneous cores interconnected by a relatively slow network. The proposed work could be helpful to modernize the computational routines provided by *e.g.* ScaLAPACK. It could also be instrumental in helping algorithm designers conceive new, innovative algorithms that help users make the most out of any supercomputer. Although StarPU is the runtime system used in this thesis, the scope of our work is much wider since the proposed solutions are applicable virtually in any runtime system relying on the STF model in distributed-memory environments. The contributions presented in this manuscript are as follows.

First, we have focused on the implementation of scalable matrix multiplication algorithms through the STF model. We have demonstrated that through the use of three advanced features – reduction operations, tasks mapping and dynamic collective communications – of the STF model it is possible to implement, in a single parameterized code, six different variants of the well-known SUMMA algorithm, namely, stationary-A, -B and -C both in a 2D and a 3D setting. This code is barely more complex than the canonical three nested loops of a sequential matrix multiplication; this ensures great ease of development and maintenance and great portability because this implementation is completely agnostic of the underlying architecture and data distribution. The above-mentioned features were already available in the StarPU runtime system; nevertheless, we have proposed an improvement of the reduction operations features that better suits large distributed-memory supercomputers. We have conducted an extensive experimental campaign on a large supercomputer (up to 256 nodes and 32,768 cores) demonstrating that not only our code is more readable and portable but it achieves performance that is on par with reference dense linear algebra libraries for the same algorithmic variants. Furthermore, because our implementations covers a wider panel of algorithmic variants, overall it achieves better performance when dealing with matrices of unbalanced dimensions.

Second, we have turned our attention to matrix factorization algorithms. In addition to the STF features presented at the previous point, scalable factorization algorithms require two novel features which we have designed and implemented within StarPU. The first is data write replication which enables multiple tasks to concurrently update multiple copies of the same data. Prior to using this feature in a matrix factorization algorithm, we have assessed its effectiveness on a communication-avoiding stencil computation algorithm showing that it can provide considerable performance benefits with only little additions to a classical STF implementation. The second feature is allreduce operations. The combined use of these two features and those in the previous point allowed us to develop portable and compact implementations of 3D matrix factorization algorithms. We have conducted experiments on large platforms to demonstrate that the obtained implementation achieves comparable or better performance than existing reference libraries.

Third, we have further validated the extended STF programming model developed in the previous two points. Although the data distribution certainly plays a fundamental role in the performance and scalability, as we explained above, this programming model allows implementing algorithms regardless of the way data is distributed because the runtime will transparently move data where the corresponding tasks are computed. This makes it very easy to experiment with novel data distributions because only very little modification in the code is needed. Based on this, we have worked in collaboration with experts of scheduling to develop data distribution schemes that are capable of reducing the communication volume in parallel algorithms for symmetric matrices. We have experimented with these novel data distributions on the symmetric matrix multiplication and the Cholesky factorization demonstrating that they can practically reduce the communication volume and, consequently, improve performance especially on relatively small-size matrices when the cost of communications is dominant. Finally, we have assessed the effectiveness of this approach in the Diodon data analysis package<sup>1</sup> which makes a heavy use of symmetric matrix-matrix multiplication in its most computing-intensive parts: we assess the performance of several symmetric layouts analyzing real-world datasets over computing nodes accelerated with GPUs. Note that to target accelerated platforms we do not need to adapt our STF expression but we simply need to provide the runtime with accelerated kernels which are readily available in GPU-specialized BLAS and LAPACK libraries.

The rest of the manuscript is structured as follows: key concepts and elements found in the scientific literature are detailed in Chapter 2 with an emphasis on hardware, how to program it efficiently and what algorithms are programmed over it. In Part I of this manuscript, the ability of the STF programming model to express scalable algorithms is assessed and enhanced. More precisely, Chapter 3 focuses on expressing scalable General Matrix-Matrix multiplication variants. While this routine is ubiquitous in numerical linear algebra, the chapter focuses on bringing the most studied – but not necessarily implemented – scalable state-of-the-art routines under a versatile, efficient expression. This routine requires the definition of essential features: the mapping of tasks, the dynamic detection of collective operations and the use of distributed-memory reduction patterns. While these features are instrumental to scalable algorithms, they do not allow the expression of the presented decomposition algorithms. Thus Chapter 4 focuses on some additional features: one is the replication of task computation explored through

<sup>&</sup>lt;sup>1</sup>diodon git repository https://gitlab.inria.fr/diodon/cppdiodon

the example of 2D Stencil computation, the other is the allreduce collective operation. The sum of these features becomes an extended STF programming model suitable to express scalable matrix decompositions. Part II of this manuscript is composed of a single chapter. Chapter 5 builds on the use of the features proposed in Part I for the development of data distribution schemes for algorithms on symmetric matrices. Chapter 6 concludes this thesis and enumerates some perspectives of the accomplished work.

### Chapter 2

# Background

Plenty of scientific fields have reveled in the use of numerical simulations because they are both confident in the equations that govern their systems and their systems are too big to fit in laboratories. Not only are numerical simulations able to tackle problems that may be hard to set up physically, the precision and scale at which they are able to do so is staggering and everincreasing. However this sustained growth exposes researchers, engineers and the scientific computing community at large to challenges to maintain, port, and efficiently execute their applications on top of the best computers.

To benefit from the latest breakthroughs in hardware, the past trends for software implementations have been to adapt the code by combining programming models together. Section 2.1 presents the leading architectures that have been manufactured over the three past decades. Porting code over these architectures is an enterprise that becomes more challenging as the software stack gets unreasonably complex and hard to maintain, therefore difficult to expand. To address this issue runtime systems that act as a layer of abstraction between applications and both the hardware and some specialized libraries are recently being favored. These runtime systems and corresponding programming models are described in Section 2.2. They meet most requirements to address the efficient use of parallel supercomputers, especially at the shared memory level. Indeed, they commonly provide programming models that have proven relatively easy to use, productive and efficient in many contexts. Section 2.3 focuses on two omnipresent algorithms in numerical linear algebra: matrix-matrix multiplication and matrix factorization. Being able to design and implement algorithms that are scalable across platforms is paramount to use supercomputers properly. Nonetheless, the latest iterations of these scalable algorithms are still developed through home-brewed, specialized abstraction layers despite the existence of general runtime systems. It appears runtime systems lack features in their programming model that make optimizations for scalability easy to leverage.

### 2.1 An ever-complexifying ecosystem

The need for computing power has been ever-increasing as faster computers can execute programs over larger inputs, sometimes in a shorter time. The programs ran on supercomputers are used in computing-intensive scientific fields to apprehend large-scale phenomenons or in industrial settings to optimize the design of new products. Breakthroughs in hardware manufacture have been a constant driver of scientific computing performance. Figure 2.1 (top) illustrates how, before 2005, processors' capabilities were growing exponentially. From 2005 onwards, Moore's law keeps proving itself valid as the number of transistors grew exponentially yet the performance of a single computing thread has stalled as the frequency of the CPU clock stagnates.

Nonetheless, one can observe that the growth in computing power for supercomputers keeps its exponential pace in the bottom of Figure 2.1. Parallelism has been the key principle to maintain such trends. The exaflop barrier was breached in 2022 with the Frontier supercomputer by assembling a system where parallelism can be leveraged at many levels from the Central Processing Units (CPUs) all the way up to the Network Interface Controllers (NICs). When using modern computing centers, a programmer wants to take advantage of all the different levels of parallelism to run their program efficiently. To achieve this goal they typically rely on a great deal of abstractions. The programming language they use to write their source code is a first abstraction – as it provides a translation to machine code – but what they often rely on are specialized libraries or middlewares that leverage the actual architectural properties of the computer they use. Such libraries typically focus on a specific component or technology in the computer: from the efficient use of a single core to the data transfers over various channels, from the orchestration of computation over many cores to the use of dedicated hardware. However, because of the expertise required to use these libraries and the very large scope they encompass, the source code resulting in their usage may come off as tough to read, troublesome to profile and prone to maintenance issues.

### 2.1.1 Evolution of supercomputers hardware

Supercomputer constructors have sought after ways to maintain a steady increase in computing power. In doing so, they evolved from the canonical single-core machine to clusters of multicore accelerated nodes. This modification of supercomputers has been incremental, with prominent architectures often lasting for about a decade. Latest supercomputers hold thousands of computing nodes each housing hundreds of computing cores, amounting in

Figure 2.1: Computing trends. **Top:** Microprocessor trends between 1970 and 2020 https://github.com/karlrupp/microprocessor-trend-data; **Bot-tom:** Top 500 between 1984 and 2023 https://top500.org/

petaFlop/s or even exaFlop/s of computing power. In this section we will briefly discuss the main technologies that are still in use on modern supercomputers.

#### 2.1.1.1 Clusters

Starting in the 1990s, as a single computing node became a commodity, supercomputers were built as the aggregate of several computing nodes linked through a high-performance network. The ability to efficiently distribute computations over these *clusters* of computing nodes – often referred to as *distributed-memory* parallel computers – was pivotal to increase supercomputers' computing power. This decade of supercomputing saw a fierce competition in vendors' products as well as a prolific literature to study distributed memory algorithms.

Linking up computing nodes through a network is a high-stake endeavor since the channels used to communicate data between CPUs are orders of magnitude slower than transfers made inside the CPU chip. Therefore, the organization of interconnections between computing nodes has been a key concern when building supercomputers. Indeed one of the metrics used to measure the cost of a running supercomputer is the number of network links it requires: it would be expensive to link every compute node in a cluster with one another but it is possible to link them indirectly. These topological questions rely on dedicated hardware that routes data transfers – *switches*. These switches interconnect parts of a single cluster with one another.

#### 2.1.1.2 Multicores

The so-called golden age of computer architecture began around the 60s and, for many years, thanks to an effective interplay between Moore's law [87] and Dennard scaling [53] allowed for producing processors that were increasingly denser, i.e., more capable, and with a higher frequency with no or little increase in the energy consumption. During this period, simply upgrading the processors of a computer lead to satisfactory performance improvements without further efforts from programmers.

In the beginning of the years 00s the Dennard scaling came to an end: the microprocessors' frequency could not be pushed any further without encountering thermal dissipation and energy consumption issues. Despite Moore's law being still valid, improving processors' performance under these constraints became more challenging. Instruction level parallelism (ILP) techniques such as vectorization or deep pipelining certainly offered a way to push performance a bit further but certainly not at the exponential rate observed in the previous decades.

It is at this moment that computing architectures switched to CPUs equipped with multiple computing cores. Instead of linking computing cores through the network, a single processor was now built equipped with multiple cores. This design makes it possible to parallelize instructions at a higher level than ILP: sets of instructions accessing different memory addresses can be executed by different cores. This essentially leads to thread-level parallelism (TLP) where a thread is a lightweight process run over a single core. Because the buses inside a computing node are orders of magnitude faster than links over the network, this design is relatively efficient to move data between fast memory such as Random-Access Memory (RAM) and computing units.

This major technological shift lead to a sharp discontinuity with the past which can be easily seen in Figure 2.1 (top). The multiplication of computing cores came with newer hardware challenges. It must also be noted that, if multicore systems are able to process instructions concurrently, the rate at which each core in the system performs stagnates and, in general, is lower compared to an old-generation single-core; the reason for this trend lies in the need to respect a power consumption budget which is shared across cores.

CPUs are equipped with cache memories that store some data closer to the Arithmetic and Logical Units (ALUs) than the relatively slow RAM. In multicore computers, this cache is typically shared among multiple cores at some level (typically the farthest from CPU). Although this allows for faster communication between cores, as a shared resource, memory accesses become the subject of contention and may create bottlenecks that degrade performance. Furthermore, modern supercomputer nodes are often equipped with multiple multicore processors possibly in a non-uniform memory architecture (NUMA) setting which makes the speed access to data irregular.

Inside modern supercomputers, a single computing node can hold as many as hundreds of cores. Figure 2.2 shows the result of the lstopo utility program delivered by hwloc when executed on Platform A. This visualization makes the hierarchy and complexity of the machine apparent. On such a platform, memory accesses are non-uniform between two cores selected randomly. Non-Uniform Memory Accesses (NUMA) domains have to be taken into consideration when allocating memory over such a machine.

This technological rupture with the past came with many daunting challenges for programmers and users of intensive computing. Indeed, upgrading to a new processor does not lead to a performance improvement for sequential codes anymore; many codes and libraries had to be adapted or rewritten with parallelism in mind.

### 2.1.1.3 PU specialization

At the beginning of the 2010s, the supercomputers started to be equipped with accelerators and, more specifically, with Graphical Processing Units (GPUs) to increase their computing power. This can be seen as a consequence of the end or the slowdown of Moore's law – an issue that can be mitigated through specialization of processing units. These specialized processing units take

Figure 2.2: The topology of a single computing node of Platform A.

advantage of data parallelism to map instructions over numerous ALUs. A GPU architecture is designed to process massively parallel workloads. Because of their design, GPUs are especially suited for operations that deal with heavy data streams while requiring a low amount of branching and conditions. This hardware specialization is of great interest for scientific computing because applications such as simulations rely on the processing of large data inputs such as arrays of floating-point numbers. GPUs are fundamentally well suited to deal with these regular problem formulations where dense numerical linear algebra is used. However, they often fail to obtain as impressive speedups over CPUs when dealing with irregular or sparse computations. In most cases, GPUs extend the reach of tractable numerical problems but they have to be used in combination with CPUs.

GPUs are often equipped with their own dedicated RAM – often called Video RAM or VRAM – and they compute instructions using data stored therein: CPUs are used to command the data transfers from the RAM to the VRAM or command the allocation of memory in the VRAM. While the GPU memory is typically smaller than RAM, the available bandwidth between this dedicated memory and the GPU cores is higher than the bandwidth between RAM and CPUs. GPUs require such dedicated memory and high memory bandwidth because of the acceleration they provide over large chunks of memory: large bandwidth is a requirement to move data across the multiple ALUs found on the GPU chip.

Because of their large computing power and their design that target massive data parallelism, GPUs are better suited to operate on larger chunks of data. This difference with CPUs is often referred to as the granularity of the operations. A single CPU core is equipped to efficiently process fine-grain operations while a GPU chip is equipped to efficiently process coarse-grain operations. When multiplying matrices, a modern CPU core can reach peak performance with hundreds of millions of flop (equivalent to multiplying square matrices of size 512) however a GPU would require a significantly larger workload to perform at its peak – about three orders of magnitude more.

Nvidia has been a key manufacturer in the beginning of the 2000s however major manufacturers are trying to seize the GPU market. Two of the principal actors are AMD and Intel.

### 2.1.1.4 Summary

In the course of the last three or four decades, three main hardware technologies have become dominant and widely-adopted in the domain of highperformance computing. The first is distributed-memory parallel computing achieved by connecting multiple computing nodes through a high-performance network. The second is represented by multicore processors. The third corresponds to the advent of accelerators (most commonly GPUs). In order to achieve high-performance at a very large scale, all these technologies are often combined in modern supercomputers. Although world-grade supercomputers do not use dedicated processing units such as the Fugaku. Nodes of a modern supercomputer, illustrated in Figure 2.3, are commonly equipped with multiple multicore processors, often in a NUMA setting, and multiple accelerators or GPUs. These processing units are connected to each other using different types of interconnects and are attached to different memories. These nodes are assembled in very large numbers thanks to dedicated, high-performance networks in order to achieve great performance and scalability. As a result, modern supercomputers are extremely *heterogeneous*: they are equipped with numerous processing units that have different speeds and capabilities, memories with different capacities, bandwidths and latencies and interconnects with different bandwidths and latencies. Therefore, although all these technologies allow increasing performance on paper, in practice they throw an incredible burden on the programmers who have to deal with all this complexity.

### 2.1.2 Parallel programming paradigms

Because of the incremental development of hardware architectures, the software stack used to program supercomputers has become incrementally complex over the years. To face this complexity, many approaches have been proposed that address different layers of the computer architecture. Through community-wide effort, some of these approaches were standardized and became adopted across scientific computing applications. MPI and OpenMP are such open standards which have been widely-implemented by vendors of hardware to deliver high performance across different machines. The use of GPUs to accelerate computers primarily relies on proprietary libraries that required more involvement from their users than standardized frameworks. Nat-

Figure 2.3: A typical HPC computing node inside a cluster of thousands of nodes. Data transfer speeds and computing speeds are indicative and only reflect adopted technologies such as PCIe4, DDR4, Infiniband HDR, etc.

urally when an application undertakes refactoring to use one single vendor's hardware, its efforts are not rewarded with performance portability across all GPUs. Ongoing initiatives aim to provide open, common standards but they are not yet widely adopted. The large combination of hardware technologies means that programmers face a challenge when trying to port their code over a large range of computer architectures. In this exercise, they must rely on the parallel programming paradigms presented in the following sections.

### 2.1.2.1 Message-passing paradigms

The Single Program Multiple Data streams (SPMD) approach has been popularized widely as it provides a way to tackle the implementation of a distributedmemory program. By using the proper distributed-memory paradigms, programmers can write one single program using various function calls to transfer data across the network. When they compile their program and command its execution over multiple instances, each instance can behave as either the receiver or the sender of the expressed data transfers – or even both when collective operations are invoked. Each computing node equipped with a single computing core would execute the compiled code concurrently. For a long time, SPMD approaches were largely platform-dependent and a plethora of ways to use the network existed. Because of the relative speed of the network, it was often satisfactory to rely on Bulk Synchronous Parallel (BSP) execution model to design algorithms: applications were divided into synchronization, communication and computation phases and each was achieved simultaneously.

The Message-Passing Interface (MPI) standard emerged in the early 90s in a community-wide effort to design software libraries to level the implementation of distributed-memory programs [107]. The MPI standard consists of routines wrapping-up essential communication primitives, including point-topoint as well as collective data transfers, that can be called with a certain level of finesse if the user desires – for instance, explicit support of asynchronism. The MPI standard exposes several key concepts that programmers can harness. One of these concepts is the *communicator* which is a set of processes that can exchange with one another, possibly using collective communication operations such as reduce, gather, all reduce, etc. Within a communicator, each process is given a numerical identifier which we call rank in order to express communications more conveniently. Communicators can be split into subcommunicators of fewer processes. Through MPI, users essentially design ways to split ranks into various, hopefully independent, communicators to express the data transfers they require. Over the years, a large literature was produced to provide scalable algorithms for the implementation of efficient communication schemes: their goal was to give the ability to execute them, however complex they could be, at an arbitrary large scale over any network topology.

Other paradigms were instrumental in leveraging distributed-memory computing power such as Partitioned Global Address Space (PGAS) – which has been implemented for C through the Unified Parallel C (UPC) extension [43] or for Fortran through coarrays (since the 2008 standard). The main difference between MPI and PGAS is that PGAS focuses on providing a logical partitioning of the memory such that retrieving a remote piece of data is easily expressed as a one-sided communication. As such, the approach is easier to manage for the programmer because it hides the need to describe communication patterns in a precise manner where the receiver and the sender have to express the same communication on their respective sides. Note that the one-sided communications were eventually incorporated into MPI – without the same focus on logical partitioning that PGAS typically provides.

Many algorithms, including numerical linear algebra algorithms, were designed in terms of MPI or PGAS paradigms: this is detailed in Section 2.3.2.

#### 2.1.2.2 OpenMP

Although it must be noted that shared-memory parallel computers existed already before multicores, it is only with the advent of this technology that shared-memory parallelism became ubiquitous and unavoidable. Therefore, since the mid 00s, many existing *multithreading* solutions were revamped and many new ones were proposed to make efficient use of this new technology. Some existing approaches such as Posix threads (or pThreads) became widely adopted but turned out to be too low-level to allow for high productivity; proprietary solutions were also proposed, such as Intel TBB [96] but did not meet the broad interest of the HPC community. Among the other existing approaches, we can cite Cilk [33] or Charm++ [79] which are still being used although only by a limited number of programmers.

Among all the existing options, certainly the one that is the most widely adopted is OpenMP, a standard that was first submitted in 1997 [35] and considerably improved and extended over the years. While there is an inherent difficulty to exhibiting parallelism in applications, programming models such as the one offered in the OpenMP standard allow users to simply decorate their code through directives to take advantage of the multiple cores. Such a directive programming approach is convenient for the programmer because they get to point out what statements are prone to parallelism – not modifying their initial serial code much – while letting the compiler produce machine code that will be efficiently dispatched across many cores.

OpenMP relies on a *fork-join* programming model where a code is made of alternating sequential and parallel sections; within a parallel section multiple threads exist which can share work, commonly, through the use of worksharing constructs. The most popular worksharing construct, especially in the early OpenMP standards, is certainly the parallel loops directive which became so widely used that OpenMP was often, although incorrectly, referred to as "loop parallelism". Through the years, the OpenMP standard has been considerably extended and improved. One major step is represented by the introduction of task parallelism in the 3.0 version of the standard, a feature that we will deeply discuss in the remainder of this document. More recently, support for accelerators was also introduced in OpenMP v4.0 as we will explain in the next section.

Although, as explained, many sequential codes had to be rewritten using some multithreading approach in order to take advantage of multicores, parallel codes based on message passing could take advantage of this new technology right away: communications between cores sitting in the same node do not correspond to messages sent through the network but, rather, to copies in the shared memory. Nevertheless, because of these relatively expensive and avoidable copies, and because of its essentially synchronous nature, the MPI model does not allow taking full advantage of shared-memory parallelism. For this reason, many, if not most, codes designed for large scale supercomputers are based on a combination of MPI and some multithreading technology, often OpenMP. This combination is not always easy to achieve and multiple approaches exist. It must be noted that the MPI standard was recently (in MPI 3.0) extended with features that are specifically designed to achieve higher performance on shared-memory parallel computers. Nevertheless, the MPI+OpenMP approach still seems to be the most widely adopted.

#### 2.1.2.3 Programming accelerators

Programming accelerators such as GPUs, often relies on the use of proprietary solutions. For example, one strong actor in the GPU sector is Nvidia that provides the CUDA programming toolkit to program their GPUs [47]. This toolkit includes compilers that provide an extension of the C/C++ language for distributing computations over the GPU cores, debugging and profiling tools and performance libraries, such as cuBLAS, a GPU-optimized implementation of the Basic Linear Algebra Subprograms (BLAS) library. As explained earlier, GPUs commonly have their dedicated memory which is faster than the main memory but of limited size; furthermore, some operations cannot be run efficiently on GPUs or are very hard to implement. Therefore, GPUs are typically used in combination with CPUs, which means that data has to be moved, more or less frequently, from CPU to GPU memory. Cuda comes with data management functions that allow allocating memory on the GPU and moving data from CPU to GPU and the other way around. It must be noted that these data movements make coding for GPUs relatively hard and, despite they happen through fast interconnects, their cost can, at times, overcome the benefit of offloading computations to GPUs.

Cuda is property of Nvidia and, therefore, does not work on GPUs produced by other vendors. Despite this lack in portability, there has been a strong motivation from the HPC community members to adapt their own application using Cuda which has been, for many years, the most widely, if not the only, adopted technology. Other prominent industrial actors such as AMD have recently jumped into the general-purpose GPU (GPGPU) market and have produced boards that are used (and increasingly so) on supercomputers among the most powerful ones. AMD offers the ROCm platform [16] that includes the Heterogeneous Interface for Portability (HIP) layer to target its GPUs as well as other ones. Intel recently delivered a series of consumergrade GPUs: it is easy to conceive that computing-intensive applications may need to rely and port on a plethora of specialized hardware in a relatively near future. For this reason efforts have been pursued, such as OpenACC [89] or OpenCL [88], to provide a standard and portable programming interface for GPUs. More recently, the OpenMP standard (since v4.0) was extended with directives for programming accelerators but support from compilers is still lacking or incomplete. Other notable efforts to improve the portability of codes across GPUs include portability/abstractions layers such as SYCL [64] or Kokkos [110]. Although all these solutions provide greater portability than proprietary options, they fail to achieve the same performance.

Large code bases have often been rewritten to target trending architectures that deliver an increasingly large amount of computing power. These new architectures come with components that can only be used through specialized packages that limit the portability when adapting applications to supercomputers. Portability may require considerable effort because architectural breakthroughs force programmers to reconsider the algorithms they implement. The diversity of supercomputers ecosystem has not been interrupted yet, so software packages will need to adapt further. The next section details the middleware – specifically runtime system – that is being considered to mitigate the cost of this adaptation.

# 2.2 Runtime systems and their programming models

In the same vein as supercomputers have become an assembly of different technologies (i.e., distributed memory, multicores and accelerators), typical modern high-performance computing codes are implemented through a complex combination of programming models and paradigms such as MPI+Open-MP+X (where X refers to any technology used to program accelerators). This mostly happened for two reasons. The first is historical: as new hardware technologies were introduced, existing codes were incrementally extended with the corresponding programming solutions. The second lies in performance: in an attempt to squeeze the last GFlop/s out of their expensive machines, HPC practitioners often prefer to have direct access to all the hardware features through dedicated programming solutions.

As the landscape of HPC architectures becomes increasingly varied and heterogeneous, the inherent difficulty to maintain a software stack that weaves multiple paradigms addressing each component of a modern supercomputer becomes unsustainable. As a consequence, the HPC community has recently leaned toward runtime systems as a way of achieving high productivity and performance portably across many architectures. Runtime systems, or more simply *runtime*, act as a layer between the application and the hardware as pictured in Figure 2.4; by hiding most of the low-level architectural details, they provide the programmer with the vision of an abstract parallel machine and a unified programming model and interface to write code independently of the hardware features. This allows for a much higher productivity and better separation of concerns; applications or mathematics specialists can focus on the development of efficient and scalable algorithms without the burden of dealing with low-level architectural details, whereas runtime experts can develop sophisticated mechanisms and methods to deploy the workload efficiently on the available computing resources.

Numerous runtime systems have been developed over the years; an extensive review of runtime systems is given by Thibault [108]. Our work focuses on runtime systems that rely on task-based parallelism, specifically through the use of the sequential task flow (STF) programming model, which we describe in the next sections.

## 2.2. RUNTIME SYSTEMS AND THEIR PROGRAMMING MODELS 19

Figure 2.4: Typical HPC application software stack.

# 2.2.1 Features of runtime systems implementing task-based programming models

Although many, high-level, unified, parallel programming models exist, taskbased parallelism and runtime systems are becoming increasingly popular in the high-performance computing domain due to their effectiveness and relative ease of use. In this programming model, the workload is expressed as a collection of *tasks*, that is, elementary operations on data. These tasks are arranged in a directed acyclic graph (DAG) that expresses their mutual dependencies and, consequently, the available parallelism: tasks lying on different paths of the dependency graph are independent and can thus be executed in any order and, possibly, concurrently. The main advantage of this programming model is that porting a code on a new architecture mostly consists in producing optimized (sequential) implementations of tasks, provided that the runtime has been extended to support the new machine. In many cases, these optimized implementation of tasks are available off the shelf within vendor libraries such as BLAS or LAPACK. For a given task type the programmer can provide several implementations, one for each type of worker that is entitled to execute tasks of this type; as such, depending on the scheduling policy and the availability of resources, the runtime can schedule the execution of a task on either worker for which an implementation was provided.

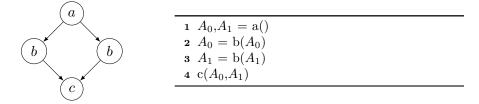

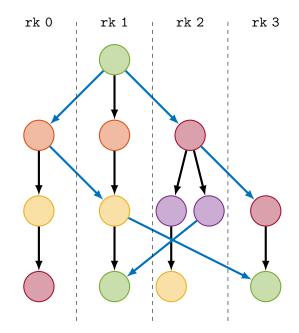

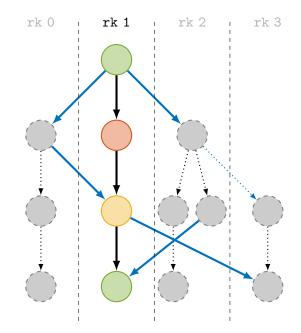

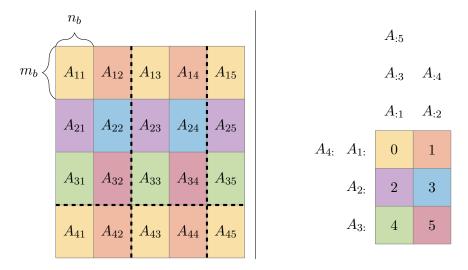

A very simple example of a DAG is provided by the diamond graph illustrated in Figure 2.5 (*left*) which represents the workload associated with the code in the right part of the figure. This DAG includes four tasks of types a, b and c. Tasks b are two different instances of the same operation but on different data and lie on the same level in the graph. From the DAG it is clear that once a is completed both b tasks can be executed and c can only be executed when both b tasks are completed themselves. In this example b could have a Nvidia GPU implementation provided by a  $cuda_b$  function and a classical CPU implementation provided by  $core_b$ ; in this case the runtime can choose to execute the two *b* tasks simultaneously on a CPU core and on a GPU.

Figure 2.5: Diamond graph with 4 tasks. Left: the DAG that can be scheduled with each task assigned a letter. **Right:** a pseudocode of a sequential execution. Note that tasks b which are on the same level in the DAG can commute.

Numerous runtime systems rely on task-based parallelism, the most popular among them certainly being OpenMP. Although they might offer different features and achieve different performance and scalability, they all have to face the same challenges and, therefore, present the same, or comparable, components which we briefly describe below.

**Programming model and interface** The programming model and interface are certainly two key ingredients of any runtime including task-based ones. Through the programming model and interface, the runtime provides programmers with a way of expressing their workload in the form of a DAG of tasks. They must be sufficiently expressive to offer high productivity which means that the programmer must be able to express complex algorithms simply and independently of the low-level architectural details to achieve great portability.