# A performance projection approach for design-space exploration on Arm HPC environment

Clément Gavoille

#### ▶ To cite this version:

Clément Gavoille. A performance projection approach for design-space exploration on Arm HPC environment. Other [cs.OH]. Université de Bordeaux, 2024. English. NNT: 2024BORD0004. tel-04468260

## HAL Id: tel-04468260 https://theses.hal.science/tel-04468260

Submitted on 20 Feb 2024

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## THÈSE PRÉSENTÉE À

## L'UNIVERSITÉ DE BORDEAUX

ÉCOLE DOCTORALE DE MATHÉMATIQUES ET D'INFORMATIQUE

par Clément Gavoille

POUR OBTENIR LE GRADE DE

## DOCTEUR

SPECIALITÉ: INFORMATIQUE

Approche de projection de performance pour l'exploration de paramètres de conception de l'environnement Arm en HPC

> Dirigée par Brice Goglin Co-dirigée par Emmanuel Jeannot

Soutenue le : 15 janvier 2024

#### Devant la commission d'examen composée de :

| Pr. Raymond NAMYST   | Professeur, Université de Bordeaux                    | Président du jury     |

|----------------------|-------------------------------------------------------|-----------------------|

| Dr. Brice Goglin     | Directeur de recherche, INRIA                         | Directeur de thèse    |

| Dr. Emmanuel Jeannot | Directeur de recherche, INRIA, Université de Bordeaux | Co-directeur de thèse |

| Dr. Aleksandar ILIC  | Assistant professor, Université de Lisbonne           | Rapporteur            |

| Pr. Olivier Sentieys | Professeur, Université de Rennes                      | Rapporteur            |

| Pr. Estela Suarez    | Professeure, Université de Bonn                       | Examinatrice          |

| Dr. Hugo Taboada     | Ingénieur-chercheur, CEA, DAM, DIF                    | Encadrant/Invité      |

| M. Conrad HILLAIRET  | Ingénieur, Arm                                        | Invité                |

## Remerciements

En premier lieu, je remercie mes directeurs de thèse, Brice Goglin et Emmanuel Jeannot, d'avoir accepté de diriger ma thèse mais aussi d'avoir su être présent malgré une première année sans avoir pu avoir d'échanges directs à cause des restrictions sanitaires.

Ensuite, je souhaite remercier de tout cœur Hugo Taboada de m'avoir encadré, accompagné et conseillé tout au long de ma thèse mais aussi sur mon stage de fin d'études d'ingénieur. Je suis très heureux d'avoir été ton premier doctorant.

Je voudrais aussi remercier Fabrice Dupros, Patrick Carribault et Conrad Hillairet qui sont de belles rencontres faites au cours de ma thèse et les remercie pour leurs conseils, nos discussions ainsi que leur participation dans mon encadrement.

Je remercie également l'ensemble des membres de mon jury pour avoir accepté, pour leurs questions et leurs retours sur mon travail.

Je souhaite aussi remercier les stagiaires, doctorants ainsi que l'ensemble des collègues que j'ai eu la chance de côtoyer à Teratec mais aussi au sein de l'équipe TADAAM de l'INRIA Bordeaux pour les échanges, pauses cafés, parties de jeux,

..

Sur un plan plus personnel, je voudrais remercier mes amis de Clématie pour avoir toujours été là pour moi même si je n'ai pas rendu la chose facile.

Ensuite, je veux remercier mes parents pour tout ce qu'ils ont fait pour moi, pour avoir éveillé mon esprit scientifique et encouragé dans cette voie. Sans eux, je n'aurais jamais pu être celui que je suis aujourd'hui et je leur dédie donc ce manuscrit.

Je souhaite aussi remercier mes trois frères: Nicolas, Antoine et Guillaume pour tout ce qu'on a partagé et ce qu'on partagera dans le futur. Je pense aussi à mes neveux et nièces: Cassandre, Marc et Constance dont l'arrivée a égayé mes années d'études.

Enfin, je veux remercier Cassandra qui fut surement la plus belle rencontre que j'ai pu faire pendant ces années de thèse. Sa présence et son soutien sont, sans aucun doute, ce qui m'a permis d'accomplir ce travail. J'espère compter sur ton soutien pour longtemps encore, tout comme tu sais que tu pourras compter sur le

mien.

Bien sur, il y a encore beaucoup de personnes que je n'ai pas pu remercier, je le fait donc ici: Merci à tous d'avoir rendu pas si solitaire cette aventure qu'est le doctorat.

**Titre** Approche de projection de performance pour l'exploration de paramètres de conception de l'environnement Arm en HPC.

Résumé La science d'aujourd'hui utilise de plus en plus la simulation pour modéliser et comprendre le monde qui nous entoure. Pour permettre à celles-ci d'être plus rapides, précises et modélisant de plus grand phénomènes, les scientifiques utilisent des supercalculateurs, domaine d'expertise du Calcul Haute-Performance. Or, à mesure que la demande en puissance de calcul grandit, ces machines se doivent d'être de plus en plus performantes. Seulement, la réduction de la taille des transistors prévue par la loi de Moore ne suffit plus à diriger l'évolution des processeurs, noyau de la puissance des supercalculateurs. Ainsi, pour continuer à être capable de répondre à cette demande, ces machines deviennent de plus en plus complexes. Et les performances des applications HPC dépendent des interactions entre les nombreux comportements des applications, les architectures des processeurs de plus en plus complexes et des choix faits par les différentes piles logicielle. Les efforts à fournir pour l'optimisation des performances des applications sur les machines sont donc de plus en plus importants.

Une solution pour simplifier ces efforts d'optimisation et obtenir de meilleures performances des applications est de rassembler l'ensemble des acteurs du HPC dans un environnement de **codesign** pour la conception des futures machines. Ainsi, dans un tel environnement où les choix faits par les concepteurs sont dirigés par les intérêts des applications, les processeurs et la pile logicielle seront adaptés aux besoins des futurs utilisateurs. Cela est encore plus important depuis la récente arrivée de l'environnement Arm en HPC, représentant 10% de la puissance de calcul totale du Top500 avec seulement 6 machines. En effet, celui-ci offre une plus grande liberté aux constructeurs dans les choix des caractéristiques des processeurs. Seulement, dans un tel environnement de codesign, il est nécessaire d'utiliser une approche de prédiction de performance prenant en compte l'impact des choix faits par l'ensemble des acteurs pour pouvoir effectuer une exploration viable de l'espace de conception.

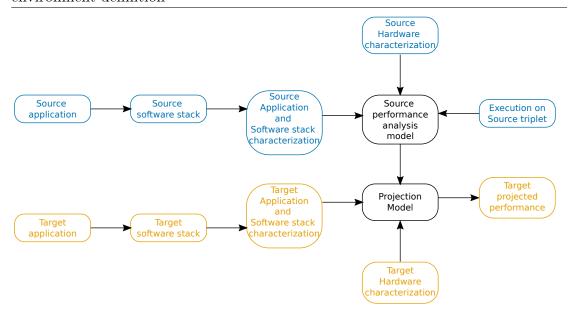

Au cours de cette thèse, nous mettons en place une approche de projection de performance adaptée à notre définition d'un environnement de codesign regroupant les acteurs et les aspects des performances des applications en 3 groupes : l'application, la pile logicielle et le matériel. Ce modèle se présente en trois étapes pour effectuer la projection d'un triplet application/pile logicielle/matériel source, et accessible, vers un futur triplet cible d'intérêt, et inaccessible. Ces étapes sont : la caractérisation des performances sur nos trois aspects, suivi de l'analyse des performances sur le triplet source qui va enfin conduire à une projection des performances vers le triplet cible en fonction des différences entre les paramètres de celui-ci et du triplet source. Cette approche est ensuite implémentée à l'aide

d'une représentation fondée sur le modèle Roofline dans laquelle on se concentre sur le maximum de performance atteignable par les triplets et on projette les performances avec une hypothèse de conservation de l'efficacité architecturale. Nous utilisons ensuite ce modèle pour l'analyse et l'exploration de paramètres matériels tels que la taille des vecteurs ou le choix du type de mémoire sur différentes architectures de cœurs Arm. Enfin, nous étendons cette exploration à des architectures multicœurs en affinant la caractérisation de la bande passante et le travail effectués par chaque cœur. L'utilisation de cette approche se concentre sur l'exploration de paramètres applicatifs et de pile logicielle sur une future architecture d'intérêt pour le HPC : le processeur EPI (pour European Processor Initiative).

Mots-clés Projection de performance, Environnement Arm, Exploration de l'espace de conception, Codesign

Laboratoires d'accueil CEA, DAM, DIF, F-91297 Arpajon, France Inria Bordeaux Sud-Ouest, 200 Avenue de la Vieille Tour, 33400 Talence

ii C. Gavoille

**Title** A performance projection approach for design-space exploration on Arm HPC environment

Abstract Today's science increasingly uses simulation to model and understand the world around us. To improve their speed, accuracy, and modeling capabilities, scientists rely on supercomputers, the domain of expertise of *High-Performance Computing*. As the demand for computing power keeps growing, these machines must become ever more powerful. However, the reduction in transistor size predicted by Moore's Law is no longer sufficient to drive the evolution of processors, the core of supercomputer power. Hence, these machines are becoming increasingly complex to answer this increasing demand. The performance of HPC applications depends on interactions between varied application behavior, a complex processor architecture, and the choices made by the software stack. As a result, optimizing applications' performance on these machines is a tedious task.

One solution to simplify optimization efforts and improve applications' performance is to bring together all HPC actors in a **codesign** environment for designing future machines. In an environment where the interests of applications drive the choices made by constructors, the processors and software stack will be adapted to the needs of future users. It is all the more vital with the recent arrival of the Arm environment in HPC, already representing 10% total computing power of the Top500 with just six machines, because this environment offers manufacturers great freedom in their choice of processor characteristics. However, in such a codesign environment, it is mandatory to use a performance prediction approach that accounts for the impact of the choices made by all players to drive the design-space exploration.

In this thesis, we implement a performance projection approach adapted to our definition of a codesign environment that groups the actors and aspects of application performance into three groups: the application, the software stack, and the hardware. This model takes the form of a three-step process for projecting an accessible application/software stack/source hardware triplet onto a future target triplet of interest, which is inaccessible. These steps are performance characterization of our three aspects, followed by performance analysis on the source triplet, which finally leads to a projection of performance towards the target triplet as a function of the differences between its parameters and those of the source triplet. Then, we implement this approach using a Roofline model representation, in which we focus on the maximum performance attainable by the triplets and project performance with an assumption of architectural efficiency conservation. We then use this model to analyze and explore hardware parameters such as hardware vector size and choice of memory type on different Arm core architectures. Finally, we extend this exploration to multi-core architectures by refining the characterization

of the bandwidth and the workload of each core. Then, we use this extension for the exploration of application and software stack parameters on a future HPC architecture of interest: the EPI (European Processor Initiative) processor.

**Keywords** Performance projection, Arm environment, Design-space exploration, Codesign

**Hosting Laboratories** CEA,DAM,DIF, F-91297 Arpajon, France Inria Bordeaux Sud-Ouest, 200 Avenue de la Vieille Tour, 33400 Talence

iv C. Gavoille

## Résumé étendu en français

Dans le but d'apporter des solutions aux grands enjeux contemporains, la science et l'industrie ont besoin de plus en plus de puissance de calcul. De nombreux domaines scientifiques, tels que la climatologie, la biologie ou la physique quantique, utilisent cette puissance à travers la mise en place de simulation sur des supercalculateurs. On parle alors de Calcul Haute-Performance (High Performance Computing, ou HPC, en anglais). Et l'architecture de ces supercalculateurs évolue pour devenir de plus en plus performants pour nourrir cette demande croissante en puissance de calcul. Aujourd'hui, on peut les définir comme un ensemble d'un ou plusieurs processeurs dans des nœuds de calculs interconnectés par un réseau rapide. Seulement, avec la fin de la Loi de Moore, les processeurs de ces machines se doivent de devenir de plus en plus complexes pour continuer à être capable de répondre à la demande croissante en puissance de calcul. La principale métrique pour mesurer les performances d'une application HPC est le nombre d'opérations à virgule flottante par seconde ou FLOPS, mais le nombre de FLOPS d'une application ne dépend pas seulement de la puissance de calcul pure offerte par la machine. En effet, elles dépendent de nombreux facteurs touchant des domaines d'expertise différents tels que les choix faits par la pile logicielle, lors du développement du code source ou de leur interaction avec l'architecture du processeur. Ainsi, l'optimisation des applications sur de nouvelles machines est une tâche complexe nécessitant de long temps de développement et une expertise dans de nombreux domaines tels que l'ingénierie logicielle, l'architecture des ordinateurs ou la modélisation de problèmes physiques.

Une solution pour simplifier les efforts d'optimisation des applications ou obtenir de meilleures performances est le développement des futures machines dans un cadre de codesign. L'objectif d'un tel environnement est de construire une machine et de développer une pile logicielle adaptées aux applications des futurs utilisateurs. En outre, avec la récente arrivée de l'environnement Arm dans le monde du HPC, ce besoin de codesign est encore plus fort du fait de la grande liberté offerte par celui-ci dans le choix des paramètres matériels. Seulement, cette liberté dans le choix des paramètres architecturaux se traduit aussi par un besoin de la possibilité d'étudier l'interaction de la pile logicielle et des applications avec

le matériel. Un tel modèle n'est possible que si l'ensemble des acteurs impliqués dans la construction et l'utilisation des supercalculateurs Arm de demain peuvent discuter et avoir des retours sur les choix de conception fait par les autres acteurs. Ainsi, dans notre cas, le point de discussion choisi est sur la **performance** des applications HPC. Il est donc indispensable d'utiliser un modèle de prédiction de performance pour diriger de telles initiatives de codesign.

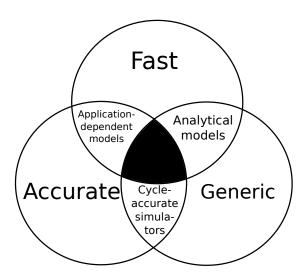

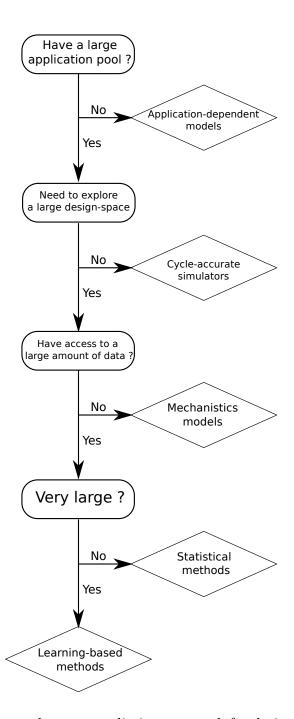

Idéalement, une telle approche se doit d'être rapide, précise et générique. Seulement, avec la complexité des machines, des logiciels et des codes de simulation d'aujourd'hui, aucun modèle ne peut coupler ces trois caractéristiques. On se doit donc de faire des compromis. Il existe donc de nombreuses approches possibles en fonction des compromis que les acteurs de l'environnement de codesign peuvent se permettre d'effectuer ou non. Les trois principales approches sont :

- La Simulation cycle-par-cycle, précise et générique. Elle fait le choix de simuler le comportement d'une machine exécutant une application sur une autre machine. En effet, cette précision se fait au détriment de la rapidité de la prédiction du fait des nombreuses interactions à modéliser;

- Les *Modèles dépendants d'une application* qui sacrifie l'aspect générique de l'approche pour modéliser le comportement d'une application en particulier et ainsi effectuer des prédictions rapides et précises sur un grand nombre d'architectures ;

- Les *Modèles analytiques* font, eux, le choix d'accepter de perdre en précision des prédictions pour la rapidité et la généricité. Ils se fondent sur une modélisation mathématique, statistique ou des méthodes d'apprentissage pour obtenir une estimation de l'évolution de la performance en fonction des paramètres d'entrée.

Du fait de ces nombreuses approches possibles, effectuer le choix d'une approche ou d'une autre va dépendre des besoins de l'environnement de codesign.

C'est l'objectif de cette thèse : Mettre en place une approche de prédiction de performance adaptée à l'exploration des paramètres de conception dans un cadre de codesign.

Ce manuscrit présente les contributions effectuées pendant trois années de thèse dans le but de mettre en place un environnement de codesign, définir une approche de projection de performance adaptée et l'implémenter pour l'exploration de paramètres à différents niveaux. En premier lieu, l'environnement de codesign est défini en séparant les acteurs et les aspects des performances des applications HPC en trois groupes distincts: les applications, la pile logicielle et le matériel. Suite à cette définition, le besoin de pouvoir analyser les impacts des choix fait par les acteurs de chacun de ces aspects entraîne le choix d'utiliser une **approche de**

vi C. Gavoille

projection de performance pour diriger l'exploration des parametres. Ensuite, nous avons effectué une première implémentation de cette approche avec pour objectif d'étudier l'impact de paramètres matériels sur les performances mono-cœurs des applications HPC. Cette implémentation se fonde sur une modélisation de type Roofline des performances pour l'analyse et la projection de performances. Les explorations de paramètres accomplies avec cette approche concluent sur différentes optimisations matérielles adaptées aux choix des applications et de la pile logicielle. Enfin, cette implémentation est ensuite naturellement étendue pour la projection des performances multi-cœurs des applications HPC. Cette extension conserve l'aspect Roofline mais raffine la caractérisation de la bande-passante et du travail de chaque cœur pour s'adapter aux difficultés apportées par une exécution en environnement multicœur. Grâce à cette approche, nous avons pu établir et reproduire une voie d'optimisation logicielle ou applicative possible des performances sur une architecture de processeur d'intérêt pour le futur proche de l'environnement Arm en HPC.

## Définition de l'environnement de codesign et mise en place de l'approche de projection de performance

Afin de faire le choix d'une approche de prédiction de performance adaptée aux besoins de notre environnement de codesign, il faut avant tout définir cet environnement et ses besoins. Ainsi, nous avons fait le choix de séparer les acteurs et les aspects des performances des applications HPC en trois groupes :

- L'application qui comprend le code source, les structures de données utilisées, les schémas numériques, ... ;

- La pile logicielle comprenant l'impact des compilateurs, des librairies d'exécution, ... ;

- Le *matériel* qui correspond à l'architecture de la machine, sa hiérarchie mémoire, ...

Du fait du besoin de caractériser indépendamment les impacts de chacun de ces aspects rapidement et de façon générique, nous avons fait le choix d'utiliser un modèle analytique pour la prédiction de performance. Nous définissons ce modèle comme une approche de projection de performance.

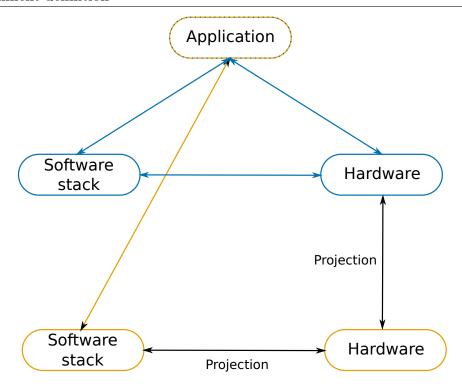

En effet, celle-ci vise à estimer l'impact des différences entre un triplet application/pile logicielle/matériel source, accessible, et un tel triplet cible, inaccessible, sur les performances finales. Cette méthodologie peut se séparer en trois étapes : la caractérisation des paramètres de chacun des aspects, l'analyse des performances du triplet source et la projection des performances vers le triplet cible. La caractérisation consiste à récupérer des métriques d'intérêt représentatives des performances sur les trois aspects des deux triplets. Ensuite, ces métriques sont utilisées pour l'analyse des performances du triplet source afin de conclure quant à leur impact sur les performances. Enfin, suite à cette estimation de l'impact de ces métriques, la projection de la performance mesurée sur le triplet source se fait grâce aux différences entre les métriques des deux triplets. Une fois que l'environnement et la méthodologie de projection utilisée pour l'exploration des paramètres de conception, nous l'implémentons ensuite dans un premier environnement simple : l'exécution monocœur d'une application.

## Exploration matérielle en environnement monocœur

Même si les applications HPC sont actuellement exécutées sur plusieurs cœurs en parallèle, l'étude de leur performance monocœur reste capitale. En effet, selon la loi d'Amdahl, les performances multicœurs d'une application sont limitées par le temps de calcul qu'elle effectue en monocœur. Ainsi, l'optimisation des performances monocœurs permet d'améliorer la capacité d'une application à passer à l'échelle.

Or, dans le cas d'une exécution séquentielle, les performances dépendent notamment des paramètres matériels et de comment la suite d'instruction interagit avec celui-ci. Ainsi, l'exploration de l'impact de paramètres matériels sur les performances monocœurs des applications HPC est vitale pour les applications d'aujourd'hui.

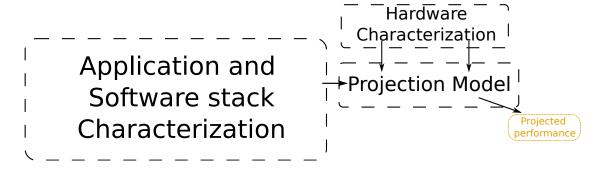

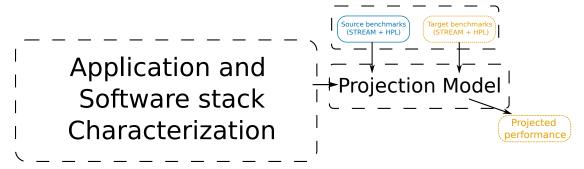

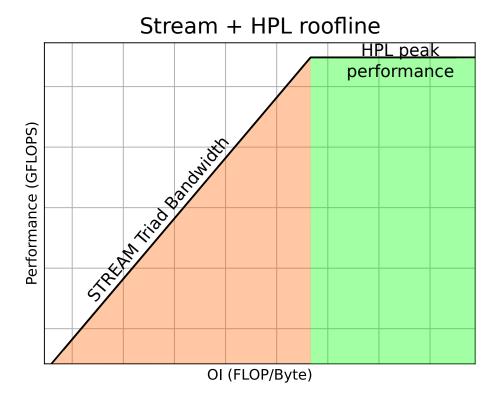

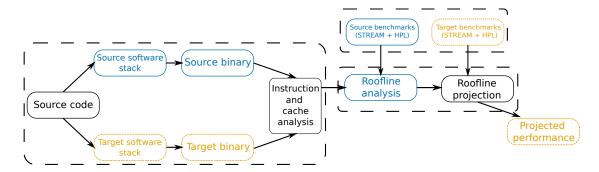

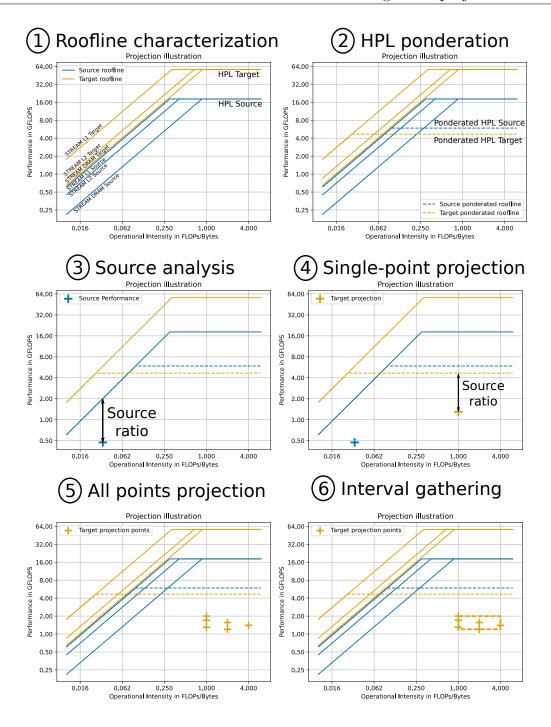

Dans cet objectif, nous implémentons la méthodologie définie précédemment à l'aide d'une représentation de type Roofline des performances. Cela se traduit par une modélisation des limites imposées par le matériel sous forme de rooflines, obtenus à l'aide des benchmarks STREAM et High Performance Linpack. Dans le cas d'une machine cible inaccessible, nous supposons qu'ils sont, soit fournis par le constructeurs, soit extrapolés. Ensuite, l'analyse du binaire (représentatif des aspects application et pile logicielle) permet de pondérer ce roofline pour être plus représentatif de la limite actuelle du mix d'instructions. Enfin, nous caractérisons le comportement de l'application à l'aide de son Intensité Opérationnelle (OI) pour les différents niveaux de mémoire. La projection se fait naturellement avec une hypothèse de conservation de l'efficacité par rapport à son roofline pondérée. Les différentes OI et rooflines (pour chaque niveau de mémoire) peuvent conduire à l'obtention d'un intervalle de performance.

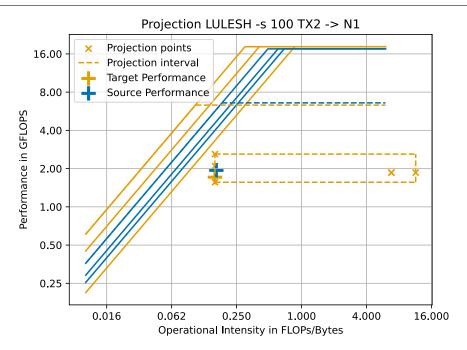

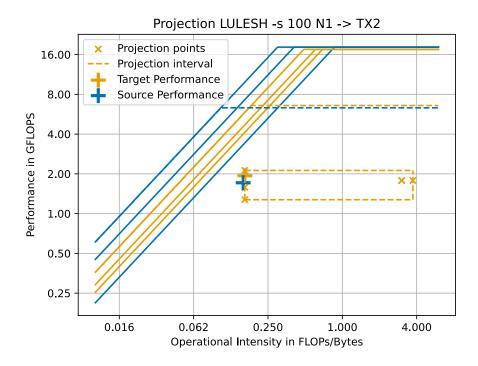

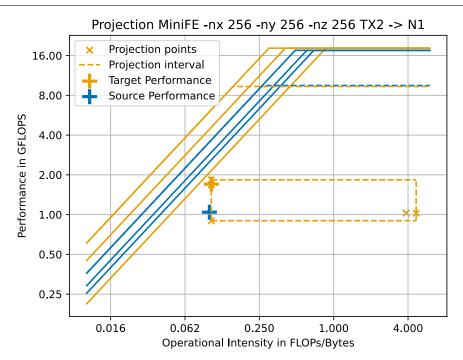

La validation de cette approche entre 3 cœurs d'architecture Arm (Marvell ThunderX2, Neoverse N1 et Fujitsu A64FX) met en avant la capacité de cette

viii C. Gavoille

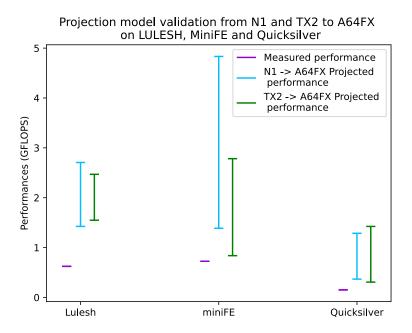

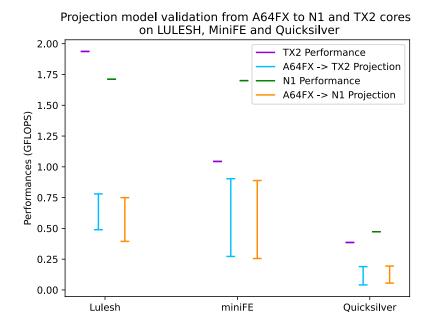

approche à obtenir des prédictions justes dans le cas de machines présentant une micro-architecture proche. Elle montre aussi la limitation de cette approche dans le cas d'une projection vers une machine trop éloignée en termes de microarchitecture, démontrant que l'hypothèse de conservation de l'efficacité est trop grossière dans ce cas.

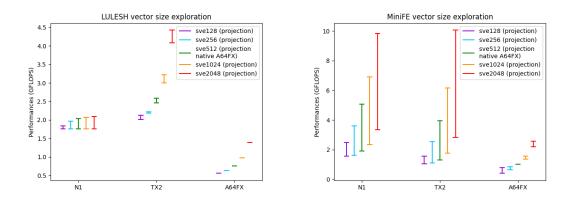

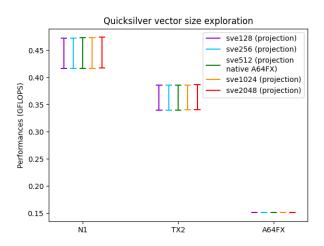

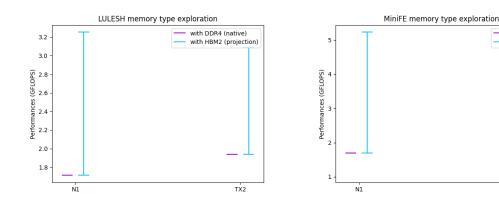

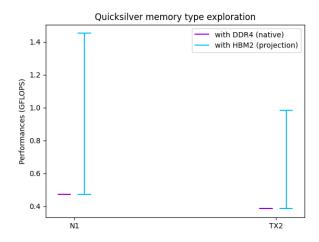

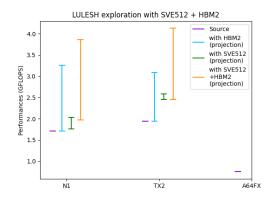

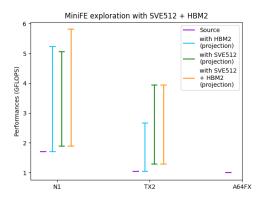

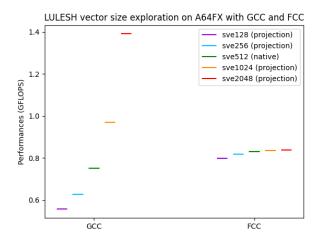

Enfin, l'exploration de paramètres matériels est accomplie en utilisant nos trois cœurs de référence en machine source et en modifiant la taille des vecteurs, le type de mémoire ou en combinant ces deux modifications. Cette étude est menée sur trois proxy-applications de référence de la suite CORAL: MiniFE, Quicksilver et LULESH. Cette exploration montre que le choix de la valeur d'un paramètre va dépendre de l'application que l'on cible ainsi que de l'architecture de référence et du choix du compilateur. Par exemple, une application comme Quicksilver ne bénéficie aucunement de l'augmentation de la taille des vecteurs alors que LULESH peut observer un gain de performance allant jusque  $\times 2$  si on part d'une architecture type ThunderX2.

## Exploration applicative et logicielle en environnement multicœur

Dans ce dernier chapitre, l'objectif est d'étendre l'approche de projection monocœur à l'aide d'une modélisation Roofline précédente à une situation en exécution multicœur. En effet, au sein d'un nœud de calcul, les applications d'aujourd'hui essayent d'utiliser au maximum les ressources offertes par l'ensemble des cœurs et de la mémoire à l'échelle du nœud. Cette projection correspond donc à un cadre plus réaliste de l'exécution d'une application sur un processeur d'un supercalculateur.

Cela est accompli en analysant le travail de chaque cœur en concurrence sur les mêmes ressources de calcul. Cela nécessite aussi d'affiner la caractérisation de la bande-passante, celle-ci ayant un impact encore plus important sur les performances des applications en multicœurs. L'approche consiste donc à une analyse du travail de chaque cœur, suivis d'une projection sur les cœurs du triplet cible puis à une sommation de l'ensemble des intervalles de projection obtenus. Une limitation de cette approche est que le nombre de cœurs entre le triplet source et le triplet cible doit être égal.

Pour les travaux de validation de cette approche, nous utilisons deux processeurs similaires mais séparés d'une génération : les processeurs Graviton 2 et Graviton 3 d'Amazon Web Services. Ce ne sont pas des processeurs directement HPC mais l'évolution de ceux-ci est représentative de la future évolution des processeurs HPC Arm suivant la roadmap Neoverse. Dans ce cas de figure, la projection entre ces processeurs admet une erreur d'au plus 20% pour deux kernels de la

suite de validation NAS. Cela s'explique notamment par un résultat similaire à la validation monocœur : une différence de comportement de la micro-architecture entre les deux générations, ce qui n'est pas considéré dans notre hypothèse de conservation de l'efficacité. Ces travaux de validations sont donc encourageants et justifient l'exploration de paramètres logiciels et applicatifs vers un processeur d'intérêt pour le HPC : l'European Processor Initiative (EPI).

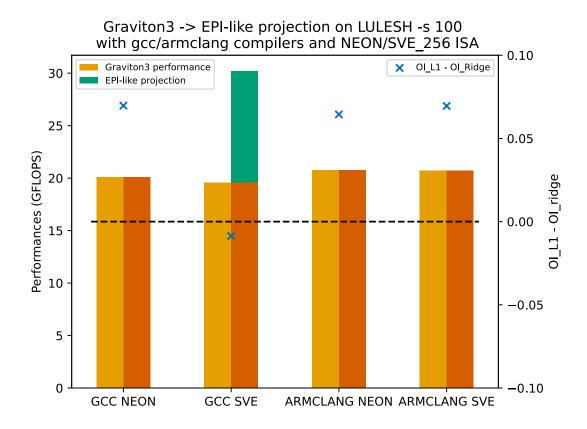

Les caractéristiques précises de celui-ci étant inconnues au moment de l'écriture de ce manuscrit, nous utilisons les informations disponibles pour représenter l'EPI à partir d'un Graviton 3 avec une mémoire HBM rapide, obtenue sur un nœud d'A64FX, et une taille de cache partagé L3 plus importante. Les seules améliorations se situent donc au niveau des caractéristiques mémoires du processeur. L'objectif est donc d'étudier comment il serait possible d'utiliser des paramètres applicatifs et logiciels pour utiliser ce gain en mémoire sur deux applications : LULESH et LAMMPS DIFFUSE. En effet, l'étude de différents compilateurs et jeux d'instructions sur LULESH montre une piste contre-intuitive : la réduction artificielle de l'intensité opérationnelle pour mieux utiliser les ressources mémoires. Nous avons donc choisi de reproduire ce comportement à l'aide d'un code synthétique dans un environnement permettant d'utiliser deux mémoires différentes avec la même architecture: le processeur Knights Landing d'Intel. Ces travaux ont montré qu'une telle piste d'optimisation, quoique contre-intuitive, est viable et montre que l'utilisation de projection de performance pour le codesign peut ouvrir la voie à de nombreuses possibilités d'optimisation des applications HPC pour les futures machines Arm.

#### Conclusion

Le développement de futurs supercalculateurs dans un environnement de codesign est une solution pour simplifier l'optimisation des applications HPC sur ces machines. Dans ce cas-là, il est nécessaire d'utiliser un modèle de prédiction de performance adapté à l'environnement de codesign pour que l'ensemble des acteurs impliqués puissent discuter sur les meilleurs paramètres de conception à choisir dans le domaine d'expertise de chacun.

Cette thèse montre qu'il est avant tout nécessaire de définir un tel environnement pour ensuite choisir une approche de prédiction adaptée. Grâce à différentes implémentations de la méthodologie de projection de performance définie dans la première contribution, les travaux effectués ont permis de montrer différentes possibilités d'optimisation et que cela doit intégrer les choix de l'application, de la pile logicielle et du matériel pour pouvoir avoir une direction claire quant aux choix effectués lors de la conception des machines HPC de demain.

C. Gavoille

# Contents

| Re               | Remerciements   |         |                                          |              |

|------------------|-----------------|---------|------------------------------------------|--------------|

| $\mathbf{R}_{0}$ | ésum            | ié éten | adu en français                          | $\mathbf{v}$ |

| In               | $\mathbf{trod}$ | uction  |                                          | 1            |

| Ι                | Co              | ontext  |                                          | 3            |

| 1                | Cor             | ntext c | of High Performance Computing            | 5            |

|                  | 1.1             | HPC     | applications                             | . 6          |

|                  |                 | 1.1.1   | LULESH                                   | . 7          |

|                  |                 | 1.1.2   | Quicksilver                              | . 8          |

|                  |                 | 1.1.3   | MiniFE                                   | . 9          |

|                  |                 | 1.1.4   | LAMMPS                                   | . 10         |

|                  | 1.2             | HPC     | supercomputers landscape                 | . 11         |

| <b>2</b>         | Har             | dware   | e architecture impact on performance     | 15           |

|                  | 2.1             | Funct   | ioning of a core                         | . 15         |

|                  |                 | 2.1.1   | The Von Neumann architecture             | . 15         |

|                  |                 | 2.1.2   | The instruction pipeline                 | . 16         |

|                  | 2.2             | Impac   | et of SIMD and FMA on performance        | . 18         |

|                  |                 | 2.2.1   | SIMD and FMA description                 | . 19         |

|                  |                 | 2.2.2   | Vector ISA in the Arm HPC environment    | . 19         |

|                  | 2.3             | Memo    | ory organization                         | . 20         |

|                  | 2.4             | Impac   | et of memory on multi-core performance   | . 22         |

|                  |                 | 2.4.1   | NUMA effect on performance               | . 23         |

|                  |                 | 2.4.2   | Shared cache impact on performance       | . 24         |

|                  |                 | 2.4.3   | Topology impact on bandwidth performance | . 25         |

|                  | 2.5             | Concl   | usion                                    | . 26         |

| 3            | Soft  | tware stack and programming environment                     | 27 |

|--------------|-------|-------------------------------------------------------------|----|

|              | 3.1   | Compiler impact on performance                              | 27 |

|              | 3.2   | Programming model and runtime optimization                  | 29 |

|              | 3.3   | Application performance analysis                            | 32 |

|              |       | 3.3.1 Profiling tools                                       | 32 |

|              |       | 3.3.2 The Roofline model as an analysis tool                | 32 |

|              | 3.4   | Conclusion                                                  | 34 |

| $\mathbf{T}$ | ne pi | roblem                                                      | 35 |

| 4            | Sta   | te of the art                                               | 37 |

|              | 4.1   | Cycle-by-cycle simulators                                   | 38 |

|              |       | 4.1.1 The gem5 simulation tool                              | 38 |

|              |       | 4.1.2 Overview of gem5-based simulators                     | 39 |

|              |       | 4.1.3 Discussion                                            | 40 |

|              | 4.2   | Application-dependent models                                | 40 |

|              |       | 4.2.1 Hydrodynamics application models                      | 41 |

|              |       | 4.2.2 Discussion                                            | 41 |

|              | 4.3   | Analytical models                                           | 42 |

|              |       | 4.3.1 Statistical approaches                                | 42 |

|              |       | 4.3.2 Learning-based methods                                | 43 |

|              |       | 4.3.3 Mechanistic models                                    | 44 |

|              |       | 4.3.4 Discussion                                            | 44 |

|              | 4.4   | Conclusion                                                  | 45 |

|              |       |                                                             | 4- |

| II           | C     | contributions                                               | 47 |

| 5            |       | up of the performance projection methodology through code-  |    |

|              | _     | n environment definition                                    | 49 |

|              |       | Codesign environment definition                             |    |

|              | 5.2   | Characteristics of our performance prediction approach      |    |

|              | 5.3   | Choice of a performance projection approach                 | 52 |

|              | 5.4   | The performance projection workflow                         | 52 |

|              | 5.5   | Conclusion                                                  | 54 |

| 6            | _     | ploration of hardware parameters impact on HPC applications |    |

|              | sing  | gle-core performance                                        | 57 |

|              | 6.1   | Single-core projection model                                | 57 |

|              |       | 6.1.1 Hardware Characterization                             | 58 |

|              |       | 6.1.2 Application and software characterization             | 59 |

|              |       |                                                             |    |

xii C. Gavoille

|   |       | 6.1.3   | Performance Projection                                              | 62 |

|---|-------|---------|---------------------------------------------------------------------|----|

|   |       | 6.1.4   | Implementation                                                      | 65 |

|   |       | 6.1.5   | Experimental environment                                            | 66 |

|   | 6.2   | Model   | validation                                                          | 67 |

|   |       | 6.2.1   | Neoverse N1 $\leftrightarrow$ Marvell ThunderX2 projection          | 68 |

|   |       | 6.2.2   | Neoverse N1 and Marvell Thunder $X2 \rightarrow Fujitsu A64FX$ pro- |    |

|   |       |         | jection                                                             | 69 |

|   | 6.3   | Hardw   | vare parameters exploration on single-core performance              | 72 |

|   |       | 6.3.1   | Exploration on SVE vector sizes                                     | 72 |

|   |       | 6.3.2   | Exploration on the introduction of HBM2 on DDR4 machines            | 74 |

|   |       | 6.3.3   | Comparison of projections from N1 and TX2 with SVE 512              |    |

|   |       |         | and HBM2 to A64FX                                                   | 76 |

|   |       | 6.3.4   | Vector sizes exploration on A64FX with different software           |    |

|   |       |         | stacks                                                              | 78 |

|   | 6.4   | Concl   | usion                                                               | 80 |

|   |       |         |                                                                     |    |

| 7 | _     |         | on of software and application parameters impact on                 |    |

|   |       |         | ications single-node performance                                    | 81 |

|   | 7.1   |         | ne projection model extension to multicore                          | 81 |

|   |       | 7.1.1   | Hardware Characterization                                           | 82 |

|   |       | 7.1.2   | Roofline ponderation                                                | 82 |

|   |       | 7.1.3   | OI characterization                                                 | 83 |

|   |       | 7.1.4   | Performance projection                                              | 83 |

|   |       | 7.1.5   | Implementation                                                      | 84 |

|   |       | 7.1.6   | Experimental Environment                                            | 85 |

|   | 7.2   |         | extension validation                                                | 85 |

|   |       | 7.2.1   | Graviton $2 \leftrightarrow$ Graviton 3 projection                  | 86 |

|   |       | 7.2.2   | Comparison with straightforward roofline projection                 | 88 |

|   | 7.3   |         | cation parameters exploration                                       | 88 |

|   | 7.4   |         | are parameters exploration on target node architecture              | 90 |

|   |       | 7.4.1   | Compilers and ISA exploration                                       | 90 |

|   | 7.5   |         | ior reproduction with synthetic kernels                             | 92 |

|   | 7.6   | Concl   | usion                                                               | 94 |

| C | anelu | ision a | nd Perspectives                                                     | 97 |

xiv C. Gavoille

# List of Figures

| 1.1 | Evolution of the performance of the Top 500 #1 and #500 super-<br>computer and the sum of all ranked machines from 1993 to June<br>2023                                                                                                                                                                                                                                                                    |    |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | Source: [19]                                                                                                                                                                                                                                                                                                                                                                                               | 6  |

| 1.2 | Simple Sedov Blast wave problem 2d modelization. LULESH represents this problem on a 3d cartesian mesh                                                                                                                                                                                                                                                                                                     |    |

|     | Source: [58]                                                                                                                                                                                                                                                                                                                                                                                               | 8  |

| 1.3 | Ale3D complex workflow. LULESH only represents a small fraction of this workflow by modelizing hydrodynamics equations with an explicit method.                                                                                                                                                                                                                                                            |    |

|     | Source: [58]                                                                                                                                                                                                                                                                                                                                                                                               | 9  |

| 1.4 | The three possible interactions with matter of the randomly positioned particles modelized by Quicksilver.                                                                                                                                                                                                                                                                                                 |    |

|     | Source: [86]                                                                                                                                                                                                                                                                                                                                                                                               | 9  |

| 1.5 | (Left) Coarse-grained model of a 100 nm virus-like particle budding through interaction with a cell membrane. Transmembrane proteins are shown in blue. (Middle) A hollow metal strut (200 nm on a side) is used to measure the mechanical strength and stiffness of ultra-lightweight nanoengineered materials. (Right) Coarse-grained simulation of catastrophic depolymerization of alpha-beta-tubulin. |    |

| 1.6 | Source: [94]                                                                                                                                                                                                                                                                                                                                                                                               | 10 |

| 1.0 | Source: [17]                                                                                                                                                                                                                                                                                                                                                                                               | 12 |

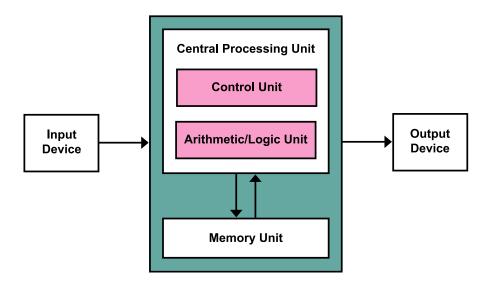

| 2.1 | The four components of Von Neumann Architecture - Source : [21] .                                                                                                                                                                                                                                                                                                                                          | 16 |

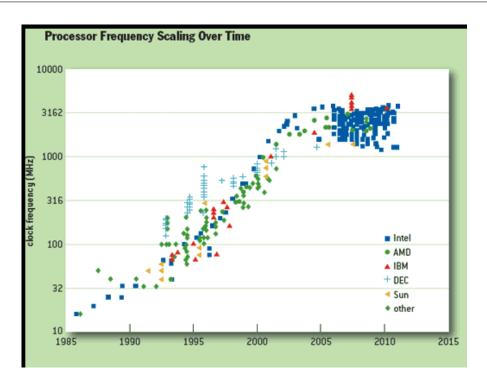

| 2.2 | CPU frequency scaling over time extracted from Stanford CPU DB Source: [42]                                                                                                                                                                                                                                                                                                                                | 17 |

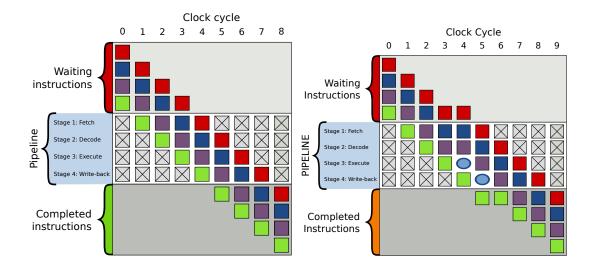

| 2.3 | Generic 4-stage instruction pipeline without a bubble (left) and with a bubble(right) - Source : [20]                                                                                                                                                                                                                                                                                                      | 18 |

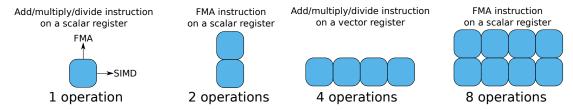

| 2.4 | Number of FLOPs issued with different type of floating-point instructions                                                                                                                                                                                                                                                                                                                                  | 19 |

|     |                                                                                                                                                                                                                                                                                                                                                                                                            |    |

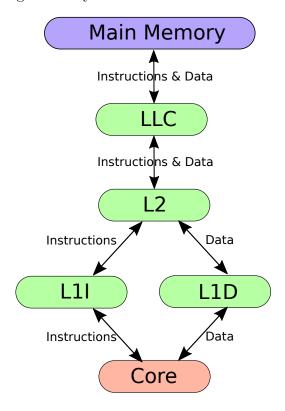

| 2.5 | Hierarchy of a four stage memory architecture: 3 cache levels and the main memory with 2 L1s, one for data and one for instructions.                                                                                                                                               | 21 |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

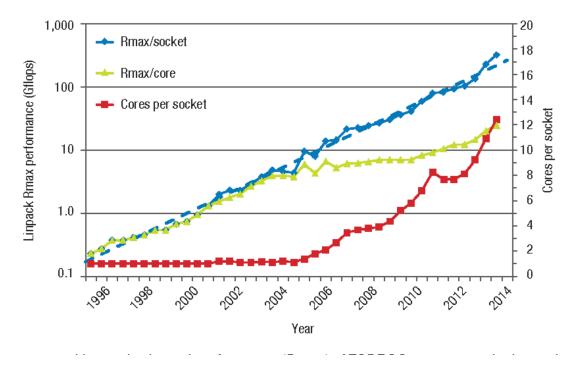

| 2.6 | Maximal computing speed of a core (Rmax/core) and a socket (Rmax/socket) and number of cores per socket of Top500 systems .                                                                                                                                                        | 23 |

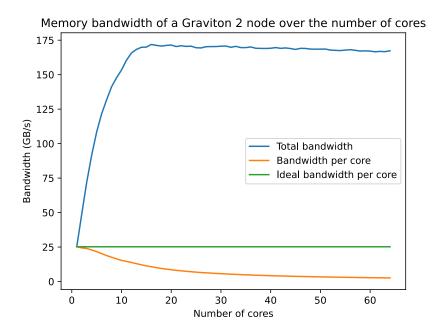

| 2.7 | Main memory bandwidth obtained with STREAM iterating over the number of cores of an AWS Graviton 2 node                                                                                                                                                                            | 24 |

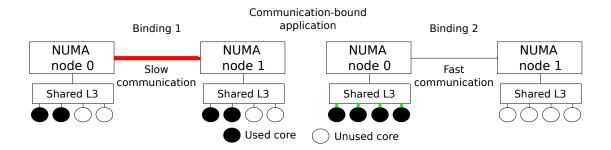

| 2.8 | Impact of two different placement policies on the performance of an application limited by communication running on four cores. Communications between cores in Binding 1 are limited by the Memory Bus bandwidth between NUMA nodes and can hinder the application's performance. | 25 |

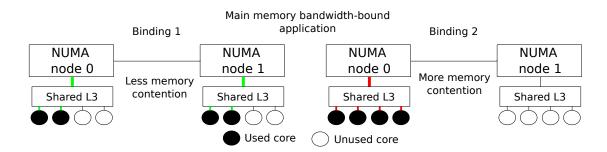

| 2.9 | Impact of two different placement policies on the performance of<br>an application limited by main memory bandwidth running on four<br>cores. Bandwidth in Binding 2 is limited by the contention on the<br>NUMA node 0 memory channels and can hinder the application's           | 26 |

|     | performance                                                                                                                                                                                                                                                                        | 20 |

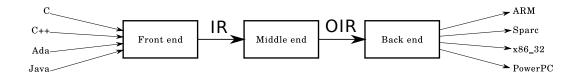

| 3.1 | The three stages of a compiler from source code (in different languages) to Machine code (for different architectures) through Intermediate Representation (IR) and Optimized IR (OIR)                                                                                             | 28 |

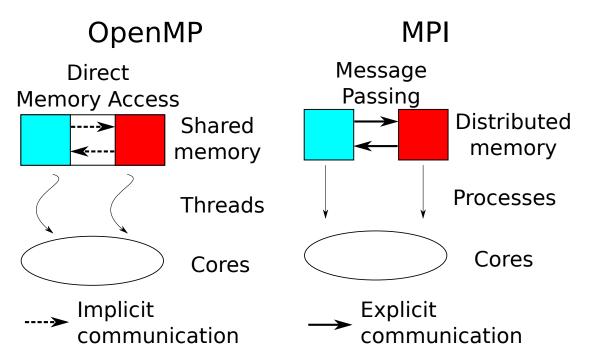

| 3.2 | Functioning of a Shared Memory programming model (OpenMP) and a Distributed Memory programming model (MPI)                                                                                                                                                                         | 30 |

| 3.3 | Combination of MPI and OpenMP to combine the strengths and cover the weaknesses of each programming models                                                                                                                                                                         | 31 |

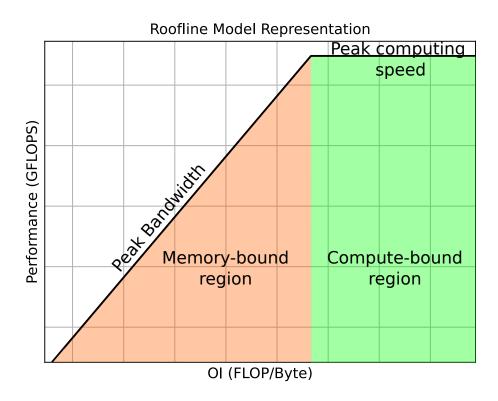

| 3.4 | Roofline representation with the performance (in GFLOPS) on the y-axis and the Operational Intensity (OI) on the x-axis. The black                                                                                                                                                 |    |

|     | roofline represents the maximum performance attainable at a certain OI.                                                                                                                                                                                                            | 33 |

| 4.1 | Overview of the three different types of approach with the aspect they choose to focus on                                                                                                                                                                                          | 38 |

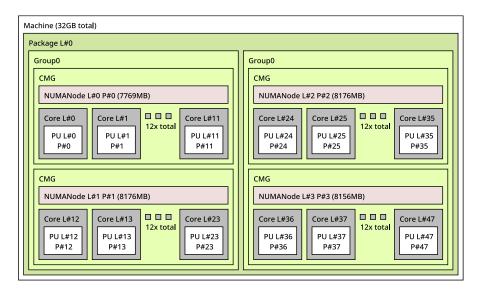

| 4.2 | Architecture of an A64FX processor obtained with <i>lstopo</i> . There are 4 CMG per processor, with 12 cores and one NUMA node each.                                                                                                                                              | 40 |

| 4.3 | Directions to choose a prediction approach for design-space exploration                                                                                                                                                                                                            | 46 |

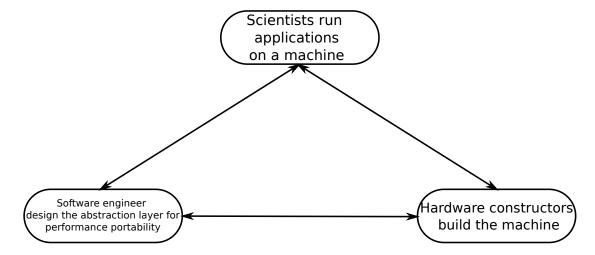

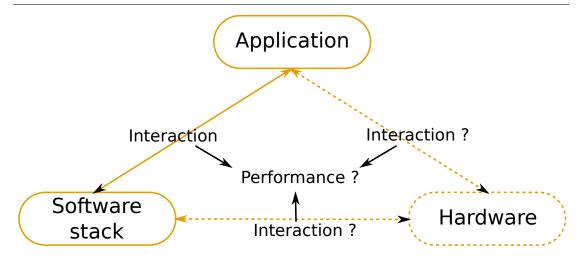

| 5.1 | Schema of the triplet of aspects interacting between each other to deliver a performance on an available machine. Information about their interaction is available through profiling in this example                                                                               | 50 |

|     |                                                                                                                                                                                                                                                                                    |    |

xvi C. GAVOILLE

|   | 5.2  | Schema of the triplet of aspects interacting between each other to deliver a performance on a future machine. In this case, information on the interaction between hardware and the two other aspects is |    |

|---|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|   | r o  | not easily available, leading to an unknown performance                                                                                                                                                  | 51 |

|   | 5.3  | Projection approach between an accessible source and a future target triplet.                                                                                                                            | 53 |

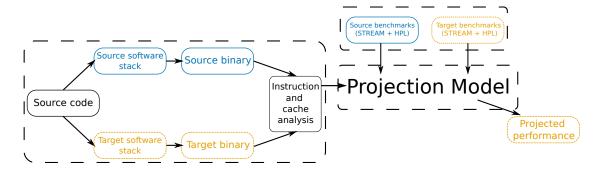

|   | 5.4  | Detailed overview of our performance projection workflow                                                                                                                                                 | 55 |

|   | 6.1  | Overview of the single-core roofline projection workflow. Target triplet is in dotted yellow.                                                                                                            | 58 |

|   | 6.2  | Hardware characterization through STREAM and HPL benchmark-                                                                                                                                              | 00 |

|   |      | ing. Source machine is in plain blue and target machine is in dotted yellow                                                                                                                              | 59 |

|   | 6.3  | Obtained roofline by running STREAM and HPL benchmark                                                                                                                                                    | 60 |

|   | 6.4  | Software and application analysis. Source triplet is in plain blue                                                                                                                                       |    |

|   |      | and target triplet is in dotted yellow                                                                                                                                                                   | 60 |

|   | 6.5  | Projection model in two stages: Roofline analysis and Projection.                                                                                                                                        |    |

|   | C C  | Source triplet is in plain blue and target triplet is in dotted yellow.                                                                                                                                  | 62 |

|   | 6.6  | Illustration of the performance projection approach with the different steps of the projection. All the figures present the OI (FLOP/Bytes                                                               | )  |

|   |      | on the x-axis and the Performance (GFLOPS) on the y-axis                                                                                                                                                 | 64 |

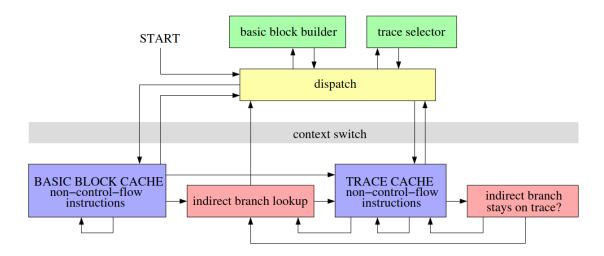

|   | 6.7  | DynamoRIO flow chart. The application code is stored in the two                                                                                                                                          |    |

|   |      | caches separated from the DynamoRIO code by a context switch.                                                                                                                                            |    |

|   |      | Source: [33]                                                                                                                                                                                             | 66 |

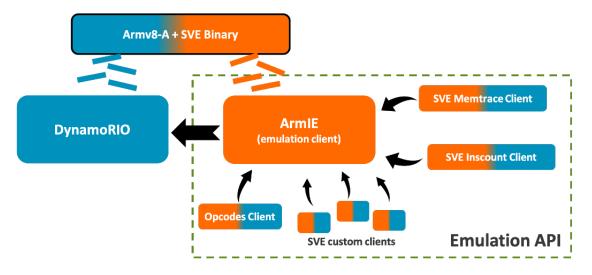

|   | 6.8  | ArmIE flow chart. It is an emulation client based on DynamoRIO                                                                                                                                           |    |

|   |      | for SVE instructions (in orange). When it is not in emulation mode (blue instructions), it behaves like a normal DynamoRIO client.                                                                       |    |

|   |      | Source:[2]                                                                                                                                                                                               | 66 |

|   | 6.9  | LULESH -s 100 TX2 $\rightarrow$ N1 projection results                                                                                                                                                    | 69 |

|   |      | LULESH -s 100 N1 $\rightarrow$ TX2 projection results                                                                                                                                                    | 70 |

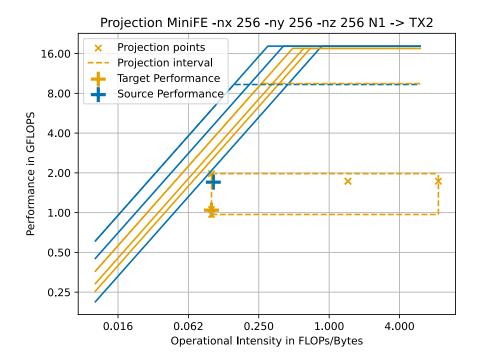

|   |      | MiniFE -nx 256 -ny 256 -nz 256 TX2 $\rightarrow$ N1 projection results                                                                                                                                   | 71 |

|   |      | MiniFE -nx 256 -ny 256 -nz 256 N1 $\rightarrow$ TX2 projection results                                                                                                                                   | 72 |

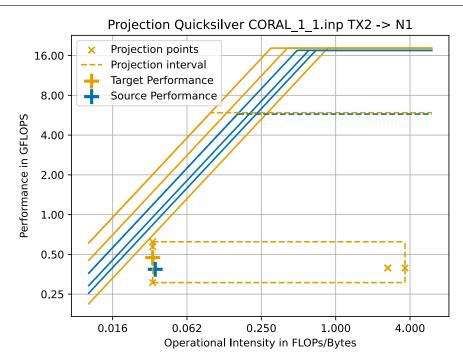

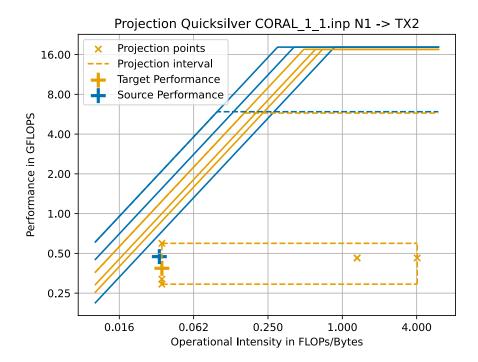

|   | 6.13 | Quicksilver with CORAL Problem 1 input $TX2 \rightarrow N1$ projection results                                                                                                                           | 73 |

|   | 6 14 | Quicksilver with CORAL Problem 1 input N1 $\rightarrow$ TX2 projection                                                                                                                                   | 10 |

|   | 0.11 | results                                                                                                                                                                                                  | 74 |

|   | 6.15 | Model validation from N1 and TX2 to A64FX on LULESH, MiniFE                                                                                                                                              |    |

|   |      | and Quicksilver                                                                                                                                                                                          | 75 |

|   | 6.16 | Model validation from N1 and TX2 to A64FX on LULESH, MiniFE                                                                                                                                              | _  |

|   | 6 17 | and Quicksilver                                                                                                                                                                                          | 76 |

|   | 0.17 | Exploration of different SVE vector sizes on LULESH                                                                                                                                                      | 76 |

| Ī |      |                                                                                                                                                                                                          |    |

| 6.18 | Exploration of different SVE vector sizes on MiniFE                          | 76  |

|------|------------------------------------------------------------------------------|-----|

| 6.19 | Exploration of different SVE vector sizes on Quicksilver                     | 77  |

| 6.20 | Exploration of introduction of HBM2 on LULESH                                | 77  |

| 6.21 | Exploration of introduction of HBM2 on MiniFE                                | 77  |

| 6.22 | Exploration of introduction of HBM2 on Quicksilver                           | 78  |

| 6.23 | Exploration of introduction of HBM2 and SVE512 on LULESH                     | 79  |

| 6.24 | Exploration of introduction of HBM2 and SVE512 on MiniFE                     | 79  |

| 6.25 | Vector sizes exploration with GCC and FCC on A64FX on LULESH                 | 79  |

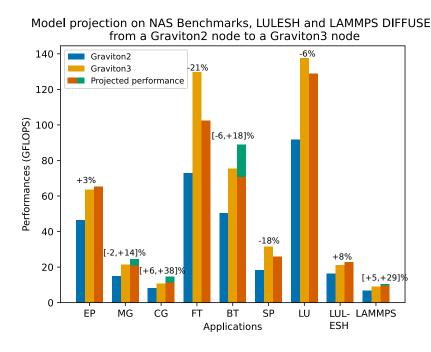

| 7.1  | Projection intervals compared to actual performance on a Graviton2           |     |

|      | and Graviton3 node. Graviton2 and Graviton3 performances are in              |     |

|      | blue and yellow, with projected performance intervals in green and           |     |

|      | orange. The number corresponds to the difference between observed            |     |

|      | and projected performance                                                    | 86  |

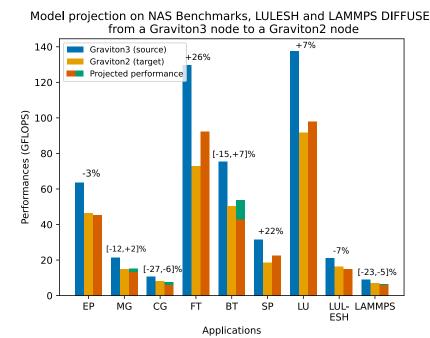

| 7.2  | Projection intervals compared to actual performance on a Graviton3           |     |

|      | and Graviton2 node                                                           | 87  |

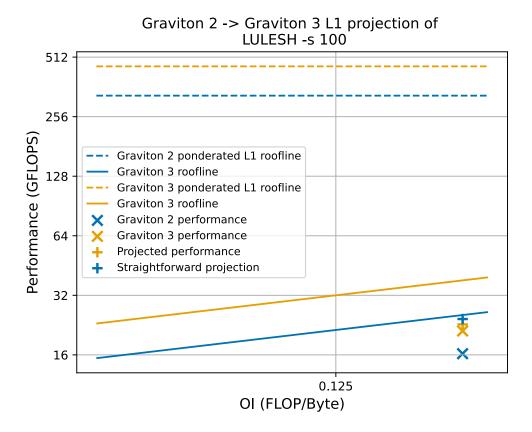

| 7.3  | Obtained Cache-Aware Roofline model of LULESH on Graviton2                   |     |

|      | and Graviton3 with the addition of L1 pondered roofline and pro-             |     |

|      | jection. Rooflines of L1, L2 and L3 memory levels have been hidden           |     |

|      | for clarity purposes                                                         | 89  |

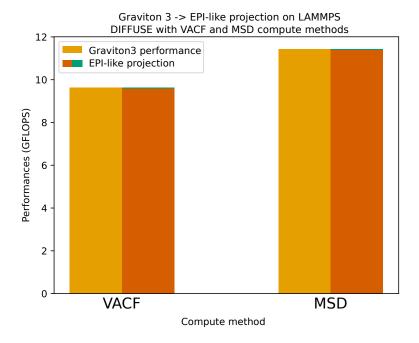

| 7.4  | Projections of two compute methods of LAMMPS DIFFUSE small                   |     |

|      | benchmark from Graviton 3 to our EPI-like machine                            | 90  |

| 7.5  | Observed performance, projections, and OIs of LULESH with dif-               |     |

|      | ferent compilers and ISA on two node architectures: Graviton3 and            |     |

|      | EPI-like. The $OI_{L1} - OI_{Ridge}$ value is represented with blue crosses. | 92  |

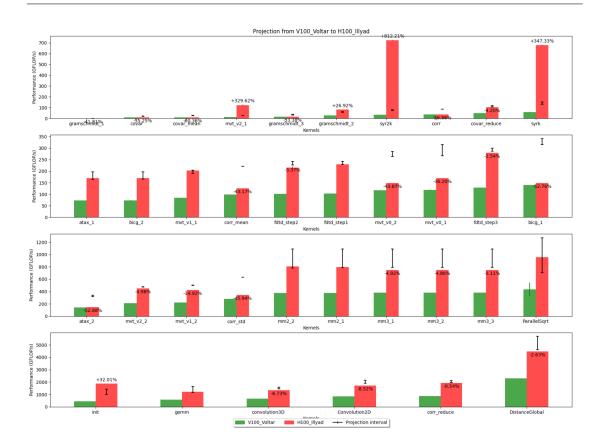

| 7.6  | $N100 \rightarrow H100$ projection results on UVMBench benchmark suite,      |     |

|      | courtesy of L. Van Lanker                                                    | 100 |

xviii C. Gavoille

# List of Tables

| 1.1 | Share of CPU architectures of the June 2023 Top 500 machines                                    | 13 |

|-----|-------------------------------------------------------------------------------------------------|----|

| 6.1 | Single-core characteristics of our 3 source cores architecture                                  | 67 |

| 7.1 | Characteristics of the Arm architectures used in model validation and design-space exploration. | 85 |

| 7.2 | Benchmarks values on KNL                                                                        | 93 |

| 7.3 | Kernels performance in GFLOPS on KNL running on DRAM and                                        |    |

|     | MCDRAM                                                                                          | 94 |

C. GAVOILLE

## Introduction

To understand our world, scientists use computer simulations to model phenomena from the infinitely small to the infinitely large. Delivering the computing power needed for these simulations is the role of High-Performance Computing (HPC) through the development of supercomputers. As science needs more and more computing power, HPC supercomputers are becoming more and more complex to deliver enough performance. Moreover, a faster application execution time opens the possibility of simulating phenomena more accurately or at a bigger scale. However, the execution time of an application running on a supercomputer depends on many complex interactions at different levels. As such, optimizing a complicated application on a complex supercomputer is a tedious task that requires deep knowledge in many different expertise fields. As the Arm HPC environment is recent but already represents a good share (10%) of the top computing power, optimizing applications in this environment is one of the challenges of today's HPC.

One solution to simplify optimization efforts and better performance of applications is to design future machines according to the specific application needs of their future users thanks to codesign. However, a codesign environment is only possible if each actor has feedback on the impact of their and the other's choices on the performance of applications. Hence, using a performance prediction model is mandatory to enable codesign initiatives as a discussion opener between every actor involved in a codesign initiative. Many prediction approaches are used in today's HPC, but, they are not necessarily adapted to a codesign environment. Proposing such a prediction approach adapted to our needs is the main contribution of this manuscript.

The first part of this manuscript presents the context of this study. After a general presentation of the HPC context, applications, and machines in Chapter 1, we describe the hardware and software stack impact on the performance of HPC application in Chapter 2 and 3. Then, we propose the solution of codesign from this context presentation and present the possible state-of-the-art prediction methods for codesign in Chapter 4.

In the second part of this manuscript, we present a performance projection

approach that is coherent with our vision of codesign and apply this methodology to explore the design space around various Arm architectures at different levels. In our definition of such an environment in Chapter 5, we split the performance of HPC applications into three aspects: the application, the hardware, and the software stack. According to these needs, relying on a mechanistic projection approach between a source application/software stack/hardware triplet and a target triplet is a viable solution for our problem. Our projection workflow can be divided into characterization, performance analysis on the source triplet, and projection on the target triplet.

With such a workflow, we first explore the impact of hardware parameters on single-core performance with analysis and projection relying on a Roofline representation of performance. Chapter 6 sets the Roofline single-core projection approach and uses our implementation to explore various hardware parameters such as hardware vector length or the change of memory type on three source Arm cores architectures: Neoverse N1, Fujitsu A64FX, and Marvell ThunderX2.

Finally, we adapt the roofline projection approach to a multicore environment thanks to a finer characterization of the bandwidth and the workload of each thread of the applications. Chapter 7 defines this multicore extension in addition to a preemptive study on the possible impact of different compilers and numerical methods when targeting a node supposedly close to the European Processor Initiative (EPI), unavailable at the time of the writing.

C. Gavoille

# Part I Context

## Chapter 1

# Context of High Performance Computing

Nowadays, science relies more and more on simulation and modelization to have a better understanding of our environment. One such example is climate science researchers that use this computing power for climate simulations. Furthermore, more computing power available translates to faster and more accurate simulations. But this need for computing power is not limited to climate science as, today, every science field such as aerospace or quantum physics relies on computing methods and simulation. And providing this computing power is the objective of High-Performance Computing (HPC) supercomputers.

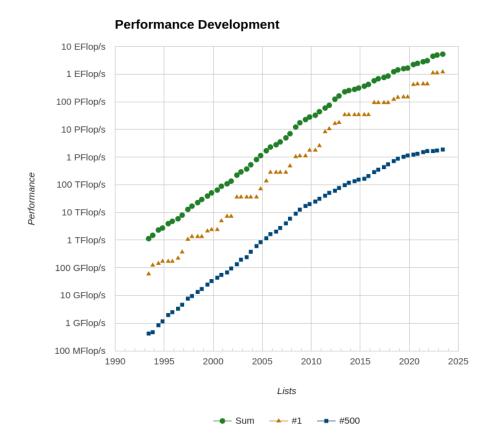

The first supercomputers were introduced in the 1960s. But their design has little similarity to today's supercomputers. Due to the increasing demand for computing power, their design has changed a lot to adapt. Figure 1.1 presents the evolution of the performance (in GFLOPS or billions of floating-point operations per second) of the sum of all 500 supercomputers of the Top500 ranking between 1993 and June 2023. As such, the available computing power has been growing exponentially since the first Top500 ranking in 1993.

Looking at the evolution of the top-ranked supercomputer, we can link its growth to the Empirical Moore's Law. However, this law is not viable anymore [93] yet the performance is still increasing and getting over the exaflops barrier (10<sup>18</sup> floating-point operations per second) with the American supercomputer Frontier. Moreover, overcoming performance barrier does not only depend on the computing speed of supercomputers. They also need to resolver the constraints imposed by the difference between memory and computing speed [81] and the power consumption and heat dissipation of CPUs [28]. It is, respectively, the memory wall and the power wall. Accordingly, to keep attaining higher performance and overcoming the barriers, the machines are becoming increasingly complex.

However, as supercomputers become increasingly complex, the HPC applica-

Figure 1.1: Evolution of the performance of the Top 500 # 1 and # 500 supercomputer and the sum of all ranked machines from 1993 to June 2023 Source: [19]

tions also need to adapt to these machines to be efficient. Hence, in today's HPC context, how are HPC applications optimized for performance on these supercomputers?

## 1.1 HPC applications

HPC applications are complex workloads that simulate many interactions between numerous physics phenomena. These workloads depend on a complex workflow with several steps before the final simulation results. Making optimization efforts

C. Gavoille

on the entire workflow is a difficult and tedious task because of the complex behavior and their long runtime. One such example is the WarpX Particle-In-Cell code awarded by the 2022 Gordon Bell prize [53]. Optimization efforts on this application were accomplished over several layers with many techniques such as load balancing, mesh refining, and parallelization. These optimization efforts on four supercomputers required an international team of researchers specialized in various domains.

One solution used to fasten and simplify these optimization efforts is the development of mini-apps and proxy apps. These codes aim to reproduce the main application's behavior or some parts of this application at a smaller scale. Hence, as the analysis time is much shorter and the execution flow is less complex, optimization of these codes is a faster and easier task than working on the full application. Then, optimization patterns found in these codes can be translated into the main application.

One of the main initiatives of this kind is the CORAL Benchmarks suite [18]. This benchmark suite consists of numerous mini-apps and proxy apps representing the HPC workload of the Lawrence Livermore National Laboratory (LLNL). It aims to converge the optimization and codesign efforts on these representative HPC workloads.

This suite is now widely used in HPC research and also in the work presented in this manuscript. We focus our validation and exploration efforts on some applications of this benchmark suite: LULESH, Quicksilver, MiniFE, and LAMMPS. All these applications are open-source through public git repositories [10, 16, 12, 15].

#### 1.1.1 LULESH

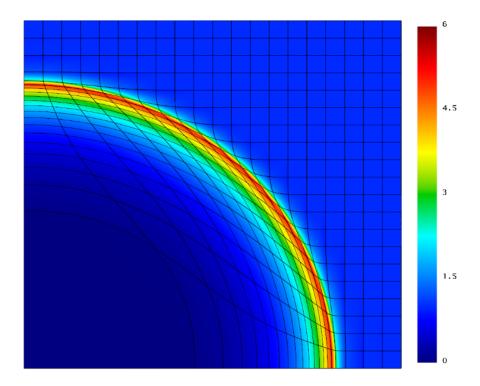

LULESH (Livermore Unstructured Lagrangian Explicit Shock Hydrodynamics) [58] is a widely used proxy application in HPC for performance prediction, analysis, and benchmarking. It is a simplification of the behavior of shockwave propagation through solid materials. It requires modeling hydrodynamics with a simple analytic answer. LULESH approximates the hydrodynamics equations discretely by partitioning the spatial problem domain into a collection of volumetric elements defined by a cartesian mesh. Figure 1.2 depicts a 2D visualization of the phenomenon modelized in 3D by LULESH.

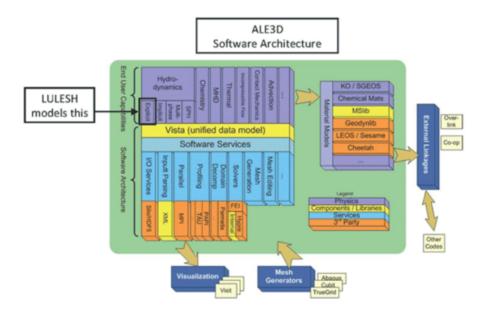

As a proxy application, LULESH represents only a minimal fraction of the LLNL's Ale3D [82] workflow described in Figure 1.3

It is a simplified application but a good representation of the numerical algorithms, data motion, and programming style typical in complex multi-material system deformation scientific simulations. This simplicity enabled LULESH to be developed using numerous programming models such as OpenMP, MPI, CUDA, or in several languages like Fortran, C/C+++, or Rust. Hence, optimizing perfor-

Figure 1.2: Simple Sedov Blast wave problem 2d modelization. LULESH represents this problem on a 3d cartesian mesh Source: [58]

mance and exploring different programming paradigms on LULESH is easier and faster than on the whole Ale3D application while still being representative of the behavior of one of the challenge problems of HPC.

## 1.1.2 Quicksilver

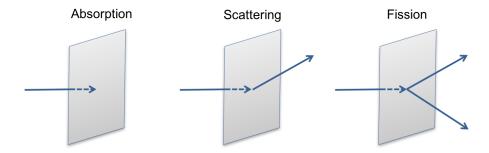

Quicksilver is a proxy application of the Mercury [29] application that simplifies a dynamic Monte Carlo particle transport problem. Monte Carlo methods [73] are also widely used in HPC applications for statistical sampling or integration approximation. Particle transport is one of its many uses.

Quicksilver modelizes three possible interactions of particles with matter: Absorption, Scattering, and Fission (See Figure 1.4).

The different possible behavior and the randomness of the Monte Carlo method generate a very conditional code with complex memory access patterns that is difficult to optimize and predict. This particular behavior justifies developing a proxy application with very flexible inputs.

C. Gavoille

Figure 1.3: Ale3D complex workflow. LULESH only represents a small fraction of this workflow by modelizing hydrodynamics equations with an explicit method. Source: [58]

Figure 1.4: The three possible interactions with matter of the randomly positioned particles modelized by Quicksilver.

Source: [86]

#### 1.1.3 MiniFE

MiniFE [11] is a mini-application implementing representative kernels of implicit finite-element applications part of the Mantevo Project of Sandia National Laboratory [26]. Here, the mini-application does not model real physics problems. However, many applications rely on an implicit solution of a nonlinear equations system. And they often use a variation of a conjugate gradient solver to resolve such systems.

MiniFE implements the conjugate gradient algorithm in four steps:

- Element-operators computation (source vector, diffusion matrix);

- Assembly (scattering element-operators into sparse matrix and vector);

- Conjugate Gradient solve (sparse matrix-vector product);

- Vector operations with BLAS (Basic Linear Algebra Subprograms).

Hence, finding optimization patterns on the various computing steps of such a linear system-solving application helps reduce the computing time of a widely used computing method and impacts the performance of numerous HPC applications.

#### 1.1.4 **LAMMPS**

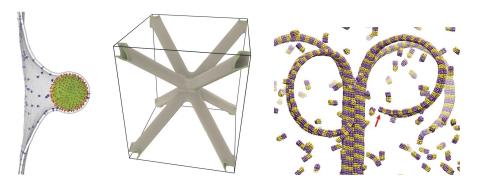

LAMMPS [94], for Large-scale Atomic/Molecular Massively Parallel Simulator, is not a single mini-application in itself. It is a classical molecular dynamics code with a focus on materials modeling. It can compute many systems such as solid-state materials (metals, semiconductors), soft matter(polymers, biomolecules), or coarse-grained systems with a variety of interatomic potentials. Figure 1.5 presents three model examples simulated with LAMMPS.

Figure 1.5: (Left) Coarse-grained model of a 100 nm virus-like particle budding through interaction with a cell membrane. Transmembrane proteins are shown in blue. (Middle) A hollow metal strut (200 nm on a side) is used to measure the mechanical strength and stiffness of ultra-lightweight nanoengineered materials. (Right) Coarse-grained simulation of catastrophic depolymerization of alpha-beta-tubulin.

Source: [94]

The flexibility of this framework allows us to use it to simulate simple phenomena and design many mini-apps. For example, we study a small particle diffusion

10 C. Gavoille

benchmark DIFFUSE obtained with LAMMPS in our experiments. It allows us to study the impact of different numerical schemes implemented in LAMMPS to compute the same solution.

To conclude, we have seen that real HPC applications rely on a complex work-flow. The optimization of these workflows requires a large amount of effort from experts in different domains. Hence, using mini-apps and proxy apps simplifies this work of performance optimization and exploration around different environments. Now that we have defined a representative panel of the HPC applications of interest through mini-apps and proxy apps, we present the current situation of today's HPC supercomputers that execute the workloads represented by these applications in the next section.

## 1.2 HPC supercomputers landscape

Supercomputers have changed a lot through their histories. Nowadays, all the Top500 supercomputers share a similar structure: a massively parallel architecture of computing nodes stored in racks linked by a high-performance interconnect.

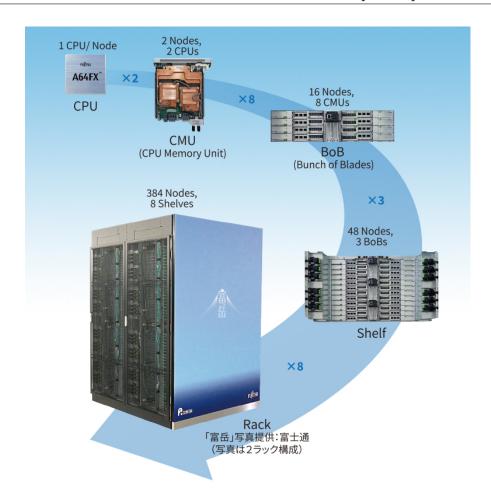

The following Figure 1.6 presents the composition of a Fugaku supercomputer rack. It is composed of 432 racks of 384 nodes split into 8 shelves with a 48 cores Fujitsu A64FX CPU per node. Fugaku consists of 158,976 nodes and 7,630,848 cores. With all these cores, Fugaku attained a performance of 442.01 PFLOPS, ranking 2nd in the Top500 of June 2023.

Using every node efficiently is primordial to obtain most of the computing power delivered by these massively parallel machines. Using parallelism in a machine is translated to many communications between computing nodes for some applications. However, communication between nodes is slow, and interconnect network performance can limit these applications' performance. Moreover, because the performance of applications is measured in FLOPS, or floating point operation per second, communication time is not seen as useful for the application. Furthermore, if a node is waiting for data because of communication time, it is also not doing any computation. Hence, optimizing the inter-nodes efficiency by implementing load balancing algorithm [101] or reducing communications time [47] of applications leads to significant performance gain on some applications. This is one of the many optimization patterns that have been found on the WarpX code by implementing particular parallelization strategies and load balancing adapted to the different machines that executed the code for the Gordon-Bell submission [53].

However, applications's performance is not only limited by inter-node commu-

Figure 1.6: Composition of a Fugaku rackSource: [17]

nications. The computing nodes' performance and efficiency can also be a limiting factor in applications' performance. Thus, an efficient usage of the node architecture is mandatory for applications to attain the highest performance on a particular machine.

In this work, we focus our study on the optimization efforts of homogenous nodes that rely on one or more general-purpose CPUs for their computing power. At first glance, with more than 95% of the June 2023 Top500 systems relying on x86 architecture (see Table 1.1), the architectural landscape of HPC CPUs seems homogenous hence simplifying optimization efforts on node efficiency.

Although present in only 1.2% of systems, the Arm architecture accounts for 9.8% of total Top500 performance. Its significant performance share is an accomplishment of the recent introduction of the Marvell ThunderX2 processors and, especially, the Fujitsu A64FX CPUs in Fugaku. Moreover, with future projects

| Architecture | Number | System Share | Performance Share |

|--------------|--------|--------------|-------------------|

| x86          | 483    | 96.4%        | 82%               |

| Power        | 7      | 1.4%         | 5.9%              |

| Arm          | 6      | 1.2%         | 9.8%              |

| Others       | 5      | 1%           | 2.3%              |

Table 1.1: Share of CPU architectures of the June 2023 Top 500 machines

relying on this Arm Neoverse roadmap [5] such as the European Processor Initiative (EPI) or NVIDIA Grace, the performance share of Arm in HPC will not be an accomplishment of a single machine.