## Degradation and Lifetime Reliability Models to Assess the Electromagnetic Compatibility Performance of Integrated Circuits Under Environmental Constraints

Md Jaber Al Rashid

#### ▶ To cite this version:

Md Jaber Al Rashid. Degradation and Lifetime Reliability Models to Assess the Electromagnetic Compatibility Performance of Integrated Circuits Under Environmental Constraints. Other. Université d'Angers, 2023. English. NNT: 2023ANGE0028. tel-04470767

#### HAL Id: tel-04470767 https://theses.hal.science/tel-04470767v1

Submitted on 21 Feb 2024

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THÈSE DE DOCTORAT DE

#### L'UNIVERSITÉ D'ANGERS

ÉCOLE DOCTORALE Nº 602 Sciences de l'Ingénierie et des Systèmes Spécialité : « Électronique, signal, génie industriel »

Par

« Md Jaber Al Rashid »

Degradation and Lifetime Reliability Models to Assess the EMC Performance of Integrated Circuits Under Environmental Constraints

Thèse présentée et soutenue à Angers, le « November 13, 2023 » Unité de recherche : Laboratoire LARIS, IETR de Rennes, ESEO Angers

Thèse No: « si pertinent »

#### Rapporteurs avant soutenance :

Ghaleb HOBLOS Professeur, ESIGELEC, IRSEEM

Tristan DUBOIS Maître de conférence HDR, Université de Bordeaux

#### **Composition du Jury:**

Président : Bruno Castanier Professeur, Université d'Angers d'exercice (à préciser après la soutenance)

Examinateurs: Ghaleb HOBLOS Professeur, ESIGELEC, IRSEEM

Tristan DUBOIS Maître de conférence HDR, Université de Bordeaux

Bruno Castanier Professeur, Université d'Angers Philippe Besnier Directeur de recherche, CNRS

Dir. de thèse : Mihaela Barreau Maître de conférences HDR, Université d'Angers Co-encadrant de thèse : Mohsen Koohestani Enseignant-Chercheur HDR, ESEO, Angers

Invité(s):

Richard Perdriau Enseignant-Chercheur HDR, ESEO, Angers

Frédéric Lafon Ingénieur EMC Master Expert, VALEO-GEES, Paris

Co-encadrant. de thèse : Laurent Saintis Maître de conférences, Université d'Angers

## **ACKNOWLEDGEMENT**

First and foreost, my sincere appreciation is expressed for the assistance, unwavering affection, support, and prayers that my parents, Harun Or Rashid and Shahnaz Rashid, have bestowed upon me during the course of my PhD studies. They have always believed in me and have been with me despite the distance. My sister and brother are also deserving of my gratitude for their unwavering support, affection, and confidence in me. It is not possible for me to be the person I am today without you all. I dedicate the entirety of my doctoral accomplishment to my family.

My deepest gratitude is extended to my three supervisors—Dr. Mohsen Koohestani from ESEO Engineering School, Dr. Mihaela Barreau, and Dr. Laurent Saintis from the LARIS, Polytech Angers—for their invaluable guidance, encouragement, and support throughout the completion of this dissertation, as well as for generating numerous ideas that formed the basis of this work. I would like to extend my heartfelt appreciation to Dr. Laurent Saintis and Dr. Mohsen Koohestani for their unwavering fortitude, encouragement, and inspiration during the years it took me to complete my PhD. These significant milestones that I have attained throughout my PhD journey are wholly at their disposal. Additionally, I appreciate Dr. Richard Perdriau's assistance and constructive criticism regarding the work I produced while at ESEO.

I would like to express my sincere appreciation to the evaluators of my doctoral dissertation, Dr. Tristan Dubois (University of Bordeaux) and Prof. Ghaleb Hoblos (ESIGE-LEC), for their meticulous examination of the manuscript and valuable comments and recommendations concerning the research endeavors detailed in the dissertation report. Moreover, I would like to express my gratitude for the insightful feedback and contributions made by two CSI members—Professor Bruno Castanier from the University of Angers—and Dr. Frederic Lafon—during the three years I spent pursuing my doctorate. Their review of the ongoing thesis work significantly enhanced the dissertation's quality. Additionally, I would like to express my gratitude to the remaining members of the doctoral examination committee for attending the defense of my thesis and offering their invaluable counsel and feedback regarding the thesis that was presented.

I express my sincere gratitude to the funding agency, Pays de la Loire Region, An-

gers Metropole, University of Angers, and ESEO Engineering School for granting me the opportunity to participate in this pioneering endeavor that characterizes the long-term evolution of electromagnetic compatibility (EMC) performance degradation at the IC component level in order to model the predictive reliability of integrated circuits. I express my gratitude to the LARIS laboratory affiliated with Polytech Angers and the RF-EMC laboratory featured in the ESEO Engineering School for furnishing me with cutting-edge facilities, including contemporary engineering components and apparatus that facilitated the execution of essential experiments and measurements essential to complete the dissertation.

Finally, I would like to extend my sincere appreciation and pleasure to all my PhD colleagues and closest friends, with a special mention to Mohammed Salim Bidou, Sabrine Dachraoui, and Faitma-Ezahra, whom I met during my doctoral studies at the LARIS laboratory in Polytech Angers. Their unwavering support, inspiration, and the countless pleasant moments we have shared together have been invaluable to me throughout this endeavor. All of these memories would be cherished for the remainder of my life. It was a delight to interact with each of you at multiple social gatherings and excursions. Furthermore, I would like to express my gratitude to my ESEO Engineering School companions, specifically Qazi MashaaI and Mokhtarul, for the invaluable moments we have shared. could remember each of you for the remainder of my existence.

# **TABLE OF CONTENTS**

| In | $\operatorname{trod}$ | luction                                                                                       | 19         |

|----|-----------------------|-----------------------------------------------------------------------------------------------|------------|

| 1  |                       | State-Of-The-Art on IC-EMC Reliability: Methodology, Modeling laging Impact on the EMC of ICs | 27         |

|    | 1.1                   | EMC of ICs: Conducted Immunity Measurement and Analysis                                       | 28         |

|    | 1.1                   | 1.1.1 Transient EM conducted immunity measurement of ICs                                      | 30         |

|    |                       | 1.1.2 Conducted immunity measurement of ICs in frequency domain                               | 35         |

|    |                       | 1.1.3 Conducted immunity and emission modeling techniques of ICs                              | 39         |

|    | 1.2                   | General Principles on EMR of ICs                                                              | 52         |

|    | 1.3                   | •                                                                                             | 62         |

|    | 1.4                   | Conclusion                                                                                    | 68         |

|    |                       |                                                                                               |            |

| 2  | Cot                   | upling Simulation and Accelerated Degradation Model for Reliability                           |            |

|    | Est                   | imation of an Analog CMOS Circuit                                                             | <b>7</b> 0 |

|    | 2.1                   | Introduction                                                                                  | 71         |

|    | 2.2                   | Circuit Design and Simulation                                                                 | 72         |

|    |                       | 2.2.1 $$ Simulation results : temperature and voltage sensitivity analysis $$                 | 74         |

|    |                       | 2.2.2 Electrical simulation model                                                             | 74         |

|    | 2.3                   | Degradation Path and ALT Modeling                                                             | 76         |

|    |                       | 2.3.1 Degradation model estimation                                                            | 77         |

|    | 2.4                   | Reliability Estimation : Life Data Analysis                                                   | 79         |

|    | 2.5                   | Conclusion                                                                                    | 85         |

| 3  | Cor                   | nducted Immunity Evaluation of Analog ICs Integrating Obsoles-                                |            |

|    | cen                   | ce and Temperature Stress in Long Lifespan Systems                                            | 86         |

|    | 3.1                   | Introduction                                                                                  | 87         |

|    | 3.2                   | Materials and Methodology                                                                     | 89         |

|    |                       | 3.2.1 Devices under test                                                                      | 90         |

|    |                       | 3.2.2 Experimental setup                                                                      | 91         |

|    | 3.3                   | Results and Findings                                                                          | 03         |

#### TABLE OF CONTENTS

|   |      | 3.3.1 Conducted immunity of ICs under nominal conditions 93                |

|---|------|----------------------------------------------------------------------------|

|   |      | 3.3.2 Conducted immunity of ICs under thermal stress conditions 94         |

|   | 3.4  | S-parameter Measurement and Impedance Extraction                           |

|   | 3.5  | Conclusion                                                                 |

| 4 | Inve | estigate and Analyze the Influence of High Temperature Accelerated         |

|   |      | ng on the Conducted Immunity Modelling of the Analog ICs 107               |

|   | 4.1  | Introduction                                                               |

|   | 4.2  | Materials and Methods                                                      |

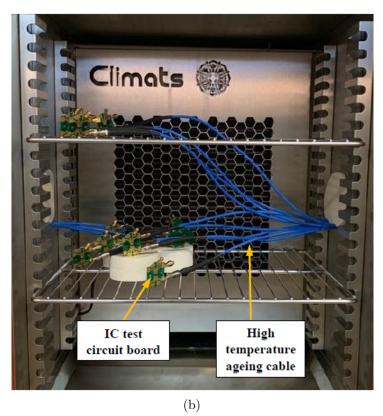

|   |      | 4.2.1 Accelerated aging test plan                                          |

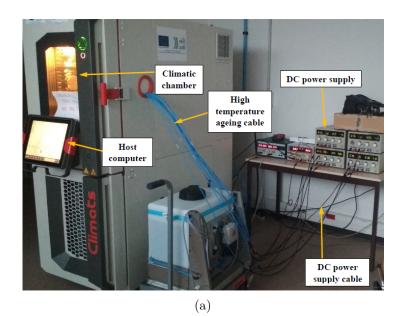

|   |      | 4.2.2 Measurement test setup and procedures                                |

|   | 4.3  | Results and Discussion                                                     |

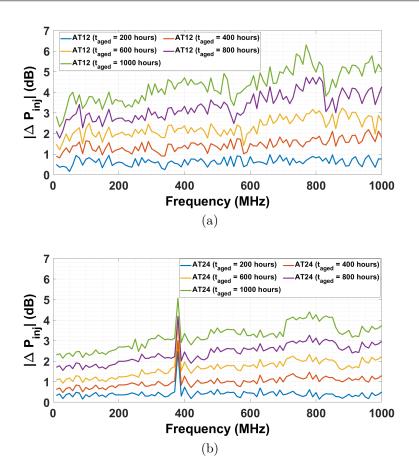

|   |      | 4.3.1 Accelerated aging impact on conducted immunity                       |

|   |      | 4.3.2 Aging induced conducted immunity drift of ICs                        |

|   | 4.4  | Effect of Aging on the ICIM-CI Model of ICs                                |

|   | 4.5  | Conclusion                                                                 |

|   | _    |                                                                            |

| 5 | _    | gradation and Reliability Modeling Approaches to Assess the Long-          |

|   |      | m EM Robustness of ICs                                                     |

|   | 5.1  | Introduction                                                               |

|   | 5.2  | State-of-the-Art on ALT and ADT                                            |

|   | 5.3  | Materials and Methods: EMR Assessment of Analog ICs                        |

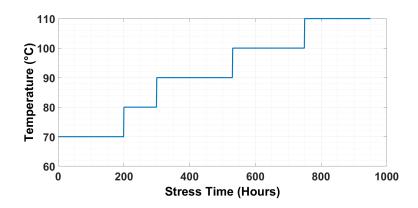

|   |      | 5.3.1 The thermal step-stress ADT plan                                     |

|   |      | 5.3.2 Measurement setup and procedure                                      |

|   |      | 5.3.3 Experimental methodology                                             |

|   | F 4  | 5.3.4 DPI test procedure and measurement algorithm                         |

|   | 5.4  | Experimental Results and Analysis of Analog ICs                            |

|   |      | 5.4.1 Conducted immunity characterization of the analog DUTs 135           |

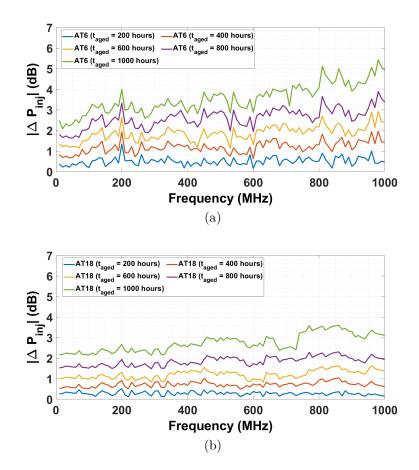

|   |      | 5.4.2 Conducted immunity drift of the aged analog ICs                      |

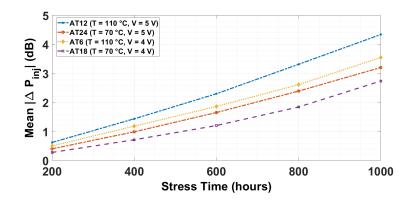

|   | 5.5  | Degradation Path Modeling and Pseudo Lifetime Estimation of Analog ICs 142 |

|   | 5.6  | Accelerated Life Test (ALT) Modeling and Analysis of Analog ICs 146        |

|   |      | 5.6.1 ALT reliability modeling and parameter estimation                    |

|   |      | 5.6.2 Reliability and life-data analysis of analog DUTs                    |

|   | 5.7  | Step-stress ADT Modeling of Analog DUTs                                    |

| 5.8     | Degra  | dation and lifetime Reliability Modeling of Digital ICs Influenced by |     |

|---------|--------|-----------------------------------------------------------------------|-----|

|         | the CS | SADT Ageing Constraints                                               | 158 |

|         | 5.8.1  | Constant stress ADT plan                                              | 158 |

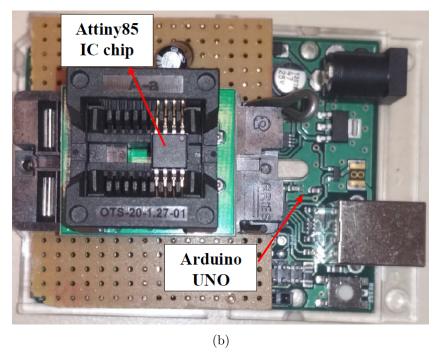

|         | 5.8.2  | Attiny85 IC under test                                                | 158 |

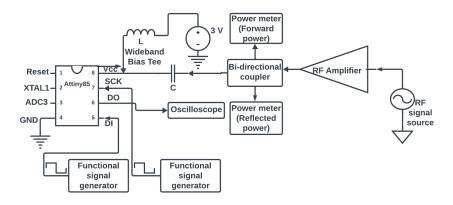

|         | 5.8.3  | Experimental methods and measurement procedures                       | 163 |

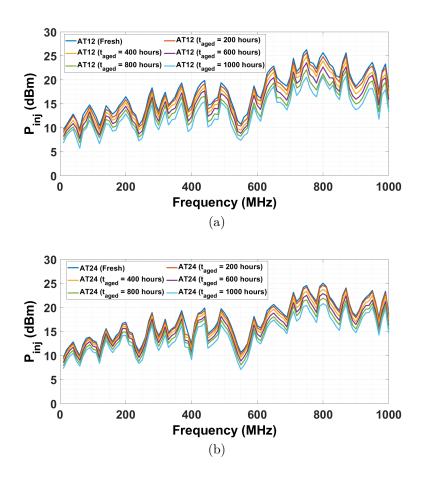

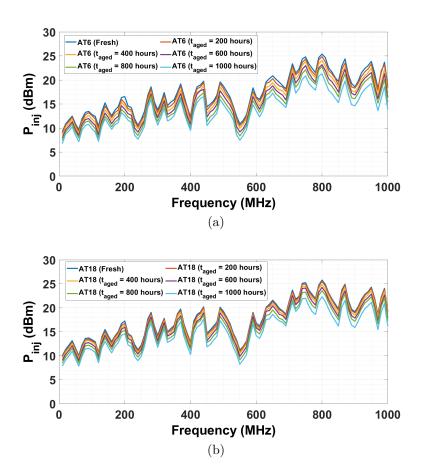

|         | 5.8.4  | Conducted immunity performance of the aged DUTs : results and         |     |

|         |        | analysis                                                              | 166 |

|         | 5.8.5  | EMC degradation modeling and parameter estimation of the aged         |     |

|         |        | DUTs                                                                  | 170 |

|         | 5.8.6  | ALT modeling and reliability analysis of the tested ICs               | 175 |

| 5.9     | Concl  | usion                                                                 | 179 |

| Conclu  | sion a | nd Perspectives                                                       | 183 |

| Bibliog | raphy  |                                                                       | 191 |

# List of Acronyms

| ADT Accelerated Degradation Test             | 22 |

|----------------------------------------------|----|

| AF Acceleration Factor                       | 62 |

| ALT Accelerated Life Test                    | 24 |

| CDF Cumulative Distribution Function         | 62 |

| CMOS Complementary Metal-Oxide-Semiconductor | 24 |

| <b>DPI</b> Direct Power Injection            | 12 |

| DUT Device Under Test                        | 22 |

| EMC Electromagnetic Compatibility            | 19 |

| EMI Electromagnetic Interference             | 19 |

| EMR Electromagnetic Robustness               | 23 |

| <b>EFT</b> Electric Fast Transient           | 12 |

| FIT Failure in Time                          | 63 |

| FPGA Field Programmable Gate Array           | 71 |

| HALT High Accelerated Life Test              | 63 |

| HCI Hot Carrier Injection                    | 58 |

#### TABLE OF CONTENTS

| HTOL High Temperature Operating Life Test                               | 71  |

|-------------------------------------------------------------------------|-----|

| IA Internal Activity                                                    | 49  |

| IB Immunity behavioral                                                  | 24  |

| IC Integrated Circuit                                                   | 19  |

| ICs Integrated Circuits                                                 | 19  |

| ICEM-CE Integrated Circuit Emission Modeling-Conducted Emission         | 28  |

| ICIM-CI Integrated Circuit Immunity Modeling-Conducted Immunity         | 22  |

| ICIM-CPI Integrated Circuit Immunity Modeling- Conducted Pulse Immunity | 28  |

| IFR Instantaneous Failure Rate                                          | 62  |

| LTOL Low Temperature Operating Life Test                                | 71  |

| MLE Maximum Likelihood Estimation                                       | 24  |

| MOSFET Metal Oxide Semiconductor Field Effect Transistor                | 73  |

| M-STORM Multi-stressor Predictive Reliability Model                     | 71  |

| MTOL Multiple Temperature Operating Lifetime                            | 71  |

| MTTF Mean Time-to-Failure                                               | 128 |

| NLB Non Linear Block                                                    | 40  |

| NBTI Negative Bias Transistor Instability |

|-------------------------------------------|

| PCB Printed Circuit Board                 |

| PDN Passive Distribution Network          |

| PDF Probability Density Function          |

| PoF Probability of Failure                |

| TDDB Time Dependent Dielectric Breakdown  |

| TTF Time-to-Failure                       |

| VNA Vector Network Analyzer               |

| $V_{th}$ Threshold Voltage                |

| $I_{on}$ Saturation Current               |

| R(t) Reliability function                 |

| $V_{ds}$ Drain-source Voltage             |

| $I_{ds}$ Drain-source Current             |

# **TABLE DES FIGURES**

| 1.1  | Electric Fast Transient (EFT) pulse waveform injected into the IC pins      |    |

|------|-----------------------------------------------------------------------------|----|

|      | using the P200 probe [11]                                                   | 31 |

| 1.2  | EFT pulse waveform injected into the IC pins using the P200 probe $[13]$ .  | 32 |

| 1.3  | EFT voltage injection on DUTs with different error states observed (a)      |    |

|      | VDD; (b) IO pins [14]                                                       | 34 |

| 1.4  | Direct Power Injection (DPI) test setup for characterizing the conducted    |    |

|      | immunity of an IC under test [17]                                           | 35 |

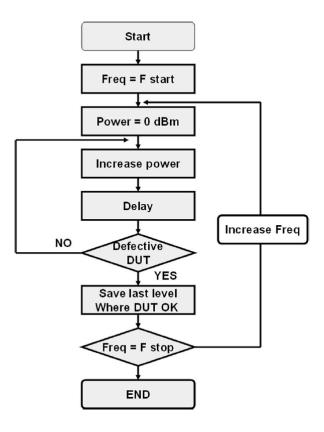

| 1.5  | Proposed flowchart for the DPI test algorithm to characterize the conducted |    |

|      | immunity level of an IC under test [17]                                     | 36 |

| 1.6  | DPI test result for evaluating the conducted immunity level of an IC under  |    |

|      | test at different failure criterion [17]                                    | 37 |

| 1.7  | DPI test algorithm setup for evaluating the conducted immunity level of     |    |

|      | an IC under test [15]                                                       | 38 |

| 1.8  | Simulation and the measurement result for evaluating the conducted im-      |    |

|      | munity level the DUT [15]                                                   | 39 |

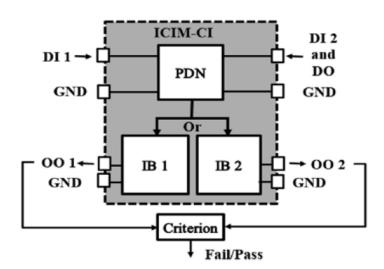

| 1.9  | Dual port ICIM-CI model structure of an IC [20]                             | 41 |

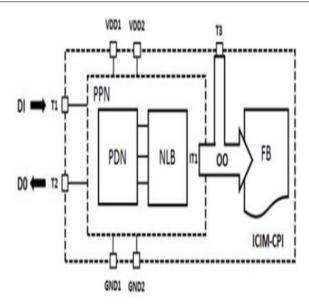

| 1.10 | Structure of the proposed ICIM-CPI model [21]                               | 42 |

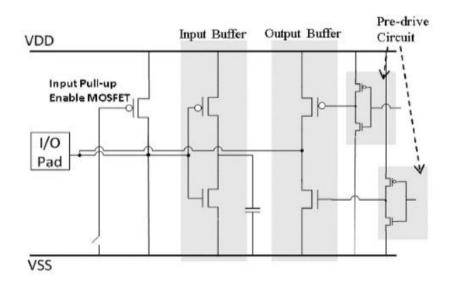

| 1.11 | IC model structure with EFT setup [22]                                      | 43 |

| 1.12 | IO model protection circuitry of IC model [22]                              | 44 |

| 1.13 | IC immunity model for the PLL component including the direct power          |    |

|      | injection test setup [24]                                                   | 45 |

| 1.14 | Measurement method for the IC PDN model extraction [25]                     | 46 |

| 1.15 | Measurement method for the IC package model extraction [25]                 | 47 |

| 1.16 | Model validation result (a) EFT voltage 200 V; (b) EFT voltage 1600 V       |    |

|      | applied to the VDD pin [22]                                                 | 48 |

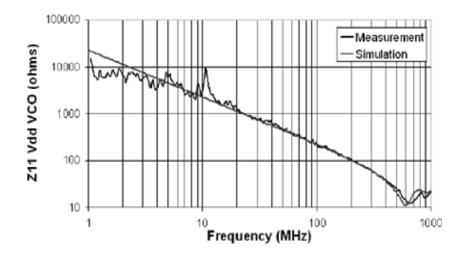

| 1.17 | Impedance measurement from VDD VCO pin [24]                                 | 49 |

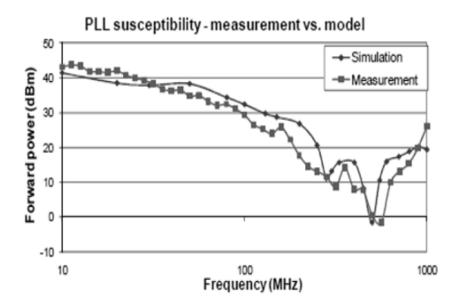

| 1.18 | Immunity profile comparison between the model and measurements [24]         | 50 |

| 1.19 | Emission model for the digital core circuit embedded in the IC [26]         | 51 |

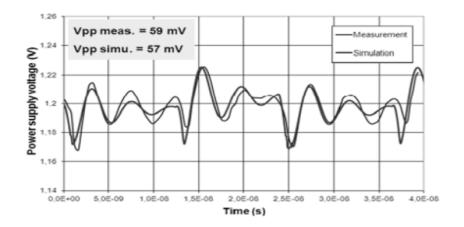

| 1.20 | Simulated and measured digital core power supply voltage fluctuation [26].  | 51 |

| 1.21 | Simulated and measured conducted EM emission level from the digital core         |    |

|------|----------------------------------------------------------------------------------|----|

|      | [26]                                                                             | 52 |

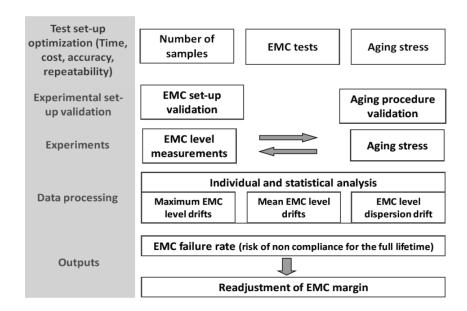

| 1.22 | Experimental methodology for characterizing EMR of ICs [1], [4]                  | 53 |

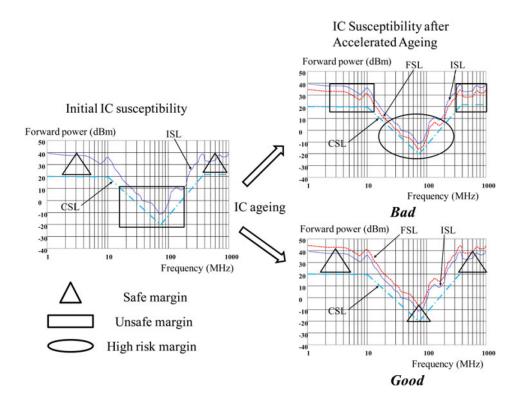

| 1.23 | Characterizing the EMR of the DUT under the influence of aging [3]               | 55 |

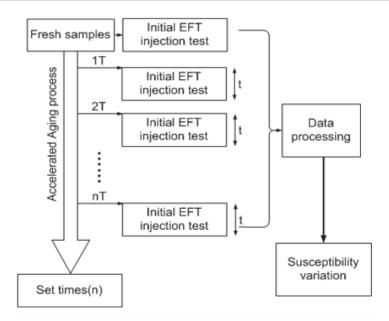

| 1.24 | Time-dependent EMR methodology under accelerated aging conditions [11].          | 56 |

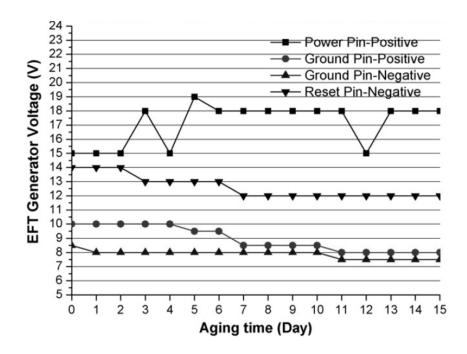

| 1.25 | EFT failure injection voltage on IC both fresh and aged IC pins[11]              | 57 |

| 1.26 | Block diagram for the ICIM-CI model with integrated external environ-            |    |

|      | mental model for aging [27]                                                      | 58 |

| 1.27 | Proposed aging-aware ICIM model methodology [8]                                  | 59 |

| 1.28 | Proposed aging-aware EM susceptibility model structure of the operational        |    |

|      | amplifier [28]                                                                   | 60 |

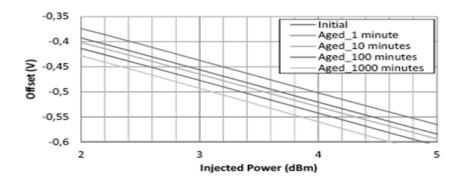

| 1.29 | Aging impact on the DC offset voltage as a function of the RF power at           |    |

|      | 200 MHz [28]                                                                     | 60 |

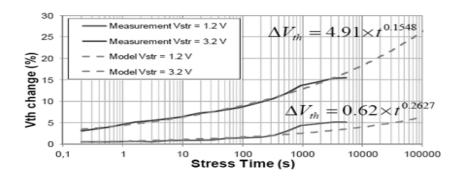

|      | Threshold voltage variations depending on the different aging conditions [26].   | 61 |

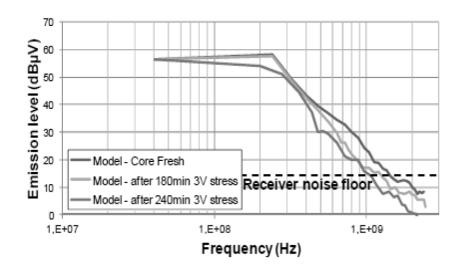

| 1.31 | Evolution of the EM emission level of the digital core circuit due to aging      |    |

|      | stress [29]                                                                      | 61 |

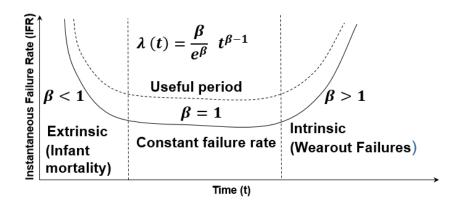

| 1.32 | Bathtub curve showing the Weibull distribution of the electronic com-            |    |

|      | ponent operating lifetime period [30]                                            | 65 |

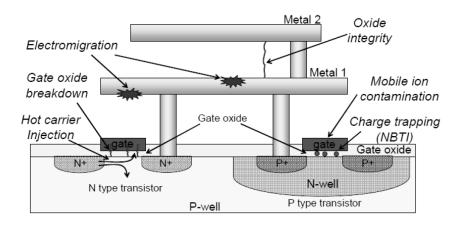

|      | Intrinsic failure mechanisms induced in CMOS transistor of an IC [33]            | 66 |

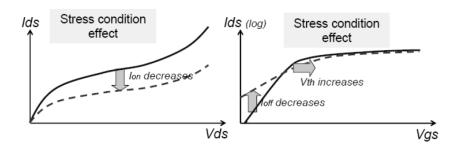

| 1.34 | CMOS transistor parameter variations induced by intrinsic failure mecha-         | 0. |

|      | nisms from an EMC point of view [33]                                             | 67 |

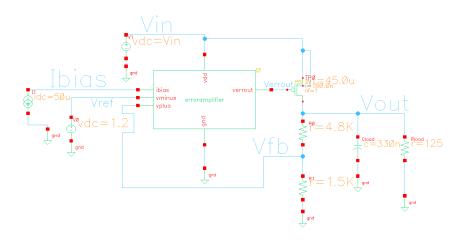

| 2.1  | Circuit design schematic of the studied regulator                                | 73 |

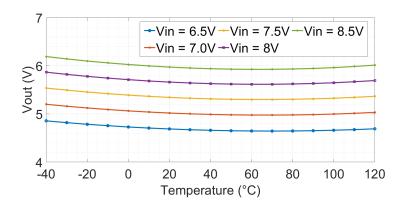

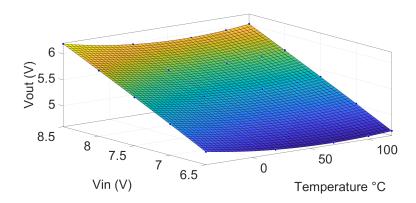

| 2.2  | Output voltage as a function of temperature and input voltage variation          | 75 |

| 2.3  | Simulation curve fitting model of the output voltage                             | 76 |

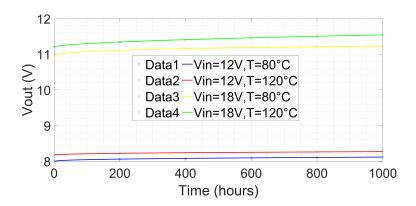

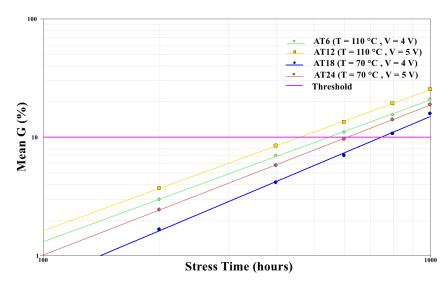

| 2.4  | Degradation path model fitted to the output voltage data of the regulator        |    |

|      | at different stress conditions                                                   | 78 |

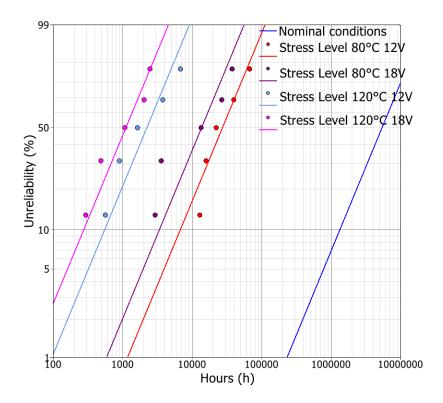

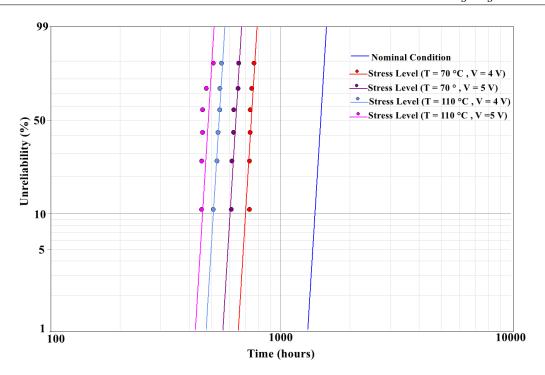

| 2.5  | Weibull distribution fits to pseudo failure time at different stress conditions. | 84 |

| 3.1  | Visual representation of the research study                                      | 88 |

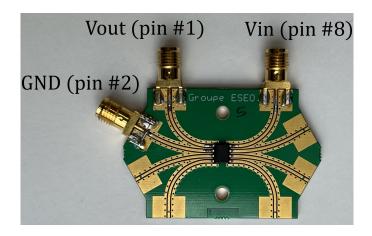

| 3.2  | Voltage regulator IC mounted on a custom DPI test board                          | 90 |

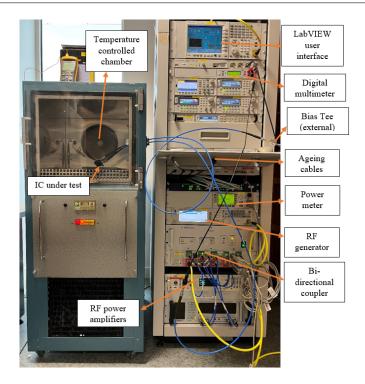

| 3.3  | DPI test bench setup with temperature controlled chamber                         | 92 |

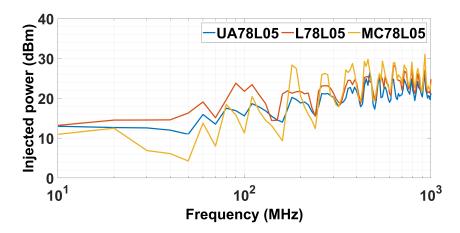

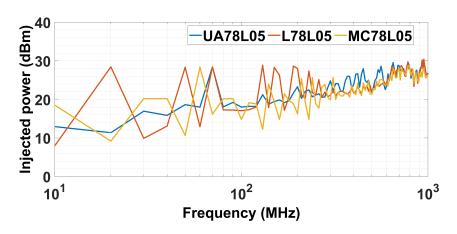

| 3.4  | Incident RF power as a function of frequency at +25 °C                           | 94 |

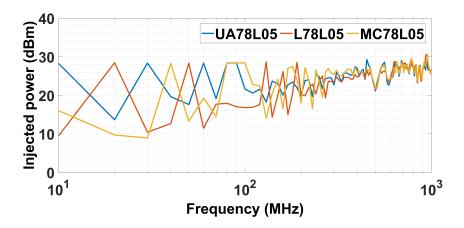

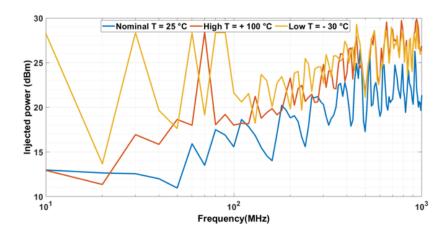

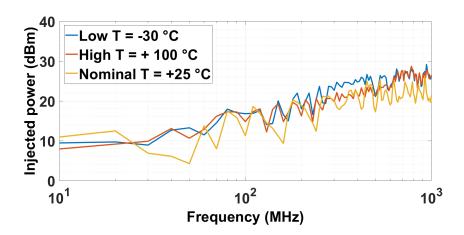

| 3.5  | Incident RF power as a function of frequency at $-30$ °C                         | 95 |

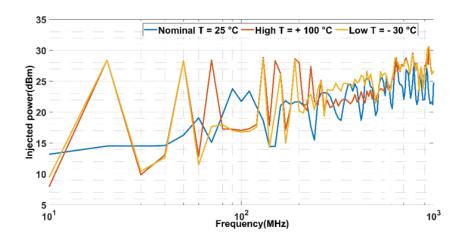

| 3.6  | Incident RF power as a function of frequency at +100 °C                          | 95 |

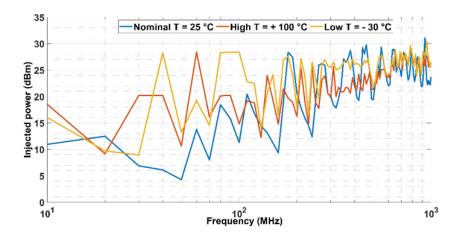

| 3.7  | Conducted immunity of UA78L05 as a function of different thermal stress conditions                                                                                                           | 97  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.8  | Conducted immunity of L78L05 as a function of different thermal stress conditions                                                                                                            | 97  |

| 3.9  | Conducted immunity of MC78L05 as a function of different thermal stress conditions                                                                                                           | 98  |

| 3.10 | Minimum immunity of the three regulators under the considered thermal stresses                                                                                                               | 98  |

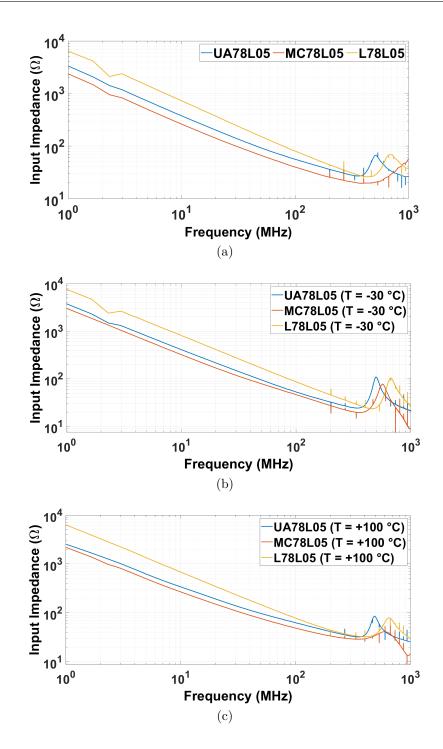

| 3.11 | Input impedance of the tested ICs at different temperatures : (a) +25 $^{\circ}\mathrm{C}$ ;                                                                                                 | 101 |

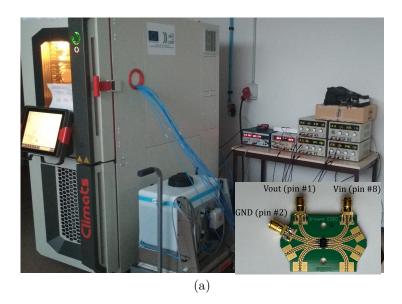

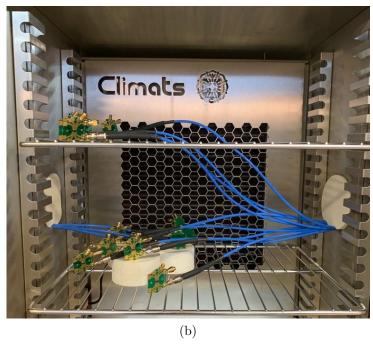

| 4.1  | Accelerated aging test set-up (a) outside view; (b) inside view of the climatic chamber                                                                                                      | 112 |

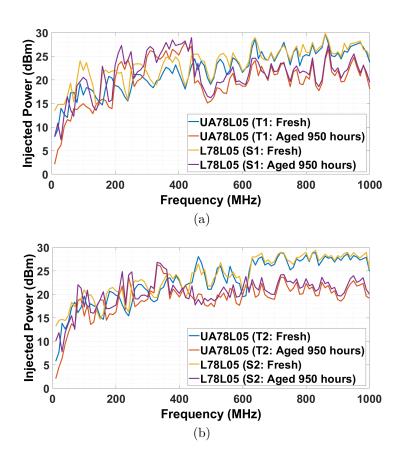

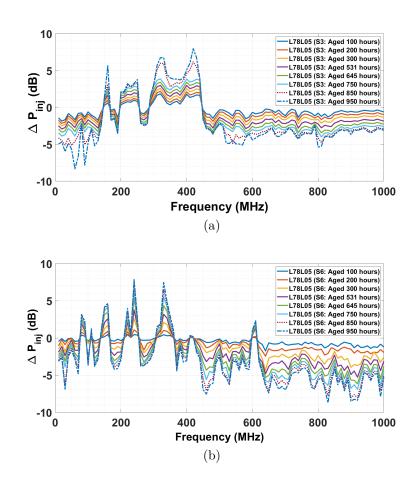

| 4.2  | Aging impact on the conducted immunity profile of IC samples under same thermal stress and (a) low electrical overstress (i.e., 9 V); (b) high electrical overstress conditions (i.e., 12 V) | 115 |

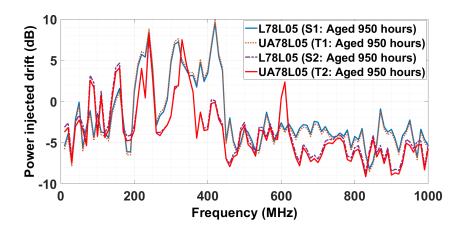

| 4.3  | Influence of the aging on the conducted immunity drift of the tested ICs.                                                                                                                    |     |

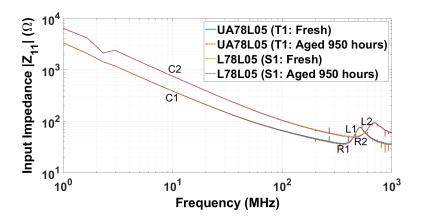

| 4.4  | Influence of the aging on the input impedance profile of $V_{in}$ of the selected                                                                                                            |     |

| 4.5  | ICs                                                                                                                                                                                          |     |

| 5.1  | The step-stress ADT plan                                                                                                                                                                     | 130 |

| 5.2  | Experimental test setup: (a) outside and (b) inside views of the climatic chamber                                                                                                            |     |

| 5.3  | Time-dependent accelerated aging methodology                                                                                                                                                 |     |

| 5.4  | (a) DPI test bench setup, (b) flowchart of the DPI measurement algorithm.                                                                                                                    |     |

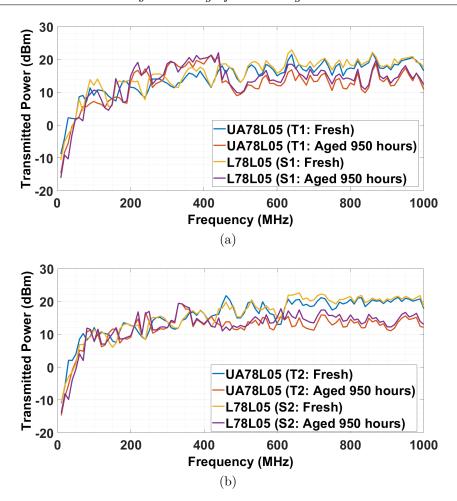

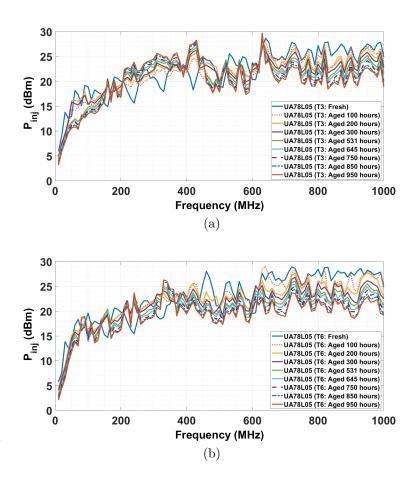

| 5.5  | Evolution of the conducted immunity level of UA78L05 samples at various stress duration caused by the identical thermal step-stress and (a) low;                                             |     |

| 5.6  | (b) high voltage overstress                                                                                                                                                                  | 137 |

|      | •                                                                                                                                                                                            | 138 |

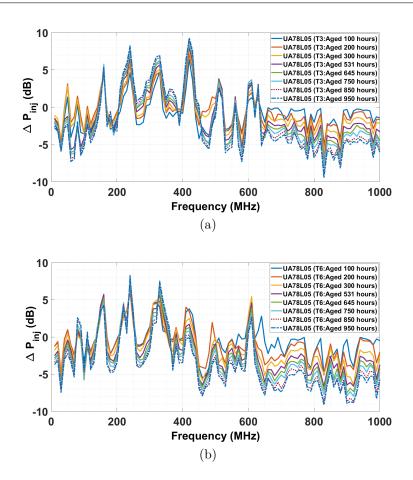

| 5.7  | Conducted immunity level drift of UA78L05 samples at various stress du-       |     |

|------|-------------------------------------------------------------------------------|-----|

|      | ration caused by the thermal step-stress as well as (a) low and (b) high      |     |

|      | voltage overstress                                                            | 140 |

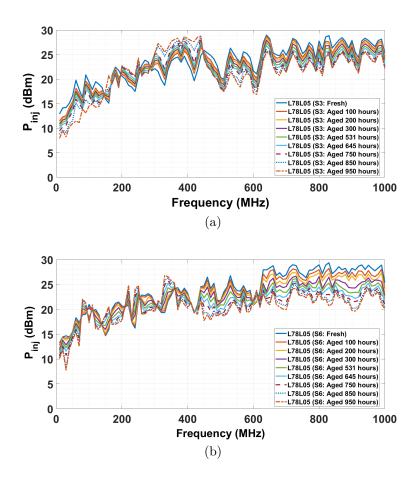

| 5.8  | Conducted immunity level drift of L78L05 samples at various stress du-        |     |

|      | ration caused by the thermal step-stress as well as (a) low and (b) high      |     |

|      | electrical overstress                                                         | 141 |

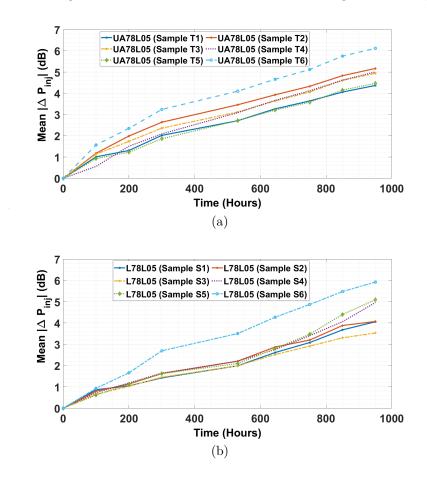

| 5.9  | Conducted immunity degradation as a function of the stress time on the        |     |

|      | tested samples of (a) UA78L05, (b) L78L05                                     | 143 |

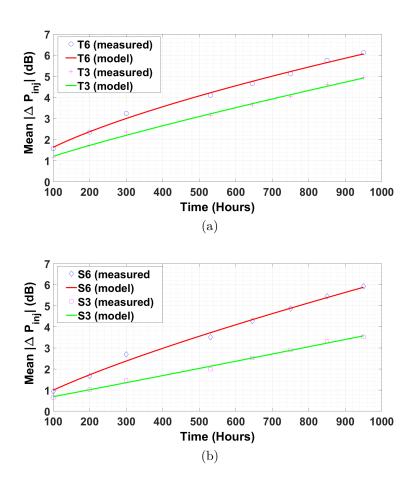

| 5.10 | Degradation path fitted to the EMC degradation data of ICs samples            |     |

|      | (a) UA78L05, (b) L78L05                                                       | 145 |

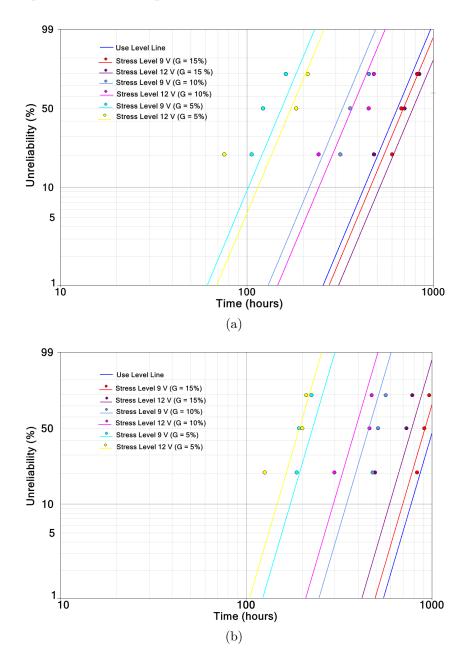

| 5.11 | lifetime reliability Weibull distribution fits to pseudo failure time at dif- |     |

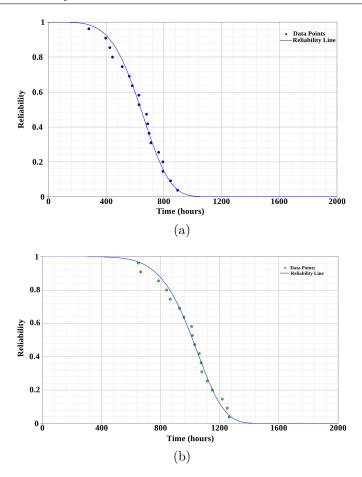

|      | ferent stress conditions applied on (a) UA78L05, (b) L78L05                   | 150 |

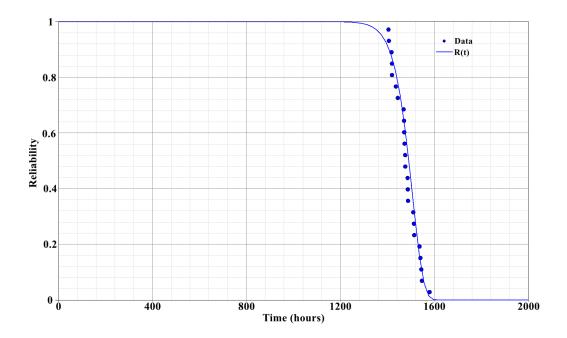

| 5.12 | Reliability function based on the proposed ALT model fits to the degrada-     |     |

|      | tion data of (a) UA78L05, (b) L78L05                                          | 152 |

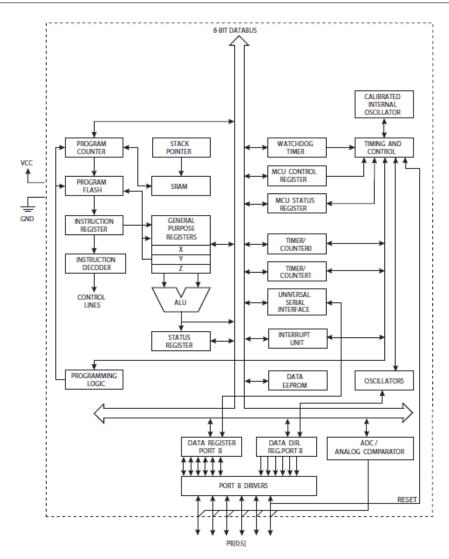

| 5.13 | Internal block diagram of the Attiny85 micro-controller IC chip [89]          | 160 |

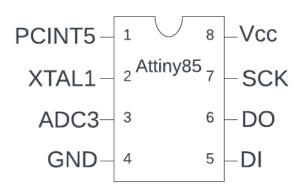

| 5.14 | Pin configuration of the Attiny85 micro-controller IC chip [89]               | 161 |

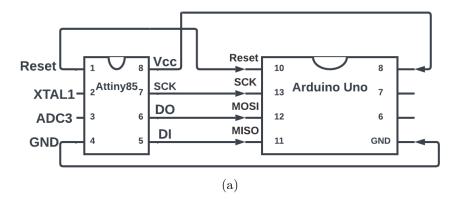

| 5.15 | Interfacing the Attiny85 IC pins with the Arduino UNO (a) schematic;          |     |

|      | (b) component                                                                 | 162 |

| 5.16 | Measurement test setup for evaluating the conducted immunity of the DUTs      | 164 |

| 5.17 | Evolution of the conducted immunity level of Attiny85 samples at various      |     |

|      | aging stress duration caused by the identical 5 V electrical voltage overs-   |     |

|      | tress and constant (a) high; (b) low thermal stress conditions                | 167 |

| 5.18 | Evolution of the conducted immunity level of Attiny85 samples at various      |     |

|      | aging stress duration caused by the identical 4 V electrical voltage overs-   |     |

|      | tress and constant (a) high; (b) low thermal stress conditions                | 168 |

| 5.19 | Conducted immunity level drift of Attiny85 samples at various aging stress    |     |

|      | time caused by the identical 5 V electrical voltage overstress as well as     |     |

|      | constant (a) high; and (b) low thermal stress conditions                      | 169 |

| 5.20 | Conducted immunity level drift of Attiny85 samples at various aging stress    |     |

|      | time caused by the identical 4 V electrical voltage overstress as well as     |     |

|      | constant (a) high; and (b) low thermal stress conditions                      | 171 |

| 5.21 | Conducted immunity degradation as a function of stress time under the         |     |

|      | influence of accelerated aging conditions on the tested IC samples            | 172 |

#### TABLE DES FIGURES

| 5.22 | Degradation paths fitted to the computed EMC degradation of the tested                       |     |

|------|----------------------------------------------------------------------------------------------|-----|

|      | IC samples                                                                                   | 173 |

| 5.23 | Log-linear degradation paths generated at different constant multiple stress                 |     |

|      | conditions to estimation of the failure time data                                            | 174 |

| 5.24 | Lifetime unreliability distribution of the logarithmic fits to the pseudo TTF                |     |

|      | data for each tested IC samples at different accelerated stress conditions. $\boldsymbol{.}$ | 177 |

| 5.25 | Reliability function curve fits to the estimated lifetime data based on the                  |     |

|      | developed ALT reliability model for the tested ICs                                           | 179 |

# LISTE DES TABLEAUX

| 1.1 | Parameters of the burst for the EFT test [12]                                  |

|-----|--------------------------------------------------------------------------------|

| 1.2 | Classification of different failure modes observed during the EFT test [11],   |

|     | [14]                                                                           |

| 1.3 | Intrinsic failure mechanisms of an IC induced by accelerated aging $[32]$ $66$ |

| 2.1 | External electronic components utilized to design the test bench circuit of    |

|     | the studied regulators                                                         |

| 2.2 | Degradation model parameters and TTF under different stress conditions . 79    |

| 2.3 | Reliability model estimation parameters under different accelerated stress     |

|     | conditions                                                                     |

| 3.1 | PDN Model Extraction for the Considered ICs as a Function of Temperature 102   |

| 3.2 | IB Look up Table for Tested ICs at Nominal Temperature                         |

| 4.1 | Design Of The Accelerated aging Test Plan                                      |

| 4.2 | Aging Induced Immunity Drift Parameters                                        |

| 5.1 | Aging stress conditions to perform the ADTs on the ICs                         |

| 5.2 | ALT Reliability Model Parameters for both L78L05 and UA78L05 $148$             |

| 5.3 | Degradation Model Parameters for both L78L05 and UA78L05 157                   |

| 5.4 | Accelerated ageing conditions to perform the constant stress ADTs on the       |

|     | ICs                                                                            |

| 5.5 | EMC degradation path modeling parameters and TTF data of various tes-          |

|     | ted IC samples                                                                 |

| 5.6 | ALT reliability modeling parameters for the tested IC samples 176              |

## INTRODUCTION

This general introduction highlights a brief overview of the background and motivation for conducting the research on the reliability study that involves developing degradation and lifetime reliability models of analog and digital circuits at the Integrated Circuit (IC) chip level developed by manufacturers, with regards to assessing the Electromagnetic Compatibility (EMC) performance, in particular, the conducted immunity to the electromagnetic (EM) disturbances due to the influence of different specified environmental stress conditions (i.e., thermal and electrical voltage overstress). It is then followed by providing research objectives aligned with the title of the thesis report. Afterwards, the organization of the thesis report is presented, prior to mentioning a list of associated publications, in scientific journals and conferences. Note that all the figures, tables and results provided in this report are produced by the author, unless specified otherwise.

#### Motivation for EMC and Reliability Study of ICs

Over the past few decades, electronic products have become increasingly pervasive in everyday life. The semiconductor industry simultaneously incorporates more and more circuits onto Printed Circuit Board (PCB)s in an effort to provide more functionality at lower power consumption, higher speed, and smaller dimensions. Not only have their complexities increased, but they are also increasingly exposed to EM contamination sources, particularly as a result of the heavy congestion of ubiquitous wireless systems emitting EM signals across a broad spectrum of frequencies. Therefore, the ability to operate these devices without interfering with one another is of the utmost importance. Particularly, their EM conduction/emission must be regulated, and they must be sufficiently immune to other Electromagnetic Interference (EMI). EM disturbances in Integrated Circuits (ICs) can originate either (1) from the external environment (external immunity issues): they are generated by other devices and propagate through PCB tracks and harnesses (conducted mode) or as EM waves (radiated mode), or (2) from within the IC itself (internal immunity, auto-immunity issues): for instance, a million-transistor digital block can generate current spikes flowing through the power supply network, whixh is likely to

disturb an analog, digital or mixed signal block located on the same die. Within a given frequency range, the conducted or radiated emission level of an IC (the "aggressor") can reach and even exceed the susceptibility level of the other (the "victim").

The rapid speed of invention, as well as the industrial EMC trend, support the massive need for downsizing of ICs with ever-increasing functionality. According to the International Technology Roadmap for Semiconductors (ITRS), reduction of the geometric size or dimention of the IC enables the integration of an increasing number of functional logic gates and transistors on an IC, but at the expense of power consumption and peak current. With peak currents of several hundreds of amperes, aPCB and system designer cannot rely solely on 'classical' PCB-level EMI reduction techniques to ensure that their product complies with standard EMC regulations. As a result, IC designers must consider the necessity for EMI suppression at their own level. Such efforts to create a modern IC chip, which governs certain processes in electronic embedded systems, not only make the IC more prone to partial or complete failure in the presence of an EM disturbance, but also make maintaining acceptable EMC characteristics much more difficult that distinguishes competitors in the IC manufacturing industry. The susceptibility to EM disturbances has resulted in growing safety and robustness to EMC specifications concerns, necessitating the development of techniques to reduce undesirable EM susceptibility to EMI. This explains why there are a number of international EMC/EMI guidelines and standards (such as IEC, IEEE, and CISPR) that specify essential requirements not only for military, medical, and automotive applications, but also for commercial products.

Every IC package (including pins) possesses conducted immunity levels, and its failure is susceptible to exposure to either electric or magnetic field. Depending on the IC's internal architecture and pin couplings, EM disturbance can affect the IC's performance to the point where it exceeds the immunity levels to electric and magnetic field (e.g., all ICs are sensitive to both fields with varying frequency responses). Furthermore, as the clock frequency of digital sequential circuit blocks embedded in modern micro-controller IC chips increases, EMI shifts to the thousands of megahertz or gigahertz range, which requires an extension of currently available immunity characterization methods to this frequency band. As a result, determining those EMC values allows engineers to analyze the IC while also knowing its conducted immunity/emission levels.

In addition, when an electronic product is designed for mass production, the functional behavior of each function is tested and validated under environmental conditions to ensure that the product will not malfunction when subjected to particular types of stress. Typically, thermal conditions, aging, humidity, and vibration are considered when evaluating such objectives. In the EMC domain, PCBs are typically designed for nominal and ambient conditions; however, the issue arises as to how the EMC performance will evolve as a result of these parameters. This demands not only evaluating the drifts of EMC levels of an electronic circuit throughout its lifespan in a given environment, but also determining sufficient margins to ensure compliance with EMC limits throughout the product's lifetime. Those accelerated aging tests make it possible to evaluate only the EMC degradation variations after aging under specified stress conditions, whereas the long-term EMC prediction under such conditions cannot be estimated without developing an accurate reliability model. The latter permits the prediction of EMC conducted immunity performance throughout the product's lifecycle, which is of great assistance to IC manufacturers in evaluating the trade-off between device performance and fabrication cost prior to manufacturing ICs.

Exposure to various environmental stress conditions can have a severe impact on the conducted immunity profile of an IC level, leading to operational failures with different failure modes (i.e., soft and hard) associated with different failure mechanisms. Those failures occur due to the coupling of EM disturbance signal on the IC pin, causing temporary and/or permanent malfunction due to exceeding the acceptable EMC limit. Aging can have a considerable impact on the degradation of the EMC performance of the analog and digital circuit components in an IC chip. As a result, the appropriate operation of the electrical performance of those ICs is also compromised, reducing the intended lifetime, reliability, and durability of an electronic component or electronic system. Maintaining the desirable long-term EMC robustness of the analog and digital circuit components embedded in an IC chip is therefore essential for ensuring the durability of an electronic component over its lifetime. In order to minimize re-design and production costs, it is necessary, during the design phase of an IC, to ensure its optimum reliability and durability while adhering to the industry standards for long-term EMC qualification. Therefore, it is essential to ensure that the ICs operating in an electronic system generate as few EM disturbances as feasible and exhibit less susceptibility to the EMI caused by other disturbance sources over the course of their entire service life.

The predicted operational lifetime of analog and digital ICs designed and developed by manufacturers for various purposes (e.g., medical, aviation, automotive, and so on) may be several months or years. Accurate assessment of the lifetime reliability of ICs can be difficult, and it is critical to consider how its functionality varies due to changing external

factors such as environmental operating conditions (i.e., thermal, humidity, pressure, vibration, mechanical shock, electrical voltage overstress) over the course of its operational life. Throughout the life cycle of an IC in an EM environment, it is essential to characterize its long-term evolution of the EMC robustness by analyzing the variations of the conducted immunity level in both the transient and frequency domains due to exposure in harsh environmental stress (temperature and/or humidity variations), which may also be incorporated to estimate its lifetime reliability.

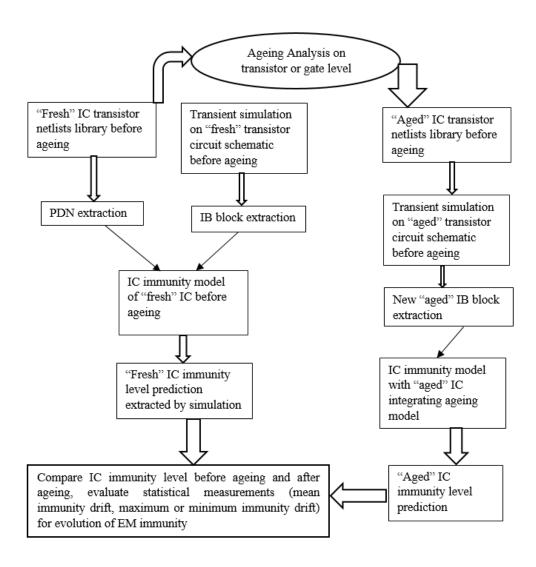

This thesis work aims to investigate and evaluate the impact of accelerated ageing on the long-term evolution of the EM robustness of both analog and digital circuits at the IC level. Consequently, the primary goal of the research work is to develop predictive degradation and lifetime reliability models to estimate unknown degradation model and lifetime reliability metrics (i.e., Instantaneous Failure Rate, Acceleration Factor, Mean Time-to-Failure, Probability of Failure) of the tested ICs in nominal as well as other tested or untested accelerated environmental stress conditions, while considering that the IC is robust and maintains the EMC compliance level within the whole lifetime of the equipment in an electronic system which they belong to. Eventually, those developed models should be validated and to become the part of the EMC performance evolution data that should be supplied by the IC manufacturers, in order to facilitate the design of functional and durable electronic products.

#### Objectives of the Thesis

The manuscript aims to propose and develop degradation and reliability models for the industry representative manufactured analog and digital IC samples by assessing the long-term evolution of the EMC conducted immunity performance under the influence environmental constraints. Those developed models enabled to predict the unknown degradation and lifetime reliability parameters, depending on characterizing the conducted immunity measurements performed in accordance to the designed Accelerated Degradation Test (ADT) plan. In addition, those developed models would enable to predict the reliability parameters in nominal as well as tested or untested different environmental stress conditions, while estimating the conducted immunity performance by developing the Integrated Circuit Immunity Modeling-Conducted Immunity (ICIM-CI) models of the tested Device Under Test (DUT) samples. The objectives of the research work presented in this report can be summarized as follows:

- 1. Conduct a comprehensive state-of-the-art review on developing the ICIM-CI models of various analog circuits, and compare the simulation model results with the conducted immunity performance measurement results obtained by performing various EMC tests (i.e., EFT and DPI).

- 2. Investigate and analyze the evolution of the EM robustness of analog ICs under the influence of multiple ageing stress conditions (i.e., thermal and electric overstress voltage).

- 3. Develop and couple accelerated degradation test model to predict the lifetime reliability parameters based on the functional performance of the designed low voltage dropout analog circuit with adjustable output in 180 nm CMOS technology.

- 4. Conduct a comparative study to evaluate the conducted immunity of functionally identical analog ICs by integrating different obsolescence and the impact of different thermal stress conditions.

- 5. Investigate the influence of applying thermal step-stress ADTs combined with constant electrical overstress conditions on the developed ICIM-CI models of the studied analog ICs.

- 6. Develop degradation and accelerated life test reliability models to predict the desired parameters based on the variation of the long-term EM robustness of both analog and digital circuits, depending on the defined multiple external stress conditions applied while performing different types of ADTs.

#### Thesis Organization

According to the general concepts on the need to conduct the research study on the reliability modeling of ICs based on the Electromagnetic Robustness (EMR) under the influence of external environmental stress conditions, the thesis report is organized in five chapters, excluding the present and the main conclusion and perspective chapter of the thesis report.

Chapter 1 provides an overview of the existing literature available on how to propose and develop different kinds of EMC simulation models (i.e. ICIM-CI, ICIM-CPI, ICIM-CE, ICEM-CE and so on) to compare with that of the measured conducted immunity and emission of various analog and digital circuits, in accordance to the current international electrotechnical commission (IEC) standards (i.e., IEC 62433-4 and IEC 62433-2).

Furthermore, the effect of continuous aging on the evolution of the EMC performance of various analog and digital circuits (e.g. operational amplifier and oscillator) is explored. Furthermore, the DPI and EFT experimental techniques required for performing and characterizing the conducted immunity of ICs in the time and frequency domains are discussed, followed by providing an overview of the basic terminologies, concepts, and general principles focusing on the IC-EMC reliability study.

Chapter 2 presents a case study of an analog Complementary Metal-Oxide-Semiconductor (CMOS) voltage regulator circuit designed in 180 nm analog-mixed signal (AMS) bulk technology with the goal of proposing and developing the degradation model based on the functional performance degradation data of the developed electrical simulation model, subjected to multiple accelerated temperature and electrical overstress conditions. Furthermore, an Accelerated Life Test (ALT) was proposed and developed with the help of the Maximum Likelihood Estimation (MLE) method for predicting model constant parameters and required reliability characteristics under the effect of applied accelerated stress conditions.

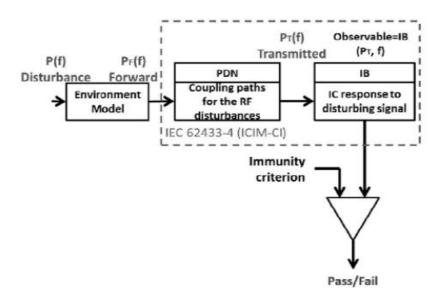

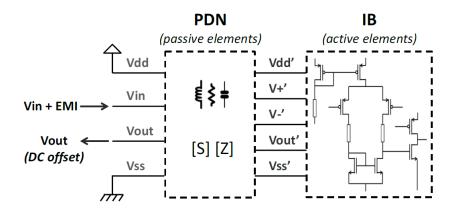

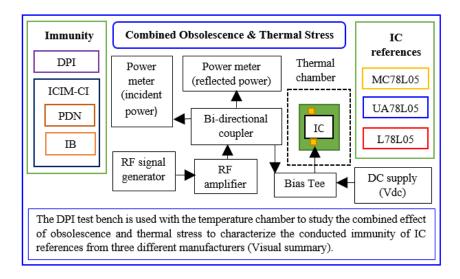

Chapter 3 investigates the conducted immunity of identical pin-compatible analog ICs developed by different manufacturers under the influence of the specified different temperature stress conditions, while integrating the obsolescence or the second-source in life-long systems. Moreover, the impact of applying extreme high and low thermal environmental stress on the developed Passive Distribution Network (PDN) and Immunity behavioral (IB) blocks of the developed ICIM-CI models of the studied analog ICs is also compared and analyzed.

Chapter 4 highlights the influence of ageing on the currently available ICIM-CI models to predict the EMC performance at the IC level. The influence of performing ADT on the observed conducted immunity drifts of different analog tested ICs with similar functionality is explored and analyzed. The ICIM-CI models, with and without considering the accelerated ageing impact, are developed and compared by analyzing the effect on both the developed PDN and IB models of the fresh and aged IC samples. This study emphasize on the importance of including versions of those available EMC model standards.

Chapter 5 investigates the effect of applying multiple accelerated stress factors (i.e. thermal and electrical voltage), while performing the thermal step-stress ADTs on the evolutions of the long-term EMR of the tested analog ICs and constant stress ADTs on the digital circuit embedded within the Attiny85 micro-controller IC chip samples, followed by developing and constructing the suitable EMC performance degradation models and

the ALT reliability models to predict the necessary model parameters.

#### **Publications**

The conducted research study presented in this thesis has resulted in the following peer-reviewed journal articles and conference proceedings. Figures and Tables illustrate the results of those publications, which have been referenced and cited within the chapters to demonstrate the originality of the author's own work. The list of peer-reviewed journal articles and conference proceedings are mentioned as follows:

- Jaber Al Rashid, Mohsen Koohsestani, Laurent Saintis, and Mihaela Barreau. Lifetime reliability modeling of digital ICs influenced by the environmental and aging constraints: A case study. IEEE Transactions on Device and Materials Reliability, 2023, (under review).

- 2. **Jaber Al Rashid**, Mohsen Koohsestani, Laurent Saintis, and Mihaela Barreau. Degradation and reliability modeling of EM robustness of voltage regulators based on ADT: An approach and a case study. *IEEE Transactions on Device and Materials Reliability*, 2023 (major revision).

- 3. **Jaber Al Rashid**, Mohsen Koohsestani, Richard Perdriau, Laurent Saintis, and Mihaela Barreau. Combining obsolescence and temperature stress to evaluate the immunity of voltage regulators to direct power injection in long lifespan systems. *IEEE Letters on EM Compatibility Practice and Applications*, 5(1): 27-32, 2023, doi: 10.1109/LEMCPA.2023.3240621.

- 4. Jaber Al Rashid, Mohsen Koohsestani, Laurent Saintis, and Mihaela Barreau. High temperature accelerated ageing influence on the conducted immunity modelling of the commonly used voltage regulator ICs. In 2023 International Symposium on EM Compatibility (EMC Europe), pages 1–6, Krakow, Poland, 2023. IEEE Xplore (paper id 119).

- Jaber Al Rashid, Laurent Saintis, Mohsen Koohsestani, and Mihaela Barreau. Coupling simulation and accelerated degradation model for reliability estimation: Application to a voltage regulator. *Microelectronics Reliability*, 138:114682, 2022, doi: 10.1016/j.microrel.2022.114682.

- 6. **Jaber Al Rashid**, Mohsen Koohsestani, Laurent Saintis, and Mihaela Barreau. A state-of-the-art review on IC-EMC reliability. *In Proceedings of the 31st European*

$Safety\ and\ Reliability\ Conference, pages\ 1850-1857, Angers, France,\ 2021.\ Research\ Publishing\ Services,\ doi:\ 10.3850/978-981-18-2016-8-154-cd.$

# A STATE-OF-THE-ART ON IC-EMC RELIABILITY: METHODOLOGY, MODELING AND AGING IMPACT ON THE EMC OF ICS

EMC is the ability of an IC to function satisfactorily in its EM environment without introducing intolerable EM disturbance to anything operating in that environment. In order to guarantee the functional safety of electronic applications and the simultaneous operation of all nearby electronic devices or other ICs in a given EM environment, the EMC performance operating in an EM system should be within the desired level. Different EMC standards (such as, IEC 61963 and IEC 62132) for ICs are now available for a variety of applications, including automotive, avionics transport, medical, and telecommunications.

Although the size and dimension issue of an IC is usually considered, the EMC issues are not considered by IC designers during the design stage because it was only addressed at the system and PCB levels. ICs are the sources of noise emission and sensitivity, so they are the source of several EMC constraints and issues related to the conducted immunity or susceptibility to external EM disturbance signals. Due to the ongoing development of CMOS technology trends related to an increase in clock speed, an increase in IC design complexity, and a decrease in the size of the transistors within ICs operating in nanoscale electronic circuits or devices, ICs are becoming more sensitive to noise [1]. Furthermore, the integration of Deep Sub-Micron (DSM) circuits in EM environments under harsh external environmental conditions implies evolution of functional electrical characteristics and/or performances of the ICs as well as continuation of the internal physical degradation or failure mechanisms, which affects the functional safety of the EM devices [2]. Considering the EMC issues of ICs and their evolution in critical environments, the

study of IC-EMC, along with the lifetime reliability of ICs, is essential to characterize the long-term evolution of the EM robustness at different external operating conditions (e.g., temperature, humidity, electrical voltage and vibration) [3].

In this first chapter, the objective is to conduct a comprehensive review of literature works and their research findings on developing accurate immunity and emission models of ICs, with a particular emphasis on quantitative evaluation of experimental characterization based on various IC-EMC measurement methods under various ALTs. The subsequent sections of this chapter presents a few recent researches on the methodology to develop, extract and validate various types of the EMC models, such as ICIM-CI, Integrated Circuit Immunity Modeling- Conducted Pulse Immunity (ICIM-CPI) and Integrated Circuit Emission Modeling-Conducted Emission (ICEM-CE) based on the IEC modeling standards, proposed for predicting and analyzing the EMC performance of various types of analog and digital circuits designed within a test chip. Those developed models were simulated and compared with the DPI conducted immunity measurements performed on different pins of the tested IC samples. In addition, literature studies on investigating the evolution of the EMR of ICs have been discussed; these existing research studies provide an overview of how applying various types of stress factors (i.e., thermal and electrical overstress) with specified magnitude and stress duration could influence the conducted EMC performance of ICs. In addition, an overview of the general principle on reliability study of electronic components at the IC level is presented to highlight the need to incorporate and integrate the environmental impact on the EMC performance for developing the degradation and reliability model. Those modes would allow to predict various reliability matrices taking into account of the conducted immunity EMC performance evolution of the tested ICs subjected to the aging caused by extreme stress conditions.

# 1.1 EMC of ICs: Conducted Immunity Measurement and Analysis

The conducted immunity level of ICs should be within the desirable range for maintaining the functional safety and reliability of electronic systems in various complex applications such as automotive and aeronautic. Throughout the operational lifetime of ICs, harsh environmental conditions, such as, extreme high or low temperature, humidity, shock, and stress tend to cause intrinsic physical degradation, resulting in significant variations in the lifelong EMC performance of IC device [4], [5]. Therefore, predicting the

lifetime reliability under the external environmental stress conditions and maintaining their long-term EMR, while operating within a system in any application is a critical issue that needs to be addressed.

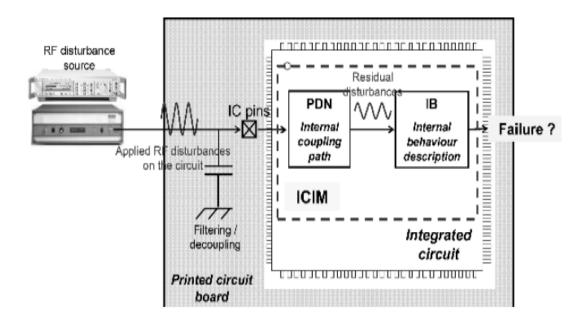

According to ISO 11451, "EMC" is "the ability of a device, equipment or system to function satisfactorily in its EM environment, without introducing EM disturbances that could interfere with the proper operation of the devices or systems located in its environment" [6]. Since EMC difficulties emerge in an EM environment (EM) from three elements, the source or aggressor, the victim, and the coupling mechanism [7]. The term "source" refers to the source of the EM energy that creates the disturbances, whether natural (i.e., lightning or man-made (for example, electrostatic discharge). The term "victim" refers to an IC or electronic equipment that receives the EM disturbance from the aggressor and has its electrical properties impaired as a result of EM interference operating on the electronic component. The term "coupling path" refers to the manner of coupling (cable, parasitic inductance, power rails, ground, parasitic capacitance, traces on a printed circuit board (PCB), and antenna) that causes harmonic disturbances to be transmitted from the source to the victim.

Characterizing and determining complex EM immunity and emission issues of ICs under complex EM environment is essential for accurate evaluation of EMC and reliability of ICs. The IC-EMC lifetime reliability metric refers to the function that can be expressed in terms of parameters to indicate or predict how long the system would be performing before exhibiting various EMC failures under different external operational conditions [8]. Adopting realistic and accurate model construction with precise model validation to predict EM immunity and emission performance of ICs have attained significant importance to IC designers and manufacturers. Evaluation of predictive EMC simulation results would be necessary to IC chip designers and manufacturers for reduction of time, number of prototype cycles and fabrication cost prior to manufacturing various kinds of ICs [8].

Simulating immunity and emission models can help IC designers to understand and anticipate EMC levels to conducted harmonic disturbance when applied to IC pins, which in turn enable IC manufacturers to provide conclusive statement on whether IC would be EMC compliant prior to manufacturing. Moreover, EMC model construction and obtaining EMC results by simulations in various CAD software are considered very useful and easy to analyze compared to that of performing various EMC performance characterization tests in accordance to the existing IEC standards (IEC 62132-4, IEC 61967-4). Developing and constructing the conducted immunity and emission models to predict the

EMC performance of ICs at the device or component level would enable the determination of different induced failure mechanisms and their origin caused by injecting conducted EFT pulses into different IC pins as well as by coupling high frequency RF signals to induce noise by causing EMI onto different analog and digital input and/or output as well as power supply pins of the IC chip.

#### 1.1.1 Transient EM conducted immunity measurement of ICs

Several studies have been conducted to characterize the immunity profile of various analog and circuits embedded in an IC chip based on the IEC standard tests (i.e., EFT, DPI).

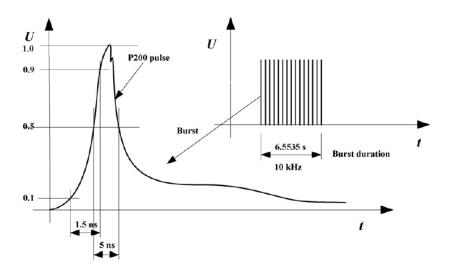

In accordance with the IEC 61000-4-4 standard [9]-[10], the EFT/Burst testing method is commonly used to evaluate the EM conducted immunity of ICs to the transient-conducted interference. The generator generates an EFT signal consisting of a sequence of bursts in transient mode that may be injected directly to either functional or power supply pins of ICs via magnetic or electric coupling. Hence, EMI causes temporary malfunction or even permanent damage to the integrated circuit [11]. EFT generator can generate interference pulses with high repetitive frequency (MHz), amplitude (U), short rising time  $(t_r)$ , pulse duration  $(t_d)$  and pulse width  $(t_w)$ . The characteristics of the waveform of a single Langer probe that emits EFT injection pulse that complies with the IEC standard 61000-4-4 is presented the Figure 1.1 [11], which was injected into different IC pins (i.e., I/O,  $V_{dd}$  and GND) using the voltage injection probe (P200). The injection probe was connected to the EFT generator, which could generate the EFT pulse with  $t_r$ ,  $t_d$ , EFT burst or pulse frequency and burst duration of 1.5 ns, 5 ns, 10 kHz and 6.5535 s, respectively. Moreover, the standardized waveform of the EFT pulse has an exponential shape with rapid rising and falling slope.

Table 1.1 shows the various parameters of the EFT pulse, whose magnitude can be varied within a certain range and conforms to the IEC 6100-4-4 standard [12]. With the voltage probe (P301), this EFT burst of pulses can be injected into different IC pins, triggering various forms of failure (i.e. soft and hard failure).

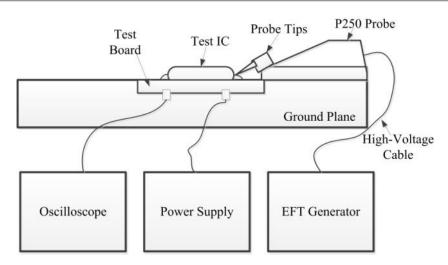

The EFT testing method is a destructive method due to injecting the EFT voltage above a certain voltage limit to different pins of the IC under test, which can affect its functionality in terms of current or voltage fluctuations. The block diagram for the EFT test setup used to evaluate the immunity of the several I/O pins, power supply (VDD) and ground (VSS) pins in the time-domain or transient mode is shown in the Figure 1.2

FIGURE 1.1 – EFT pulse waveform injected into the IC pins using the P200 probe [11].

Table 1.1 – Parameters of the burst for the EFT test [12].

| Set                                 | Output voltage peak values and repetition frequencies |                          |                      |  |  |  |

|-------------------------------------|-------------------------------------------------------|--------------------------|----------------------|--|--|--|

| voltage                             | U <sub>S</sub><br>(open circu                         | it) $U_S$ (50 $\Omega$ ) | Repetition frequency |  |  |  |

| kV                                  | kV                                                    | kV                       | kHz                  |  |  |  |

| 0.25                                | 0.25                                                  | 0.125                    | 5 or 100             |  |  |  |

| 0.5                                 | 0.5                                                   | 0.25                     | 5 or 100             |  |  |  |

| 1                                   | 1                                                     | 0.5                      | 5 or 100             |  |  |  |

| 2                                   | 2                                                     | 1                        | 5 or 100             |  |  |  |

| 4                                   | 4                                                     | 2                        | 5 or 100             |  |  |  |

| Wave shape into a 50 $\Omega$ load: |                                                       |                          |                      |  |  |  |

| rise time t <sub>r</sub>            |                                                       | (5± 1.5) ns              |                      |  |  |  |

| pulse width t                       | N                                                     | $(50 \pm 15) \text{ ns}$ |                      |  |  |  |

| peak voltage                        |                                                       | U <sub>S</sub> =         | ±2%                  |  |  |  |

|                                     |                                                       |                          |                      |  |  |  |

[13]. The EFT test bench was consisted of the EFT source integrated with the control software for generating the EFT signal with fixed parameters, the DUT mounted on the EMC test board, DC power supply, ground plane, injection probe (P250) for injecting the EFT pulse into the IC pins and the oscilloscope for the EFT source to monitor the EFT measurement results.

In [14], researchers injected the EFT pulse into the VDD, GND and several I/0 pins

FIGURE 1.2 – EFT pulse waveform injected into the IC pins using the P200 probe [13]

Table 1.2 – Classification of different failure modes observed during the EFT test [11], [14].

| States                                | Description                                                                                                         |

|---------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| No failure (A)<br>Self-recovering (B) | DUT performs as designed during and after EFT injection<br>DUT doesn't perform as designed during exposure, but can |

| Self-recovering (B)                   | return to normal operation after EFT-Burst is removed                                                               |

| Soft failure (C)                      | DUT doesn't perform as designed during exposure. DUT                                                                |

|                                       | doesn't return to normal until exposure is removed and reset pin is asserted                                        |

| Repower-recovering                    | DUT doesn't perform as designed during exposure. DUT                                                                |

| (D)                                   | doesn't return to normal until exposure is removed and power to DUT is cycled                                       |

| Damaged (E)                           | DUT can't return to normal due to physical damage or other permanent performance degradation                        |

of the DUT in order to investigate the immunity of different pins of the DUT. Different types of failure modes or error states (A, B, C, D and E) were identified due to the injection of the EFT voltage on these pins under test (PUT). The immunity criterion to the EFT disturbance was detected and evaluated by observing these different kinds of failure modes on the tested IC pins. Table 1.2 shows four failure modes identified during the EFT immunity test conducted on the IC DUT [11], [14]. These observed failure modes can be categorized into three different types of failure mechanisms (e.g. soft failure, power recycling and self-recovering failure). Soft-failure (C) could be observed when the normal operation of the micro-controller IC under test would be interrupted due to the injection

of the EFT pulse on its pins and the DUT would only resume its normal functionality due to the removal of the EFT pulse and upon the activation of reset pin. This failure mechanism would be observed due to the wrong switching of the logic gates resulting in an unexpected storage of data in the flash memory or register [11], [14].

Power recycling failure is caused by the error state D as shown in the Table 1.2 due to the latch-up of the CMOS devices within the DUT, which can be detected by observing a large spike of the current or EFT voltage injected on the PUT. This phenomenon would occur due to the switching of the internal transistors (i.e., NPN and PNP) into the onstate above a certain EFT voltage injection on the PUT, generating a significantly large current to flow through the low resistance conducting path developed between the VDD and the VSS pin of the DUT [13]. Self recovering failure mode or error state B would occur when the microcontroller is disturbed due to different failure mechanisms, such as, power-on reset (POR), watchdog reset (WDOG), external pin reset (PIN), loss of clock (LOC), and low-voltage detect (LVD). If the VDD voltage would be lower than the reset voltage of the DUT, then the POR is triggered. LVD would be activated for protecting the data stored in the register of the microcontroller DUT, when the VDD is reduced below the lowest permitted detected voltage (LVDL). In order to prevent this failure mechanism, the DUT might be equipped with the low voltage prevention circuit, which would ensure the IC to remain in the reset state until its VDD would become greater than the VLDL after the EFT pulse is removed [11].

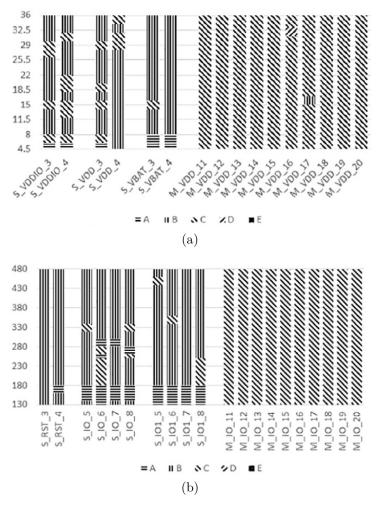

In [14], the EFT test conducted to evaluate the conducted immunity of the the VDD and I/O pins of two different micro-controllers. The IC with 8051 architecture was denoted by 'S', and the other IC was labelled as 'M' due to having the ARM architecture. Different error states (i.e. A, B, C and D) or permanent malfunction induced by the EFT pulse were considered as the immunity criterion for assessing the conducted immunity of the tested ICs to the transient disturbance. The EFT voltage injected to the power and IO pins on the two DUTs is shown in the Figure 1.3, and different error states were observed on the pins under tests (PUTs), depending on the magnitude of the injected EFT voltage prior to causing the tested ICs to malfunction permanently. Due to the injection of the positive polarity EFT voltage on the power pins of the DUTs, the Figure 1.3a showed that the immunity of the IC chip (i.e., 'M') was less compared to the other IC as the error state C was observed due to injection of higher EFT voltage on its VDD pins. However, the 'S' chip showed error state A upto low EFT voltage, followed by observing the mode B failure due to injecting high EFT voltage on its VDD pins. Similarly, the Figure 1.3b

illustrates that the IO pins of the 'S' chip was more immune to the EFT disturbances compared to the other tested IC. The IO pins of the 'S' could withstand higher EFT voltage injection than that of the 'M'. Besides, the 'M' chip showed higher degree of failure modes (i.e., state C), while the 'S' chip could only demonstrated failure mode B [14]. While comparing the EFT results depicted in the Figures 1.3a and 1.3b, it was found that the IO pins required higher EFT voltage (indicated in the y-axis) injection than those VDD pins for observing different failure modes, and causing permanent degradation of the IC functionality induced by the EFT disturbance.

FIGURE 1.3 – EFT voltage injection on DUTs with different error states observed (a) VDD; (b) IO pins [14].

# 1.1.2 Conducted immunity measurement of ICs in frequency domain

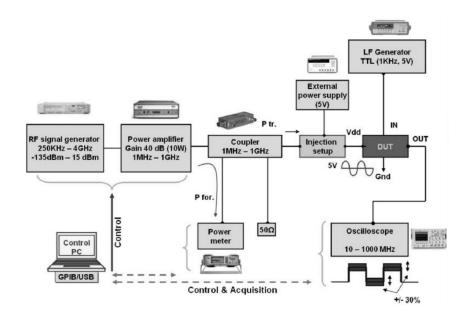

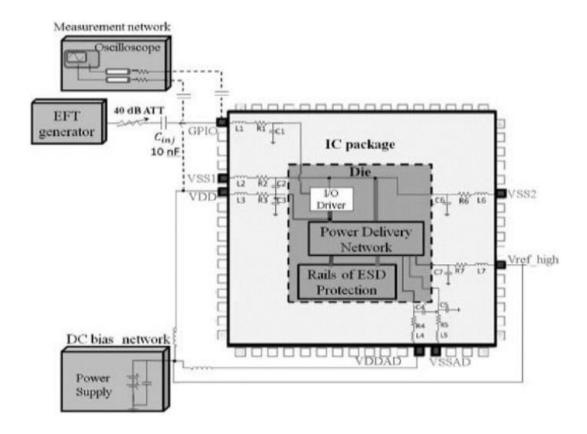

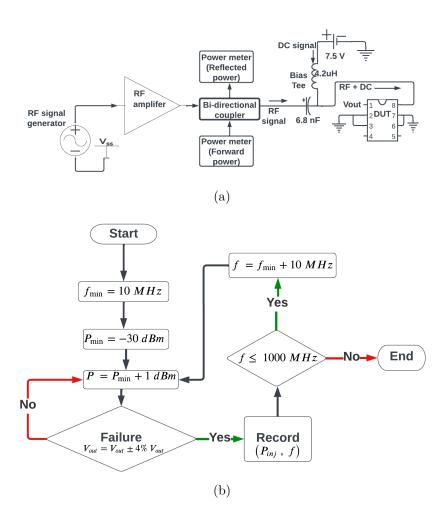

The DPI conducted immunity testing method is regarded as one of the most effective techniques for characterizing the conducted immunity of ICs in the presence of radio frequency (RF) continuous-wave single-tone EM disturbances. The RF signal at a specific frequency (f) with conducted forward power is injected into various IC pins via the cable harness or PCB traces to ensure an efficient coupling mechanism during the conduction mode propagation of the RF signal power [15]. The DPI immunity test can be conducted in accordance to the IEC 62132-4 standard [16]. The DPI test-bench setup consists of the different electrical components to characterize the effect of inducing the conducted EM disturbance on the functionality of an IC sample under test. In general, the DPI test bench is composed of radio-frequency (RF) signal generator, RF power amplifier, bi-directional coupler, decoupling network, power meters, oscilloscope and a control computer to monitor the relevant output data [2].

FIGURE 1.4 – DPI test setup for characterizing the conducted immunity of an IC under test [17].

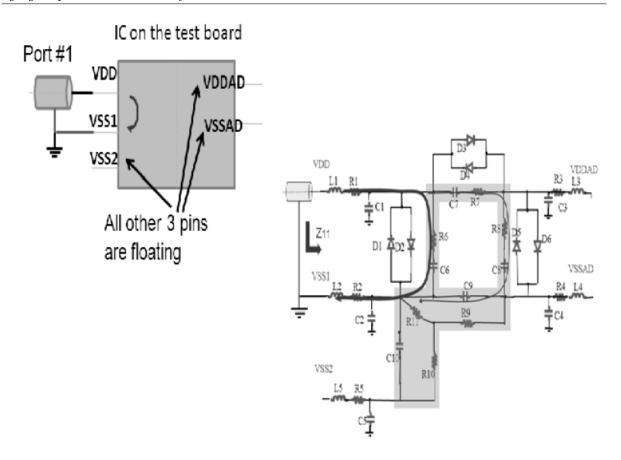

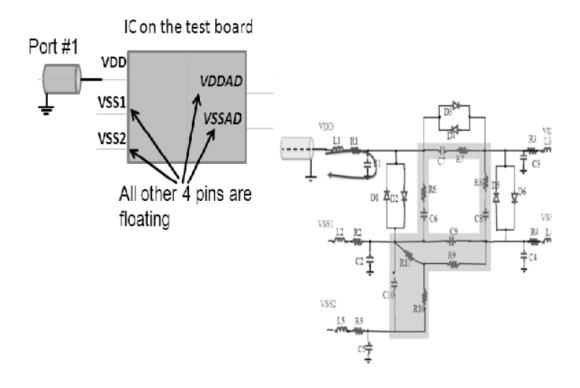

In [17], the DPI test setup used for characterizing the conducted immunity of an inverter circuit between the DPI frequency range between 1 MHz and 1 GHz is shown in Figure 1.4. The injection setup refers to the decoupling network, which consist of a 47 pF

coupling capacitor or the bias tee connected in series. The RF signal generator is used as an interference source to send continuous-wave harmonic disturbance signal at a specific signal power, which is then amplified by the RF amplifier. The use of the wideband bias tee is crucial for allowing the continuous sinusoidal RF signal generated by the RF signal generator to superimpose on the DC signal of the power supply pin of the DUT, whereas one end of the inductor is connected to the external power supply and the other end to the coupling capacitor. The RF power amplifier is used to amplify the power of the RF signal, which is then injected to the PUT of the IC through the injection capacitor that blocks the DC signal provided by an external power supply, after flowing through the bidirectional coupler. A bi-directional coupler is connected with two different power meters for measuring the RF signal forward and reflected power, respectively. The DPI failure criterion is considered depending on the DUT specifications, sensitivity of the circuit, functionality in nominal condition and the applications where the IC usually operates.

FIGURE 1.5 – Proposed flowchart for the DPI test algorithm to characterize the conducted immunity level of an IC under test [17].

DPI test algorithm was implemented according to the IEC 62132-4 standard for evaluating the conducted immunity level of the DUT, which is shown in the Figure 1.5 [17]. The amplitude of the RF signal power was incremented linearly, while varying the DPI frequency between 50 and 1000 MHz with a linear step size of 50 MHz. If the measured RF signal power at any corresponding DPI frequency would exceed the considered failure criterion, that minimum power injected on the DUT the DPI failure should be recorded at each corresponding frequency for causing the DPI failure.

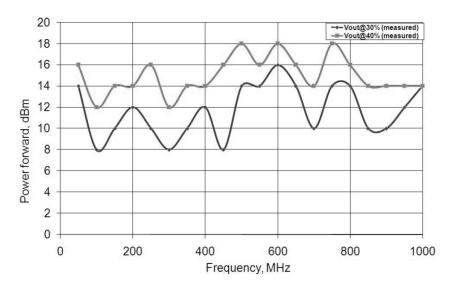

FIGURE 1.6 – DPI test result for evaluating the conducted immunity level of an IC under test at different failure criterion [17].

Different failure threshold criterion (i.e.,  $\pm 20\%$ ,  $\pm 30\%$  and  $\pm 40\%$ ) variations of the nominal output voltage level and a  $\pm 10\%$  jitter variation were considered [17]. Figure 1.6 plots two different conducted immunity waveforms of the DPI measurement data (i.e. forward power and frequency) for a CMOS inverter circuit at different failure criterion. It was found that greater amount of forward power was needed to exceed the  $\pm 40\%$  failure criterion compared to that of the  $\pm 30\%$  variations considered on the nominal output voltage. Hence, the tested CMOS inverter circuit showed higher conducted immunity profile throughout the entire DPI range due to considering higher criterion (i.e.  $\pm 40\%$  against  $\pm 30\%$ ).

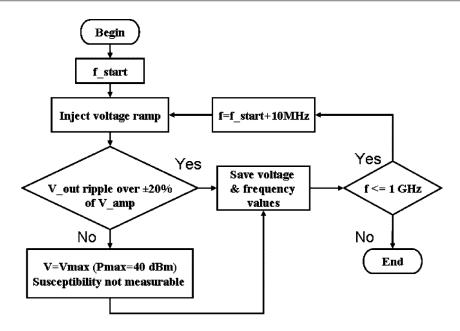

The DPI simulation algorithm was proposed in [15] based on the DPI test measurement procedure established in accordance to the IEC 62132-4 standard [16]. Figure 1.7 demonstrates the DPI flowchart based on the DPI measurement performed on the digital

FIGURE 1.7 – DPI test algorithm setup for evaluating the conducted immunity level of an IC under test [15].

core of the custom-made CESAME IC chip fabricated in 0.18 um CMOS technology. The flowchart shows that DPI frequency of the disturbance signal was considered to vary between 10 MHz and 1 GHz with a linear step size of 10 MHz. The simulation was conducted in the time-domain at each DPI frequency. Moreover, considering a fixed DPI frequency, the generated RF signal power was incremented linearly with a small step-size from a minimum value (e.g., -30 dBm) to the maximum power limit (40 dBm) until the DPI failure would be observed. The DUT was considered to fail if the considered failure criterion (i.e.,  $\pm 20\%$  variation on the voltage of the output data and a jitter more than  $\pm 10\%$  of the data output edges) was exceeded due to injecting the amplified RF disturbance signal on the power supply pin of the NORM digital core of the DUT.

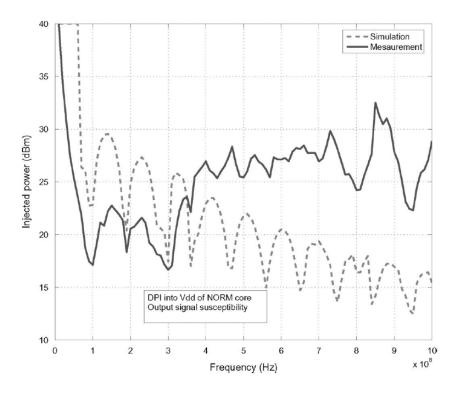

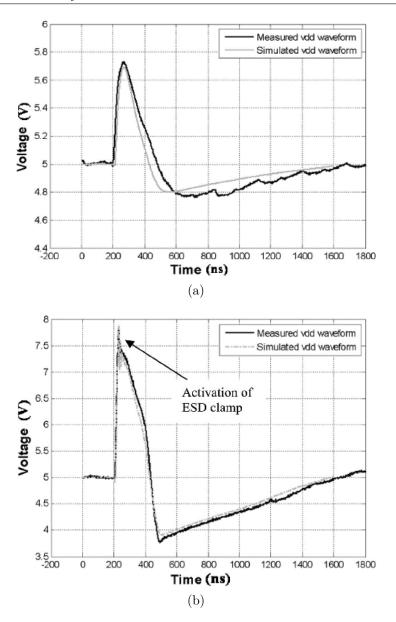

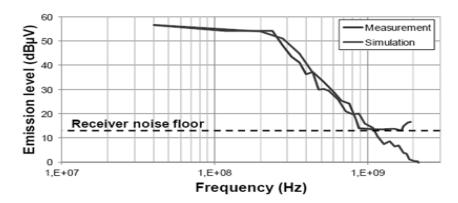

The exact injected power into the IC PUT at each corresponding DPI frequency was recorded when the failure criterion condition was achieved. Figure 1.8 plots both the measurement and simulated data of the injected power versus the DPI frequency ranging between 10 and 1000 MHz [15]. The proposed DPI simulation model could be validated as the simulation results was found to be comparable to that of the experimental measurements due to observing similar frequency matching locations at the high and low conducted immunity data points (i.e., injected power). However, a significant difference

FIGURE 1.8 – Simulation and the measurement result for evaluating the conducted immunity level the DUT [15].

of around 20 dBm injected power between the measurement and simulation curves could be observed above 360 MHz due to the ripples, without taking into account of the the power losses within the DPI system in the proposed model.

# 1.1.3 Conducted immunity and emission modeling techniques of ICs

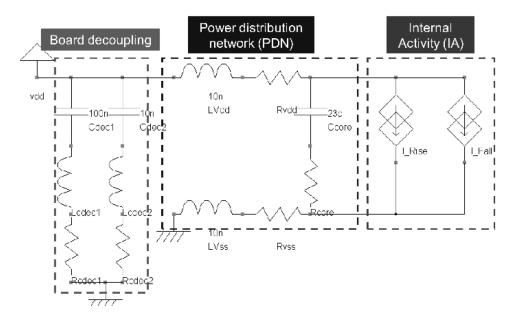

Producing accurate EMC models enables to predict the conducted immunity and emission levels ICs accurately in both time and frequency domain, as well as allows determination of various failure modes and mechanisms activated due to either injecting the EFT signal or coupling of a continuous sinusoidal disturbance signal with a singletone frequency to both analog and digital circuit structures (i.e., oscillator, regulator, micro-controller and so on) embedded within different IC model [8].