## Efficient hardware designs of the new Versatile Video Coding (VVC) tools for ASIC platforms

Brahim Farhat

#### ▶ To cite this version:

Brahim Farhat. Efficient hardware designs of the new Versatile Video Coding (VVC) tools for ASIC platforms. Signal and Image processing. INSA de Rennes, 2022. English. NNT: 2022ISAR0009 . tel-04477217

## HAL Id: tel-04477217 https://theses.hal.science/tel-04477217

Submitted on 26 Feb 2024

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## THESE DE DOCTORAT DE

L'Institut National des Sciences Appliquees Rennes

ECOLE DOCTORALE N° 601

Mathématiques et Sciences et Technologies de l'Information et de la Communication

Spécialité: Signal, Image et Vision

Par

#### « Ibrahim FARHAT »

« Efficient hardware designs of the new Versatile Video Coding (VVC) tools for ASIC platforms »

Thèse présentée et soutenue à « Rennes », le « 31 Mai 2022 »

Unité de recherche : Institut d'Electronique et des Technologies du numéRique (IETR)- UMR CNRS 6164

Thèse N°: D22 - 11 / 22ISAR 11

#### Rapporteurs avant soutenance :

Fernando PESCADOR Professeur Université Polytechnique de Madrid (UPM)

Virginie FRESSE Maitre de conférences Université Jean Monet Saint-Etienne

#### **Composition du Jury:**

Attention, en cas d'absence d'un des membres du Jury le jour de la soutenance, la composition du jury doit être revue pour s'assurer qu'elle est conforme et devra être répercutée sur la couverture de thèse

Président : Dominique GINHAC Professeur des universités, Université de Bourgogne Examinateurs : Dominique GINHAC Professeur des universités, Université de Bourgogne Professeur des universités, Université de Bourgogne

François BERRY Professeur des universités, Université Clermont Auvergne

Wassim HAMIDOUCHE Maître de conférences, INSA Rennes

Adrien GRILL Ingénieur R&D, VITEC

Dir. de thèse : Daniel MENARD Professeur des universités, INSA Rennes Co-dir. de thèse : Olivier DEFORGES Professeur des universités, INSA Rennes

#### Intitulé de la thèse :

Conceptions matérielles efficaces pour des nouveaux outils du standard VVC pour les plates-formes ASIC

\_

Efficient hardware designs of the new Versatile Video Coding (VVC) tools for ASIC platforms

#### Acknowledgements

First of all, I would like to thank my family and friends for their support at all stages of my education to whom I owe every success in my life.

I would like to express my sincere and deep gratitude to my thesis supervisor at the IETR laboratory of INSA Rennes, Dr. Wassim Hamidouche, for his continuous support, his advice, his encouragement and for being always available when I needed it. I would like to thank him for his time, his support and his ideas.

I would also like to thank my thesis director at the IETR laboratory of INSA Rennes, Professor Daniel Menard for his advice, dedication and support during these years of work. I will always be grateful to him for giving me the opportunity to work with him.

I would like to thank my supervisor, Adrien Grill, from VITEC. He was able to convey the enthusiasm of his daily work by feeding it with daily challenges. In addition to being an excellent supervisor, he is an extremely diligent engineer. I would like to thank him for his time, his support and his ideas.

A special mention to Professor Olivier Déforge, my supervisor at IETR, for his support, time, wise advises and ideas. A special mention to Jean-Marc Thesis, my supervisor at VITEC, for his contribution of time, support and ideas.

'Unless you try to do something beyond what you have already mastered you will never grow.'  $Ralph\ Waldo\ Emerson$

# **Table of contents**

| Li | st of f | igures                                                | xi |

|----|---------|-------------------------------------------------------|----|

| Li | st of t | ables                                                 | XV |

| 1  | Rési    | ımé en Français                                       | 1  |

|    | 1.1     | Préamble                                              | 1  |

|    | 1.2     | Contexte et motivation                                | 2  |

|    | 1.3     | Contributions                                         | 3  |

|    | 1.4     | Organisation                                          | 4  |

| 2  | Intr    | oduction                                              | 7  |

|    | 2.1     | Preamble                                              | 7  |

|    | 2.2     | Context and Motivation                                | 8  |

|    | 2.3     | Manuscript contributions                              | 8  |

|    | 2.4     | Manuscript organization                               | 9  |

| I  | Vid     | eo compression background and real time video codecs  | 13 |

| 3  | Vide    | eo compression background                             | 15 |

|    | 3.1     | Introduction                                          | 15 |

|    | 3.2     | Video Formats and applications                        | 15 |

|    |         | 3.2.1 Color space and chroma sub-sampling             | 15 |

|    |         | 3.2.2 Structure and configurations of a digital video | 16 |

|    |         | 3.2.3 Common Test Conditions                          | 17 |

|    |         | 3.2.4 Distortion measures and optimization            | 18 |

|    | 3.3     | Video Compression history                             | 20 |

|    | 3.4     | Versatile Video Coding (VVC)/H.266                    | 22 |

|    |         | 3.4.1 Block Partitioning                              | 23 |

|    |         | 3.4.2 Intra-Picture Prediction                        | 25 |

|    |         | 3.4.3 Inter-Picture Prediction                        | 26 |

|    |         | 3.4.4 Transform and Quantization                      | 27 |

|    |         | 3.4.5 In-loop Filters                                 | 28 |

viii Table of contents

|    |     | 3.4.6 Entropy Coding                                                          | 31 |

|----|-----|-------------------------------------------------------------------------------|----|

|    | 3.5 | Characterization of real-time video encoder                                   | 31 |

|    |     | 3.5.1 Video encoding in today's devices                                       | 31 |

|    |     | 3.5.2 Real time encoders                                                      | 32 |

|    | 3.6 | Conclusion                                                                    | 35 |

|    |     |                                                                               |    |

| II | Lic | ghtweight hardware implementation of VVC Transform for ASIC platform          | 37 |

|    |     |                                                                               |    |

| 4  |     | kground and related hardware design studies of the VVC Transform              | 39 |

|    | 4.1 | Introduction                                                                  | 39 |

|    | 4.2 | Background of the separable transform (MTS)                                   | 40 |

|    | 4.3 | Background of the separable transform (LFNST)                                 | 45 |

|    | 4.4 | State-of-the-art on hardware implementations of separable transforms          | 48 |

|    |     | 4.4.1 Hardware Implementations of Discrete Cosine Transform (DCT)-2           | 48 |

|    |     | 4.4.2 Hardware Implementation of the Multiple Transform Selection (MTS) block | 49 |

|    | 4.5 | Conclusion                                                                    | 50 |

| 5  | HW  | Design of MTS for 4K VVC Decoder                                              | 51 |

|    | 5.1 | Introduction                                                                  | 51 |

|    | 5.2 | Constant Multiplier based MTS architecture                                    | 54 |

|    |     | 5.2.1 iDCT-2 unified hardware architecture                                    | 54 |

|    |     | 5.2.2 N-point iDiscrete Sine Transform (DST)-7/iDCT-8                         | 58 |

|    | 5.3 | Regular Multiplier based MTS architecture                                     | 59 |

|    |     | 5.3.1 Read Only Memory (ROM)                                                  | 60 |

|    |     | 5.3.2 Coefficients preparation module                                         | 61 |

|    |     | 5.3.3 Multiplication module                                                   | 62 |

|    | 5.4 | Experimental and Synthesis Results                                            | 63 |

|    | 5.5 | Conclusion                                                                    | 65 |

| 6  | HW  | LFNST and MTS inverse transform design for 4K VVC Decoders                    | 67 |

|    | 6.1 | Introduction                                                                  | 67 |

|    | 6.2 | 1-D iMTS design                                                               | 69 |

|    |     | 6.2.1 Read Only Memory                                                        | 70 |

|    |     | 6.2.2 Multiplication Module                                                   | 71 |

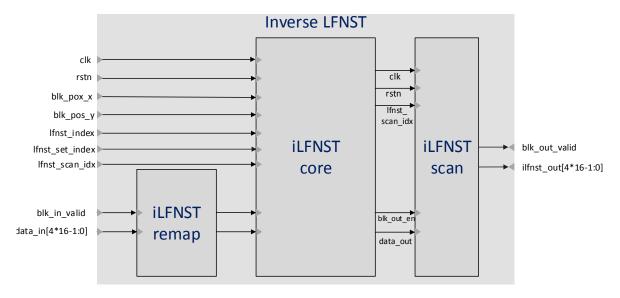

|    | 6.3 | iLow Frequency Non-Separable Transform (LFNST) design                         | 72 |

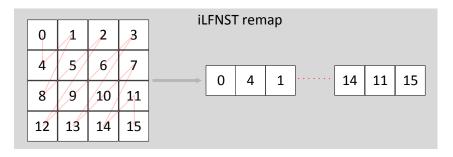

|    |     | 6.3.1 iLFNST remap module                                                     | 72 |

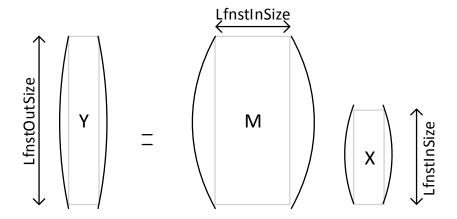

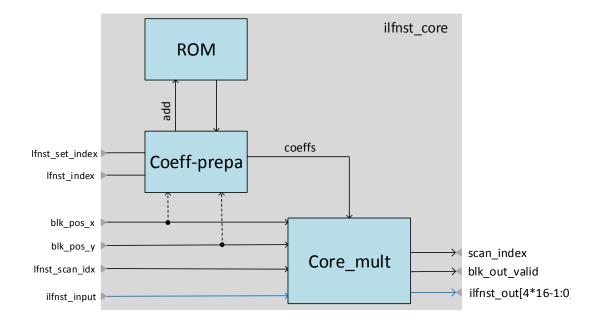

|    |     | 6.3.2 iLFNST core module                                                      | 73 |

|    |     | 6.3.3 iLFNST scan module                                                      | 77 |

|    | 6.4 | Unified inverse LFNST + MTS design                                            | 78 |

|    | 6.5 | Experimental and Synthesis Results                                            | 79 |

|    |     | 6.5.1 Experimental setup                                                      | 79 |

|    |     |                                                                               |    |

Table of contents ix

|           |                                               | 6.5.2 Coding performance                                                                                                                                                                                                                                                                                                                                                                      | 80<br>81                                                                                              |

|-----------|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

|           |                                               | 6.5.4 Inverse Versatile Video Coding (VVC) Transform compared to inverse High                                                                                                                                                                                                                                                                                                                 |                                                                                                       |

|           |                                               | Efficiency Video Coding (HEVC) Transform                                                                                                                                                                                                                                                                                                                                                      | 82                                                                                                    |

|           | 6.6                                           | Conclusion                                                                                                                                                                                                                                                                                                                                                                                    | 83                                                                                                    |

| 7         | Trai                                          | nsform HW design studies and optimizations for 4K VVC encoder                                                                                                                                                                                                                                                                                                                                 | 85                                                                                                    |

|           | 7.1                                           | Introduction                                                                                                                                                                                                                                                                                                                                                                                  | 85                                                                                                    |

|           | 7.2                                           | Shared LFNST/DCT design for 32 pixels/cycle throughput                                                                                                                                                                                                                                                                                                                                        | 88                                                                                                    |

|           |                                               | 7.2.1 Shared design for forward DCT-2 horizontal and LFNST                                                                                                                                                                                                                                                                                                                                    | 89                                                                                                    |

|           |                                               | 7.2.2 Shared design for forward DCT-2 vertical and inverse LFNST                                                                                                                                                                                                                                                                                                                              | 91                                                                                                    |

|           |                                               | 7.2.3 Discussion                                                                                                                                                                                                                                                                                                                                                                              | 92                                                                                                    |

|           | 7.3                                           | Shared DCT/iDCT design for 32 pixels/cycle throughput                                                                                                                                                                                                                                                                                                                                         | 93                                                                                                    |

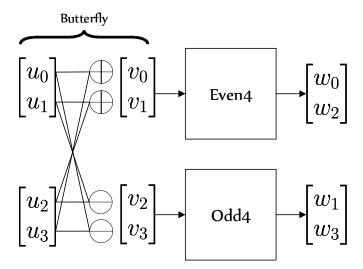

|           |                                               | 7.3.1 N-point butterfly                                                                                                                                                                                                                                                                                                                                                                       | 94                                                                                                    |

|           |                                               | 7.3.2 Core multiplication                                                                                                                                                                                                                                                                                                                                                                     | 94                                                                                                    |

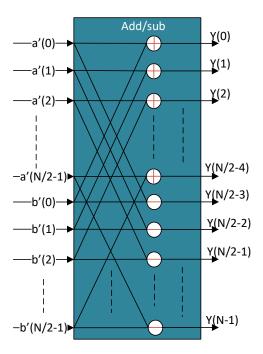

|           |                                               | 7.3.3 Add/sub                                                                                                                                                                                                                                                                                                                                                                                 | 96                                                                                                    |

|           |                                               | 7.3.4 Performance summary                                                                                                                                                                                                                                                                                                                                                                     | 97                                                                                                    |

|           | 7.4                                           | Results and comparison                                                                                                                                                                                                                                                                                                                                                                        | 98                                                                                                    |

|           | 7.5                                           | Conclusion                                                                                                                                                                                                                                                                                                                                                                                    | 99                                                                                                    |

|           |                                               | ightweight hardware implementation of VVC Adaptive Loop Filter for ASIC                                                                                                                                                                                                                                                                                                                       |                                                                                                       |

| pl        | atfor                                         | m · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                       | 101                                                                                                   |

| pl        | atfor<br>Bacl                                 | m<br>kground and state of the art of the VVC ALF                                                                                                                                                                                                                                                                                                                                              | <ul><li>101</li><li>103</li></ul>                                                                     |

| pl        | atfor<br>Back<br>8.1                          | kground and state of the art of the VVC ALF  Introduction                                                                                                                                                                                                                                                                                                                                     | <b>101 103</b> 103                                                                                    |

| pl        | atfor<br>Bacl                                 | kground and state of the art of the VVC ALF Introduction                                                                                                                                                                                                                                                                                                                                      | 101<br>103<br>103<br>104                                                                              |

| pl        | atfor<br>Back<br>8.1                          | kground and state of the art of the VVC ALF Introduction                                                                                                                                                                                                                                                                                                                                      | 101<br>103<br>103<br>104<br>106                                                                       |

| pl        | atfor<br>Back<br>8.1                          | kground and state of the art of the VVC ALF Introduction                                                                                                                                                                                                                                                                                                                                      | 101<br>103<br>103<br>104<br>106<br>110                                                                |

| pl        | atfor<br>Back<br>8.1                          | kground and state of the art of the VVC ALF Introduction                                                                                                                                                                                                                                                                                                                                      | 101<br>103<br>103<br>104<br>106<br>110<br>111                                                         |

| pl        | Back<br>8.1<br>8.2                            | kground and state of the art of the VVC ALF Introduction Adaptive Loop Filter (ALF) Filters 8.2.1 Luma filter 8.2.2 Chroma filters 8.2.3 Filtering process 8.2.4 Virtual Boundary Filtering Process                                                                                                                                                                                           | 101<br>103<br>103<br>104<br>106<br>110<br>111                                                         |

| pl        | 8.1<br>8.2                                    | kground and state of the art of the VVC ALF Introduction                                                                                                                                                                                                                                                                                                                                      | 101<br>103<br>104<br>106<br>110<br>111<br>111                                                         |

| III<br>pl | Back<br>8.1<br>8.2                            | kground and state of the art of the VVC ALF Introduction Adaptive Loop Filter (ALF) Filters 8.2.1 Luma filter 8.2.2 Chroma filters 8.2.3 Filtering process 8.2.4 Virtual Boundary Filtering Process                                                                                                                                                                                           | 101<br>103<br>103<br>104<br>106<br>110<br>111                                                         |

| pl        | 8.1<br>8.2<br>8.3<br>8.4                      | kground and state of the art of the VVC ALF Introduction Adaptive Loop Filter (ALF) Filters 8.2.1 Luma filter 8.2.2 Chroma filters 8.2.3 Filtering process 8.2.4 Virtual Boundary Filtering Process Related Work Conclusion  F HW design for 4K VVC decoder                                                                                                                                   | 101<br>103<br>104<br>106<br>110<br>111<br>111                                                         |

| pl<br>8   | 8.1<br>8.2<br>8.3<br>8.4                      | kground and state of the art of the VVC ALF Introduction                                                                                                                                                                                                                                                                                                                                      | 101<br>103<br>104<br>106<br>110<br>111<br>111<br>112<br>113                                           |

| pl<br>8   | 8.1<br>8.2<br>8.3<br>8.4                      | kground and state of the art of the VVC ALF Introduction Adaptive Loop Filter (ALF) Filters 8.2.1 Luma filter 8.2.2 Chroma filters 8.2.3 Filtering process 8.2.4 Virtual Boundary Filtering Process Related Work Conclusion  F HW design for 4K VVC decoder                                                                                                                                   | 101<br>103<br>104<br>106<br>110<br>111<br>111<br>112<br>113                                           |

| pl<br>8   | 8.1<br>8.2<br>8.3<br>8.4<br><b>ALF</b><br>9.1 | kground and state of the art of the VVC ALF Introduction Adaptive Loop Filter (ALF) Filters 8.2.1 Luma filter 8.2.2 Chroma filters 8.2.3 Filtering process 8.2.4 Virtual Boundary Filtering Process Related Work Conclusion  F HW design for 4K VVC decoder Introduction                                                                                                                      | 101<br>103<br>104<br>106<br>110<br>111<br>111<br>112<br>113<br>115<br>116                             |

| pl<br>8   | 8.3<br>8.4<br>ALF<br>9.1<br>9.2               | kground and state of the art of the VVC ALF Introduction Adaptive Loop Filter (ALF) Filters 8.2.1 Luma filter 8.2.2 Chroma filters 8.2.3 Filtering process 8.2.4 Virtual Boundary Filtering Process Related Work Conclusion  F HW design for 4K VVC decoder Introduction Top level design                                                                                                     | 101<br>103<br>104<br>106<br>110<br>111<br>111<br>112<br>113<br>115<br>116                             |

| pl<br>8   | 8.3<br>8.4<br>ALF<br>9.1<br>9.2               | kground and state of the art of the VVC ALF Introduction Adaptive Loop Filter (ALF) Filters 8.2.1 Luma filter 8.2.2 Chroma filters 8.2.3 Filtering process 8.2.4 Virtual Boundary Filtering Process Related Work Conclusion  F HW design for 4K VVC decoder Introduction Top level design Core module requirements and input scanning 9.3.1 Required surrounding samples 9.3.2 Input scanning | 101 103 104 106 110 111 111 112 113 115 116 118 119                                                   |

| pl<br>8   | 8.3<br>8.4<br>ALF<br>9.1<br>9.2               | kground and state of the art of the VVC ALF Introduction Adaptive Loop Filter (ALF) Filters 8.2.1 Luma filter 8.2.2 Chroma filters 8.2.3 Filtering process 8.2.4 Virtual Boundary Filtering Process Related Work Conclusion  F HW design for 4K VVC decoder Introduction Top level design Core module requirements and input scanning 9.3.1 Required surrounding samples                      | 101<br>103<br>104<br>106<br>110<br>111<br>111<br>112<br>113<br>115<br>116<br>118<br>118<br>119<br>123 |

Table of contents

|    | 9.5     | Luma/Chroma unified core architecture                  | 128 |

|----|---------|--------------------------------------------------------|-----|

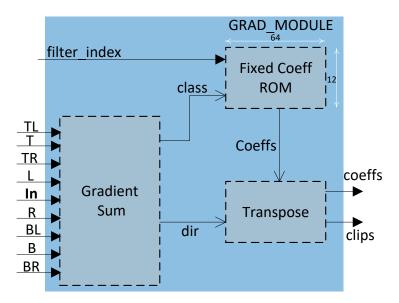

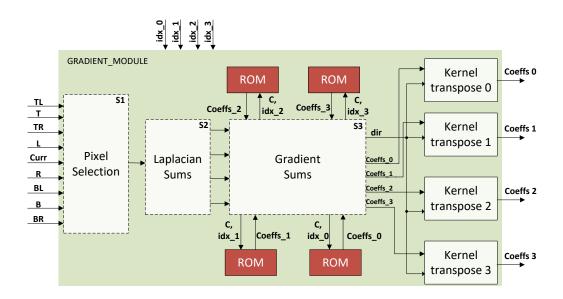

|    | ,       | 9.5.1 Gradient Module                                  |     |

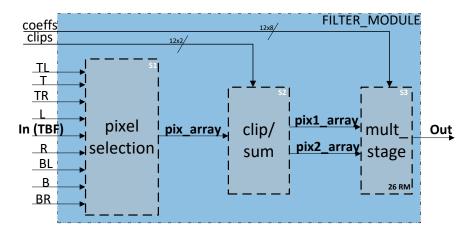

|    |         | 9.5.2 Core filters                                     |     |

|    | 9.6     | Experimental and Synthesis Results                     |     |

|    | , , ,   | 9.6.1 ALF coding gain and software complexity analysis |     |

|    |         | 9.6.2 Synthesis Results                                |     |

|    | 9.7     | Conclusion                                             |     |

|    | · · ·   |                                                        |     |

| 10 | ALF     | and ALF decision HW design for 4K VVC encoder          | 135 |

|    | 10.1    | Introduction                                           | 135 |

|    | 10.2    | ALF for Luma only design                               | 136 |

|    |         | 10.2.1 Top level design                                | 137 |

|    |         | 10.2.2 Memory dimensions and handler                   | 138 |

|    |         | 10.2.3 Gradient design                                 | 139 |

|    |         | 10.2.4 7×7 diamond shape filter design                 | 140 |

|    | 10.3    | ALF decision design                                    | 141 |

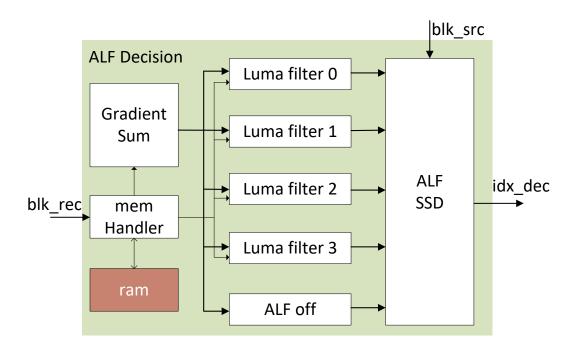

|    |         | 10.3.1 Top level design                                | 142 |

|    |         | 10.3.2 Memory dimensions and handler                   | 144 |

|    |         | 10.3.3 Gradient design                                 | 145 |

|    |         | 10.3.4 7×7 diamond shape filter design                 | 146 |

|    |         | 10.3.5 Sum of Square Differences design                | 147 |

|    | 10.4    | Experimental and Synthesis Results                     |     |

|    |         | 10.4.1 Experimental setup                              | 147 |

|    |         | 10.4.2 ALF for Luma results                            | 149 |

|    |         | 10.4.3 ALF decision results and analysis               | 150 |

|    |         | 10.4.4 ALF decoder VS ALF encoder                      |     |

|    | 10.5    | Conclusion                                             | 151 |

|    |         |                                                        |     |

| 11 |         |                                                        | 153 |

|    |         | Summary of PhD Achievements                            |     |

|    | 11.2    | Perspectives for future works                          | 155 |

|    |         |                                                        |     |

| IV | Re      | eferences and Publications                             | 157 |

| P۵ | feren   | cos                                                    | 159 |

| w  | ici eil |                                                        | 137 |

| A  |         |                                                        | 167 |

|    | A.1     | Scientific journals                                    | 167 |

|    | A.2     | International Conference                               | 167 |

# List of figures

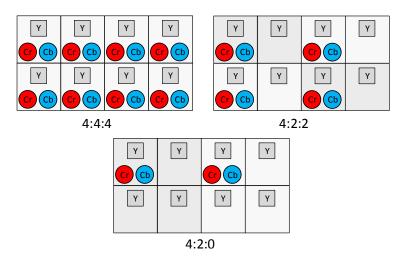

| 3.1  | Different Chroma sub-sampling for YCrCb color space                                        | 16 |

|------|--------------------------------------------------------------------------------------------|----|

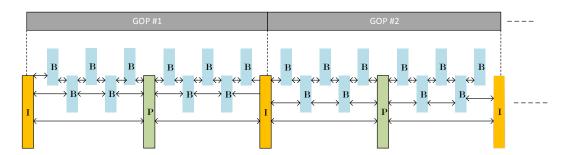

| 3.2  | Group of Picture sequencing for RA structure                                               | 17 |

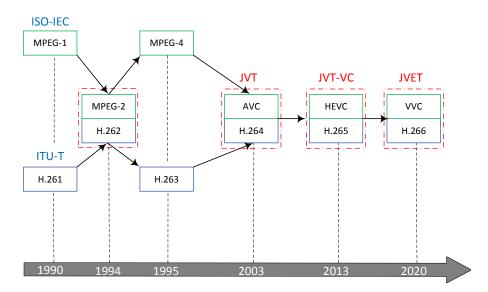

| 3.3  | Milestones of video coding standardization history                                         | 20 |

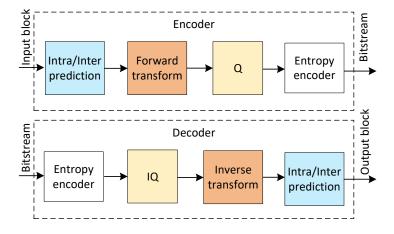

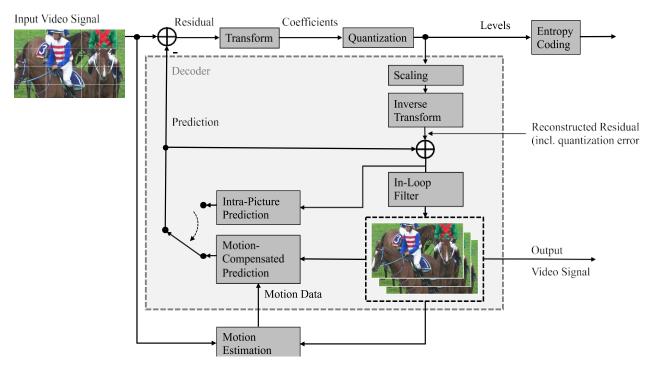

| 3.4  | Structure of the hybrid video coding schema                                                | 22 |

| 3.5  | Structure of the VVC video coding scheme                                                   | 23 |

| 3.6  | Example of a picture divided into CTUs, Slices and Tiles                                   | 24 |

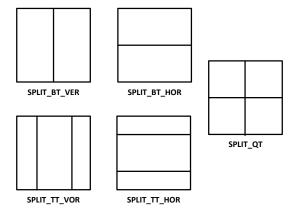

| 3.7  | Multi-type tree splitting modes                                                            | 24 |

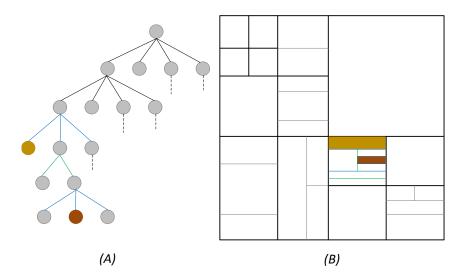

| 3.8  | Example of Quad-tree with nested multi-type tree coding block structure                    | 25 |

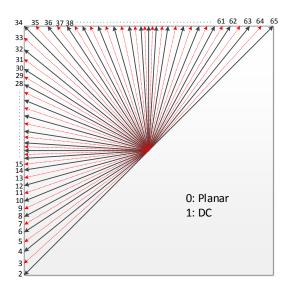

| 3.9  | Intra prediction modes                                                                     | 26 |

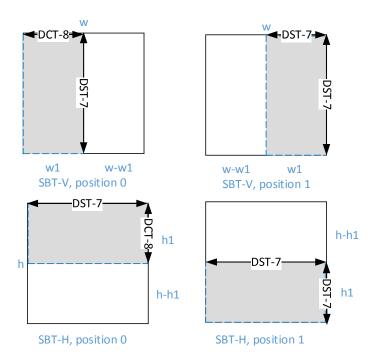

| 3.10 | SBT position and transform type                                                            | 29 |

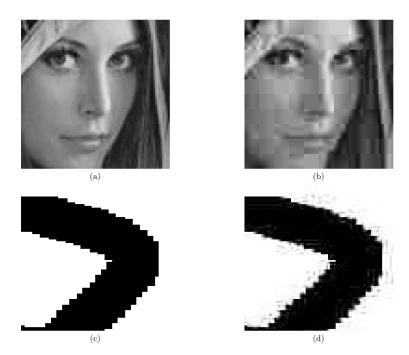

| 3.11 | Blocking and ringing artifacts in highly compressed images. (a) and (c) shows por-         |    |

|      | tions of original uncompressed images, (b) and (d) shows the same portions com-            |    |

|      | pressed. Blocking artifacts are visible in (b) and ringing artifacts are visible in (d)    |    |

|      |                                                                                            | 30 |

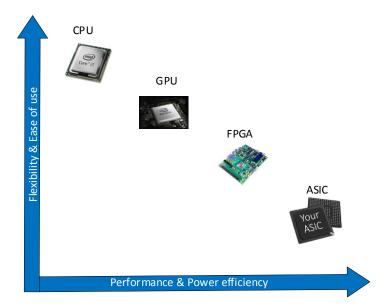

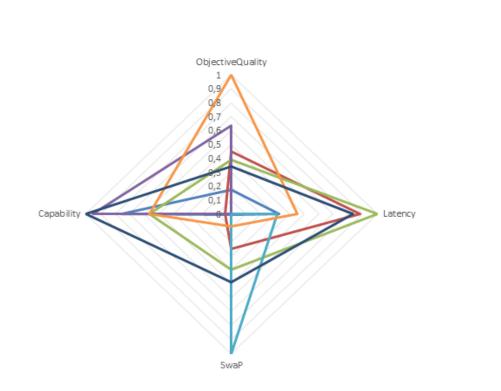

| 3.12 | Comparison of chip types & capabilities                                                    | 32 |

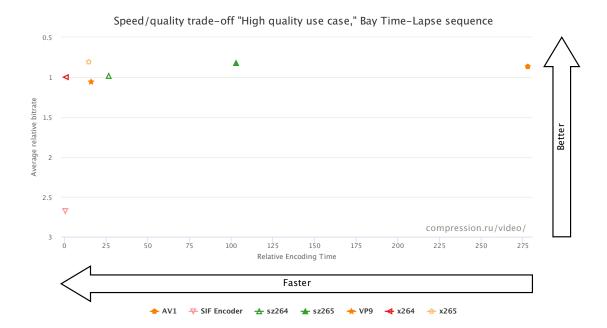

|      | Subjective Quality/Speed comparison, MSU 2018 [1]                                          | 34 |

| 3.14 | Overall evaluation for 7 point-to-point commercially encoders with objective quality,      |    |

|      | latency, Capability score, and SWaP characteristics (internal VITEC study)                 | 34 |

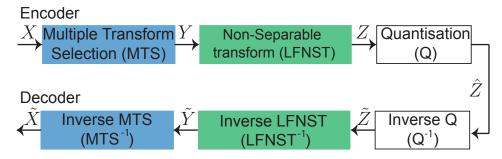

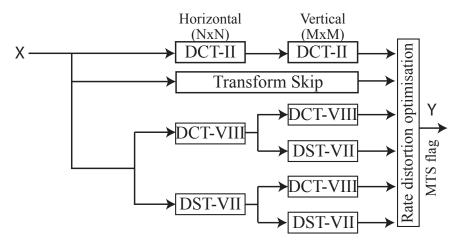

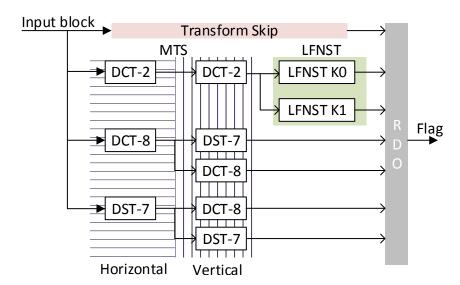

| 4.1  | VVC transform module                                                                       | 40 |

| 4.2  | Illustration of the butterfly decomposition for 4-point forward DCT-2                      | 42 |

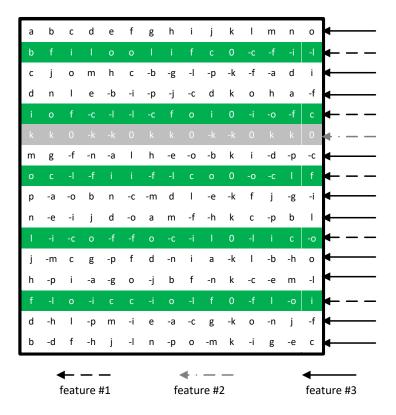

| 4.3  | Illustration of three features in the 16 $\times$ 16 DST-7 transform matrix of VVC [2]     | 43 |

| 4.4  | The concept of 2D separable transforms selection in VVC. X is the input block of           |    |

|      | residuals, Y is the output transformed block and MTS flag is the index of the selected     |    |

|      | set of transforms. The DST-7 and DCT-8 transforms are used only for Luma samples           |    |

|      | of block size lower than 64                                                                | 44 |

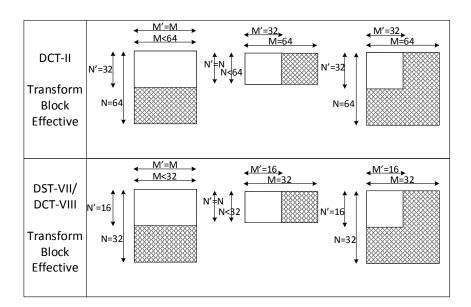

| 4.5  | Zeroing for large block sizes, $M'$ and $N'$ are the effective width and height sizes. The |    |

|      | block area set to zero is illustrated in gray color                                        | 46 |

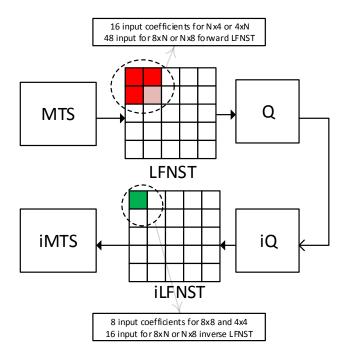

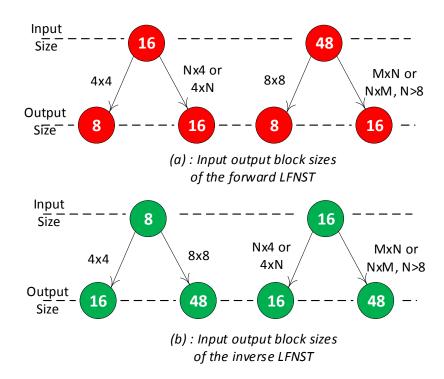

| 4.6  | Low-Frequency Non-Separable Transform (LFNST) process                                      | 47 |

| 4.7  | LFNST input/output block sizes at the encoder and decoder sides                            | 48 |

| 5.1  | 2D VVC transform in a folded architecture                                                  | 53 |

**xii** List of figures

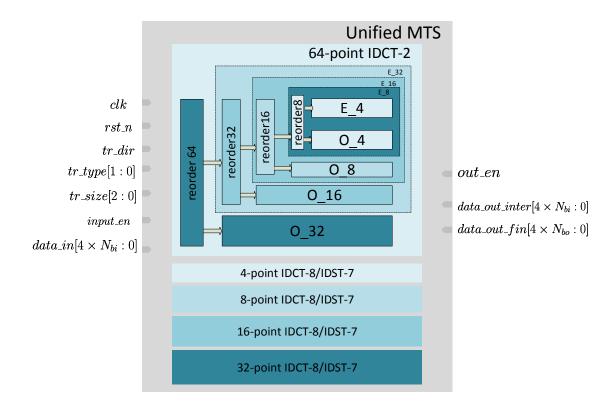

| 5.2  | Inverse Constant Multipliers (CM)-based MTS top level block diagram                               | 55 |

|------|---------------------------------------------------------------------------------------------------|----|

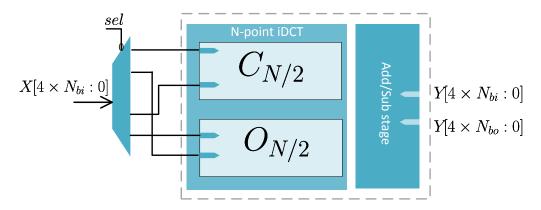

| 5.3  | N-point inverse DCT-2 top level design                                                            | 56 |

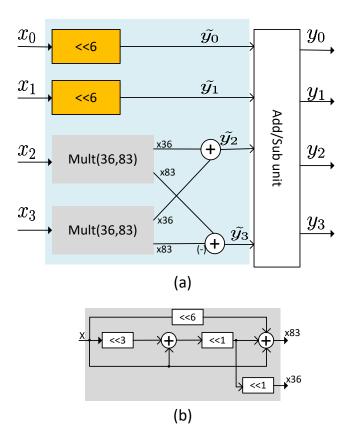

| 5.4  | 16-point iDCT2 butterfly decomposition                                                            | 57 |

| 5.5  | Proposed design for the 4-point iDCT-2 using constant multipliers(a): 4-point iDCT-               |    |

|      | 2 architecture (b): add and shift unit for the 36 and 83 operators                                | 58 |

| 5.6  | N-point Add/Sub unit                                                                              | 59 |

| 5.7  | N-point iDCT-8/iDST-7 hardware design using iDST-7 as kernel transformation, pre-                 |    |

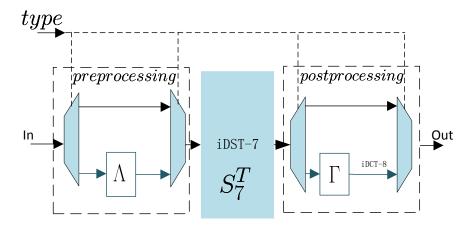

|      | processing and post-processing blocks are used when iDCT-8 type is active                         | 60 |

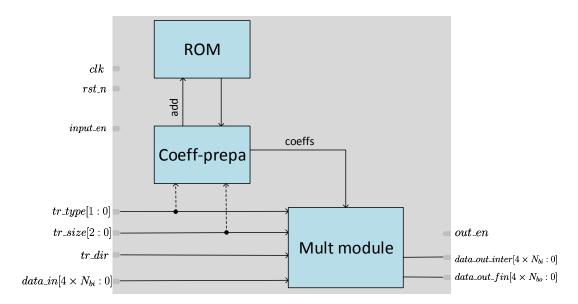

| 5.8  | Inverse Regular Multiplier (RM)-based MTS top level block diagram                                 | 61 |

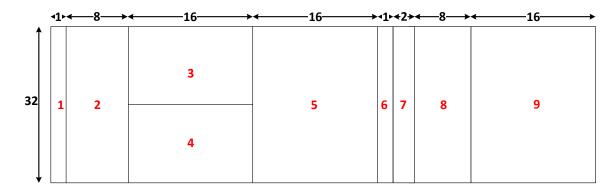

| 5.9  | Read Only Memory divided into regions                                                             | 61 |

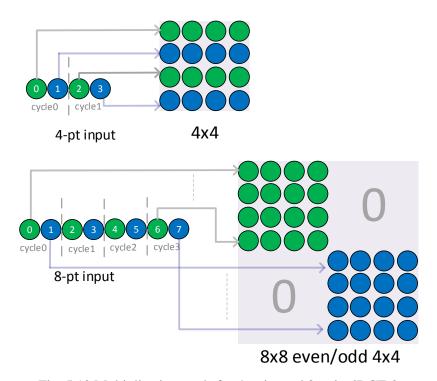

| 5.10 |                                                                                                   | 63 |

| 5.11 | RM architecture, $X_0$ and $X_1$ are the input samples, $C_i$ is the transform coefficient, $m_i$ |    |

|      | is a multiplier and $Y_i$ represents the output                                                   | 64 |

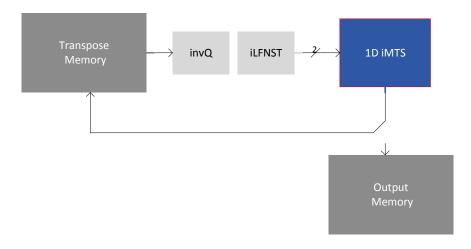

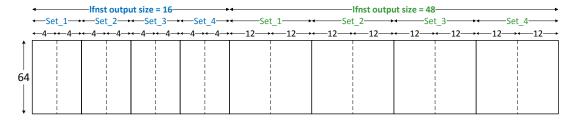

| 6.1  | 2D VVC transform in a folded architecture                                                         | 68 |

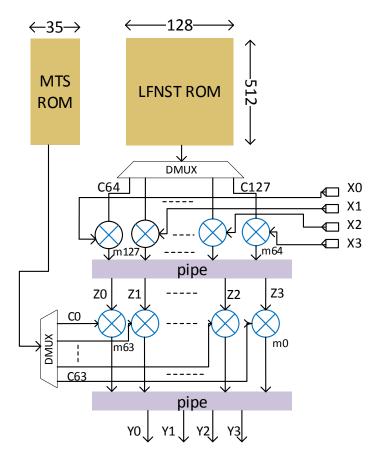

| 6.2  | Read Only Memory for 4 samples/cycle iMTS decomposed over nine regions                            | 70 |

| 6.3  | RM architecture, $X_0, X_1, X_2$ and $X_3$ are the input samples, $C_i$ is the transform coeffi-  |    |

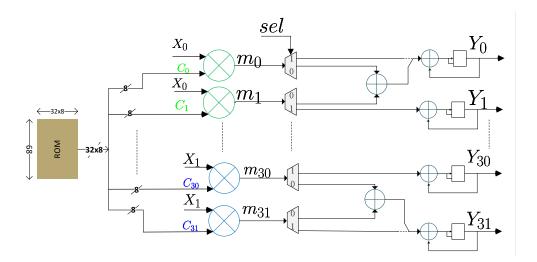

|      | cient, $m_i$ is a multiplier and $Y_i$ represents the output                                      | 71 |

| 6.4  | iLFNST top level design                                                                           | 72 |

| 6.5  | iLFNST remapping process                                                                          | 73 |

| 6.6  | LFNST matrix multiplication                                                                       | 73 |

| 6.7  | iLFNST multiplication pools. Four pools every clock cycle associated to one input                 |    |

|      | sample                                                                                            | 74 |

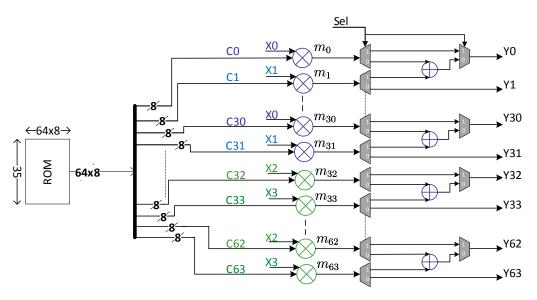

| 6.8  | iLFNST core modules                                                                               | 75 |

| 6.9  | iLFNST Read Only Memory                                                                           | 75 |

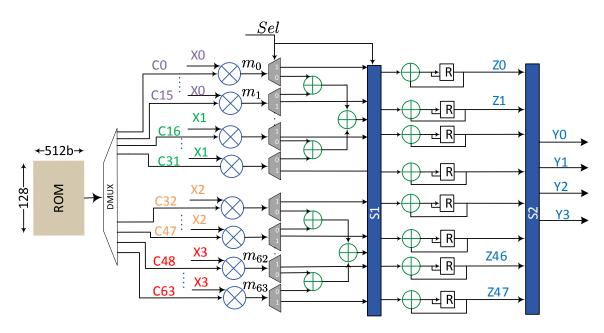

| 6.10 | LFNST core multiplication @4 samples/cycle                                                        | 77 |

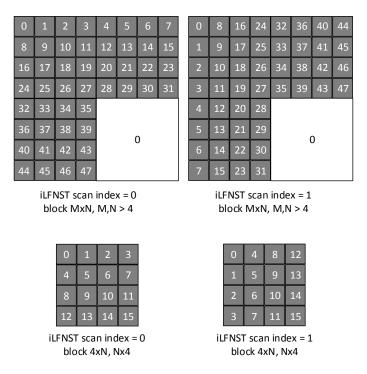

| 6.11 | Scanning iLFNST core output data depending on iLFNST scan index and input block                   |    |

|      | size                                                                                              | 77 |

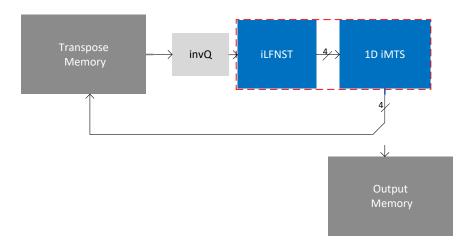

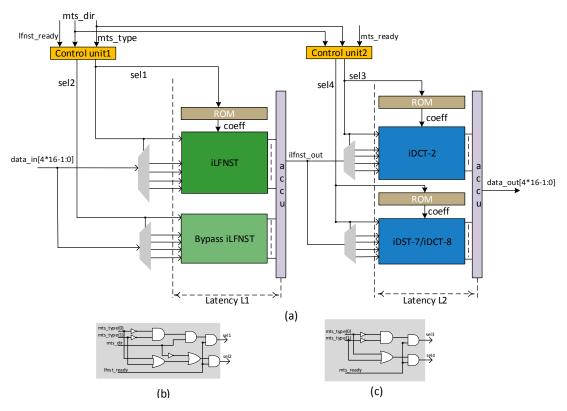

| 6.12 | Proposed hardware iMTS and iLFNST architecture, (a) Unified design for all sizes                  |    |

|      | and all transform types, (b) Control unit 1 for iLFNST, (c) Control unit 2 for iMTS               | 78 |

| 6.13 | Pipeline the VVC transform module including iMTS and iLFNST. Four samples $X_i$                   |    |

|      | are processed every clock cycle                                                                   | 79 |

| 7.1  | All combinations search for the encoder LFNST + MTS transforms                                    | 86 |

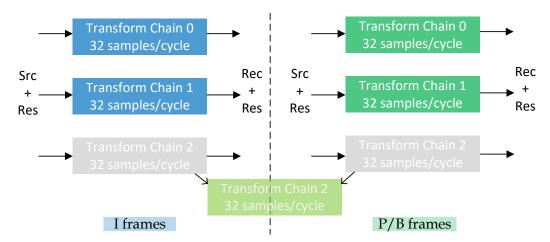

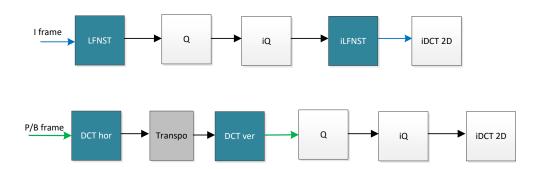

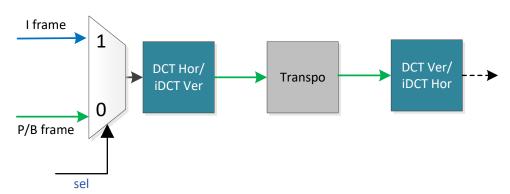

| 7.2  | Transform chains for I and P/B frames                                                             | 88 |

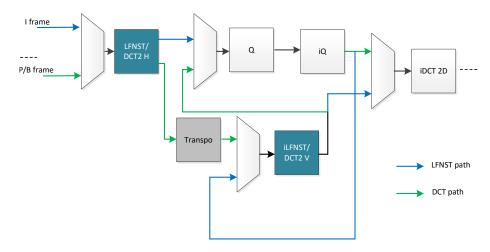

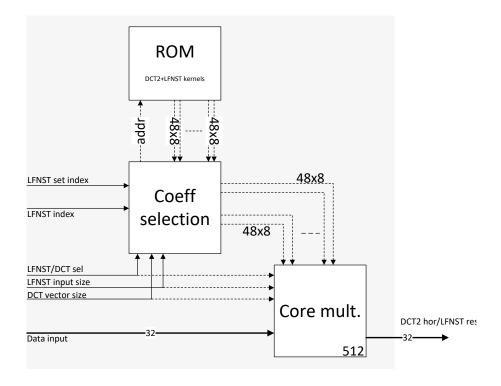

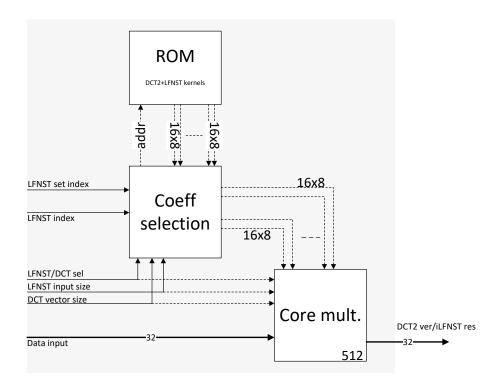

| 7.3  | Shared LFNST/DCT-2 design within the transform chain                                              | 89 |

| 7.4  | Shared LFNST/DCT-2 design functional diagram                                                      | 89 |

| 7.5  | Module block diagram for DCT-2 hor/forward LFNST                                                  | 90 |

| 7.6  | Module block diagram for DCT-2 ver/inverse LFNST                                                  | 92 |

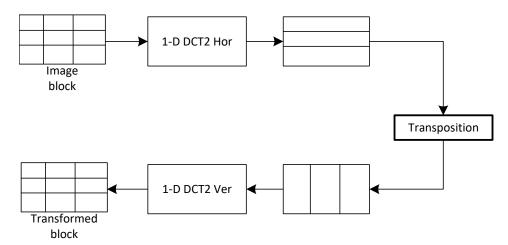

| 7.7  | 2-D forward DCT-2                                                                                 | 93 |

| 7.8  | Shared DCT/iDCT chain                                                                             | 93 |

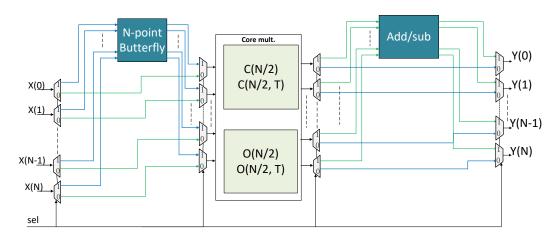

| 7.9  | Unified N-point DCT/iDCT architecture                                                             | 94 |

|      |                                                                                                   |    |

List of figures xiii

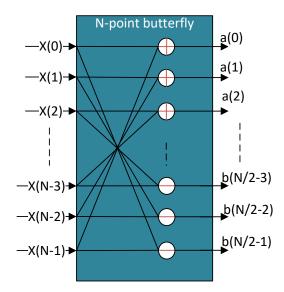

| 7.10 | N-point butterfly forward DCT-2 module                                                               |

|------|------------------------------------------------------------------------------------------------------|

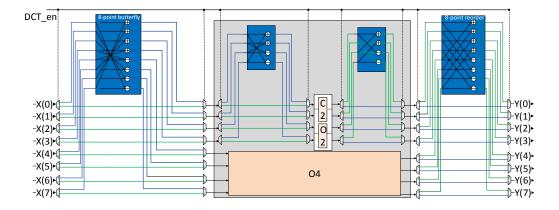

| 7.11 | 8-point shared DCT-2/iDCT-2 design                                                                   |

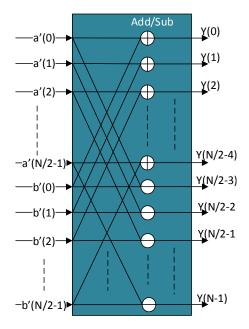

| 7.12 | N-point add/sub inverse DCT-2 module                                                                 |

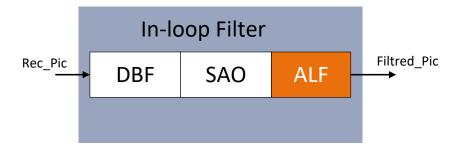

| 8.1  | VVC In loop filters                                                                                  |

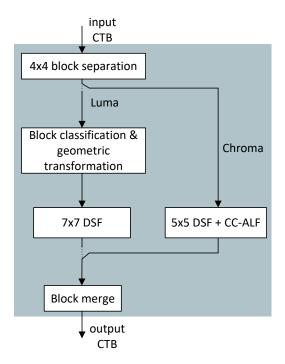

| 8.2  | ALF filtering steps for Luma and Chroma Coding Tree Block (CTB)s 105                                 |

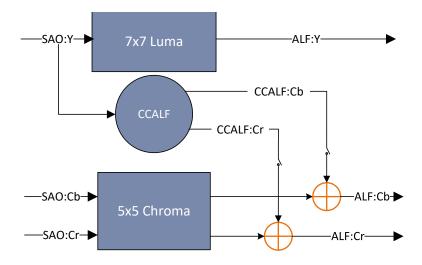

| 8.3  | ALF Luma and Chroma filters in the VVC decoder                                                       |

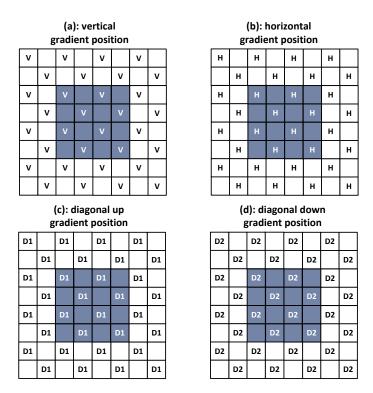

| 8.4  | Sub-sampled gradients in vertical, horizontal and two diagonal directions. Empty                     |

|      | samples are not used for gradients computation. The samples of current 4×4 macro-                    |

|      | block are highlighted in blue color                                                                  |

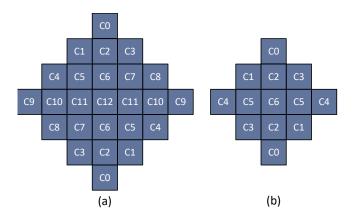

| 8.5  | Diamond Shape filters for Luma and Chroma, (a): Luma 2D $7 \times 7$ , (b) Chroma 2D $5 \times 5110$ |

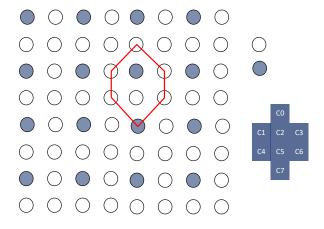

| 8.6  | Cross component 2D Diamond Shape filter, 420 sub-sampling example. Blue circles                      |

|      | represent the Chroma component while white circles are the Luma component 110                        |

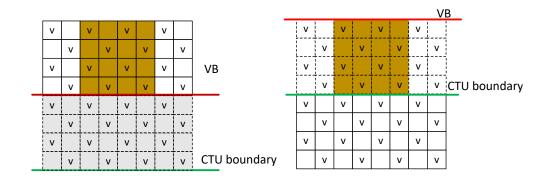

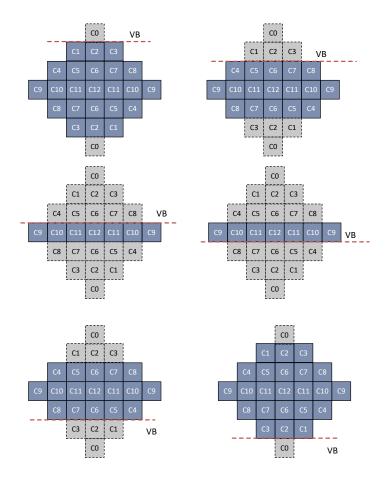

| 8.7  | Modified block classification at virtual boundaries                                                  |

| 8.8  | Modified ALF filtering for Luma component at virtual boundaries                                      |

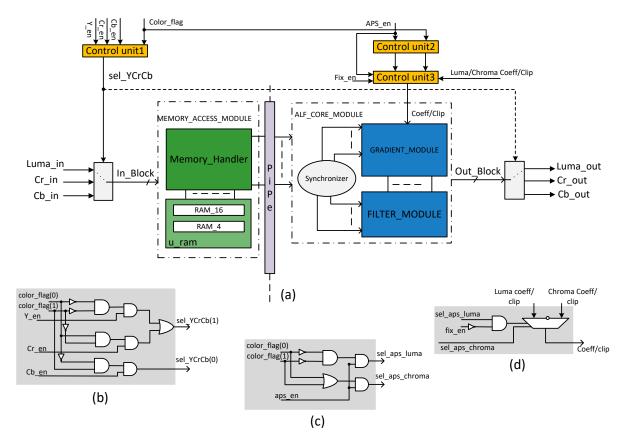

| 9.1  | Proposed hardware ALF architecture, (a): Unified design for ALL filters, (b): Control                |

|      | unit 1: this unit will initiate the start signals depending on the input color component.            |

|      | (c): Control unit 2: this unit will initiate the coefficients in Adaptation Parameter                |

|      | Set (APS) enable signals depending on the input color component, (d): Control unit                   |

|      | 3: depending on the APS enable and the Fix_en signals, this unit will propagate the                  |

|      | appropriate coefficients and clip values to the core module                                          |

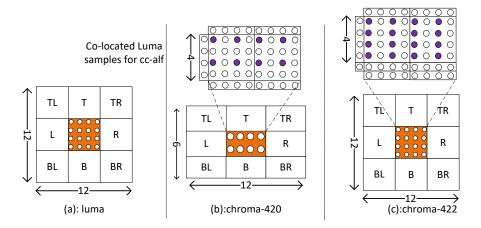

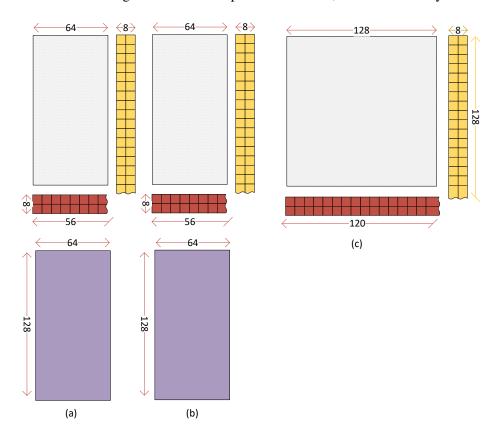

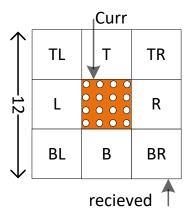

| 9.2  | (a) required macro blocks for Luma component (b) required macro blocks for Chroma                    |

|      | component with 4:2:0 sub-sampling (c) required macro blocks for Chroma compo-                        |

|      | nent with 4:2:2 sub-sampling                                                                         |

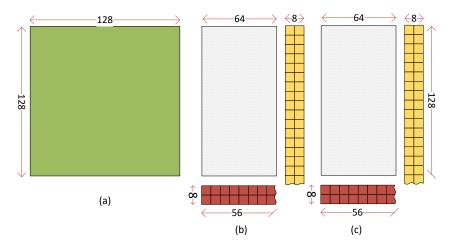

| 9.3  | Scenario (A) required memory for 4:2:2 sub-sampling example, (a) Luma blocks, (b)                    |

|      | Chroma Cr blocks, (c) Chroma Cb blocks                                                               |

| 9.4  | Scenario (B) required memory for 4:2:2 sub-sampling example, (a) and (b) show the                    |

|      | Chroma Cr and Cb filtered and unfiltered blocks for memory, (c) Luma memory blocks 121               |

| 9.5  | Scenario (C) required memory for 4:2:2 sub-sampling example: (a) Luma Line, Col-                     |

|      | umn and Cross-Component Adaptive Loop Filter (CCALF) storage, (b) Chroma Cr                          |

|      | Line and Column storage, (c) Chroma Cr Line and Column storage                                       |

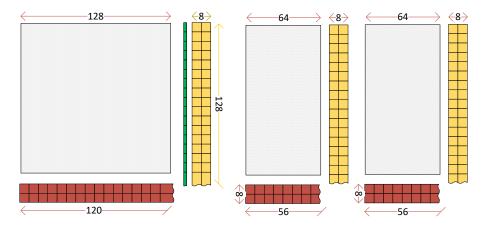

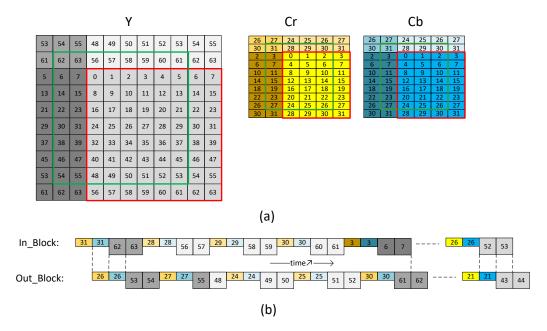

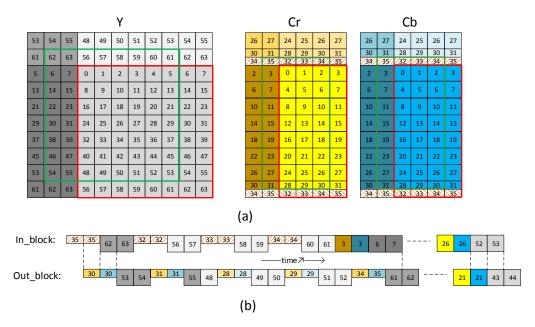

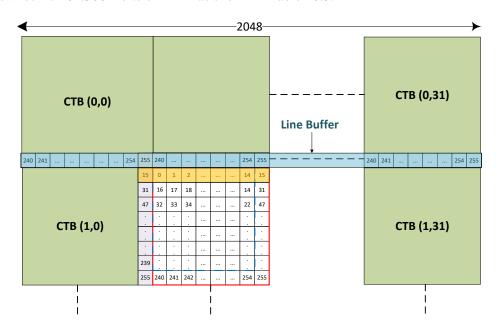

| 9.6  | ALF macro block scanning for 4:2:0 sub-sampling. (a): Coding Tree Unit (CTU)32                       |

|      | example: the red rectangle is the current CTB. The green rectangle represents the                    |

|      | block processed by the ALF (bounded by the VB). (b) input/output macro-blocks                        |

|      | sequencing: one $4\times2$ Cr macro-block followed by one $4\times2$ Cb macro-block followed         |

|      | by two 4×4 Y macro blocks                                                                            |

| 9.7  | ALF macro-block scanning for 4:2:2 sub-sampling. (a): CTU32 example: the red                         |

|      | rectangle is the current CTB. The green rectangle represents the block processed by                  |

|      | the ALF (bounded by the VB). (b) input/output macro-blocks sequencing: one $4\times4$                |

|      | Cr macro-block followed by one $4\times4$ Cb macro-block followed by two $4\times4$ Y macro          |

|      | blocks                                                                                               |

**xiv** List of figures

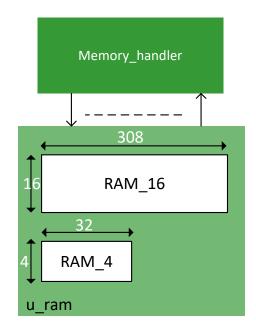

| 9.8   | ALF Random Access Memories                                                             | 127 |

|-------|----------------------------------------------------------------------------------------|-----|

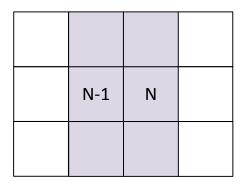

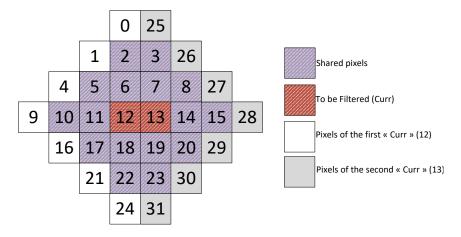

| 9.9   | Shared region between two successive macro-blocks at the same line                     | 128 |

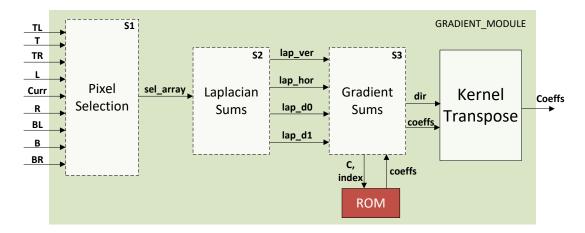

| 9.10  | Gradient sum module                                                                    | 129 |

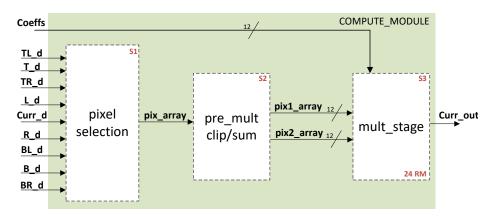

| 9.11  | ALF filter module                                                                      | 130 |

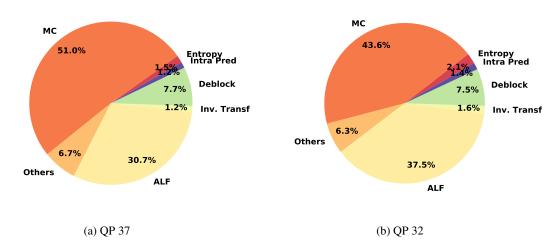

| 9.12  | Complexity distribution of decoding tools in the VTM software for two different QPs.   | 131 |

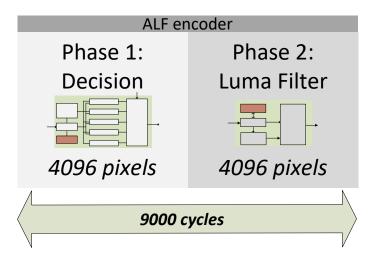

| 10.1  | ALF encoder phases                                                                     | 136 |

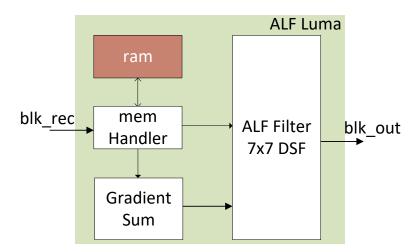

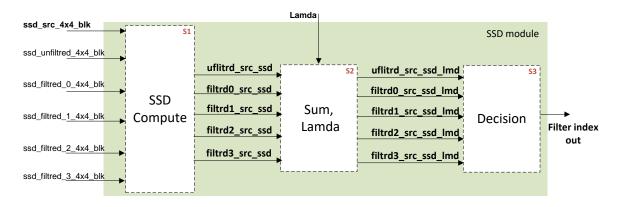

| 10.2  | ALF encoder top level design                                                           | 138 |

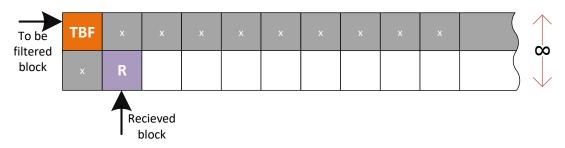

| 10.3  | Distance between the received and the to be filtered Luma block                        | 138 |

| 10.4  | Shared region between two successive Luma blocks                                       | 139 |

| 10.5  | Gradient top level design for Luma filter                                              | 140 |

| 10.6  | ALF Luma 7×7 filter top design                                                         | 140 |

| 10.7  | pixel array indexation                                                                 | 141 |

| 10.8  | ALF Decision input arrival order and filtered region. Red block is the filtered region |     |

|       | while the green block represents the CTB. The blue arrows mimics the sequencing        |     |

|       | order                                                                                  | 142 |

| 10.9  | ALF encoder top level design                                                           | 143 |

| 10.10 | Required blocks for Luma gradient and 7×7 filter                                       | 144 |

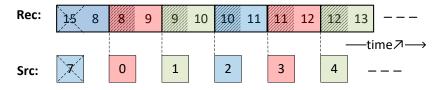

| 10.11 | 1 ALF decision source and reconstructed samples sequencing order. Two 4x4 REC          |     |

|       | blocks are scanned along with one 4x4 SRC blocks every cycle. The shopped blocks       |     |

|       | belongs to the not filtered region                                                     | 144 |

| 10.12 | 2ALF decision Random-Access Memory (RAM) blocks                                        | 145 |

| 10.13 | 3ALF decision gradient sum computation                                                 | 146 |

| 10.14 | 4ALF decision Sum of Square Differences (SSD) module                                   | 147 |

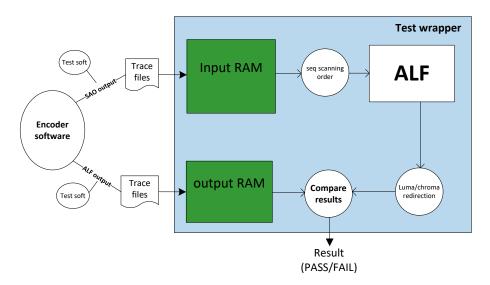

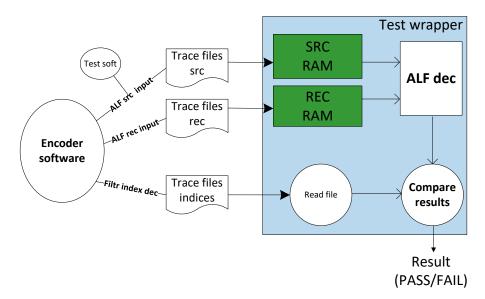

| 10.15 | 5ALF test-bench top level design                                                       | 148 |

| 10.16 | SALF decision test-bench top level design                                              | 148 |

| 11.1  | Thesis summary                                                                         | 154 |

# List of tables

| 4.1  | Primary Transform signaling in VVC                                                          | 45 |

|------|---------------------------------------------------------------------------------------------|----|

| 4.2  | Intra Prediction Mode (IPM) based secondary transform signaling in VVC                      | 47 |

| 5.1  | 2-D iMTS throughput performance bookmarking per block size for 4Kp30:420 reso-              |    |

|      | lution                                                                                      | 52 |

| 5.2  | MTS module interface                                                                        | 54 |

| 5.3  | Coefficient preparation module access and address definitions                               | 62 |

| 5.4  | Synthesis results for both ASIC and Field Programmable Gate Array (FPGA) platforms          | 63 |

| 5.5  | Comparison of different hardware transform designs                                          | 64 |

| 6.1  | LFNST & 1-D MTS throughput performance per block size for 4Kp60:420 resolution              |    |

|      | @450Mhz                                                                                     | 67 |

| 6.2  | LFNST & MTS design interface                                                                | 69 |

| 6.3  | Summary table for iMTS functional consumption                                               | 71 |

| 6.4  | LFNST input output characteristics                                                          | 73 |

| 6.5  | input/output rate table                                                                     | 74 |

| 6.6  | Coefficient preparation module input/output mapping                                         | 76 |

| 6.7  | Performance (%) in terms of Bjøntegaard Delta Rate (BD-BR) and run time complex-            |    |

|      | ity when MTS and LFNST tools turned off in VTM8.0 [3]. Evaluations performed                |    |

|      | under the VVC common test conditions [4]                                                    | 81 |

| 6.8  | Synthesis results for MTS-2 p/c and 4 p/c at 450 MHz                                        | 81 |

| 6.9  | Synthesis results for LFNST-2 p/c and 4 p/c at 450 MHz                                      | 81 |

| 6.10 | VVC vs HEVC Transform synthesis results at 450 MHz                                          | 82 |

| 6.11 | VVC vs HEVC separable Transform synthesis results at 450 MHz                                | 83 |

| 7.1  | Transform candidates and total samples area for I frames in respect to $64 \times 64$ CTU   |    |

|      | budget                                                                                      | 87 |

| 7.2  | Transform candidates and total samples area for P/B frames in respect to $64 \times 64$ CTU |    |

|      | budget                                                                                      | 87 |

| 7.3  | shared 1-D DCT-2 hor/forward LFNST multiplication cost                                      | 90 |

| 7.4  | shared 1-D DCT-2 ver/Inverse LFNST multiplication cost                                      | 91 |

| 7.5  | number of circuits per transform size                                                       | 97 |

| 7.6  | Cost summary                                                                                | 98 |

**xvi** List of tables

| 7.7  | DCT/iDCT vs DCT/LFNST                                                             | 99   |

|------|-----------------------------------------------------------------------------------|------|

| 8.1  | Mapping between the gradient values and the geometric transformations             | 109  |

| 9.1  | ALF throughput performance per CTU size for 4Kp30 with 4:2:2 resolution @450Mhz   | z115 |

| 9.2  | ALF design interfaces                                                             | 117  |

| 9.3  | Scenario (A) memory cost for 10-bits samples                                      | 120  |

| 9.4  | Scenario (B) memory cost for 10-bits samples                                      | 122  |

| 9.5  | Scenario (C) memory cost for 10-bits samples                                      | 123  |

| 9.6  | Memory usage (Kbits) comparison for different scanning order scenarios            | 123  |

| 9.7  | Performance (%) in terms of BD-BR and run time complexity when ALF, CCALF         |      |

|      | and Sample Adaptive Offset (SAO) tools turned off in VTM10.0 [5]. Evaluations     |      |

|      | performed under the VVC common test conditions [6]                                | 130  |

| 9.8  | Synthesis results for ALF @2 p/c at 450 MHz on Application-Specific Integrated    |      |

|      | Circuit (ASIC) 28-nm platform for typical condition of 85 Celsius with 0.8V input |      |

|      | voltage                                                                           | 131  |

| 9.9  | Power results for ALF @2 p/c at 450 MHz on ASIC 28-nm platform for typical        |      |

|      | condition of 85 Celsius                                                           | 132  |

| 9.10 | Adaptive Loop Filter vs Inverse transform blocks (MTS + LFNST) @2 p/c             | 132  |

| 9.11 | Comparison of different ALF hardware designs on FPGA and ASIC platforms           | 133  |

| 10.1 | ALF for Luma module interfaces                                                    | 137  |

| 10.2 | ALF decision design interfaces                                                    | 143  |

| 10.3 | ALF decision memory cost for different samples width sizes                        | 145  |

| 10.4 | Test sequences category and status                                                | 149  |

| 10.5 | Area synthesis results for ALF for Luma only @2 p/c at 450 MHz on ASIC 28-nm      |      |

|      | platform for typical condition of 85 Celsius with 0.8 input voltage               | 149  |

| 10.6 | Power results for ALF @2 p/c at 450 MHz on ASIC 28-nm platform for typical        |      |

|      | condition of 85 Celsius                                                           | 150  |

| 10.7 | Area synthesis results for ALF for Luma only @2 p/c at 450 MHz on ASIC 28-nm      |      |

|      | platform for typical condition of 85 Celsius with 0.8 input voltage               | 151  |

| 10.8 | Power results for ALF decision @1 p/c at 450 MHz on ASIC 28-nm platform for       |      |

|      | typical condition of 85 Celsius                                                   | 151  |

| 10.9 | Comparison between ALF decoder and encoder designs targeting ASIC platform for    |      |

|      | typical condition of 85 Celsius with 0.8 input voltage                            | 152  |

## Glossary

ALF Adaptive Loop Filter.

**ALM** Adaptive Logic Module.

**APS** Adaptation Parameter Set.

ASIC Application-Specific Integrated Circuit.

AVC Advanced Video Coding.

**B** bottom.

BD-BR Bjøntegaard Delta Rate.

**BL** bottom left.

BR bottom right.

BT Binary Tree.

**CCALF** Cross-Component Adaptive Loop Filter.

CM Constant Multipliers.

CTB Coding Tree Block.

CTC Common Test Conditions.

CTU Coding Tree Unit.

CU Coding Unit.

DC Design Compiler.

**DCT** Discrete Cosine Transform.

**DF** Deblocking Filter.

**DPB** Decoded Picture Buffer.

**xviii** Glossary

**DSF** Diamond Shape Filter.

**DSP** Digital Signal Processing.

**DST** Discrete Sine Transform.

**FPGA** Field Programmable Gate Array.

FPS Frame Per Second.

**HEVC** High Efficiency Video Coding.

HW Hardware.

**IICT** Inverse Integer Core Transforms.

**IP** Intellectual Property.

**JEM** Joint Exploration Model.

JVET Joint Video Experts Team.

KLT Karhunen-Loéve Theorem.

L left.

LFNST Low Frequency Non-Separable Transform.

MC Motion Compensation.

MPEG Motion Picture Experts Group.

MSE Mean Squared Error.

MTS Multiple Transform Selection.

MTT Multi Type Tree.

**NSST** Non-Separable Secondary Transform.

**QP** Quantization Parameter.

QT Quad-Tree.

R right.

**RAM** Random-Access Memory.

**RD** Rate Distortion.

Glossary

**RDO** Rate Distortion Optimization.

RM Regular Multiplier.

**ROM** Read-Only Memory.

**SAO** Sample Adaptive Offset.

**SPS** Sequence Parameter Set.

**SRAM** Static Random Access Memory.

SSD Sum of Square Differences.

T top.

TL top left.

TR top right.

TSMC Taiwan Semiconductor Manufacturing Company.

TT Ternary Tree.

TU Transform Unit.

VB Virtual Boundary.

VCEG Video Coding Experts Group.

VHDL VHSIC Hardware Description Language.

VLSI Very Large Scale Integration.

VTM VVC Test Model.

VVC Versatile Video Coding.

## Chapter 1

## Résumé en Français

#### 1.1 Préamble

Les récents progrès technologiques des appareils électroniques tels que les appareils mobiles, les écrans et les caméras ont fait exploser la demande de consommation multimédia. L'évolution rapide des processeurs puissants et des réseaux à haut débit, accompagnée d'un changement radical vers une interaction sociale en ligne croissante, conduit à une consommation vidéo d'une ampleur sans précédent. Selon une étude récente menée par la société Cisco, le trafic vidéo sur l'IP mondial représentera 82 % de l'ensemble du trafic IP d'ici 2023, contre 61 % en 2016 [7]. Une autre étude de la société Ericsson annonce que le trafic vidéo devrait représenter 69 % de l'ensemble du trafic de données mobiles en 2021 et devrait passer à 79 % en 2027 [8]. En outre, les applications vidéo émergentes telles que les vidéos à gamme dynamique élevée (HDR) et les vidéos à 360° nécessitent une consommation de bande passante élevée et des recherches supplémentaires.

La norme HEVC [9] a été finalisée en 2013 pour répondre à la demande croissante de vidéos à plus haute résolution, apportant un gain de compression de 50% à qualité égale par rapport à son prédécesseur H.264/Advanced Video Coding (AVC). Contestée par le codec ouvert et libre de droits AV1, une nouvelle norme de codage vidéo VVC [10] a été finalisée en juillet 2020, apportant un gain de compression supplémentaire par rapport au HEVC. VVC comprend des outils de codage supplémentaires pour répondre à la consommation vidéo jusqu'à 8K ou plus, au HDR, à la gamme de couleurs étendue, au contenu d'écran généré par ordinateur et à la vidéo 360° pour la réalité virtuelle et augmentée. Toutes les normes de compression vidéo traitent la transmission efficace et le stockage numérique des vidéos. La procédure de normalisation englobe diverses exigences, notamment le débit binaire, la qualité de l'image, le délai, l'accessibilité aléatoire et la complexité. Une norme de codage vidéo est conçue pour répondre à de nombreuses applications, á savoire les communications en temps réel, la diffusion de vidéos à la demande et la diffusion en direct. Cependant, ces normes ne spécifient pas directement une mise en œuvre pour un produit final. L'application d'une norme à un produit nécessite une adaptation soigneuse à l'application cible spécifique. En particulier, l'application en temps réel présente de nombreuses contraintes auxquelles il faut répondre avant qu'elle ne devienne un produit valide. L'utilisation d'une solution Hardware (HW) dédiée permet d'atteindre une qualité supérieure tout en maintenant une faible consommation d'énergie et une transmission en temps réel. 2 Résumé en Français

La conception et l'implémentation d'une solution HW pour le nouveau standard VVC est le terrain de jeu de cette thèse.

#### 1.2 Contexte et motivation

Cette thèse se concentre sur la conception et l'implémentation de nouveaux outils VVC pour une application en temps réel ciblant un encodeur et un décodeur ASIC HW professionnel disponible comme produit commercial sur le marché. L'objectif de ces produits est de supporter des applications d'encodage et de décodage en temps réel jusqu'à 4K tout en maintenant une faible consommation d'énergie dans un dispositif matériel compact dédié, entièrement développé par VITEC, la société partenaire française experte en codage vidéo en temps réel.

VVC introduit de nouveaux outils de codage qui améliorent l'efficacité globale du codage par rapport à son prédécesseur HEVC. Cependant, ces nouveaux outils ont un impact significatif sur la complexité du VVC qui est estimée à quatre fois celle du HEVC. Ces outils s'accompagnent d'une forte augmentation de la complexité de calcul du côté du décodage et (encore plus) du codage. En particulier, la partie transformée et le filtre en boucle de VVC introduisent leurs propres nouveaux outils et ont un impact majeur sur les complexités d'encodage et de décodage. Le module de transformation VVC comprend des transformations séparables et non séparables nommées respectivement MTS et LFNST. L'outil MTS implique trois types de transformations trigonométriques, notamment DCT type 2 (DCT-2), DCT type 8 (DCT-8) et DST type 7 (DST-7), avec des tailles de bloc pouvant atteindre 64 × 64 pour DCT-2 et 32 × 32 pour DCT-8 et DST-7. L'utilisation des familles DCT/DST donne la possibilité d'appliquer des transformations séparables, la transformation d'un bloc pouvant être appliquée séparément dans les directions horizontale et verticale. La LFNST, quant à elle, est une transformation non séparable, ce qui signifie qu'elle est appliquée en une seule fois. Et ceci après la transformation séparable et avant la quantification du côté de l'encodeur. Du côté du décodeur, elle est appliquée après la quantification inverse et avant la transformation séparable inverse. Différente de la transformation primaire, la transformation secondaire n'opère que sur les coefficients de transformation basse fréquence. Elle est appliquée pour toutes les tailles de Transform Unit (TU) de 4 × 4 à 64 × 64, y compris les blocs symétriques et asymétriques. Pour son processus de filtre en boucle, VVC introduit l'utilisation d'un nouvel outil appelé ALF. Les filtres en boucle sont situés dans la boucle de décodage de l'encodeur et visent à améliorer la qualité percue de la séquence vidéo décodée en éliminant les artefacts de blocage, d'anneau ou de flou générés par les étapes de décodage précédentes. Le rôle principal du ALF est de contribuer à la réduction des artefacts visibles tels que le ringing et le blurring en diminuant l'erreur absolue moyenne entre l'image originale et l'image reconstruite. Pour ce faire, il utilise différents filtres pour les composantes Luma et Chroma. Pour la composante Luma, il utilise un 7 × 7 Diamond Shape Filter (DSF). Pour les composantes Chroma, le ALF utilise deux filtres. Le premier est un filtre DSF  $5 \times 5$  et le second est le filtre diamant CCALF qui utilise les échantillons Luma co-localisés pour filtrer les échantillons Chroma. De plus, l'utilisation d'une conception HW dédiée au codage vidéo s'avère plus efficace que la solution logicielle, selon l'étude publiée par Xilinx [11]. En outre, un HW codec efficace doit être optimisé en termes de taille, de poids et de consommation d'énergie afin d'offrir la meilleure expérience utilisateur tout en réalisant 1.3 Contributions 3

une application en temps réel avec la meilleure qualité vidéo.

#### 1.3 Contributions

L'objectif global de ce doctorat est d'étudier les conceptions matérielles et la réduction de la complexité des nouveaux outils VVC dans un cadre de codage en temps réel pour les plateformes ASIC. Les conceptions proposées visent à réduire le coût de la puce ASIC en termes de surface, de mémoire et de consommation électrique. Trois outils principaux ont été étudiés pour le contexte de l'encodeur et du décodeur : MTS, LFNST et ALF. Dans ce contexte, les contributions de la thèse ont été identifiées comme suit :

- Conception matérielle Transformer pour le VVC encodeur et décodeur: L'objectif est de concevoir une implémentation matérielle efficace pour les outils de transformation dans le contexte d'un décodeur et d'un encodeur ciblant la plate-forme ASIC. Il s'agit d'une architecture multistandard qui prend en charge le bloc de transformation des normes MPEG récentes, notamment AVC, HEVC et VVC. L'architecture est optimisée et élimine les complexités inutiles trouvées dans d'autres architectures proposées en utilisant des multiplicateurs réguliers au lieu de multiplicateurs constants. Le LFNST, un des nouveaux outils introduits dans le VVC, est implémenté dans une conception unifor avec le MTS. La conception proposée utilise un total de 64 multiplicateurs réguliers dans une architecture pipe-lined. Il exploite toutes les optimisations des transformations primaires et secondaires, y compris la décomposition papillon, la remise à zéro des coefficients et la relation linéaire inhérente entre les types de transformation. La transformation unifiée maintient un débit constant de 1 échantillon par cycle et une latence système fixe pour toutes les tailles de blocs.

- Conception matérielle ALF pour VVC encodeur et décodeur: L'objectif est de concevoir une implémentation matérielle efficace pour le nouvel outil ALF dans le contexte d'un décodeur et d'un encodeur ciblant une plateforme ASIC 4K. Une nouvelle architecture matérielle est présentée, en tenant compte de ses trois filtres :  $7 \times 7$ ,  $5 \times 5$  et  $3 \times 4$  CCALF. La solution proposée établit un ordre de balayage entre les composantes Luma et Chroma qui réduit considérablement la mémoire. La conception tire parti de toutes les caractéristiques de ALF et établit un module matériel unifié pour tous les filtres. Elle utilise 26 multiplicateurs réguliers dans une architecture pipe-lined avec un débit fixe de 2 pixels/cycle et une latence système fixe quel que soit le filtre sélectionné. Pour le contexte du codeur, le ALF comporte deux phases : le filtrage et le processus de décision. Il a été conçu après une étude approfondie de l'algorithme de décision ALF et a abouti à une architecture matérielle de première génération, mais implémentable, capable de capter une part importante des performances de cet outil. En fait, l'étude a révélé qu'un bon compromis entre le taux, la distorsion et la complexité matérielle est trouvé lorsque le codeur active le ALF pour les échantillons Luma uniquement et pour les CTUs de taille 64. En outre, il limite le processus de décision à quatre ensembles fixes de coefficients, testant ainsi quatre des seize indices d'ensembles de filtres définis dans la norme. À notre connaissance,

4 Résumé en Français

il s'agit de la première contribution dans la littérature qui propose une étude de conception matérielle complète pour le module ALF.

Dans cette thèse, les conceptions et études proposées pour ces objectifs ont été intégrées dans un encodeur/décodeur vidéo professionnel en temps réel HW.

#### 1.4 Organisation

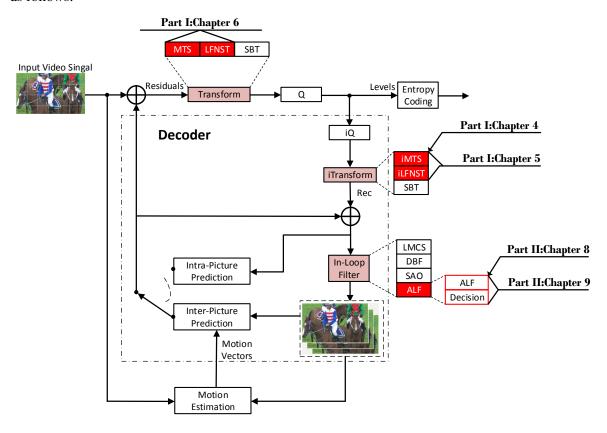

Le chapitre 3 commence par une introduction aux bases du codage vidéo et à certains concepts essentiels pour cette thèse, de l'histoire de la compression vidéo à travers les principaux standards et codecs, au schéma classique de compression vidéo hybride. Il présente un bref aperçu des principaux outils de l'état de l'art VVC. En outre, il présente la caractérisation d'un codec vidéo en temps réel avec une comparaison entre plusieurs codeurs commerciaux.

Dans le chapitre 4, l'accent est rapidement mis sur l'étape de transformation où un historique du processus de transformation est discuté pour les normes VVC. En particulier, les outils MTS et LFNST sont discutés et décrits en détail. Ensuite, les propositions importantes de l'état de l'art en matière d'optimisation de transformée, d'approximation et d'implémentation matérielle essentiellement pour les types de transformée MTS sont présentées.

Le chapitre 5 aborde l'implémentation du processus MTS y compris ses trois types de transformation (DCT-2, 8 et DST-7). Ce dernier est conçu dans le contexte d'un système 4K HW temps réel. ASIC VVC en temps réel. Dans ce cas, le module 2-D MTS doit soutenir un débit fixe de 1 échantillon/cycle. En outre, pour faciliter le chaînage entre différentes tailles de blocs, ce dernier doit maintenir une latence unifiée indépendamment des tailles de blocs et des types de transformation. Presque toutes les études de l'état de l'art pour la conception de la première transformation HW considèrent principalement une approche sans multiplicateur, c'est-à-dire CM, au lieu d'utiliser RM. Dans ce travail, une étude et une comparaison pour deux architectures matérielles pour le VVC MTS est présentée. La première implémente la transformation en utilisant une architecture basée sur CM, tandis que la seconde utilise une architecture basée sur RM. Enfin, les résultats expérimentaux et de synthèse sont discutés et comparés aux travaux connexes.

Le chapitre 6 aborde le problème de l'implémentation matérielle du VVC 1D inverse. MTS et LFNST visant une résolution de 4Kp60 et une fréquence de 450Mhz. Les MTS et LFNST 1-D doivent tous deux supporter une latence système fixe avec un débit fixe de 4 échantillons/cycle. D'après notre étude précédente du chapitre 5, la meilleure approche pour implémenter l'iMTS est une architecture basée sur l'RM. C'est également la même approche utilisée pour mettre en œuvre l'iLFNST. Dans ce travail, une architecture matérielle unifiée pour les VVC iMTS et iLFNST utilisant une architecture basée sur RM est décrite. Enfin, le montage expérimental et les résultats de synthèse des implémentations de la transformation VVC avec une comparaison avec la transformation HEVC sont présentés.

Le chapitre 7 présente une comparaison entre une conception partagée unissant le DCT-2 et son inverse et une conception partagée unissant le DCT-2 et le LFNST à un débit de 32 échantillons/cycle dans le contexte d'un VVC 4K temps réel. ASIC en temps réel. Tout d'abord, le coût de chaque

1.4 Organisation 5

conception partagée séparément est étudié. Ensuite, une comparaison entre les deux solutions avec une mise en évidence des principales différences est présentée.

Le chapitre 8 se concentre sur le contexte de l'outil ALF de VVC. Il présente les différents filtres utilisés par l'ALF pour les composantes Luma et Chroma. En outre, il présente les implémentations matérielles existantes de l'ALF.

Le chapitre 9 présente une nouvelle architecture matérielle pour le filtre VVC ALF, en considérant ses trois filtres :  $7 \times 7$ ,  $5 \times 5$  et  $3 \times 4$  CCALF. Cette conception est basée sur le dernier Working Draft et le dernier VVC Test Model (VTM). La conception proposée maintient un débit fixe de 2 pixels/cycle avec une latence système fixe qui permet le traitement de vidéo 4K à 60 images par seconde en sous-échantillonnage 4:2:2 Chroma. La conception proposée est intégrée dans une puce décodeur vidéo professionnelle supportant plusieurs normes de codage vidéo. L'article décrit tout d'abord la conception de haut niveau du module ALF. Deuxièmement, il montre les différents balayages d'entrée ainsi que l'ordre de balayage le plus optimal. Troisièmement, il décrit les configurations de mémoire de l'ordre de balayage d'entrée proposé. Ensuite, la conception proposée pour le module de gradient et pour les filtres ALF de base est abordée. Enfin, il présente le montage expérimental et les résultats de synthèse du ALF ainsi qu'une comparaison avec l'état de l'art.

Le chapitre 10 se concentre sur la conception matérielle des ALF dans le contexte du codeur. Il présente tout d'abord les conceptions matérielles des modules de mémoire, de somme des gradients et de filtrage pour le ALF Luma pour un débit de deux pixels/cycle. Deuxièmement, il décrit l'architecture de décision ALF pour un débit d'un pixel/cycle. Troisièmement, il présente les conceptions matérielles de la mémoire, du gradient, du filtrage et des modules SSD pour la décision ALF. Enfin, il présente le montage expérimental et les résultats de synthèse en comparaison avec le décodeur ALF.

## **Chapter 2**

## Introduction

#### 2.1 Preamble

The recent technological progress in electronic devices such as mobile devices, screens and cameras has skyrocketed the multimedia consumption demand. Rapidly evolving powerful processors and high-speed networks accompanied with a radical shift to increasing online social interaction lead video consumption on an unprecedented scale. According to a recent study conducted by Cisco company in [7], the video traffic over Global IP will account for 82% of all IP traffic by 2023, up from 61% in 2016. Another study from Ericsson company announced that video traffic is estimated to account for 69% of all mobile data traffic in 2021 and is expected to increase to 79% percent in 2027 [8]. Besides, emerging video applications such as High Dynamic Range (HDR) and 360 videos require a high bandwidth consumption and further research.

The HEVC standard [9] was finalized in 2013 to address growing demands for higher resolution videos, bringing a 50% compression gain at the same quality against its predecessor H.264/AVC. Challenged by the open and royalty-free codec AV1, a new video coding standard VVC [10] was finalized in July 2020, bringing further compression gain over HEVC. VVC includes additional coding tools to address video consumption up to 8K or larger, HDR, wide color gamut, computer-generated screen content, and 360° video for virtual and augmented reality. All video compression standards address efficient transmission and digital storage of videos. The standardization procedure encapsulates various requirements, including bit rate, picture quality, delay, random accessibility, and complexity. A video coding standard is designed to address many applications, including real-time communications, on-demand video delivery, and live streaming. However, these standards do not directly specify an implementation for an end product. Applying a standard to a product requires careful adaptation to the specific target application. In particular, the real-time application has many constraints that must be answered before it can become a valid product. Using dedicated HW solution allows the capability to reach higher quality while maintaining low energy consumption and real-time transmission. Designing and implementing HW solution for the new VVC standard is the playground of this thesis.

8 Introduction

#### 2.2 Context and Motivation

This thesis focuses on designing and implementing new VVC tools for a real-time application targeting a professional HW ASIC encoder and decoder available as a commercial product in the market. The aim of these products is to support up to 4K real-time encoding and decoding applications while maintaining a low power consumption in a compact dedicated hardware device fully developed by VITEC, the French partner company which expertise in real-time video coding.