# Real-time flexible and virtualized transponders for optical telecommunications

Alexandre Gouin

#### ▶ To cite this version:

Alexandre Gouin. Real-time flexible and virtualized transponders for optical telecommunications. Signal and Image processing. INSA de Rennes, 2022. English. NNT: 2022ISAR0011. tel-04482228

### HAL Id: tel-04482228 https://theses.hal.science/tel-04482228

Submitted on 28 Feb 2024

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### THÈSE DE DOCTORAT DE

#### L'INSTITUT NATIONAL DES SCIENCES APPLIQUÉES RENNES

ÉCOLE DOCTORALE N° 601

Mathématiques et Sciences et Technologies de l'Information et de la Communication

Spécialité: Télécommunications

Par

### Alexandre GOUIN

# Transpondeurs temps-réel flexibles pour les télécommunications optiques et virtualisés

Real-time flexible and virtualized transponders for optical communications

Thèse présentée et soutenue à Rennes, le 31/05/2022

Unité de recherche : IETR

ISAR 12 / D22 - 12

#### Rapporteurs avant soutenance :

Olivier ROMAIN PR, Université de Cergy Pontoise

Cédric WARE PR, Télécom Paris

**Composition du Jury:**

Présidente : Christelle AUPETIT-BERTHELEMOT PR, XLIM

Examinateurs : Cédric WARE PR, Télécom Paris

Olivier ROMAIN PR, ETIS

Matthieu GAUTIER MCF-HDR, IRISA Angélique RISSONS PR, ISAE - SUP AERO

Jean-Christophe PREVOTET PR, IETR

Dir. de thèse : Fabienne NOUVEL MCF-HDR, IETR

Co-dir. de thèse : Patricia LAYEC Ingénieure de recherche, Nokia Bell Labs

Invité:

Arnaud DUPAS Ingénieur de Recherche, Nokia Bell Labs

## **C**ONTENTS

| Abstract                                                                  | vi             |

|---------------------------------------------------------------------------|----------------|

| List of publications                                                      | viii           |

| List of Figures                                                           | ix             |

| List of Tables                                                            | xix            |

| Acronyms                                                                  | xxi            |

| Résumé étendu en Français                                                 | xxiii          |

| Réseaux de transport optique                                              | xxiv           |

| Couche physique                                                           | xxiv           |

| Plan de contrôle                                                          | xxvii          |

| Généralités sur le transpondeur optique et le transpondeur optique reconf | igurablexxviii |

| Prototypage d'un transpondeur optique flexible pour réseaux SDN           | xxxii          |

| Protocole d'auto-négociation pour transpondeur optique                    | xxxiii         |

| Monitoring embarqué                                                       | xxxvi          |

| Validation du prototype complet                                           | xl             |

| Intégration avec un setup temps-réel                                      | xliii          |

| Service d'accélération et transpondeur                                    | xliv           |

| Réseau de neurone sur FPGA                                                | xlvi           |

| Validation en simulation                                                  | xlviii         |

| Validation en implémentation                                              | l              |

| Conclusion                                                                | liii           |

| 1 Introduction                                                            | 1              |

| 2 The optical transport network and the optical transponder               | 5              |

| 2.1 Optical transport networks                                            | 6              |

| 2.1.1 Optical layer architecture                                          | 6              |

|   |      | 2.1.2 Optical line equipment                                             | 10        |

|---|------|--------------------------------------------------------------------------|-----------|

|   |      | 2.1.2.1 Optical Transponder                                              | 10        |

|   |      | 2.1.2.2 OADM                                                             | 12        |

|   |      | 2.1.2.3 Amplifiers                                                       | 15        |

|   |      | 2.1.3 Optical link impairment                                            | 15        |

|   |      | 2.1.4 Optical transport network control plane                            | 17        |

|   | 2.2  | Optical Transponders                                                     | 20        |

|   |      | 2.2.1 Architecture                                                       | 20        |

|   |      | 2.2.2 Digital and Analog conversion                                      | 21        |

|   |      | 2.2.3 Digital signal processing                                          | 22        |

|   |      | 2.2.3.1 Transmitter side DSP $\dots$                                     | 23        |

|   |      | 2.2.3.2 Receiver side DSP                                                | 25        |

|   |      | 2.2.4 Transmitter                                                        | 26        |

|   |      | 2.2.5 Receiver                                                           | 27        |

|   |      | 2.2.6 Physical optical interface                                         | 28        |

|   | 2.3  | Conclusion                                                               | 30        |

| 3 | Flex | xibility and reconfigurable transponders                                 | 31        |

|   | 3.1  | •                                                                        | 31        |

|   |      | 3.1.1 The FPGA hardware                                                  | 32        |

|   | 3.2  | Network flexibility                                                      | 37        |

|   |      | 3.2.1 SDN and Hardware Virtualization                                    | 38        |

|   | 3.3  | Reconfigurable optical transponders                                      | 41        |

|   |      | 3.3.1 The Sliceable Bandwidth Variable Transponder                       | 42        |

|   |      | 3.3.1.1 Bandwidth Variable Transponder                                   | 42        |

|   |      | 3.3.1.2 Sliceability and virtualization                                  | 45        |

|   |      | 3.3.2 Automatic hitless reconfigurable transponders for flexible optical |           |

|   |      | networks                                                                 | 48        |

|   | 3.4  | Conclusion                                                               | 51        |

| 4 | Rea  | d-time optical flexible transponder prototype for software defined       |           |

| _ |      |                                                                          | <b>52</b> |

|   | 4.1  | Introduction                                                             | 52<br>52  |

|   | 4.2  | Prototype transponder presentation                                       | 53        |

|   | 4.3  | Auto-Negotiation Protocol                                                | 55        |

|   | T.0  | 11400 110gottation 1 1000cot                                             | 99        |

|    |       | 4.3.1   | Design                                                          | . 55  |

|----|-------|---------|-----------------------------------------------------------------|-------|

|    |       | 4.3.2   | Implementation                                                  | . 56  |

|    |       | 4.3.3   | Validation                                                      | . 59  |

|    | 4.4   | Embed   | dded monitoring processing and decision-making                  | . 63  |

|    | 4.5   | Netwo   | rk Controller Interfacing                                       | . 68  |

|    | 4.6   | Protot  | type transponder validation                                     | . 70  |

|    | 4.7   | Integra | ation with a baud-rate variable setup                           | . 78  |

|    |       | 4.7.1   | Transmitter                                                     | . 79  |

|    |       | 4.7.2   | Receiver and deframer board                                     | . 82  |

|    |       | 4.7.3   | Validation                                                      | . 87  |

|    | 4.8   | Conclu  | ısion                                                           | . 90  |

| 5  | Tra   | nspond  | ler and acceleration services                                   | 92    |

|    | 5.1   | Neura   | l network-based power monitoring                                | . 93  |

|    |       | 5.1.1   | Generalities on neural network algorithms                       | . 93  |

|    |       | 5.1.2   | Neural network-based optical nonlinearity monitoring and launch |       |

|    |       |         | power optimization                                              | . 96  |

|    | 5.2   | FPGA    | implementation                                                  | . 101 |

|    |       | 5.2.1   | Data set and neural network generation                          | . 102 |

|    |       | 5.2.2   | Logical Implementation                                          | . 107 |

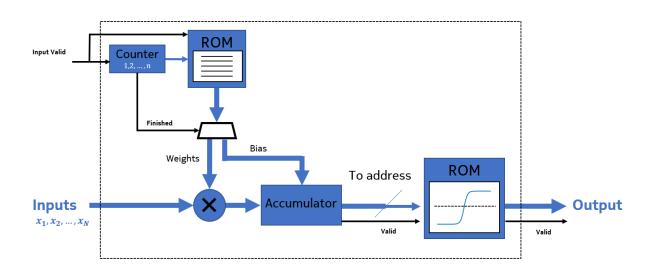

|    |       |         | 5.2.2.1 Neuron and network hardware structure                   | . 107 |

|    |       |         | 5.2.2.2 Simulation validation and resource utilization          | . 113 |

|    |       | 5.2.3   | Network weights update                                          | . 117 |

|    |       | 5.2.4   | Implementation and validation                                   | . 122 |

|    | 5.3   | Conclu  | ısion                                                           | . 125 |

| 6  | Con   | clusio  | n and perspectives                                              | 126   |

| Bi | bliog | graphy  |                                                                 | 129   |

### **ABSTRACT**

Optical transport networks, the high capacity network where optical links span from hundreds to thousand kilometers, have undergone major changes in recent years to accompany the ever growing demands in bitrate, service reliability and reduction in latency. The Elastic Optical Network paradigm is under a lot of development, taking advantage of the higher reconfigurability of optical hardware and increases of the control plane automation capabilities to make the networks more reliable and flexible.

In this manuscript, we focus on the optical transponder, the optical equipment that bridges the access networks where client signals come from and the optical transport network that routes them to their destination. This equipment has followed the trend of flexibility and is more reconfigurable than ever. From the modulation format, the optical launch power, the central frequency of the signal, the error correction code, etc... One can tune an optical transponder parameter to the current needs of the network. Also, the transponder is following the adoption of the virtualization techniques inside the optical network, which allows more advanced handling of its resources by the control plane and increases the automation capabilities of the optical network.

However fully flexible optical networks are not yet a reality, as some challenges have yet to be resolved. Firstly, the hardware is reconfigurable but has its limitations, especially the necessity to be put offline for the reconfiguration to be applied. As a change in the emitter can require adaptations in the receiver, efficient and synchronous changes of parameters are still a challenge. Also, the over centralization of monitoring and decision making in the control plane creates performance bottlenecks, which leads to higher time to detect a failure in the network and propose a change of configuration to resolve it. This makes reconfigurations rare and operational margins high for optical transponders, which will not run at their maximum potential.

We believe that to alleviate the aforementioned challenges for fully flexible optical networks, optical transponders should be given more decision power. By bringing more intelligence to the device, allowing it to process its own monitoring data, make decisions on the ideal set of parameters to resolve a degradation in quality of service and triggering itself a synchronous change of parameters with another transponder of the network will

allow for more active and frequent reconfigurations in the optical networks, increasing the networks overall flexibility and reliability.

Firstly, we provide in this thesis work an auto-negotiation protocol for optical transponders that allows for fast synchronous change of parameters. Integrated with a commercial transponder and an embedded monitoring and decision-making solution we have validated our solution against a centralized control plane in a network testbed in terms of fault detection and resolution times. We also validate our auto-negotiation solution with a real-time baud-rate variable setup and showcase a synchronized change of baudrate from 14GBaud to 7GBaud with the help of the protocol.

Secondly, we provide a neural network solution for embedded monitoring in the optical data plane. By allowing for a reconfiguration of the neurons weights of the network we believe that this solution can both provide advanced monitoring techniques for the optical equipment and allow smarter fault detection and reconfigurations in the data plane and provide computational resources for the optical control plane for remote monitoring which would accelerate decision making for the whole network.

### LIST OF PUBLICATIONS

- [i] **A. Gouin**, A. Dupas, and P. Layec, « In-Line Transmission Parameters Synchronization Protocol for Hitless Optical Coherent Communication », in 2020 International Conference on Optical Network Design and Modeling (ONDM), may 2020, p. 1-3. doi: 10.23919/ONDM48393.2020.9132995.

- [ii] **A. Gouin**, A. Dupas, L. G. Renom, A. Benabdallah, F. Boitier, and P. Layec, « Dynamic auto-negotiation with real-time transponders in software defined optical networks », in 2021 Optical Fiber Communications Conference and Exhibition (OFC), june 2021, p. 1-3., doi: 10.1364/OFC.2021.W6A.6

- [iii] **A. Gouin**, A. Dupas, L. Gifre Renom, A. Benabdallah, F. Boitier, and P. Layec, « Real-time optical transponder prototype with autonegotiation protocol for software defined networks », Journal of Optical Communications and Networking (JOCN), vol. 13, n. 9, p. 224, sept. 2021, doi: 10.1364/JOCN.427938.

- [iv] **A. Gouin**, A. Dupas, , F. Boitier, F. Nouvel, J.C. Prévotet and P. Layec, "Real-time optical transponder prototype with auto-negotiation protocol for software defined networks", GDR SOC2, Juin 2021, p. 2.

- [v] E. Dutisseuil, A. Dupas, **A. Gouin**, F. Boitier, and P. Layec, « Hitless Transmission Baud Rate Switching in a Real-Time Transponder Assisted by an Auto-Negotiation Protocol » (Top Scored), in 2022 Optical Fiber Communications Conference and Exhibition (OFC), march 2022, p. 4.

## **LIST OF FIGURES**

| 1  | Représentation de la technologie de Multiplexage en Longueur d'Onde            |

|----|--------------------------------------------------------------------------------|

|    | $(WDM)  \dots  xxv$                                                            |

| 2  | Structure d'une trame OTN (Optical Transport Network). Plusieurs sous          |

|    | structures cohabitent dans la trame : OTU (Optical Transport Unit), ODU        |

|    | (Optical Data Unit) et OPU (Optical Payload Unit), chacun comprenant           |

|    | leurs propres champs (permettant le monitoring, le concaténation, etc des      |

|    | signaux clients)                                                               |

| 3  | Représentations de (a) la grille de fréquence fixe traditionnellemnt utilisée  |

|    | dans les réseaux de transport optique, et (b) la grille flexible utilisée dans |

|    | les réseaux modernes élastiques                                                |

| 4  | Réprésentation de la couche physique d'un réseau de trasnport optique xxvi     |

| 5  | Représentation simplifée d'un plan de contrôle centralisé SDN (Software        |

|    | Defined Network)                                                               |

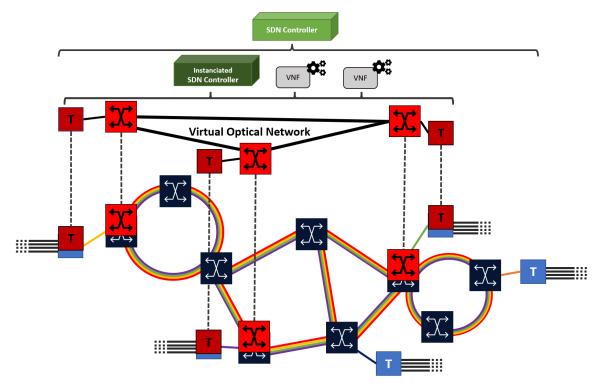

| 6  | Exemple de sous-réseau optique virtuel avec un contrôleur SDN instancié        |

|    | spécifiquement et des fonctions virtuelles VNF                                 |

| 7  | Représentation graphique d'un transpondeur optique xxx                         |

| 8  | Représentation des constellations pour les modulations (a) QPSK, (b) 16-       |

|    | QAM et (c) PM-QPSK                                                             |

| 9  | Représentation d'un transpondeur multi-flow, où le trafic client provenant     |

|    | de quatre ports à 100Gb est reparti sur deux ports ligne xxxi                  |

| 10 | Représentation de la virtualisation du transpondeur multi-flow de la Figure    |

|    | 9 en deux transpondeurs virtuels                                               |

| 11 | Exemple d'implémentation de white box avec des transpondeurs xxxii             |

| 12 | Représentation de notre prototype de transpondeur avec monitoring et           |

|    | auto-négociation                                                               |

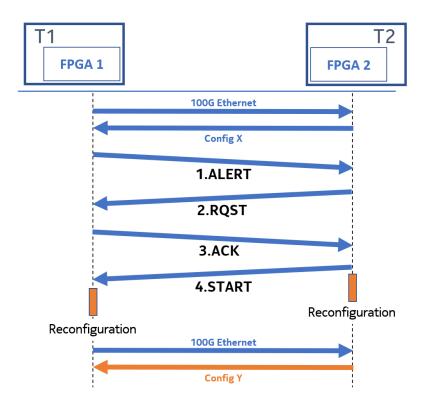

| 13 | Séquence des opération de notre protocole d'auto-négociation xxxiv             |

| 14 | Représentation schématique de l'implémentation temps-réel de notre pro-        |

|    | tocole d'auto-négociation xxxv                                                 |

| 15 | Représentation de notre palteforme de test pour la validation de notre pro-       |

|----|-----------------------------------------------------------------------------------|

|    | tocole d'auto-négociation, avec deux FPGAs pour l'insertion et la détection       |

|    | des messages d'auto-négociation, séparés par 2m ou 10km de fibre simple           |

|    | mode, et un Spirent pour générer et analyser du traffic Ethernet à 100Gbps. xxxvi |

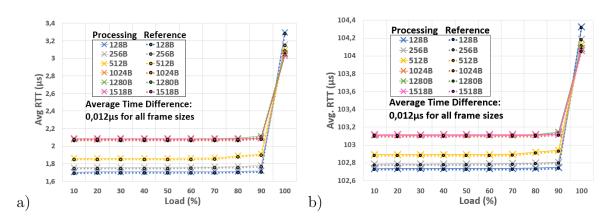

| 16 | Temps d'aller-retour (RTT) moyen en µs, selon les différentes tailles de          |

|    | trames en fonction de la charge en %, pour les setups avec et sans le pro-        |

|    | tocole d'auto-négociation. Les cartes sont séparées par (a) 2m de fibre et        |

|    | (b) 10km de fibre                                                                 |

| 17 | Prototype de monitoring embarqué avec un transpondeur Nokia PSI-2T xxxviii        |

| 18 | Coefficient $\beta$ de la courbe de puissance de réception en fonction du nombre  |

|    | de samples utilisés pour le calcul pour (a) une dégradation rapide et (b)         |

|    | un dégradation lente                                                              |

| 19 | Représentation de notre prototype complet avec FPGA, transpondeur com-            |

|    | mercial et Raspberry Pi                                                           |

| 20 | Intégration de notre transpondeur prototype au sein d'un banc de test réseau. xli |

| 21 | Résultats agrégés de 100 répétitions de notre protocole de validation pour        |

|    | (a) le setup où notre transpondeur prototype se charge de la détection et de      |

|    | la résolution de la dégradation induite par l'augmentation de l'atténuation       |

|    | dans l'atténuateur variable et (b) quand le plan de contrôle SDN s'occupe         |

|    | de la détection et la résolution. Les courbes représentent les valeurs mé-        |

|    | dianes des métriques capturées, les parties transparentes représentent les        |

|    | 15.8 et 84.2 quantiles. Sous les courbes on a tracé les histogrammes de ré-       |

|    | ception par le plan de contrôle des messages de notification Reconf. Start        |

|    | et Reconf. End                                                                    |

| 22 | Setup expérimental pour le changement de baudrate synchrone et sans               |

|    | perte de trafic en utilisant le protocole d'auto-négociation. Il est composé      |

|    | d'un Transmetteur (Tx) et d'un Récepteur (Rx) cohérents. Une voie de              |

|    | contrôle est mise en place entre la carte FPGA gérant le protocole d'auto-        |

|    | négociation et le Tx pour simuler une communication bidirectionnelle pour         |

|    | le protocole. Tous les FPGA du setup sont liés un ordinateur via un lien          |

|    | UART xliv                                                                         |

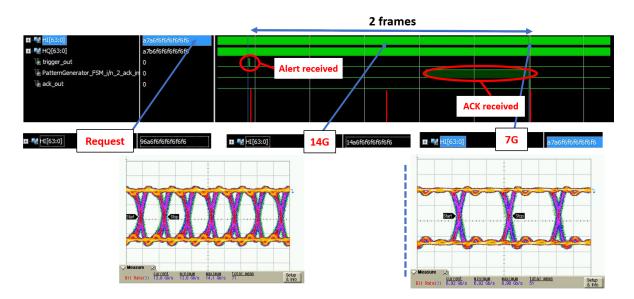

| 23 | Capture du FPGA gérant le protocole d'auto-négociation. On voit un                |

|    | changement de baudrate de 14GBaud à 7GBaud synchronisé grâce au pro-              |

|    | tocole. Le message ALERT a été envoyé avant les trames capturées xly              |

| 24  | Structure d'un réseau de neurone avec une couche cachée xlvi                       |

|-----|------------------------------------------------------------------------------------|

| 25  | Structure d'un neurone de réseau de neurone avec quatre entrées. Les en-           |

|     | trées sont multipliées avec des poids correspondants, sommées avec un biais,       |

|     | et passent dans une fonction d'activation xlvi                                     |

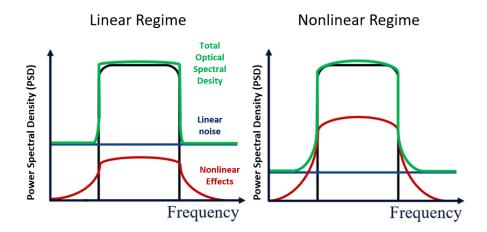

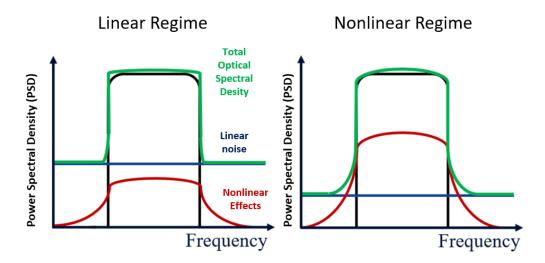

| 26  | Spectre optique dans le régime fortement linéaire et dans le régime forte-         |

|     | ment non-linéaire. Le canal modulé est représenté en noir, en bleu les con-        |

|     | tributions linéaires et en rouge les contributions non-linéaires. En vert est      |

|     | représenté le spectre total                                                        |

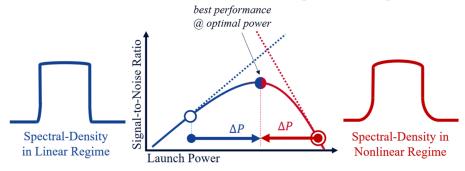

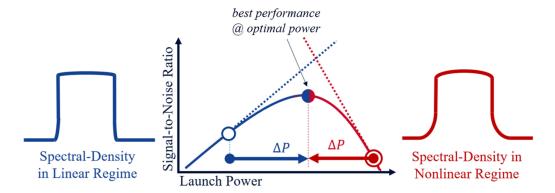

| 27  | Représentation du SNR d'un signal optique en fonction de la puissance              |

|     | d'émission. En bleu est représenté le système en régime fortement linéaire         |

|     | et en rouge en régime fortement non-linéaire. Il faut trouver la bonne puis-       |

|     | sance d'émission pour avoir la valeur de SNR au sommet de la courbe en             |

|     | cloche                                                                             |

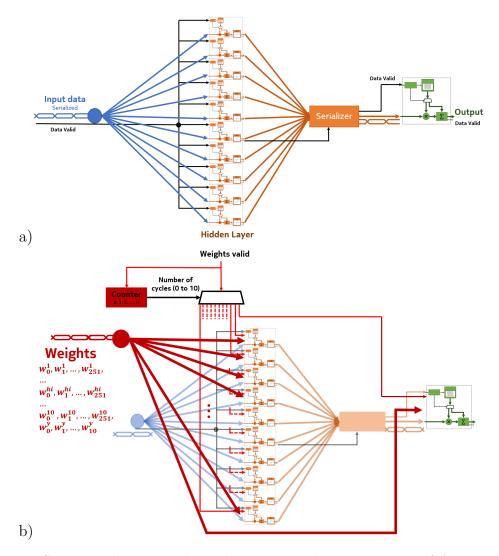

| 28  | Structure de notre réseau de neurones logique pour FPGA. La Figure (a)             |

|     | représente la gestion des flux de données circulent des entrées jusqu'à la         |

|     | sortie et dans la Figure (b) la logique de mise à jour des poids des neurones.xlix |

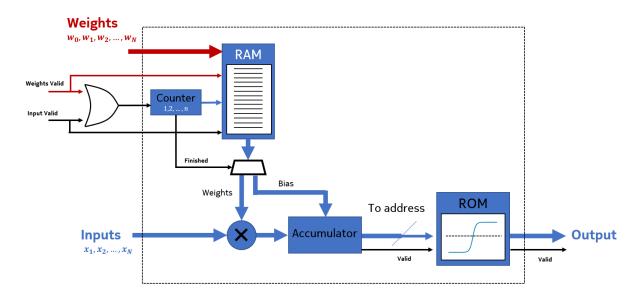

| 29  | Implémentation sur FPGA d'un neurone, avec en rouge la logique pour la             |

|     | mise à jour des poids et en noir les signaux de contrôle                           |

| 30  | Captures de simulation fonctionnelle (a) d'un neurone (b) du réseau de             |

| 0.1 | neurones                                                                           |

| 31  | Schéma de notre banc de test avec un processuer logique Microblaze, le             |

| 20  | réseau de neurone et un serveur web pour récupérer les spectres et les poids. lii  |

| 32  | Capture of the implemented neural network liii                                     |

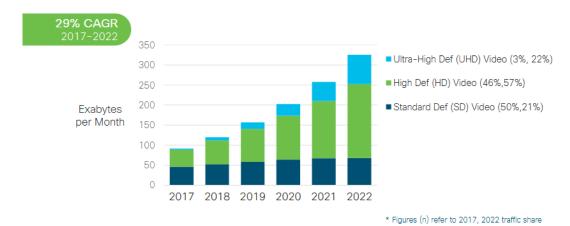

| 1.1 | Global IP traffic growth in Exabytes per Month measured and forecasted             |

|     | by Cisco. Measurements pulled from Virtual Networking Indexes of their             |

|     | respective years, and forecasts from the Virtual Networking Index 2017-            |

|     | 2022 [1]                                                                           |

| 1.2 | Impact and growth of video application traffic and influence of the defini-        |

|     | tion on this impact. Source [1]                                                    |

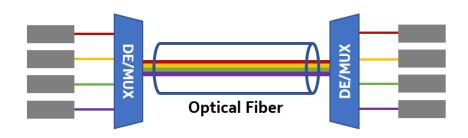

| 2.1 | Simple representation of the WDM technology                                        |

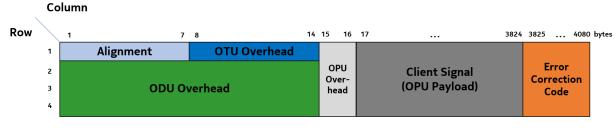

| 2.2 | Structure of an OTN frame                                                          |

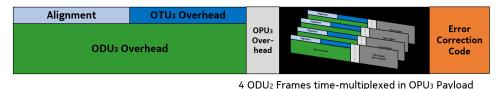

| 2.3 | Representation of an OTU3 frame transporting 4 ODU2 frames using time              |

|     | multiplexing                                                                       |

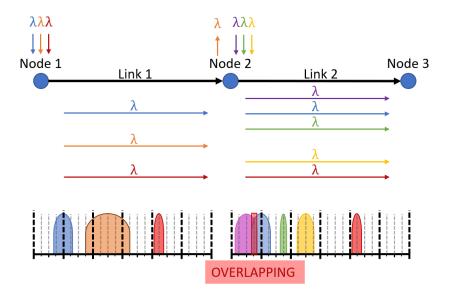

| 2.4  | Example of spectral slot allocation in a)fixed and b)flex grid scenario, with a 12.5GHz granularity for b)                                                  | 9  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.5  | Example of a spectral slot assignment causing overlapping in a flex-grid                                                                                    |    |

|      | scenario                                                                                                                                                    | 9  |

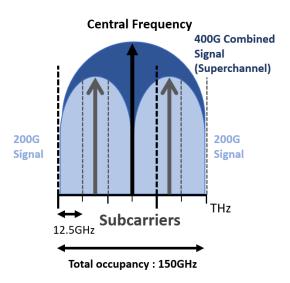

| 2.6  | Example of a super channel in the flexgrid, where two 200G signals are                                                                                      |    |

|      | combined into a 400G super channel                                                                                                                          | 10 |

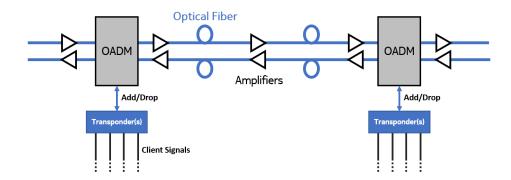

| 2.7  | Representation of an optical transport networkd data plane                                                                                                  | 11 |

| 2.8  | Optical line in transport networks, with Transponders, OADMs and amplifiers                                                                                 | 11 |

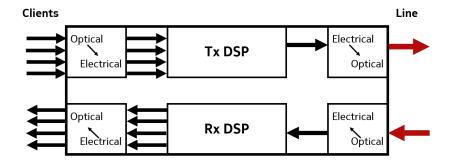

| 2.9  | Basic representation of an optical transponder                                                                                                              | 12 |

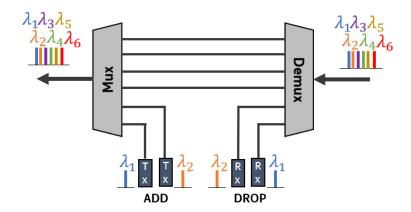

| 2.10 | Implementation example of a parallel OADM                                                                                                                   | 12 |

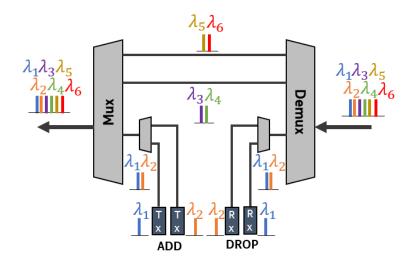

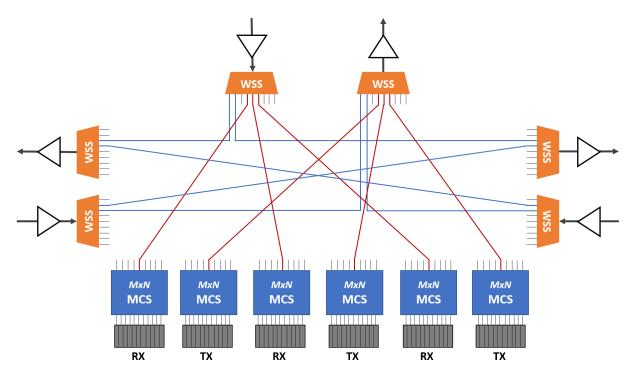

| 2.11 | Implementation examples of a parallel modular OADM                                                                                                          | 13 |

| 2.12 | Implementation example of a parallel two-degree OADM                                                                                                        | 13 |

| 2.13 | Example architecture of a 3-degree CDC ROADM with example signals.                                                                                          |    |

|      | Blue signals are signals going through the ROADM to be dropped at a                                                                                         |    |

|      | later point and red signals are signals added and dropped in the device $$ . $$                                                                             | 14 |

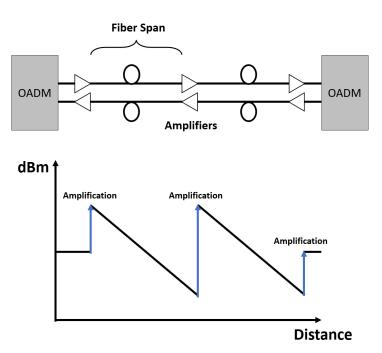

| 2.14 | Optical link between two OADMs, with amplifiers placed at entry and exit                                                                                    |    |

|      | points of the equipment and in the middle of the link. The fiber portion                                                                                    |    |

|      | between two amplifiers is called a fiber span                                                                                                               | 15 |

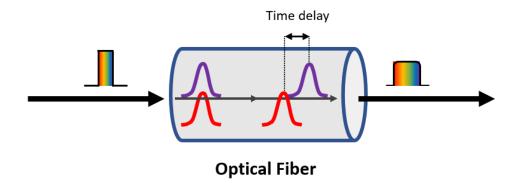

| 2.15 | Representation of the effects of Chromatic Dispersion                                                                                                       | 16 |

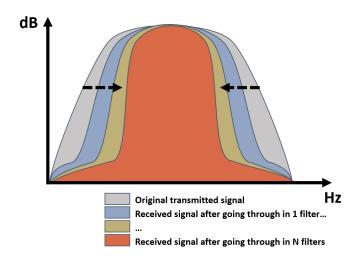

| 2.16 | Effects of cascaded filtering on the spectrum of a received signal                                                                                          | 17 |

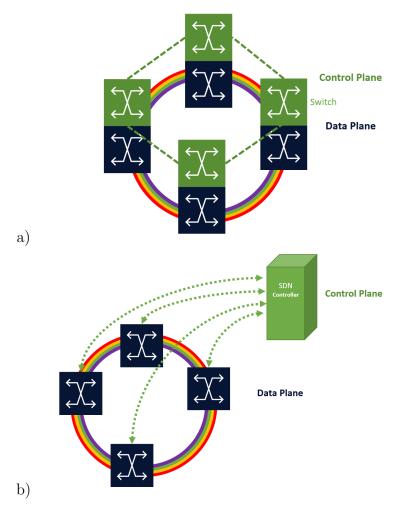

| 2.17 | Simple representation of the a) traditional control plane architecture and                                                                                  |    |

|      | b) the SDN architecture                                                                                                                                     | 18 |

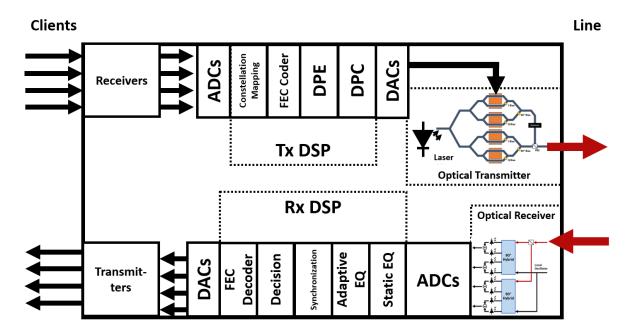

| 2.18 | Representation of an optical transponder                                                                                                                    | 21 |

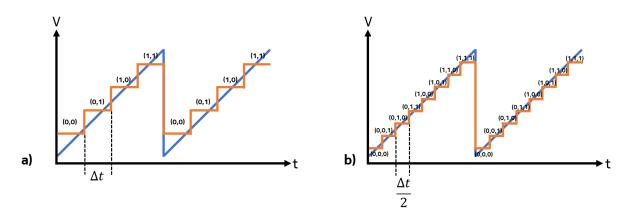

| 2.19 | Basic representation of the operation of a DAC and an ADC converting a ramp signal (the blue line), with (a) 2-bit resolution and $\Delta t$ sampling rate, |    |

|      | (b) 3-bit resolution and double sampling rate. The orange line represents                                                                                   |    |

|      | the output waveform from the DAC and the ADC conversion is represented                                                                                      |    |

|      | by the bit vectors                                                                                                                                          | 22 |

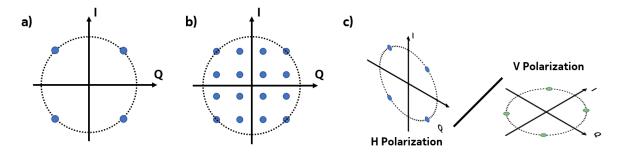

| 2.20 | Representation of (a) the QPSK, (b) 16-QAM and (c) PM-QPSK modula-                                                                                          |    |

|      | tion formats                                                                                                                                                | 23 |

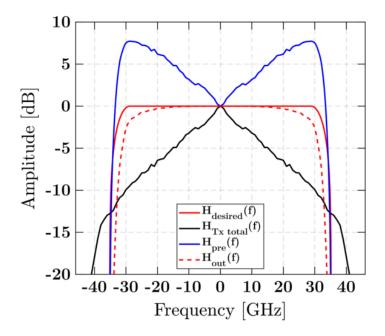

| 2.21 | Representation of the digital pre-emphasis processing. $H_{desired}$ represents                                                                             |    |

|      | the ideal signal spectrum, $H_{TxTotal}$ the transfer function of the DAC, $H_{pre}$                                                                        |    |

|      | the transfer function of the DPE filter and $H_{out}$ the resulting spectrum                                                                                |    |

|      | after the DPE                                                                                                                                               | 24 |

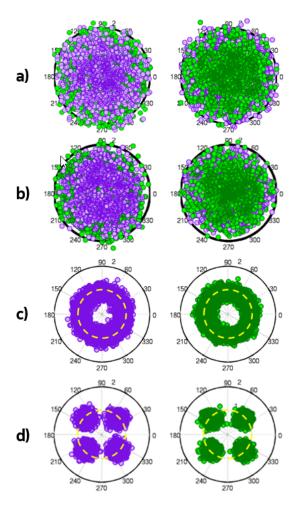

| 2.22       | Representation of DSP steps on the reception of a PM-QPSK signal, with on the left the Horizontal polarization and on the right the Vertical one. (a) is the signal coming from the ADC, (b) is the signal after CD compensation, (c) is the signal after CMA, and (d) is after carrier and phase recovery | 25 |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

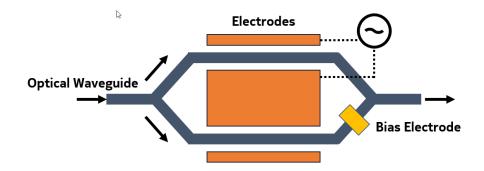

| 2.23       | Basic structure of a Mach-Zender Modulator                                                                                                                                                                                                                                                                 | 27 |

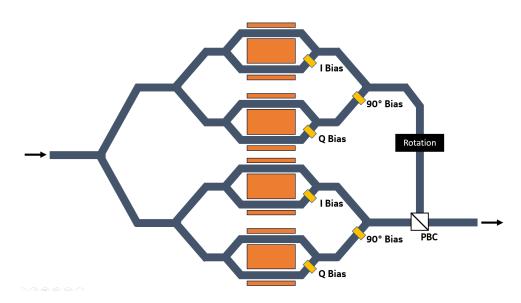

| 2.24       | Coherent I/Q modulator using multiple MZMs                                                                                                                                                                                                                                                                 | 27 |

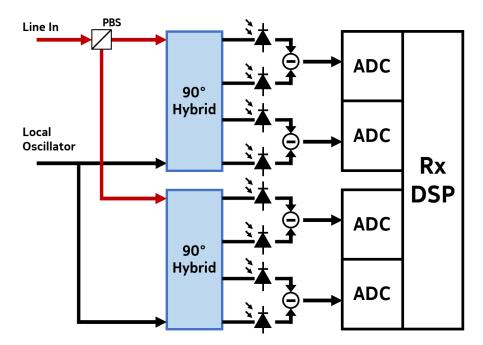

| 2.25       | Representation of a coherent receiver                                                                                                                                                                                                                                                                      | 28 |

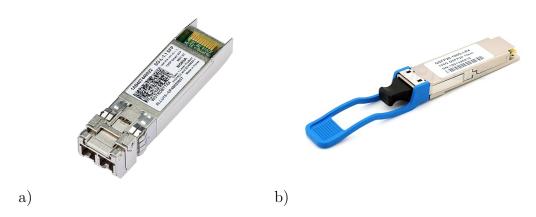

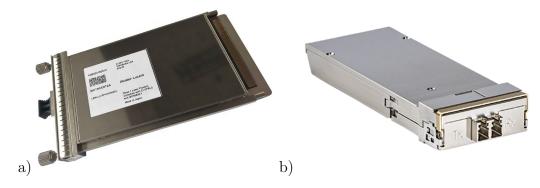

| 2.26       | Photograph of (a) a SFP Module and (b) a QSFP module                                                                                                                                                                                                                                                       | 29 |

| 2.27       | Photograph of (a) a CFP module, (b) a CFP2 module                                                                                                                                                                                                                                                          | 29 |

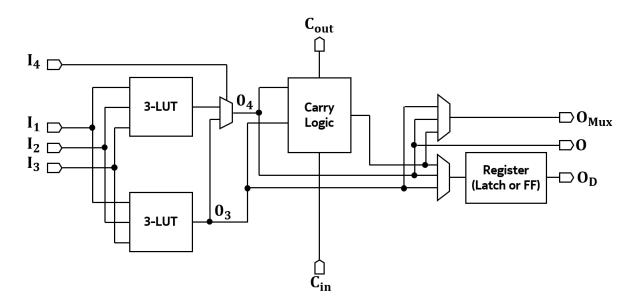

| 3.1        | Architecture example of a CLB with four inputs                                                                                                                                                                                                                                                             | 33 |

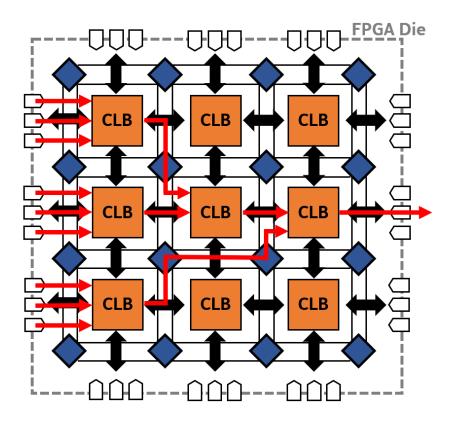

| 3.2        | Representation of the routing inside an FPGA. The blue diamonds represent the switches, the red arrows show a dataflow example, coming in the FPGA, processed by and routed to the CLBs and going out the die                                                                                              | 34 |

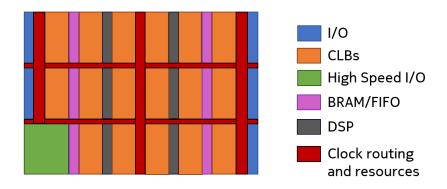

| 3.3        | Example layout of an FPGA                                                                                                                                                                                                                                                                                  | 36 |

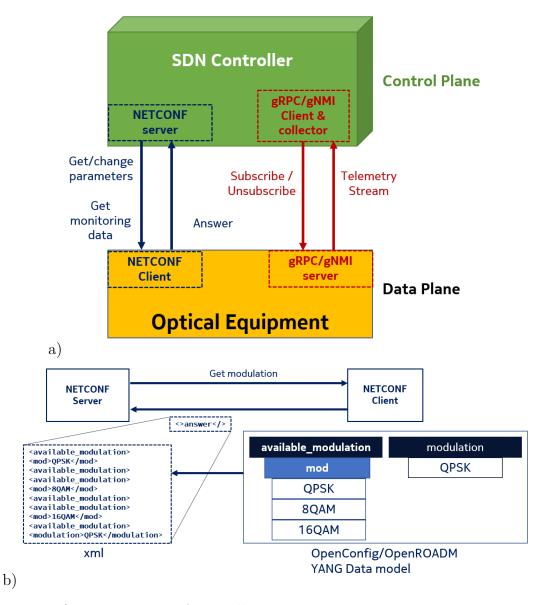

| 3.4        | a)Representation of controller-equipment communication b)Example of a server asking a client to give him his list of modulation formats and the current format in use. The answer sent to the server is coded into an xml file for this example, but the answer can be coded in any language the           |    |

|            | protocol for server/client communication supports                                                                                                                                                                                                                                                          | 40 |

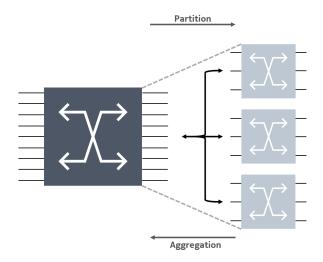

| 3.5        | Base principle of hardware virtualization using partition and aggregation .                                                                                                                                                                                                                                | 41 |

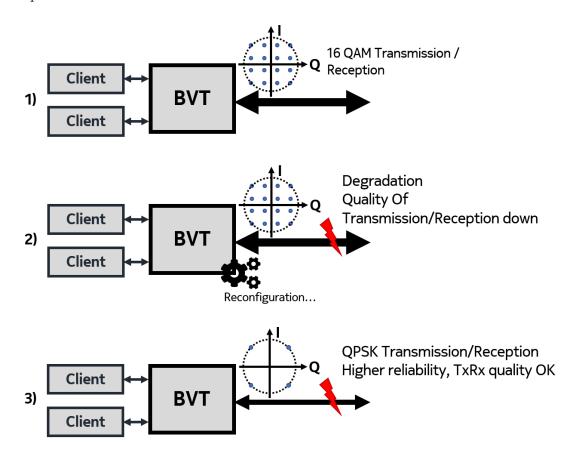

| 3.6<br>3.7 | Example representation of a VON in an optical network with VNFs Classical use case for BVTs, decreasing the modulation format order to increase the transmission/reception resiliency to degradations in the optical                                                                                       | 42 |

|            | path                                                                                                                                                                                                                                                                                                       | 43 |

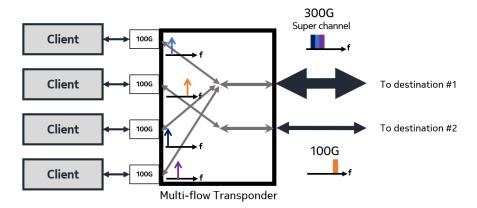

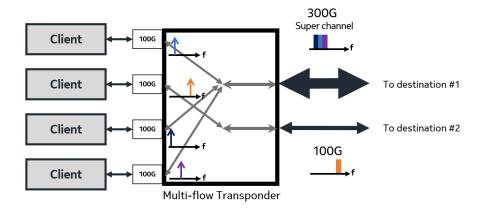

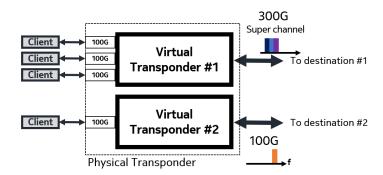

| 3.8        | Representation of the principle of a multi-flow transponder                                                                                                                                                                                                                                                | 46 |

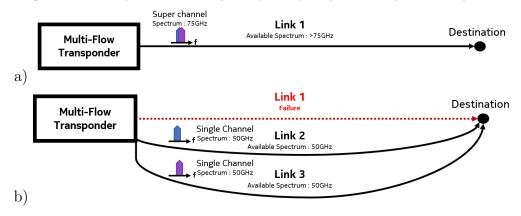

| 3.9        | Restoration after a link failure using a multi-flow transponder                                                                                                                                                                                                                                            | 46 |

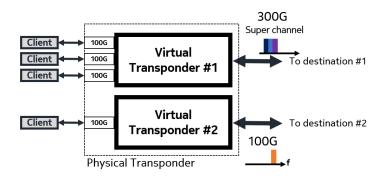

| 3.10       | Representation of how the multi-flow transponder in Figure 3.8 can be virtualized into two virtual optical transponders by the control plane                                                                                                                                                               | 47 |

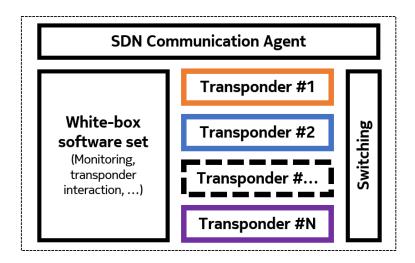

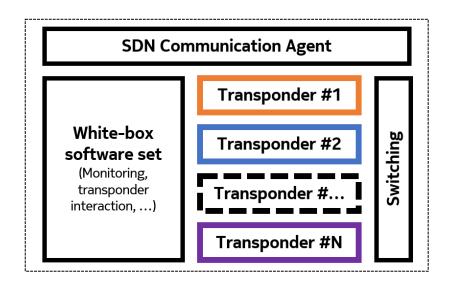

| 3.11       | Representation example of a white box using transponders, each one of them possibly from different vendors. An software agent handles communication with the control plane, and software helps handling and monitoring                                                                                     |    |

|            | the array of transponders                                                                                                                                                                                                                                                                                  | 48 |

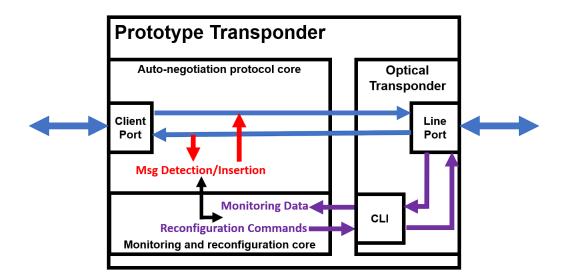

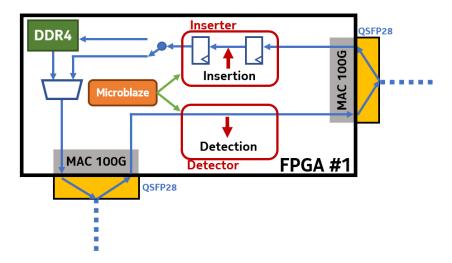

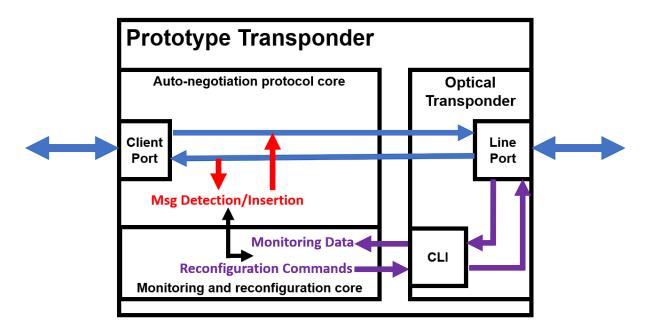

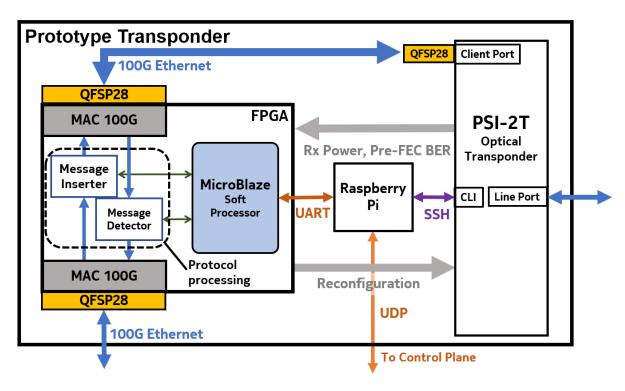

| 4.1  | bilities                                                                                                                                                                                                                 | 54       |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

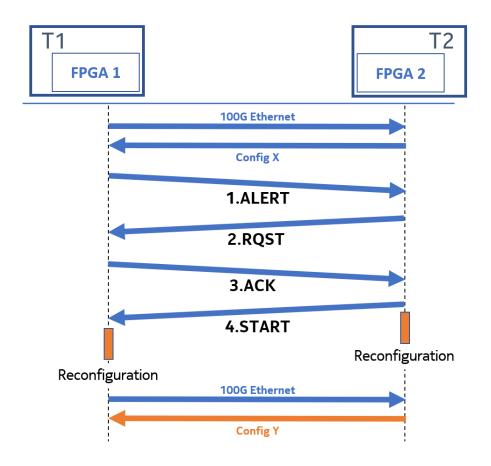

| 4.2  | Sequence of operations of our auto-negotiation protocol                                                                                                                                                                  | 55       |

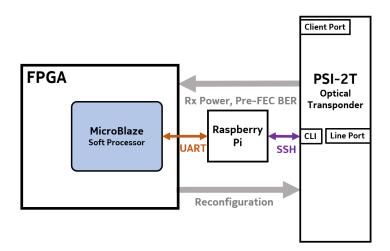

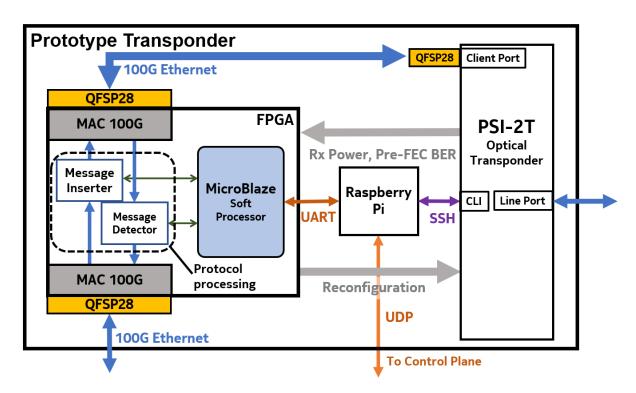

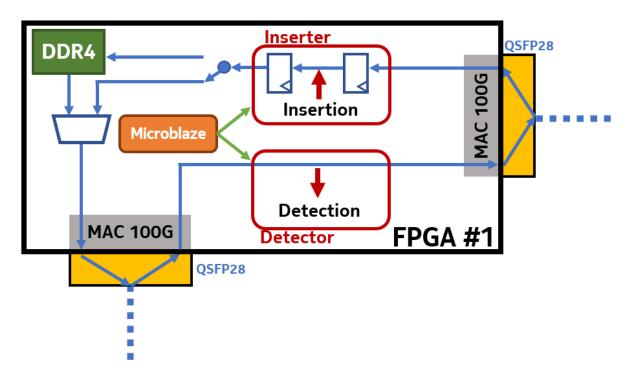

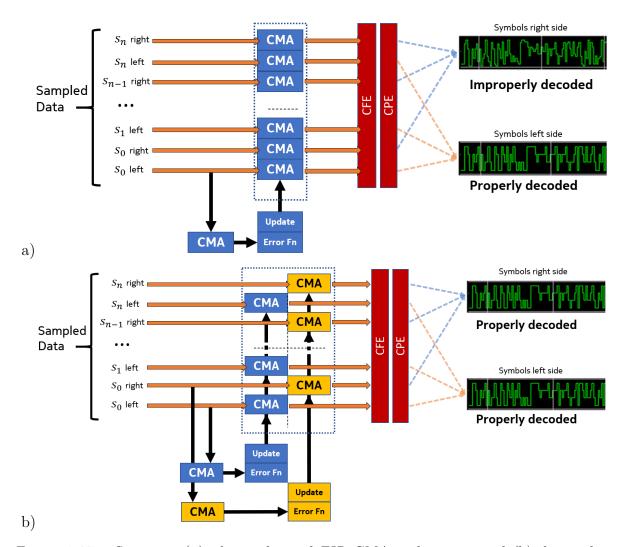

| 4.3  | Schematic representation of the real-time implementation of our auto-negotiatic protocol, that will be integrated with an optical transponder in the full prototype (Figure 4.1)                                         | on<br>57 |

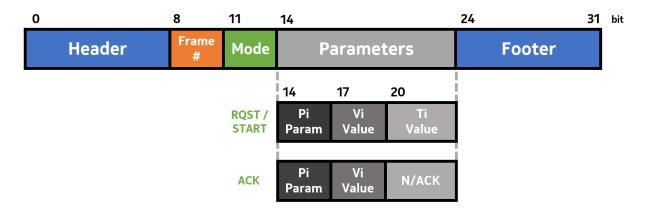

| 4.4  | Composition of the frames of the protocol in our implementation                                                                                                                                                          | 58       |

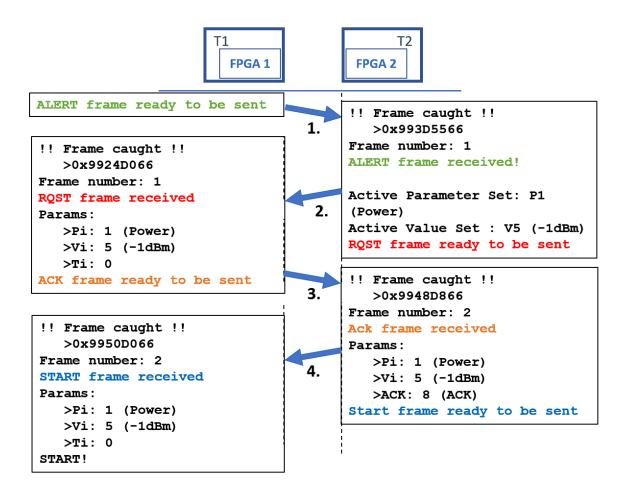

| 4.5  | Log extracts of the MicroBlaze processor on the FPGA cards during protocol operations. Indexes refer to Figure 4.2                                                                                                       | 59       |

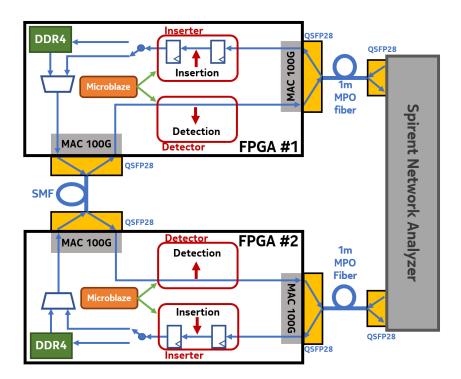

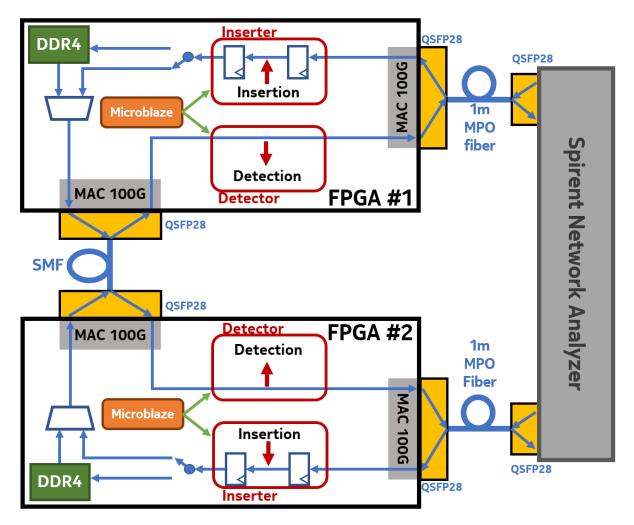

| 4.6  | Representation of our setup to validate our protocol implementation from 4.6, using two FPGA boards and one Spirent Network Analyzer to generate traffic and measure packet loss and latency                             | 60       |

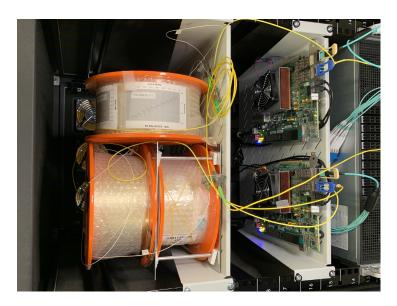

| 4.7  | Photograph of the setup with the two FPGA boards connected to each other and separated by 10km SMF. The Spirent is not pictured but is connected to the FPGA with the MPO (Multi-Fibre Push On, blue on the photo) fiber | 61       |

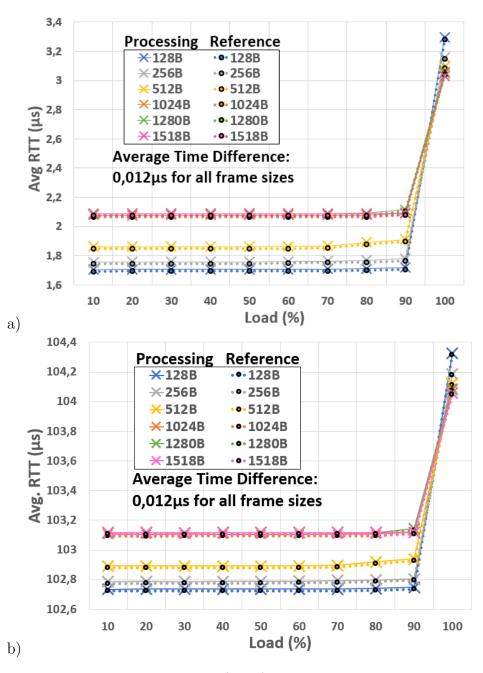

| 4.8  | Average Round Trip Time (RTT) in µs for frame sizes from 128 bytes to 1518 bytes, as a function of port load in %. The two FPGAs are separated by a) 2m, b) 10km SMF                                                     | 62       |

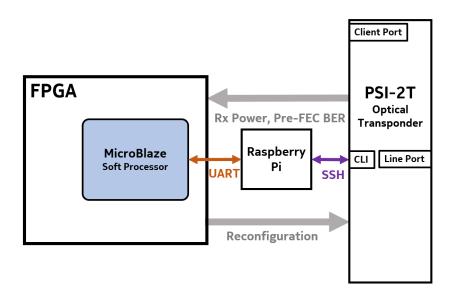

| 4.9  | Embedded monitoring and decision making prototype for commercial transponder Nokia PSI-2T                                                                                                                                | -<br>64  |

| 4.10 |                                                                                                                                                                                                                          | 66       |

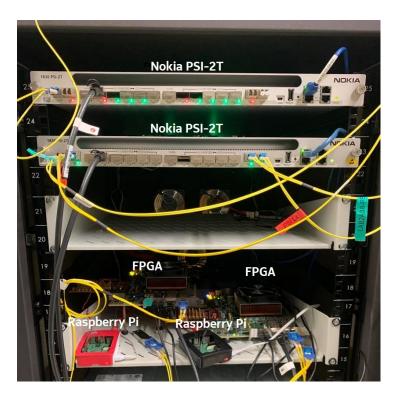

| 4.11 | Annotated photograph of the setup, with two FPGA boards, two PSI-2Ts and two Raspberry Pi, connected to the Spirent (not pictured)                                                                                       | 67       |

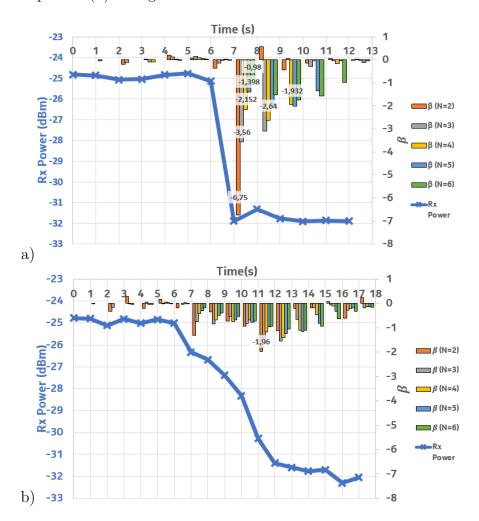

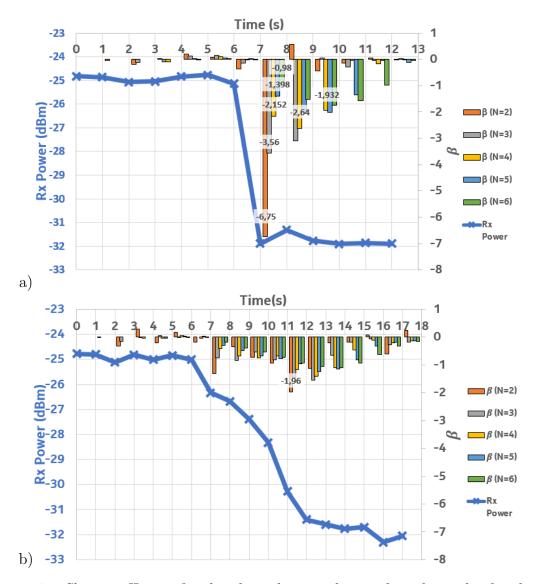

| 4.12 | Slope coefficient $\beta$ value depending on the number of samples for the computation for a (a) fast, (b) slow Rx Power degradation                                                                                     | 68       |

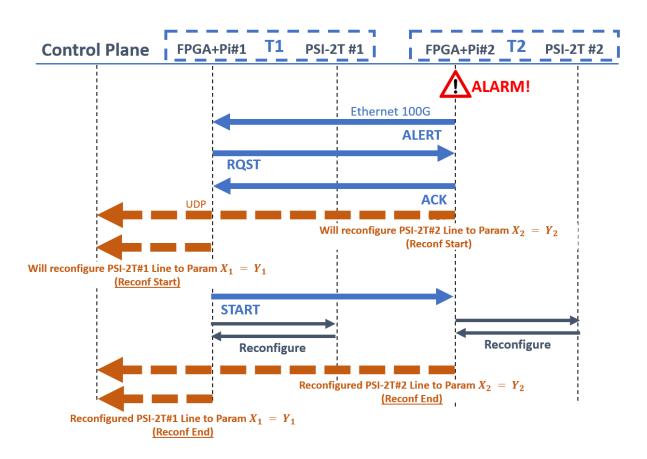

| 4.13 | Example of an auto-negotiation procedure between two of our prototype optical transponder (see Figure 4.15) with the integration of notifications                                                                        | 60       |

| 111  | to the control plane                                                                                                                                                                                                     | 69       |

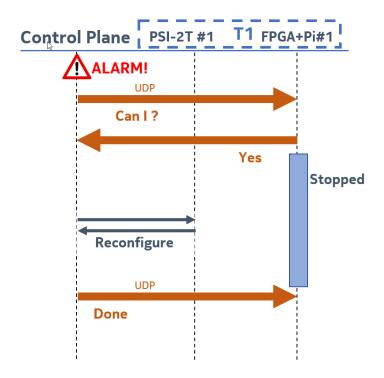

| 4.14 | Example of a centralized reconfiguration using the UDP message to stop our prototype from creating conflicts                                                                                                             | 70       |

| 4.15 | Representation of the prototype (presented in Figure 4.1) full implementation, with FPGA, Raspberry Pi and Nokia PSI-2T commercial optical transponder                                                                                                                                                                                                                          | 71 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

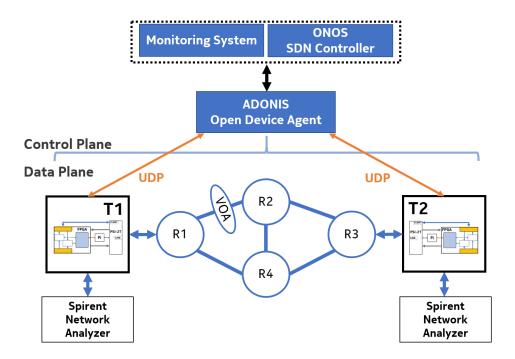

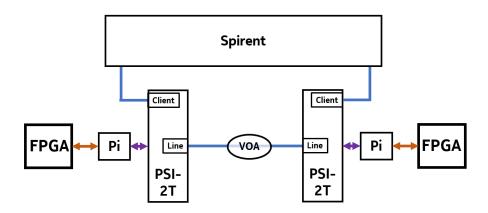

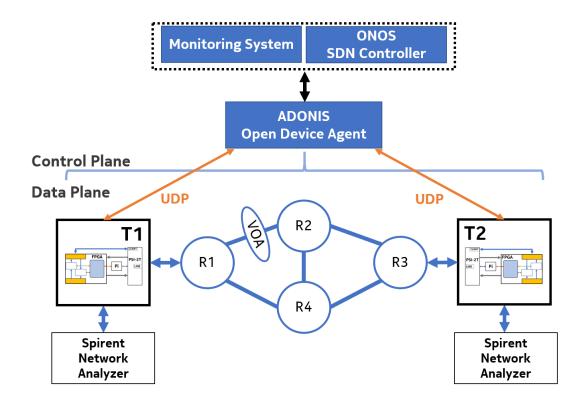

| 4.16 | Integration of our real-time prototype transponder from Figure 4.15 with auto-negotiation inside a network testbed                                                                                                                                                                                                                                                              | 72 |

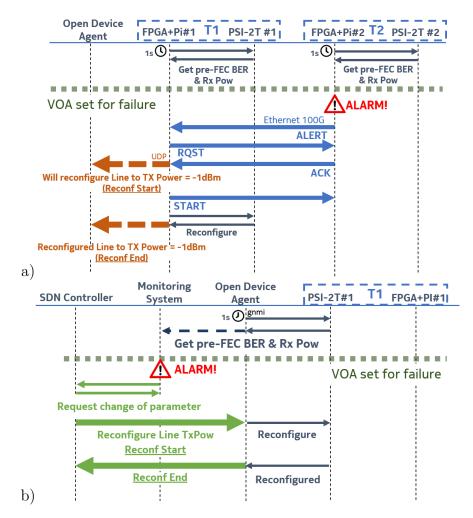

| 4.17 | Workflow for validation in a network testbed, with (a) FPGA-controlled setup and (b) SDN controller-controlled setup                                                                                                                                                                                                                                                            | 73 |

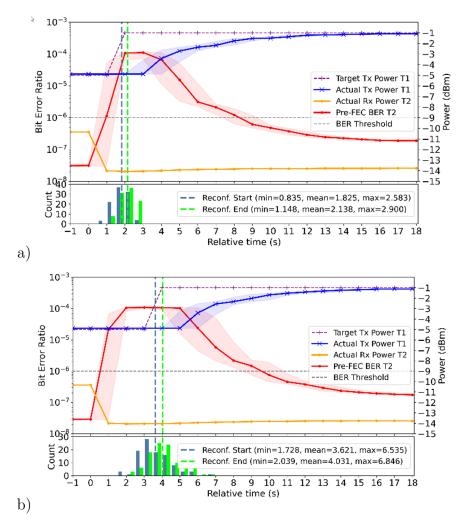

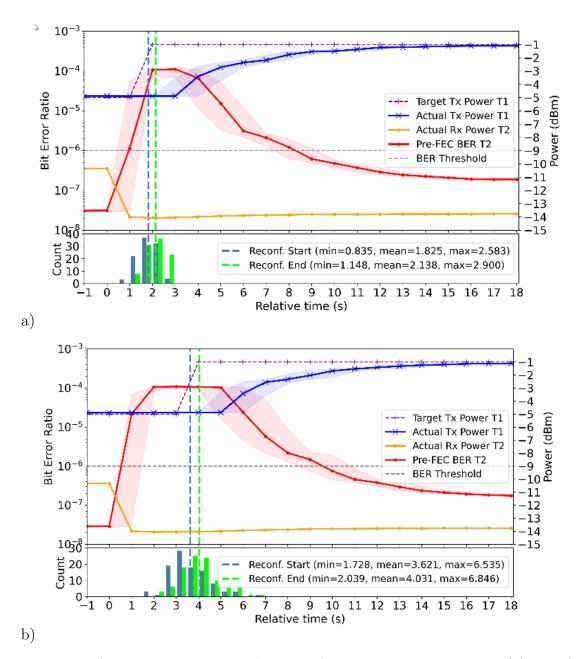

| 4.18 | Aggregated experimental results for auto-negotiation setup (a) and SDN setup (b). At the top of each figure we plotted the median values of the monitored metrics. The confidence interval of the pre-FEC BER and output power corresponds to the 15.8 and 84.2 quantiles. At the bottom we plotted the histogram for the notification messages "Reconf. Start" and "Reconf.    |    |

|      | End". Timing results are also gathered in Table 4.2                                                                                                                                                                                                                                                                                                                             | 75 |

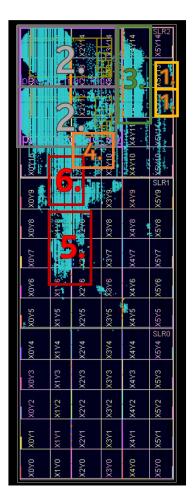

| 4.19 | Representation of the resource utilization of our design in the FPGA die $$ .                                                                                                                                                                                                                                                                                                   | 77 |

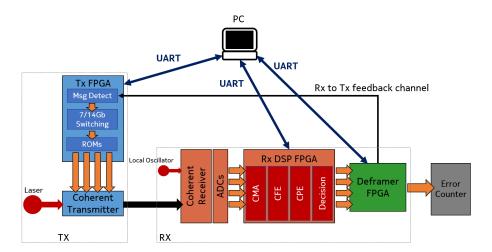

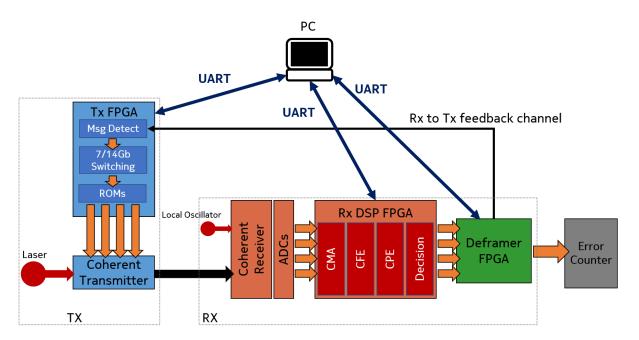

| 4.20 | Experimental setup for the synchronous hitless change of baud-rate using the developed protocol. It is composed of a coherent transmitter (Tx) and a coherent receiver (Rx). A feedback channel is setup between the Rx and the Tx for bidirectional auto-negotiation protocol operations. All the FPGA boards in the setup are managed using an UART link that is connected in |    |

|      | our experiment to a computer                                                                                                                                                                                                                                                                                                                                                    | 78 |

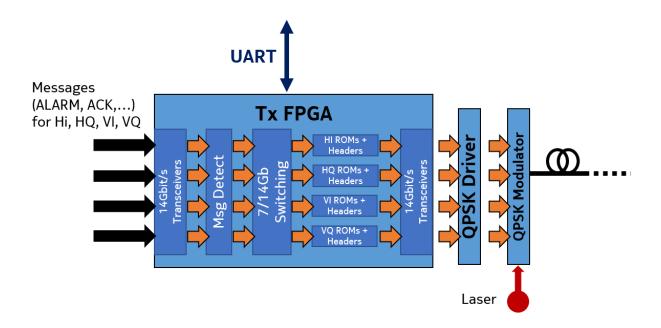

| 4.21 | Representation of the variable baud-rate transmitter                                                                                                                                                                                                                                                                                                                            | 79 |

| 4.22 | Photograph of the variable baud-rate transmitter                                                                                                                                                                                                                                                                                                                                | 80 |

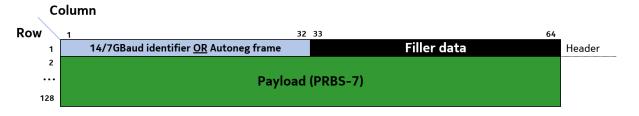

| 4.23 | Frame structure sent by the transmitter for this experiment                                                                                                                                                                                                                                                                                                                     | 80 |

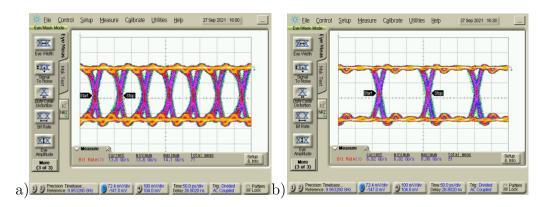

| 4.24 | Eye diagram of the optical signal sent by the transmitter at (a) 14GBaud                                                                                                                                                                                                                                                                                                        |    |

|      | and (b) 7GBaud                                                                                                                                                                                                                                                                                                                                                                  | 81 |

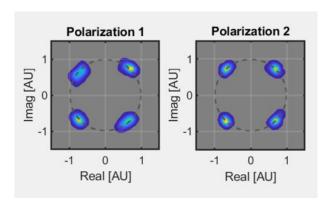

| 4.25 | Constellation of the PM-QPSK signal, for the Horizontal and Vertical po-                                                                                                                                                                                                                                                                                                        | 01 |

|      | larizations, at 14GBaud                                                                                                                                                                                                                                                                                                                                                         | 81 |

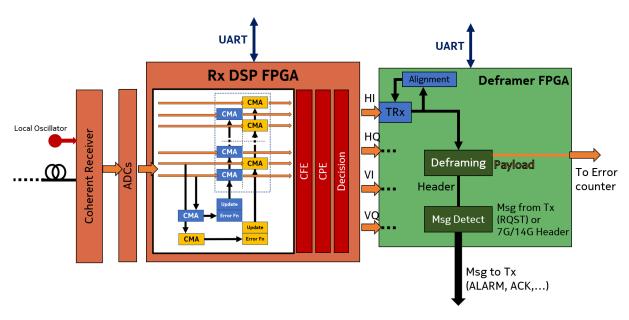

| 4.26 | Full representation of the Receiver with the coherent receiver and the ADC, the DSP FPGA and the deframer FPGA board                                                                                                                                                                                                                                                            | 82 |

| 4.27 | Structure (a) of a traditional FIR-CMA architecture and (b) the used architecture for the real-time receiver of this experiment. On the right side of both figures, $s_0$ is given as an example of a recovered symbol at half                                                                                                                                                  |    |

|      | baud-rate                                                                                                                                                                                                                                                                                                                                                                       | 83 |

| 4.28 | Capture of header detection and removal by the deframing logic in simula-                                           |    |

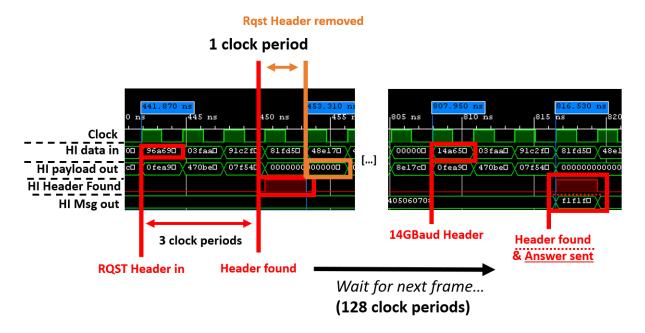

|------|---------------------------------------------------------------------------------------------------------------------|----|

|      | tion. The header in this example is the header indicating 14GBaud transmission. The clock period is 2.86ns (250MHz) | 96 |

| 4.00 | mission. The clock period is 2.86ns (350MHz)                                                                        | 86 |

| 4.29 |                                                                                                                     |    |

|      | logic in simulation. After the message is detected, we delay the answer until                                       | 96 |

| 4.00 | the next frame is received                                                                                          | 86 |

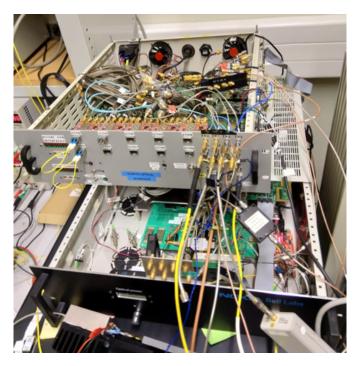

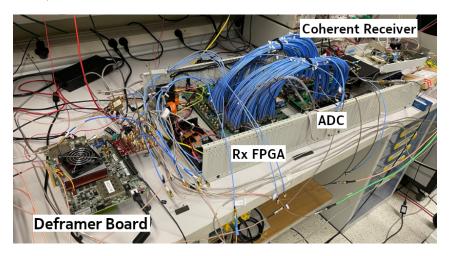

|      | Annotated photograph of the variable baud-rate receiver                                                             | 87 |

| 4.31 | Labview developed interface to pilot the deframer board, connected via                                              |    |

|      | UART                                                                                                                | 88 |

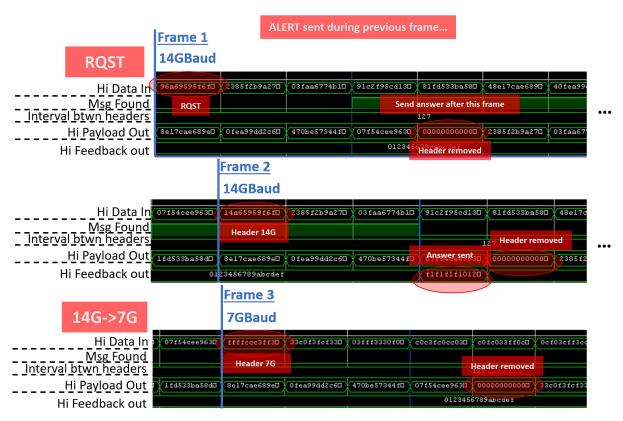

| 4.32 | Capture from the Deframer FPGA board showcasing a change of baudrate                                                |    |

|      | from 14GBaud to 7GBaud with the auto-negotiation protocol. The ALERT                                                |    |

|      | message was sent before the first pictured frame                                                                    | 89 |

| 4.33 | Capture from the Transmitter showcasing a change of baudrate from 14GB<br>aud $$                                    |    |

|      | to 7GB and synchronized with the auto-negotiation protocol. Below the cap-                                          |    |

|      | tures, we inserted oscilloscope captures of the eye diagram before and after                                        |    |

|      | the change of baudrate                                                                                              | 90 |

| 4.34 | Capture from the Receiver showcasing a change of baudrate from 7GBaud                                               |    |

|      | to 14GBaud                                                                                                          | 90 |

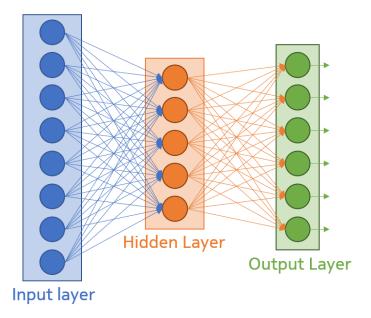

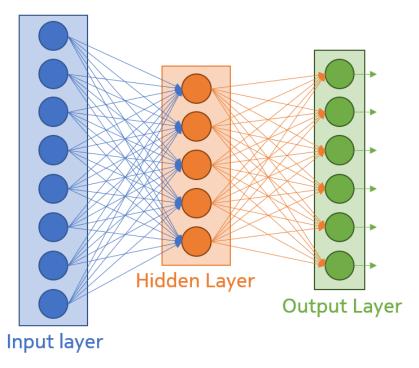

| 5.1  | Basic structure of an Artificial Neural Network with a single layer of five                                         |    |

|      | neurons in the hidden layer, eight inputs and six outputs                                                           | 94 |

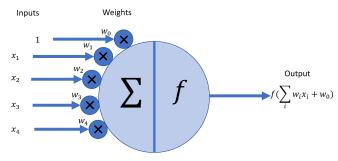

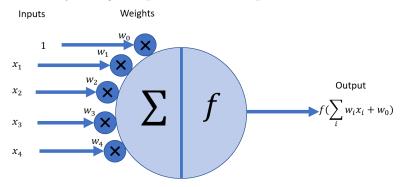

| 5.2  | Structure of a neuron of an artificial neural network with four inputs. Inputs                                      |    |

|      | are multiplied by their weights, summed altogether with an additional bias                                          |    |

|      | and processed through an activation function                                                                        | 94 |

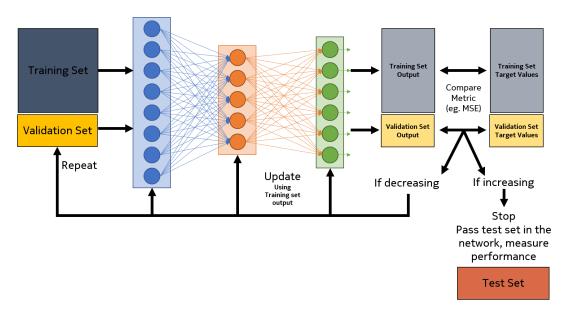

| 5.3  | Schematization of the training of a neural network                                                                  | 96 |

| 5.4  | Optical spectrum on a single channel in highly linear and highly nonlinear                                          |    |

|      | regime. The modulated channel is showed with the black line. In blue is                                             |    |

|      | represented the white linear noise, in red the nonlinear effects, and in green                                      |    |

|      | is the received spectrum with contributions of both linear and nonlinear                                            |    |

|      | effects                                                                                                             | 97 |

| 5.5  | Representation of the SNR of a received spectrum as a function of the                                               |    |

|      | launch power. In blue is shown the highly linear regime and in red the                                              |    |

|      | highly nonlinear regime. Atop the bell curve is the optimal launch power                                            |    |

|      | to maximize the SNR                                                                                                 | 98 |

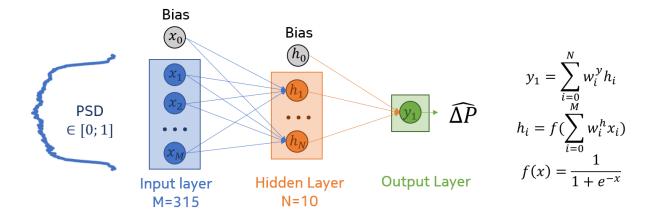

| 5.6  | Proposed Artificial Neural Network for power monitoring. The input is                            |

|------|--------------------------------------------------------------------------------------------------|

|      | a normalized Power Spectral Density (PSD) of a single channel on 315                             |

|      | samples. The hidden layer is composed of a single layer of ten neurons. The                      |

|      | single output produces an estimation of the power correction to apply to                         |

|      | maximize the SNR $\widehat{\Delta P}$ . Biases are always equal to one                           |

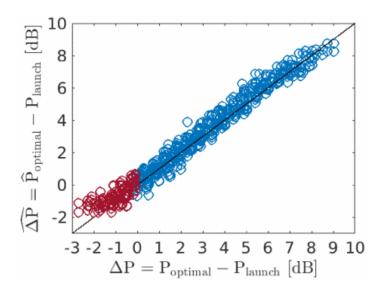

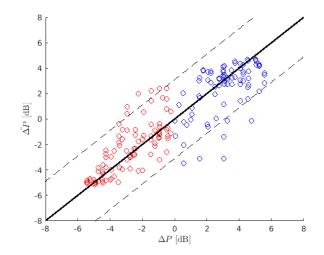

| 5.7  | Neural network self-test prediction scattered plot. The black line represents                    |

|      | the perfect theoretical power correction $\Delta P$ and circles represent the pre-               |

|      | diction $\widehat{\Delta P}$ out of the ANN. Blue circles represents when the system was         |

|      | operating in the linear regime, and in red when the system was operating                         |

|      | in nonlinear regime                                                                              |

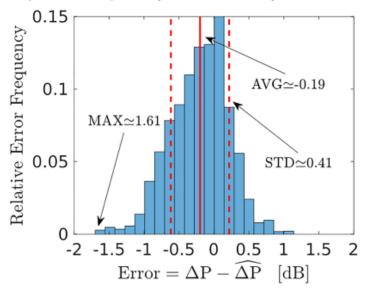

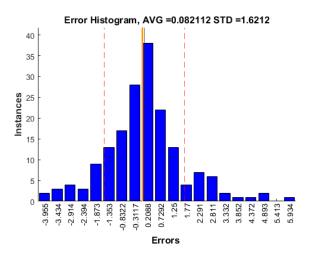

| 5.8  | Error histogram of the ANN, AVG labeling the average error, STD the                              |

|      | standard deviation and MAX the maximum absolute error                                            |

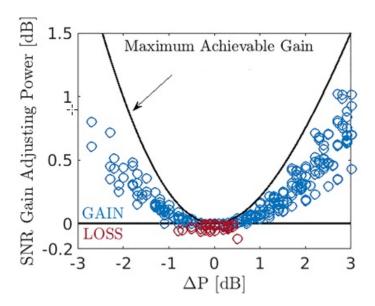

| 5.9  | Resulting gain in SNR when applying the predicted power correction $\widehat{\Delta P}$ ,        |

|      | compared to the maximum achievable gain when applying the ideal power                            |

|      | correction $\Delta P$ . The blue circles show when the correction results in a SNR               |

|      | gain, and in red when it results in a loss. Maximum achievable SNR gain                          |

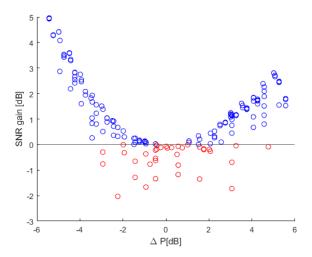

|      | with the test set is around 1dB, and loss around -0.1dB 101                                      |

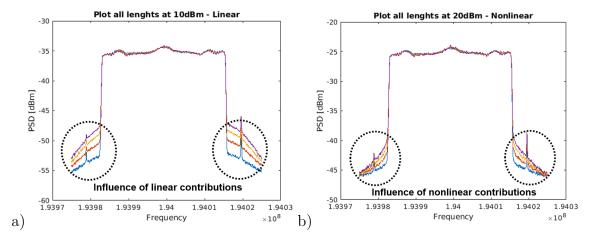

| 5.10 | Plot of the PSD for all lengths at (a) 10dBm launch power, (b) at 20dBm                          |

|      | launch power                                                                                     |

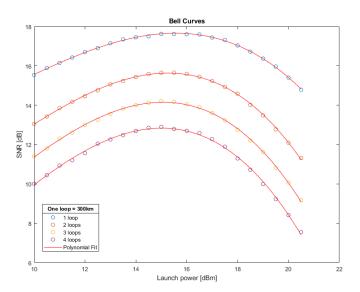

| 5.11 | Plot of the SNR as a function of then launch power with its associated bell                      |

|      | curves for distances from 300 to 1200km. The solid lines represent the fit                       |

|      | line from a polynome of degree 3                                                                 |

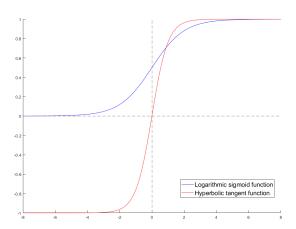

| 5.12 | Plot of the logarithmic sigmoid and the hyperbolic tangent functions $104$                       |

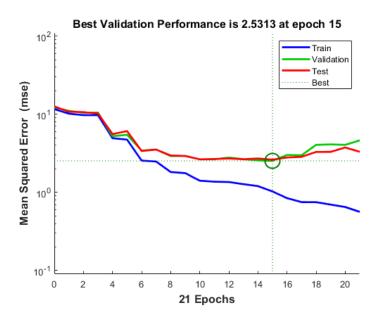

| 5.13 | Plot of the evolution of the neural network performance on the data set                          |

|      | as more epochs are being realized. The green circle represents the point at                      |

|      | which the early stopping mechanism is triggered                                                  |

| 5.14 | Plot of the predicted result $\widehat{\Delta P}$ from the neural network as a function of       |

|      | the the expected result $\Delta P$ . The blue dots represent when the system was                 |

|      | in highly linear regime and the red dots when the system was in highly                           |

|      | nonlinear regime. The black line represents the ideal fit line where $\Delta P =$                |

|      | $\widehat{\Delta P}$ , and dashed lines the standard deviation of the neural network output. 105 |

| 5.15 | Error histogram after a training of the neural network. Orange vertical line                     |

|      | shows 0 error                                                                                    |

| 5 16 | Resulting gain in terms of SNR after a training of the neural network 106                        |

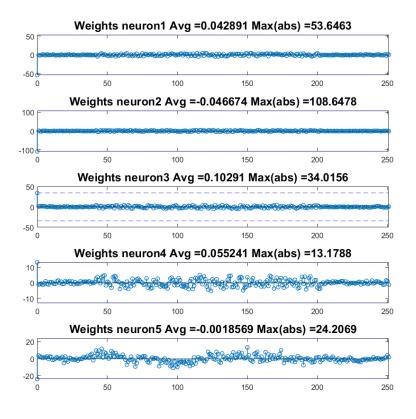

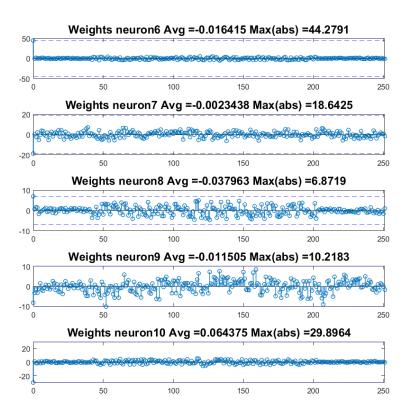

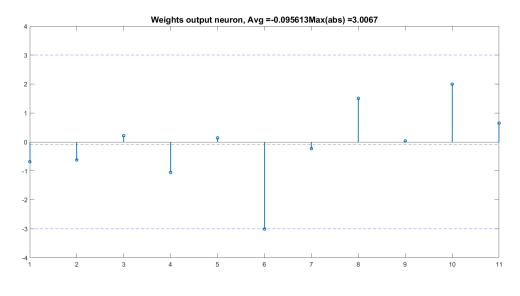

| 5.17 | Plot of the weights (a) for the ten neurons of the hidden layer, (b) for the               |     |

|------|--------------------------------------------------------------------------------------------|-----|

|      | output layer neuron, with their average value and their maximum absolute                   |     |

|      | value (index 0 is the bias weight $w_0^i$ as noted in Figure 5.6, 1 is the weight          |     |

|      | for the first input $w_1^i$ etc)                                                           | 109 |

| 5.18 | Schematization of the logical implementation of a neuron. Control signals                  |     |

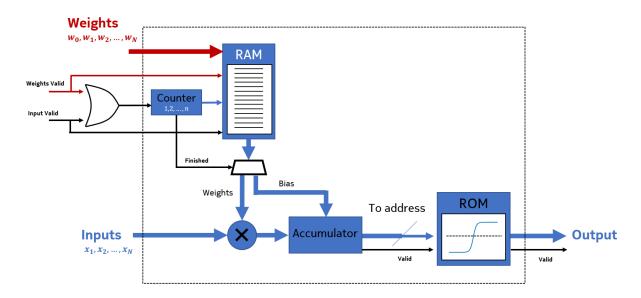

|      | are represented in black                                                                   | 109 |

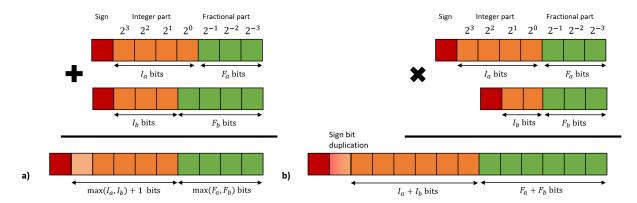

| 5.19 | Rules of the signed fixed point arithmetic for (a) addition and (b) multi-                 |     |

|      | plication                                                                                  | 110 |

| 5.20 | Representation of the adaptations made on the bit vector from the accumu-                  |     |

|      | lator to fetch the value from the value from the activation function ROM.                  |     |

|      | As an example we took initial signed vectors with four bits integer part                   |     |

|      | and three bits fractional part and a ROM depth of 6                                        | 112 |

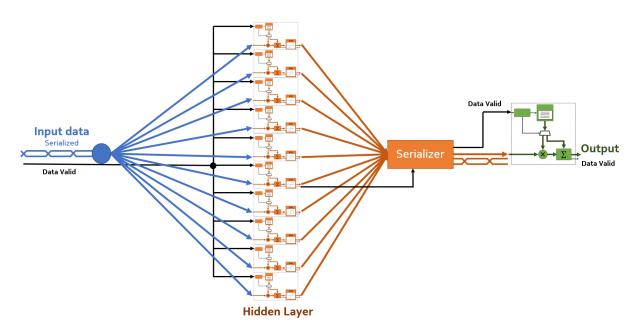

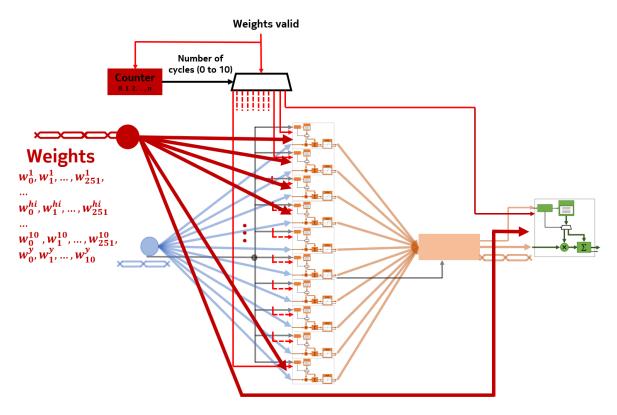

| 5.21 | Structure of the neural network logical implementation for FPGA. Neurons                   |     |

|      | in the hidden layer refer to the neuron structure presented in Figure 5.18,                |     |

|      | output layer neuron is the same, but with no activation function ROM. $$ . $$ .            | 112 |

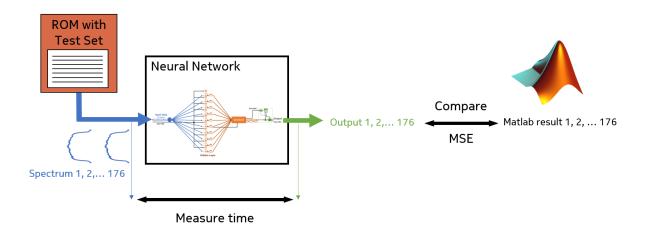

| 5.22 | Simulation setup to validate our neural network and measure its perfor-                    |     |

|      | mance in terms of timing and precision                                                     | 114 |

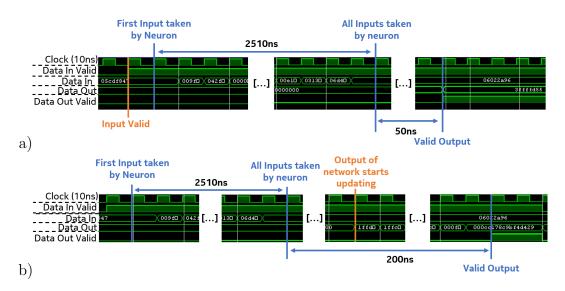

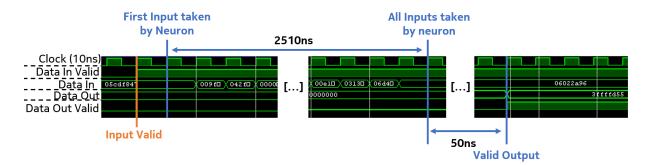

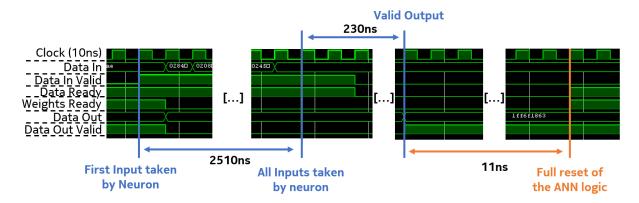

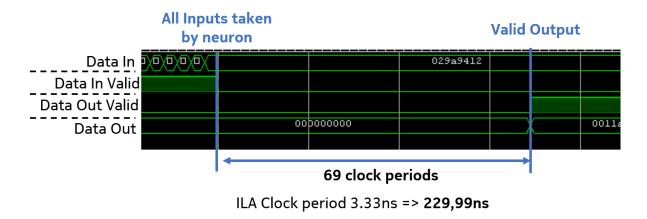

| 5.23 | Extract of the simulation results focused on a neuron of the network. $\ . \ . \ .$        | 115 |

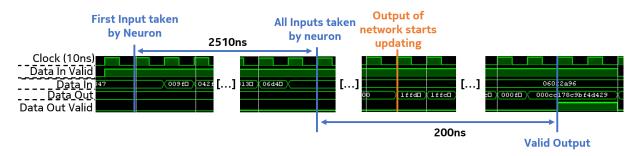

| 5.24 | Extract of the simulation result of the FPGA neural network                                | 115 |

| 5.25 | New logical implementation of the neuron allowing for weights re-writing. $\boldsymbol{.}$ | 119 |

| 5.26 | Highlight on the weight update logic for the FPGA ANN                                      | 120 |

| 5.27 | Simulation extracts of the validation of the logical neural network wrapper.               | 121 |

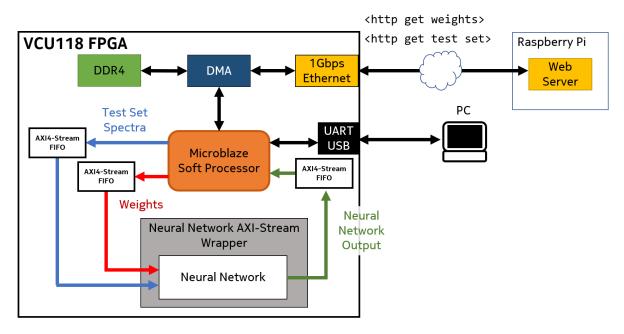

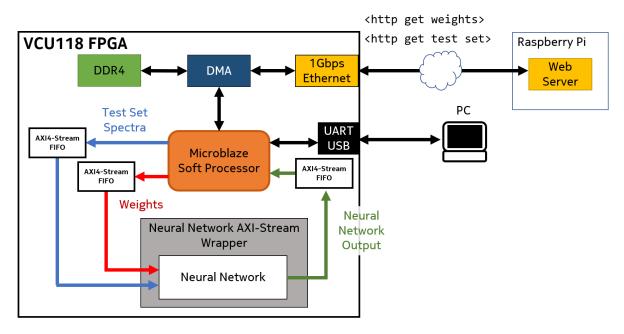

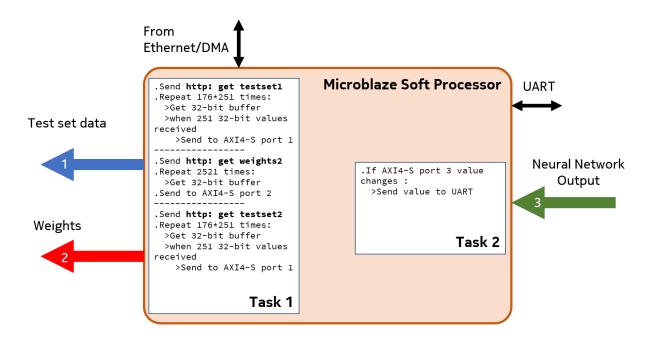

| 5.28 | Schematization of our setup with a Microblaze soft processor, the logical                  |     |

|      | neural network and a web server to collect test sets and weights                           | 122 |

| 5.29 | Tasks developed in the Microblaze to handle our validation scenario                        | 123 |

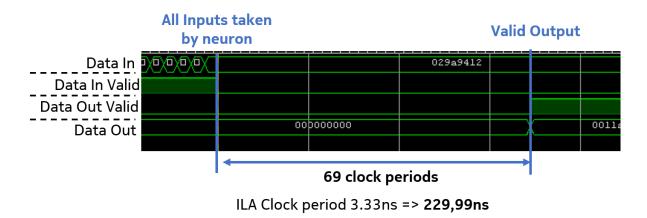

| 5 30 | Capture of the implemented neural network                                                  | 125 |

## LIST OF TABLES

| 1   | Taux de trames perdues en ‰ selon les tailles de trames à 100% de charge, pour (a) 2m de séparation entre les cartes et (b) 10km de séparation. Les trames perdues sont nulles pour toutes les autres charges                                                                                                                                                                                                                                                                                                                                    | xxxvi |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 2   | Erreur quadratique moyenne (MSE) de notre implementation FPGA du réseau de neurones comparé à celui généré dans Matlab pour différentes tailles en bit des poids et la fonction d'activation (width) et différents nombre de valeurs de fonction d'activation (depth)                                                                                                                                                                                                                                                                            | li    |

| 3   | Résultats d'implémentation récupérés du Microblaze. Un tick processeur correspond à 10ms                                                                                                                                                                                                                                                                                                                                                                                                                                                         | liii  |

| 4.1 | Frame loss in ‰ for multiple frame sizes from 128 bytes to 1518 bytes, at 100% port load with a) 2m, b) 10km SMF separating the two FPGAs. Frame loss is null for all other loads                                                                                                                                                                                                                                                                                                                                                                | 63    |

| 4.2 | Minimum, average and maximum time for notification messages Reconf. Start and Reconf. End for both setups                                                                                                                                                                                                                                                                                                                                                                                                                                        | 74    |

| 4.3 | Resource Utilization Report for our FPGA design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 77    |

| 5.1 | Mean Square Error of our FPGA Artificial Neural Network versus the same one generated in Matlab (lower is better) with various weights ROM width and activation function ROM depth and width                                                                                                                                                                                                                                                                                                                                                     | 116   |

| 5.2 | Summary of FPGA resource utilization of the implemented neural network design. Setup $(X,Y)/Z$ corresponds to the depth of the activation function ROM $(2^X$ values stored), the width of the activation function bit vectors $(Y \text{ bits})$ and the width of the weights bit vectors $(Z \text{ bits})$ respectively. BRAM (Block RAM, 18kb or 36kb) usage is given as an indicator, as the implementation tool will fall back into using only the URAM (Ultra RAM, 288kb) indicated for our case. In short, the BRAM usage corresponds to |       |

|     | the usage if the FPGA didn't have access to URAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 118   |

5.3 Validation and timing results from the Microblaze processor. A tick corresponds to 10ms. Ticks to receive whole test sets ommits the time to receive the HTTP header from the web server (1 tick for Initial Set, 2 for Final Set).124

### **ACRONYMS**

ADC Analog-to-Digital Converter. xxviii, 21, 22, 25, 27, 82, 84, 87

**ANN** Artificial Neural Network. 4, 20, 92–96, 98–101, 107, 113, 117, 118, 120–125, 127

BER Bit Error Rate. xxxiii, 19, 37, 50, 64, 65, 67, 72, 74

BVT Bandwidth Variable Transponder. 4, 42–44, 46

CMA Constant Modulus Algorithm. 26, 82, 84, 85

DAC Digital-to-Analog Converter. xxix, 21, 22, 24, 26, 102

**DDR** Double-Data-Rate. xxxv, 35, 57, 122

**DSP** Digital Signal Processing. xiii, xxix, xliii, 2, 11, 21, 22, 24–27, 29, 30, 35, 41, 44, 45, 47, 50, 53, 82, 85, 87, 117, 118

**EDFA** Erbium Doped Fiber Amplifier. 15, 102

**FEC** Forward Error Correction. xxix, 7, 23, 38, 45, 48, 64–67, 72, 74, 85, 88

**FIFO** First In First Out. li, 35, 121, 122

**FPGA** Field Programmable Gate Array. xxiv, xxxiv–xxxvi, xl, xliii, xlv–xlviii, li, lii, 4, 31–36, 40, 44, 45, 47, 53, 57–61, 63, 64, 70, 72, 76, 79, 80, 82, 85, 87, 88, 90, 91, 93, 101, 107, 109, 113–115, 117, 120, 122, 123, 125, 127

GMPLS Generalized Multi-Protocol Label Switching. 18, 37

**LUT** Look Up Table. 33, 34, 36, 44, 113, 117, 118

MAC Medium Access Controller. xxxiv, xxxv, 35, 57

MSE Mean Square Error. 95, 104, 114–116

OADM Optical Add-Drop Multiplexer. xxvii, 3, 10–13, 15, 41, 47

**ODU** Optical Data Unit. 7, 55, 56

**OTN** Optical Transport Network. xxiv, xxv, xxxiii, 3, 6, 7, 45

PRBS Pseudo Random Binary Sequence. 79, 85

**PSD** Power Spectral Density. 98, 99, 102

**QPSK** Quadrature Phase Shift Keying. xxix, 23, 26, 44, 49, 50, 52, 80, 84, 102

**RAM** Random Access Memory. xxxv, 35, 36, 76, 113, 117–119, 122

ROADM Reconfigurable Optical Add-Drop Multiplexer. xl, 13, 14, 17, 38, 41, 45, 71

**ROM** Read-Only Memory. 79, 107, 110, 111, 114–117, 119, 123

S-BVT Sliceable Bandwidth Variable Transponder. xxx, 4, 31, 42, 46, 47, 49

**SDN** Software Defined Network. xxvii, xxviii, xxxii, xl, 3, 18, 19, 37, 39, 41, 45, 50, 71, 73, 74, 76, 91, 92, 126

SNR Signal-to-Noise Ratio. xlv, 97–99, 103, 113, 125, 127

SSH Secure Shell. xxxvii, 64

tanh Hyperbolic Tangent. 103, 107, 110

UART Universal Asynchrounous Receiver-Transmitter. xxxvii, li, 64, 72, 87, 122, 123

VHDL Very High Speed Integrated Circuit Hardware Description Language. 36, 57

WDM Wave Division Multiplexing. xxiv, xxv, xxvii, xxviii, 3, 6, 7, 10, 12, 13, 16, 44

YANG Yet Another Next Generation. 38, 46

### RÉSUMÉ ÉTENDU EN FRANÇAIS

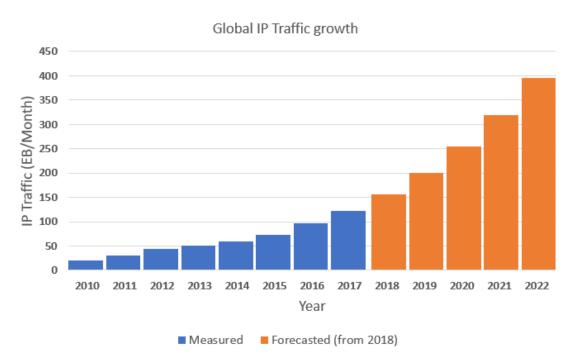

Les réseaux optiques sont devenus le moyen privilégié de faire transiter l'information à très grande vitesse et sur des grandes distances. Ils interconnectent les usagers, les villes, pays et régions et continents entre eux et leur utilisation ne cesse de croître, tandis que les besoins en débit et en réduction de latence ne cessent d'augmenter, notamment dans le contexte d'adoption de la 5G, des services dans le cloud et de l'internet des objets.

Pour subvenir à l'augmentation incessante des besoins, de nouvelles fonctionnalités et de nouvelles façons de concevoir les réseaux optiques ont émergées. Tout d'abord, l'adoption des communications cohérentes a permis d'augmenter sensiblement les débits possibles pour les communications optiques, en utilisant l'amplitude la phase et la polarisation du signal optique pour transmettre l'information. Aussi, les développements modernes des équipements ont permis de pouvoir reconfigurer le matériel, afin de pouvoir répondre à une baisse de qualité de service efficacement, en changeant un paramètre de transmission ou en reroutant le trafic dans le réseau. Aussi, l'adoption du plan de contrôle centralisé a permis le développement des capacités d'automatisation et de virtualisation des ressources dans les réseaux. Toutes ces évolutions sont à la base du développement des réseaux optiques flexibles d'aujourd'hui.

Si les réseaux ont gagné en flexibilité, il reste néanmoins des axes d'améliorations avant l'arrivée des réseaux réellement flexibles et automatisés. Tout d'abord, reconfigurer le matériel conduit encore souvent à des interruptions de service pendant que le matériel change ses paramètres, ce qui fait que les adaptations dans le réseau sont encore rares. De plus, la centralisation du plan de contrôle permet certes de gagner en efficacité et en automation, mais l'hyper concentration des tâches de surveillance et de prise de décision crée des délais et des pertes de performance pour la détection et la résolution des dégradations dans le réseau.

Dans cette thèse et au vu de ce contexte, nous nous sommes concentrés sur le transpondeur optique, équipement faisant le lien entre les réseaux d'accès d'où proviennent les données client et les réseaux de transport optique. Cet équipement est au centre des récents développements de flexibilité et de virtualisation.

Dans une première partie nous allons développer le contexte des réseaux de transport

optique, et des concepts de flexibilité et de virtualisation. Nous allons aussi présenter plus en détail le transpondeur optique et de ses évolutions modernes. Nous allons ensuite présenter une solution d'auto-négociation et de monitoring embarqué permettant le déclenchement de reconfigurations rapides et synchronisées pour compenser une dégradation en qualité de service. Nous allons mesurer ses performances et les comparer à un plan de contrôle centralisé pour résoudre une dégradation au sein d'un banc de test réseau. Nous allons aussi présenter une solution de monitoring avec réseau de neurones embarquée sur Field Programmable Gate Array (FPGA). Cette solution possède une fonctionnalité de reconfiguration des poids des neurones afin de changer la fonction effectuée par le réseau, permettant au plan de contrôle centralisé de réaliser du monitoring déporté, notamment sur des métriques sous utilisées et demandant un grand flux de données. Nous avons validé cette solution en termes de performances et de précision en réalisant un monitoring des contributions nonlinéaires à partir des spectres optiques.

### Réseaux de transport optique

#### Couche physique

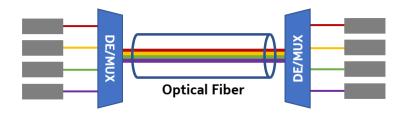

Les réseaux de transport optiques recouvrent les réseaux métropolitains (distance entre nœuds optiques de quelques dizaines à quelques centaines de kilomètres environ) et coeurs de réseaux (milliers de kilomètres entre nœuds), et sont au cœur des transformations récentes dans les réseaux optiques et des besoins croissants en débit et en fiabilité [2]. Ils sont basés autour de deux technologies majeures, le Multiplexage en Longueur d'Onde ou Wave Division Multiplexing (WDM), et le standard OTN (Optical Transport Network). Le WDM permet à une fibre optique de porter plusieurs longueurs d'onde multiplexées sur un signal. Cela permet d'augmenter significativement la capacité des réseaux optiques. Les signaux des clients du réseau optique peuvent être ajoutés ou retirés du signal WDM selon leur point d'arrivée ou de destination dans le réseau. Le WDM est représenté dans la Figure 1.

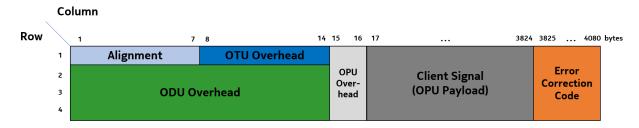

Le standard OTN est un groupe d'outils permettant de gérer les signaux clients et leurs longueurs d'onde du réseau de transport optique, et est basé sur un format de trame avec un grand nombre de champs permettant de monitorer, router et concaténer les signaux. Plusieurs générations de trames OTN existent et sont adaptées au débit maximum supporté (par exemple l'OTU4 supporte le transport de signaux client jusqu'à

Figure 1 – Représentation de la technologie de Multiplexage en Longueur d'Onde (WDM)

Figure 2 – Structure d'une trame OTN (Optical Transport Network). Plusieurs sous structures cohabitent dans la trame : OTU (Optical Transport Unit), ODU (Optical Data Unit) et OPU (Optical Payload Unit), chacun comprenant leurs propres champs (permettant le monitoring, le concaténation, etc...des signaux clients).

100Gbps), avec la possibilité de multiplexer plusieurs trames de générations inférieures, pour transformer plusieurs signaux à faible débit en un signal à haut débit. La structure d'une trame OTN est représentée dans la Figure 2.

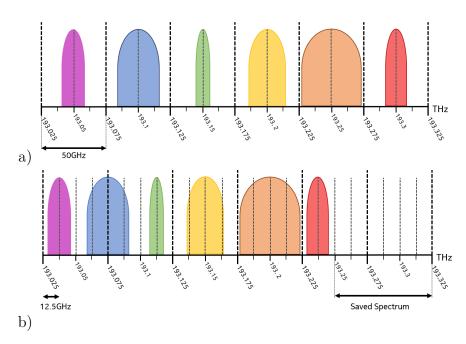

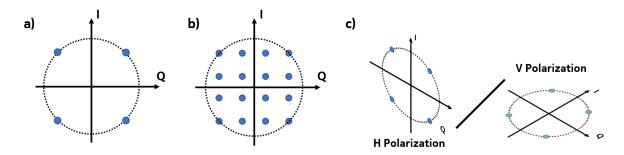

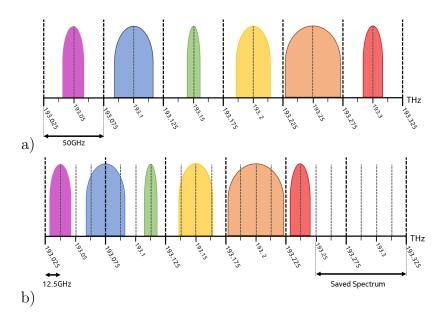

Aujourd'hui, le paradigme principal dans les réseaux de transport optique est le Réseau Optique Elastique (Elastic Optical Network, EON), qui a été rendu possible grâce à l'introduction de plusieurs principes. Le premier changement ayant permis l'arrivée des réseaux élastiques est l'introduction des équipements reconfigurables au sein du réseau de transport optique, permettant d'adapter la configuration de chaque équipement aux besoins du réseau en débit ou en robustesse par exemple. L'autre changement a été l'utilisation de la grille flexible (flexgrid) de fréquence dans les réseaux WDM. Contrairement à la grille dite fixe traditionnellement utilisée, qui répartissait les signaux optiques dans un emplacement de 50GHz de large dans la bande de fréquence, la flexgrid permet une plus grande granularité en utilisant des slots plus fins (par exemple 12.5GHz de largeur de bande), qui peuvent être remplis de façon plus intelligente et plus adaptées aux besoins de chaque signal [3], comme montré dans la Figure 3. Cela permet aussi d'économiser de la bande spectrale et d'utiliser des signaux à bande passante plus large que 50GHz sans gâcher inutilement de l'espace.

Figure 3 – Représentations de (a) la grille de fréquence fixe traditionnellemnt utilisée dans les réseaux de transport optique, et (b) la grille flexible utilisée dans les réseaux modernes élastiques.

Figure 4 - Réprésentation de la couche physique d'un réseau de trasnport optique.

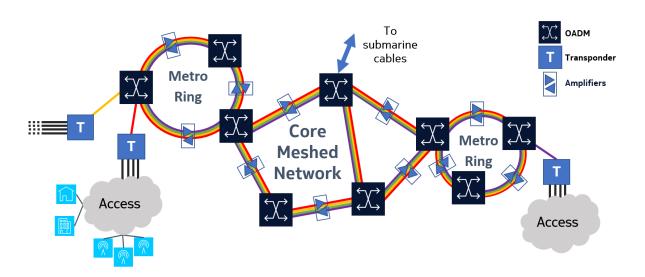

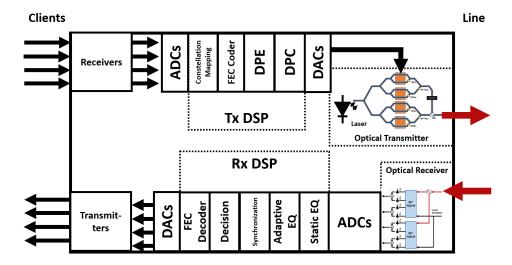

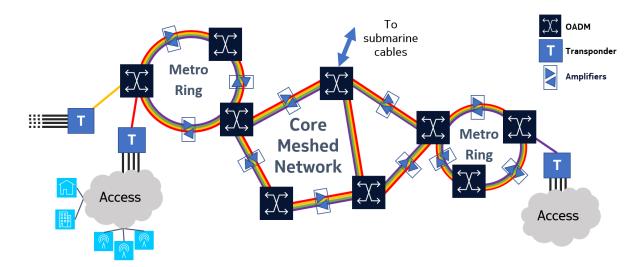

La Figure 4 montre une représentation de réseau de transport optique, avec ses différents équipements. Tout d'abord les transpondeurs optiques, qui font la liaison entre les réseaux d'accès, d'où proviennent les signaux des clients, et le réseau de transport optique. Ils multiplexent les signaux client sur un signal compatible WDM et envoient ce dernier à un Optical Add-Drop Multiplexer (OADM) qui routera ce signal vers sa destination dans le réseau optique, où le signal sera démultiplexé par le transpondeur en sortie. Dans les chemins optiques se trouvent aussi des amplificateurs qui permettent d'augmenter la distance maximale de transmission du signal optique, mais ajoutant des effets indésirables dans la transmission en contrepartie. Ces différents éléments ont pu évoluer au gré des avancées techniques, proposant différentes possibilités de configuration, et pouvant être reconfigurés à distance par un opérateur ou par un élément du plan de contrôle.

#### Plan de contrôle

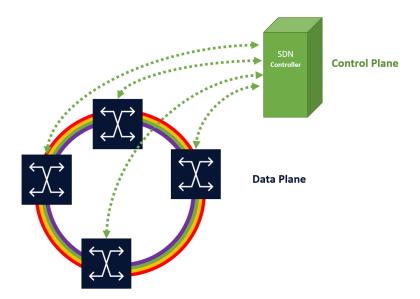

Pour orchestrer efficacement et automatiquement les différents éléments du réseau, l'approche la plus commune aujourd'hui est de mettre en place un plan de contrôle optique centralisé. Ce plan de contrôle possède des fonctions de monitoring qui surveillent l'état des différents éléments de la couche physique afin de proposer des configurations appropriées pour les équipements optiques. Le paradigme actuel d'organisation du plan de contrôle est le Software Defined Network (SDN) [4]. Il se base sur une grande centralisation des fonctions de contrôle au sein d'un groupe d'entités séparé de la couche physique. La Figure 5 montre une représentation simplifiée d'un plan de contrôle SDN. Pour connaître précisément l'état du réseau, le plan de contrôle récolte régulièrement les données de monitoring des équipements optiques, comme par exemple la puissance de réception, le taux d'erreur (ou Bit Error Rate) avant et après code de correction d'erreur (Forward Error Correction, FEC). Plusieurs techniques de récupération des données de monitoring existent, les plus récentes se basant sur des flux des données, permettant une récolte rapide des données de monitoring et permettant au plan de contrôle de pouvoir s'abonner ou de se désabonner à ces flux et d'adapter ses stratégies de monitoring selon les besoins [5].

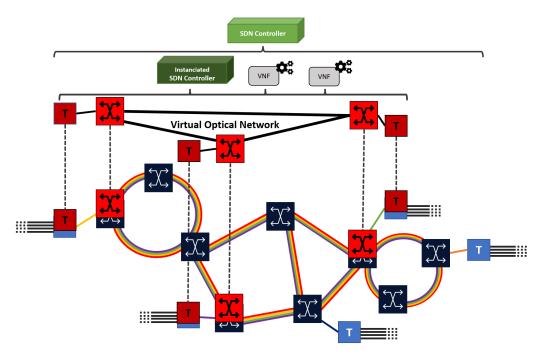

Influencés par l'informatique dans le *cloud*, les réseaux optiques ont commencé à intégrer de la virtualisation dans la gestion du réseau et des équipements. Le principe de la virtualisation est de découpler les fonctions logicielles du matériel, ce qui permet par exemple au plan de contrôle de créer des sous-réseaux avec des besoins particuliers (en latence, en sécurité, en débit, etc...). Les équipements peuvent être partitionnés en plusieurs équipement virtuels ou agrégés en un seul super équipement, des fonctions spécifiques

Figure 5 – Représentation simplifée d'un plan de contrôle centralisé SDN (Software Defined Network)