# Development of integrated emission architectures for THz applications in 28nm FD-SOI CMOS technology

Sébastien Sadlo

#### ▶ To cite this version:

Sébastien Sadlo. Development of integrated emission architectures for THz applications in 28nm FD-SOI CMOS technology. Electronics. Université de Bordeaux, 2023. English. NNT : 2023BORD0356. tel-04483252

## HAL Id: tel-04483252 https://theses.hal.science/tel-04483252v1

Submitted on 29 Feb 2024

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### THÈSE PRÉSENTÉE

#### POUR OBTENIR LE GRADE DE

#### **DOCTEUR DE**

#### L'UNIVERSITÉ DE BORDEAUX

ECOLE DOCTORALE DES SCIENCES PHYSIQUES ET DE L'INGÉNIEUR SPÉCIALITÉ : ELECTRONIQUE

Par Sébastien SADLO

# "Development of integrated emission architectures for THz applications in 28nm FD-SOI CMOS technology"

"Développement d'architectures d'émission intégrées pour les applications THz en technologie CMOS avancées"

> Thèse CIFRE Préparée en collaboration avec : STMicroelectronics, Crolles, France Laboratoire IMS, Bordeaux, France

Soutenue le : 30 novembre 2023

Membres du jury :

| Mme. | Daniela DRAGOMIRESCU | Professeure des universités | INSA Toulouse          | Rapporteure            |

|------|----------------------|-----------------------------|------------------------|------------------------|

| M.   | Ehsan AFSHARI        | Professeur des universités  | University of Michigan | Rapporteur             |

| M.   | Yann DEVAL           | Professeur des universités  | Université de Bordeaux | Président              |

| M.   | Andreas KAISER       | Professeur des universités  | ISEN                   | Examinateur            |

| M.   | Raphael GUILLAUME    | Ingénieur-Docteur           | STMicroelectronics     | Invité                 |

| Mme. | Nathalie DELTIMPLE   | Professeure des universités | Bordeaux INP           | Directrice de these    |

| Mme. | Andreia CATHELIN     | Docteure HDR                | STMicroelectronics     | Co-directrice de these |

#### **Abstract**

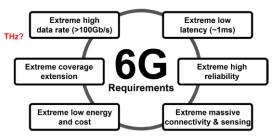

The THz part of the spectrum allows disruptive applications such as 100 Gb/s wireless communications, imaging, and spectroscopy and offers an interesting perspective for the 6G future standards. The need for this kind of application is rising and nanoscale VLSI CMOS technologies dispose of active devices with high enough ft and fmax to integrate Systems on Chips in this frequency range.

This work presents research results towards the design of amplification circuits above fmax/2 in 28nm FD-SOI CMOS technology. This thesis enriches state of the art for amplifier gain boosting design methodology and extends it for large bandwidth operation. The theoretical study of this work compares the proposed solution with the classical approaches. In light of the state of the art, an analysis of the performance's limitations regarding the saturated output power, bandwidth, and efficiency is presented. Design methods to improve these metrics are proposed and the design and measurements of 200 GHz power amplifiers are presented.

Keywords: CMOS, FD-SOI, sub-THZ, 6G, power amplifier, silicon, integrated circuit

#### Résumé

La partie du spectre THz permet des applications disruptives telles que les communications sans fil à 100 Gb/s, l'imagerie, la spectroscopie et offre une perspective intéressante pour les normes futures de la 6G. Le besoin pour ce type d'applications est en hausse et les technologies CMOS VLSI à l'échelle nanométrique disposent de dispositifs actifs avec une  $f_t$  et une  $f_{max}$  suffisamment élevées pour intégrer des systèmes sur puces dans cette plage de fréquences.

Ce travail présente des résultats de recherche pour la conception de circuits d'amplification au-dessus de  $f_{max}/2$  en technologie CMOS FD-SOI 28nm. Cette thèse enrichit l'état de l'art pour la méthodologie de conception d'amplification de gain et l'étend pour une grande opération de bande passante. L'étude théorique de ce travail compare la solution proposée avec les approches classiques. À la lumière de l'état de l'art, une analyse des limitations de performance concernant la puissance de sortie saturée, la bande passante et l'efficacité est présentée. Des méthodes de conception pour améliorer ces métriques sont proposées et la conception et les mesures d'amplificateurs de puissance de 200 GHz sont présentées.

Mots clés: CMOS, FD-SOI, sub-THZ, 6G, amplificateur de puissance, silicium, circuit intégré

#### **Acknowledgments**

Many people have contributed along the journey of this thesis. The support and guidance of my advisors, Nathalie Deltimple and Andreia Cathelin, kept me on course in the right direction. Their knowledge of the domain and the research world allowed them to identify this subject at the right time.

I would like to acknowledge professors Daniela Dragomirescu and Ehsan Afshari for accepting to review this PhD dissertation. I want to thank all the members of the jury, Yan Deval, Andreas Kaiser and Raphael Guillaume for participating to the PhD presentation and defense. All the feedback and the interesting discussions allowed to enrich the PhD defense.

My family has played a key role throughout the years, always supporting and encouraging me. My parents, Alina and Jan, and my sister, Patricia, were always attentive and had the right words to get through the difficult days. Special thanks to Stefania, I could not have done it without you.

The environment of this thesis between STMicroelectronics and the IMS laboratory was very rich, each person that I had the chance meet during these years contributed in a certain way to the thesis.

I would like to thank my ST colleagues from the R&D Team where everything started during my internship, prior to the thesis, and where everything continues today. Thank you Christophe for your formative supervision, your discipline and good mood. Thank you Antoine and David for the pleasant atmosphere during our PhD years and now our daily work.

I am thankful to the PhD team "Chip Decathlon": Denis Flores, Andres Aprilla, Khalil Bouchoucha, Soufiane Mourrane, Julien Poupon, Virgile Colrat and Adrien Verplancke. We were on the same boat, some of us arrived at destination and others are still on their way. But the great time working by your side leaves nothing but pleasant memories despite the quantity of work, the stress and the fatigue that we endured.

I would like also to thank people from ST that had advised me along the thesis, Denis Pache, Frederic Paillardet, Philippe Cathelin, your experience and your kindness are a great example to follow

Finally, I would like to thank the people that I met and worked with at the IMS lab, Antoine Lhomel, Colin Boulanger, Emmanuel Pages, Remi Queheille, Timothée Le Gall, Magali De Matos, Sebastien Fregonese, Marina Deng, Jean-Charles Henrion, Gwennael Diverrez, the experience and the memories from this period have greatly fed my PhD journey.

# **Table of Contents**

| Chapter    | 1 Introduction                                                                        | 17 |

|------------|---------------------------------------------------------------------------------------|----|

| Chapter    | 2 Introduction to THz                                                                 | 19 |

| 2.1        | Physical opportunities of the sub-THz spectrum                                        | 20 |

| 2.1.       | 1 Imaging                                                                             | 21 |

| 2.1.       | 2 Spectroscopy                                                                        | 21 |

| 2.1.       | 3 Radar                                                                               | 22 |

| 2.1.       |                                                                                       |    |

| 2.2        | Largely available bandwidths, increasing needs for data rates                         |    |

| 2.3        | Architectures: Frequency upconverting, Harmonic multipliers, Fundamental              |    |

| 2.4        | Transceivers over 100GHz                                                              |    |

| 2.5        | Power Amplifiers over 100GHz                                                          |    |

| 2.6        | Conclusion on actual limits in transmission circuits                                  |    |

| 2.7        | References                                                                            |    |

| Chapter    | · · · · · · · · · · · · · · · · · · ·                                                 |    |

| 3.1        | Network analysis                                                                      |    |

| 3.1.       |                                                                                       |    |

| 3.2        | The scaling of transistors through the development of integrated circuit technologies |    |

| 3.3        | MOSFET presentation                                                                   |    |

| 3.4        | I-V characteristics                                                                   |    |

| 3.5        | High-frequency transistor linear model                                                |    |

| 3.5.       |                                                                                       |    |

| 3.5.       |                                                                                       |    |

| 3.5.       | 1 37 1                                                                                |    |

| 3.6        | f <sub>t</sub> , f <sub>max</sub> dependency on current density and geometry          |    |

| 3.7        | Inductors                                                                             |    |

| 3.8<br>3.9 | Capacitors  Transmission Lines                                                        |    |

| 3.10       | Conclusion                                                                            |    |

| 3.10       | References                                                                            |    |

| Chapter    |                                                                                       |    |

| 4.1        | Two port Gain boosting theory                                                         |    |

| 4.1.       |                                                                                       |    |

| 4.2        | Inductive and capacitive Common Source Neutralization                                 |    |

| 4.3        | Gain planes                                                                           |    |

| 4.4        | Design methodology                                                                    |    |

| 4.5        | Implementation of Gain-boosted Amplifier in 28nm FD-SOI                               |    |

| 4.6        | Measurement and analysis                                                              |    |

| 4.7        | Conclusion on results and goals for higher bandwidth and power                        |    |

| 4.8        | References                                                                            |    |

| Chapter    |                                                                                       |    |

| 5.1        | Specifications for the PA                                                             |    |

| 5.2        | Large signal impedance matching and device sizing                                     |    |

| 5.3        | Large transistor design optimization for sub-THz operation                            |    |

| 5.4        | Impedance Matching and power combining techniques for large BW                        |    |

| 5.5        | High power Amplification cells, CS, and Cascode comparison                            |    |

| 5.5.1      | Differential neutralized Common Source                                          | 123   |

|------------|---------------------------------------------------------------------------------|-------|

| 5.5.2      | Differential Cascode with internal matching                                     | 125   |

| 5.6 Larg   | ge band gain boosting                                                           | 126   |

| 5.7 Imp    | lementation of PAs in 28nm FDSOI                                                | 128   |

| 5.7.1      | Classic 3 stages PA                                                             | 128   |

| 5.7.2      | Boosted 3 stage PA                                                              | 129   |

| 5.8 Mea    | surements and analysis of results                                               | 132   |

| 5.9 Con    | clusion on results                                                              | 135   |

| 5.10 Refe  | erences                                                                         | 135   |

| Chapter 6  | Conclusions and perspectives                                                    | 138   |

| 6.1 Sun    | nmary                                                                           | 138   |

| 6.2 Pers   | spectives                                                                       |       |

| 6.2.1      | Improvement of the designed 200GHz PAs                                          | 139   |

| 6.2.2      | Development of new passive devices geometries                                   | 139   |

| 6.2.3      | Development of new amplifier architectures specific to FD-SOI technologies      | 140   |

| 6.3 List   | of publications                                                                 | 140   |

| Appendix A | Definition of PA metrics                                                        | 142   |

| Appendix B | PA over 100GHZ State of the Art                                                 | 145   |

| Appendix C | Network analysis                                                                | 146   |

| Appendix D | Lumped modeling limit                                                           | 156   |

| Appendix E | Optimization and simulation of large transistor cell for sub-THz PA application | າ 160 |

# List of figures

| Figure 2.1 The electromagnetic spectrum, and various applications as a function of frequenc                                                                                               | -     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| [Rapp19]Figure 2.2 The THz gap with respect to source technology, including quantum cascade laser                                                                                         |       |

| frequency multipliers (•), and other electronic devices (-). Hollow symbols represent cryoger                                                                                             | nic   |

| results [Crow05]                                                                                                                                                                          |       |

| Figure 2.3 Main THz applications map [Pfei19]                                                                                                                                             |       |

| Figure 2.4 Transmission-mode images at THz of a badge and an envelope [Hadi11]                                                                                                            |       |

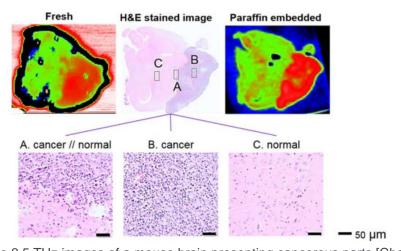

| Figure 2.5 THz images of a mouse brain presenting cancerous parts [Cheo17]                                                                                                                |       |

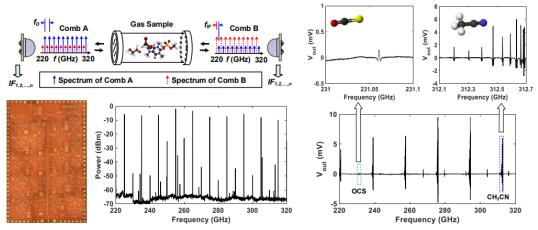

| Figure 2.6 Dual-THz-comb spectrometer for gas sensing [Wang18a]                                                                                                                           |       |

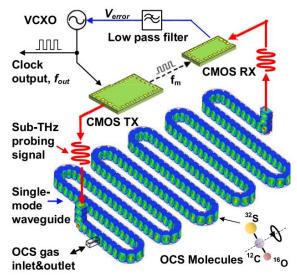

| Figure 2.7 CMOS molecular clock implementation [Wang18b]                                                                                                                                  |       |

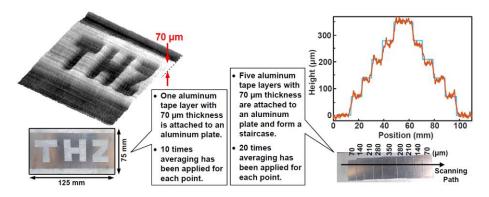

| Figure 2.8 THz images [Hoss21]                                                                                                                                                            |       |

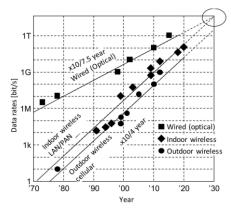

| Figure 2.9 Evolution of data rate of wired communication and wireless communication over the                                                                                              |       |

| years [Fuji18]                                                                                                                                                                            | 23    |

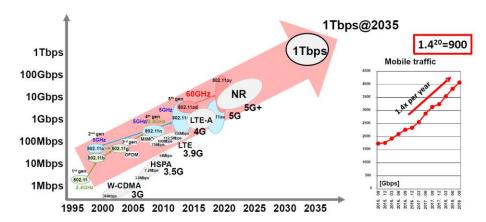

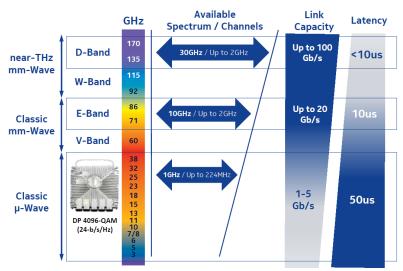

| Figure 2.10 Evolution of wireless communication standards' data rates over the years [Okad: Figure 2.11 Available spectrum and channel bandwidths as a function of the carrier frequence. | -     |

| [Shah22]                                                                                                                                                                                  | •     |

| Figure 2.12 6G Requirements [Okad22]                                                                                                                                                      |       |

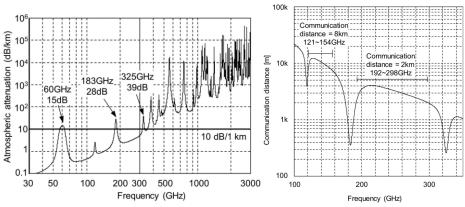

| Figure 2.13 Atmospheric attenuation (left) [Fuji18]                                                                                                                                       |       |

| Figure 2.14 Comparison of 30GHz and 300GHz antenna arrays at constant surface [Okad22                                                                                                     |       |

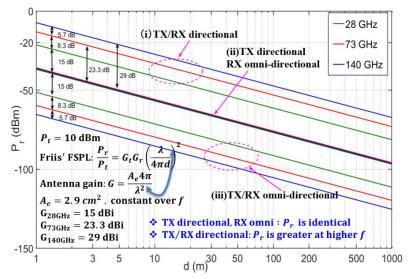

| Figure 2.15 Received power vs. distance for different signal frequency and Tx/Rx antenna                                                                                                  | ., 27 |

| configurations [Xing18]                                                                                                                                                                   | 28    |

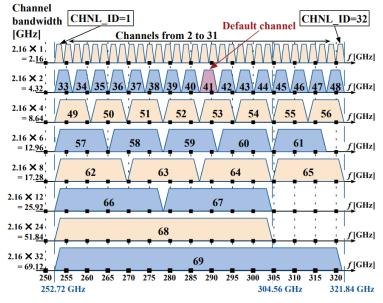

| Figure 2.16 IEEE 802.15.3d channel plan [Petro20]                                                                                                                                         |       |

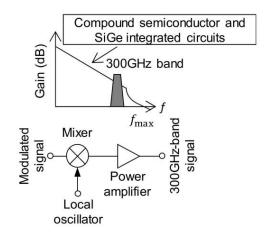

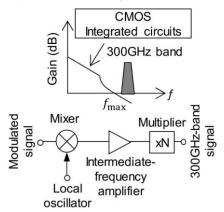

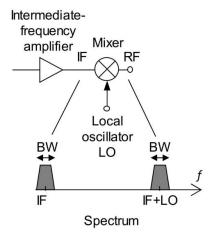

| Figure 2.17 Schematic of PA last emitter architecture [Fuji18]                                                                                                                            |       |

| Figure 2.18 Schematic of multiplication-based emitter architecture [Fuji18]                                                                                                               |       |

| Figure 2.19 Schematic of mixer last emitter architecture [Fuji18]                                                                                                                         |       |

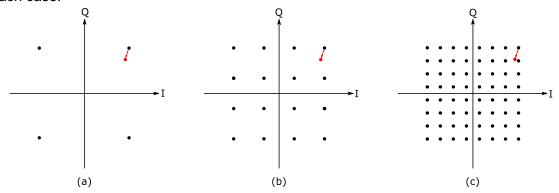

| Figure 2.20 Representation of 4-QAM (a) 16-QAM (b) and 64-QAM (c) constellations in black                                                                                                 |       |

| non-ideal symbol in red and its associated error vector                                                                                                                                   |       |

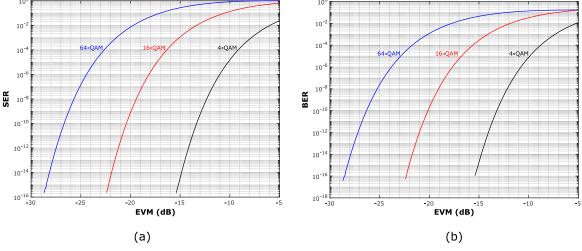

| Figure 2.21 SER (a) BER (b) as a function of EVM                                                                                                                                          |       |

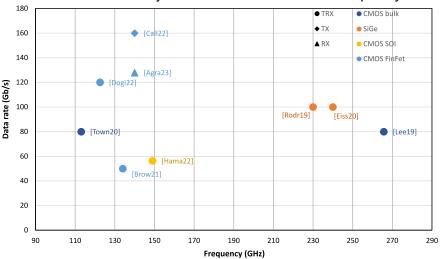

| Figure 2.22 State of the art of transceivers, transmitters, and receiver over 100GHz                                                                                                      |       |

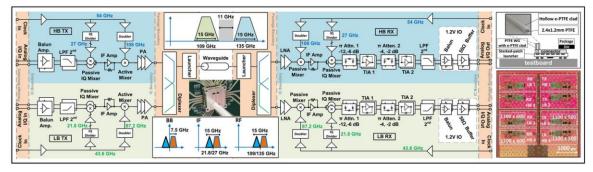

| Figure 2.23 Transceiver architecture with illustrations of the frequency plan, waveguide conn                                                                                             |       |

| and die photograph [Dogi22]                                                                                                                                                               |       |

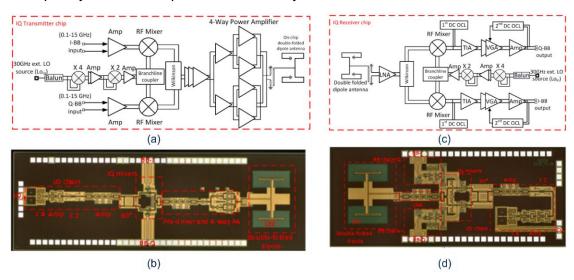

| Figure 2.24 240GHz IQ transmitter schematic (a), chip microphotograph (b), and IQ receiver                                                                                                |       |

| schematic (c) and chip microphotograph (d)                                                                                                                                                | 34    |

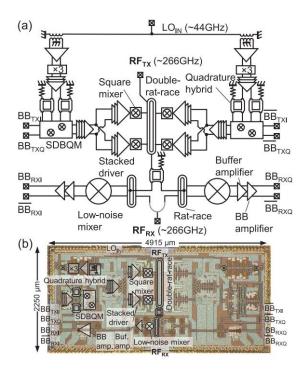

| Figure 2.25 (a) Overall schematic of the 300-GHz-band CMOS TRX. SDBQM: Semidoubly b                                                                                                       |       |

| quadrature mixer. (b) Die micrograph.                                                                                                                                                     |       |

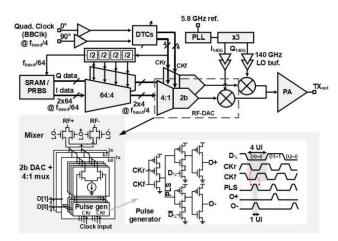

| Figure 2.26 Top-level architecture of transmitter showing details of RF-DAC with 4:1 MUX [C                                                                                               | =     |

| Figure 2.27: High-level architecture of the fully integrated receiver (top) and implementation of                                                                                         |       |

| coupled-line-based Guanella balun (bottom left). Configuration of test chip for stand-alone                                                                                               |       |

| characterization of receiver front-end (RXFE) and ADC with sampling rate fs (bottom right) [A                                                                                             | -     |

|                                                                                                                                                                                           |       |

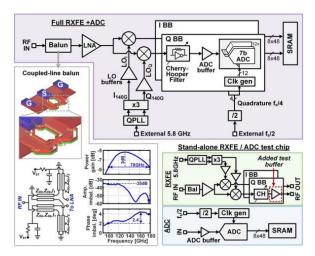

| Figure 2.28 EVM as a function of data rate for transceivers over 100GHz                                                                                                                   |       |

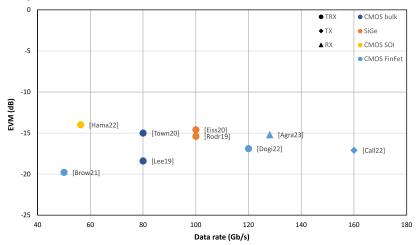

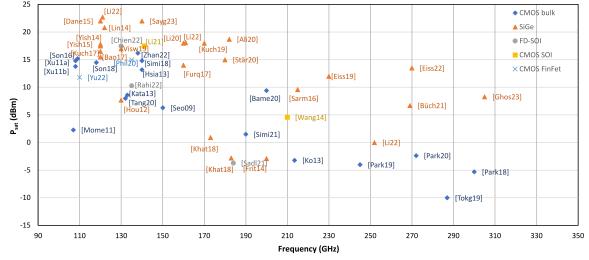

| Figure 2.29 Representation of published PA before 2020's P <sub>sat</sub> as a function of frequency                                                                                      |       |

| Figure 2.30 Representation of all published PA's P <sub>sat</sub> as a function of frequency                                                                                              | 37    |

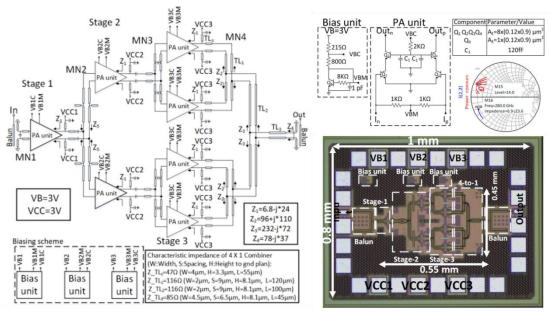

| Figure 2.31 4-way combined PA top-level schematic and die photograph [Eiss22]                                                                                                             | 38    |

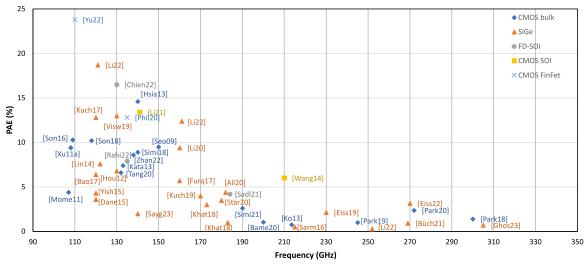

| Figure 2.32 Representation of all published PA's PAE as a function of frequency                                 | 39     |

|-----------------------------------------------------------------------------------------------------------------|--------|

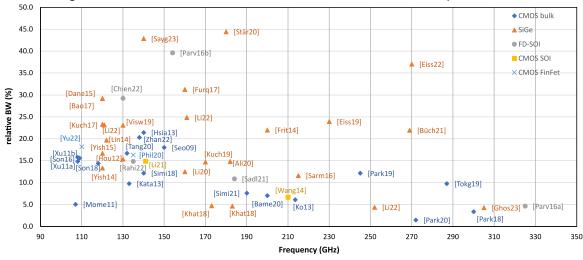

| Figure 2.33 Representation of all published PA's relative bandwidth as a function of frequency                  | 39     |

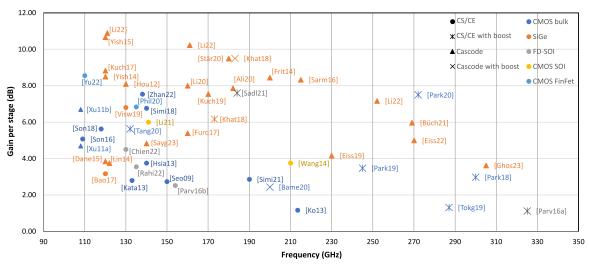

| Figure 2.34 Representation of all published PA's gain per stage as a function of frequency                      | 40     |

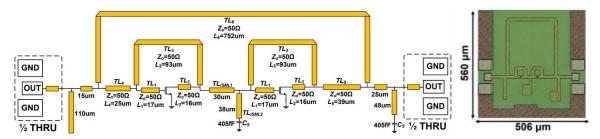

| Figure 2.35 Schematic and chip microphotograph of 280GHz amplifier [Park20]                                     |        |

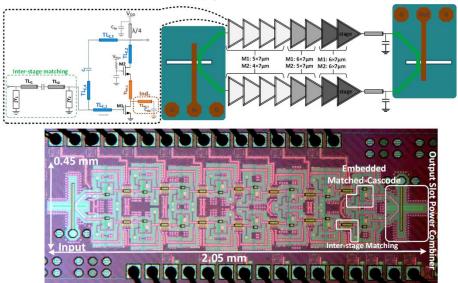

| Figure 2.36 Block diagram of 200GHz PA and chip microphotograph [Bame20]                                        |        |

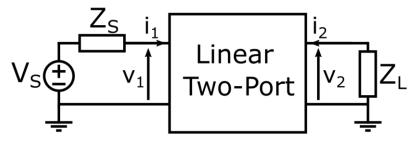

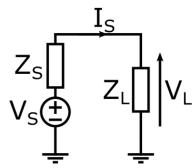

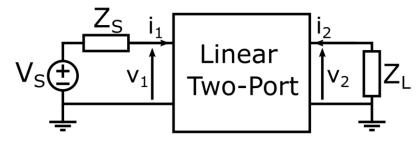

| Figure 3.1 Schematic of a linear two-port                                                                       |        |

| Figure 3.2 Schematic of a linear two port with one port connected to a voltage source and the ot                |        |

|                                                                                                                 |        |

| connected to a load                                                                                             |        |

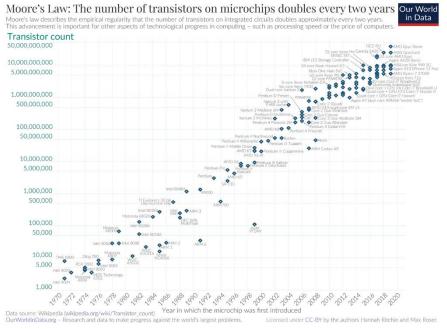

| Figure 3.3 Number of transistors per chip over the years [Wiki1]                                                |        |

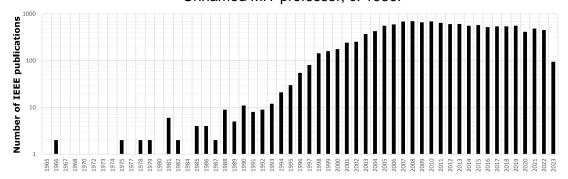

| Figure 3.4 Number of results on IEEE Explore for the search "RF"AND("MOS"OR"CMOS") per y                        |        |

| of publication                                                                                                  | 48     |

| Figure 3.5 Properties of the main semiconductor materials used in high-frequency transistors                    |        |

| [Voin13]                                                                                                        |        |

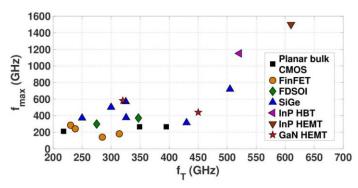

| Figure 3.6 $f_t$ and $f_{max}$ performances of different transistor technologies [irds22]                       |        |

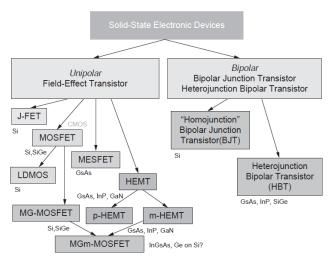

| Figure 3.7 Main high-frequency transistor types [Voin13]                                                        | 50     |

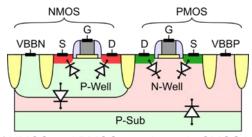

| Figure 3.8 Schematic of NMOS and PMOS transistors in CMOS bulk technology [Cath17]                              | 50     |

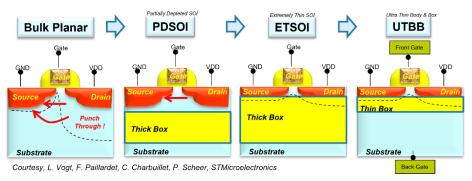

| Figure 3.9 Evolution of MOSFET transistor types, from bulk to FDSOI (UTBB)                                      | 51     |

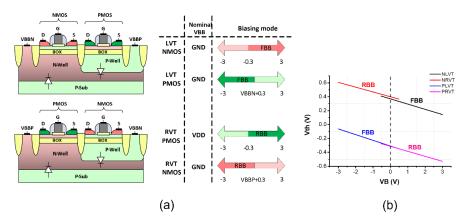

| Figure 3.10 Schematic of 28nm FD-SOI transistor flavors (a) and threshold voltage control capa                  | bility |

| through the backgate voltage (b) [Cath17]                                                                       | -      |

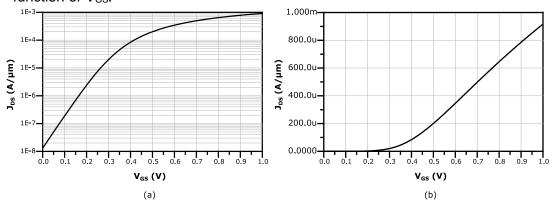

| Figure 3.11 Simulation of the current density $J_{DS}$ in function of gate-source voltage with $V_{DS}=1V$      |        |

| L=30nm, for a lvtnfet in 28nm FD-SOI in log (a) and linear (b) scale                                            |        |

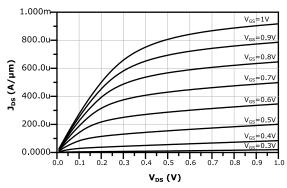

| Figure 3.12 Simulation of the current density $J_{DS}$ in function of drain-source voltage with different       |        |

| values of $V_{GS}$ and $L=30nm$ , for a lythfet in 28nm FD-SOI                                                  |        |

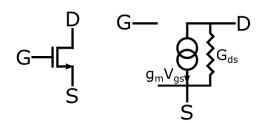

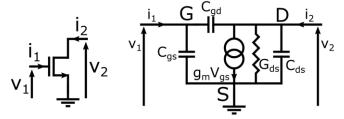

| Figure 3.13 Transistor symbol (a) Intrinsic transistor model (b)                                                |        |

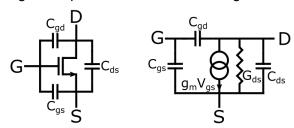

| Figure 3.14 Transistor with capacitances (a) Transistor with capacitances model                                 |        |

|                                                                                                                 |        |

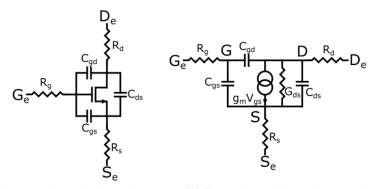

| Figure 3.15 Transistor with extrinsic resistances (a) Transistor with extrinsic resistances model (             |        |

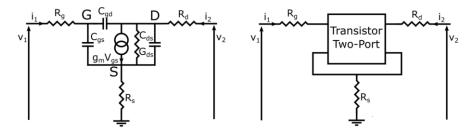

| Figure 3.16 Transistor used in Common Source topology schematic (a) model (b)                                   |        |

| Figure 3.17 Transistor used in Common Source topology model with components (a) with intrins                    |        |

| two-port (b)                                                                                                    |        |

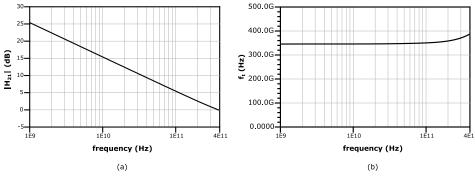

| Figure 3.18 Simulations of $ H_{21} $ (a) and $f_t$ extrapolation (b) over frequency of a lythfet transistor in |        |

| 28 nm FD-SOI with $L=30$ nm, $V_{DS}=1$ V, and $J_{DS}=0.3$ mA/ $\mu$ m                                         |        |

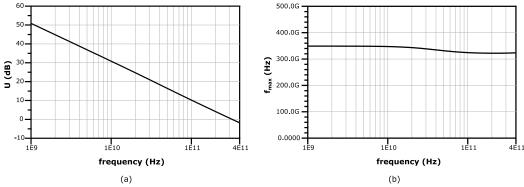

| Figure 3.19 Simulations of $U$ (a) and $f_{max}$ extrapolation (b) over frequency of a lythrest transistor in   |        |

| 28nm FD-SOI with $L=30 \text{ nm}$ , $V_{DS}=1 \text{ V}$ and $J_{DS}=0.3 \text{ mA/}\mu\text{m}$               |        |

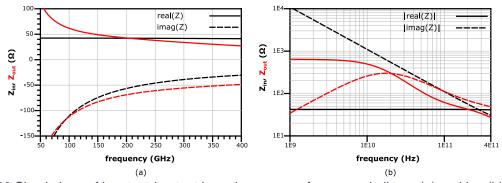

| Figure 3.20 Simulations of input and output impedances over frequency in linear (a) and log (b)                 |        |

| scale of a CS transistor with $L=30$ nm and $W=16$ $\mu m$ at $J_{DS}=0.3$ $mA/\mu m$                           |        |

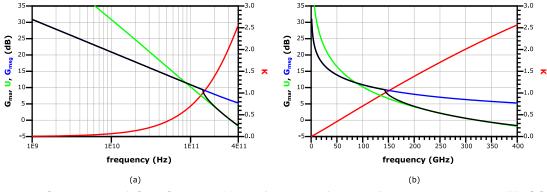

| Figure 3.21 Simulations of $G_{ma}$ , $G_{msg}$ , and $K$ over frequency for a lytnfet transistor in 28nm FD-S0 |        |

| with <i>L=30 nm</i> , <i>Vds=1 V</i> , and <i>j=0.3 mA/μm</i> in log (a) and linear (b) scale                   | 61     |

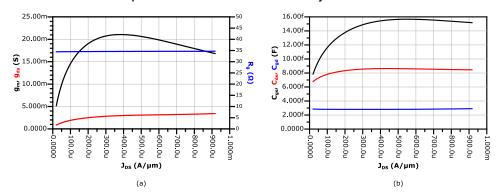

| Figure 3.22 Simulations of transistor parameters in function of current density for a lytnfet transis           | stor   |

| in 28nm FD-SOI with <i>L=30 nm</i> , <i>W</i> <sub>tot</sub> =16 μm, <i>Vds</i> =1 <i>V</i>                     | 61     |

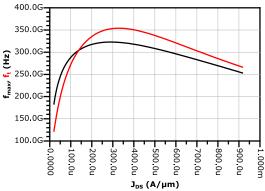

| Figure 3.23 Simulations of transistor $f_f/f_{max}$ as a function of current density for a lytnfet transistor   | in     |

| 28nm FD-SOI with <i>L=30 nm</i> , <i>W<sub>tot</sub>=16 μm</i> , <i>Vds=1 V</i>                                 | 62     |

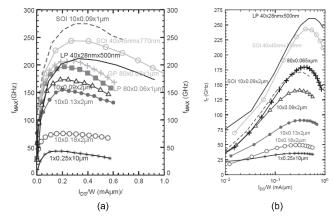

| Figure 3.24 Measured $f_{\#}f_{max}$ of N-MOS transistors in different processes in function of current         |        |

| density [Voin13]                                                                                                | 62     |

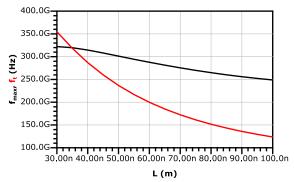

| Figure 3.25 Simulated and extracted maximal $f_{max}$ and $f_t$ at 150 GHz in function of gate length $L$       |        |

| W=16 μm                                                                                                         |        |

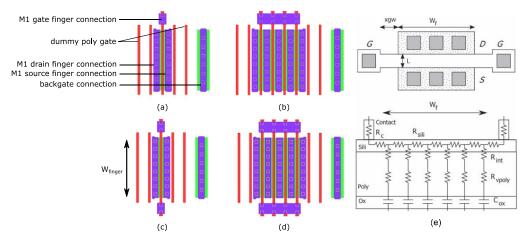

| Figure 3.26 Schematics of lvtnfet rf transistor layouts with one gate access and one (a) or 4 gate              |        |

| fingers (b); two gate accesses and one (c) or 4 gate fingers (d). Top view and cross-section of a               |        |

| single-gate-finger transistor illustrating gate resistance components [Dorm13] (e)                              |        |

| onigio gato inigor transistor indotrating gate resistance compensation [Domito] (e)                             | 03     |

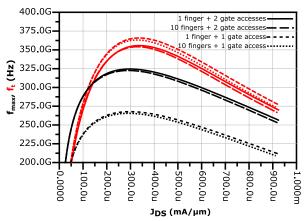

| Figure 3.27 Simulations of $f_t$ and $f_{max}$ as a function of current density for one or two gate accesses                                                                                           | ,   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| and one or ten gate fingers with $L$ =30 $nm$ and $W_{	extit{finger}}$ =800 $nm$                                                                                                                       | 64  |

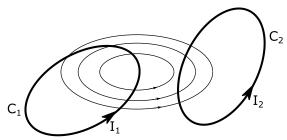

| Figure 3.28 Schematic of magnetic fields coupling between two conductor loops                                                                                                                          | 65  |

| Figure 3.29 Two rectangular conductors with magnetic field coupling                                                                                                                                    | 65  |

| Figure 3.30 Summary of the effect of magnetic coupling between two conductors on the effective                                                                                                         |     |

| inductance, resistance, and quality factor                                                                                                                                                             |     |

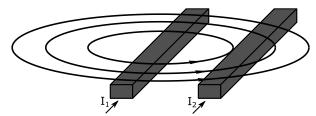

| Figure 3.31 Schematic of a conductor divided into sub-conductors where the number of conductor                                                                                                         |     |

| neighbors is proportional to its brightness                                                                                                                                                            |     |

| Figure 3.32 Current distribution in a 2µm thick and 5µm wide rectangular copper conductor at 5GI                                                                                                       |     |

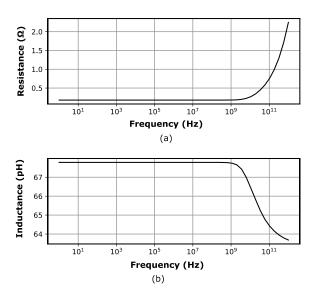

| (a) 60GHz (b) and 150GHz (c)                                                                                                                                                                           | 68  |

| Figure 3.33 Calculated resistance and inductance of a 5x2µm and 100µm long conductor over                                                                                                              |     |

| frequency                                                                                                                                                                                              |     |

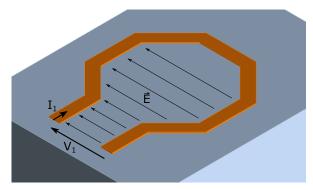

| Figure 3.34 3D view of an octagonal inductor over the substrate                                                                                                                                        | 69  |

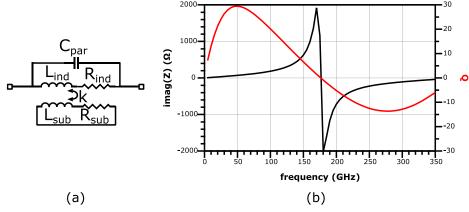

| Figure 3.35 Inductor lumped component model (a) simulated reactance and quality factor of                                                                                                              |     |

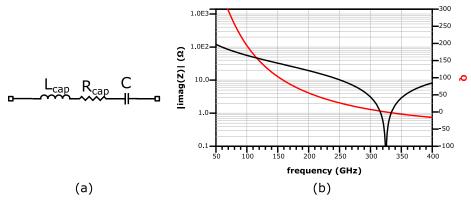

| inductor from figure 3.32 over frequency (b)                                                                                                                                                           | 70  |

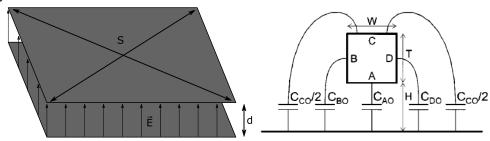

| Figure 3.36 Parallel plate capacitor schematic (a), a schematic of a rectangular conductor over a                                                                                                      |     |

| ground plane and the electrical field [stel] (b)                                                                                                                                                       |     |

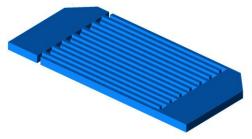

| Figure 3.37 3D view of an interdigitated capacitor                                                                                                                                                     | 72  |

| Figure 3.38 Lumped elements capacitor model (a) simulated reactance and quality factor of the                                                                                                          | 70  |

| capacitor from Figure 3.35                                                                                                                                                                             |     |

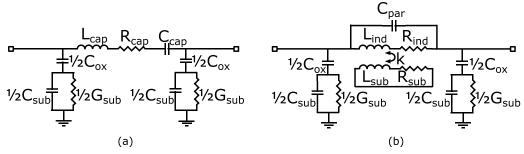

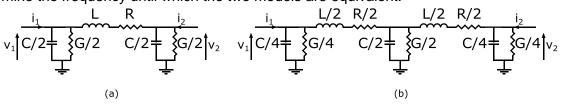

| Figure 3.39 Equivalent π lumped model of a capacitor (a) and an inductor (b)                                                                                                                           |     |

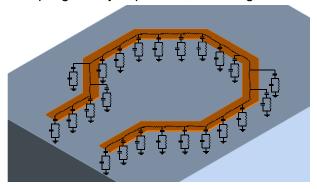

| Figure 3.40 3D view of an inductor with distributed elements                                                                                                                                           |     |

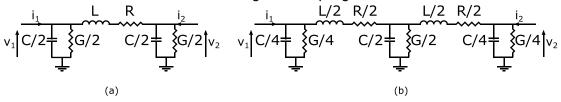

| Figure 3.41 π-model (a) and double-π-model (b) of an inductor                                                                                                                                          | 74  |

| Figure 3.42 3D view of a two-conductor transmission line (a), distributed electric model of a transmission line (b), section of a transmission line electric model (c), section of a transmission line |     |

| electric model with ground conductor impedance (d)                                                                                                                                                     |     |

| Figure 3.43 Calculated input impedance of a 50 $\Omega$ TL as a function of electrical length for different                                                                                            |     |

| load impedance: $50\Omega$ (a), $30\Omega$ (b), open and short (c)                                                                                                                                     |     |

| Figure 3.44 Cross-section view of 28nm FD-SOI process BEOL 8 metal layers stack                                                                                                                        |     |

| Figure 3.45 Cross section of different transmission line types that can be implemented in IC                                                                                                           | , , |

| technologies: Microstrip (a), CPW (b), and CPWG (c)                                                                                                                                                    | 80  |

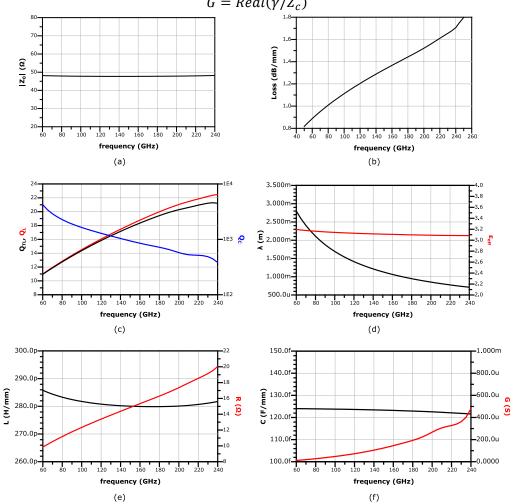

| Figure 3.46 Simulated parameters of the CPWG TL presented in Figure 3.46(c)                                                                                                                            |     |

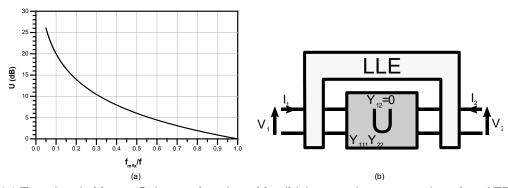

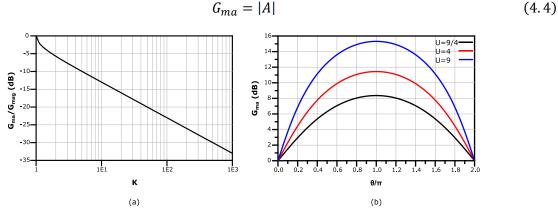

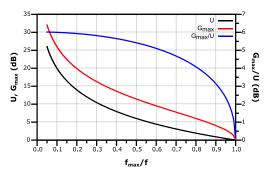

| Figure 4.1 Transistor's Mason Gain as a function of f <sub>max</sub> /f (a) general representation of an ATP wit                                                                                       |     |

| its intrinsic unilateral Gain and internal embedding (b)                                                                                                                                               |     |

| Figure 4.2 Contribution of the right factor in (4.3) as a function of K (a) G <sub>ma</sub> when K=1 for different                                                                                     |     |

| values of θ                                                                                                                                                                                            |     |

| Figure 4.3 U, G <sub>max</sub> , and the difference between both gains as a function of f <sub>max</sub> /f                                                                                            |     |

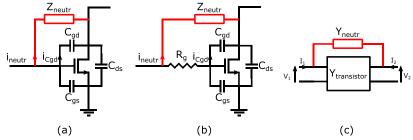

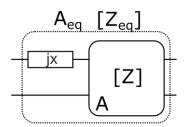

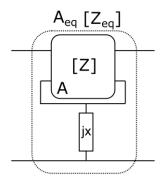

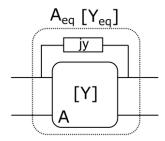

| Figure 4.4 Representation of the principle of CS neutralization (a) and representation of real                                                                                                         |     |

| implementation (b). Y-Matrix two-port representation of the neutralized CS                                                                                                                             | 87  |

| Figure 4.5 Simulation of neutralized CS's parameters at 150GHz as a function of neutralization                                                                                                         |     |

| impedance: $G_{ma}$ and $K$ (a) magnitude and phase of $A$ (b)                                                                                                                                         | 88  |

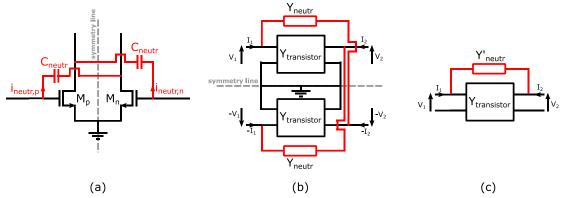

| Figure 4.6 Differential capacitively neutralized CS pair schematic (a), matrix representation (b), ar                                                                                                  | nd  |

| half equivalent matrix representation (c)                                                                                                                                                              | 89  |

| Figure 4.7 Simulations of a CS topology based on a 28nmFD-SOI transistor (L=30nm, W=16µm                                                                                                               |     |

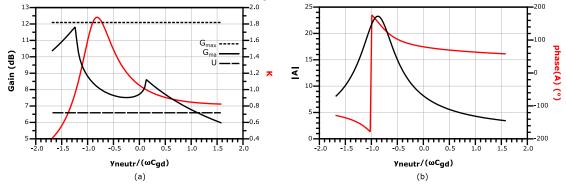

| biased at $J_{opt}$ =0.3mA/ $\mu$ m) with different neutralization methods                                                                                                                             | 90  |

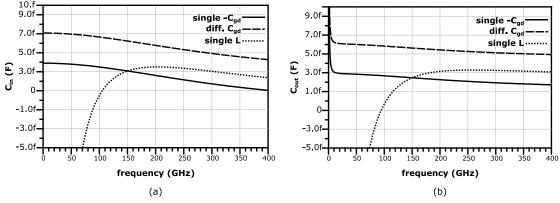

| Figure 4.8 Simulated input (a) and output (b) parallel capacitance over frequency for different                                                                                                        |     |

| neutralization methods                                                                                                                                                                                 | 90  |

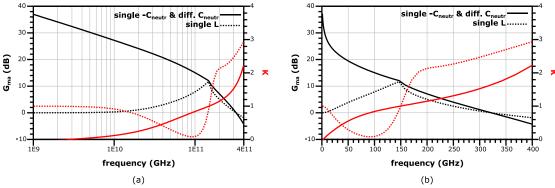

| Figure 4.9 Simulations of a CS topology based on a 28nmFD-SOI transistor (L=30nm, W=16µm                    |     |

|-------------------------------------------------------------------------------------------------------------|-----|

| biased at J <sub>opt</sub> ) with different over-neutralization methods                                     | 91  |

| Figure 4.10 190GHz over-neutralized PA in 28nm bulk CMOS [Simi21]                                           | 91  |

| Figure 4.11 210GHz over-neutralized PA in 32nm bulk CMOS [Wang14]                                           | 91  |

| Figure 4.12 107GHz amplifier with inductive feedback in 130nm bulk CMOS [Mome11]                            | 92  |

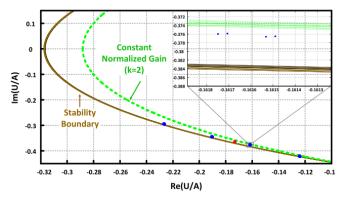

| Figure 4.13 Stability circle in the Gain plane                                                              | 92  |

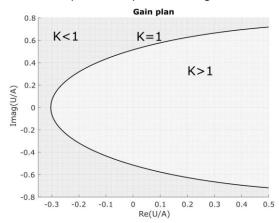

| Figure 4.14 Constant Gain circles in the Gain plane                                                         | 93  |

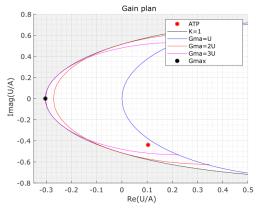

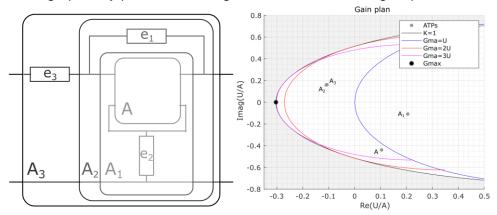

| Figure 4.15 LLE on an ATP and movement on the Gain plane                                                    | 94  |

| Figure 4.16 Schematic of an ATP embedded with a series element                                              |     |

| Figure 4.17 Schematic of an ATP embedded with a degeneration element                                        |     |

| Figure 4.18 Schematic of an ATP embedded with a parallel element                                            | 95  |

| Figure 4.19 Presented graphical design methodology [Bame17]                                                 | 96  |

| Figure 4.20 Gain boosting design method using an optimization algorithm [Kath18]                            |     |

| Figure 4.21 Three elements embedding around an ATP                                                          |     |

| Figure 4.22 Step-by-step equivalent ATP matrix calculation from starting ATP (a), intermediate              |     |

| matrix with series elements (b), total equivalent matrix with three elements LLE (c)                        | 97  |

| Figure 4.23 General representation of an LLE (a) simulations of transistor gain over frequency wi           |     |

| and without gain boosting at 190GHz (b)                                                                     |     |

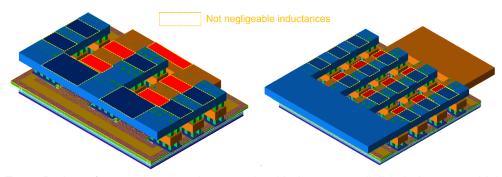

| Figure 4.24 3D view of the optimized transistor staircase finger access layout: up to third thin me         |     |

| layer (left) up to last sixth thin metal layer (right)                                                      |     |

| Figure 4.25 Drain/source finger accesses 3D view (a) electrical model (b) EM simulation (c)                 |     |

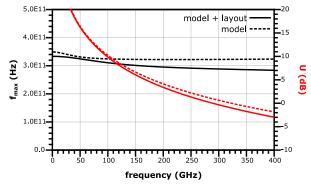

| Figure 4.26 Effect of BEOL layout on transistor model, for f <sub>max</sub> and U                           |     |

| Figure 4.27 Schematic of the transistor with its embedding elements, calculated embedding                   |     |

| elements combinations that boost the gain to G <sub>max</sub> at 190GHz                                     | 100 |

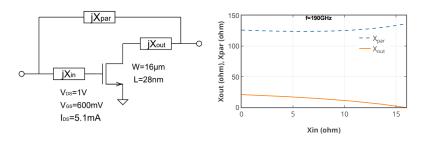

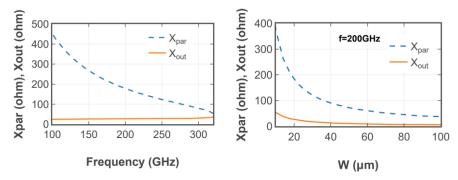

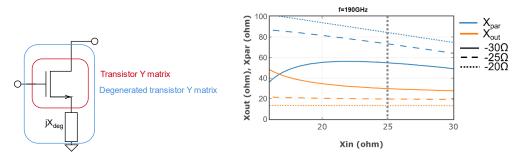

| Figure 4.28 Calculated embedding solution values in function of frequency and transistor size wh            |     |

| X <sub>in</sub> =0                                                                                          |     |

| Figure 4.29 Pre-embedded CS transistor with degeneration (left) and calculation of embedding                |     |

| elements towards G <sub>max</sub> for different degeneration impedances (right)                             | 100 |

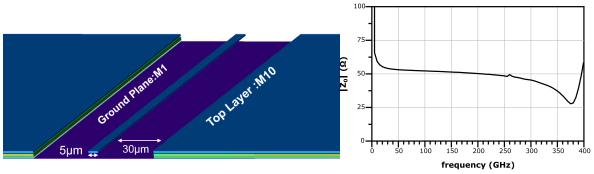

| Figure 4.30 3D view of the 50 $\Omega$ Microstrip transmission line used in the amplifier (left) and simula |     |

|                                                                                                             | 101 |

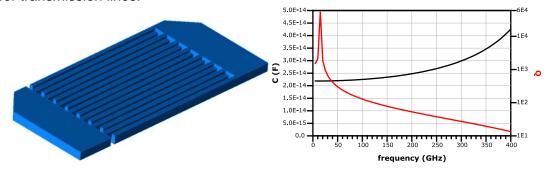

| Figure 4.31 3D view of the interdigitated capacitance used for the degeneration (left) simulated            |     |

| capacitance value and quality factor (right)                                                                | 102 |

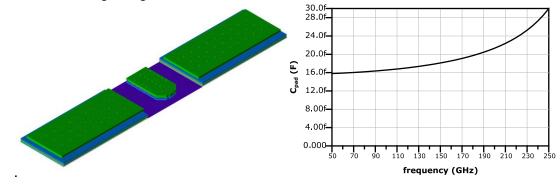

| Figure 4.32 3D view of the used RF pad in the amplifier (left) and simulated pad capacitance ove            |     |

| frequency (right)                                                                                           |     |

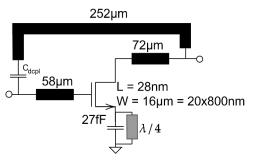

| Figure 4.33 Schematic of the core gain boosted amplifier at 190GHz                                          |     |

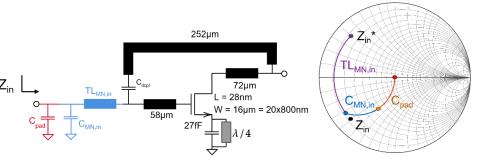

| Figure 4.34 Addition of the input impedance matching network schematic (left) and impedance                 |     |

| transformation represented on a Smith chart (right)                                                         | 103 |

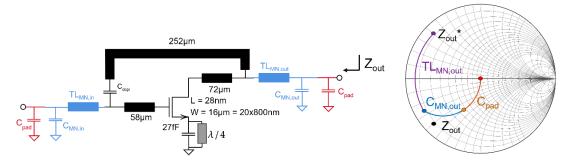

| Figure 4.35 Addition of the output impedance matching network schematic (left) and impedance                |     |

| transformation represented on a Smith chart (right)                                                         | 103 |

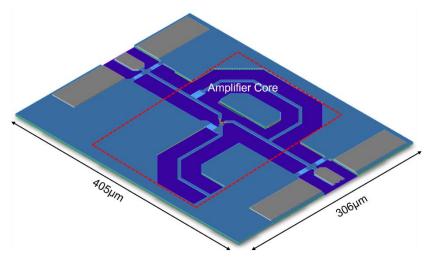

| Figure 4.36 Gain Boosted Amplifier 3D view                                                                  |     |

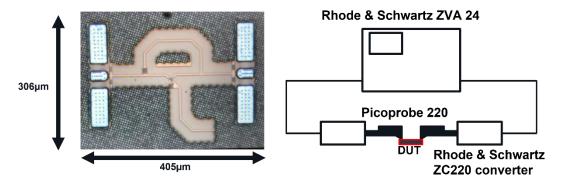

| Figure 4.37 Chip microphotograph (left) measurement setup schematic (right)                                 |     |

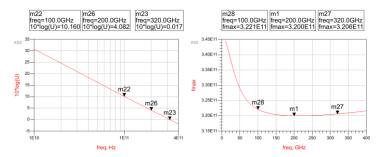

| Figure 4.38 S-parameters measurement and simulations comparison [Sadlo21]                                   |     |

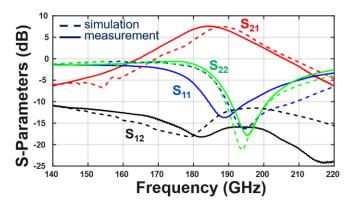

| Figure 4.39 Simulation to measurement S-Parameters comparison                                               |     |

| Figure 4.40 Amplifier measurements on multiple dies                                                         |     |

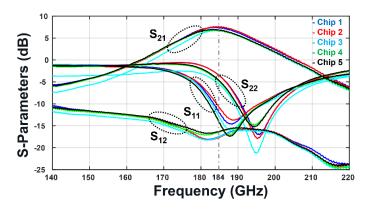

| Figure 4.41 Dispersion on multiple dies measurement                                                         |     |

| Figure 4.42 Large signal measurements at 184GHz: gain, output power, and PAE                                |     |

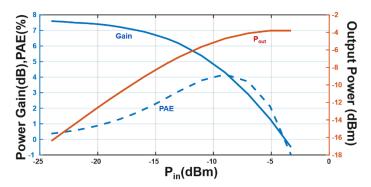

| Figure 4.43 Large signal performances at 184GHz                                                             |     |

| Figure 4.44 Comparison table with the state-of-the-art                                                      |     |

| · · · · · · · · · · · · · · · · · ·                                                                         |     |

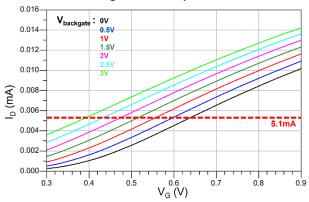

| Figure 4.45 Measured current consumption versus gate voltage for different backgate biases                                                                                | 107   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

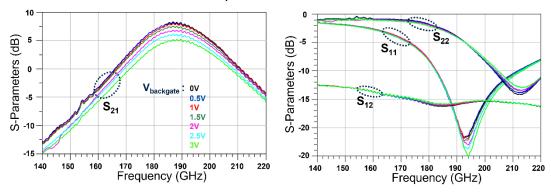

| Figure 4.46 S-parameters measurement of the Gain boosted amplifier at constant DC current f                                                                               |       |

| different backgate voltages                                                                                                                                               |       |

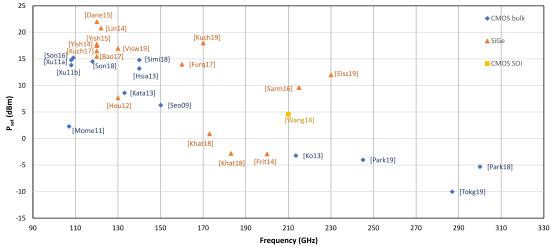

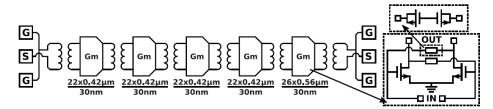

| Figure 5.1 State of the Art of PA around 200GHz in CMOS technologies                                                                                                      |       |

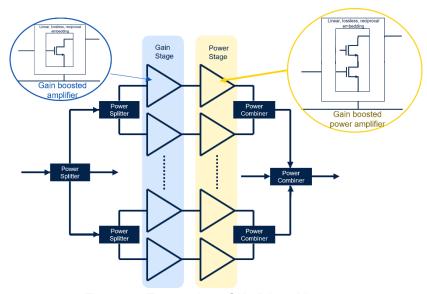

| Figure 5.2 Targeted 200GHz PA architecture                                                                                                                                |       |

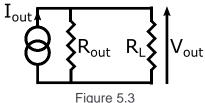

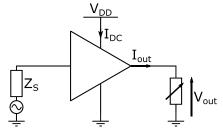

| Figure 5.3                                                                                                                                                                |       |

| Figure 5.4 Load-pull principal schematic                                                                                                                                  |       |

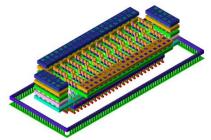

| Figure 5.5 3D view of a 26x600nm transistor cell laid out up to 6th thin metal layer                                                                                      |       |

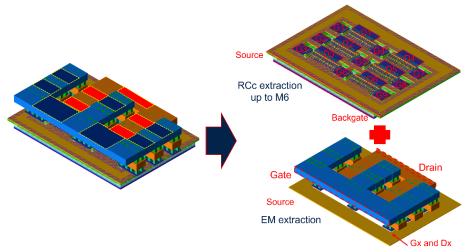

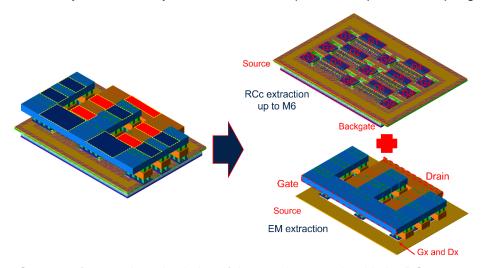

| Figure 5.6 Strategy of a complete simulation of the transistor matrix with the RCc extracted low part and EM simulated higher part                                        |       |

| Figure 5.7 Summary of transistors' f <sub>max</sub> for L=30nm                                                                                                            |       |

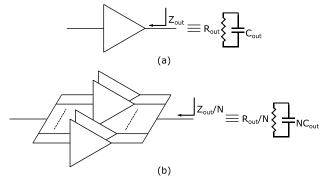

| Figure 5.8 Equivalent RC parallel output impedance of an amplifier (a) and of N parallel amplifi                                                                          |       |

| (b)                                                                                                                                                                       |       |

| Figure 5.9 Equivalent RC parallel output impedance of a differential amplifier                                                                                            |       |

| Figure 5.10 Impact of parasitical access components on single scheme operation (a) and differ                                                                             |       |

| scheme operation (b)                                                                                                                                                      |       |

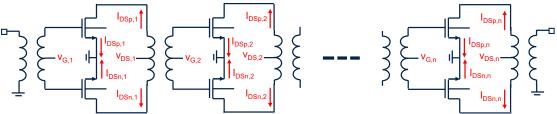

| Figure 5.11 Cascaded N CS stages with DC to RF couplers present on each gate and drain                                                                                    |       |

| Figure 5.12 Cascaded N CS stages with DC pass and DC block components                                                                                                     |       |

| Figure 5.13 Coupled inductors transformer-based N CS stage amplifier                                                                                                      |       |

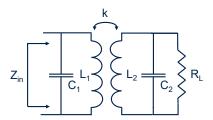

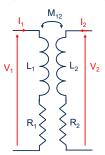

| Figure 5.14 Schematic of a transformer with an R//C load                                                                                                                  |       |

| Figure 5.15 Characteristic pulsations of a transformer                                                                                                                    |       |

| Figure 5.16 Coupled inductors with series resistance two port                                                                                                             |       |

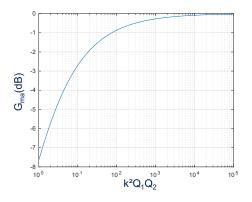

| Figure 5.17 Transformer $G_{ma}$ ad a function of the product of the coupling factor and quality fact                                                                     |       |

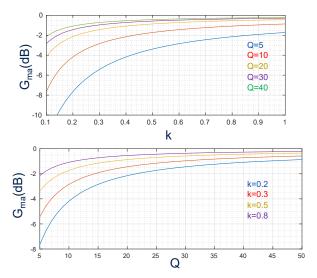

| . Iguio erro riancionio. Gina da anaronom er uno product er uno coupinig racio: ana quant, raci                                                                           |       |

| Figure 5.18 Transformer $G_{ma}$ ad a function of the coupling factor (up) and geometrical mean qu                                                                        |       |

| factor (down)                                                                                                                                                             | -     |

| Figure 5.19 Layout view and simulations of an example of broadband operating transformer for                                                                              |       |

| 90Ω//30fF to 50Ω matching                                                                                                                                                 |       |

| Figure 5.20 Marchand Balun principle schematic                                                                                                                            | 121   |

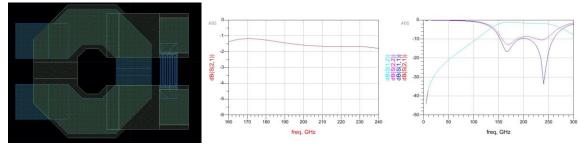

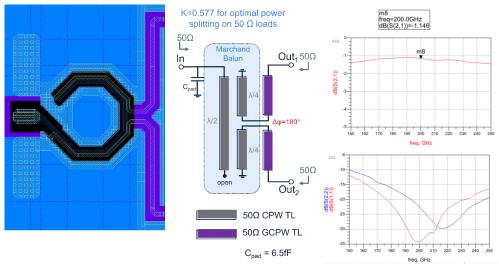

| Figure 5.21 Designed Marchand balun at 200GHz in 28nm-FDSOI with layout view, schematic                                                                                   | , and |

| simulated S-parameters (with a differential 100Ω port between ports 2 and 3)                                                                                              | 122   |

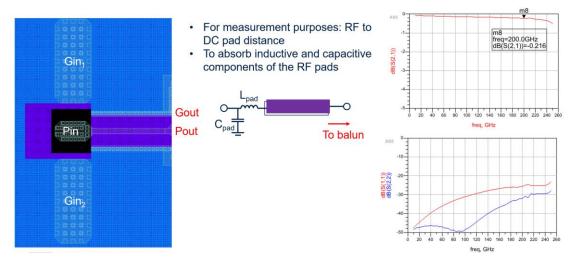

| Figure 5.22 Designed and simulated transition between the RF pads and the balun                                                                                           | 123   |

| Figure 5.23 Schematic of the designed differential neutralized CS amplifier and the transistor                                                                            |       |

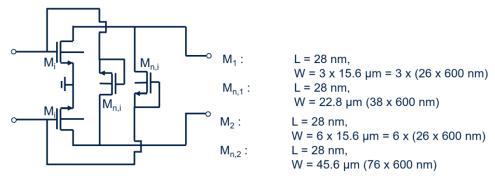

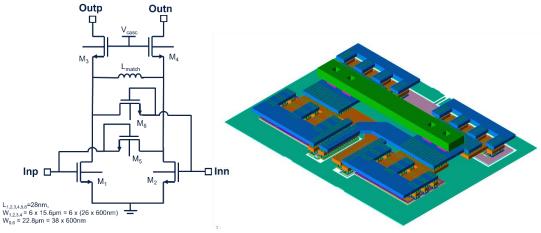

| dimensions                                                                                                                                                                | 123   |

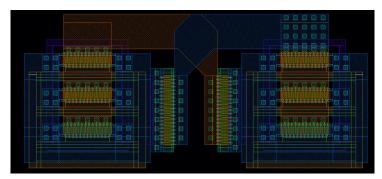

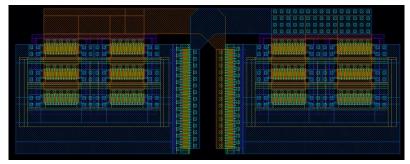

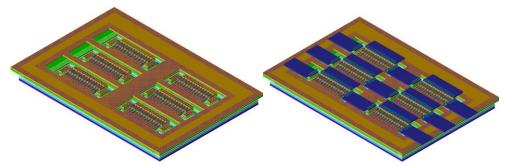

| Figure 5.24 3-transistor matrix differential neutralized CS amplification stage                                                                                           | 124   |

| Figure 5.25 6-transistor matrix differential neutralized CS amplification stage                                                                                           | 124   |

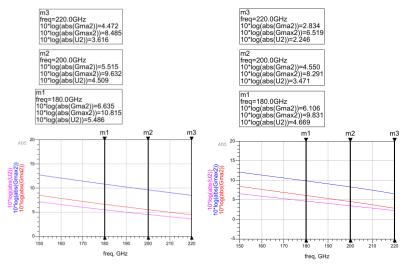

| Figure 5.26 Simulated gain metrics of the CS stages: 3-transistor matrix (left) and 6-transistor r                                                                        |       |

| (right)                                                                                                                                                                   |       |

| Figure 5.27 Equivalent RC components of the input and output impedances from the designed                                                                                 |       |

| amplification stages                                                                                                                                                      |       |

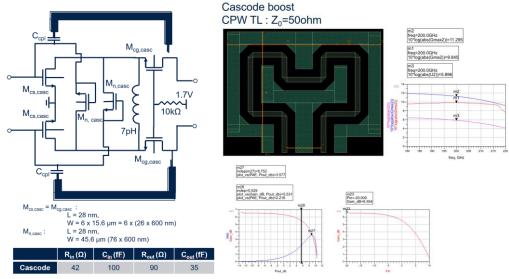

| Figure 5.28 Differential Cascode with internal matching schematic and 3D view                                                                                             |       |

| Figure 5.29 Simulations of the Gain performances and Large signal performances of the Casco                                                                               |       |

| stage                                                                                                                                                                     |       |

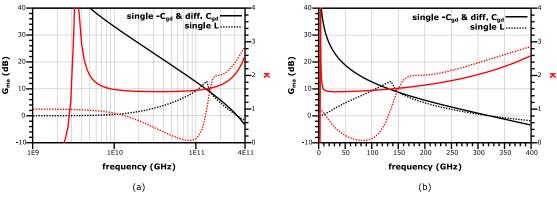

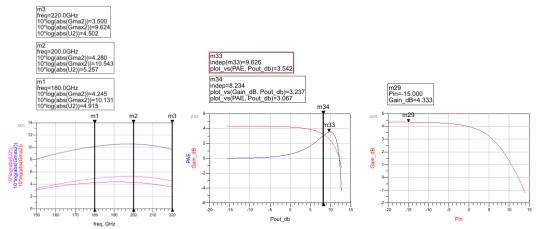

| Figure 5.30 6-transistors matrix used for broadband gain boosting (left) calculated requires values for this transistor and the impedance over frequency of the chosen TI |       |

| X <sub>par</sub> for this transistor and the impedance over frequency of the chosen TL                                                                                    |       |

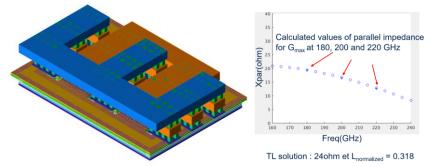

| Figure 5.31 Designed boosted CS stage schematic, designed feedback TL, and simulated resugning of the amplifier stage.                                                    | •     |

| gain of the amplifier stage                                                                                                                                               | 12/   |

| Figure 5.32 Designed boosted Cascode stage schematic, designed feedback TL, and simulate                           | ∍d    |

|--------------------------------------------------------------------------------------------------------------------|-------|

| resulting gain and large signal performances of the amplifier stage                                                | 127   |

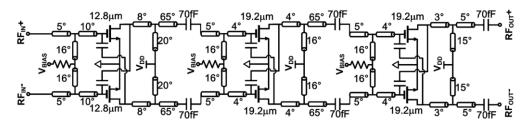

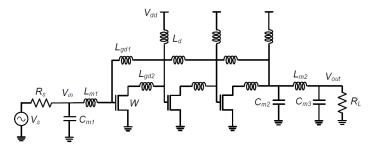

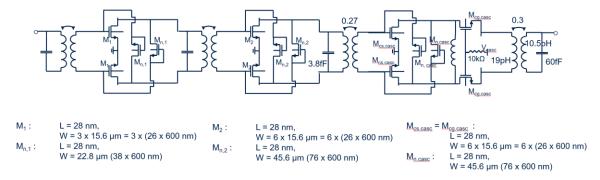

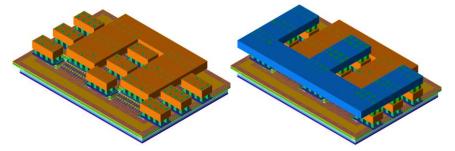

| Figure 5.33 Schematic of the classic PA implementation in 28nm-FDSOI                                               | 128   |

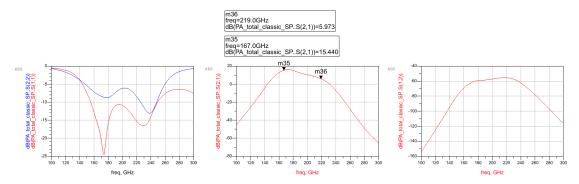

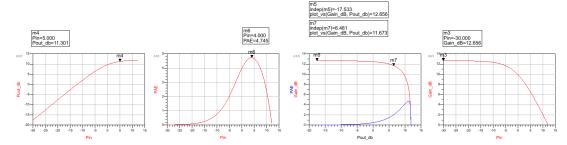

| Figure 5.34 S-parameters simulations of the classic PA implementation                                              | 129   |

| Figure 5.35 Large signal simulations at 200GHz of the classic PA implementation                                    | 129   |

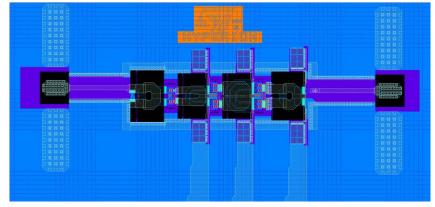

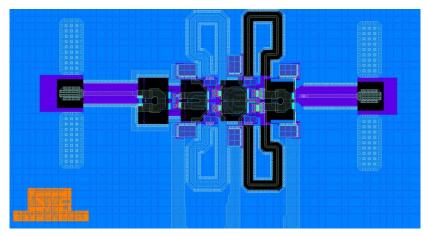

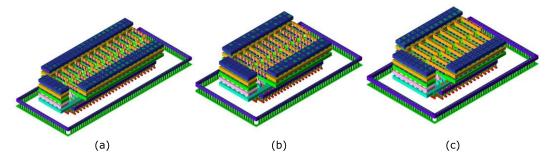

| Figure 5.36 Layout view of the classic PA                                                                          | 129   |

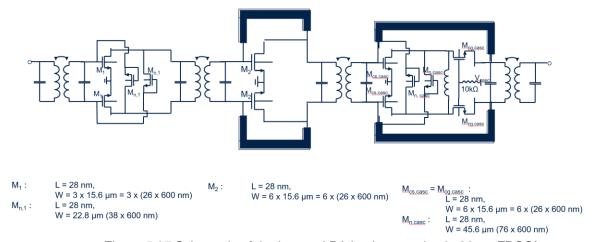

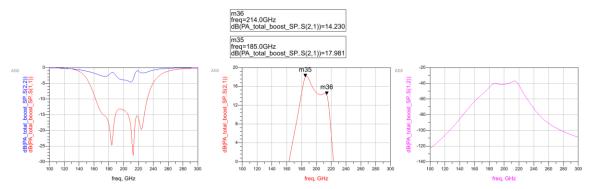

| Figure 5.37 Schematic of the boosted PA implementation in 28nm-FDSOI                                               | 130   |

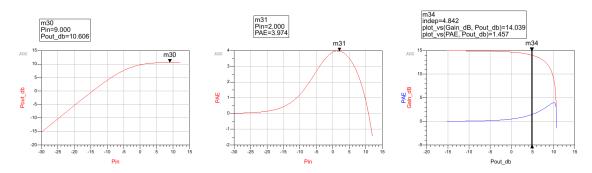

| Figure 5.38 S-parameters simulations of the boosted PA implementation                                              |       |

| Figure 5.39 Large signal simulations at 200GHz of the boosted PA implementation                                    | 130   |

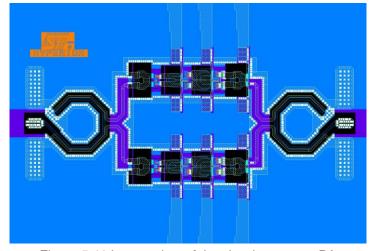

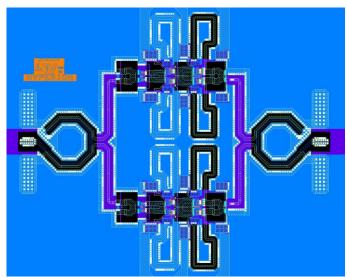

| Figure 5.40 Layout view of the boosted PA                                                                          | 131   |

| Figure 5.41 Layout view of the classic two-way PA                                                                  | 131   |

| Figure 5.42 Layout view of the boosted two-way PAPA                                                                | 131   |

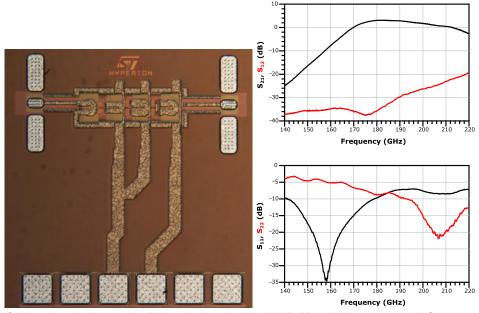

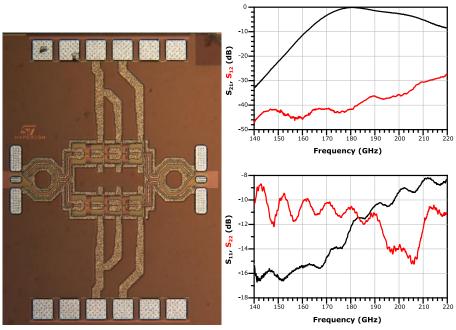

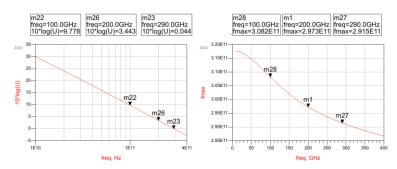

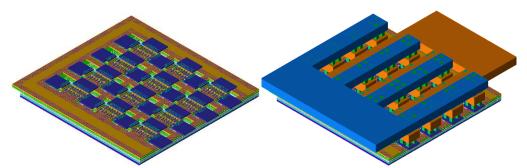

| Figure 5.43 Chip microphotograph of the simple classic PA (left) and the measured S-paramet                        |       |

| (right)                                                                                                            |       |

| Figure 5.44 Chip microphotograph of the double classic PA (left) and the measured S-parame                         |       |

| (right)                                                                                                            |       |

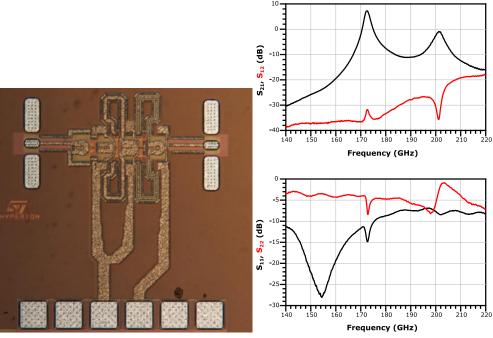

| Figure 5.45 Chip microphotograph of the simple boosted PA (left) and the measured S-parame                         | eters |

| (right)                                                                                                            |       |

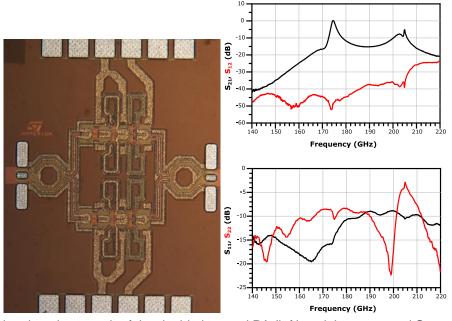

| Figure 5.46 Chip microphotograph of the double boosted PA (left) and the measured S-param                          |       |

| (right)                                                                                                            |       |

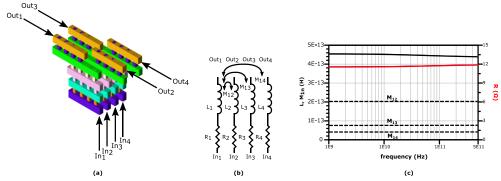

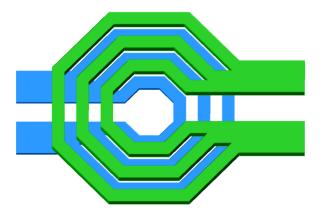

| Figure 6.1 Parallel interleaved coupled inductors                                                                  |       |

| Figure 6.2 Gain-boosted multi-stage amplifier with body bias control                                               |       |

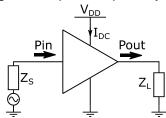

| Figure A.1 Generic PA schematic with source and load impedance                                                     |       |

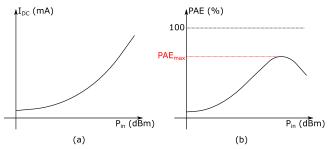

| Figure A.2 P <sub>out</sub> (a) and Gain (b) response of a generic PA as a function of input power P <sub>in</sub> |       |

| Figure A.3 Current consumption (a) and PAE (b) of a PA as a function of P <sub>in</sub>                            |       |

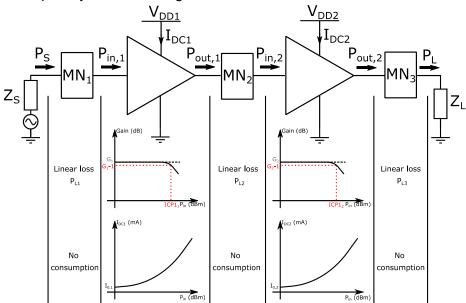

| Figure A.4 Two-stage power amplifier schematic with individual component response as a fund                        |       |

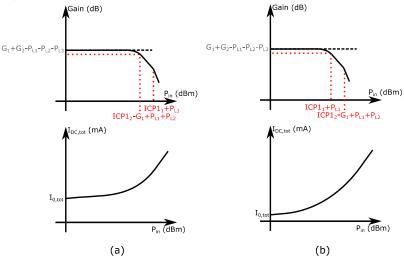

| of power levels                                                                                                    |       |

| Figure A.5 Total gain response and current consumption of two stages PA for a high P <sub>sat</sub> first s        |       |

| (a) and a moderate P <sub>sat</sub> second stage (b)                                                               | -     |

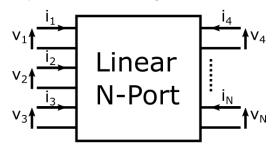

| Figure C.1 Schematic of a linear N-port network                                                                    |       |

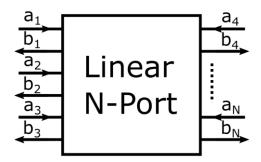

| Figure C.2 Linear N-port network with the incident and reflected power waves                                       |       |

| Figure C.3 Schematic of a linear two-port                                                                          |       |

| Figure C.4 Conversion matrixes                                                                                     |       |

| Figure C.5 Combination of parallel (left) and series (right) LTPs                                                  |       |

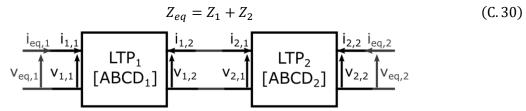

| Figure C.6 Combination of cascaded LTPs                                                                            |       |

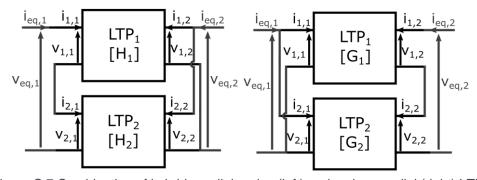

| Figure C.7 Combination of hybrid parallel-series (left) and series-parallel (right) LTPs                           | 151   |

| Figure C.8 Schematic of a voltage source $V_S$ with an internal impedance $Z_L$ connected to a loa                 |       |

| impedance Z <sub>L</sub>                                                                                           |       |

| Figure C.9 Schematic of a linear two port with one port connected to a voltage source and the                      |       |

| connected to a load                                                                                                |       |

| Figure D.1 π-model (a) and double-π-model (b) of an inductor                                                       |       |

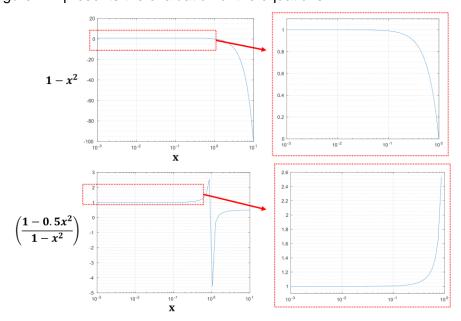

| Figure D.2 Evaluation of the ratio between real and extracted component values as a function                       |       |

| normalized frequency                                                                                               |       |

| Figure D.3 Evaluation of Equations D.14 and D.15 for the different order of magnitudes of                          |       |

| frequencies                                                                                                        | 157   |

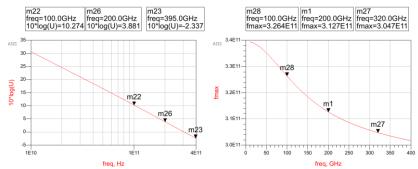

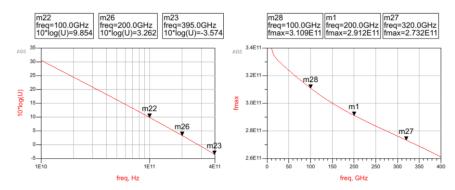

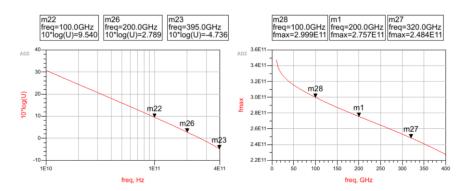

| Figure E.1 Simulated Mason's gain (a) and extrapolated f <sub>max</sub> (b) over frequency for a 28nm FD           |       |

| DK transistor model.                                                                                               |       |

|                                                                                                                    |       |

| Figure E.2 Simulated Mason's gain (a) and extrapolated fmax (b) over frequency for a 28nr             | n FD-SOI                |

|-------------------------------------------------------------------------------------------------------|-------------------------|

| transistor with RCc extracted layout                                                                  | 160                     |

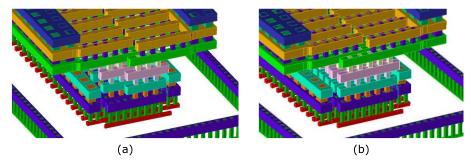

| Figure E.3 3D views of multiple combinations of finger width and number of fingers to pro-            | duce a W <sub>tot</sub> |

| of around 16µm: 26x600nm (a) 20x800nm (b) 16x1000nm (c)                                               | 161                     |

| Figure E.4 3D view of the transistor staircase finger accesses using half the width (a) and           | full width              |

| (b) for the drain and source fingers access.                                                          | 161                     |

| Figure E.5 Comparison of f <sub>max</sub> results of different transistor geometries                  |                         |

| Figure E.6 3D view of a 20x600nm transistor cell laid out up to 6th thin metal layer with gar         | te access               |

| on both sides                                                                                         | 162                     |

| Figure E.7 Simulated Mason's gain (a) and extrapolated f <sub>max</sub> (b) over frequency for a 28nr | n FD-SOI                |

| transistor with RCc extracted layout for a two-side gate access                                       | 162                     |

| Figure E.8 3D view of a 6-transistor matrix up to the last thin metal layer                           | 163                     |

| Figure E.9 3D view of a 6-transistor matrix up to the thick metal layers                              | 163                     |

| Figure E.10 3D view of a 12-transistor matrix                                                         | 163                     |

| Figure E.11 3D view of a 6 and 12 transistor matrix with the non-negligible inductances hi            | ghlighted               |

|                                                                                                       | 164                     |

| Figure E.12 Strategy of a complete simulation of the transistor matrix with the RCc extract           |                         |

| part and EM simulated higher part                                                                     | 164                     |

| Figure E.13 Simulated Mason's Gain and f <sub>max</sub> of 6 transistor matrix                        |                         |

| Figure E.14 Simulated Mason's Gain and f <sub>max</sub> of 12 transistor matrix                       | 165                     |

| Figure E.15 Comparison summary of the transistor matrixes' performances. L=30nm                       | 165                     |

## **Chapter 1** Introduction

The design of Radio-Frequency (RF) circuits has first been developed with the main target of transmitting data wirelessly over long distances. As the field grew and the technologies and the circuit performances improved new applications were thought of. The use of higher and higher bandwidths and frequencies created opportunities to exploit wave-matter interactions. The millimeter-wave (mmWave) and Terahertz (THz) frequencies belong to the highest frequencies that can be generated today by RFIC technologies. The matter reacts differently over this large spectrum part and signals of these bands can be used for spectroscopy, imaging, or space radiation observation. In addition, the photon's energy is very low compared to other imaging techniques such as X-Rays, and consequently mmWave and THz frequencies do not ionize and damage the matter. The wavelength in free space is equal to 3mm at 100GHz and further decreases with higher frequencies. Thus, very precise distance measurements can be done using these frequency signals in industry, in radar applications, and in the biomedical field. Wireless communications also benefit greatly from the large available bandwidth in these bands. This enables data rates one order of magnitude higher than mmWave 5G applications, up to hundreds of gigabits per second. With the available low-cost silicon technologies, the development of RF front ends opens the door to numerous mass-market disruptive applications.

However, the implementation of such RFICs deals with components close to their limits and lumped element approximation is no longer applicable. Hence the device modeling, the passive elements design and simulation, and the circuit blocks architecture must be adapted to the constraints. This thesis work has the three following main goals to path the way towards the design of sub-THz RFIC systems:

- -After evaluating the limitations of devices, propose a design methodology to increase the transistor and passive devices' performances

- -Propose innovative circuit architectures adapted to the high operation frequencies by taking advantage of the small transmission line and passive elements due to the short wavelength

- -Demonstrate the capability of the VLSI CMOS FD-SOI technology for future 6G and other over 100GHz applications.

This manuscript is composed of six chapters. The first one is dedicated to the general introduction with the presentation of the context, the main goals, and the outline of this thesis.

The second chapter presents the available opportunities in mmWave and sub-THz frequency bands. The state of the art in these bands is presented and the design challenges are discussed. Finally, it highlights the problems that this thesis wants to address.

The third chapter presents the integrated circuit (IC) technologies and their limitations to design at mmWave and sub-THz frequencies. The high-frequency transistor and passive device's behavior are presented.

The fourth chapter studies the Gain Boosting design technics to enable the design close to the  $f_{max}$ . It presents a design methodology for sub-THz Gain Boosted amplifiers and the implementation of an amplifier at 184 GHz in 28nm FD-SOI CMOS technology from STMicroelectronics.

#### **Chapter 1 Introduction**

The fifth chapter further investigates the gain boosting techniques for the design of sub-THz amplifiers having at the same time great performances in gain, saturation power level, and operation frequency bandwidth. The limitations of each metric are studied, and large bandwidth gain boosting, power combining, and large bandwidth impedance matching technics are presented. Finally, the design and measurement results of a 190GHz power amplifier are presented.

The last sixth chapter of this thesis concludes with the presented work and discusses the future research perspectives regarding the integration of systems in VLSI technologies operating at mm-Wave and THz frequency bands.

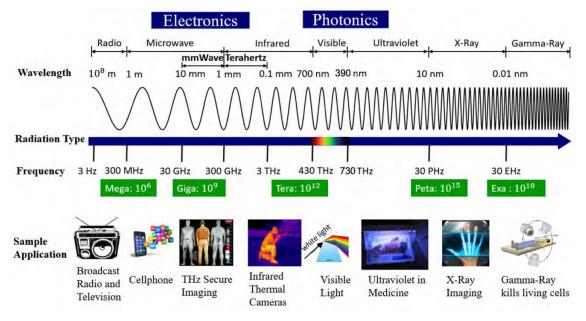

The terahertz (THz) frequency band is located between the millimeter wave and the far-infrared spectrums, in the 300GHz to 3THz range (Figure 2.1). The wavelengths in vacuum at these frequencies are under the millimeter and range from 0.1mm to 10µm. At these frequencies, the short wavelength can be used for precise imaging or distance measurements for industrial or radar applications. Some materials are transparent for these frequency waves and these properties can be exploited to realize scanning for security or industrial purposes. Along the large THz frequency bandwidth, numerous molecular absorption frequencies are present and therefore it can be used for spectroscopy. These frequencies are neither harmful nor destructive as the X-Rays are and consequently are an interesting alternative. Finally, a relatively small bandwidth to the frequency of operation represents multiple gigahertz (GHz) that enables from multiple to hundreds of gigabits per second communication data rates. These frequency bands are disruptive for wireless communication given the achievable bandwidths.

Figure 2.1 The electromagnetic spectrum, and various applications as a function of frequency [Rapp19]

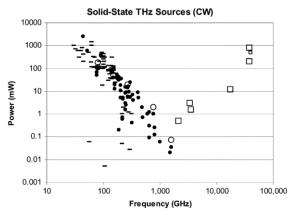

The THz frequencies offer a large scope of new applications but the available components operating at these frequencies are limited. Frequencies above the THz bands are generated with optical components while below frequencies are in the millimeter wave range and are thus generated with electronic circuits. The lack of solutions in this frequency band is known as the THz gap and is illustrated in Figure 2.2.

Figure 2.2 The THz gap with respect to source technology, including quantum cascade lasers (□), frequency multipliers (•), and other electronic devices (–). Hollow symbols represent cryogenic results [Crow05]

The sub-THz band is in the 100GHz-1THz range and still presents the advantages and opportunities of the THz band. However, it is in the scope of operation of recent electronic devices that present maximal operation frequencies of a couple of hundred Gigahertz. Therefore, research to integrate the previously described systems in silicon integrated circuits is increasingly present in the academic and industrial worlds. In addition, the low cost of silicon-integrated circuit technologies enables the deployment of sub-THz circuits for mass-consumer markets. However, the design of such circuits is challenging as the operation frequencies are close to the device's limits. New architecture and design methodologies must be developed to overcome these limitations.

The following parts of this chapter will first present the main possible applications at sub-THz frequencies. Then the need for high wireless communication data rates will be discussed. Following, possible communication architecture will be presented and a summary of the state of the art of the literature will be depicted. Finally, the actual limits of the circuits presented in the SOA will be highlighted and compared with the objectives of the thesis.

#### 2.1 Physical opportunities of the sub-THz spectrum

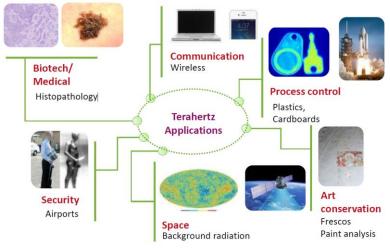

Figure 2.3 illustrates the numerous possible applications that enable the sub-THz spectrum, the main applications are presented in the following sections.

Figure 2.3 Main THz applications map [Pfei19]

#### 2.1.1 Imaging

The transparency of some materials to THz waves opens the opportunity to realize imaging captors using these wavelengths. Multiple cases can leverage this technology.

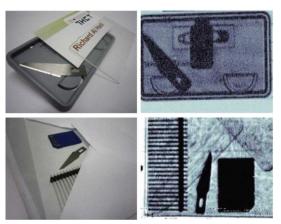

Security imaging can greatly benefit from it as metallic materials are reflective at these frequencies and the detection of weapons can be done as depicted in Figure 2.4.

Figure 2.4 Transmission-mode images at THz of a badge and an envelope [Hadi11]

THz security scanning has the advantage of detecting metallic objects without harming people or altering materials. It has all the advantages of X-ray imaging as it depicts the objects' forms but without the inconveniences of the X-ray systems that require specific expensive radiation generators. Silicon solutions are handy and low-cost in comparison.

On the other side of imaging applications, biomedical imagery can benefit from THz as well. The organic matter reaction to the THz illumination depends on its chemical composition. Therefore, THz imaging can be used to discriminate abnormal tissues. Figure 2.5 depicts the imagery of a mouse brain where the cancerous parts appear on the THz images.

Figure 2.5 THz images of a mouse brain presenting cancerous parts [Cheo17]

#### 2.1.2 Spectroscopy

Sub-THz and THz frequency bands are sufficiently large to present multiple molecular absorption frequencies. Spectroscopy can be realized using these frequencies to identify specific components. Hence, sub-THz circuits can be used for the pharmaceutics industry or gas detection. Figure 2.6 presents a 220 to 320GHz CMOS rotational spectrometer for molecular detection [Wang18].

The spectrometer can analyze a mixture of gazes and simultaneously identify multiple molecules from the absorption rays in the 220 to 320GHz band.

Figure 2.6 Dual-THz-comb spectrometer for gas sensing [Wang18a]

THz spectrum enables unprecedented wave-matter interaction applications using IC technologies. Molecular absorption frequency is a very precise data that can be used as an absolute reference. Another use of the wave-matter interaction is a chip-scale clock referenced on a molecular absorption frequency. By referencing the electronic clock oscillation to the rotational-mode transition of OCS molecules at the sub-THz, the clock achieves an "atomic-clock-grade" precision using a mainstream 65nm CMOS process IC and a THz waveguide [Wang18b].

Figure 2.7 CMOS molecular clock implementation [Wang18b]

#### 2.1.3 Radar

High-resolution integrated radars are crucial in nowadays' automotive, vital sign, and security sensing applications. The sub-THz/THz spectrum shows great opportunities in both high-resolution and all-weather radar imaging capabilities.

Figure 2.8 THz images [Hoss21]

Figure 2.8 presents the micrometer distance measurement capability of a 250GHz FMCW radar [Hoss21]. Thanks to the short wavelength a micrometer resolution can be achieved. It has promising applications in the industry for process and quality control.

#### 2.1.4 Communication

The world is increasingly interconnected and every increase in available bandwidth is leveraged by actual applications and enables new disruptive usages. The number of connected devices increases rapidly as well, leading to an exponential increase in wireless communication capability demand. The spectrum is saturated up to 100GHz and a significative bandwidth increase is not possible in the frequency ranges used for 5G, 4G, or Wifi standards. The next section focusses on the motivations to use the sub-THz spectrum for the next generations of wireless communications.

#### 2.2 Largely available bandwidths, increasing needs for data rates

The data rate of communication has been increasing exponentially year-by-year as presented in Figure 2.9 [Fuji18]. Wired communications were dominant regarding the data rates for decades. Wireless communications were in another class and the comparison wasn't pertinent. However, the demand for wireless data rates increased much faster than the wired one to the point that we can predict that in the next decade, the wireless needs will meet the optical wired data-rates. Conversely, in the optical domain, the wireless world requires disruptive innovations to follow the demand. Hundreds of Gigabits per second are conceivable with actual research results but the increase to the Terabit per second area still requires R&D.

Figure 2.9 Evolution of data rate of wired communication and wireless communication over the years [Fuji18]

Successive generations of communication standards were developed by the industry, with a couple of Mb/s for the first indoor generations and only hundreds of kilobits per second for the first outdoor standards. In comparison to today's available rates, even with a 1.4-time increase year-by-year [Okad22], the first years' rates were still low, but each evolution opened the door for disruptive applications. Figure 2.10 presents the chronological evolution of these standards since 1995 and predicts by following the trend of an available 1Tbps link in 2035.

Figure 2.10 Evolution of wireless communication standards' data rates over the years [Okad22]

The rate of information that can be transmitted is bounded to two metrics, the used bandwidth and the signal-to-noise power ratio. Channel capacity C is the theoretical upper boundary on the information data rate that can be communicated for any error rate. The Shannon-Hartley theorem gives the following expression of C:

$$C = BW \cdot \log_2\left(1 + \frac{S}{N}\right) \tag{2.1}$$

Where *BW* is the signal bandwidth, S is the average signal power over the bandwidth, and N is the average noise power over the bandwidth.

The spectral efficiency can be defined as the maximal data rate per unit of frequency. Therefore, it is bounded as well with a quantity defined from (2.1):

$$\eta = \frac{C}{BW} = \log_2\left(1 + \frac{S}{N}\right) \tag{2.2}$$

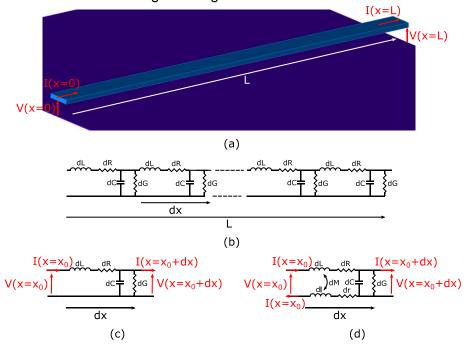

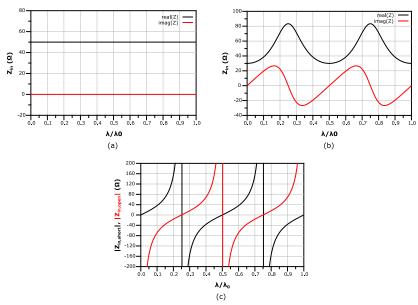

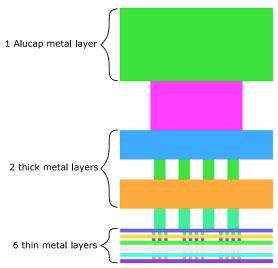

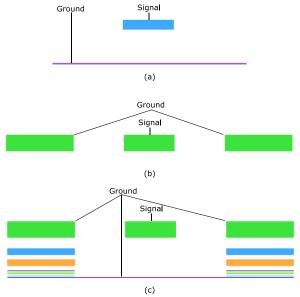

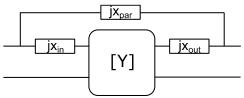

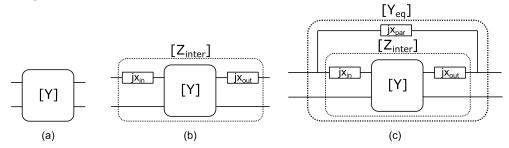

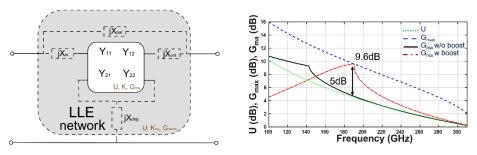

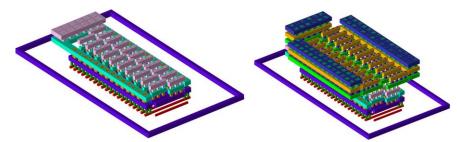

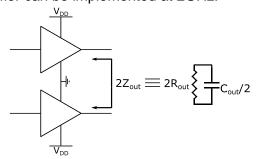

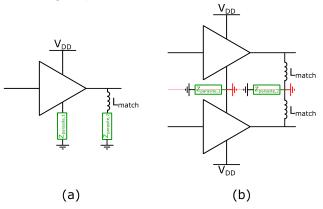

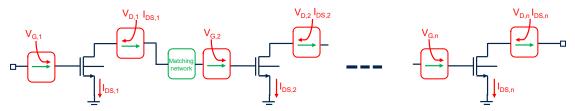

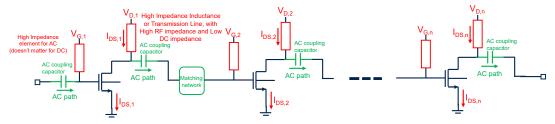

Equation (2.2) shows that complex signal modulations, which increase the spectral efficiency, require a high signal-to-noise ratio. Hence the spectral efficiency is limited by the signal power level. However, the signal power is limited for safety and practical reasons. For connected objects, battery life is crucial, and it is desired to reduce power consumption. Consequently, the bandwidth remains the only leverage to increase the channel capacity. For this reason, wireless standards tend to use higher frequencies to address the demand. Nowadays, the last generations of Wifi use 2.4GHz, 5GHz, and up to 10GHz frequency bands. For higher short-distance data rates, the WiGig uses the V-Band 60GHz available band. For outdoor technologies, the last 5G standard uses mm-Wave frequency bands mostly around 30GHz. Figure 2.11 presents the available spectrum and channel bandwidth in function of the carrier frequency. The link capacity is also depicted and illustrates the correlation between used bandwidth and capacity.