## Processor and memory co-scheduling of embedded real-time applications on multicore platforms

Ikram Senoussaoui

### ► To cite this version:

Ikram Senoussaoui. Processor and memory co-scheduling of embedded real-time applications on multicore platforms. Embedded Systems. Université de Lille; Université d'Oran 1 Ahmed Ben Bella, 2023. English. NNT: . tel-04495150v1

## HAL Id: tel-04495150 https://theses.hal.science/tel-04495150v1

Submitted on 8 Mar 2024 (v1), last revised 23 May 2024 (v2)

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## UNIVERSITY OF LILLE UNIVERSITY OF ORAN1

## A thesis submitted in fulfillment of the requirements for the degree of Doctor of Philosophy

Discipline: Computer Science

## Ikram SENOUSSAOUI

## Processor and memory co-scheduling of embedded real-time applications on multicore platforms

Co-ordonnancement processeur et mémoire des applications temps-réel sur les plateformes multicœurs

Under the direction of: Pr. LIPARI Giuseppe Pr. BENHAOUA Mohammed Kamel

December 14, 2023

| Maryline CHETTO          | Full Professor, LS2N, University of Nantes, France      | Referee    |

|--------------------------|---------------------------------------------------------|------------|

| Hadda CHERROUN           | Full Professor, LIM, University of Laghouat, Algeria    | Referee    |

| Sidi Mohammed BENSLIMANE | Full Professor, LabRI, ESI-SBA, Algeria                 | Examiner   |

| Emmanuel GROLLEAU        | Full Professor, LIAS, ISAE-ENSMA Poitiers, France       | Examiner   |

| Bilel DERBEL             | Full Professor, CRIStAL, University of Lille, France    | President  |

| Houssam-Eddine ZAHAF     | Associate Professor, LS2N, University of Nantes, France | Supervisor |

| Mohammed Kamel BENHAOUA  | Full Professor, LAPECI, University of Mascara, Algeria  | Director   |

| Giuseppe LIPARI          | Full Professor, CRIStAL, University of Lille, France    | Director   |

|                          |                                                         |            |

## Résumé

La demande en puissance de calcul dans les systèmes embarqués temps-réel a considérablement augmenté ces dernières années. Les plateformes multicœurs qui sont généralement équipés d'un sous-système de mémoire partagé par tous les cœurs ont répondu dans une certaine mesure à ce besoin croissant en capacité de calcul. Cependant, dans les systèmes temps-réel, l'utilisation simultanée du sous-système de mémoire peut induire à des interférences mémoire significatives. Ces dernières peuvent rendre les pires temps d'exécution des tâches (WCET) très pessimistes et conduire à une sous-utilisation du système.

Cette thèse se concentre sur la réduction des interférences résultantes des conflits liés aux ressources partagées (par exemple les mémoires cache, les bus de communication et la mémoire principale) dans les systèmes multicœurs grâce au co-ordonnancement des calculs et des transferts de donnée des applications temps-réel. À cette fin, nous utilisons des modèles de tâches existants tels que le modèle *DFPP (Deferred Fixed Preemption Point)*, le modèle *PREM (PRedictable-Exécution-Model)* et le modèle *AER (Acquisition-Execution-Restitution model)*. Nous proposons un nouveau modèle de tâche réaliste et plusieurs algorithmes de co-ordonnancement et de partitionnement des tâches temps-réel. Nous montrons que de tels ordonnanceurs peuvent améliorer jusqu'à 50% le taux d'ordonnançabilité par rapport aux ordonnanceurs équivalents générés avec les méthodes de l'état de l'art. De plus, nous démontrons expérimentalement l'applicabilité de nos méthodologies sur la famille de processeurs multicœurs Infineon AURIX TC-397 en utilisant différents benchmarks.

## Abstract

The demand for computational power in real-time embedded systems has increased significantly in recent years. Multicore platforms which are generally equipped with a single memory subsystem shared by all cores, have satisfied this increasing need for computation capability to some extent. However, in real-time systems, simultaneous use of the memory subsystem may result in significant memory interference. Such memory interference owing to resource contention may lead to very pessimistic worst-case execution time bounds (WCETs) and lead to under-utilization of the system.

This thesis focuses on reducing interference resulting from shared resource contention (e.g., caches, buses and main memory) on multicore systems through processor and memory co-scheduling for real-time applications. To this end, we use existing task models such as *DFPP (Deferred Fixed Preemption Point)* model, *PREM (Predictable-Execution-Model)* and *AER (Acquisition-Execution-Restitution)* model. We also propose a new realistic task model and several algorithms for task set allocation and for processor and memory co-scheduling. We show that our proposed methodologies can improve schedulability by up to 50% compared to equivalent schedules generated with the state-of-the-art methods. Furthermore, we experimentally demonstrate the applicability of our methodologies on the Infineon AURIX TC-397 multicore family of processors using different benchmarks.

# Acknowledgements

I have always enjoyed reading the acknowledgments for dissertation manuscripts. This time, it's my turn to indulge.

Four years might seem like a short time in the grand scheme of things, but it certainly doesn't feel like it when your life is constantly changing, for worse or for better, and they definitely felt way longer to me during this experience as a Ph.D. From moving to another country to being stuck at home during the pandemic, there have been many ups and downs in this journey, so much so that the version of me a few years back feels almost like a stranger now. Despite all the struggles and hardships encountered along the way, I honestly think this has been a positive experience for me, with many teachable moments and growing ventures.

I would like to express my first thanks to my supervisors, who gave me this opportunity and mentored me through-out this experience. A big thank to Prof. Mohammed Kamel BENHAOUA for his help, advices, support and above all his trust and understanding. I express my gratitude to Prof. Giuseppe LIPARI, he has been a seemingly inexhaustible source of wisdom in all the subjects we worked on. I appreciated his scientific rigor and his human qualities. His immense knowledge and plentiful experience have encouraged me in all the time of my academic research and daily life. Special thanks to Dr. Houssam-eddine ZAHAF who participated in the direction of the thesis and had a significant impact on the choices made during these years. He has been always available for suggestions and discussions. Thank you for being a friend and a big brother to me. Many thanks to (Dr, Senior Scientist) Richard OLEJNIK, who directed me during my first year of the thesis in France.

I would thank also the members of my jury. Firstly, Prof. Maryline CHETTO and Prof. Hadda CHERROUN for accepting and putting time even in their very full agenda, to read and evaluate my work. I thank also Prof. Sidi Mohammed BENSLIMANE, Prof. Emmanuel GROLLEAU and Prof. Bilel DERBEL to be members of my jury and accept to examine the research presented in this dissertation.

A big thank goes to everyone who worked at the LAPECI and CRISTAL laboratories during these years, especially to the members of the SYCOMORES team (Lille), who became like a second family to me, and to the ORTESE team (Oran1). Each contributed to making this experience more enjoyable, sharing the hardships and the joys of this work. We are a relatively small group, but there would be too many people to name all of them here. Still, some people deserve special thanks for how they helped me get through these past few years. People like Julien FORJET, his reviewing was precious. I appreciated his support and encouragement. Also, I would like to express my gratitude to all Ph.D students, former Ph.D students and post-docs I met during these years.

I also want to thank all of my friends outside the workplace for all the fun we had together throughout these years.

First and foremost, I would like to thank and express my gratitude to my dear parents, my brother Yacine and my sisters Manel and Bouchra, for their tireless support during these four years of my Ph.D and my whole life, and for the unconditional love they have shown me, which prevented me from giving up.

# Contents

| $\mathbf{A}$ | bstra | $\operatorname{ct}$                                     | ii       |  |

|--------------|-------|---------------------------------------------------------|----------|--|

| In           | trod  | uction                                                  | <b>2</b> |  |

| Ι            | M     | Motivation, Background and Related work                 |          |  |

| 1            | Mu    | tiprocessors and Parallel Systems                       | 6        |  |

|              | 1.1   | Introduction                                            | 7        |  |

|              | 1.2   | Uniprocessor vs multiprocessor systems                  | 7        |  |

|              | 1.3   | Classification of multiprocessor systems                | 8        |  |

|              |       | 1.3.1 Based on their structure                          | 8        |  |

|              |       | 1.3.2 Based on their architecture and microarchitecture | 8        |  |

|              |       | 1.3.3 Based on their memory architecture                | 9        |  |

|              | 1.4   | Scratchpad vs cache memories in multicore platforms     | 10       |  |

|              | 1.5   | Programming parallel architecture                       | 11       |  |

|              |       | 1.5.1 POSIX Threads                                     | 11       |  |

|              |       | 1.5.2 OpenMP framework                                  | 12       |  |

|              | 1.6   | Conclusion                                              | 13       |  |

| <b>2</b>     | Rea   | l-time Systems                                          | 14       |  |

|              | 2.1   | Introduction                                            | 15       |  |

|              | 2.2   | Task models                                             | 15       |  |

|              |       | 2.2.1 Liu and Layland model                             | 16       |  |

|              |       | 2.2.2 PREM and AER models                               | 17       |  |

|              |       | 2.2.3 Directed Acyclic Graph (DAG)                      | 18       |  |

|              | 2.3   | Priority assignment for scheduling                      | 19       |  |

|              |       | 2.3.1 Scheduling characteristics                        | 19       |  |

|              | 2.4   | Time- vs event-triggered real-time scheduling           | 20       |  |

|              | 2.5   | Preemptive vs non-preemptive scheduling                 | 21       |  |

|              | 2.6   | Earliest Deadline First (EDF)                           | 21       |  |

|              |       | 2.6.1 Preemptive real-time scheduling                   | 21       |  |

|              |       | 2.6.2 Non-preemptive real-time scheduling               | 23       |  |

|              | 2.7   | Preemptive multiprocessor real-time scheduling          | 24       |  |

|              | 2.8   | Conclusion                                              | 25       |  |

| 3 | Processor and Memory Co-scheduling in Multicore Systems |                                                    |    |  |  |  |  |

|---|---------------------------------------------------------|----------------------------------------------------|----|--|--|--|--|

|   | 3.1                                                     | Introduction                                       | 27 |  |  |  |  |

|   | 3.2                                                     | Cache related delays in multicore systems          | 27 |  |  |  |  |

|   | 3.3                                                     | Shared resources contention: main memory and buses | 29 |  |  |  |  |

|   | 3.4                                                     | Related work                                       | 30 |  |  |  |  |

|   | 3.5                                                     | Conclusion                                         | 34 |  |  |  |  |

## **II** Contributions

35

| <b>4</b> | Allo         | ocation of Real-time Tasks Onto Identical Core Platforms   |            |

|----------|--------------|------------------------------------------------------------|------------|

|          | Une          | der Deferred Fixed Preemption-point Model                  | 36         |

|          | 4.1          | Introduction                                               | 37         |

|          | 4.2          | System model                                               | 37         |

|          |              | 4.2.1 Task model                                           | 37         |

|          |              | 4.2.2 Architecture model                                   | 38         |

|          | 4.3          | Limited Preemption analysis for single-processor           | 39         |

|          |              | 4.3.1 Maximum non-preemptive execution-time                | 39         |

|          |              | 4.3.2 Selection of effective preemption points             | 40         |

|          | 4.4          | Task allocation                                            | 40         |

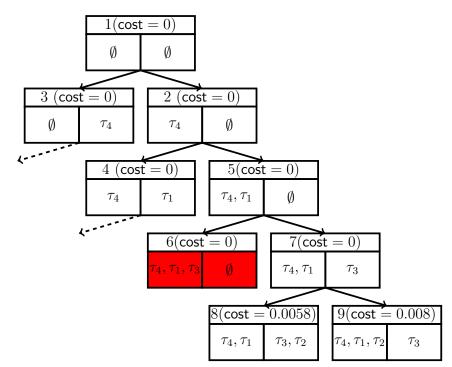

|          |              | 4.4.1 Enumerating algorithm                                | 41         |

|          |              | 4.4.2 Branch and Bound                                     | 42         |

|          |              | 4.4.3 Computational complexity                             | 46         |

|          |              | 4.4.4 Allocation heuristics                                | 47         |

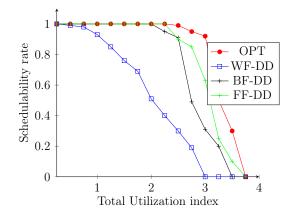

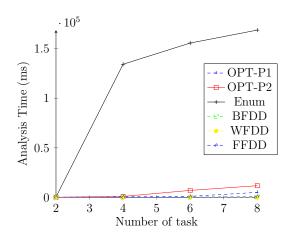

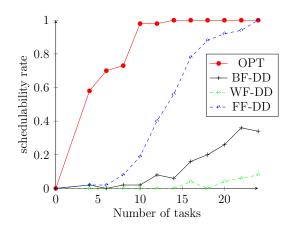

|          | 4.5          | Results and discussions                                    | 48         |

|          |              | 4.5.1 Task generation                                      | 48         |

|          |              | 4.5.2 Simulation results and discussions                   | 48         |

|          | 4.6          | Conclusion                                                 | 52         |

| <b>5</b> | Cor          | ntention-free Scheduling of PREM Tasks on Partitioned Mul- |            |

| J        |              | re Platforms                                               | 53         |

|          | 5.1          | Introduction                                               | <b>5</b> 4 |

|          | $5.1 \\ 5.2$ | System model                                               | 54         |

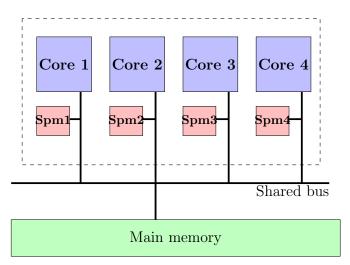

|          | 0.2          | 5.2.1 Architecture model                                   | 54<br>54   |

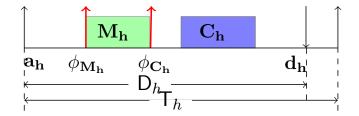

|          |              | 5.2.2 Task model                                           | 55         |

|          | 5.3          | Offset based processor and memory co-scheduling            | 55         |

|          | 0.0          | 5.3.1 Task-level offsets : sufficient condition            | 56         |

|          |              | 5.3.2 Integer-Linear-Programming based offset assignment   | 50<br>57   |

|          | 5.4          | Deadline based processor and memory co-scheduling          | 60         |

|          | $5.4 \\ 5.5$ | Results and discussions                                    | 61         |

|          | 0.0          | 5.5.1 Task set generation                                  | 61<br>62   |

|          |              | 5.5.2 Results of synthetic task set experiments            | 62         |

|          | 5.6          |                                                            | 64         |

|          | 0.0          | Conclusion                                                 | 04         |

| 6        | Me   | ory-processor Co-scheduling AECR-DAG Real-time Tasks                                                                                                  |

|----------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | on 1 | rtitioned Multicore Platforms with Scratchpads 65                                                                                                     |

|          | 6.1  | $ntroduction \dots \dots$                       |

|          | 6.2  | $ by stem model \dots \dots$                    |

|          |      | $5.2.1  \text{Architecture model}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                   |

|          |      | 5.2.2 Task model                                                                                                                                      |

|          | 6.3  | DAG tasks allocation and transformation                                                                                                               |

|          |      | 5.3.1 Decision variables and objective function                                                                                                       |

|          | 6.4  | Deadline based DAG memory-processor co-scheduling 73                                                                                                  |

|          |      | 5.4.1 Fair and proportional deadline assignment                                                                                                       |

|          |      | 6.4.2 GA-based intermediate deadline assignment                                                                                                       |

|          |      | $5.4.3  \text{Evaluation Strategy} \dots \dots$ |

|          |      | 5.4.4 Creating the next generation                                                                                                                    |

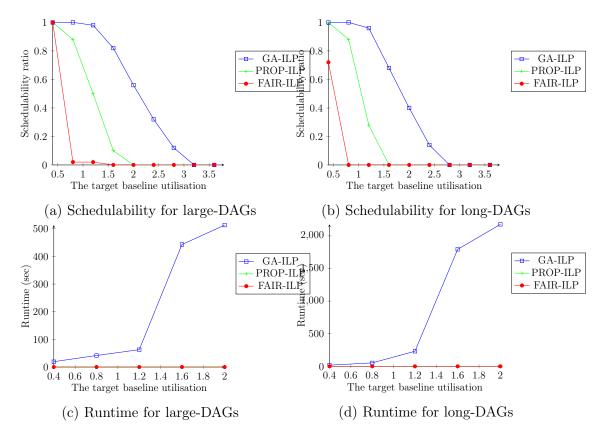

|          | 6.5  | Results and discussions                                                                                                                               |

|          |      | $5.5.1  \text{Task generation}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                      |

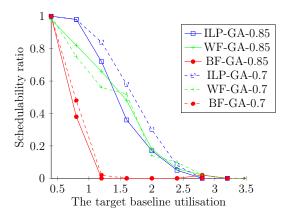

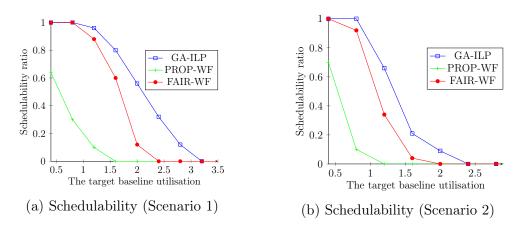

|          |      | 5.5.2 Simulation results and discussions                                                                                                              |

|          | 6.6  | Conclusion                                                                                                                                            |

| <b>7</b> | Cor  | lusion and perspectives 93                                                                                                                            |

|          | 7.1  | Conclusion                                                                                                                                            |

|          | 7.2  | imitations and perspectives                                                                                                                           |

# List of Figures

| 1.1  | Shared memory model                                                                 | 9  |

|------|-------------------------------------------------------------------------------------|----|

| 1.2  | Distributed memory model.                                                           | 9  |

| 1.3  | Hybrid memory model                                                                 | 10 |

| 1.4  | Example of Fork-Join Model                                                          | 13 |

| 2.1  | Periodic constrained-deadline task parameters                                       | 17 |

| 2.2  | DAG task example                                                                    | 18 |

| 2.3  | Partitioned scheduling vs global scheduling.                                        | 25 |

| 4.1  | Example of task parameters                                                          | 38 |

| 4.2  | Example of branch and bound                                                         | 46 |

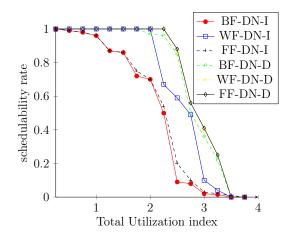

| 4.3  | Schedulability for optimal solutions against BF, WF and FF $\ldots$                 | 49 |

| 4.4  | The analysis time as a function of number of task                                   | 50 |

| 4.5  | Schedulability at different taskset size                                            | 50 |

| 4.6  | Performance of BF, WF and FF using sorted tasks by density                          | 51 |

| 4.7  | Performance of BF, WF and FF using sorted tasks by laxity $\ . \ .$                 | 51 |

| 5.1  | Multicore target platform.                                                          | 54 |

| 5.2  | Example of task parameters                                                          | 56 |

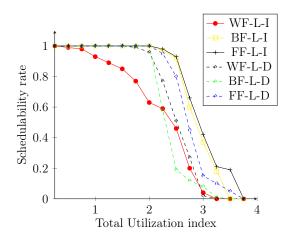

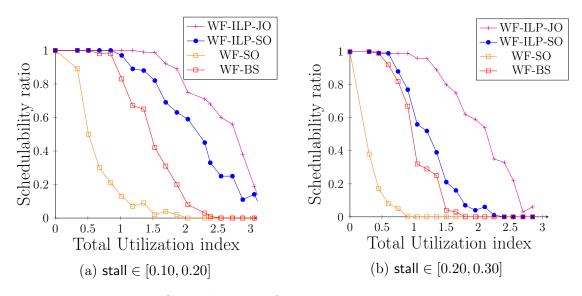

| 5.3  | Schedulability of ILP vs heuristics approaches                                      | 62 |

| 5.4  | Heuristics algorithms performances                                                  | 63 |

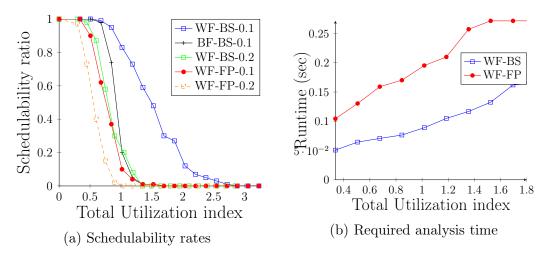

| 6.1  | Multicore architecture featuring 4 cores, and its interconnection                   |    |

|      | buses                                                                               | 67 |

| 6.2  | DAG task example, computation subtasks are mapped on a dual-                        |    |

|      | core platform                                                                       | 68 |

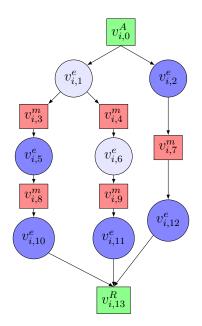

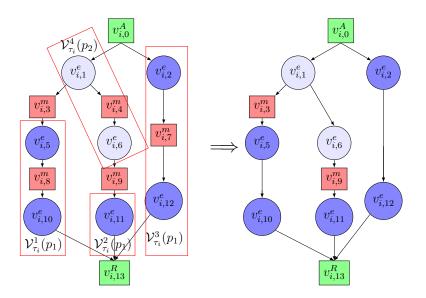

| 6.3  | DAG task transformation.                                                            | 71 |

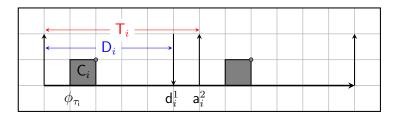

| 6.4  | Example of offset and local deadline                                                | 74 |

| 6.5  | Example of an individual.                                                           | 77 |

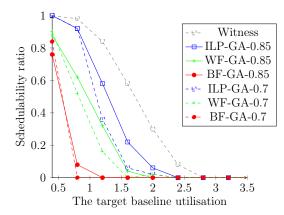

| 6.6  | Schedulability rate for large DAG: $U^{max} = 0.7 \text{ vs } U^{max} = 0.85 \dots$ | 88 |

| 6.7  | Schedulability rate for long DAG: $U^{max}=0.7~\mathrm{vs}~U^{max}=0.85$            | 88 |

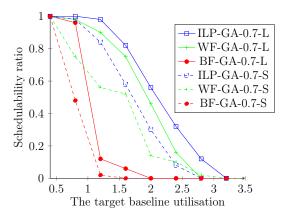

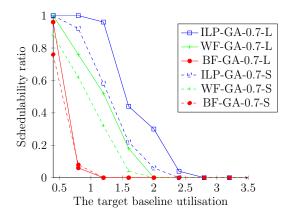

| 6.8  | Schedulability rate for large DAGs: small vs large population                       | 89 |

| 6.9  | Schedulability rate for long DAGs: small vs large population                        | 89 |

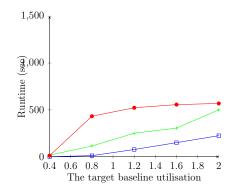

| 6.10 | 1 ( ) 0                                                                             | 90 |

| 6.11 |                                                                                     | 91 |

| 6.12 | GA-ILP's performances VS the literature                                             | 92 |

# List of Tables

| 4.1 | Task parameters                                  | 46 |

|-----|--------------------------------------------------|----|

| 6.1 | Example of Individual                            | 78 |

| 6.2 | Swapping local deadlines after a crossover point | 85 |

## List of Acronyms

- AD Autonomous driving. 15

- **AECR** Acquisition Execution Communication Restitution Model. 4

- **AECR-DAG** Acquisition Execution Communication Restitution Model-DAG. 24, 69, 79, 87, 92

- AER Acquisition Execution Restitution Model. 3, 17, 29, 34, 66

- **BB** Branch and Bound. 40

- **BF** Best-Fit. 25, 47–49

- **COTS** Commercial off-the-shelf software. 29

- CRPD cache-related preemption delays. 3, 28, 31

- DAG Directed Acyclic Graph. 4, 17, 33, 66

- dbf Demand bound function. 22

- **DFPP** Deferred Fixed Preemption Point. 3

- **DLA** Deep learning accelerators. 9

- **DM** Deadline Monotonic. 19

- **DPM** deferred preemption model. 30

- **DSP** Digital signal processors. 9

- **EDF** Earliest Deadline First. 19, 21, 22, 39, 40, 54, 59, 60, 64, 73, 82, 84

- ET Event-triggered. 20

- FCFS First-Come First-Served. 33

- **FF** First-Fit. 47–49

- FIFO First-In-First-Out. 29

- FPP Fixed Preemption Points. 28

- LLF Least Laxity First. 19

- LPM Limited Preemptive Models. 28

- NFP Floating Non-Preemptive Regions. 28

- **PREM** PRedictable Execution Model. 3, 17, 29, 32, 54, 64

- **PT** Preemption Thresholds. 28

- **PTS** Preemption Thresholds Scheduling. 31

- **RM** Rate Monotonic. 19

- SMP Homogeneous or Symmetric Multiprocessors. 8

- **SPM** Scratchpad memory. 11

- **TDMA** Time Division Multiple Access. 32

- TT Time-triggered. 19, 20

- WCET Worst-case execution time estimation. 2, 10, 29

- **WF** Worst-Fit. 25, 47, 48

## Introduction

### Context and motivation

Real-time systems are computing systems that must react with predictable time behavior to events in the environment. As a consequence, their correct behavior depends not only on the logical correctness of the computations but also on the time at which the results are produced [132]. Nowadays, real-time computing plays a crucial role in our society, as more and more complex systems rely, in part or completely, on computer control. Automotive applications, robotics, medical systems and flight control systems are examples of applications that require realtime computing.

Worst-case execution time estimation (WCET) is the key element of timing analysis of real-time systems. The WCET is defined as the maximum length of time that a task may take to completely execute on a given hardware platform. For single-core platforms, the WCET estimate is based on the time spent by the longest execution path of the process.

The demand for computational power in real-time embedded systems has increased significantly, making multicore and heterogeneous systems attractive in the real-time domain. Multicore platforms can provide significantly more processing power than traditional single-core platforms, however, due to the underlying complexity and interference in accessing shared resources, schedulability and predictability should not be guaranteed.

In multicore settings, where different applications running concurrently on different cores compete for the access to shared memories, the combination of interference for accessing a shared memory (i.e. the main memory) and local cache related delays can be large and highly variable depending on the platform architecture and the number of parallel access requests. These runtime-related delays inflate significantly the WCETs of tasks especially when preemption is enabled.

Shared memory interference represents a big challenge for the predictability of real-time embedded systems. In general, it is difficult to accurately compute the worst-case interference profile, which likely leads to include scenarios that might never occur, therefore over-estimating the worst-case interference.

In cache-based preemptive real-time systems, the preempted and the preempting tasks may interfere on the cache memory. This interference leads to cache misses in the preempted task which result in additional delays [64]. In fact, when a preemption occurs, the analysis must account for the time needed to reload cache blocks that have been evicted by preempting tasks. These delays are known as *cache-related preemption delays (CRPD)*. CRPD may be large in fully preemptive systems as a given task can be preempted by any other higher priority task. Non-preemptive systems, on the other hand, may suffer from long blocking times: when a low priority task starts its execution, higher priority tasks are blocked waiting for the low priority task to finish, causing priority inversion.

We believe that reducing the impact of memory interference on WCET estimation can improve application performance in multi-core architectures. Models such as the *Deferred Fixed Preemption Point (DFPP)*, the *Predictable Execution Model (PREM)* and the *Acquisition-Execution-Restitution (AER)* model can help us in improving predictability in these systems.

In this thesis, we tackle the problem of reducing/avoinding shared memory contention for real-time task sets expressed with different predictable models on several types of multicore architectures (i.e. cache-based architectures and scratchpad-based architectures). The next section briefly describes our contributions and the organization of the subsequent chapters of this document.

## Contributions

Our contributions consist in proposing efficient scheduling approaches for different predictable task models on multicore architectures. The outline of this manuscript and the main contributions are summarized in this section.

The thesis is divided into seven chapters.

In Chapter 1 & 2 we introduce real-time systems, multicore and parallel systems. In Chapter 3, we describe the memory interference problem in multicore architectures and we place the problem in the state of the art.

In Chapter 4, we explore techniques to allocate a set of real-time task onto an identical multicore platform with caches so to reduce the preemption costs. To this end, we present optimal algorithms and heuristics to solve this problem. This chapter present i) an exact allocation algorithm for a set of real-time tasks presenting fixed-preemption points onto an identical core platform, (ii) several techniques to reduce the time and space complexity of computing the exact solution as well as (iii) efficient allocation heuristics; and finally (iv) an exhaustive evaluation of the proposed approaches using a large set of synthetic experiments. In the model we use in this chapter, each fixed-preemption point is characterized by an architecture related cost, it is defined as the cumulative execution overhead due to the combination of processor components effects such as the cache-related effect, which results in very high costs due to the unpredictability of caches. We adopt in Chapter 5 the Predictable Execution Model (PREM) in order to achieve a higher degree of predictability.

In Chapter 5, we tackle the problem of contention in multicore architecture with scratchpad memories. The goal is to avoid shared memory contention for a set of tasks modeled using PREM. In this chapter, we explore and compare different designs for scheduling memory phases: a time-triggered-based approach and an on-line scheduling approach for memory phases. We show that obtaining an optimal solution of this problem is very time consuming even for small task set size. We propose heuristics that allows to find a feasible solution in a reasonable time. We compare the proposed approaches against the state of the art using a set of synthetic experiments in terms of schedulability and analysis time and we show that our techniques improve up to 50% the schedulability. The different approaches are implemented on an Infineon AURIX TC397 multicore microcontroller and validated using a set of tasks extracted from well-known benchmarks from the literature.

In the sixth chapter, we proposed a new model named Acquisition-Execution-Communication-Restitution-DAG (AECR). An AECR-DAG application is a Directed Acyclic Graph (DAG) of communicating subtasks respecting AER model. We use a genetic algorithm to derive scheduling parameters for a set of AECR-DAG tasks. Subtasks are partitioned onto the multicore platform while their memory requests and relative communications are scheduled onto the shared buses, in order to prevent interference and ensure predictability. We propose an ILP formulation to solve the mapping problem. Specifically, all subtasks and communications are assigned appropriate intermediate offsets and deadlines to guarantee that they comply with the system's timing constraints.

In all the proposed approaches of the two precedent chapters (5 & 6), we consider a multicore platform with scratchpads and preemptive partitioned scheduling at the core level for computations phases.

We conclude with an overview of our findings, their impact, and future directions in the thesis conclusion (Chapter 7).

# Part I

# Motivation, Background and Related work

# Chapter 1

# Multiprocessors and Parallel Systems

## Contents

| 1.1 | Intro | oduction                                                                       | 7  |

|-----|-------|--------------------------------------------------------------------------------|----|

| 1.2 | Uniț  | processor vs multiprocessor systems                                            | 7  |

| 1.3 | Clas  | sification of multiprocessor systems                                           | 8  |

|     | 1.3.1 | Based on their structure $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 8  |

|     | 1.3.2 | Based on their architecture and microarchitecture                              | 8  |

|     | 1.3.3 | Based on their memory architecture $\ldots \ldots \ldots$                      | 9  |

| 1.4 | Scra  | tchpad vs cache memories in multicore platforms                                | 10 |

| 1.5 | Prog  | gramming parallel architecture                                                 | 11 |

|     | 1.5.1 | POSIX Threads                                                                  | 11 |

|     | 1.5.2 | OpenMP framework                                                               | 12 |

| 1.6 | Con   | $\operatorname{clusion}$                                                       | 13 |

### 1.1 Introduction

The concept of algorithms and modern computers is defined by Alan Turing [138] who presented the Turing Machine. He proved that mathematical computations can be performed by machines if they are represented by an algorithm. Turing machines are considered as the central concept of modern computers. Modern computer systems are built on ICs (*Integrated Circuits* (1958-1971)). Depending on the number of available processing units, modern computer systems can be classified as uniprocessor and multiprocessor systems.

### **1.2** Uniprocessor vs multiprocessor systems

A uniprocessor platform is a computer system with a single Central Processing Unit (CPU). This unit performs all computations sequentially, with just one task executing at any given time instance. As a result of the hardware constraint, no true (physical) parallelism is accomplished on such systems; yet, multitasking can be supported in such systems. Multitasking means that more than one task can be executed on the processor on a time-sharing basis.

In 1965, Moore's observation [137] states that the number of transistors in an IC doubles each two years, hence the performance of chips doubles as well. We can see that the evolution of Intel processors roughly parallels Moore's law. The number of transistors incorporated in their CPUs has increased dramatically over the years. According to Moore's law, processor performance advances exponentially over time as the number of transistors in integrated circuits doubles, increasing clock speed and allowing computers to accomplish tasks quicker. Since clock rates of processors are not going faster in the same previous rate, platform performance is improved by duplicating the number of CPUs, therefore, the multicore/multiprocessor solution was presented.

Multiprocessor systems are those that include more than one processing unit, allowing computations to be done in parallel. Until recently, uniprocessor systems predominated over multiprocessor systems in industrial execution platforms. It's either because system designers were afraid of the risk that came with modifying their previous reliable uniprocessor designs, or because uniprocessor performance was sufficient for most embedded system applications.

However, as the demand for processing power and effectiveness for massive computations and applications grows, a move from uniprocessor to multiprocessor systems is on the horizon. For example, in 2011, the percentage of uniprocessor applications was greater than 30% of total industrial applications. However, this ratio is likely to fall to 15% in the next few years as multiprocessor platforms gain popularity [34].

Multiprocessor systems offer software-level parallelism, hence, concurrent tasks and processes can execute simultaneously on different processing units.

## **1.3** Classification of multiprocessor systems

Multiprocessor are differentiated and classified according to different criteria. In this section, we present the most important classes.

### 1.3.1 Based on their structure

Multiprocessing systems can be classified based on their structure as follows:

- Multiprocessor system. As stated before, it consists of more than one processing unit. Applications can choose to benefit from the performance improvement provided by this architecture. Otherwise said, sequential applications can opt to execute sequentially on such systems without modifying their programming techniques. Parallelism can be achieved by splitting processes/threads of an application among several processors in the system, thereby increasing execution speed. Processors can also share system memory through a communication bus (see the classification according the memory architecture 1.3.3).

- Multicore system. A system's core is made up of more than one logical unit. These units (often 2 to 8 cores) have their own individual memory cache or scratchpad as well as another level of cache memory shared by the processor's cores (LLC for Last Level memory Cache). Application programming distinguishes multiprocessor from multicore systems. An application has to change its sequential architecture in order to scale up its performance while executing on multicore systems. The abovementioned systems are usually found in general-purpose devices. Examples are Intel, ARM and AMD processors;

- Many-core system. This system, which typically refers to extremely large multicore platforms, has the same technical architecture as multicore systems. The number of cores ranges from dozens to hundreds per single processor. These systems implement parallel architecture, hence, software has to be adapted to such systems in order to get advantage of hardware capabilities. For example, the TILE-GX 3 72-core processor from Tilera (2009).

### 1.3.2 Based on their architecture and microarchitecture

Based on the type of processors, multicores (multiprocessor) systems can be divided into categories as follows:

• Homogeneous or Symmetric Multiprocessors (SMP). The system's processors are all of the same type (multiple central processing units CPUs or multiple graphics processing units (GPUs)). They have typically identical architectures, instruction sets, and the execution rate of tasks is the same on all of them;

- Uniform Processors. In these systems, each processor has a speed or computational capacity that determines the rate at which a task is executed;

- Heterogeneous Processors. They incorporate multiple processing units of different types, each optimized for specific tasks in a single system. These systems can include a mix of CPUs, GPUs, deep learning accelerators (DLAs), digital signal processors (DSPs), and other specialized processors. Hence, the execution rate of a task is determined by the type of processor and the task itself.

### 1.3.3 Based on their memory architecture

According to memory architecture, multiprocessor systems can be divided into categories as follows:

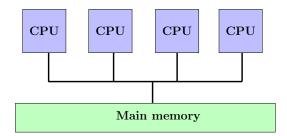

• Shared memory. A multicore (multiprocessor) with shared memory provides a single memory that is shared by all processors. Any processor can physically access data at any location in memory (see Figure 1.1). In all the contributions of this work, we used a shared memory multicore architecture.

Figure 1.1: Shared memory model.

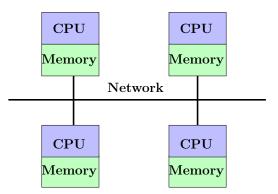

• Distributed memory. In a multicore (multiprocessor) with distributed memory, each processor has its own private memory. Processings can only operate on local data and must communicate with one or more remote processors, if remote data is needed (see Figure 1.2).

Figure 1.2: Distributed memory model.

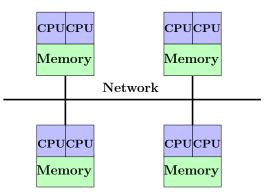

• Hybrid memory. In a multiprocessor with hybrid memory, the distributed and shared memory models are combined. Each unit is a shared memory system (there are two or more cores sharing the same memory resources). Then, shared memories are connected through networks, forming a distributive system. Today, the fastest computers in the world employ both shared and distributed memory architectures (see Figure 1.3).

Figure 1.3: Hybrid memory model.

## 1.4 Scratchpad vs cache memories in multicore platforms

The increasing performance gap between the processor and the off-chip memory has made it important to use on-chip memory in real-time embedded systems. CPU caches in a modern multi-core platform typically consist of two or three cache memory levels between the core and the main memory. Usually, each core has a private smaller Level 1 (L1) cache memory. All cores share a larger Level 2 (L2) and/or a Level 3 (L3) cache memory. Caches have been extensively used to bridge that gap.

Data transfers between main memoty and caches are managed by hardware, in a transparent manner to the programmer and compiler. Unfortunately, caches are source of predictability problems in hard real-time systems. The cache replacement strategy might introduce unpredictability of the cache behavior. Instruction prefetching, out-of-order execution, and control speculation introduce interferences between processor components, e.g. caches, pipelines and prefetch queues.

A lot of progress has been achieved in the last ten years to statically predict worst-case execution times (WCETs) of tasks on architectures with caches [100, 108, 113, 120]. However, cache-aware WCET analysis techniques are not always applicable due to the lack of documentation of hardware manuals concerning the cache replacement policies.Moreover, caches are sources of timing anomalies in dynamically scheduled processors [112] (a cache miss may in some cases result in a shorter execution time than a hit). In such situations, cache locking and cache partitioning techniques are of interest [89]. Scratchpad memory (SPM) is a popular choice in real-time embedded systems. It is a small software-managed on-chip static RAM that has been widely accepted as an alternative to cache memory, as it offers better timing predictability compared to caches. The scratchpad memory is mapped into the address space of the processor, and is accessed whenever the address of a memory access falls within a predefined range. Contrary to caches, the compiler and/or the programmer explicitly controls the allocation of instructions and data to the scratchpad memory. This operating principle makes the latency of each memory access, and thus program execution time, more predictable. Significant effort has been invested in developing efficient static and dynamic allocation techniques for scratchpad memories [75, 76, 101, 105].

Many of the modern multicore platforms offer scratchpad memories, for example: NXP S32, Renesas R-car, STM Stellar, and Aurix Infineon platform series.

## 1.5 Programming parallel architecture

We define parallel applications as those applications that perform their computations simultaneously on multiple processors. Parallelism is important in order to get advantage of hardware advancement of processor architecture such as multiprocessor. It is crucial to remember that adding more processing units to execution platforms to increase performance is worthless if the designed software is incompatible with the hardware. Software parallelism is classified into the following classes:

- Inter-task parallelism: in which tasks execute in parallel. An example of such parallelism is a set of tasks which executes on multiple processors.

- Intra-task parallelism: or the inter-subtask parallelism, here a parallel task consists of subtasks which execute in parallel.

- Intra-subtask parallelism: a subtask of a parallel task consists of a set of threads running in parallel. In this case, a subtask requires more than one processor to execute.

A thread is an execution portion of a parallel task (or a subtask). Task's threads are usually all activated at the same time and have to terminate their execution at the same time. There are multiple programming languages and frameworks that allow the code to be executed in parallel on different threads. Two frameworks are available to the C programming language that we will present in this manuscript: *POSIX Threads(Pthreads)* and *OpenMP*.

### 1.5.1 POSIX Threads

POSIX Threads is a common threading model when working in C or C++, usually referred to as Pthread, it is a standardized model to work with threads. POSIX Threads can be use to parallelism task of a program in order to increase the execution speed. The POSIX standard states that threads must share a number of informations, for example the threads must share:

- Process ID

- Parent Process ID

- User and group IDs

- Open FD's (File Descriptors)

POSIX Threads offers a header file and a library that must be included at compilation time and a set of functions to create, manipulate, synchronise and kill threads in a program. The starting point for threads in a Pthreads program is the *pthreads\_create* function, this function takes a pointer to a function that is the starting point for the new thread. Then, the *pthread\_exit* function is used to kill the thread. In the main thread, the *pthread\_join* function is used to wait for the executing threads [3]. There are several other Pthread procedures for example those used for synchronization (with locks and barriers) and Mutexes.

### 1.5.2 OpenMP framework

OpenMP [42] is a parallel programming model for shared-memory multiprocessor systems developed in 1990 by SGI. The goal of OpenMP is to provide a standard and portable API for writing shared-memory parallel programs. OpenMP works in conjunction with either standard Fortran or C/C++. It is comprised of a set of compiler directives used in the source code. These directives are instructional notes to any compiler supporting OpenMP. They take the form of source code comments (in Fortran) or #pragmas (in C/C++). Collectively, these directives and library routines are formally described by the application programming interface (API) now known as OpenMP.

OpenMP is designed to support incremental parallelization, or the ability to parallelize an application a little at a time at a rate where the developer feels additional effort is worthwhile [104].

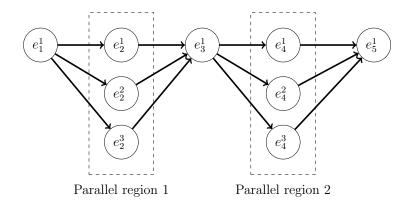

To create the threads when an parallel directive is encountered, OpenMP uses the Fork-Join model. Figure 1.4 shows an example of a Fork-Join model. When a executing thread encounters a parallel construct it will create a team of threads(fork) and become the master thread of the team. Then the team executes the code assigned to it and before the initial or master thread continue to execute the code after the parallel construct all the threads in the team are terminated(join).

Figure 1.4: Example of Fork-Join Model

The first sequential execution in Figure 1.4 is  $e_1^1$  called the source thread. Three parallels threads  $e_2^1$ ,  $e_2^2$  and  $e_2^3$  gathered in "parallel region 1" are forked from  $e_1^1$ . The second sequential execution is  $e_3^1$  and it joints the three threads forked by  $e_1^1$ , it forks at its turn three parallel threads  $e_4^1$ ,  $e_4^2$  and  $e_4^3$  gathered in "parallel region 2". The last sequential task joins the threads created by  $e_3^1$  and continue till the task ends.

Compared to using pthreads and working with mutex and condition variables, OpenMP is much easier to use because the compiler takes care of transforming the sequential code into parallel code according to the directives [33, 65].

## 1.6 Conclusion

In this chapter, we presented an overview of multicore architectures, the different types of memory used in these architectures and reviewed two parallel programming languages. These are notions on which our work will be based. We will consider a set of tasks with timing constraints to be partitioned on a multicore platform with the goal of reducing/avoiding shared resources contention. Before that, we will give a quick overview on real-time systems in the next chapter.

# Chapter 2

# **Real-time Systems**

### Contents

| 2.1 Intr | oduction                                                          | 15        |

|----------|-------------------------------------------------------------------|-----------|

| 2.2 Tasl | k models                                                          | 15        |

| 2.2.1    | Liu and Layland model                                             | 16        |

| 2.2.2    | PREM and AER models                                               | 17        |

| 2.2.3    | Directed Acyclic Graph (DAG)                                      | 18        |

| 2.3 Pric | ority assignment for scheduling                                   | 19        |

| 2.3.1    | Scheduling characteristics                                        | 19        |

| 2.4 Tim  | ne- vs event-triggered real-time scheduling                       | 20        |

| 2.5 Pre  | emptive vs non-preemptive scheduling                              | <b>21</b> |

| 2.6 Ear  | liest Deadline First (EDF)                                        | <b>21</b> |

| 2.6.1    | Preemptive real-time scheduling                                   | 21        |

| 2.6.2    | Non-preemptive real-time scheduling $\ldots \ldots \ldots \ldots$ | 23        |

| 2.7 Pre  | emptive multiprocessor real-time scheduling                       | <b>24</b> |

| 2.8 Con  | $\operatorname{nclusion}$                                         | <b>25</b> |

## 2.1 Introduction

Real-time systems are computing systems that must react within precise time constraints to events in the environment. As a consequence, the correct behavior of these systems depends not only on the value of the computation but also on the time at which the results are produced [57].

A real-time system interacts with its environment through the use of sensors and/or actuators. Given the dynamic nature of the environment, the system's response to a change in the environment cannot be postponed indefinitely. The state of the system at any point in time must be correct in relation to the state of the environment. Any state of the system that causes an accident in the environment or in the system itself, such as the destruction of system components, is regarded as a failure. The cost of failure classifies these systems into 3 classes:

- Hard real-time systems: are systems in which a failure to meet even a single deadline may lead to complete or appalling system failure. This is particularly true for the autonomous driving (AD) systems, which incorporate complex functions along with strong safety requirements. Its software functions must coexist and share resources with other software vehicle functions without sacrificing real-time safety requirements;

- Soft real-time systems: are systems in which one or more failures to meet the deadline are not considered complete system failure, but that performance is considered to be degraded. Web browsing is an example of soft real-time system;

- Firm real-time systems: are not hard-real time systems, but results delivered after a deadline that has been violated, are ignored. Video conferencing and satellite based tracking are good examples of firm real-time system.

## 2.2 Task models

Real-time systems applications generally consist of a set of concurrent functionalities called tasks with timing-related properties. A task is a *thread*, i.e. a sequential piece of code executing on a multi-threading operating system. The pseudo-code of a typical real-time task in a POSIX-like environment is shown in Listing 2.1. A task can be activated several times during the system life. Each activation is called a "job" or "instance". In this thesis, we consider a set of real-time tasks  $\mathcal{T}$ , each task  $\tau_i$  is described as a infinite succession of jobs. We denote  $j_i^l$  the  $l^{th}$  job of task  $\tau_i$ . Each job  $j_i^l$  is characterized by three parameters  $(\mathbf{a}_i^l, \mathbf{d}_i^l, \mathbf{c}_i^l)$ .  $\mathbf{a}_i^l$  represents the job arrival time, it corresponds to the time instance when the job  $j_i^l$  becomes ready to start its execution.  $\mathbf{d}_i^l$  is the job absolute deadline, and  $\mathbf{c}_i^l$  represents the execution time of  $j_i^l$ .

According to the recurrence problem, we can distinguish three types of realtime tasks:

- Periodic task: two consecutive releases (jobs) of the same task are separated by a fixed inter-arrival time;

- Sporadic task: two consecutive releases (jobs) of the same task are separated by a minimum inter-arrival time;

- Aperiodic task: There is no correlation between the activation of two successive instances of an aperiodic task.

```

void* task()

{

// Initialization

while (true) {

// task code

wait_for_next_activation() ;

}

}

```

Listing 2.1: Example of real-time task code

### 2.2.1 Liu and Layland model

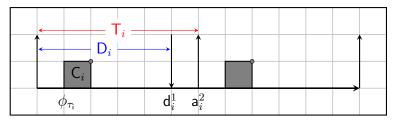

The classic model by Liu and Layland [135] modeled a real-time task by  $\tau_i = (C_i, D_i, T_i)$ :

• C<sub>i</sub>: is the worst-case execution time of the task, it is equal to:

$$\mathsf{C}_i = \max_{\forall l} (\mathsf{c}_i^l) \tag{2.1}$$

It represents the maximum elapsed time between the processor acquisition and the task completion without considering any interruption. Several techniques are proposed in the literature to upper-bound and estimate this value, a good overview can be found in [109].

- D<sub>i</sub>: is the task's relative deadline, it represents the time within the task have to end it's execution (i.e. the lenght of any interval [a<sup>l</sup><sub>i</sub>, d<sup>l</sup><sub>i</sub>]);

- T<sub>i</sub>: is the task period, it represents the minimum inter-arrival time between two jobs if we consider sporadic real-time tasks.

If  $D_i$  is equal to the task period  $T_i$  then, the deadline is said to be *implicit*. If  $D_i$  is less than or equal to the task period  $T_i$ , then the deadline is *constrained*(2.1).

It is important to distinguish between two classes of periodic task sets, regarding the activation time of the 1<sup>st</sup> instance of tasks (called the offset  $\phi_{\tau_i}$ ): synchronous and asynchronous task sets. Synchronous task sets are those in which all offsets are equal, for example  $\phi_{\tau_0} = \phi_{\tau_1} \cdots \phi_{\tau_n} = 0$ . Asynchronous task sets in contrast are those where the offsets of two distinct tasks might be not equal [111]. In this context, if the offsets of the jobs of a single task are equal, then we say that the offset is static. On the other hand, if at least one job offset of the task is different from the offset of the other jobs, then the offsets are dynamic.

Tasks may be characterized by other derived parameters. First, the task utilization, given by  $u_i = C_i/T_i$ , which indicates the extent to which a task utilizes the computing resources. Thus, the total utilization is given by  $U_{\mathcal{T}} = \sum_{\tau_i \in \mathcal{T}} u_i$ . The maximum possible utilization for a single computing unit is assumed to be equal to 1. Second, the worst-case response time  $R_i$  which is defined as the longest time from a job arriving to its completion. Finally, the hyperperiod H which is defined as the least common multiple of all task periods.

All the task parameters cited above are graphically represented in Figure 2.1.

Figure 2.1: Periodic constrained-deadline task parameters.

If jobs of different tasks can execute in any order, they are said to be independent. Dependencies between tasks can be classified into: control dependencies (mutual exclusion and precedence constraints) or data dependency. When job  $j_i^l$ can start the execution only after another job  $j_h^k$  finishes its execution in a task model, then such constraint is called precedence constraint. These precedences can be modeled using a precedence graph. The latter, is a directed acyclic graph which represents the precedence constraints among a set of jobs. In real-time systems, jobs communicate via shared ressources, hence, data of one job depends on the results produced by others.

Several models that embody these dependencies were proposed in the literature. In this thesis we focus in particular on phased models (i.e. PREM and AER) and the common model of parallelism which is the Directed-Acyclic-Graph (DAG) model.

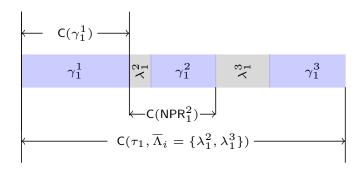

### 2.2.2 PREM and AER models

Under PREM model [61], the task code is divided into a set of scheduling intervals executed sequentially at run-time: compatible intervals and predictable intervals. Predictable intervals are divided into two phases: (i) a non-preemptive *memory phase* and a *computation phase*. In the memory phase, the core/processor accesses to the main memory to perform data fetches and replacements [50, 61]. At the end of the memory phase, all required data is available in the core local memory. Therefore, during the computation phase, the task can perform computations without any need to access to the main memory. Instead, OS activity is confined to compatible intervals.

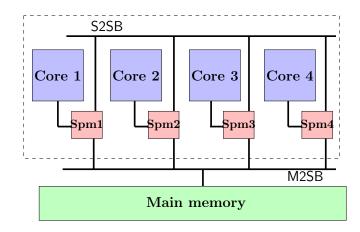

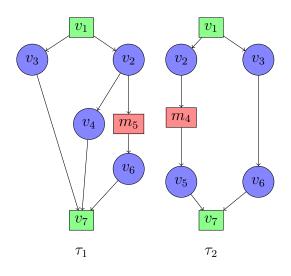

Figure 2.2: DAG task example

The AER model [39] is an extension of the PREM model. Under this model, tasks are divided into three distinct phases, namely: acquisition (A) and restitution (R) which are memory phases and a pure computation(E) phase.

These models where data transfers and computations are separated allow to both mitigate delays related to shared access to the main memory and make them easier to analyze. Since the memory and the computation phases are decoupled, it is possible to exploit parallelism. In fact, the computation phases of different tasks can execute in parallel with any other phase of any other task. These models ere used in Chapter 5 & 6.

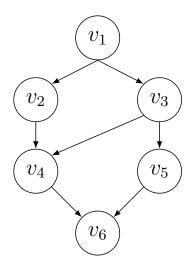

### 2.2.3 Directed Acyclic Graph (DAG)

A task  $\tau_i$  in task set  $\mathcal{T}$  is represented by a tuple  $(\mathsf{G}_i, \mathsf{D}_i, \mathsf{T}_i)$ , where  $\mathsf{G}_i$  is a Directed Acyclic Graph (DAG) that describes the internal structure of  $\tau_i$ ,  $\mathsf{D}_i$  is its endto-end relative deadline, and  $\mathsf{T}_i$  is its period. A DAG is acyclic, i.e. there is no closed cycle between vertices of the graph, it can be periodic or sporadic.

Task  $\tau_i$  consists of a set of subtasks (execution portions) under precedence constraints that determine their execution flow. Each subtask is characterized by a specific WCET and disposes a set of predecessors and a set of successors. Each DAG may have one or more than one *source* subtask and one or more than one *sink* subtask. A source subtask has no predecessor and it is activated by the activation of its DAG. A sink subtask is an ending subtask in the DAG and has no successors. An example of a DAG task is given in Figure 2.2 which shows the structure of the DAG model.

This model is used in Chapter 6 of this thesis along with the AER model to build our new task model named AECR - DAG.

## 2.3 Priority assignment for scheduling

In real-time systems, we assume that real-time tasks are arbitrated using a scheduler in order to be execute on computing resources such as unicore or multicore CPUs. Similar to general-purpose operating systems such as Linux, real-time operating systems also associate a notion of priority to tasks to determine the order in which they should be scheduled. We can define a scheduler as the algorithm which determine which of the task jobs is run on the core(s) at each moment of time.

According to the nature of priority assignment, three broad categories of real-time scheduling are identified: (i) fixed-task priority scheduling, (ii) fixed-job priority scheduling and (iii) dynamic-job priority scheduling. Under fixed-task priority scheduling, the priority of the task and all its jobs does not change during the whole system life; The algorithms Rate Monotonic (RM, Liu and Lay-land, [135]) and Deadline Monotonic (DM, Leung and Whitehead, [133]) belong to this first class. Under fixed-job priority scheduling, the priority of the task is allowed to change but not the priority of jobs. More specifically, a job has a fixed priority during its execution, but jobs of the same task may have different priorities. Earliest Deadline First (EDF, Liu and Layland, [135]) represents perfectly this class of scheduling algorithm. In the last class of scheduling algorithm, the priority of a job can changes at each moment of time during the execution. Least Laxity First (LLF Dertouzos, [134]) is the perfect example of dynamic-job priority scheduling algorithm.

The various scheduling algorithms cited above are *online*. They will schedule the tasks during the execution of the system. There exist also *off-line* schedulers, that will determine which task have to be executed based on an offline schedule. An example of an offline scheduler is the *time-triggered* (TT) discussed in Section 2.4.

### 2.3.1 Scheduling characteristics

Before diving into details, it is necessary to give more definitions [28].

### Preemption

Preemption is the act of temporarily interrupting an executing job and invoke a scheduler to determine which process should execute next. Therefore, allowing higher priority jobs to acquire the preemptible resource. The interrupted job resumes its execution at some later time point.

#### Schedulability

A task is referred to as schedulable according to a given scheduling algorithm if its worst-case response time under that scheduling algorithm is less than or equal to its deadline. Similarly, a task set is referred to as schedulable according to a given scheduling algorithm if all of its tasks are schedulable.

### Feasibility

A task set is said to be feasible with respect to a given system if there exists some scheduling algorithm that can schedule all possible sequences of jobs that may be generated by the task set on that system without missing any deadlines.

### Optimality

A scheduling algorithm is referred as optimal if it can schedule all the task sets that can be scheduled by any other algorithm.

#### Sufficient tests

A schedulability test is said to be sufficient, with respect to a scheduling algorithm and a system, if all of the task sets that are deemed schedulable according to the test are in fact schedulable.

#### Necessary tests

Similarly, a schedulability test is said to be necessary if all of the task sets that are deemed un-schedulable according to the test are in fact unschedulable.

#### Exact tests

Finally, a schedulability test is termed as exact, if it is both sufficient and necessary.

#### Predictability

predictability represents an important property in real-time systems where task execution times are variable up to some worst-case value.

A scheduling algorithm is said to be predictable if the response times of jobs cannot be increased by decreasing their execution times, with all other parameters remaining constant.

### 2.4 Time- vs event-triggered real-time scheduling

Time- and event-triggered are the two major approaches for designing and scheduling real-time systems. In time-triggered (TT) systems, a pre-elaborated, offline static plan dictates the exact points in time when each task must execute and for how long it is allowed to execute. In event-triggered (ET) systems on the other hand, tasks are released for execution as a consequence of events, whose times of occurrence are not necessarily known in advance [17]. These events may indeed be related with time, such as the recurrent expiration of a timer cycle, but they can also be asynchronous, such as entering a particular system state, or receiving particular sensor or user inputs. At runtime, the scheduler makes online decisions about which task to execute, typically based on the priorities assigned to tasks whose activation events have occurred and need be handled. More extensive comparisons between time- and event-triggered systems are given in [95, 97].

## 2.5 Preemptive vs non-preemptive scheduling

Preemption is a key factor in real-time scheduling algorithms, since it allows the operating system to immediately allocate the processor/core to incoming tasks that have higher priority to complete [77]. Task priorities are determined by the scheduling algorithm used. For instance, under dynamic priority scheduling such as EDF, higher priority task corresponds to higher urgency due to its earlier deadline.

Through fully preemptive scheduling, the scheduler can suspend a running task on a processor/core at any time. The context of the preempted task is saved, and be replaced with the one of the higher priority task. Whenever a preemption occurs, diffrent sources of overhead must be considered. We will go into more detail regarding these overheads in the next chapter.

In the contrast, a task can not be interrupted in the non-preemptive scheduling. Once the task starts its execution, it executes until completion, even when higher priority tasks arrive, which will allow for more predictable execution behavior. However, the system utilization may be degraded since additional blocking delays must to be considered in this case. This is a popular problem in the non-preemptive scheduling called the *priority inversion*. The priority inversion problem occurs when a higher priority task cannot execute (remains blocked) waiting for a low priority task to complete its execution.

Indeed, when the preemption cost is neglected in the analysis, fully preemptive scheduling is more efficient in terms of processor utilization than nonpreemptive scheduling.

## 2.6 Earliest Deadline First (EDF)

In this document, we limit ourselves to fixed-job priority scheduling.

As mentioned previously, Earliest Deadline First (EDF) is a fixed-job priority scheduler. It assigns the higher priority to the job having the smallest value of absolute deadline. EDF's scheduling analysis changes depending on whether it is preemptive or non-preemptive scheduling. In this chapter, the scheduling analyses for EDF are presented for systems with and without preemptions.

### 2.6.1 Preemptive real-time scheduling

#### Synchronous tasks

EDF is an optimal scheduling algorithm on preemptive uniprocessor, that is, if there exists an real-time scheduler for a set of tasks, EDF can also schedule these tasks while respecting their timing constraints. The schedulability analysis of a preemptive system using EDF algorithm is based on the use of the processor demand bound analysis proposed by Baruah et al. [130]. We start from the concept of *demand function*. The demand function (df) for a given task set  $\mathcal{T}$  is the amount of time demanded by the tasks in an interval  $[t_1, t_2)$  that the core/processor must execute. The demand function is defined as:

$$df(t_1, t_2) = \sum_{i=1}^{|\mathcal{T}|} \Delta_i(t_1, t_2) \cdot \mathsf{C}_i$$

(2.2)

where:

$$\Delta_i(t_1, t_2) = \left( \left\lfloor \frac{t_2 - \phi_i - \mathsf{D}_i}{\mathsf{T}_i} \right\rfloor - \left\lceil \frac{t_1 - \phi_i}{\mathsf{T}_i} \right\rceil + 1 \right)_0 \tag{2.3}$$

is the number of jobs of task  $\tau_i$  with release time greater than or equal to  $t_1$  and deadline less then or equal to  $t_2$  [130].

Considering a fully preemptive single core/processor scheduler, a necessary and sufficient condition for a set of tasks to be schedulable by EDF consists in checking that the demand never exceeds the length of the interval.

**Lemma 1** (Baruah et al. [130]). The taskset  $\mathcal{T}$  is feasible on a single core/processor ( $U_{\mathcal{T}} \leq 1$ ) if and only if:

$$\forall 0 \le t_1 < t_2 \le 2\mathsf{H} + \phi_{\max}, \quad df(t_1, t_2) \le t_2 - t_1$$

(2.4)

where  $\phi_{max}$  is the largest offset.

The worst case demand is found for intervals starting at 0. Thereby, we can define the *demand bound function (dbf.* For a set of synchronous periodic tasks and of a set of sporadic tasks  $\mathcal{T} = \{\tau_1, \dots, \tau_n\}$ , the demand bound function  $\mathsf{dbf}(\mathcal{T}, t)$  corresponds to the maximum cumulative worst-case execution time of all jobs having their arrival time and absolute deadline within any interval of time of length t. It can be computed as follow:

$$\mathsf{dbf}(t) = \sum_{i=1}^{|\mathcal{T}|} \mathsf{dbf}_i(t) \tag{2.5}$$

Where  $\mathsf{dbf}_i(t)$  is the demand bound function of a task  $\tau_i$  in the interval of time of length t computed as follow:

$$\mathsf{dbf}_i(t) = df(0, t) \tag{2.6}$$

An exact schedulability test for a set of synchronous tasks was proposed by Baruah et al. [130]: if for each interval of length t, the demand bound of the task set is less than t, then the system is schedulable.

**Theorem 1** Given a set of tasks  $\mathcal{T}$ .  $\mathcal{T}$  is schedulable on a single core if and only if:

- $U_T \leq 1$  and,

- $\forall t \leq L^*, \mathsf{dbf}(t) \leq t$

where  $L^*$  is an estimated upper bound on the first idle time.

We can continue testing until H, instead of ending at  $L^*$ .

#### Asynchronous tasks

The previous theorem 1 of Baruah et al. [130] does not hold in the case of asynchronous task sets. It still gives a sufficient condition, in the sense that if the hypothesis holds for the corresponding synchronous task set, than the original asynchronous task set is feasible. However the condition is no longer necessary. Authors in [96] proposed an approximate schedulability test with pseudo-polynomial complexity for asynchronous task sets:

$$\forall t \le L^*, \mathsf{dbf}(t) = \max_{\forall \tau_i \in \mathcal{T}} \left\{ \sum_{\tau_j \in \mathcal{T}} \left( \left\lfloor \frac{t - \overline{\phi}_{j,i} - d_j}{\mathsf{T}_i} \right\rfloor + 1 \right)_0 \cdot \mathsf{C}_j \right\}$$

(2.7)

where  $\overline{\phi}_{j,i} = (\phi_j - \phi_i) \mod \mathsf{T}_i$ . To understand Equation (6.15), consider that all the other tasks in  $\mathcal{T}$  are activated with an offset relative to the arrival of  $\tau_i$ . Therefore, we need to align the offset of one task to the beginning of an interval of length t and compute the workload generated in the interval. We do this for every task, and then we take the maximum. The resulting dbf is an upper bound to the actual dbf in that interval.

### 2.6.2 Non-preemptive real-time scheduling

#### Synchronous tasks

Jeffay et al. [124] proposed a schedulability test for non-preemptive systems. This test is valid only for systems with tasks that have implicit deadlines. For a task set  $\mathcal{T}$  where tasks are sorted in non-decreasing order by period (i.e., for any pair of tasks  $\tau_i$ ,  $\tau_j$ , if i > j, then  $\mathsf{T}_i \ge \mathsf{T}_j$ ). If  $\mathcal{T}$  is schedulable then:

1)

$$\sum_{\tau_i \in \mathcal{T}} \frac{\mathsf{C}_i}{\mathsf{T}_i} \le 1; \tag{2.8}$$

2)

$$\forall i, 1 < i \le |\mathcal{T}|; \ \forall t, \mathsf{T}_1 < t < \mathsf{T}_i: \ \mathsf{C}_i + \sum_{j=1}^{i-1} \left\lfloor \frac{t-1}{\mathsf{T}_j} \right\rfloor \cdot \mathsf{C}_j \le t$$

(2.9)

In the first condition, we verify that the processor's global utilization does not exceed its computing capacity; Then, the second condition ensures that task blocking does not compromise adherence to time constraints.

For tasks with constrained deadline, the demand bound function can be expressed as follow [92]:

$$dbf(t) = \sum_{i=1}^{|\mathcal{T}|} dbf_i(t) + B(t)$$

(2.10)

where:

$$\mathsf{B}(t) = \max\{\mathsf{C}_j \mid \mathsf{D}_j > t\}.$$

(2.11)

is the blocking time due to non-preemptive scheduling.

#### Asynchronous tasks

Schedulability analysis of tasks with offsets has been studied in [96]. Authors proposed a theorem which deals with blocking time due to mutually exclusive resources:

**Theorem 2** Given an asynchronous task set  $\mathcal{T}$ . The tasks are schedulable if the cumulative utilisation is less than 1 ( $U_{\mathcal{T}} \leq 1$ ) and,

$$\forall t < L^*, \quad \sum_{\tau_i \in \mathcal{T}} \mathsf{dbf}_i(t) + \mathsf{B}(t) \le t$$

(2.12)

This theorem will be extended in Chapter 6 to the AECR-DAG task sets.

Further considerations had to be taken into account for a multiprocessor settings [1, 103, 131]. As our focus is on working with modern cyber-physical systems, which typically involve multicore CPUs, in the next section, we provide background for multiprocessor scheduling on real-time systems.

## 2.7 Preemptive multiprocessor real-time scheduling

The problem of scheduling real-time applications on multiprocessor systems is more complicated and challenging than real-time scheduling on uniprocessor systems. It is because there are more decisions to be taken in the case of multiprocessor scheduling and more issues to be considered.

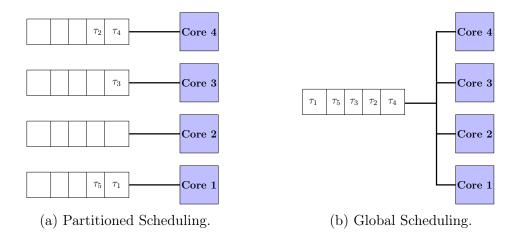

On a multiprocessor, which we deal with throughout this thesis, real-time scheduling can be further classified into two categories: (i) Global and (ii) Partitioned (Semi-Partitioned and Federated scheduling are not considered in this work).

- Under global scheduling, tasks may migrate across processors. Two diffrent migration types are found:

- Job level migration: a job can start its execution on a processor and be interrupted to continue its execution in an other processor.

- Task level migration: a job is executed on only one processor/core, but jobs of the same task may be executed on different processors.

- Under partitioned scheduling, tasks are pinned to specific processor/core and may not migrate even if other cores are idle. Mostly, partitioning algorithms passes through three steps: (i) sorting tasks according to some criteria (for example sorting by deadline); (ii) Assign tasks to a processor; (iii) and the use of uniprocessor scheduling algorithms on each processor to schedule the processor's tasks after each task-to-processor assignment.

To make the difference between the two categories, we present in the following an illustration example of a platform with 4 cores (Figure 2.3). In Figure 2.3a representing the partitioned scheduling, each core has its own ready-queue. In the other hand, in Figure 2.3b representing the global scheduling, all cores have the same ready-queue and the m-highest priority jobs are run at the same time on m-processors.

Figure 2.3: Partitioned scheduling vs global scheduling.

While it may seem intuitive to always prefer global scheduling due to higher utilization benefits, previous works have shown that partitioned scheduling is much easier to analyze and can be used for most practical cases instead because it effectively boils down to the uniprocessor case for each core, allowing a large body of existing analyses to be applicable [25]. On the contrary, while global scheduling offers fast average-case response times, it is relatively harder to analyze and has high overheads in practice [67, 81]. The worst-case performance remains comparable to partitioned scheduling, which makes it less gainful for real-time systems. As a result, we focus on partitioned fixed-job priority task scheduling in our work.

An important consideration under partitioned scheduling is the manner in which tasks are partitioned across multiple computing resources. As this is proved to be a NP-hard problem, existing real-time literature suggests the use of heuristics such as *Best-fit (BF* and *Worst-fit (WF)* [1, 103] to allocate tasks on processor cores. In this thesis, we propose several exact methods for real-time task partitioning on a multicore platform.

### 2.8 Conclusion

In this chapter, we presented an overview of real-time systems and scheduling theory for uniprocessor and multiprocessor systems. We assume that all ingredients are ready to enter into our problem analysis. In the next chapter, we will discuss in details the runtime overheads in multicore architecture.

## Chapter 3

## Processor and Memory Co-scheduling in Multicore Systems

## Contents

| 3.1        | Introduction                                       | <b>27</b> |

|------------|----------------------------------------------------|-----------|

| 3.2        | Cache related delays in multicore systems          | <b>27</b> |

| 3.3        | Shared resources contention: main memory and buses | 29        |

| <b>3.4</b> | Related work                                       | 30        |

| 3.5        | Conclusion                                         | 34        |

## 3.1 Introduction