# Approximated Computing-based Methods for Hardware Resources Reduction Targeting Heterogeneous Systems Hugo Miomandre

#### ► To cite this version:

Hugo Miomandre. Approximated Computing-based Methods for Hardware Resources Reduction Targeting Heterogeneous Systems. Signal and Image processing. INSA de Rennes, 2022. English. NNT: 2022ISAR0021. tel-04496146

# HAL Id: tel-04496146 https://theses.hal.science/tel-04496146v1

Submitted on 8 Mar 2024

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THÈSE DE DOCTORAT DE

L'INSTITUT NATIONAL DES SCIENCES APPLIQUÉES DE RENNES COMUE UNIVERSITÉ BRETAGNE LOIRE

ÉCOLE DOCTORALE N° 601 Mathématiques et Sciences et Technologies de l'Information et de la Communication Spécialité : Signal, Image, Vision

# Par Hugo MIOMANDRE

### Approximated Computing-based Methods for Memory Resources Reduction Targeting Heterogeneous Systems

Thèse présentée et soutenue à Rennes, le 05 Décembre 2022 Unité de recherche : IETR Thèse N° : 22ISAR 35 / D22 - 35

#### Rapporteurs avant soutenance :

Alberto BOSIO Professeur des Universités, INL, École Centrale Lyon

Christophe JÉGO Professeur des Universités, IMS, Bordeaux INP

#### Composition du Jury :

| Président :<br>Examinateurs : | Daniel CHILLET<br>Francesca PALUMBO | Professeur des Universités, IRISA, Enssat<br>Associate Professor, UNISS |

|-------------------------------|-------------------------------------|-------------------------------------------------------------------------|

|                               | Nicolas GAC                         | Maître de Conférence (HdR), L2S, CentraleSupélec                        |

|                               |                                     |                                                                         |

|                               | Alberto BOSIO                       | Professeur des Universités, INL, École Centrale Lyon                    |

|                               | Christophe JÉGO                     | Professeur des Universités, IMS, Bordeaux INP                           |

| Dir. de thèse :               | Jean-François NEZAN                 | Professeur des Universités, IETR, INSA Rennes                           |

| Encadrant :                   | Daniel MÉNARD                       | Professeur des Universités, IETR, INSA Rennes                           |

# Table of Contents

| A | cknov | wledge  | ments                                                                        | 7  |

|---|-------|---------|------------------------------------------------------------------------------|----|

| 1 | Intr  | oducti  | on                                                                           | 9  |

|   | 1.1   | Genera  | al Context                                                                   | 10 |

|   | 1.2   | Scope   | of this Thesis and Contributions                                             | 12 |

|   | 1.3   | Outlin  | e                                                                            | 13 |

| Ι | Ba    | ockgro  | ound                                                                         | 15 |

| 2 | App   | oroxim  | ate Computing                                                                | 17 |

|   | 2.1   | Overvi  | ew of Approximate Computing Techniques                                       | 18 |

|   |       | 2.1.1   | Computation Level                                                            | 18 |

|   |       | 2.1.2   | Hardware Level                                                               | 20 |

|   |       | 2.1.3   | Data Level                                                                   | 21 |

|   |       |         | 2.1.3.1 Reduction of the number of data $\ldots \ldots \ldots \ldots \ldots$ | 21 |

|   |       |         | 2.1.3.2 Relaxed Synchronization                                              | 23 |

|   | 2.2   | Precisi | on Optimisation                                                              | 23 |

|   |       | 2.2.1   | Floating-Point Representation                                                | 24 |

|   |       | 2.2.2   | Fixed-Point Representation                                                   | 27 |

|   |       | 2.2.3   | Variation from IEEE-754 Floating-Point Standard                              | 31 |

#### TABLE OF CONTENTS

| 3  | Pro | gramn                             | ning Models                                                                  | 37 |  |  |  |  |

|----|-----|-----------------------------------|------------------------------------------------------------------------------|----|--|--|--|--|

|    | 3.1 | 3.1 Task-based Programming Models |                                                                              |    |  |  |  |  |

|    |     | 3.1.1                             | Processes                                                                    | 39 |  |  |  |  |

|    |     | 3.1.2                             | Threads                                                                      | 40 |  |  |  |  |

|    |     |                                   | 3.1.2.1 POSIX Threads                                                        | 40 |  |  |  |  |

|    |     |                                   | 3.1.2.2 OpenMP                                                               | 41 |  |  |  |  |

|    | 3.2 | Accele                            | rator-based Programming Models                                               | 42 |  |  |  |  |

|    |     | 3.2.1                             | OpenCL/CUDA                                                                  | 43 |  |  |  |  |

|    |     | 3.2.2                             | OpenACC/OpenMP 4.0                                                           | 44 |  |  |  |  |

|    | 3.3 | Datafl                            | ow-based Models of Computation                                               | 45 |  |  |  |  |

|    |     | 3.3.1                             | Process Network                                                              | 45 |  |  |  |  |

|    |     | 3.3.2                             | Parallelism with Dataflow Model of Computation $\ldots \ldots \ldots \ldots$ | 46 |  |  |  |  |

|    |     | 3.3.3                             | Synchronous Dataflow (SDF)                                                   | 48 |  |  |  |  |

|    |     | 3.3.4                             | Parameterized and Interfaced Synchronous Dataflow (PiSDF) $\ . \ .$          | 49 |  |  |  |  |

|    |     | 3.3.5                             | Existing tools for Dataflow Applications Design                              | 52 |  |  |  |  |

| 4  | Ap  | olicatio                          | ons                                                                          | 55 |  |  |  |  |

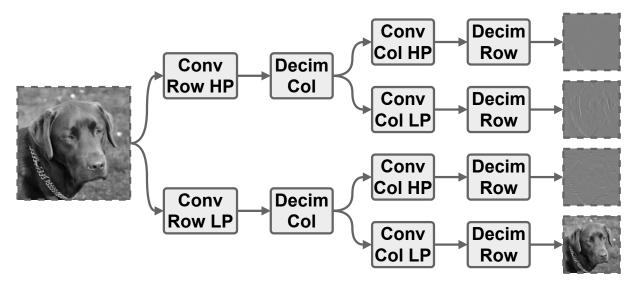

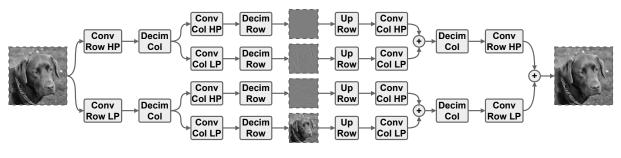

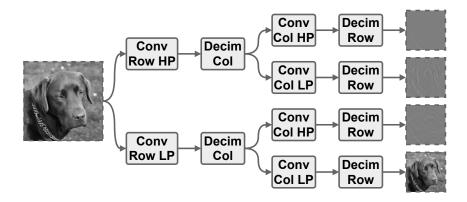

|    | 4.1 | 2D Wa                             | avelet Filter                                                                | 56 |  |  |  |  |

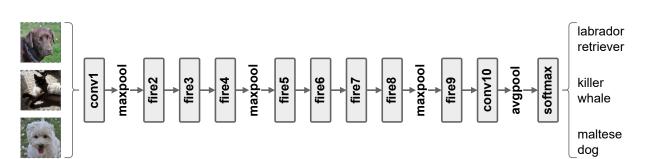

|    | 4.2 | Squeez                            | zeNet CNN                                                                    | 58 |  |  |  |  |

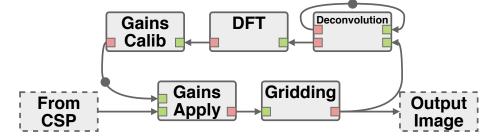

|    | 4.3 | Square                            | e Kilometre Array Science Data Processor Implementation                      | 59 |  |  |  |  |

| II | С   | ontri                             | butions                                                                      | 63 |  |  |  |  |

| 5  | Dat | a Rep                             | resentation in Approximate Buffer                                            | 65 |  |  |  |  |

|    | 5.1 |                                   | Soncept of Approximate Buffer                                                | 66 |  |  |  |  |

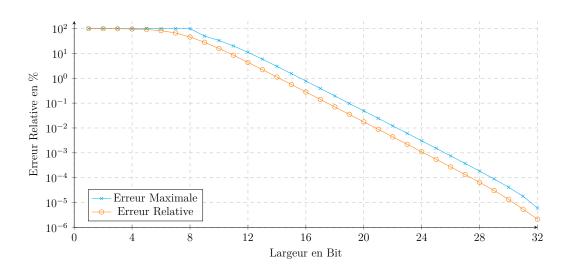

|    | 5.2 |                                   | Truncation                                                                   | 67 |  |  |  |  |

|    | 5.3 |                                   | Point Representation                                                         | 69 |  |  |  |  |

|    | 5.4 | Custo                             | m Floating-Point Representation                                              | 72 |  |  |  |  |

|    | 5.5 |                                   | m Quantization                                                               | 74 |  |  |  |  |

|    | 5.6 |                                   | imental Results                                                              | 77 |  |  |  |  |

|    |     | 5.6.1                             | 2D Wavelet Filter                                                            | 77 |  |  |  |  |

|    |     | 5.6.2                             | SqueezeNet Deep Neural Network                                               | 80 |  |  |  |  |

|    |     | 5.6.3                             | SDP Evolutionary Pipeline                                                    | 81 |  |  |  |  |

| Imp | olemen                                                             | tation for Approximate Buffer                                                                                                                                                                                                                                                                                                  | 85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|-----|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 6.1 | .1 Software Implementation for CPU                                 |                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

|     | 6.1.1                                                              | Data conversion                                                                                                                                                                                                                                                                                                                | 87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|     | 6.1.2                                                              | Insertion/extraction                                                                                                                                                                                                                                                                                                           | 88                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|     | 6.1.3                                                              | Experimental Results                                                                                                                                                                                                                                                                                                           | 92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|     |                                                                    | 6.1.3.1 2D Wavelet Filter                                                                                                                                                                                                                                                                                                      | 92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|     |                                                                    | $6.1.3.2  SqueezeNet  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  $                                                                                                                                                                                                                                | 93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|     |                                                                    | 6.1.3.3 Science Data Processor                                                                                                                                                                                                                                                                                                 | 96                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

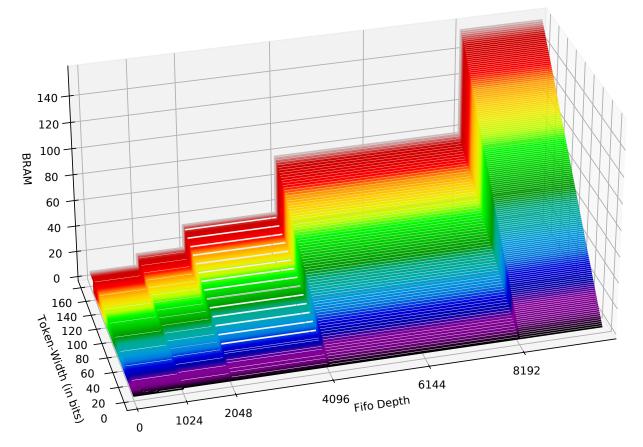

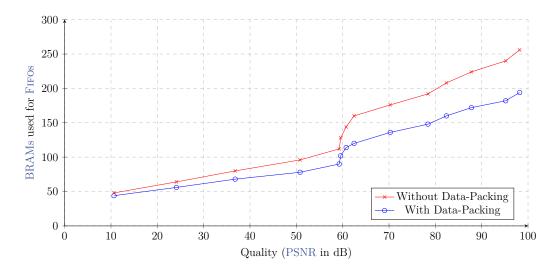

| 6.2 | Hardw                                                              | vare Implementation for FPGA                                                                                                                                                                                                                                                                                                   | 97                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|     | 6.2.1                                                              | Results on FPGA                                                                                                                                                                                                                                                                                                                | 101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| Des | ign Sp                                                             | ace Exploration for Approximate Buffers                                                                                                                                                                                                                                                                                        | 105                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| 7.1 | State                                                              | of the Art on Design Space Exploration for Approximate Computing                                                                                                                                                                                                                                                               | 106                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| 7.2 | Auton                                                              | natic Approximate Buffer Configuration                                                                                                                                                                                                                                                                                         | 107                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|     | 7.2.1                                                              | Memory Footprint Minimisation Algorithm                                                                                                                                                                                                                                                                                        | 107                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|     |                                                                    | 7.2.1.1 Min Value Determination                                                                                                                                                                                                                                                                                                | 107                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|     |                                                                    | 7.2.1.2 Iterative Process                                                                                                                                                                                                                                                                                                      | 109                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|     |                                                                    | 7.2.1.3 Bit Scraping                                                                                                                                                                                                                                                                                                           | 111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|     | 7.2.2                                                              | Complexity Analysis                                                                                                                                                                                                                                                                                                            | 112                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|     | 7.2.3                                                              | Example                                                                                                                                                                                                                                                                                                                        | 113                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| 7.3 | Exper                                                              | imental Results                                                                                                                                                                                                                                                                                                                | 115                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|     | 7.3.1                                                              | 2D Wavelet Filter                                                                                                                                                                                                                                                                                                              | 115                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|     | 7.3.2                                                              | SqueezeNet CNN                                                                                                                                                                                                                                                                                                                 | 116                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|     | 7.3.3                                                              | SDP Imaging Pipeline                                                                                                                                                                                                                                                                                                           | 117                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

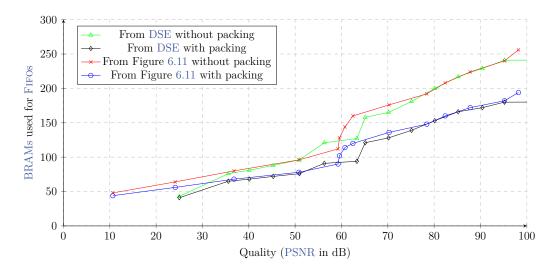

|     | 7.3.4                                                              | 2D-DWT on FPGA                                                                                                                                                                                                                                                                                                                 | 118                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| Cor | nclusio                                                            | n                                                                                                                                                                                                                                                                                                                              | 121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| 8.1 | Summ                                                               | ary                                                                                                                                                                                                                                                                                                                            | 121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| 8.2 |                                                                    |                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

|     | 8.2.1                                                              | Impact on Other Parameters                                                                                                                                                                                                                                                                                                     | 123                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|     | 8.2.2                                                              | Extension with Additional Features                                                                                                                                                                                                                                                                                             | 123                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|     | 8.2.3                                                              | Interactions with Complementary Approaches                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| Fre | nch Su                                                             | mmary                                                                                                                                                                                                                                                                                                                          | 125                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|     |                                                                    |                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

|     | 6.1<br>6.1<br>7.1<br>7.2<br>7.3<br>7.3<br>7.3<br>7.3<br>7.3<br>7.3 | 6.1       Softwa $6.1.1$ $6.1.2$ $6.1.3$ $6.1.3$ $6.2$ Hardwa $6.2.1$ State $7.2$ Auton $7.2.1$ State $7.2.2$ $7.2.3$ $7.3$ Exper $7.3.1$ $7.3.2$ $7.3.1$ $7.3.4$ Co-lusion $8.1$ Summ $8.2$ Future $8.2.1$ $8.2.2$ $8.2.3$ $8.2.3$ | 6.1.1       Data conversion         6.1.2       Insertion/extraction         6.1.3       Experimental Results         6.1.3.1       2D Wavelet Filter         6.1.3.2       SqueezeNet         6.1.3.3       Science Data Processor         6.2       Hardware Implementation for FPGA         6.2.1       Results on FPGA         6.2.1       Results on FPGA         6.2.1       Results on FPGA         7.1       State of the Art on Design Space Exploration for Approximate Buffers         7.1       State of the Art on Design Space Exploration for Approximate Computing         7.2       Automatic Approximate Buffer Configuration         7.2.1       Memory Footprint Minimisation Algorithm         7.2.1.1       Min Value Determination         7.2.1.2       Iterative Process         7.2.3       Example         7.3.3       Experimental Results         7.3.1       2D Wavelet Filter         7.3.2       SqueezeNet CNN         7.3.3       SDP Imaging Pipeline         7.3.4       2D-DWT on FPGA         8.1       Summary         8.2       Future Works         8.2.1       Impact on Other Parameters         8.2.2       Extension with Addi |  |  |  |  |

#### TABLE OF CONTENTS

|         | A.1.1   | Portée de cette Thèse et Contributions | . 126 |

|---------|---------|----------------------------------------|-------|

|         | A.1.2   | Outline                                | . 127 |

| A.2     | État d  | e l'Art                                | . 127 |

|         | A.2.1   | Calcul à-Peu-Près AxC                  | . 127 |

|         | A.2.2   | Modèle de Calculs Flot de Donnée       | . 129 |

| A.3     | Conce   | pt de Mémoire Tampon à-Peu-Près        | . 130 |

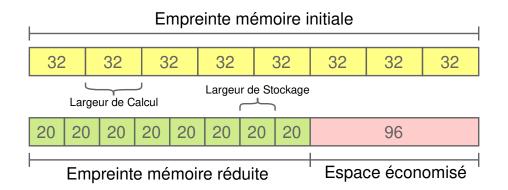

| A.4     | Implén  | nentation de Mémoire Tampon à-Peu-Près | . 131 |

| A.5     | Conclu  | ision                                  | . 134 |

| List of | Figure  | es                                     | 137   |

| List of | Tables  | 5                                      | 138   |

| List of | Listing | gs                                     | 139   |

| Acrony  | yms     |                                        | 140   |

| Glossa  | ry      |                                        | 145   |

| Person  | al Pub  | lications                              | 147   |

| Bibliog | raphy   |                                        | 149   |

# Acknowledgements

I would like to thank my thesis directors, Jean-François Nezan et Daniel Ménard for their guidance and support during the 3 years of this PhD, my reviewers Alberto Bosio and Christophe Jégo for taking the time to read this manuscript, and the members of the jury Daniel Chillet, Francesca Palumbo and Nicolas Gac.

I would also like to thank Karol Desnos and Kevin Martin for the internship opportunity that ultimately led me down this path.

Moreover, thank to the SARS-CoV-2 which made me waste roughly a year of work and productivity.

Finally, I would like to thank everyone from the EII department and the VAADER research team, both for the three years of my engineering degree and for the three years of my PhD and INSA Rennes, and to the occupants of office 214 for the everyday stupidity.

# CHAPTER 1

# Introduction

Since the last few decades, the volume of processed data has been growing in conjunction with the increase in computational power of High-Performance Computing (HPC) systems, as well as the generalization of connected embedded systems in all forms, from Internet of Things (IoT) devices to smartphones.

Embedded systems are computer systems purposely designed for specific applications, as stand-alones such as autonomous lawnmower, digital camera or home appliances, or as part of bigger assemblies such as the multiple subsystems in vehicles.

The increase in computing resources also goes in pair with the augmentation and complexification of memory related systems. Both on personal computers and smartphones, the amount of available RAM doubles every 2 to 3 years<sup>1</sup>. In a computer system, memory is used to store data, to store program instruction, to save temporary values, and for synchronization.

An infinitely fast processor can only operate as fast as data are transmitted to and from it. The issue of avoiding this memory wall [WM95; JWN10; Ziv+17] has been known for at almost 3 decades, leading to the conception of dedicated memory-specific mechanisms. Consequently, it is evaluated that up to 80% of silicon area can be dedicated to caches, memories, memory controllers, interconnects for the sole purpose of data transmission

<sup>1.</sup> Example with smartphones: iPhone 2G (2007): 128MB, iPhone 14 Pro (2022): 6GB, Current highest-end: 18GB

inside a chip [DCD97]. Additionally, the transfer of data between memory and Processing Elements (PEs) can represent up to 62% of the energy consumed by the whole system.

As an example, in Advanced Micro Devices (AMD) Central Processing Units (CPUs) with the Zen 3 architecture, the 32MB L3 cache alone takes around 52% of a CCD<sup>2</sup> silicon area, but an additional 64MB can be stacked on top of it [Bur+22], for a total of 96MB, 12MB per core. Similarly, in AMD Graphics Processing Units (GPUs) with the RDNA 3 architecture, a fully enabled chip features a 300mm<sup>2</sup> main die accompanied by 6 individual 37mm<sup>2</sup> 16MB Last Level Cache (LLC) dies, resulting in 43% of the silicon area dedicated solely to LLC.

#### **1.1** General Context

The increased volume of processed data impacts computing systems on every scale, from edge computing [ZC20] to HPC. It also affects the consumer scale, with use-cases such as image processing on smartphones [Mor+21], where the amount of data processing have skyrocketed both in hardware and in software, with the improvement of camera sensors and screens along with the onboard processing power.

#### Large Scale Computations

The increase of data processing capabilities enables the computation of complex datasets for specific purposes [Bra19]. The most common everyday example concerns the collection and exploitation of user-generated data by companies of the information technology industry. Often designated with acronyms such as GAFAM<sup>3</sup> or FAANG<sup>4</sup>, these companies rely on large scale data processing for user profiling and recommendations [AT05].

Other application examples of intense data processing are scientific research projects such as the Large Hadron Collider (LHC) or the Square Kilometre Array (SKA) radio telescope.

The LHC is largest and highest-energy particle collider, designed for research in particle physics, at the European Organization for Nuclear Research (CERN). It consists in a 27 kilometres ring, with detectors specialized for specific phenomena. The LHC contains about 150 million sensors delivering data 40 million times per second, filtered to a few

<sup>2.</sup> Core Complex Die, containing up to 8 cores.

<sup>3.</sup> GAFAM: Google, Apple, Facebook, Amazon, Microsoft.

<sup>4.</sup> FAANG: Facebook, Amazon, Apple, Netflix, Google.

thousands collision per seconds, for a yearly production of 88 Petabytes. The power consumption for the LHC alone is about 90 Megawatts, and 200 Megawatts for all of CERN. The LHCb detector alone, upgraded in 2022, can process around 4 Terabytes per seconds of raw data, selecting 10 Gigabytes per seconds of interesting collision data.

The SKA radio telescope is an international effort to build the world's largest radiotelescope, with a final collecting area of around one square kilometre. The SKA is expected to start its operations with hundreds of parabolic dishes and tens of thousands antennae in South Africa and Australia, producing more than 30 terabits per seconds of raw data.

#### Machine Learning

Machine learning have found applications in various domains, such as image/video processing (classification [KSH12], video compression [Tis+20], image upsampling [Bas+21], autonomous driving [Kir+21; Gri+20]), language processing [OMK18], network intrusion detection [Sou+22; De +21]...

The gain of popularity around machine learning during the last decade as given birth to extremely large deep learning models. These models can be composed of tens to hundreds of billions of parameters and trained on large dataset.

As an example, a few large language processing models can be cited: Generative Pretrained Transformer 3 (GPT-3) [Bro+20] with 175 billion parameters trained on a 45 Terabytes dataset, DeepMind Gopher [Rae+21] with 280 billion parameters trained on MassiveText, a 10.5 Terabytes dataset, Microsoft/Nvidia Megatron-Turing [Smi+22] with 530 billion, or Google PaLM [Cho+22] with 540 billion parameters.

A currently trendy application of machine learning is Text-to-Image generation, with examples such as: DALL-E [Ram+21] (derived from GPT-3) with 12 billions parameters trained on a 250 million image-text pairs dataset, Midjourney, Google Imagen [Sah+22] with 2 billion parameters, Parti [Yu+22] with 20 billion, or Stable Diffusion [Rom+21].

These models require a lot of hardware resources for training and inference, with the power consumption that goes along with it. Specific optimizations such as memory optimizations become increasingly necessary to facilitate the deployment and embedding of these models by reducing the hardware resources requirements as well as the associated memory consumption.

### **1.2** Scope of this Thesis and Contributions

Memory-related limitations are a major consideration during design and deployment of data processing applications on computer systems, either in terms of capacity, energy, transmission or area.

The Approximate Computing (AxC) paradigm [HO13] has emerged as a way to improve the energy efficiency and/or the performance of computer systems, by trading-off result accuracy in application where data integrity is not critical, such as dropping a frame during the encoding or decoding of a video stream. AxC techniques can be segmented in 3 categories, whether they impact the data used during computations, the nature of the computation itself, or parameters of the hardware. These techniques tend to be difficult to implement but are susceptible to reduce the strain on the memory systems of a computing platforms.

Another method to impact the requirement related to memory systems is the use of specific Models of Computation (MoCs). Describing a data processing application with specific MoCs can highlight opportunities for memory optimizations. Dataflow-based MoCs have the particularity of bringing to the forefront the handling of memory, both in terms of allocation and transit, highlighting opportunities for optimization.

The objective of this thesis is to develop new techniques to enable reductions of memory footprint requirements of data processing applications using the AxC paradigm alongside dataflow-based representations.

The main contributions of this thesis are:

- 1. A study of the impact of bit-width and representation of the storage memory of applications on the output quality. Data storage is considered using an arbitrary number of bits, coupled with a customizable data representation to minimize the loss of quality. This contribution has been published partly in [Mio+20].

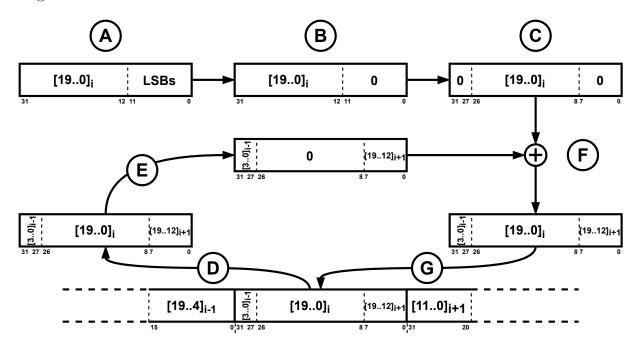

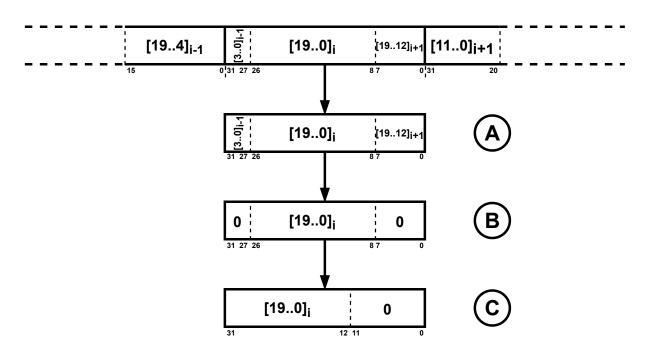

- 2. A method to convert and store in memory of data with an arbitrary bit-width for CPU-based platforms. This method handles the memory operations to store unaligned data of unconventional bit-width into concatenated segments. This contribution has been published partly in [Mio+20].

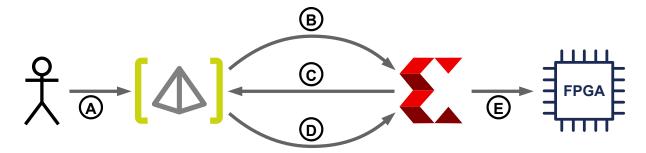

- 3. A method to efficiently insert and extract data from packet for Field-Programmable Gate Array (FPGA) storage resources optimization. This method is able, from a dataflow representation, right after the buffer-sizing process, to find optimal pack-

ing ratio to reduce the requirement on embedded hardware storage resources. This contribution has not been published yet.

4. A Design Space Exploration (DSE) method based on AxC to reduce the memory footprint of an application by reducing the bit-width used for internal data storage. This method finds an acceptable association between data representation and storage bit-width for a set of memory buffer of an application. The memory footprint is minimized while respecting a determined quality constraint. This contribution has been published in [MNM22].

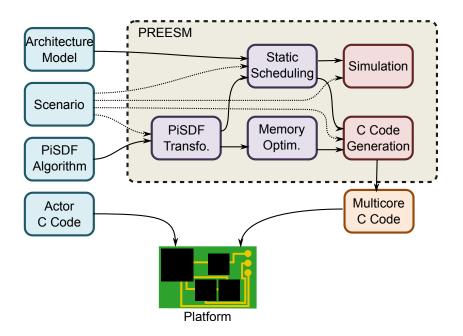

Most of the contributions of this thesis as been integrated into the Parallel and Real-time Embedded Executives Scheduling Method (PREESM) application development framework.

#### 1.3 Outline

This thesis is organized in to parts: Part I presents the general context and motivation of this thesis, and Part II introduces and evaluates the contributions of this thesis.

In Part I, Chapter 2 provides a general overview of AxC techniques and which aspect of an application they affect. Chapter 3 presents the main programming model paradigms for parallel computations, along with the concept of dataflow MoC used in this thesis. Finally, Chapter 4 details the applications used to evaluate the contributions of this thesis.

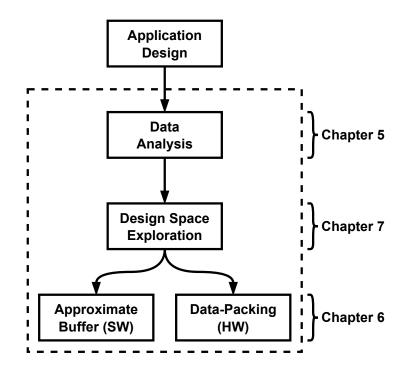

In Part II, Chapter 5 goes over the general concept and impact on quality of the AxC contributions of this thesis. Chapter 6 provides guidelines one the implementation of these contributions. Chapter 7 presents a DSE method for efficient parametrization of the AxC techniques presented in previous chapters. Finally, Chapter 8 concludes this work and proposes potential future research paths.

Part I

# Background

# CHAPTER 2

## Approximate Computing

#### Introduction

An objective of this thesis is to design techniques based on the Approximate Computing (AxC) paradigm. For this purpose, this chapter introduces the concept of AxC and presents a non-exhaustive list of diverse existing AxC techniques. An AxC technique is a technique which, when applied on a system (hardware and/or software), will lead to the production of an inaccurate yet usable output. The compensation for this inaccuracy is a reduced set of resources (processing power, memory footprint, energy consumption, silicon area, ...) or an increase in performance (higher throughput, lower latency, ...) depending on the needs and the AxC techniques used [BMS22].

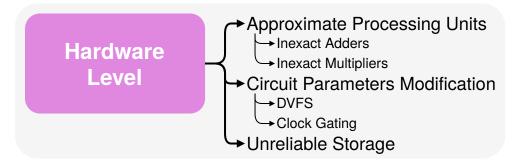

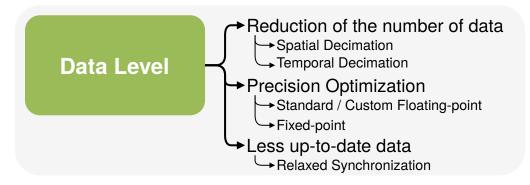

These AxC techniques can be segmented in 3 groups depending on the way they affect the system. First, *Computation Level* AxC techniques modifying the nature of the computations are presented in Section 2.1.1. Then, *Hardware Level* AxC techniques relying on specific hardware behaviour or modification are presented in Section 2.1.2. Finally, *Data Level* AxC techniques applied on the data themselves are presented in Section 2.1.3.

This thesis will specifically focus on *Data Level* AxC techniques aiming at reducing the memory footprint of an application. A wider summary of other AxC techniques is available in [Bon19; XMK15; Mit16; BMS22].

Section 2.1 presents a non-exhaustive overview of various AxC techniques while Section 2.2 specifically focuses on precision optimization and specific data-types.

# 2.1 Overview of Approximate Computing Techniques

#### 2.1.1 Computation Level

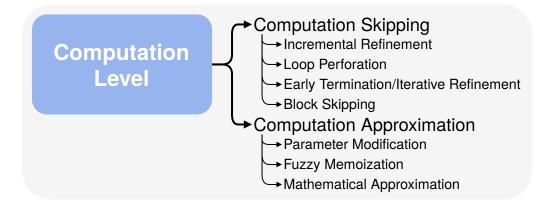

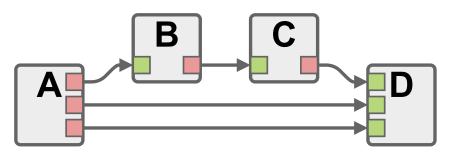

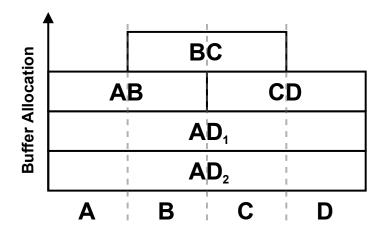

Computation Level AxC techniques consists in modifying the algorithm itself to reduce its complexity. The two main methods are *Computation Skipping* and *Computation Approximation*, as shown in Figure 2.1.

Figure 2.1: Computation-level approximate computing techniques.

Computation Skipping consists in not executing portions of the program to reduce the computation complexity. Fine-grained Computation Skipping can be done with Loop Perforation, by executing only a subset of the iterations of a loop [Sid+11; Vas+15], or by Early Termination, generally by prematurely ending a computation loop of a convergent iterative algorithm such as gradient descent [Meh+09; Zha+14]. A coarser-grained Computation Skipping is doable with Block Skipping, by not executing entire processing blocks of a complex application such as a video encoder/decoder [Bon+22].

Computation Approximation consists in replacing a complex computation by a simpler, faster one, producing close enough results. Two possible methods are *Fuzzy Memoization* and *Mathematical Approximation*. *Memoization* consists in storing the result of a computation in a Look-Up Table (LUT) to reuse it the next time the same computation has to be processed, simply skipping it, working like a cache memory, using input operands as ad-

dresses [Sur+15]. By itself, *Memoization* is not an AxC technique, and benefits from using it could be voided by the size of the LUT stored in memory. *Fuzzy Memoization* extends this principle by masking N Least Significant Bit (LSB) from the operands. This results in group of operands being affected the same LUT address, and thus the same result. The trade-off between output quality, processing time and the LUT memory footprint can be tweaked by adjusting the parameter N. *Mathematical Approximation* techniques are quite straightforward and are commonly used in embedded systems. It consists in implementing simpler mathematical functions in place of more sophisticated ones, as presented in [Mul20]. One way of implementing such method is to approximate a sophisticated function by a group of simpler polynomial functions, which coefficients are stored in a LUT, the N Most Significant Bit (MSB) of the operand serving as the LUT address.

Another method of mathematical approximation is to simply perform a set of computation producing an accurate enough result compared to its accurate counterpart. An example of this is the algorithm for the fast inverse square root (Listing 2.1), made popular for its use in the video game Quake III Arena for computing angles of incidence and reflection for lighting and shading. It computes an approximation of  $\frac{1}{\sqrt{x}}$  with unconventional operations, such as shifting a floating-point operand and subtracting to a magic number (0x5F3759DF).

```

float Q_rsqrt(float number){

1

2

long i;

3

float x2, y;

4

const float threehalfs = 1.5F;

5

6

x2 = number * 0.5F;

7

= number;

у

// evil floating point

8

i

= * ( long * ) &y;

bit level hacking

0x5f3759df - ( i >> 1 );

// what the fuck?

9

i

=

( float * ) &i;

10

=

*

У

= y * ( threehalfs - ( x2 * y * y ) );

// 1st

11

У

iteration

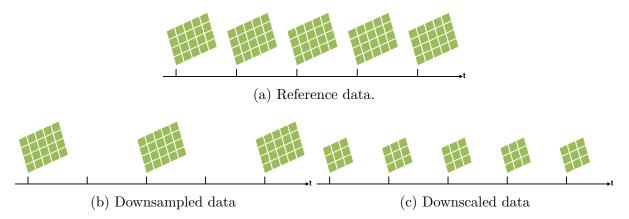

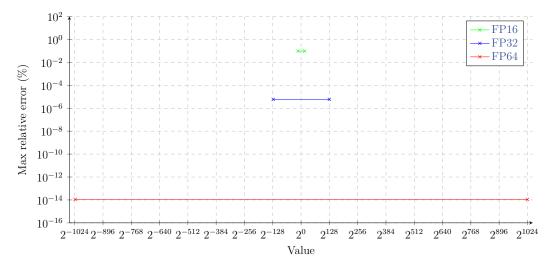

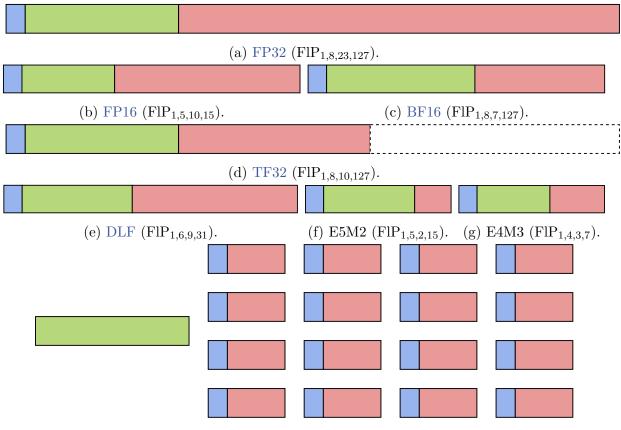

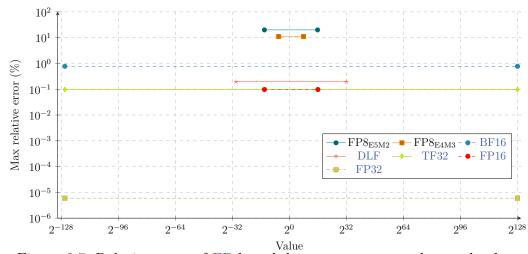

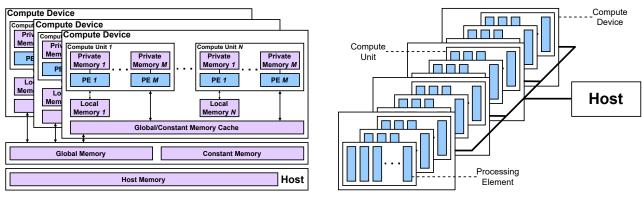

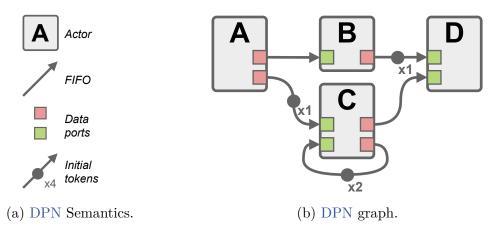

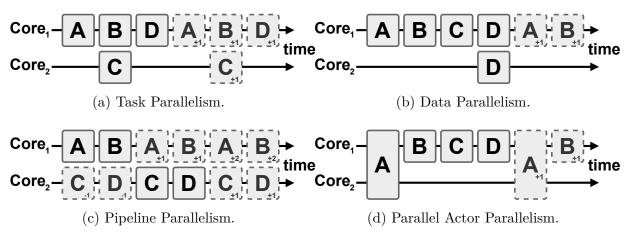

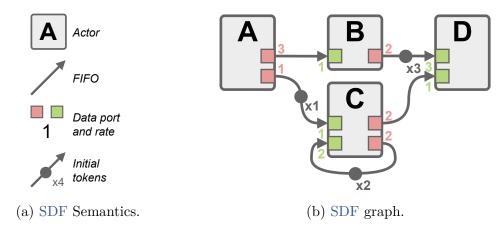

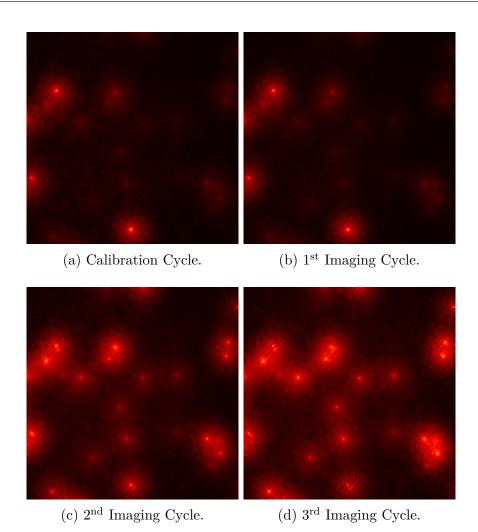

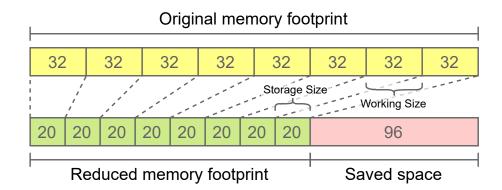

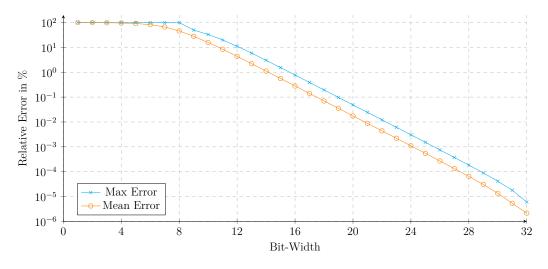

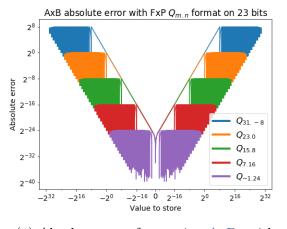

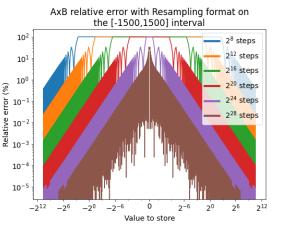

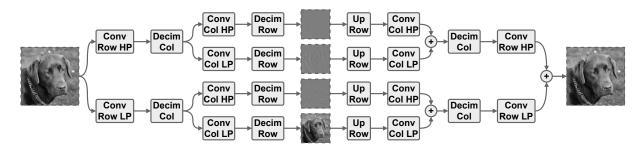

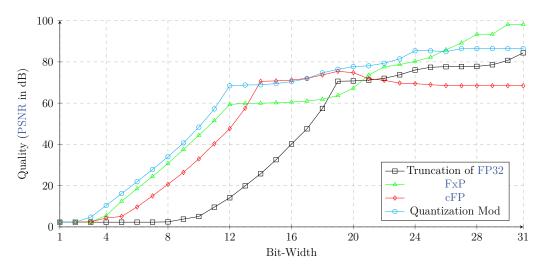

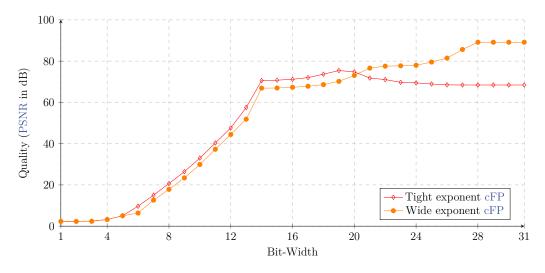

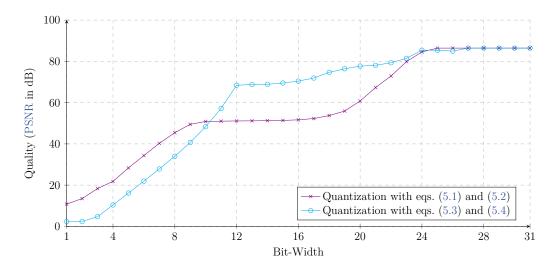

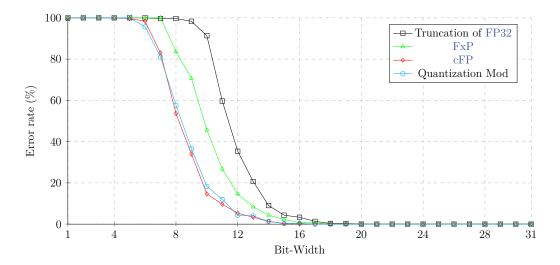

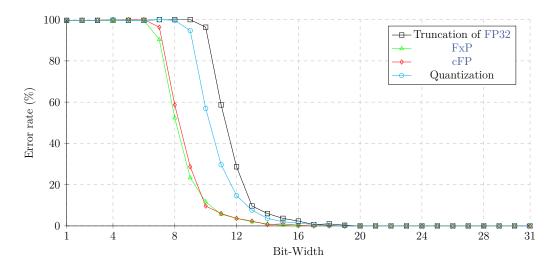

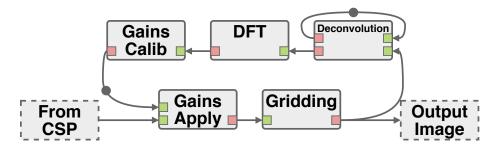

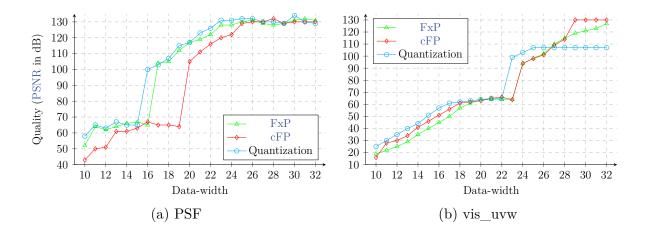

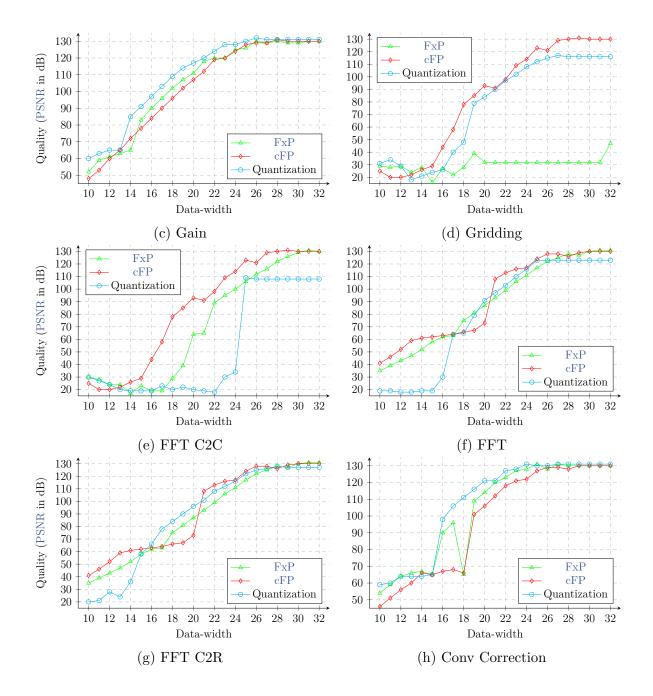

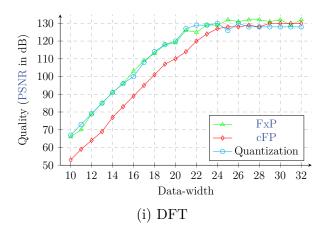

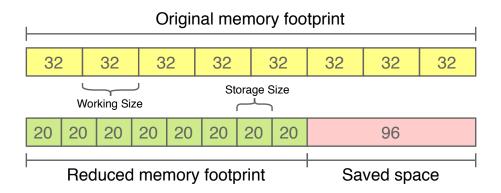

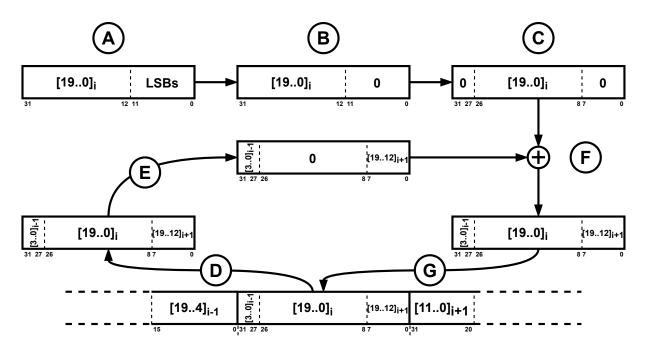

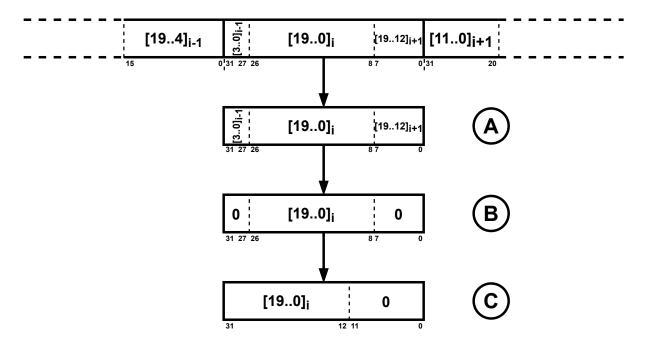

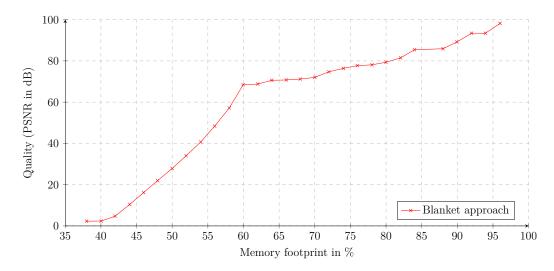

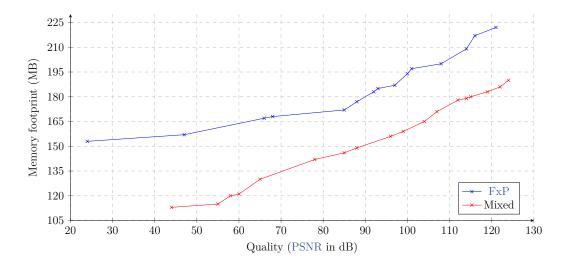

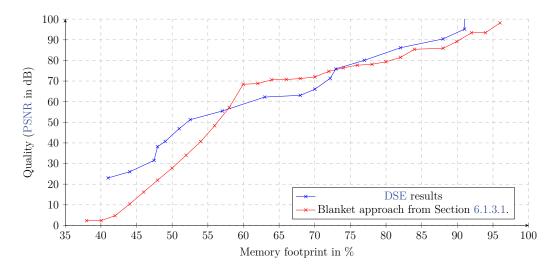

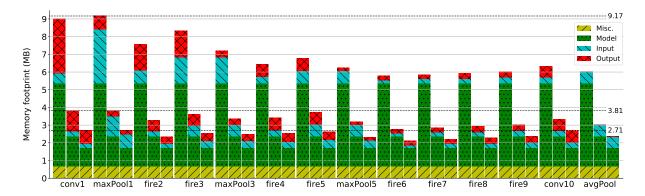

12