# Condition and Health Monitoring of Modular Multilevel Converter for HVDC grids

Diego Alejandro Velazco Navarro

#### ▶ To cite this version:

Diego Alejandro Velazco Navarro. Condition and Health Monitoring of Modular Multilevel Converter for HVDC grids. Electric power. Université Claude Bernard - Lyon I, 2023. English. NNT: 2023LYO10085. tel-04504744

# HAL Id: tel-04504744 https://theses.hal.science/tel-04504744v1

Submitted on 14 Mar 2024

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### THESE de DOCTORAT DE L'UNIVERSITE CLAUDE BERNARD LYON 1

# Ecole Doctorale N° 160 ECOLE DOCTORALE ELECTRONIQUE, ELECTROTECHNIQUE, AUTOMATIQUE DE LYON

Spécialité de doctorat : Génie électrique

Soutenue publiquement le 12/06/2023, par : **Diego Alejandro VELAZCO NAVARRO**

# Du diagnostic au pronostic de l'état de santé des IGBT dans un convertisseur modulaire multiniveaux pour les réseaux HVDC

#### Devant le jury composé de :

Mme. Hélène FREMONT, Professeure des Universités, Univ. Bordeaux 1 Présidente

Mme. Mounira BOUARROUDJ, Maître de conférences (HDR), UPEC-INSPE

M. Huai WANG, Professeur, Université d'Aalborg

Mme. Marie Cécile PERA, Professeure des Universités, UFC

M. Hubert RAZIK, Professeur des Universités, UCBL

Rapporteuse

M. Guy CLERC, Professeur des Universités, UCBL Directeur de thèse M. Emmanuel BOUTLEUX, Maître de conférences, ECL Co-directeur de thèse/Invité

M. François WALLART, Ing. Manager R&D, SuperGrid Institute Encadrant ind./Invité

# Condition and Health Monitoring of Modular Multilevel Converter for HVDC Grids

# A Dissertation submitted to UNIVERSITE CLAUDE BERNARD LYON 1

In partial fulfillment of the requirements for the degree of DOCTOR OF PHILOSOFY

# Presented by:

## Diego Alejandro VELAZCO NAVARRO

Supervised by: Prof. Guy Clerc

Co-supervised by: Dr. Emmanuel Boutleux

2023

A mis papás Franz y Patricia por su esfuerzo y su apoyo incondicional

A mi hermano Alvaro mi compañero de la vida

y a mi abuela María Paz donde quiera que estés...

# Acknowledgements

I would like to take the opportunity to thank all the people that have been present throughout the last years of hard work.

I would like to express my sincere gratitude to the members of the PhD committee. I am honored that they have accepted the invitation to participate in the defense and I profoundly appreciate the interest showed on my work and their contribution to review this dissertation.

I am deeply thankful to my supervisor Prof. Guy Clerc. I have not seen another supervisor so involved in a thesis as him, and for this I would like to thank him. Without his precious guide, this work would have not been possible. Moreover, I would like to thank him for the encouragement throughout the hard times of the thesis and for putting some pressure when it was needed. Working alongside Guy has shown me what hard work really means and has helped me grow professionally and personally.

My sincere gratitude to my co-supervisor Emmanuel Boutleux. The discussions with Emmanuel allowed to see problems from a different perspective. I would also like to thank him for always caring about the mental and human aspect that a thesis demands.

I would like to express my profound gratitude to François Wallart. He was not meant to be my industrial supervisor from the beginning, but he has been completely invested in this project, ever since he took charge. I would like to thank him for all the hours we spent working together and for all the time and hard work that he has devoted so that this thesis can be accomplished. Without François the test bench would have never been possible, and he deserves all my recognition for this. I would also like to thank him for always being joyful to work with, for all the tennis-related conversations and for always looking out for my well-being and keeping me motivated.

I would also like to thank Ms. Hiba Houmsi and Mr. Maxime Valle for their enormous contributions to this work. They contributed to have an operational test bench and performing the estimations of the junction temperature. I would like to acknowledge that they have done a great work and wish them the best of luck for all their future projects.

I would like to thank Mr. Jean François Roche from ARCEL. His involvement in the realization of the test bench was greatly appreciated and the discussions with him have significantly contributed to the development of the experimental setup.

A great thank you to all the members of the Power Electronics team at SuperGrid Institute. They have all contributed in one way or another to the fruition of this work. I would like to thank them for all the time spent together, the coffee breaks, the technical discussions as well as for building long-lasting friendships. It is a real pleasure to be a part of this team.

Finally, a special acknowledgement to my friends and family who have been vital in this process. Their support has meant the world to me and has allowed me to finally, after more than 1 year than expected, to wrap up this thesis.

Abstract

# Abstract

The growing power and energy demand, as well as the integration of new renewable sources into the electrical system and the long distances between electrical consumers and producers are pushing the actual AC grid to evolve. Hence, HVDC has emerged as a promising solution for upgrading the power transmission infrastructure and meet the demanding requirements and future needs of the electrical grid. Moreover, HVDC is nowadays the preferred technology for bulk power transmission and the integration of large-scale renewable sources such as offshore windfarms.

One fundamental component of HVDC systems is the converter station. At the ends of an HVDC line, the converter station is responsible for interfacing the DC link with the AC grid. Among the different types of technology for converter stations VSC have gained in relevance in the last few decades, as they provide improved functionalities when compared to the traditional converters employed for HVDC applications. Concerning VSC topologies, the MMC has emerged as the most advantageous topology and the main candidate for future HVDC projects.

The MMC is a scalable converter composed mainly of stacks of SMs that allow its operation. Each SM is composed itself by a large storage capacitor and IGBT modules used for the insertion or the bypass of the capacitor. As power transmission is a critical application, HVDC systems are subjected to very demanding reliability and availability requirements and the MMC is not the exception. This thesis addresses the condition monitoring and the prognosis of the remaining useful life of IGBT modules in a HVDC-MMC application, as these elements were identified as one of the weakest components present in converter applications.

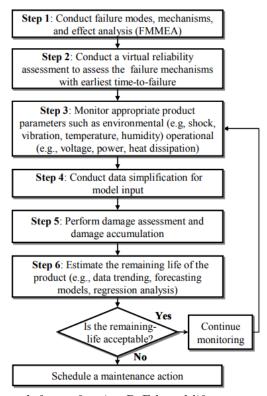

A physics-of-failure approach is chosen for the prognosis scheme. This scheme uses the thermal loading of the semiconductor devices of a HB-SM for making computations of the lifetime consumption in the evaluated period. Then, from this lifetime estimation the remaining useful life can be inferred. Additionally, the prognosis scheme allows the calculation of the reliability of the HB-SM by considering the reliability functions of its composing elements. Consequently, this calculation is used for computing the redundancy needed for attaining the target availability values with the help of a Markov Chain and Monte Carlo simulations.

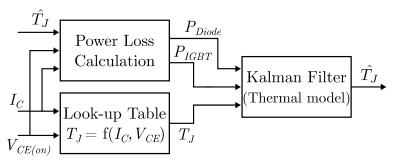

Another important subject addressed in this thesis is the condition monitoring of IGBT modules. For this purpose, a Power Cycling testbench was developed. The  $V_{CE(on)}$  was chosen as the parameter for tracking the evolution of the degradation state of the power device throughout the cycling tests. Consequently, an online  $V_{CE(on)}$  measurement board was conceived and developed. In order to get more relevant insights of the cycling protocol applied, a strategy for the online estimation of the junction temperature of IGBT devices was developed and it is based on the use of a Kalman filter. This strategy also enables to perform an estimation of the degradation of the state-of-health of the IGBT by analyzing the Thermo-Sensitive Electrical Parameters.

<u>Abstract</u> ii

Résumé

# Résumé

Les réseaux de transport d'électricité doivent s'adapter pour faire face aux défis de la croissance de la demande d'énergie, de la rapide expansion des moyens de production des énergies renouvelables et de l'éloignement des centres de production et consommation. Dans ce contexte, la transmission d'énergie en courant continu à très haute tension (HVDC) commence à s'imposer comme la technologie privilégiée pour les applications de forte puissance.

Dans les systèmes de transmission HVDC, le convertisseur de puissance joue un rôle majeur. Cet équipement réalise la conversion du courant continu (DC) en courant alternatif (AC), pour pouvoir interfacer le lien HVDC au réseau de puissance existant en AC. Parmi les différents types des technologies des convertisseurs pour les réseaux HVDC, les convertisseurs à source de tension (VSC) supplantent peu à peu les convertisseurs à source de courant (LCC) car ils fournissent des fonctionnalités améliorées comme un meilleur encombrement et une meilleure compatibilité avec un futur réseau maillé HVDC.

En ce qui concerne les topologies VSC, le convertisseur MMC est aujourd'hui la topologie de référence. Il s'agit d'une structure modulaire, composée principalement de piles de sous-modules (SMs). Chaque SM est composé en lui-même d'un condensateur et de modules IGBT utilisés pour l'insertion ou le bypass du condensateur.

Etant donné que le transport d'énergie est une application critique, les systèmes HVDC sont soumis à des normes de fiabilité et de disponibilité très exigeantes et le MMC ne fait pas l'exception. C'est pourquoi ce travail aborde la surveillance de l'état de santé et le pronostic de la durée de vie restante des IGBT présents dans les SMs du convertisseur. Ce travail se focalise sur les IGBT car ils ont été identifiés comme l'un des composants les plus fragiles dans les convertisseurs de puissance.

Une approche par analyse de la physique de la défaillance a été choisie pour mettre au point une méthodologie de pronostic de la vie restante du convertisseur. Cette démarche utilise le profil thermique subi par les semiconducteurs pour calculer la consommation de la durée de vie écoulée dans la période évaluée et en déduire la durée restante. Par ailleurs, cette démarche permet de faire des calculs de la fiabilité des SMs en considérant la consommation de la durée de vie et la fonction de fiabilité des éléments qui le composent. En outre, des calculs des niveaux de redondance à installer, pour atteindre aux besoins de disponibilité, sont réalisés grâce à cette méthodologie.

Un autre sujet important abordé dans cette recherche est le suivi de la dégradation des modules IGBT. Pour étudier cela, un banc de cyclage actif a été développé. La tension  $V_{CE(on)}$  a été choisie comme paramètre de surveillance pour suivre la dégradation du module tout au long des tests de cyclage. Par conséquent, une carte de mesure de cette tension a été développée et cette carte a permis de développer une méthode pour estimer la température de jonction des IGBT. Elle se base sur un filtre de Kalman, dont le réglage est réalisé en utilisant la méthode ALS qui permet d'obtenir le réglage optimal du filtre. Les essais ont aussi permis de tracer l'évolution d'autres paramètres sensibles à la dégradation.

<u>Résumé</u> iv

Resumen

# Resumen

Las redes de transporte de energía eléctrica deben adaptarse a los desafíos que conlleva el incremento de la demanda de energía, la expansión de las fuentes de energías renovables y al alejamiento de los centros de producción de los centros de consumo. Es bajo este contexto, que los sistemas de transporte de electricidad en corriente continua y alta tensión (HVDC) han surgido como una solución prometedora para mejorar la infraestructura de los sistemas de transmisión en corriente alterna y cumplir con los exigentes requisitos de las futuras redes eléctricas.

En los sistemas de transmisión HVDC, el convertidor de potencia juega un rol fundamental. Éste último realiza la conversión de corriente continua (CC) en corriente alterna (CA), para poder interconectar una línea HVDC al sistema de potencia existente. Entre las diferentes tecnologías para redes HVDC, los convertidores a fuente de tensión (VSC) están remplazando progresivamente a los convertidores a fuente de corriente (LCC). En efecto, los convertidores VSC otorgan nuevas funcionalidades que facilitarían la implementación de redes multiterminales en CC.

Dentro de las topologías VSC, el convertidor modular multinivel (MMC) es hoy en día, la topología predilecta para nuevas líneas HVDC. Se trata de una estructura modular compuesta de submódulos (SMs). Cada SM está compuesto de un condensador y de módulos IGBT que son utilizados para la inserción o el bypass del condensador.

Dado que el transporte de energía es una aplicación critica, los sistemas HVDC se rigen por estrictas normas de fiabilidad y disponibilidad. Es por este motivo que este trabajo aborda la supervisión del estado de salud y el pronóstico de la vida restante de los IGBTs presentes en los SMs del convertidor MMC. Esta tesis hace énfasis en los IGBTs, puesto que éstos han sido identificados como uno de los componentes más frágiles dentro de los convertidores de potencia.

Un enfoque basado en el análisis de las causas físicas de la degradación ha sido adoptado para diagnosticar la vida restante de los SMs. Este enfoque utiliza el perfil térmico experimentado por los IGBTs para calcular el consumo de la duración de vida en el periodo evaluado y deducir la vida restante. Además, este método permite calcular la fiabilidad de los SMs tomando en cuenta el perfil de carga y los indicadores de fiabilidad de sus elementos. También, el cálculo de niveles de redundancia es posible gracias a este enfoque.

Otro aspecto fundamental abordado en este trabajo es la supervisión de la degradación de los módulos IGBT. Un banco de envejecimiento basado en variaciones térmicas ha sido desarrollado para este fin. La tensión  $V_{CE(on)}$  ha sido escogida como un parámetro para el monitoreo de la degradación del módulo durante las pruebas de envejecimiento. Consecuentemente, una tarjeta electrónica para medir este parámetro ha sido desarrollada y ha permitido la implementación de un método de estimación de la temperatura del IGBT. Dicha metodología utiliza un filtro de Kalman que es parametrizado gracias al algoritmo ALS, lo cual asegura un funcionamiento optimo del filtro y una estimación precisa de la temperatura del IGBT. Finalmente, las pruebas de envejecimiento han permitido monitorear la evolución de otros parámetros sensibles a la degradación.

Resumen vi

Contents

# Contents

| Abstract                                                          | i                            |

|-------------------------------------------------------------------|------------------------------|

| Résumé                                                            | iii                          |

| Resumen                                                           | v                            |

| Contents                                                          | vii                          |

| List of abbreviations                                             | xi                           |

| General Introduction                                              |                              |

| Background                                                        | xiii<br>xvii<br>xviii<br>xix |

| 1. State of the art on CM and prognosis techniques for IGBT modu  |                              |

| 1.1. Introduction                                                 |                              |

| 1.2. Background on IGBT modules                                   | 3                            |

| 1.2.1. Press-pack modules                                         |                              |

| 1.2.2. Wire-bonded (Flat-Pack) modules                            |                              |

| 1.2.3. Comparison between module packaging technologies           |                              |

| 1.3. Failure mechanisms of power modules                          |                              |

| 1.3.1. Chip-related failure mechanisms                            |                              |

| 1.3.2. Package-related failure mechanisms                         |                              |

| 1.3.3. Summary on failure mechanisms.                             |                              |

| 1.4. Notions related to prognosis and Condition Monitoring        |                              |

| 1.5. Condition Monitoring for IGBT modules                        |                              |

| 1.5.1. Bond wire CM techniques                                    |                              |

| 1.5.2. Solder layer CM techniques                                 |                              |

| 1.6.1. Physics-of-Failure methods                                 |                              |

| 1.6.2. Data-based methods                                         |                              |

| 1.6.3. Fusion methods                                             |                              |

| 1.7. Chapter conclusion                                           |                              |

| 2. MMC modelling for lifetime estimation and reliability analysis | 41                           |

| 2.1. Introduction                                                 | 43                           |

| 2.2. Modelling background                                         |                              |

| 2.2.1. Type 5 model – Reduced order average model                 |                              |

| 2 2 2 Type 4 model – Semi-analytic detailed model                 |                              |

Contents

| 2.2.3. Averaged – Detailed model                                          | 17  |

|---------------------------------------------------------------------------|-----|

| 2.3. Mathematical description                                             |     |

| 2.4. Steady-state analysis                                                |     |

| 2.4.1. Calculation of arm currents and voltages                           |     |

| 2.4.2. Study of capacitor dynamics                                        |     |

| 2.5. Modular multilevel converter control                                 |     |

| 2.5.1. Low level control                                                  |     |

| 2.5.2. High level control.                                                |     |

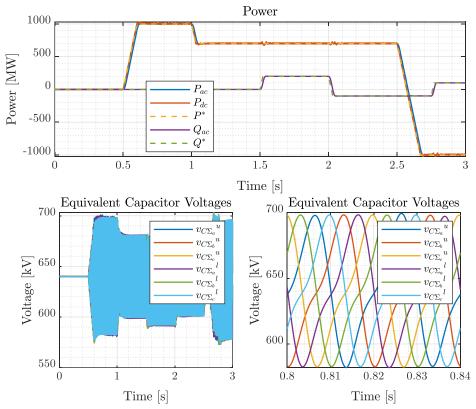

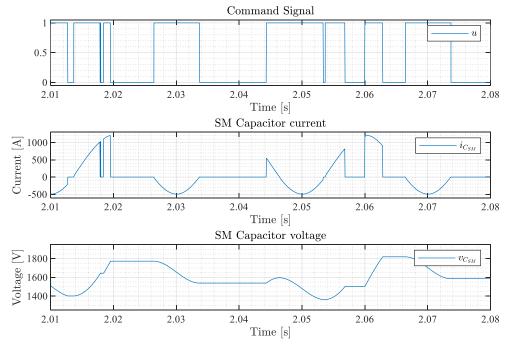

| 2.6. Simulation results of converter operation                            |     |

| 2.7. Chapter conclusion                                                   |     |

| 3. Methodologies for Lifetime Estimation, Reliability Predict             |     |

| Redundancy Computations                                                   | 69  |

| 3.1. Introduction                                                         | 71  |

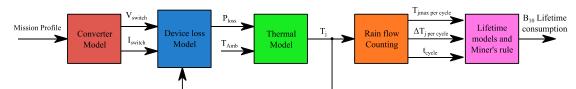

| 3.2. Methodology for lifetime estimation based on mission profile         | 71  |

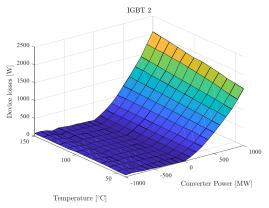

| 3.2.1. Estimation of power losses                                         | 72  |

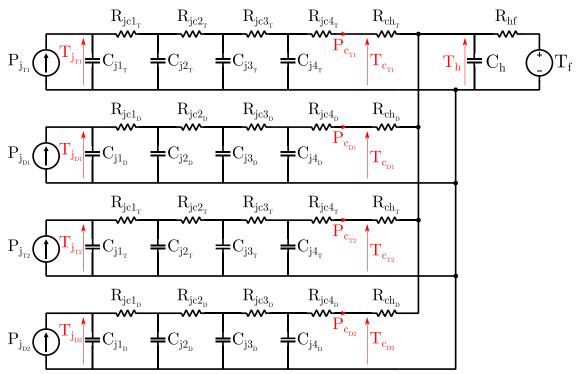

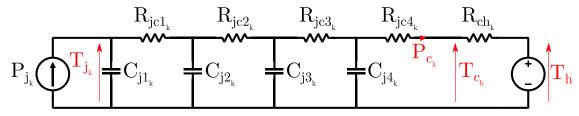

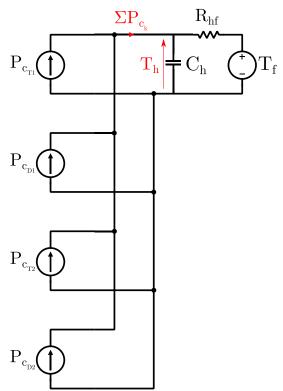

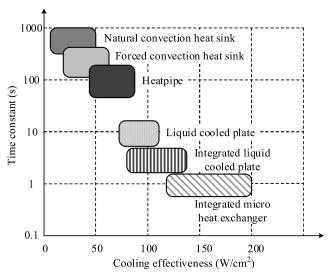

| 3.2.2. Thermal modelling                                                  | 76  |

| 3.2.3. Calculation of lifetime consumption and remaining useful life      | 85  |

| 3.2.4. Case studies                                                       | 89  |

| 3.2.5. Results                                                            | 94  |

| 3.3. Methodology for reliability predictions                              | 99  |

| 3.3.1. Probability analysis                                               | 100 |

| 3.3.2. Reliability based on manufacturer off-the-shelf reliability inputs | 101 |

| 3.3.3. Reliability based on experienced mission profile                   | 103 |

| 3.4. Methodology for redundancy computations                              | 106 |

| 3.4.1. Analytical approach for redundancy computations                    | 107 |

| 3.4.2. Markov Chain approach for redundancy computations                  | 108 |

| 3.4.3. Discussion on the redundancy computation methodology               | 110 |

| 3.5. Chapter conclusion                                                   | 113 |

| 4. Power Cycling Test                                                     | 115 |

| 4.1. Introduction                                                         | 117 |

| 4.2. Motivation for performing power cycling tests                        | 117 |

| 4.3. Review of power cycling testing methods                              | 119 |

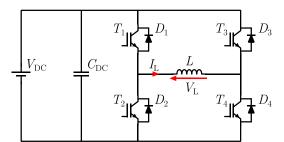

| 4.3.1. DC power cycling                                                   | 120 |

| 4.3.2. AC power cycling                                                   | 122 |

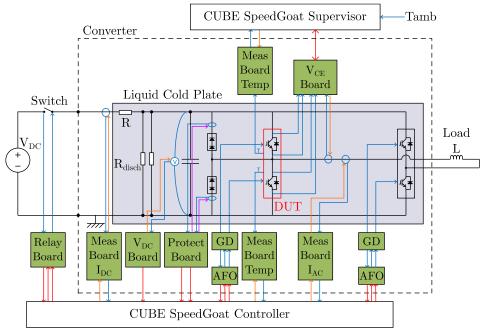

| 4.4. Power cycling test setup                                             | 124 |

| 4.4.1. Configuration of the AC power cycling test setup                   | 124 |

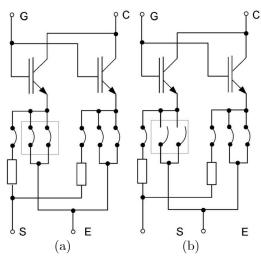

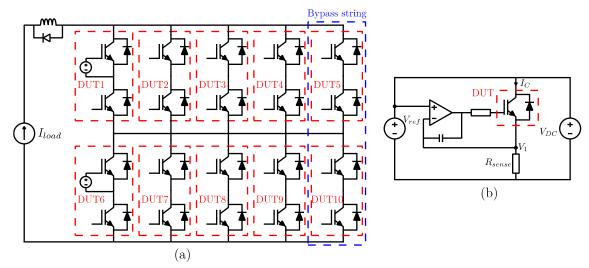

| 4.4.2. Choice of device under test                                        | 128 |

| 4.4.3. Operating principle of the setup                                   | 128 |

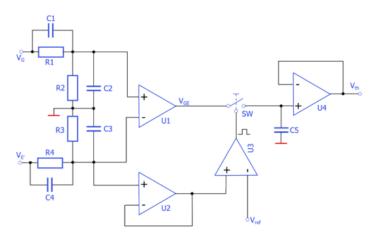

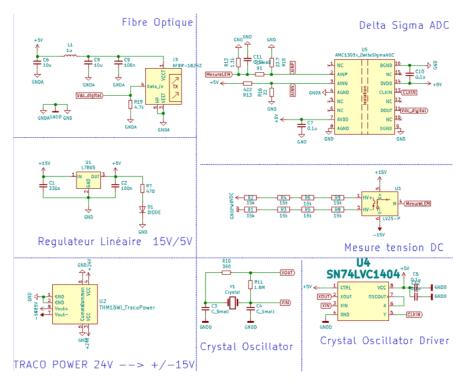

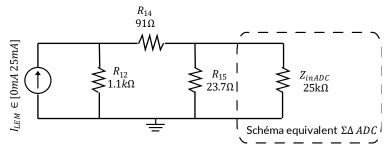

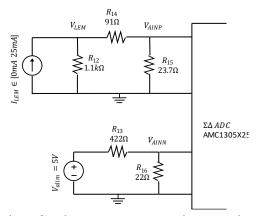

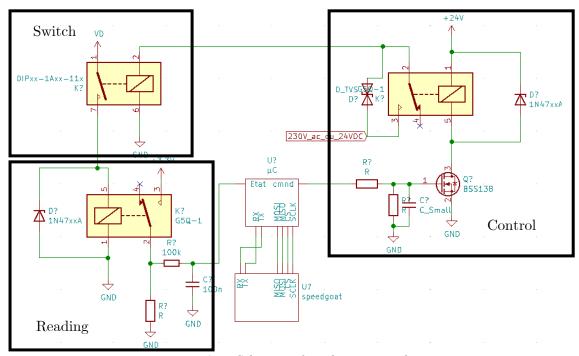

| 4.4.4. Electronic boards                                                  |     |

| 4.5. Junction temperature estimation                                      | 145 |

| 4.5.1. I-V Characterization                                               | 145 |

| 4.5.2. Preliminary $Tj$ estimation from I-V characterization              | 146 |

Contents

| 4.5.3. Kalman filter for final $Tj$ estimation                                 | 148                     |

|--------------------------------------------------------------------------------|-------------------------|

| 4.5.4. Autocovariance Least-Squares method                                     | 156                     |

| 4.5.5. Validation of $Tj$ estimation with fiber optics measurement             | 161                     |

| 4.6. Power cycling experiments                                                 | 164                     |

| 4.6.1. Statistical background for cycling tests                                | 164                     |

| 4.6.2. Calculation of power cycling conditions                                 | 166                     |

| 4.6.3. Protocol for PC tests                                                   | 166                     |

| 4.7. Measurements and test results                                             | 171                     |

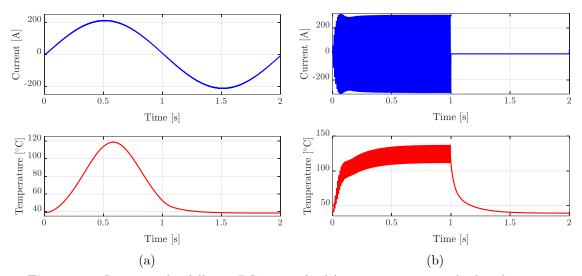

| 4.7.1. Real-time measurements                                                  | 171                     |

| 4.7.2. Junction temperature estimation                                         | 173                     |

| 4.7.3. Degradation assessment                                                  | 175                     |

| 4.7.4. Discussion on the power cycling experiments                             | 180                     |

| 4.8. Chapter conclusion                                                        | 181                     |

| Conclusions and Perspectives                                                   | 185                     |

| Conclusions                                                                    | 185                     |

| Perspectives                                                                   | 187                     |

| References                                                                     | 189                     |

| Appendices                                                                     | 211                     |

| A.1. Derivation of the reduced average model                                   | 211                     |

| A.2. Voltage to current adapting circuit for RTD measurement                   | 213                     |

| A.3. Dimensioning of the $Vdc$ board                                           | 216                     |

| A.4. Additional information on the Relay board                                 | 219                     |

| A.4.1. Structure of the code for communication                                 | 219                     |

| A.5. Construction of matrix $M$ for the ALS method                             | 221                     |

| A.6. Résumé étendu en Français                                                 | 223                     |

| A.6.1. Introduction générale                                                   | 223                     |

| A.6.2. Chapitre 1 : Etat de l'art                                              | 226                     |

| A.6.3. Chapitre 2 : Modélisation d'un convertisseur modulaire multiniveau pour | l'analyse de            |

| 11.0.5. Chapter 2. Modensation d un convertisseur modulaire mutumiveau pour    |                         |

| fiabilitéfiabilité                                                             | 230                     |

| -                                                                              |                         |

| fiabilité                                                                      | fiabilité et des        |

| fiabilité                                                                      | fiabilité et des<br>233 |

Contents x

# List of abbreviations

AC Alternating Current

ACM Autocovariance Matrix

ADC Analog to Digital Converter

ALS Autocovariance Least-Squares Method ANFIS Adaptative Neuro-Fuzzy Inference System

ANN Artificial Neural Network AVM Average Value Models

BCA Balancing Control Algorithm

CDF Cumulative Distribution Function

CHB Cascaded H-Bridge Converter

CIGRE Conseil international des grands réseaux électriques

CM Condition Monitoring

CSC Current-Source Converter

CTE Coefficient of Thermal Expansion

DBC Direct Bonded-Copper Layer

DC Direct Current

DSEP Damage-Sensitive Electrical Parameter

DUT Device Under Test

EMI Electromagnetic Interference

ENTSO-E European Network of Transmission System Operators for Electricity

EOL End-of-Life

EOS Electrical Overstress

FB-SM Full-Bridge Submodule

FC Flying Capacitor Converter

FEA Finite Element Analysis

FIT Failures In Time (number of failures per 10<sup>9</sup> hours) FMMEA Failure Mode, Mechanism and Effect Analysis

FWD Free-Wheeling Diode

GD Gate Driver

GPIO General Purpose Input/Output ports

GPR Gaussian Process Regression

H3TRB High Humidity High Temperature Reverse Bias

HB-SM Half-Bridge Submodule HCI Hot Carrier Injection HS High-Side Switch

HTGS High Temperature Gate Bias

HTRB High Temperature Reverse Bias

HVAC High Voltage Alternating Current

HVDC High Voltage Direct Current

IEC International Electrotechnical Commission

IGBT Insulated-Gate Bipolar Transistor

KBA Knowledge-Based Agent

KF Kalman Filter

LCC Line Commutated Converter

LSLow-Side Switch

MMC Modular Multilevel Converter

MOSFET Metal-Oxide-Semiconductor Field-Effect Transistor

MTDC Multi Terminal DC grids

MTOE Millions of Tons of Oil Equivalent MVDC Medium Voltage Direct Current

NLM Nearest Level Modulation

NPC Neutral-Point Clamped Converter NTC Negative Temperature Coefficient

OHL Overhead Lines OWF Offshore Windfarm

P2P Point-to-Point HVDC link

PCPower Cycling

**PCA** Principal Component Analysis

PCB Printed Circuit Board

PDF Probability Density Function

PF Power Factor

PIProportional-Integral (PI) Controller

PLLPhase-Locked Loop PoF Physics-of-Failure

PTC Positive Temperature Coefficient

**PWM** Pulse Width Modulation

RMS Root Mean Square

RTD Resistance Temperature Detector

RUL Remaining Useful Life

SEM Scanning Electron Microscope

SMSubmodule

SMU Source Meter Unit SOA Safe Operating Area

SOH State-of-Health

**SSBP** Simple State-Based Prognostics

**TDDB** Time Dependent Dielectric Breakdown

Time-Delay Neural Network **TDNN** TIM Thermal Interface Material TRB Temperature Reverse Bias

**TSEP** Temperature Sensitive Electrical Parameters

TSO Transmission System Operator

**UART** Universal Asynchronous Receiver/Transmitter

VSC Voltage-Source Converter

# General Introduction

## Background

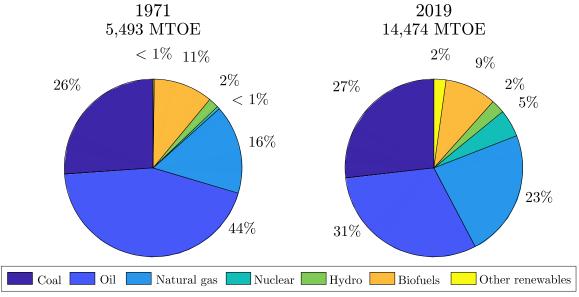

The energy demands around the world are growing, in fact they have been growing at an accelerated pace since the industrial revolution in the early 1800s. Moreover, modern societies have evolved under a strongly energy-dependent model where energy consumption is ever-growing [1]. Given this high energy demand, fossil fuels have played a major role since they are easily available, and they have low production costs. An evolution of the primary energy sources can be seen in Figure i.1.

Figure i.1. Global primary energy sources in 1973 and 2019 in Millions of tons of oil equivalent (MTOE) [2]

Even though fossil fuels have allowed for a rapid development of society, they pose nowadays a major problematic related to CO<sub>2</sub> emissions and its contribution to the greenhouse effect. It is in this climatic context, that newer energy sources have seen a major development in the past few decades. First, nuclear energy was seen as a viable solution regarding its climatic impact, however, nuclear fuel waste management proved to be a blocking point, as well as its highly demanding safety requirements. Subsequently, renewable energies have soared as the most viable technologies for emission-free energy production. Therefore, new climatic policies have placed renewable energies at the heart of coming energy projects and initiatives.

Not only has energy production seen the impact of the high energy demands. Power transmission must also deal with this constraint. The growing energy demands on power transmission systems are pushing towards the rapid development of High Voltage Direct Current (HVDC) technologies. As an example of this trend towards HVDC, the European commission, in partnership with the European Network of Transmission System Operators for Electricity (ENTSO-E), has set its first objective of increasing the number of

interconnections by 15% until 2030, with, in particular, the integration of tens of thousands of kilometers of HVDC lines [3], [4].

HVDC has been recognized as a major contender for performing long-distance bulk-power transmission, asynchronous AC systems interconnections, interconnection of different regions requiring submarine and/or underground cables, and transmission of offshore wind power to shore [5], [6].

Some of the advantages of HVDC are the lower conduction losses on the DC lines compared to its AC counterparts as there is no skin effect, nor proximity effect on DC. In addition, DC has the advantage of the absence of losses due to reactive current [7].

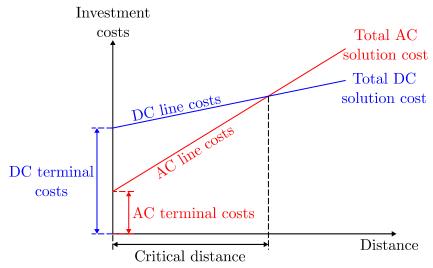

Despite all the advantages of DC over AC, a major drawback for HVDC systems is the cost of the power conversion stations needed to interface DC links to the existing AC infrastructure. The tradeoff between the cost of AC/DC converter stations and the attractive characteristics of DC transmission are suitable beyond a critical distance, otherwise known as break-even distance [6]–[9]. An illustration of the costs of high voltage AC and DC transmission systems as a function of the distance of the interconnections can be seen in Figure i.2. Depending on the type of transmission line the break-even distance can be different. In the case of overhead lines (OHL) this distance is estimated at around 500-800 km, while cable transmission systems become economically more attractive at distances longer than 60-80 km [8], [9].

Figure i.2. HVAC and HVDC transmission comparison

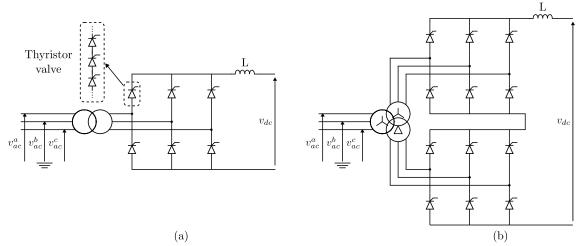

In this research work, the subject of the study will be the AC/DC converter station at the ends of the DC power transmission line. There are several examples of efforts for developing DC conversion stages in the first part of the 1900s [10], [11]. However, the main technological milestone that has allowed the development of AC/DC conversion is the emergence of Silicon-based power semiconductors [7]. The first example of AC/DC power converters for high voltage is the Line Commutated Converter (LCC). It is categorized as a current-source converter (CSC), as it behaves as a current source on the AC side. This converter topology reposes on the use of thyristors, as illustrated in Figure i.3.

Figure i.3. (a) Simplified schematic of a Line Commutated Converter, (b) Twelve-pulse converter

The thyristors used in LCC have ratings of 8.5kV - 5kA [7]. Therefore, it is necessary to connect the semiconductors in series, in order to withstand the high voltages corresponding to HVDC applications. The series association of semiconductor devices is known as a valve.

Thyristors can be switched on; however, they need the current to pass through zero in order to switch off. This characteristic impacts the performance of the converter as the converter relies on the AC side network for the turn-off of the semiconductors and cannot be used as the only power source. This also implies that the active power P and the reactive power Q cannot be controlled independently in this topology. Hence, the converter requires the use of large filters for reactive energy compensation. Filters are not only used for this purpose, but also for reducing the current swing on the AC side and suppress the important harmonic content. In order to address the latter issue, the twelve-pulse topology seen in Figure i.3 can be used. Moreover, with this technology the DC current cannot change direction, as it flows through a large inductance as depicted in Figure i.3. Thus, power reversals are achieved by changing the polarity of the DC voltage.

In order to address the issues of current-source converters, the voltage-source converter (VSC) technology has gained in relevance since the late 1990s [12]. VSC technologies rely on the use of semiconductors such as the Insulated-Gate Bipolar Transistor (IGBT), that can be controlled at both turn-on and turn-off. This allows for an additional degree of freedom, which enables the independent control of the active and reactive power. This characteristic also allows converters to no longer rely on the AC grid for its operation and gives them "black-start" capabilities [9]. Since the turn-off of the devices can be controlled in VSCs, they can switch much faster than CSCs and improve the harmonic performance, which can result in the elimination of filters [13].

In contrast to CSC, VSC allows for power reversals by maintaining the voltage polarity and changing the direction of the current. This makes VSCs much easier to connect into a Multi-terminal HVDC system of DC-Grid [14].

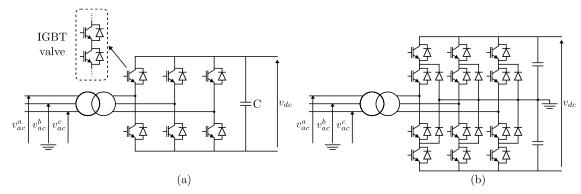

There are several VSC topologies. The first VSC topology introduced for HVDC applications is the 2-level converter, which can be seen in Figure i.4 (a). Current IGBT technology for HVDC has ratings of 3.3kV to 6.5kV and 1kA to 2 kA [15]. It is therefore necessary to assemble these components in series to withstand the voltage levels of HVDC applications. Similar to thyristors in LCC, IGBTs are assembled in "IGBT valves" that make up a single switching element. A major drawback of this structure is that components inside an IGBT valve need to be perfectly synchronized during the switching actions. Otherwise, some of the individual IGBTs will experience overvoltages that can lead to the destruction of the power module and can lead to catastrophic scenarios. In order to attain a better voltage distribution among the components inside a valve, snubber circuits are employed. These elements lead to higher power losses during normal operation and will impact the volume and the weight of the converter station, which can be of particular interest for some applications.

Figure i.4. VSC topologies: (a) 2-level converter, (b) 3-level converter, NPC topology

In order to deal with the issues concerning the series assembly of components and the nonnegligible switching losses for reducing the AC harmonic content, different VSC topologies have emerged. Among some of them the Floating Capacitor Converter (FC), or the Cascaded H-Bridges Converter (CHB) can be mentioned [16]–[18]. However, one of the most widely used in HVDC applications is the Neutral-Point Clamped Converter (NPC) seen in Figure i.4 (b). It is a 3-level converter, which can generate output levels of  $+v_{dc}/2$ , 0 and  $-v_{dc}/2$ . The IGBT valves in this topology withstand only half the voltage when compared with the 2-level topology. The zero-voltage level output can be obtained with the use of the clamping diodes present in this topology.

This structure allows a decrease in losses and reduced harmonic content to the detriment of higher system complexity and control strategy. There are other issues concerning the NPC. For instance, the number of diodes present in this topology is quite important. Also, the voltages across the capacitors need to be balanced, hence they may require the use of additional circuits. Given these characteristics, this topology in practical HVDC applications is limited to three levels, contrary to the theoretical multilevel capabilities inherent to the NPC building block.

The series assembly of elements for obtaining switching "valves" and the higher switching frequencies are the principal downsides of the VSC topologies mentioned previously. A multilevel architecture can help overcome the limitations of the classical VSC circuits. Thus, the Modular Multilevel Converter (MMC) topology arose as a viable alternative for HVDC applications. This topology will thus be the subject of this thesis and will be discussed in more detail in the following paragraph.

#### Modular Multilevel Converter

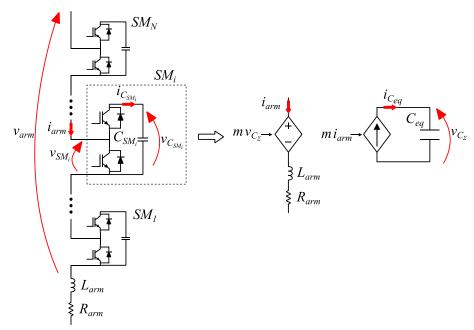

A major technological advance for VSC technologies is the Modular Multilevel Converter (MMC) seen on Figure i.5. It was first introduced in 2003 by German professor R. Marquardt [19], [20]. This topology is considered the most promising for HVDC transmission applications, as it has the main advantages of other VSC structures but without the drawbacks. Additionally, the MMC is scalable, its modular structure allows an improved output quality and the topology is more efficient as it has reduced switching losses [21].

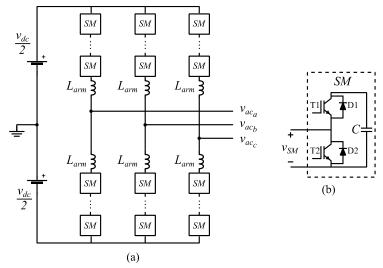

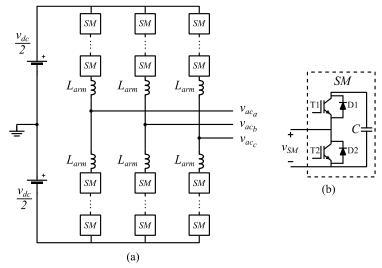

Figure i.5. (a) Three-phase Modular Multilevel Converter, (b) Half-bridge submodule

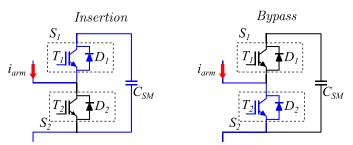

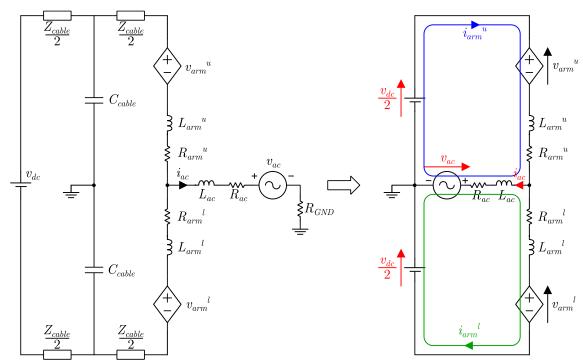

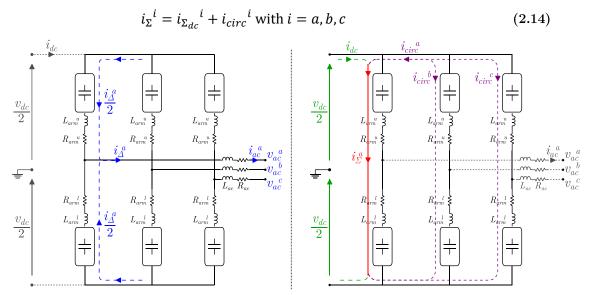

The MMC topology shown in Figure i.5 (a) has three phases, otherwise known as a converter leg. Each leg is composed of an upper and lower arm, which are composed themselves of an arm inductor  $L_{arm}$  and a stack of submodules. The submodules are connected in series for generating the output voltage levels of the HVDC system. Multiple submodule configurations are proposed in the literature [22], but the two most popular are the half-bridge (HB-SM) and full-bridge (FB-SM) configurations. In practical applications today, the HB-SM is the most used due to cost considerations.

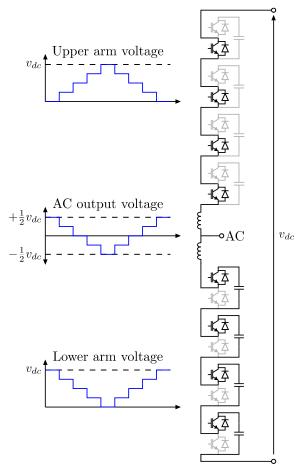

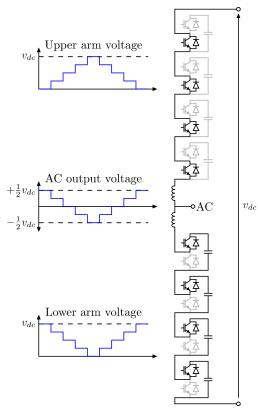

A HB-SM topology can be seen in Figure i.5 (b). It consists of a storage capacitor and two IGBT modules. Each IGBT module has an IGBT device and its antiparallel diode, in order to perform three-quadrant operation. The IGBT modules allow the insertion or the bypass of the storage capacitor. The output voltage of an MMC arm can be controlled by inserting/bypassing submodules in order to obtain the desired waveforms. An illustration of the output voltage of an arm and of a converter leg can be seen in Figure i.6.

Figure i.6. Working principle of a single phase of an MMC

## Problem statement and thesis scope

According to the ENTSO-E, TSOs and other end-users of HVDC should consider that improved reliability (e.g. decreasing 1-2 trips per year on average) and improved availability (e.g. decreasing 1-2 outages days per year on average) can bring significant cost savings to TSOs and/or society [23].

The scope of this work is limited to the power converter, in this case the Modular Multilevel Converter. It was seen that the MMC topology consists mainly of the submodules HB-SMs, which are basically composed of IGBT modules and storage capacitors. According to a survey on the reliability of power converters [24], both these elements are considered critical and among the weakest links that define the reliability of the circuits in which they are present.

This work will focus more particularly on the IGBT devices, as studying both elements deem to be a rather long and difficult task. Moreover, IGBT devices according to [24], are the weakest components in the power conversion chain and several works have been reported for addressing the state-of-health (SOH) of the storage capacitor in the MMC application [25]–[27]. Therefore, this work intends to understand the main failure modes and mechanisms of the IGBT device in an HVDC-MMC application and to select an

appropriate strategy for assessing its state-of-health and determine its remaining useful life (RUL) while in online operation.

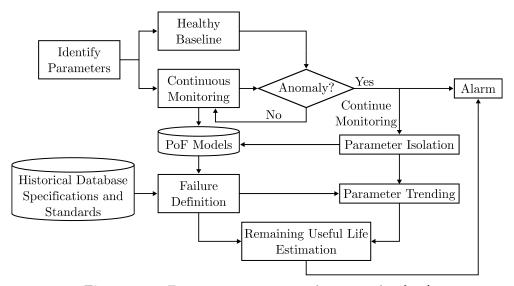

There are several strategies for enhancing the reliability and availability of power converters. Among them, Condition Monitoring (CM) has gained in relevance in the last few decades [28] and will be the chosen strategy for the rest of this thesis. The CM approach consists of tracking the evolution of a particular parameter indicative of the state of degradation of an element, in order to assess its degradation. From this method, additional efforts can be made in order to prognose the expected end-of-life (EOL) of the studied element and determine its RUL.

A particular point of interest in this study is the thermal loading of the IGBT components. This is a crucial subject for deploying a prognosis methodology as it will be seen in the body of this work.

#### Thesis outline

The organization of this thesis is as follows:

- Chapter 1 deals with the IGBT modules used in an HVDC-MMC application, subsequently it covers the main failure modes and mechanisms they can experience. Finally, a comprehensive review on the techniques for the condition monitoring and the prognosis of the remaining useful life of these devices is presented.

- Chapter 2 describes the modelling of a MMC. This model will be employed for obtaining the electrical waveforms and the loading conditions of the IGBT devices to be studied in this application.

- Chapter 3 presents a methodology for the estimation of the lifetime of the semiconductors present in a HB-SM. This methodology considers the mission profile experienced by the semiconductors and translates it to a thermal profile. The computed thermal profile is used for the calculation of the lifetime consumption experienced in the evaluated period. Additionally, this chapter presents a methodology for evaluating the reliability of a MMC arm and consequently computing the redundancy requirements for attaining a target converter availability.

- Chapter 4 presents a power cycling testbench developed for studying the degradation process of the IGBT devices. The online surveillance of the collector-emitter voltage is also addressed in this chapter. Additionally, the estimation of the junction temperature of the IGBTs is covered. Finally, the results of the power cycling tests are presented in this chapter.

#### Main contributions

The main contributions of this thesis to the scientific community are:

A thorough overview of the typical failure modes and mechanisms of IGBT modules suited for a HVDC-MMC application.

- A review of the state-of-the-art on the prognosis and condition monitoring of IGBT modules.

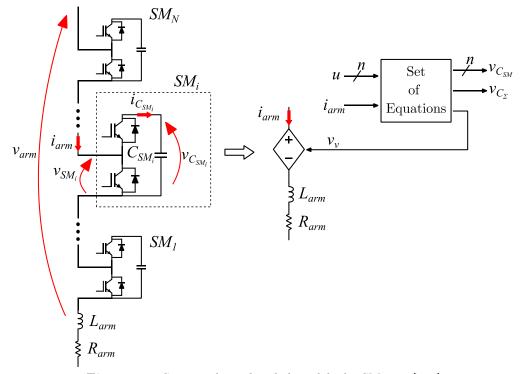

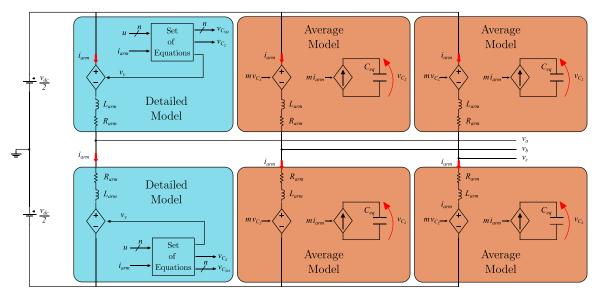

- A hybrid averaged-detailed model of the MMC for obtaining the electrical waveforms of the elements of a HB-SM.

- A methodology for the estimation of the lifetime consumption of semiconductor devices considering the mission profile of the converter. This topic was the subject of a conference paper [29].

- A novel model-based interpolation/extrapolation method, for the calculation of the lifetime consumption based on thermal profiles.

- Reliability predictions of the semiconductors inside a HB-SM. These predictions

consider the mission profile experienced by the semiconductors and the

manufacturer lifetime models.

- A methodology for computing the number of required SMs based on the reliability of its composing elements. This methodology considers the target availability of the HVDC application as well as the mission profile of the semiconductors. Correspondingly, this work was the subject of a conference paper [30].

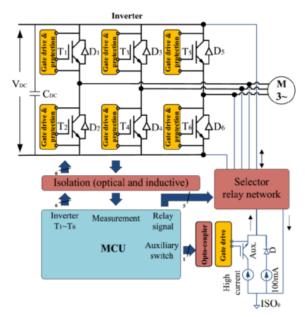

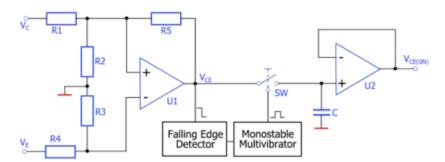

- An AC Power Cycling testbench was developed in this thesis, along with all the instrumentation required for performing a condition monitoring scheme for IGBT devices.

- An upgraded circuit for the online measurement of  $V_{CE(on)}$  was proposed. Moreover, this circuit is not only suitable for IGBT devices, but also for faster semiconductor devices.

- A methodology for the estimation of the junction temperature of IGBT devices based on the online measurement of  $V_{CE(on)}$  and a Kalman filter.

## List of publications

- D. Velazco, G. Clerc, E. Boutleux, F. Wallart, and L. Chédot, "IGBT Lifetime Estimation in a Modular Multilevel Converter for bidirectional point-to-point HVDC application," in 2020 22nd European Conference on Power Electronics and Applications (EPE'20 ECCE Europe), Sep. 2020, pp. 1–10. doi: 10.23919/EPE20ECCEEurope43536.2020.9215880.

- D. Velazco, G. Clerc, E. Boutleux, and F. Wallart, "Comparison of Redundancy Requirements for Modular Multilevel Converter Considering Manufacturer Reliability Inputs and Mission Profile," in 2022 24th European Conference on Power Electronics and Applications (EPE'22 ECCE Europe), Sep. 2022, pp. 1–10

# 1. State of the art on CM and prognosis techniques for IGBT modules

| 1.1. Introduction                                          | 3  |

|------------------------------------------------------------|----|

| 1.2. Background on IGBT modules                            | 3  |

| 1.2.1. Press-pack modules                                  |    |

| 1.2.2. Wire-bonded (Flat-Pack) modules                     |    |

| 1.3. Failure mechanisms of power modules                   |    |

| 1.3.1. Chip-related failure mechanisms                     | 10 |

| 1.3.1.1. Overstress failure mechanisms                     | 10 |

| 1.3.1.2. Wear-out failure mechanisms                       | 10 |

| 1.3.2. Package-related failure mechanisms                  | 11 |

| 1.3.2.1. Overstress failure mechanisms                     | 11 |

| 1.3.2.2. Wear-out failure mechanisms                       | 11 |

| 1.3.2.2.1. Bond wire degradation                           | 12 |

| 1.3.2.2.2. Solder layer degradation                        | 13 |

| 1.3.2.2.3. Metallization layer degradation                 | 14 |

| 1.3.3. Summary on failure mechanisms                       | 14 |

| 1.4. Notions related to prognosis and Condition Monitoring | 16 |

| 1.5. Condition Monitoring for IGBT modules                 | 17 |

| 1.5.1. Bond wire CM techniques                             | 17 |

| 1.5.2. Solder layer CM techniques                          |    |

| 1.6. Prognosis of IGBT modules                             |    |

| 1.6.1. Physics-of-Failure methods                          | 24 |

| 1.6.1.1. Lifetime models                                   |    |

| 1.6.1.1.1. Analytical lifetime models                      |    |

| 1.6.1.1.2. Physical lifetime models                        |    |

| 1.6.1.1.2.1. Solder joint models                           |    |

| Ÿ                                                          |    |

| 1.6.1.1.2.2. Bond wire models                              |    |

| 1.6.1.2. Cycle counting methods                            |    |

| 1.6.1.2.1. Rainflow Counting Algorithm                     |    |

| 1.6.1.3. Cumulative Damage models                          |    |

| 1.6.1.4. Examples of PoF methods                           |    |

| 1.6.2. Data-based methods                                  | 99 |

| Chapter 1 State of the art on CM and prognosis techniques for | $\overline{\text{IGBT modules}}$ |

|---------------------------------------------------------------|----------------------------------|

|                                                               | 2                                |

| 1.6.2.1. Examples of Data-based methods                       | 33                               |

| 1.6.3. Fusion methods                                         | 37                               |

| 1.6.3.1. Examples of Fusion methods                           | 38                               |

| 1.7. Chapter conclusion                                       | 39                               |

#### 1.1. Introduction

From the general introduction it was seen that the IGBT is one of the main elements of the Modular Multilevel Converter. Additionally, in the survey reported in [24], it was mentioned that the most fragile component in power converters is the semiconductor. Hence, this thesis will focus on the reliability of the IGBT in the context of the MMC application. This work will intend to set a basis for a prognosis of the lifetime of these devices, as well as performing other relevant reliability-related computations.

This chapter starts with a background description on the IGBT module. More detail on the different types of modules employed in VSC-HVDC applications will be discussed.

Additionally, the failure mechanisms of the IGBT devices will be presented. The main stressors, failure modes and the parameters that can help the monitoring of the different failure types will be introduced.

Subsequently, a thorough state of the art on the approaches for the prognosis of the state of health of these elements will be made. The prognosis approaches will be discussed and the main advantages and disadvantages of each of them will be mentioned.

In the last section of this chapter some of the more relevant works on the Condition Monitoring of the IGBT devices will be presented. A critical summary on the applied methods will be made at the end of this paragraph.

## 1.2. Background on IGBT modules

Insulated Gate Bipolar Transistors (IGBTs) are a mature technology of semiconductors that has been under continuous improvement [31] since its introduction in the early 1980s [32], [33]. This type of semiconductor has a wide variety of applications such as wind energy generation, hybrid vehicles, high speed rails, energy transmission and distribution.

This family of semiconductor can address broad voltage ranges from 300 V to 6.5 kV and current handling capabilities larger than power MOSFETs [34]–[36]. These characteristics make IGBTs a suitable technology for HVDC applications such as the MMC [19], [20]. In HVDC-MMC it is reported that 84% of converter failures are due to valve device failures [37]. As the IGBT module is one of the main elements of the valves, it is important to perform reliability evaluations of this type of device.

In the case of HVDC applications, there is an interest in using the highest voltagerated devices in order to decrease the number of stages required for achieving AC-DC conversion at high voltages. Semiconductor manufacturers have developed specific IGBT packaging technologies addressed to this type of usage. The relevant packaging technologies for high-power transmission are press-pack and wire-bonded (flat-pack) modules, which will be discussed later in this chapter.

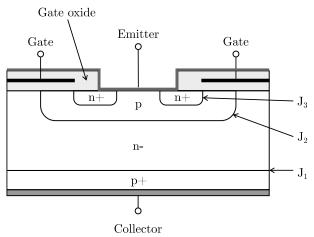

Regardless of the packaging technology used by the modules, the semiconductors inside them are composed by elementary semiconductor cells, which are arranged in such a way that they constitute a semiconductor chip [38]. A cell corresponding to a typical IGBT design can be seen in Figure 1.1.

Figure 1.1. Layered schematic of an IGBT cell [39]

In Figure 1.1, the three electrical terminals of the cell (collector, emitter, gate) and the different junctions inside the device can be seen. Depending on the voltage applied between the gate and the emitter the pn junctions  $J_1$ ,  $J_2$  and  $J_3$  will either be conducting or in a blocked state, which will eventually turn the IGBT on (positive gate-emitter voltage) or off (0V or negative gate-emitter voltage). The gate connections are encapsulated in electrically insulated gate oxide.

The IGBT structure is placed on a silicon chip, but in order to be able to connect the chip to the circuit it is necessary to use an external packaging. Thus, the power component is composed of one or more semiconductor chips in a package. The package and its connection technology are just as important as the characteristics of the semiconductor regarding the reliability of the whole component [40].

A power module has an internal circuit topology, composed of several power semiconductor components and packaging interconnections [41]. In order to increase the power rating of the module, it is necessary to provide a similar loss repartition on each of its internal components. In IGBT power modules, it is a common practice to install IGBT chips as well as diode chips, for free-wheeling purposes and for allowing three quadrant operation.

High-power IGBTs generally have low on-state voltages, which reduce the conduction losses. The total losses experienced by high-power devices can reach several kilowatts. Hence, the package must be conceived in such a manner that the heat generated by the losses can be dissipated away from the chips, for ensuring that the thermal limits of the silicon chips are not met. The packaging must therefore have a high reliability and a high durability under alternating load conditions [42]. Moreover, the package must provide high electrical conductivity for avoiding undesirable electrical properties like parasitic resistance, parasitic capacitance and parasitic inductance [42].

The main packaging technologies for high-power applications such as the HVDC-MMC will be described in the following lines.

#### 1.2.1. Press-pack modules

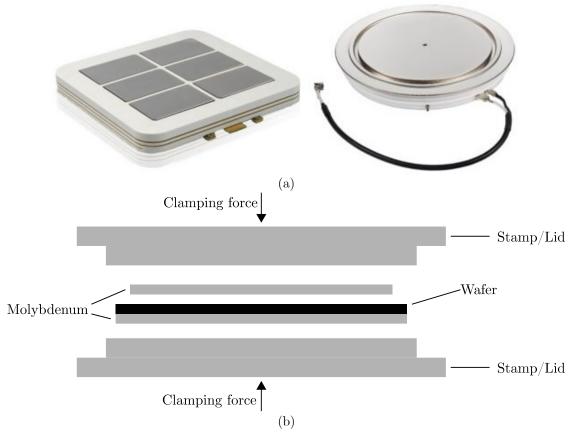

Press-pack technology has proved to be a robust and reliable packaging method for devices like thyristors and diodes in high-power applications [43]. It is a solderless packaging structure, which achieves thermal and electrical contacts by pressuring components from one device to another. Recently, this technology has been adapted for high-power rated IGBT devices. In Figure 1.2 some examples of press-pack modules can be seen as well as the internal structure of a monolithic press-pack device.

Figure 1.2. IGBT press-pack modules (a) Example modules [44], [45], (b) Internal structure [43]

From Figure 1.2 (b) it can be seen that, this packaging technology has a molybdenum plate and a metal lid on either side of the Si wafer. These elements provide the electrical and thermal contact between stacks of similar devices. Additionally, the packages are hermetically sealed. Molybdenum is used as it has a similar CTE to that of silicone, also its hardness properties make this metal a desired choice for its placement between the metal lids and the chips.

## 1.2.2. Wire-bonded (Flat-Pack) modules

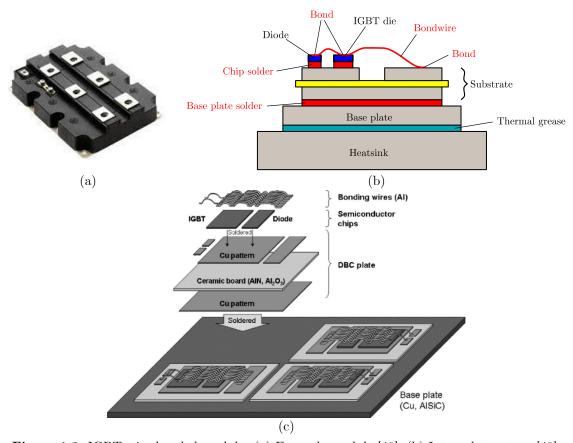

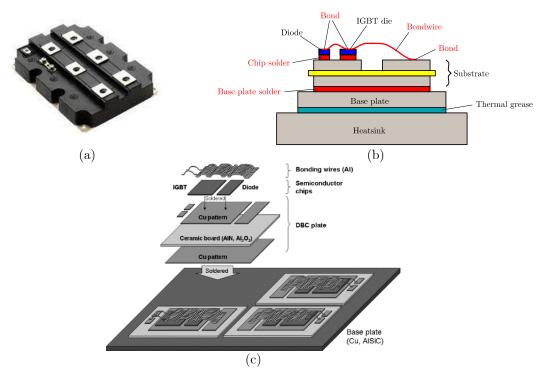

The most widely used packaging technology corresponds to the wire-bonded modules. A high-power wire-bonded module, as well as its internal structure can be seen in Figure 1.3 [40], [42], [46].

Figure 1.3. IGBT wire-bonded modules (a) Example module [40], (b) Internal structure [40], [42], [46], (c) Exploded view of IGBT module structure [47]

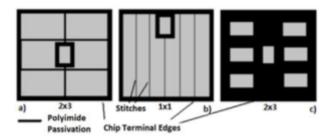

In this type of packaging technology bonding pads are used for connecting the different gate and emitter electrical terminals to the semiconductor dies. Metallization layers are employed for performing electrical connections to the bonding pads. The metallization layers on the chips are made from aluminum alloys for aluminum wire-bonding the die with the power terminals of the device. In most emitter metallization designs, the bonding pads are disposed in a matrix array for preventing the formation of hotspots as seen on Figure 1.4 [48].

Figure 1.4. Common emitter metallization layouts [48]

The collector and its metallization layers are located on the other side of the chips. The collector metallization has 3 roles: First, it works as an electrical connection between the collector and the package. Second, it acts as a thermal interface between the chip and the package [40]. Third, it functions as an adhesion layer between the die and the solder layer

used for attaching the die to the package. In some cases, extra metallization layers are added to the backside metallization to protect the semiconductor from contamination [40].

The wire-bonded modules have a direct bonded copper layer (DBC) as shown in Figure 1.3 (b) and Figure 1.3 (c). The metallization layers on top of the IGBT/free-wheeling diodes (FWD) dies are connected to the top copper layer of the DBC through aluminum bond wires. This top copper layer is used as a power track to connect devices to each other and to module terminals [49].

The metallization layers on the bottom side of the chips are soldered to the top copper layer of DBC. These solder layers are also known as die attaches or chip attaches and can also be seen in red below the semiconductor chips on Figure 1.3 (b). They also serve three functions: First, they conduct current from the dies to the top layer of the DBC. Second, they transfer heat from chips to DBC. Third, they fix the dies to the DBC [49].

The DBC consists of two copper layers sandwiching a ceramic layer that provides electrical isolation between the chips and the baseplate. The DBC is generally soldered to a copper baseplate. The solder layer between the DBC and the baseplate is called DBC attach, and it performs two functions: First, it transfers heat from the DBC to the baseplate that is mounted on a heatsink. Second, it fixes the DBC to the baseplate that is mounted on the heatsink [40], [46], [48], [50].

# 1.2.3. Comparison between module packaging technologies

Both packaging technologies, are currently being used in HVDC applications. In Table 1.1 [51] a comparison between both technologies can be seen. From Table 1.1, it can be seen that press-pack technology is more reliable from a power/thermal cycling perspective [52]. Thus, this technology is being pushed for high-power applications. However, wire-bonded technology is still more widely used than press-packed technology in most applications and several MMC manufacturers still use wire-bonded devices for this sort of purpose. Thus, for the rest of this study, the focus will be made on wire-bonded devices as this is the weakest technology for high-power IGBT modules.

# 1.3. Failure mechanisms of power modules

As mentioned previously, the packaging technology for this research work corresponds to wire-bonded modules. This type of technology is more susceptible to failures than the more recent press-pack technology. But the former is still being widely employed and there are still many reliability-related aspects to address for wire-bonded technologies.

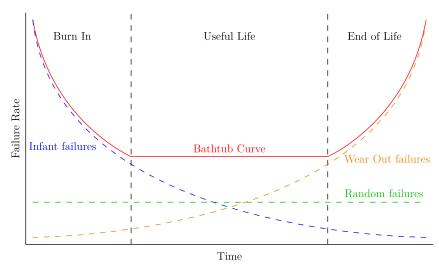

Failures in wire-bonded modules can be categorized according to different criteria. In [53] the different failure mechanisms were categorized by the nature of the fault. Hence, failure mechanisms can be classified as intrinsic and extrinsic [54], [55]. Intrinsic failure mechanisms are due to natural degradation of materials and show wear-out behavior. Extrinsic failure mechanisms are due to unintended defects of product deviations. They are random in nature and show early-life failures and random failures [41].

|                                               | XX7· 1 1 1 1 1                                                                                                                                                                 | D 1 11                                                                                                                                                                                        |

|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Feature                                       | Wire-bonded modules                                                                                                                                                            | Press-pack modules                                                                                                                                                                            |

| Thermal and power cycling reliability         | Mismatch in CTE can lead to fatigue failure                                                                                                                                    | The possibility of fatigue failure is reduced since wire bond and solder interconnect are substituted with bondless pressure contact [52]                                                     |

| Single die failure<br>susceptibility          | The state (open- or short-circuit) after a single die failure is not defined. It can lead to catastrophic failure of the whole module                                          | With a redundant design, the module can continuously operate with a single die failure. A failed die can be replaced during planned system services                                           |

| Explosion safety                              | An explosion was observed when short-circuit conditions were met [56], [57]                                                                                                    | The plasma formed by a short-<br>circuit can be confined inside the<br>module through proper<br>designing                                                                                     |

| Cooling system                                | Simple: a heatsink with cooling fans or liquid cold plates can be used                                                                                                         | Complicated: deionized water is used                                                                                                                                                          |

| Heat dissipation                              | Large temperature differences<br>between individual chips can<br>occur due to inherent variability<br>in thermal resistance of their<br>solder interconnects and<br>substrates | Uneven heat dissipation is reduced by sharing common heatsink blocks: the temperature difference between the hottest and coldest dies were 6°C during the heating phase of a power cycle [58] |

| Current distribution                          | Current flow in individual dies<br>can be uneven due to their<br>temperature differences                                                                                       | Current flow in individual dies is<br>"quite homogeneous" between<br>individual dies [58]                                                                                                     |

| Die mounting                                  | Conventional (inexpensive)                                                                                                                                                     | Unique (expensive)                                                                                                                                                                            |

| Electrical insulation                         | A ceramic layer itself in the DBC substrate provides the internal insulation                                                                                                   | A die carrier subassembly<br>requires housing for the<br>insulation                                                                                                                           |

| Transient voltage at high switching frequency | Transient voltage of individual dies varies unless their electrical circuits are perfectly identical                                                                           | Differences in transient voltage<br>of individual dies are reduced<br>since a common inductive path<br>is shared                                                                              |

${\bf Table~1.1~Comparison~between~press-pack~and~wire-bond~packaging~technologies~[59]-[62] }$

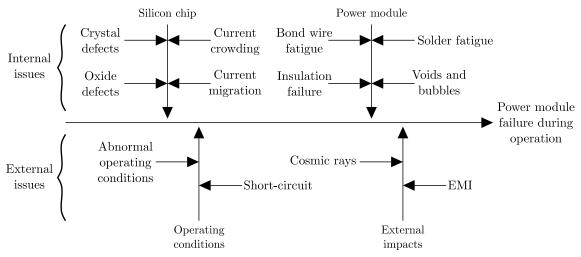

Also, failure mechanisms in IGBT modules can be classified by the location at which the failure is originated [49], [63]. According to this criterion, they can be categorized in chip-related failures and package-related failures. A comprehensive diagram depicting the origin of the failure mechanisms in IGBT modules can be seen in Figure 1.5 [41], [63]. Additionally, Table 1.2 [49] shows more details on the different failure modes and gives an insight on the effect of the failures on the system.

Figure 1.5. Potential failure types in power modules [41], [63]

| Mode         | Type                       | Failure                                               | Effect                                                          |  |

|--------------|----------------------------|-------------------------------------------------------|-----------------------------------------------------------------|--|

|              | Overstress                 | Gate overvoltage (voltage breakdown)                  | Open-circuit faults                                             |  |

|              | [40], [42],<br>[55], [64], | Overvoltage (voltage<br>breakdown)                    | -Short-circuit faults (most of the cases)                       |  |

| Chip-related | [65]                       | Overcurrent Cosmic rays burn out                      | ,                                                               |  |

|              | Wear-out [40], [66]-       | Time dependent dielectric breakdown (TDDB)            | -Mal-operation of gate<br>drivers & switches                    |  |

|              | [71]                       | Hot Carrier Injection (HCI) Electrochemical migration | -Loss of chip's voltage<br>blocking capability                  |  |

|              |                            | Mechanical shock and stresses Thermal shock           | -Open or short-circuit faults -Accelerate wear-out              |  |

| Package-     | Overstress [40], [72]      | Thermal runaway & flashovers                          | -Melting and burnouts<br>(more common in harsh<br>environments) |  |

| related      | Wear-out [40], [67]– [72]  | Thermomechanical fatigue                              | -Thermal losses (most of                                        |  |

| Toldiood     |                            | Thermomechanical creep                                | the cases)                                                      |  |

|              |                            | Electro & electro-chemical migration                  | -Stray (leakage) current issues                                 |  |

|              |                            | Insulation degradation                                | -Loss of module's voltage<br>blocking capability                |  |

${\bf Table~1.2~Failure~mode~classification~in~power~modules~[49]}$

A brief description of the main failure mechanisms of IGBT modules will be made in the following paragraph. The failure mechanisms will be categorized by the location at which they take place.

## 1.3.1. Chip-related failure mechanisms

#### 1.3.1.1. Overstress failure mechanisms

The main overstress failure mechanisms are due to electrical overstress (EOS), and burnout [42], [72].

In the case of electrical overstress, overvoltages can lead to secondary breakdown under high-voltage and excessive heating [65], [73]–[76]. In order to prevent this issue, it is necessary to ensure that the safe operating area (SOA) for the device is suited to the application and that proper cooling of the semiconductor is achieved [77].

As for burnout failures, they are observed either at the final phase of wear out or because of random events. These failures are associated with short-circuit conditions, where a large current flows through the device while blocking the full line voltage [72]. These conditions lead to the thermal runaway and the destruction of the device.

Latch-up is a failure mechanism inherent to IGBT devices. It happens when a big dv/dt is produced during the turn-off and can trigger the parasitic thyristor in the IGBT structure [72], [77]. The latch-up is a burnout failure as the triggering of the parasitic component leads to the thermal destruction of the device. Another catastrophic burnout of an IGBT chip can be originated from cosmic ray collision on the device [78].

Although in some cases the overstress failures of chips show up as an open-circuit, in most of the cases they manifest as short-circuit of the device [40], [65], [75], [76].

#### 1.3.1.2. Wear-out failure mechanisms

The most common wear-out failures for IGBT dies are Time Dependent Dielectric Breakdown (TDDB) and Hot Carrier Injection (HCI) [66], [72].

The dielectric breakdown is caused by gate degradation due to accumulated defects [79]. In [80], three defect generation mechanisms are identified: impact ionization, anode hole injection and trap creation. Catastrophic breakdown occurs when the device experiences severe electrical or thermal stress.

Regarding HCI, two mechanisms are distinguished. The first is the electric field distortion due to accumulation of ionic contaminants in the passivation of the high-field region. The second is the growth of defects in the gate oxide [81]. During high temperature operation, hot carriers can be injected into the gate oxide when carriers attain high energy. These mechanisms lead to shifts in the device characteristics, such as threshold voltage, leakage current, transconductance, or saturation, and eventually to device degradation [73], [82], [83].

Finally, another relevant wear-out failure mechanism is electrochemical migration. In presence of the appropriate conditions (high humidity, high temperature and high voltage), electrical migration at chip passivation layer and terminal structure lead to an increase in leakage currents and loss of blocking capabilities [67]–[71], [84].

## 1.3.2. Package-related failure mechanisms

#### 1.3.2.1. Overstress failure mechanisms

The main causes for overstress failures at package level are thermal shocks, thermal runaways, mechanical shocks and stresses [49]. The result of a mechanical shock can damage the internal structure of the IGBT module and compromise its voltage blocking capability. This in turn, will lead to voltage breakdown [85].

Thermal runaway happens under high temperature and it leads to the melting of the connections inside the package [40], [72]. Another possible cause for package-related overstress are flashover-generated burnouts [40], [49].

#### 1.3.2.2. Wear-out failure mechanisms

For package-related failures, the principal failure mechanisms are thermomechanical fatigue, thermomechanical creep, electromigration and corrosion [72], [86].

Electromigration is originated in bond wires and metallization layers in the presence of high currents. This phenomenon leads to the creation of voids and hot spots [49], [72].

As for corrosion, it is reported that humidity and corrosive chemicals existing in various industrial applications can be a very important source of packaging degradation [67], [72], [87]. Additionally, humidity degrades the insulation characteristics of module encapsulation materials such as Si-gel [49], [67].

Concerning thermomechanical creep, it is caused by high operating temperatures that lead to the weakening of the mechanical strength of the package layers, which eventually can result in the formation of cracks [72], [88].

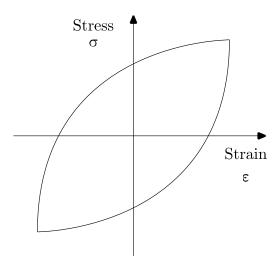

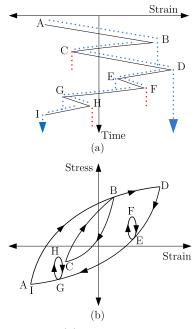

Among all the package-related failure mechanisms the more relevant are those related to thermomechanical fatigue [49]. The cause behind these mechanisms is the mismatch of the coefficients of thermal expansion (CTE) of the different layers of the IGBT module [72]. Additionally, temperature gradients are produced in the thermal path because of the difference in the thermal characteristics of the different module layers [89]. In Table 1.3 the typical thermal properties of a wire-bonded package can be seen.

IGBT module manufacturers have made efforts for reducing the stress induced by thermomechanical cycling. They have produced modules with materials that reduce the stress in the adjacent layers such as Al<sub>2</sub>O<sub>3</sub> for the ceramic layer and copper baseplates [90]. Other notable improvements in packaging thermal performances were reported in [91]–[98].

The main failure mechanisms resulting from the thermomechanical fatigue are bondwire degradation, solder layer degradation and degradation of metallization layers. These mechanisms, being the more relevant, will be discussed separately and in more detail.

| Layer         | Material    | Conductivity (W/m/K) | Capacity<br>(J/kg/K) | $ m CTE \ (10^{-6}/K)$ |

|---------------|-------------|----------------------|----------------------|------------------------|

| Bond wire     | Al-alloy    | 220                  | 896                  | 23                     |

| Metallization | Al-anoy     | 220                  | 090                  | 20                     |

| Chip/Die      | Si          | 100                  | 741                  | 3                      |

| Die attach    | Solder SnAg | 28                   |                      | 57                     |

| DBC attach    | (96.5/3.5)  | 20                   | -                    | 91                     |

| DBC layer 1   |             |                      |                      |                        |

| DBC layer 2   | Cu          | 380                  | 381                  | 17                     |

| Baseplate     |             |                      |                      |                        |

| DBC ceramic   | $Al_2O_3$   | 25                   | 850-1k               | 8                      |

| DDC ceramic   | AlN         | 180                  | 700-760              | 5                      |

Table 1.3 Thermal properties of standard IGBT wire-bonded package [40]

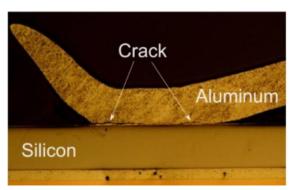

#### 1.3.2.2.1. Bond wire degradation

Bond wire failures are mainly caused by crack growth at the bond wire/chip interface due to temperature swings and the different CTEs between Si and Al [99]. Stress is produced at this interface as both layers experience different strains. The resulting stress is dependent on the temperature [73].

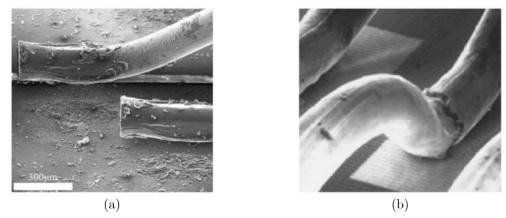

Cracks are generally initiated at the boundaries of the bonded area of the wire, since the expansion of the wire is restricted at the edges of the bond pad [100]. Therefore, cracks propagate from the edges towards the center of the bonded area through the pad between the wire and the metallization or through the body of the wire [101] as seen on Figure 1.6. When cracks reach the center of the Al wire, bond wire lift-off is produced and the connection between the wire and the chip is lost. An example of bond wire lift-off can be seen in Figure 1.7 (a). Another site where cracks initiate and propagate is the wire heel, however, this mechanism is less frequent. If the cracks at the wire heel reach the center of the wire heel cracking is produced and the electrical connection is compromised. In Figure 1.7 (b) an example of bond wire heel crack can be seen.

Figure 1.6. Cracking of the bonded pad between the Si chip and the Al bond wire [101]

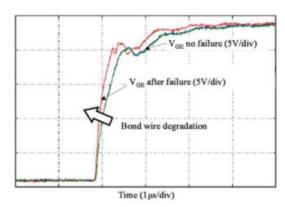

It is worth mentioning that both failure mechanisms happen when the module is submitted to power cycling. Once a wire has failed, the current is redistributed through the remaining wires. This results in an increase in current and hence in temperature of the remaining bond wires, which accelerates its degradation. The loss of electrical contact between the wire and the chip results in the increase of the on-state resistance of the module, which will lead to higher conduction losses.

Figure 1.7. SEM images of bond wire degradation [72], [102]: (a) lift-off, (b) heel cracking

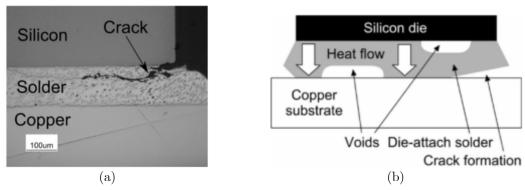

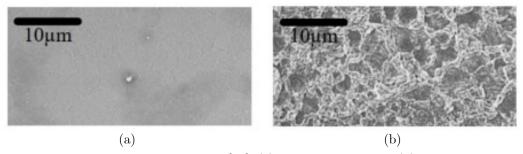

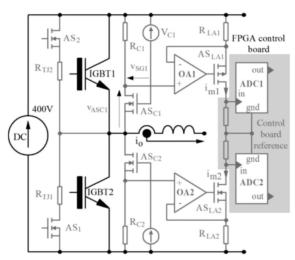

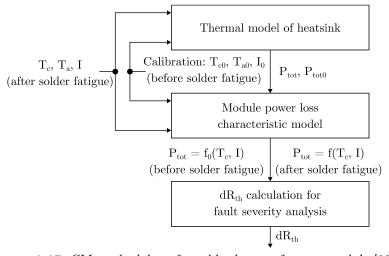

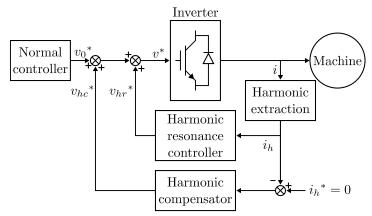

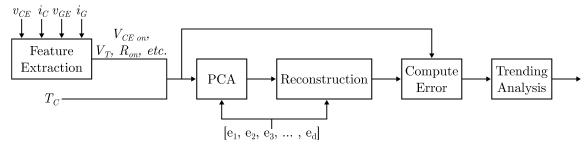

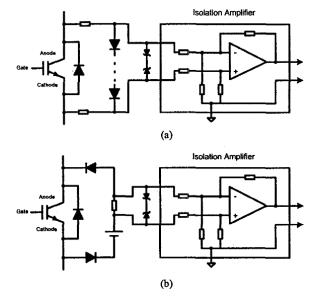

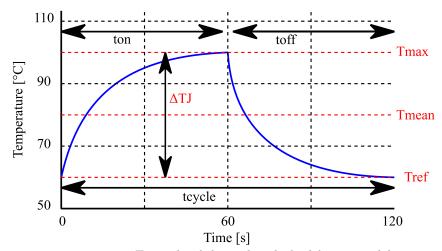

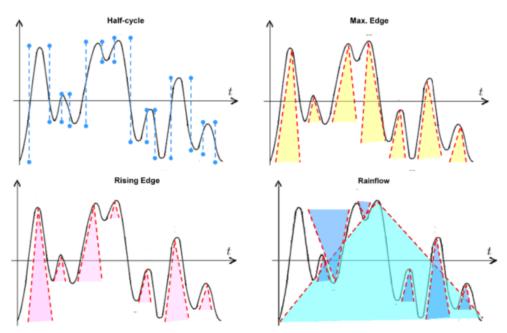

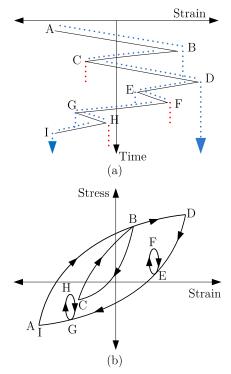

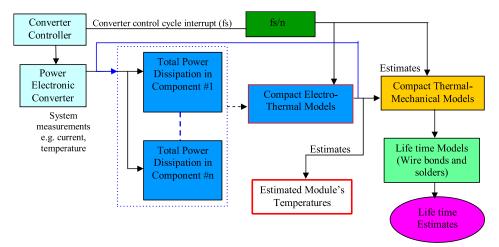

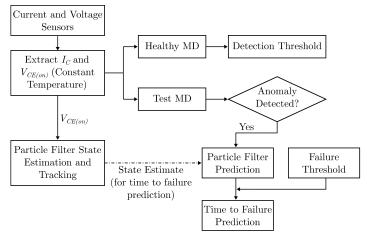

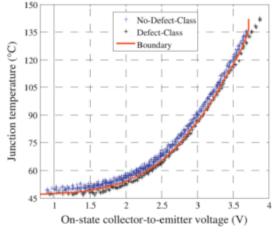

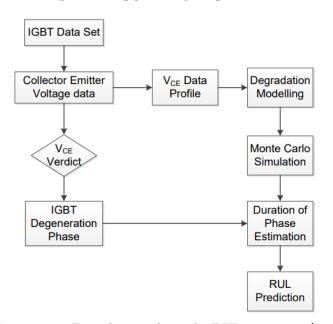

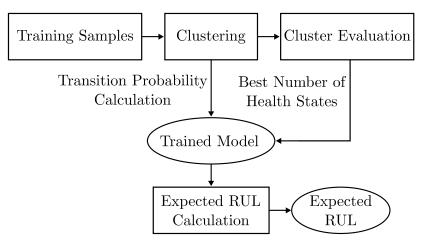

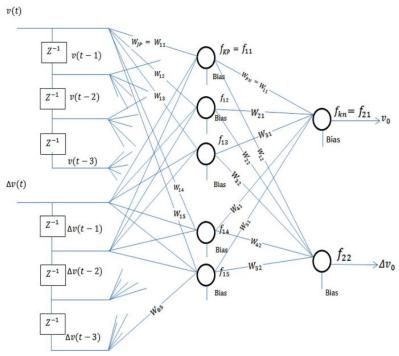

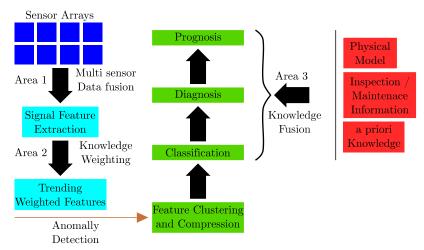

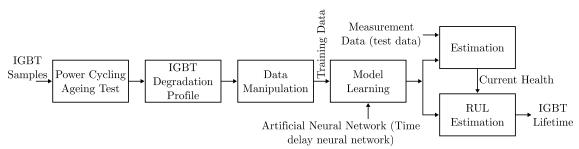

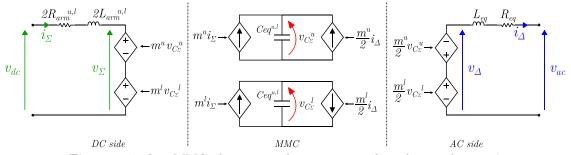

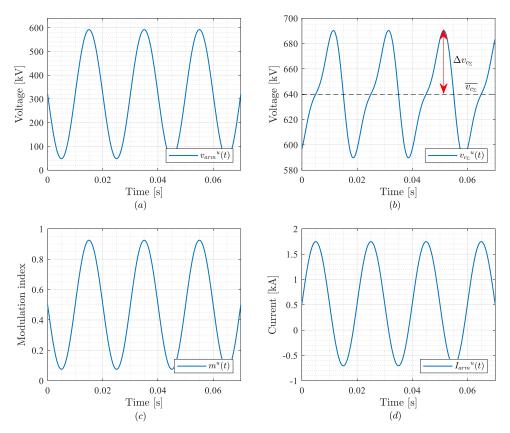

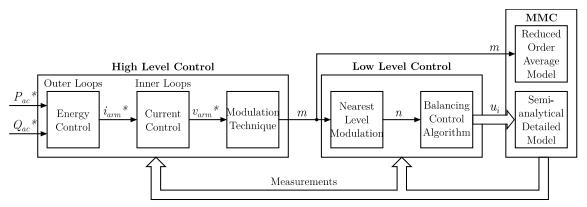

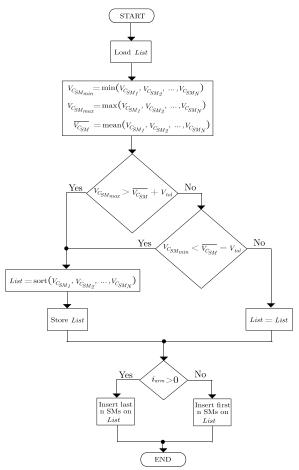

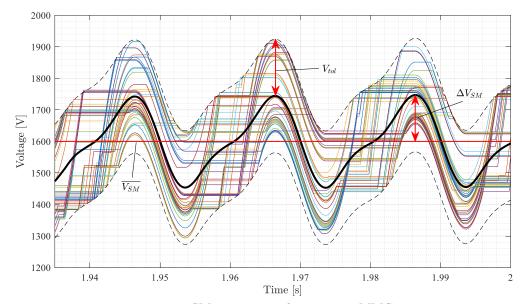

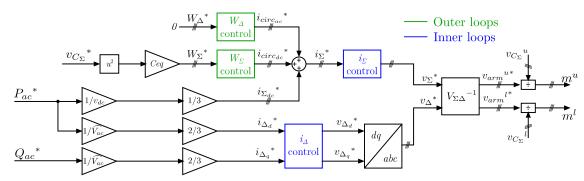

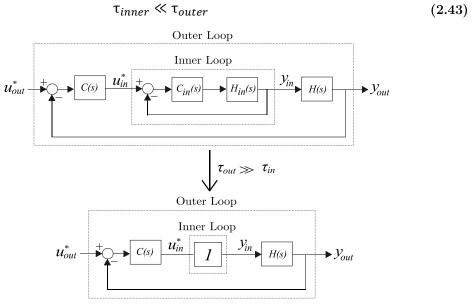

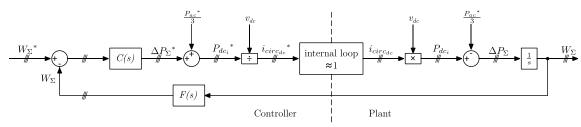

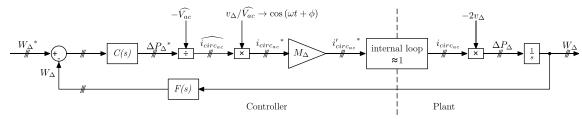

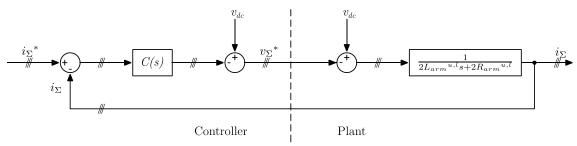

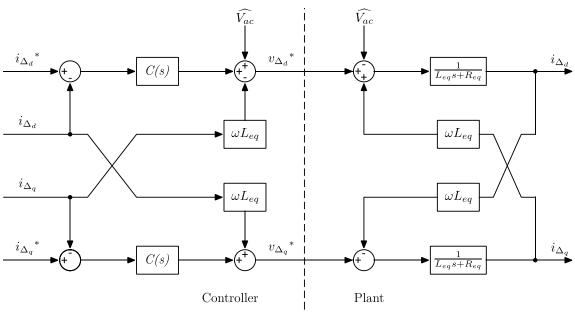

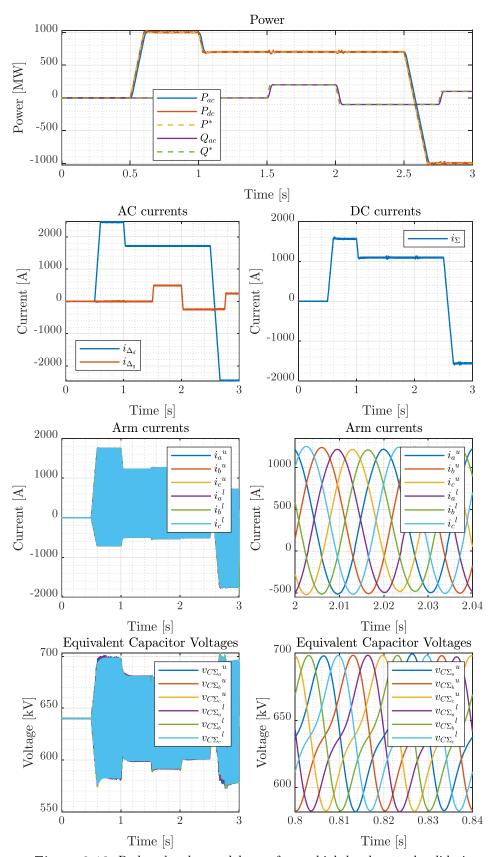

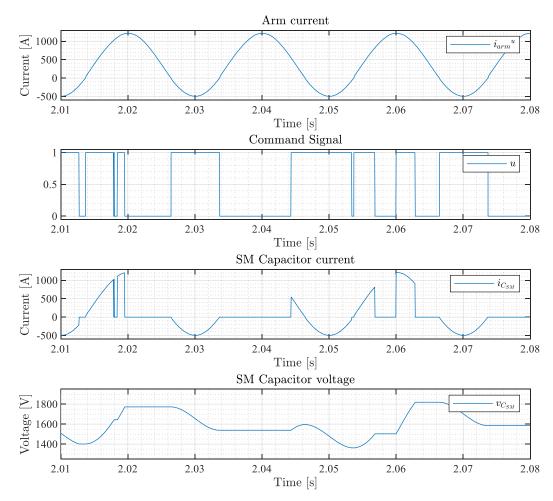

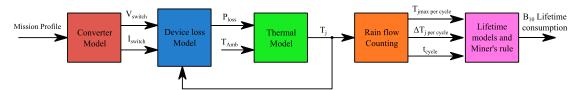

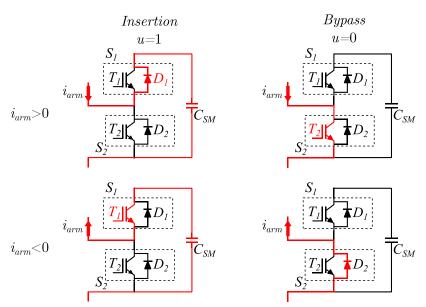

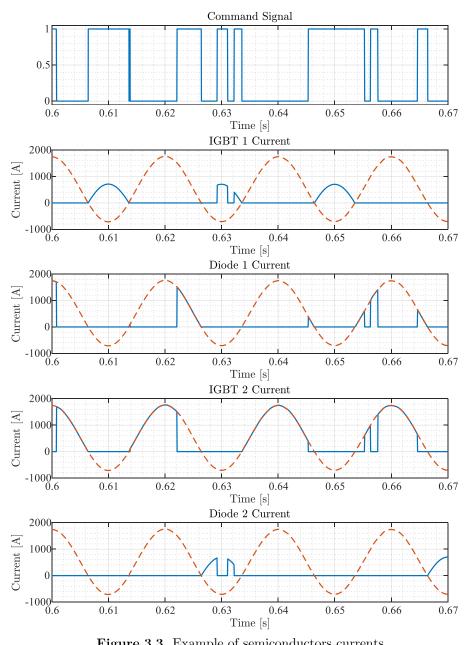

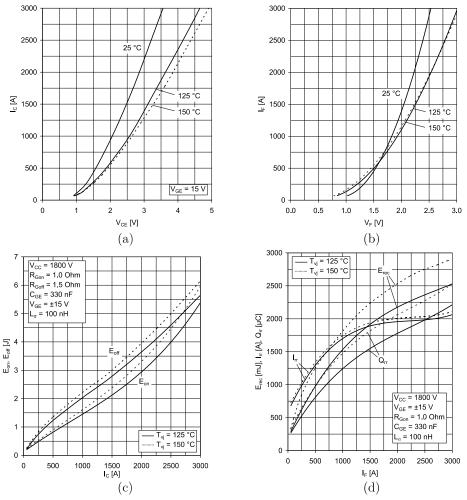

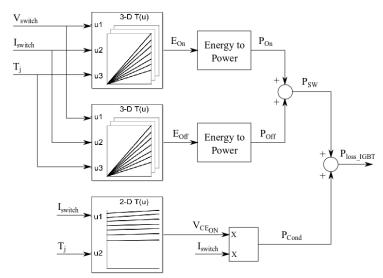

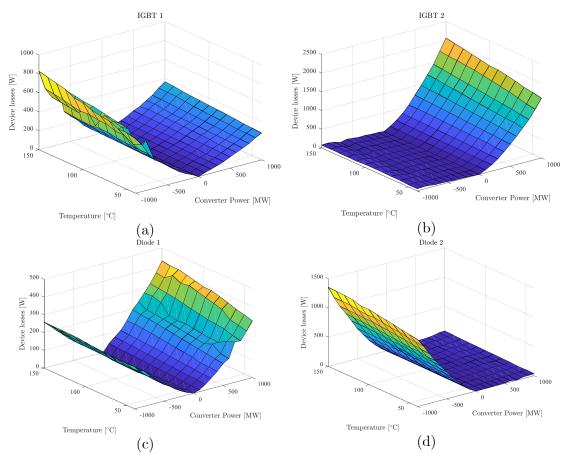

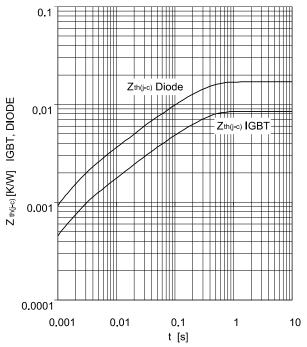

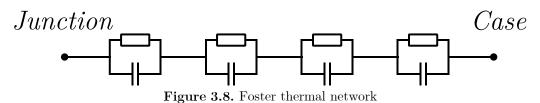

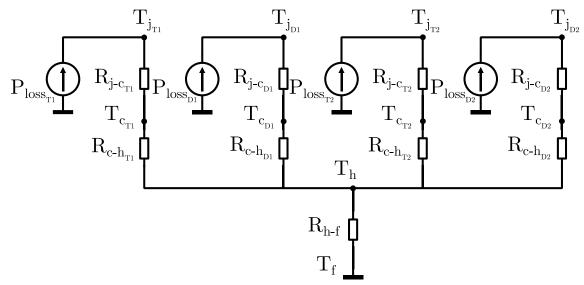

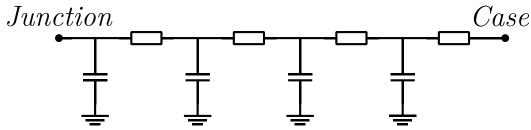

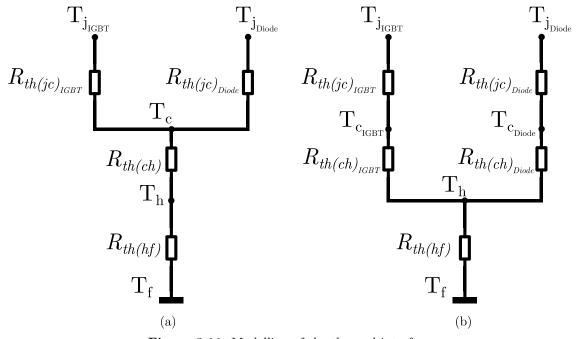

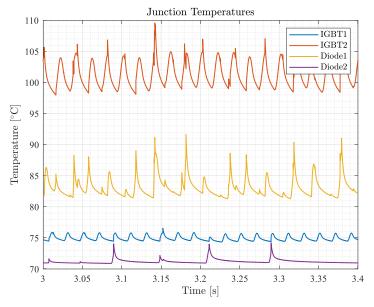

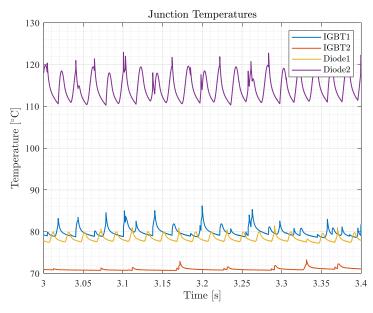

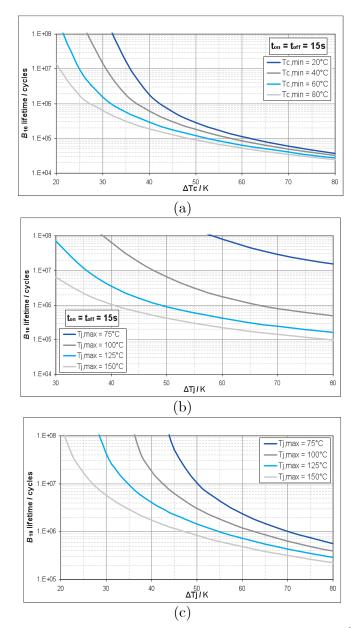

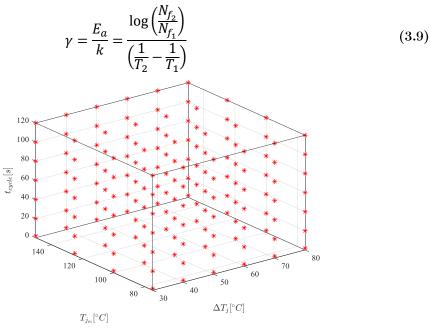

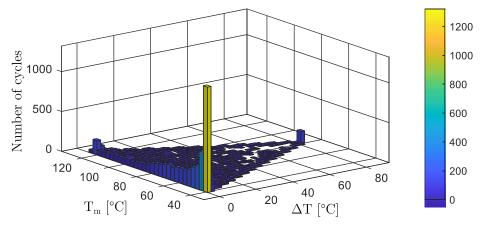

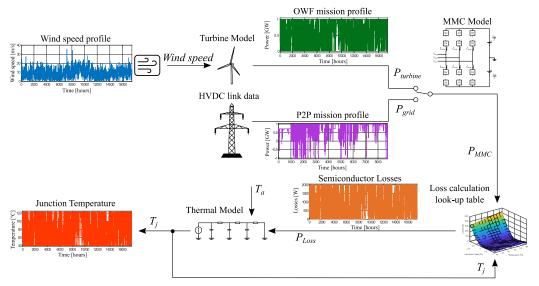

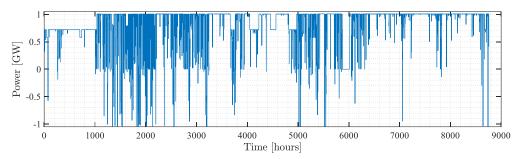

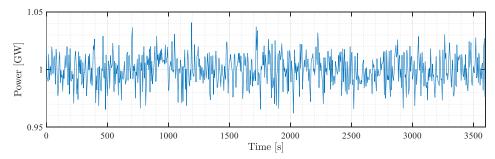

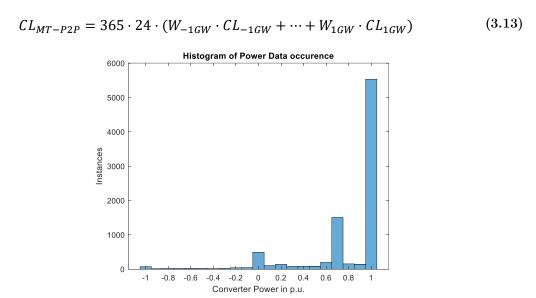

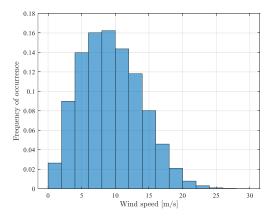

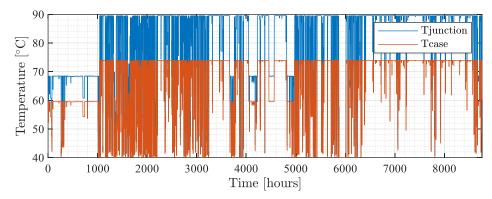

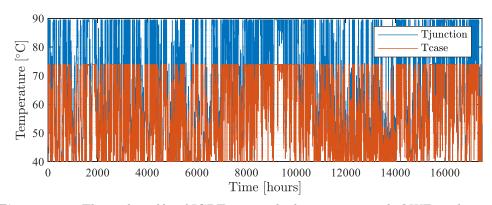

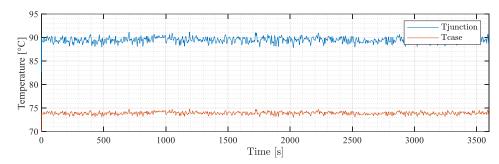

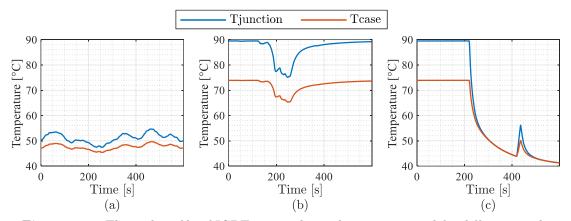

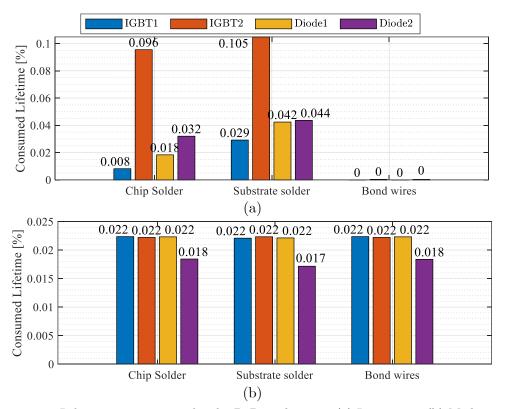

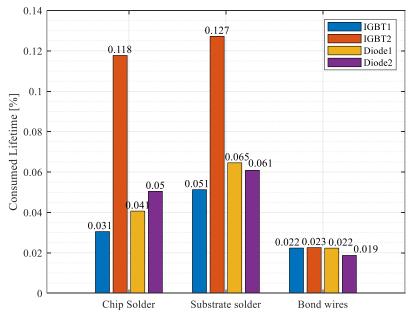

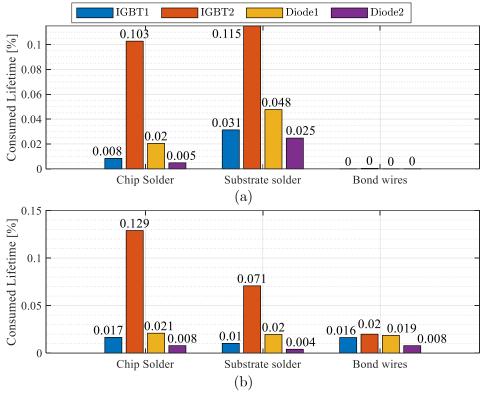

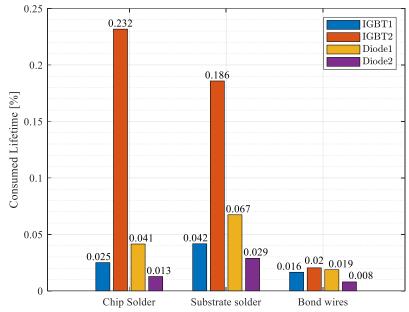

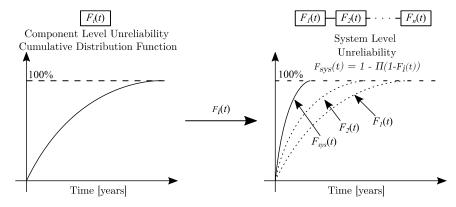

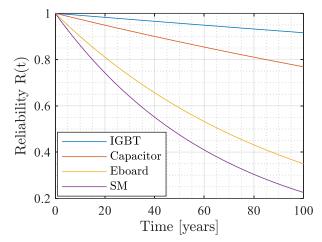

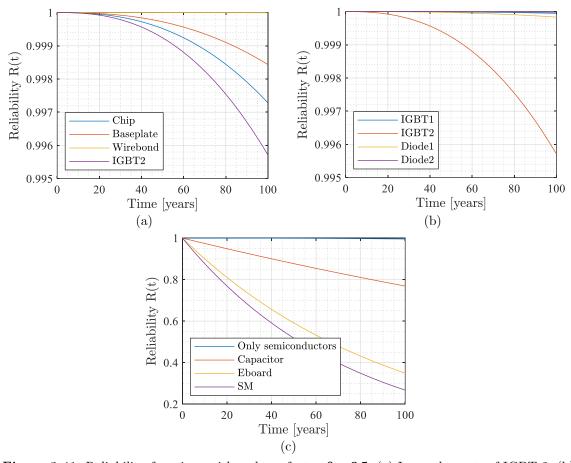

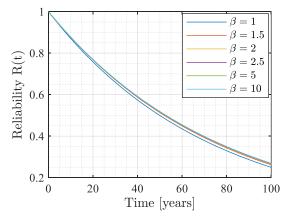

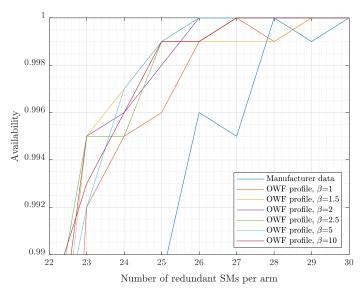

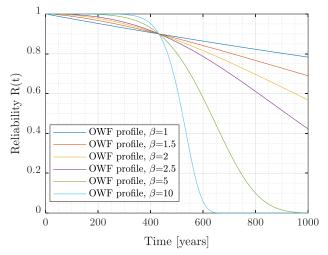

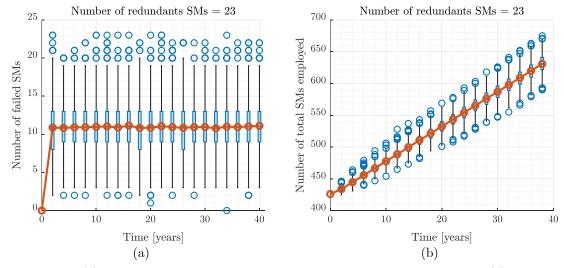

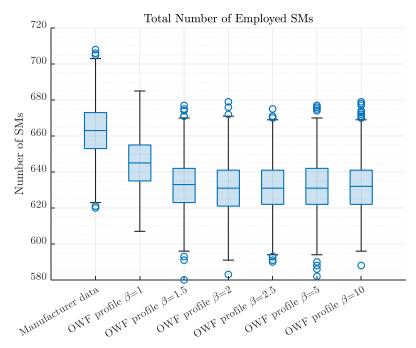

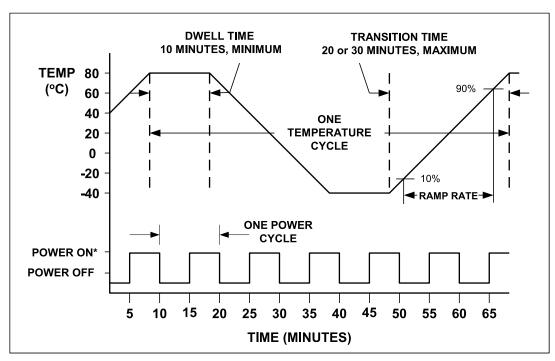

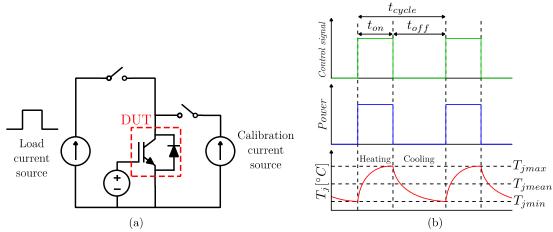

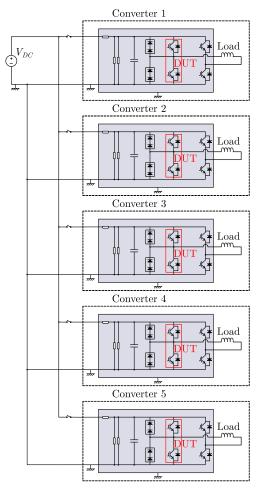

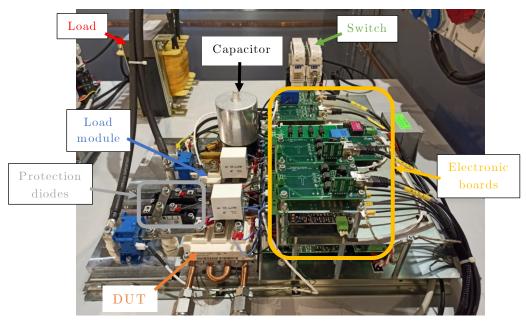

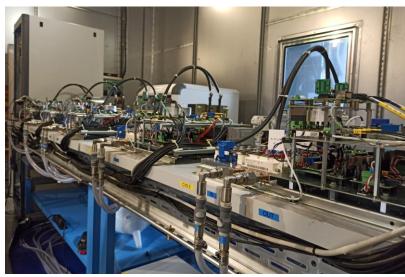

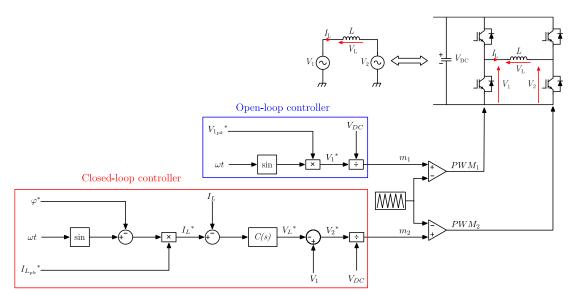

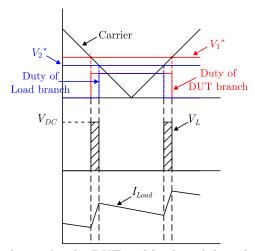

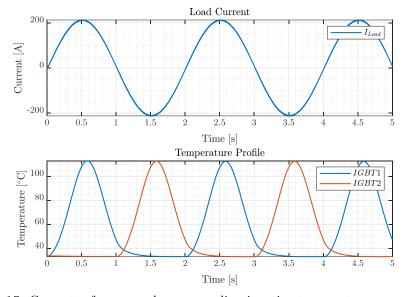

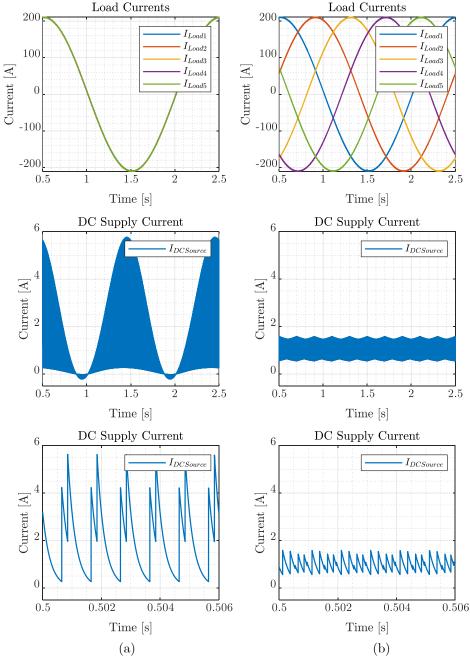

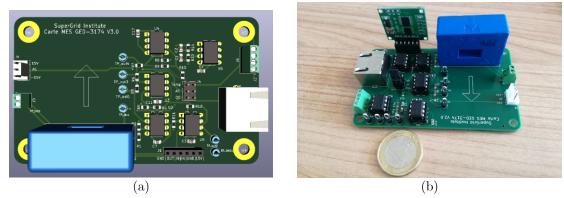

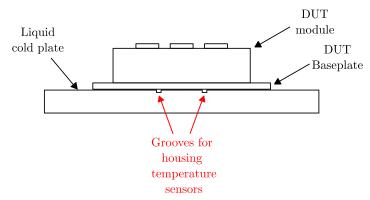

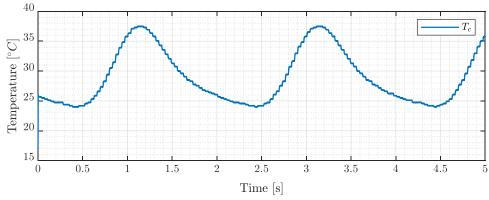

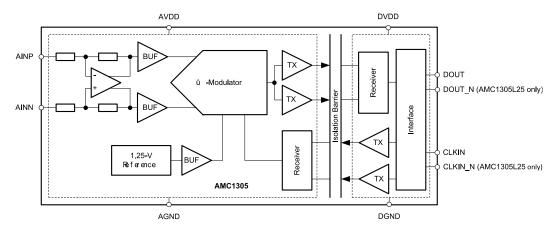

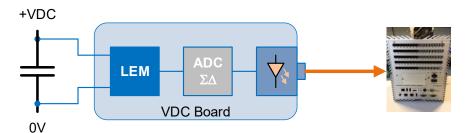

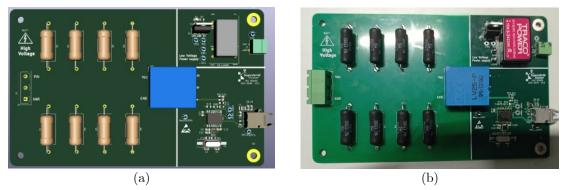

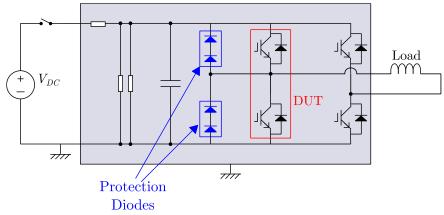

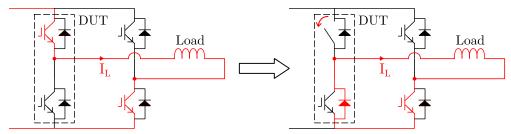

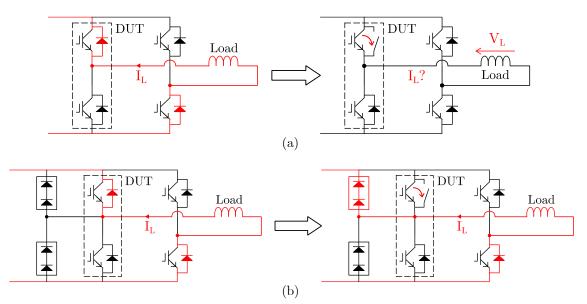

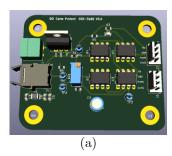

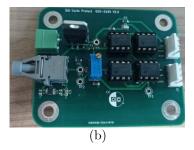

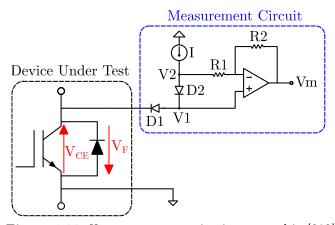

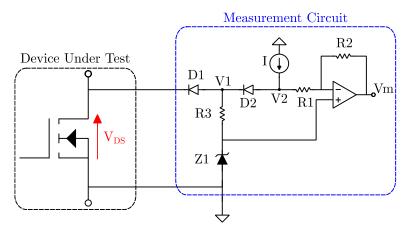

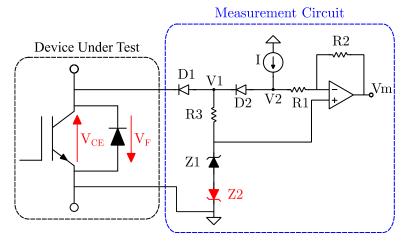

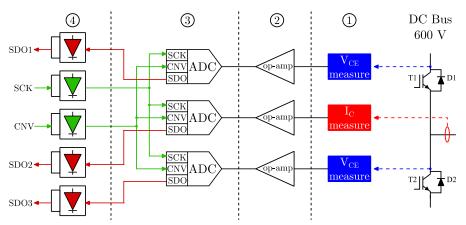

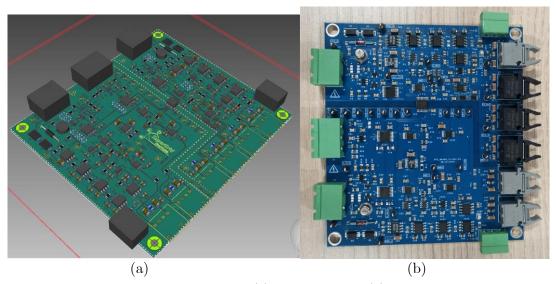

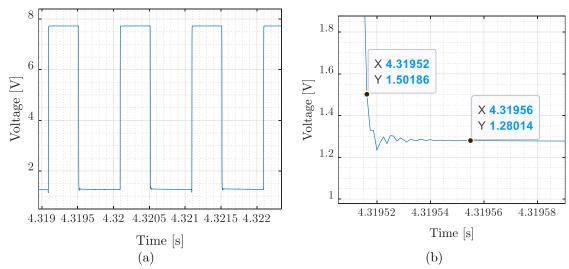

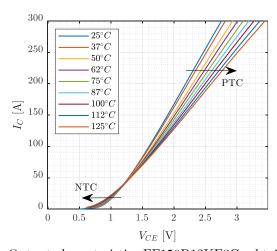

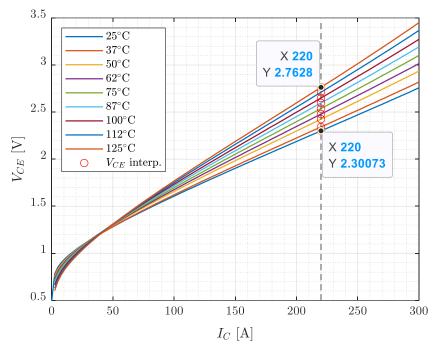

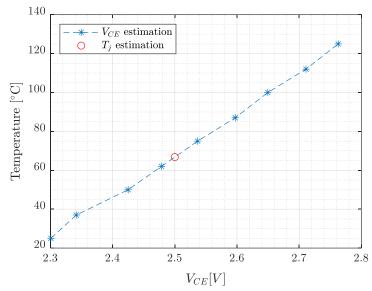

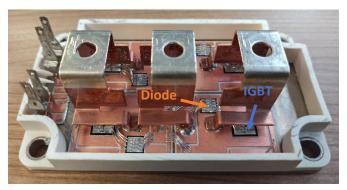

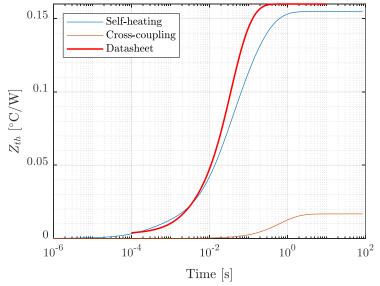

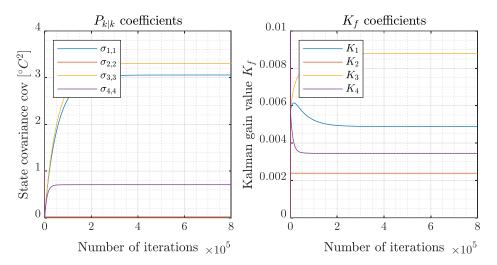

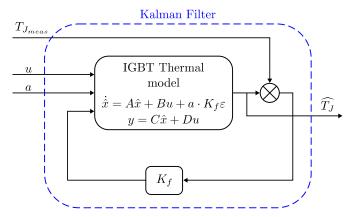

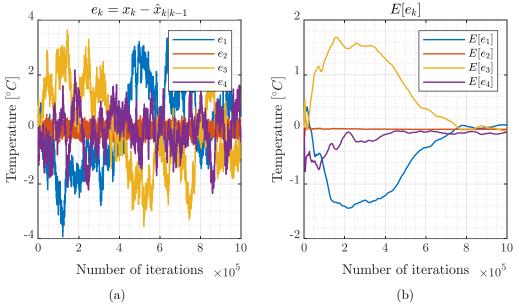

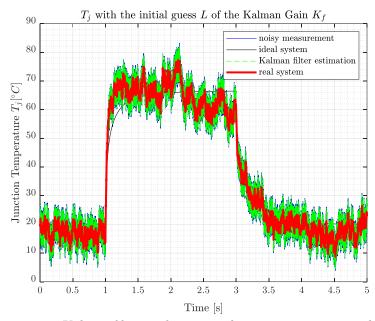

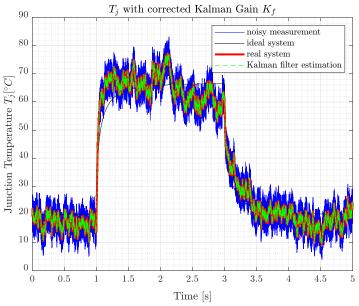

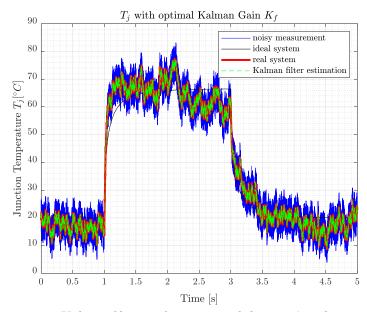

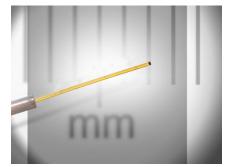

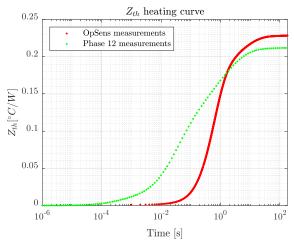

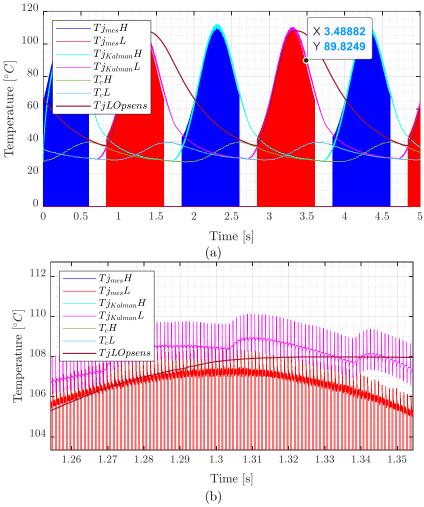

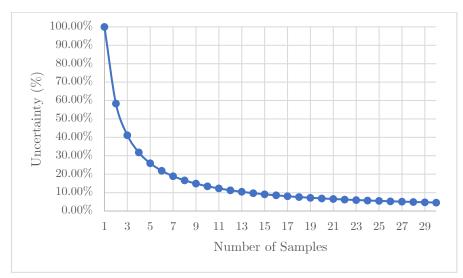

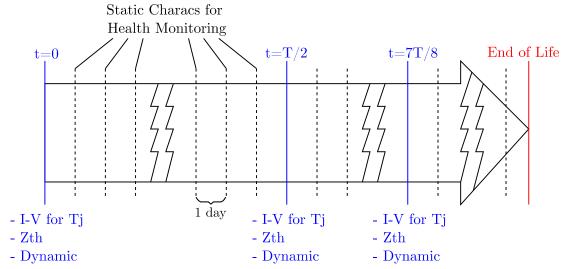

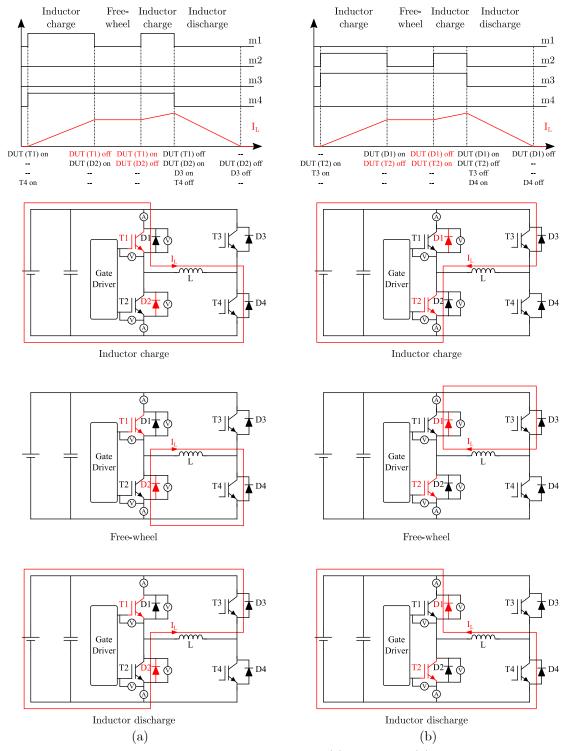

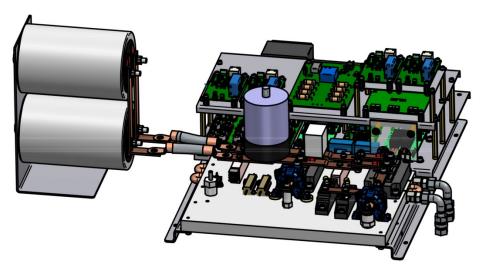

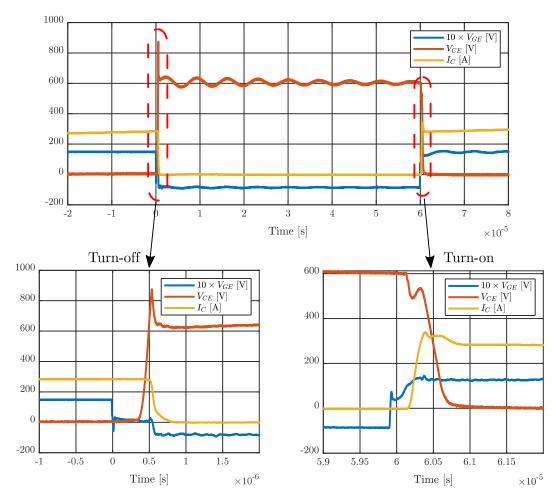

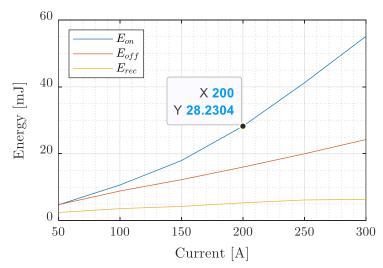

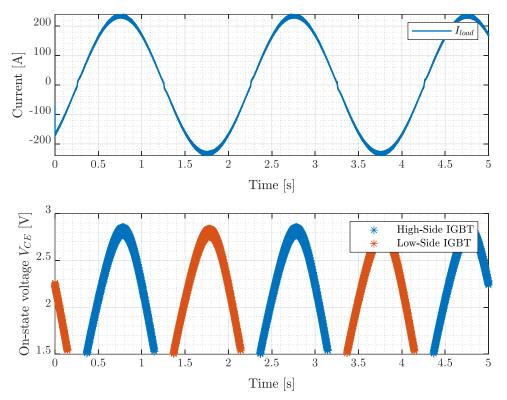

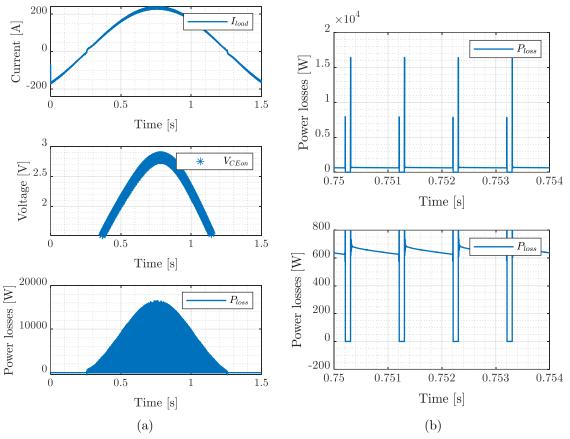

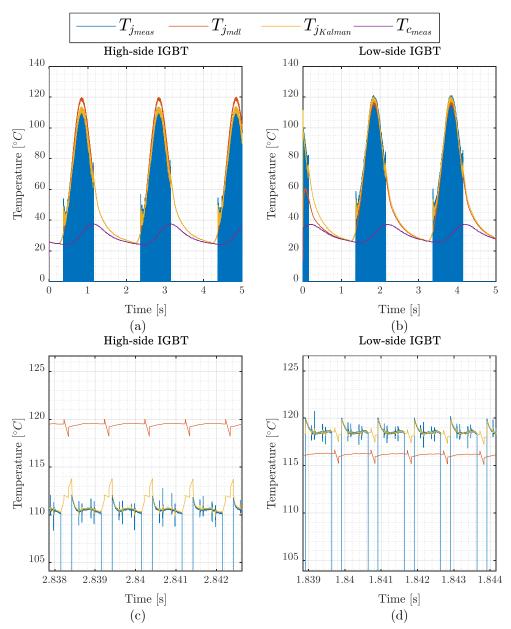

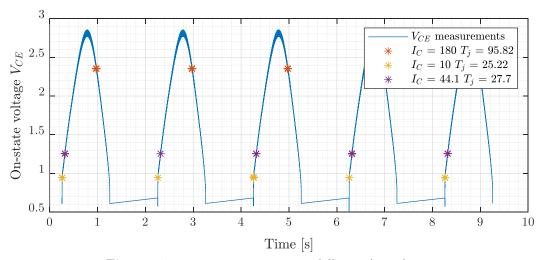

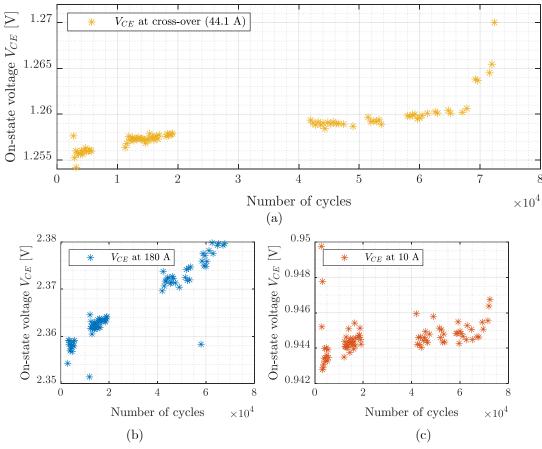

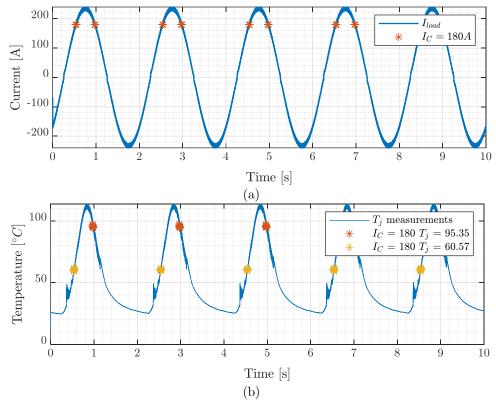

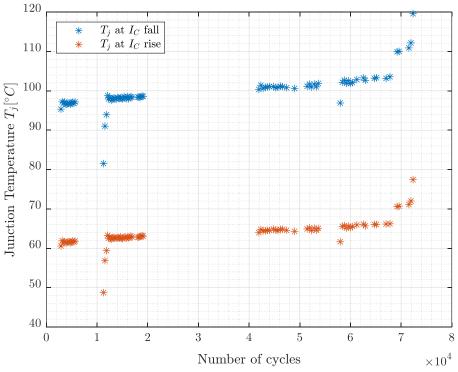

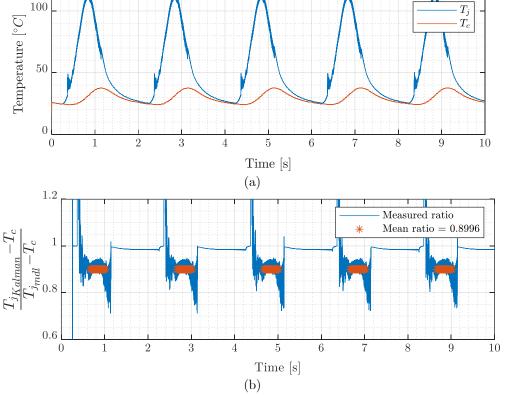

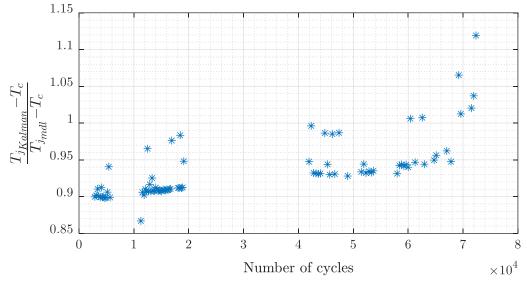

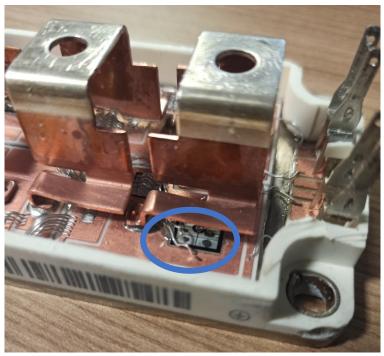

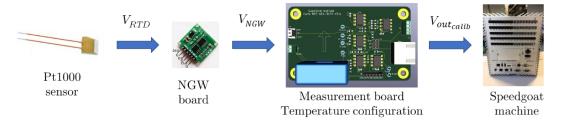

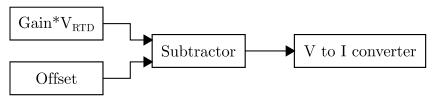

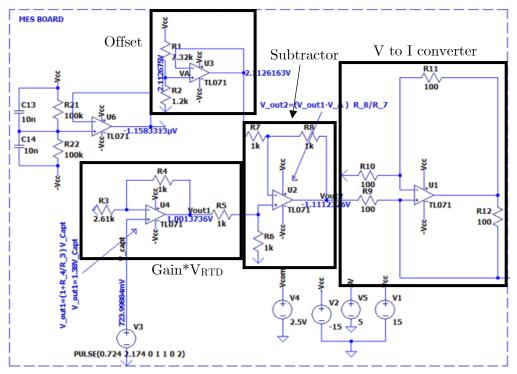

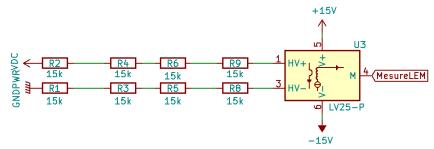

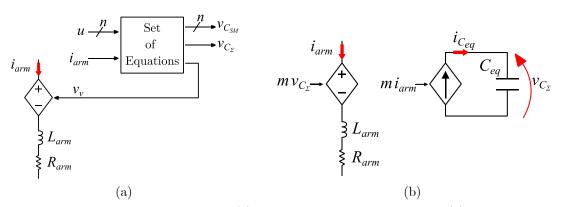

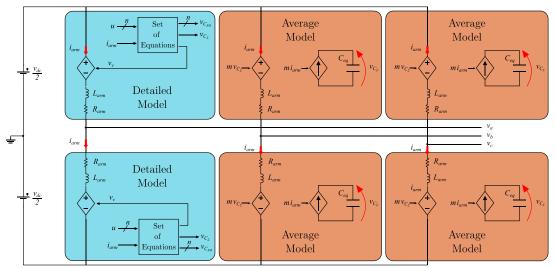

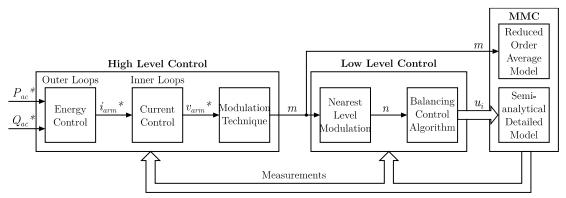

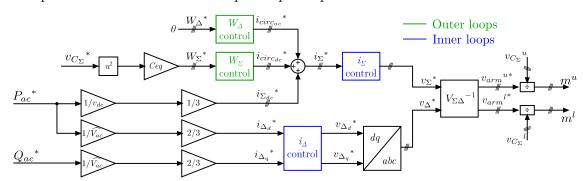

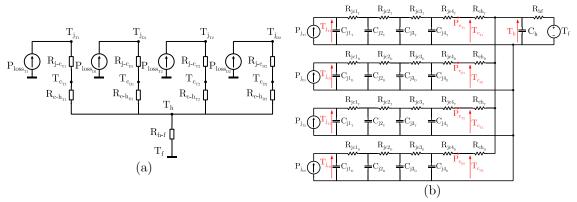

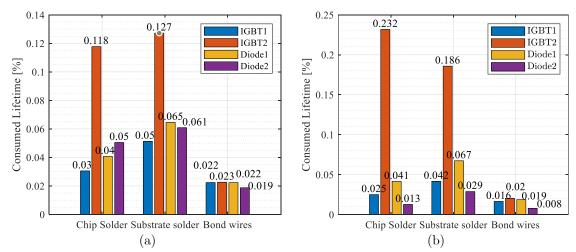

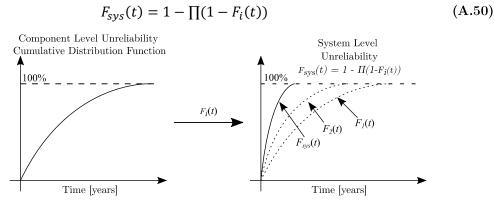

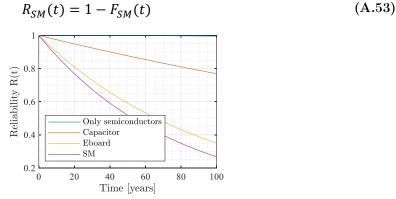

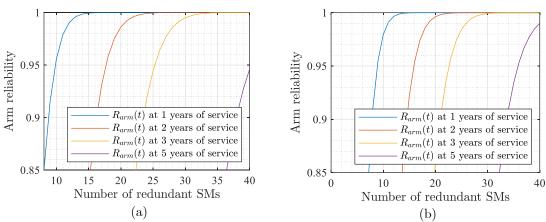

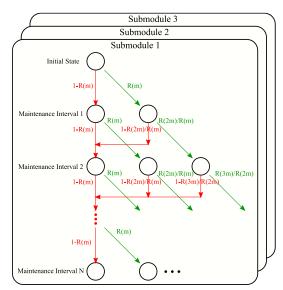

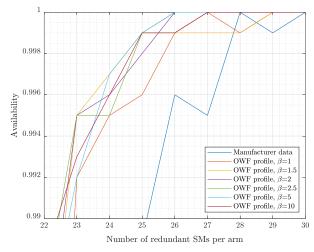

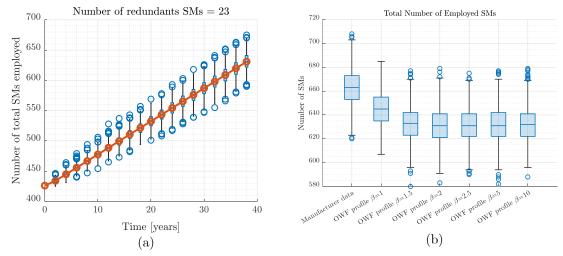

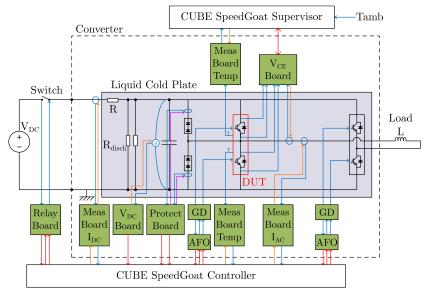

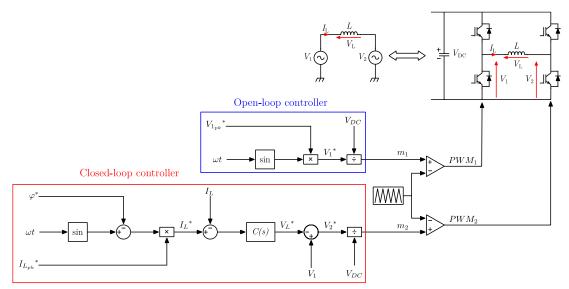

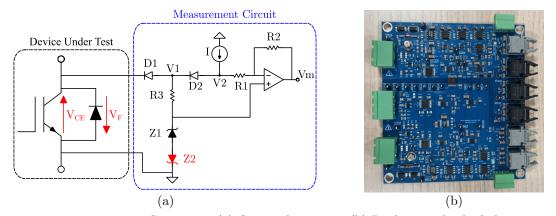

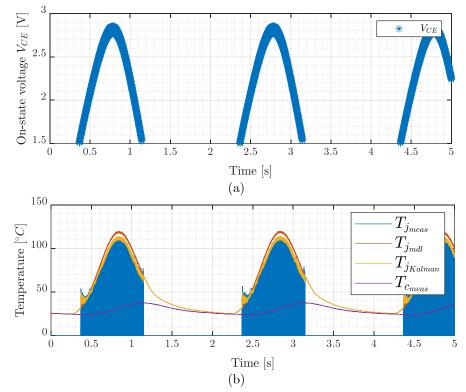

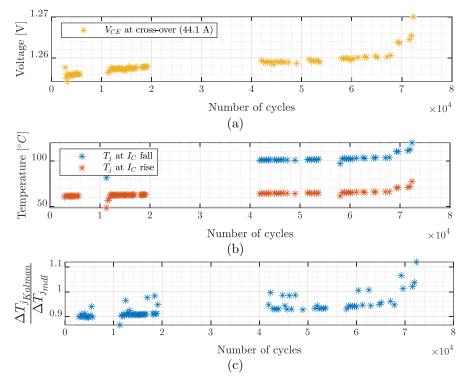

#### 1.3.2.2.2. Solder layer degradation