## Enhancements in Embedded Systems Security using Machine Learning

Ritu Ranjan Shrivastwa

### ▶ To cite this version:

Ritu Ranjan Shrivastwa. Enhancements in Embedded Systems Security using Machine Learning. Embedded Systems. Institut Polytechnique de Paris, 2023. English. NNT: 2023IPPAT051. tel-04506109

## HAL Id: tel-04506109 https://theses.hal.science/tel-04506109

Submitted on 15 Mar 2024

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Enhancements in Embedded Systems Security using Machine Learning

Thèse de doctorat de l'Institut Polytechnique de Paris Préparée à Télécom Paris

Ecole doctorale n° 626 Ecole doctorale de l'Institut Polytechnique de Paris (ED IP Paris) Spécialité de doctorat: Réseaux, informations et communications

Thèse présentée et soutenue à Paris, le 05/12/2023, par

### **RITU RANJAN SHRIVASTWA**

Jury composition:

| M. Jean-Max DUTERTRE<br>Professeur, Ecole des Mines de Saint-Étienne, France                                         | Président/Examinateur |

|----------------------------------------------------------------------------------------------------------------------|-----------------------|

| M. Yossi OREN<br>Professeur, Ben-Gurion University, Israel                                                           | Rapporteur            |

| M. Philippe MAURINE<br>Maître de conférence HDR, LIRMM, Université de<br>Montpellier, France<br>M. Gilles SASSATELLI | Rapporteur            |

| Professeur, LIRMM, Université de Montpellier, France                                                                 | Examinateur           |

| M. Giorgio DI NATALE<br>Professeur, TIMA, Université Grenoble Alpes, France                                          | Examinateur           |

| M. Jean-Luc DANGER<br>Professor, Télécom Paris, France                                                               | Directeur de thèse    |

| M. Sylvain GUILLEY<br>CTO, Secure-IC et Professeur Invité de Télécom Paris,<br>France                                | Co-directeur de thèse |

Thèse de doctorat

II

# Contents

| 1 | Intro | oduction 1                                                                   |

|---|-------|------------------------------------------------------------------------------|

|   | 1.1   | Context                                                                      |

|   | 1.2   | Problem definition                                                           |

|   |       | 1.2.1 Design and development                                                 |

|   |       | 1.2.2 Production                                                             |

|   |       | 1.2.3 Supply-Chain                                                           |

|   | 1.3   | External Fault Injection                                                     |

|   | 1.4   | Hardware Trojans                                                             |

|   | 1.5   | Intrusion Detection System                                                   |

|   | 1.6   | Countermeasures using ML                                                     |

|   | 1.7   | Objectives                                                                   |

| ~ |       |                                                                              |

| 2 |       | ated Works       9         Introduction to Embedded Systems security       9 |

|   | 2.1   |                                                                              |

|   | 2.2   | 5                                                                            |

|   |       | 2.2.1 Electro-Magnetic Fault Injection                                       |

|   |       | 2.2.2 Clock-Glitch Fault Injection                                           |

|   | ~ ~   | 2.2.3 Laser Fault Injection                                                  |

|   | 2.3   | Hardware Trojans                                                             |

|   |       | 2.3.1 Hardware Trojan Introduction                                           |

|   |       | 2.3.2 Types of Hardware Trojans                                              |

|   |       | 2.3.3 How and where in the life-cycle can a HT be inserted 16                |

|   |       | 2.3.4 Hardware Trojan Detection                                              |

|   | 2.4   | Intrusion detection systems                                                  |

|   |       | 2.4.1 Application of IDS in IoT                                              |

|   | 2.5   | Machine Learning                                                             |

|   |       | 2.5.1 Introduction to ML                                                     |

|   |       | 2.5.2 Types of ML algorithms 25                                              |

|   |       | 2.5.3 Non-security applications of ML                                        |

|   |       | 2.5.4 Embedded systems security using ML                                     |

|   |       | 2.5.5 Detecting Fault attacks with Machine Learning                          |

|   |       | 2.5.6 Detecting Hardware Trojans with Machine Learning 28                    |

|   |       | 2.5.7 Statistical methods                                                    |

|   |       | 2.5.8 Machine Learning based IDS                                             |

|   | 2.6   | Certification and Standardization of AI                                      |

|   |       | 2.6.1 Introduction                                                           |

|   |       | 2.6.2 Standards and Guidance on Al                                           |

|   | 07   |                                                                                  | 32 |

|---|------|----------------------------------------------------------------------------------|----|

|   | 2.7  | Conclusion                                                                       | 32 |

| 3 |      | ,                                                                                | 33 |

|   | 3.1  |                                                                                  | 33 |

|   | 3.2  |                                                                                  | 34 |

|   |      | 5                                                                                | 34 |

|   |      |                                                                                  | 34 |

|   |      |                                                                                  | 34 |

|   | 3.3  | 5                                                                                | 36 |

|   | 3.4  | 55                                                                               | 37 |

|   |      |                                                                                  | 37 |

|   |      | 3.4.2 Classical threshold optimization method for comparison with the ML model 3 |    |

|   |      |                                                                                  | 40 |

|   | 3.5  |                                                                                  | 42 |

|   |      | 5                                                                                | 42 |

|   |      |                                                                                  | 43 |

|   |      |                                                                                  | 44 |

|   |      | 3.5.4 Classification between combined EMFI and CGFI against Nominal con-         | 45 |

|   |      | dition                                                                           | 40 |

|   |      |                                                                                  | 45 |

|   | 3.6  |                                                                                  | 46 |

|   | 0.0  |                                                                                  | 46 |

|   |      |                                                                                  | 47 |

|   |      |                                                                                  | 47 |

|   | 3.7  | •                                                                                | 48 |

|   | 3.8  | Conclusion                                                                       | 49 |

| 4 | Insi | der (Hardware Trojan) Detection                                                  | 51 |

|   | 4.1  |                                                                                  | 51 |

|   | 4.2  | Machine Learning based Hardware Trojan detection                                 | 52 |

|   |      | 4.2.1 Supervised ML algorithms used for HT detection                             | 52 |

|   | 4.3  | Hardware Trojan Design                                                           | 54 |

|   |      | 4.3.1 P&R Level                                                                  | 55 |

|   |      | 4.3.2 RTL level                                                                  | 55 |

|   | 4.4  | Hardware Trojan Detection Using Electromagnetic Emanation                        | 55 |

|   |      | 4.4.1 Experimental Setup                                                         | 55 |

|   |      | 1                                                                                | 56 |

|   |      | 4.4.3 Some state-of-the-art detection methodologies for the purpose of com-      |    |

|   |      | I                                                                                | 57 |

|   |      |                                                                                  | 57 |

|   |      |                                                                                  | 58 |

|   |      | 8                                                                                | 58 |

|   |      | 0, 1                                                                             | 59 |

|   |      | 55 1                                                                             | 61 |

|   | 4.5  |                                                                                  | 62 |

|   | 4.6  | Conclusion                                                                       | 64 |

| <ul> <li>5.1 Introduction</li></ul>                                  | solution   | 65<br>66<br>66<br>68 |

|----------------------------------------------------------------------|------------|----------------------|

| 5.2.1 Security Threats and Attack Surface covered in the presented s | I solution | 66<br>68             |

| · · ·                                                                |            | 68                   |

| 5.2.2 Propagation of the amulated controlled environment             |            |                      |

|                                                                      |            |                      |

| 5.3 Presented methodology and design idea                            |            | 69                   |

| 5.3.1 Sources of data                                                |            | 69                   |

| 5.3.2 ML based IDS Structure                                         |            | 69                   |

| 5.3.3 Network IDS (NIDS)                                             |            | 69                   |

| 5.3.4 Sensor or Host IDS (HIDS)                                      |            | 70                   |

| 5.3.5 ML parameters                                                  |            | 70                   |

| 5.3.6 Network communication with the cloud                           |            | 70                   |

| 5.3.7 Results                                                        |            | 71                   |

| 5.4 Discussion                                                       |            | 75                   |

| 5.5 Conclusion                                                       |            | 75                   |

| 6 Conclusion & Perspectives                                          | ,          | 77                   |

| 6.1 Conclusion                                                       |            | 77                   |

| 6.2 Perspectives                                                     |            | 79                   |

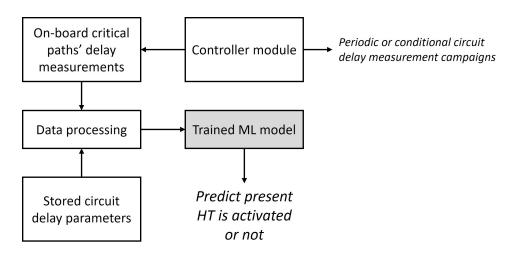

| 6.3 Timing based Hardware Trojan detection IP                        |            | 80                   |

| 6.3.1 Methodology and design idea                                    |            | 80                   |

| 6.4 Novelty/Outlier detection for FIA                                |            | 80                   |

| 6.5 List of Publications                                             |            | 81                   |

| 6.5.1 Conference                                                     |            | 81                   |

| 6.5.2 Journal                                                        |            | 81                   |

| 6.5.3 Patent                                                         |            | 81                   |

# Acknowledgements

It has been an adventurous, rewarding and at the same time arduous journey working on this part-time thesis deemed under the significant collaboration of the esteemed organization Secure-IC and the prestigious university Télécom-Paris. I took great pleasure in the endeavours to write this thesis of my four years of industrial research journey and I can in many words thank my thesis director and supervisor Prof. Jean-Luc DANGER and my thesis co-director and cosupervisor Prof. Sylvain GUILLEY for their tremendous support, guidance and encouragements during this whole period. It is with their kind supervision, through many meetings, discussions and brainstorming sessions, that I am able to complete my thesis work.

I also take this opportunity to sincerely thank all the jury members for agreeing to be a part of the defense jury, to review and examine the thesis manuscript. I express my grateful thanks to the reviewers Prof. Yossi OREN and Assoc. Prof. Philippe MAURINE, and the examiners Prof. Gilles SASSATELLI, Prof. Jean-Max DUTERTRE, and Prof. Giorgio DI NATALE.

In my company, Secure-IC, I must thank my manager Dr. Youssef SOUISSI for his encouragements and support during the period of my PhD work. I would also like to thank my CEO M. Hassan TRIQUI for his support in this process. Additionally, I would like to extend my thanks to all my colleagues and my teammates in Secure-IC, who in one way or the other helped me during my thesis works and supported me for the same.

I must also thank the administrative body of the doctoral school at Télécom-Paris and EDIPP, Prof. Adriana TAPUS and Ms. Florence Besnard, and also to the director of LTCI Prof. Talel ABDESSALEM.

I would like to express my gratitude to my friends in Secure-IC and beyond who had been with me through thick and thin during this period.

Finally, I would like to express my heartfelt gratitude to my wife, my mother, my father and my brother, without the support of whom this journey would not have been made possible.

# Abstract

The cybersecurity requirements and concerns have grown exponentially piggy-backing on the growing market of embedded and integrated systems rolling out in the market through many verticals including IoT, Industrial-IoT, smart cities, healthcare, automotive, armed forces, remote intelligence, etc. to name a few. The end devices have become more sophisticated over time to provide high-end user services. This has been the result of the advancements in the semiconductor industry by enabling high-end computations at the edge or end-nodes. However, the current market demands the capability of managing the devices remotely to enable many features such as firmware updates and remote life-cycle management. This high sophistication of the connected-device architecture in many forms including Vehicle-to-Anything (V2X) have also paved the way for threat actors to inject and exploit vulnerabilities that usually pass unseen from the verification phases or are introduced in the design because of distributed development culture in the semiconductor industry. To cope with the growing size of the attack surfaces and exposed vulnerabilities, it is pertinent to introduce cybersecurity verification mechanisms that identify and manage those weaknesses and vulnerabilities and save the equipment manufactures from obsoletion due to security issues as well as protect user data to maintain privacy and confidentiality. However, the size of data in most cases is also a big challenge and therefore the reliance on Machine Learning (ML) and Artificial Intelligence (AI) comes into play.

In this PhD manuscript, the challenges associated with the protection of different devices in terms of physical, internal threats in embedded/integrated designs, as well as network security in some cases, have been addressed. The focus of the work is to provide generic frameworks, through evaluation and experimentation, for different security challenges that are generally encountered in the embedded and integrated systems domain. Therefore, the work has been divided into three major areas viz. External Fault Injection detection, Hardware Trojan detection, and Intrusion Detection System (IDS) with a working example of automotive use-case in a simulated V2X architecture. The major contribution is in the system design and defense upgrade to enhance security of different types of devices from baremetal to the operating systems level while extending it to network level with server-side defense monitoring. To prove the effectiveness of the proposed architectures, design and validation/testing methodologies, results and comparisons with similar works have been presented for the proposed defense mechanisms.

Abstract

# Thesis summary

### Chapter 1 – Introduction

The modern semiconductor industry allows the flexibility for a semiconductor company to develop all the parts of a device in-house by allowing the outsourcing of the tasks to which it does not hold the expertise in such as fabrication and packaging. The recent trend for chip manufacturers is to develop the design and produce the synthesizable RTL which then is forwarded to a partner industry for fabrication, packaging and testing services. This has created a massive outsourcing network in the entire industry where there are different companies focused on various stages in the VLSI design flow. This being said, there are two major outcomes of this distributed infrastructure viz. a) the production rate is significantly increased and the processing time is highly reduced as multiple stages can be carried out in parallel, and b) the vulnerability of tampering the design is increased manifold because most of the processing and different parts originate or are modified in third-party locations which can be considered insecure. As a result, we currently see a rise in the number of connected devices.

This modality of development and production has boosted the productivity of the connected devices but at the same time allowed for a rise in the hardware Trojan vulnerability among these devices and the risk of other threats associated with distributed development and production such as overproduction. To that end, it is essential to have robust countermeasures against the growing threats and also to have a strong defence mechanism that keeps up to the growing threat level in terms of detection accuracy. This means we are looking for smart solutions for both protection and evaluation that have low footprint to reduce overhead on the overall design as well as does not decrease production time with overly complicated security gates at each phase of the production. The amount of data handling is high and the detection is expected to have high accuracy with reliability over different types of data. The immediate answer that comes to mind is Artificial Intelligence (AI) and Machine Learning (ML). In this thesis work, the author propose different solutions to counter the various challenges that arise in the semiconductor development and manufacturing process by utilizing AI techniques. The solution for protection can range from reactive to proactive techniques viz. creating countermeasures at hardware as well as software level that actively resides inside the chip or the system to be protected, as well as evaluation methodologies that can be used to determine if any perturbation activity as fault injection or presence of a Hardware Trojan (HT) persists in a fabricated chip or chip batches. This topic is very timely since normalization in this respect is on-going (see e.g., the ISO/IEC DTR 5891.2<sup>1</sup>: Information security, cybersecurity and privacy protection – Hardware monitoring technology for hardware security assessment, which is in the draft technical report stage [1]).

<sup>&</sup>lt;sup>1</sup>This upcoming standard discusses hardware monitoring aspects for security at the hardware layer in the postsilicon phase during runtime.

**Contributions.** This thesis focuses on the various challenges associated with the protection of embedded and integrated devices against physical, internal and network originating threats. To this end, three separate axes of work have been conducted:

The fist axis targets Fault Injection physical attacks at the chip level and the objective is to devise a detection methodology that can detect such attacks preemptively and report security incidents to the chip control to take remedial actions. For the first time it is demonstrated how aggregation of sensors can be used on-the-fly for abnormal conditions detection, with controlled false positive rate. This contribution is covered in the **chapter 3**.

The second work is concerning Hardware Trojans which is a serious practical concern and is an ever present danger in the current distributed development practice in the semiconductor industry. This work focuses on detecting the presence of extremely stealthy Hardware Trojans in the design, that are never triggered throughout the data acquisition process, with the help of Machine Learning modelling of the ElectroMagnetic (EM) emanation data collected from the active chip. It is shown that even tiny Hardware Trojans can be efficiently detected by this method, which leverages multidimensional (spatial & temporal) measurements. **Chapter 4** corresponds to the contributions in this axis of the thesis work.

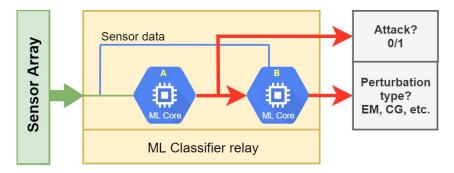

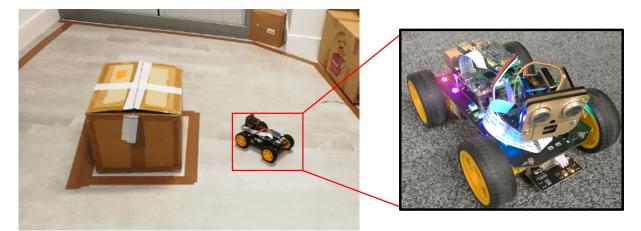

The third axis of contribution is focused on threats in an Internet-of-Things (IoT) infrastructure. The V2X (Vehicle to anything) scenario is considered where an emulated vehicle is constructed with sensing capabilities and through an IoT communication protocol it is connected to a Server running some applications. The emulated vehicle consists of a sensing unit and detection units running on Machine Learning engines that are trained to detect sensor and network based intrusions or perturbations. Such system is shown to work very reliably even with modest computation power. **Chapter 5** presents the contributions from this axis of the thesis work.

### Chapter 2 – Related works

This chapter includes a survey of different modalities in which embedded system security is assessed and averted in the state-of-the-art. Additionally, how machine learning techniques are used towards security at the hardware level is also discussed. All the topics involved in this thesis manuscript are studied for their security implications in embedded systems which include:

- · Fault injection attacks

- Hardware Trojans

- Intrusion Detection Systems

- · Edge to cloud systems

- · AI and ML for chip and device security

- · Communication protocols in IoT

- · IoT related standards and regulations (e.g., [1])

With the growing use of AI in multiple applications including security analysis as well as, in some cases, security applications (with the major example being in the automotive industry for smart car navigation systems), it has become necessary to have standardized approaches to creating AI driven software or hardware applications with the aspect of security built-in the systems. There are already semiconductor manufacturers of AI based ASICs that are solely made for the purpose of Advanced Driver Assistance Systems (ADAS) or Automated Driving Systems (ADS) with AI powered image detection and processing blocks integrated within the System-on-Chip (SoC). The security certification aspects of such use cases solely rely on the existing security standards and schemes that are out of date compared to the parameters that come into play within the security boundary when such AI applications are included. The lack of standardized methodology is also the reason why the trust in AI is difficult to achieve. Additionally, it is also seemingly difficult to create a generalized framework for developing AI based security applications. To that end many certification bodies are working towards standardizing the use of AI in various applications and domains. A detailed aspect of all such efforts of AI standardization shall also be detailed in this thesis chapter.

### Chapter 3 – External Fault Injection detection

The exposed devices in insecure locations are vulnerable to perturbation attacks that account for high severity in terms of threats arising from an adversary. These attacks comprising of Fault Injections (FI) in the chip or device through various means such as Electro-Magnetic (EMFI), Clock-Glitch (CGFI), voltage, temperature, Laser (LFI), Focused Ion-Beam (FIB), etc. are invasive and have the potential to disrupt the system as well as, with some precision. They allow the adversary to perturb specific areas within the chip that can allow unauthorized control switching such as granting access without authentication, authentication, or security bypass and in most cases lead to Denial-of-Service (DoS), all of which are catastrophic for the system when amplified as Distributed DoS on device classes. Indeed, these identified threats are relevant to the security critical applications such as the ones described in the general section. Therefore, through the introduction of multimodal attack detection IPs (such as digital sensors) within the design and a machine learning based inference unit within the chip, it is proposed to create a solution of interconnected system of perturbation sensitive sensors with an aggregation unit collating the inputs from all the digital sensors to feed an integrated AI module capable of predicting the presence of any FI related threats is proposed. The solution is tested experimentally with real data (captured from experimental benches) to prove the efficiency of such an approach.

### Chapter 4 – Insider (Hardware Trojan) detection

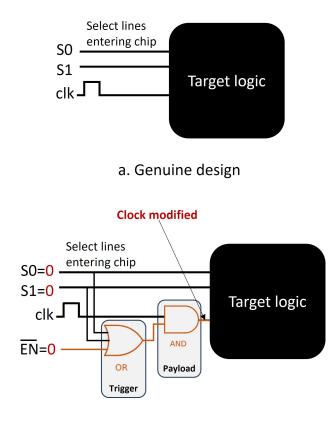

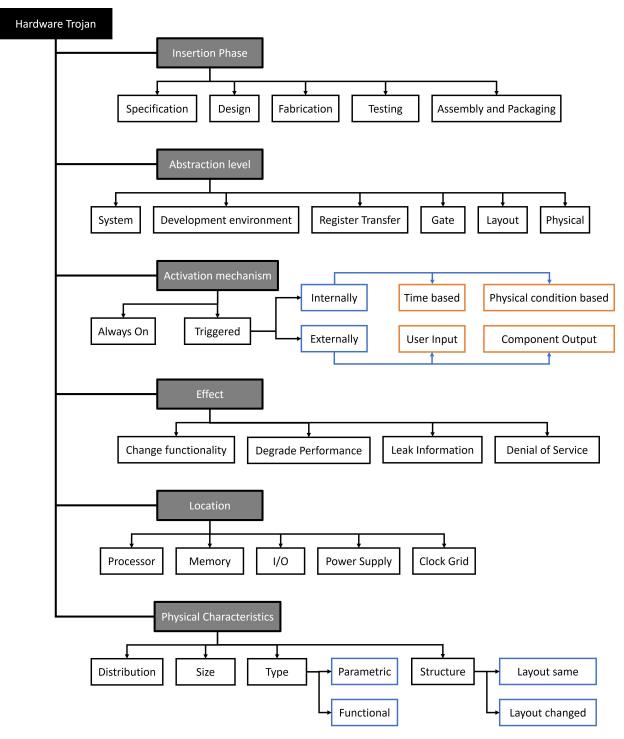

Another area of perturbation of system behavior to maliciously achieve a targeted function, usually placed discretely by malicious third parties with an automated or manual trigger mechanism integrated in the design, which is originally unintended from the system functionality point of view, is the presence of internal system threats popularly known as Hardware Trojans (HT). The detection of HTs becomes more difficult (cf. ISO/IEC TR 5891) since the insertion can take place even in the last phases of the semiconductor manufacturing process. Thereby, in this work a ML based HT detection mechanism is proposed to detect different types of Trojans such as in the Register Transfer Level (RTL) or the Place and Route (P&R) level. The data

collected is through Electro-Magnetic (EM) cartography of a chip containing the Trojans (real data) and through precise ML engineering and classification it is shown that it is possible to identify the presence of even a tiny (down to 0.1%) HT with this verification process. Several methodologies are applied and tested on the large data sets and the effectiveness in detecting the HTs are demonstrated through experimented inferences and compared with existing state-of-the-art research.

### Chapter 5 – Intrusion Detection System

Another aspect of external perturbation is at the device level by conflicting the system stability through adversarial attacks. A popular use-case is autonomous smart cars in the V2X (Vehicle to anything) infrastructure (see risk analysis in Common Criteria (CC)[2] Protection Profile PP0114 [3]). To this end, it is highly critical to secure such devices as human lives are involved in case of adversary induced perturbation such as failure of braking systems, unwanted acceleration or stopping, etc. The functional safety aspect of automotive development indeed tackles failures such as through ISO 26262 standard. However, the cybersecurity aspect is still relied upon classical security mechanisms and a strong cybersecurity culture in automotive development. Therefore, a more advanced form of an intelligent system is required such as the one proposed in this thesis through an AI capable smart IDS. The IDS proposed is a parallel architecture of AI engines that are trained on real data collected from a miniature smart car model with built-in sensor mechanisms mimicking a real smart-car. The AI based IDS is capable of detecting perturbations received at the sensor level as well as intrusions from the network level. To extend the security concept beyond V2X to the whole IoT segment, the smart car is connected to a server that runs a monitoring and a firmware upgrade application through a standard IoT protocol. Through many data collection sessions of both nominal as well as perturbed conditions the AI models are trained and are shown to achieve good results in terms of detection accuracy.

# Résumé de la thèse

### Chapitre 1 – Introduction

L'industrie moderne des semi-conducteurs offre à une entreprise de semi-conducteurs la flexibilité de développer toutes les parties d'un dispositif en interne en permettant l'externalisation des tâches pour lesquelles elle ne possède pas l'expertise, telles que la fabrication et l'emballage. La tendance récente pour les fabricants de puces est de développer la conception et de produire le RTL (abbréviation de "Register Transfer Level") synthétisable qui est ensuite transmis à une industrie partenaire pour les services de fabrication, de conditionnement et de test. Cela a créé un vaste réseau d'externalisation dans l'ensemble du secteur, où différentes entreprises se concentrent sur différentes étapes du flux de conception VLSI (abbréviation de "Very Large Scale Integration"). Cela étant dit, cette infrastructure distribuée a deux conséquences majeures, à savoir. a) le taux de production est considérablement augmenté et le temps de traitement est fortement réduit car plusieurs étapes peuvent être effectuées en parallèle, et b) la vulnérabilité de falsification de la conception est considérablement accrue car la plupart du traitement et les différentes pièces proviennent ou sont modifiées dans des établissements tiers qui peuvent être considérés comme non sécurisés. D'autre part nous constatons actuellement une augmentation du nombre d'appareils connectés qui utilisent des circuits VLSI.

Cette modalité de développement et de production a augmenté la productivité des appareils connectés, mais a en même temps permis une augmentation de menaces potentielles associées au développement et à la production distribués, telles que les chevaux de Troie matériels (HT, abbréviation de "Hardware Trojans") ou la surproduction illégale. Pour améliorer la sécurité face à ces menaces croissantes, il est essentiel de disposer de contre-mesures robustes et/ou d'un mécanisme de détection de menaces solides notamment en termes de précision de détection. Il faut donc rechercher des solutions efficaces pour la protection et l'évaluation mais aussi des solutions de faible complexité afin de réduire les coûts de conception sans impacter le temps de production. Comme la quantité de données traitées est élevée, la détection devrait avoir une grande précision et fiabilité guelque soit le type et la taille des données. Pour satisfaire cette exigence, une solution envisagée est l'emploi d'intelligence artificielle (IA), plus précisément l'apprentissage automatique (ML, abbréviation de "Machine Learning"). Dans ce travail de thèse, je propose différentes solutions pour relever les différents défis qui se posent dans le processus de développement et de fabrication des semi-conducteurs en utilisant des techniques d'IA. La solution de protection peut utiliser des techniques réactives (détection) ou proactives (prévention). Les techniques de prévention reposent sur le rajoût de contre-mesures au niveau matériel ou logiciel offrant une résilience à l'intérieur de la puce ou du système à protéger. Les techniques de détection nécessitent des méthodologies d'évaluation qui peuvent être utilisées pour déterminer si une activité de perturbation, telle qu'une injection de fautes (détecton à la volée) ou la présence d'un cheval de Troie matériel (détection à la volée ou avant utilisation) a lieu dans une puce. Ce sujet est d'actualité puisque la normalisation à cet égard est en cours (voir par exemple, la norme ISO/IEC DTR 5891.2<sup>2</sup> : Sécurité de l'information, cybersécurité et protection de la vie privée – Technologie de surveillance du matériel pour l'évaluation de la sécurité du matériel, qui est au stade du projet de rapport technique [1]).

**Contributions.** Cette thèse se concentre sur les différents défis associés à la protection des appareils embarqués et intégrés contre les menaces physiques, internes et provenant du réseau. Pour cela, trois axes de travail distincts ont été menés :

Le premier axe cible les attaques physiques par injection de fautes (FI, abbréviation de "Fault Injection") au niveau de la puce et l'objectif est de concevoir une méthodologie de détection capable de détecter de telles attaques de manière préventive et de signaler les incidents de sécurité au contrôle de la puce pour prendre des mesures correctives. Pour la première fois, il est démontré comment l'agrégation de capteurs peut être utilisée à la volée pour la détection de conditions anormales, avec un taux de faux positifs contrôlé. Cette contribution est couverte dans le **chapitre 3**.

Le deuxième travail concerne les HT, qui constituent un problème pratique sérieux et un danger toujours présent dans les pratiques actuelles de développement distribué dans l'industrie des semi-conducteurs. Ce travail se concentre sur la détection de la présence de chevaux de Troie matériels extrêmement furtifs dans la conception, qui ne sont jamais déclenchés tout au long du processus d'acquisition de données, à l'aide d'une modélisation d'apprentissage automatique des données d'émanation électromagnétique (EM) collectées à partir de la puce active. Il est démontré que même les plus petits chevaux de Troie matériels peuvent être détectés efficacement par cette méthode, qui exploite des mesures multidimensionnelles (spatiales et temporelles). **Chapitre 4** correspond aux contributions dans cet axe du travail de thèse.

Le troisième axe de contribution est axé sur les menaces dans une infrastructure Internet des Objets (IoT, abbréviation de "Internet-of-Things"). Le scénario V2X (abbréviation de "Vehicle to everything") est envisagé dans lequel un véhicule émulé est construit avec des capacités de détection et via un protocole de communication IoT, il est connecté à un serveur exécutant certaines applications. Le véhicule émulé se compose d'une unité de détection et d'unités de détection fonctionnant sur des moteurs d'apprentissage automatique qui sont formés pour détecter les intrusions ou les perturbations basées sur les capteurs et le réseau. Il est démontré qu'un tel système fonctionne de manière très fiable, même avec une puissance de calcul modeste. **Chapitre 5** présente les contributions de cet axe du travail de thèse.

### Chapitre 2 – Œuvres liées

Ce chapitre comprend une étude des différentes modalités dans lesquelles la sécurité des systèmes embarqués est évaluée et pratiquée dans l'état de l'art. De plus, la manière dont les techniques d'apprentissage automatique sont utilisées pour la sécurité au niveau matériel est également abordée. Tous les sujets impliqués dans ce manuscrit de thèse sont étudiés pour leurs implications en matière de sécurité dans les systèmes embarqués, notamment :

<sup>&</sup>lt;sup>2</sup>Cette prochaine norme traite des aspects de surveillance du matériel pour la sécurité au niveau de la couche matérielle dans la phase post-silicium pendant l'exécution.

- Attaques par injection de fautes

- Chevaux de Troie matériels

- Systèmes de détection d'intrusion

- Systèmes Edge à Cloud

- · IA et ML pour la sécurité des puces et des appareils

- Protocoles de communication dans l'IoT

- Normes et réglementations liées à l'IoT (par example [1])

Avec l'utilisation croissante de l'IA dans de multiples applications, y compris l'analyse de sécurité ainsi que, dans certains cas, les applications de sécurité (le principal exemple étant dans l'industrie automobile pour les systèmes de navigation intelligents), il est devenu nécessaire d'avoir des approches standardisées pour créer de l'IA. applications logicielles ou matérielles pilotées avec l'aspect de sécurité intégré aux systèmes. Il existe déjà des fabricants de semiconducteurs d'ASIC basés sur l'IA qui sont uniquement conçus pour les systèmes avancés d'aide à la conduite (ADAS, abbréviation de "Advanced Driver Assistance Systems") ou les systèmes de conduite automatisée (ADS, abbréviation de "Automated Driving Systems") avec des blocs de détection et de traitement d'images alimentés par l'IA intégrés dans le système sur puce (SoC, abbréviation de "System-on-Chip"). Les aspects de certification de sécurité de tels cas d'utilisation reposent uniquement sur les normes et systèmes de sécurité existants qui sont obsolètes par rapport aux paramètres qui entrent en jeu dans les limites de sécurité lorsque de telles applications d'IA sont incluses. Le manque de méthodologie standardisée est également la raison pour laquelle la confiance dans l'IA est difficile à instaurer. De plus, il semble également difficile de créer un cadre généralisé pour développer des applications de sécurité basées sur l'IA. À cette fin, de nombreux organismes de certification s'efforcent de normaliser l'utilisation de l'IA dans diverses applications et domaines. Un aspect détaillé de tous ces efforts de normalisation de l'IA sera également détaillé dans ce chapitre de thèse.

### Chapitre 3 – Détection d'Injection de Fautes Externe

Les appareils exposés dans des emplacements non sécurisés sont vulnérables aux attaques de perturbation qui représentent une menace très puissantes pour retrouver un secret. Ces attaques comprennent des FI dans la puce ou le dispositif par divers moyens tels que le rayonnement électromagnétique (EMFI, abbréviation de "ElectroMagnetic Fault Injection"), le parasitage de l'horloge (CGFI, abbréviation de "Clock-Glitch Fault Injection"), la tension, la température, le laser (LFI, abbréviation de "Laser Fault Injection"), le faisceau d'ions focalisé (FIB, abbréviation de "Focused Ion-Beam"), etc. sont invasifs et peuvent potentiellement perturber le système, avec une certaine précision. Ils permettent à l'adversaire de perturber des zones spécifiques de la puce qui peuvent permettre une commutation de contrôle non autorisée, comme l'octroi d'un accès sans authentification, authentification ou contournement de sécurité, et conduisent dans la plupart des cas à un déni de service (DoS, abbréviation de "Denial-of-Service"), qui sont tous catastrophiques pour le système lorsqu'il est amplifié en tant que DoS distribué sur les classes d'appareils. En effet, ces menaces concernent les applications critiques pour la sécurité telles que celles décrites dans la section générale. Par conséquent, grâce à l'introduction de blocs de détection d'attaques multimodales (telles que des capteurs numériques) dans la conception, et l'ajoût d'une unité d'inférence basée sur l'apprentissage automatique au sein de la puce, il est proposé de créer une système interconnecté de capteurs sensibles aux perturbations avec une unité d'agrégation. Ce système permet la collecte des données de tous les capteurs numériques pour alimenter un module d'IA intégré capable de prédire la présence de toute menace liée à la FI. La solution est testée expérimentalement avec des données réelles (capturées sur des bancs expérimentaux) pour prouver l'efficacité d'une telle approche.

## Chapitre 4 – Détection d'initiés (chevaux de Troie matériels)

Les chevaux de Troie matériels (HT) permettent de perturber le comportement du système pour atteindre de manière malveillante une fonction ciblée, généralement. Le HT est placé discrètement par des tiers malveillants avec un mécanisme de déclenchement automatisé ou manuel intégré dans la conception. La détection des HT devient plus difficile (cf. ISO/IEC TR 5891) puisque l'insertion peut avoir lieu même dans les dernières phases du processus de fabrication des semi-conducteurs. Ainsi, dans ce travail, un mécanisme de détection HT basé sur les techniques ML est proposé pour détecter différents types de chevaux de Troie, comme au niveau RTL ou P&R. Les données collectées proviennent de la cartographie EM d'une puce contenant les chevaux de Troie (données réelles) et grâce à une ingénierie et une classification ML précises, il est démontré qu'il est possible d'identifier la présence même d'un infime (jusqu'à 0,1%) HT avec ce processus de vérification. Plusieurs méthodologies sont appliquées et testées sur de grands ensembles de données et l'efficacité de la détection des HT est démontrée par des inférences expérimentées et comparée aux recherches de pointe existantes.

## Chapitre 5 – Système de Détection d'Intrusion

Un autre aspect de la perturbation externe est de compromettre la stabilité d'un système interconnecté par le biais d'attaques contradictoires. Un cas d'utilisation populaire est celui des voitures intelligentes autonomes dans l'infrastructure V2X (voir l'analyse des risques dans CC[2] Profil de protection PP0114 [3]). À cette fin, il est obligatoire de sécuriser ces dispositifs, car des vies humaines sont impliquées en cas de perturbation induite par un adversaire, telle qu'une défaillance des systèmes de freinage, une accélération ou un arrêt non désiré, etc. L'aspect sécurité fonctionnelle du développement automobile s'attaque en effet aux défaillances telles que Norme ISO 26262. La voiture étant un élement d'un système interconnecté, il est devenu indispensable de transposer la culture de "cybersécurité" dans ce domaine. Par exemple, une forme de sécurisation du système autonome peut reposer sur un système de détection d'intrusion (IDS) intelligent à base d'IA comme proposé dans cette thèse. L'IDS proposé est une architecture parallèle de moteurs d'IA entraînés sur des données réelles collectées à partir d'un modèle de voiture intelligente miniature avec des mécanismes de capteurs intégrés imitant une véritable voiture intelligente. L'IDS basé sur l'IA est capable de détecter les perturbations reçues au niveau des capteurs ainsi que les intrusions au niveau du réseau. Pour étendre le concept de sécurité au-delà du V2X à l'ensemble du segment IoT, la voiture intelligente est connectée à un serveur qui exécute une application de surveillance et de mise à niveau du micrologiciel via un protocole loT standard. Grâce à de nombreuses sessions de collecte

de données dans des conditions nominales et perturbées, les modèles d'IA sont entraînés et obtiennent de bons résultats en termes de précision de détection.

## Acronyms

ADAS Advanced Driver Assistance Systems. 30 ADS Automated Driving Systems. 30 AES Advanced Encryption Standard. 11, 18, 29 AI Artificial Intelligence. 7, 29-32, 65 ANN Artificial Neural Networks. 22, 24 API Application Programming Interface. 22, 70 ARP Address Resolution Protocol. 67, 68, 72 ASIC Application Specific Integrated Circuit. 16, 24, 66 CAD Computer Aided Design. 16 CC Common Criteria. 11, 30, XIV, XVIII **CEM** Common Evaluation Methodology. 11 CGFI Clock-Glitch Fault Injection. 6, 12, 33, 36, 42-46, 49, 67, 78, IV **CNN** Convolutional Neural Networks. 22 CoAP Constrained Application Protocol. 21, 65, 70, 75, 79 CPU Central Processing Unit. 16, 20, 68 CSP Critical Security Parameter. 1, 16, 20 **CWE** Common Weakness Enumeration. 10 **DFA** Differential Fault Analysis. 67 **DNN** Deep Neural Networks. 22, 53 DoS Denial of Service. 2, 5, 12, 16, 67, 72, 73, 75, 78, XXVI DS Digital Sensor. 34–36, 39–41, 43, 45–49, XXV DTC Decision Tree Classifier. 53, 59, 61 **DTLS** Datagram Transport Layer Security. 21

Acronyms

- DUT Design-Under-Test. 34, 36, 46, 50, 53, 54, 64

- **DVFS** Dynamic Voltage and Frequency Scaling. 10

- EDA Electronic Design Automation. 4, 14, 16, 46

- EE Elliptical Envelope. 54, 62

- EM Electro-Magnetic. 18, 29, 34, 35, 41, 43, 55–57, 59, 61, 64, 78, XIV, XVIII, XXV, XXVI

- EMFI Electro-Magnetic Fault Injection. 6, 11, 12, 33–37, 40–46, 49, 52, 55, 67, 78, IV, XXV

- FBBI Forward Body Biasing Injection. 6

- FFT Fast Fourier Transform. 70

- FIA Fault Injection Attacks. 10, 20, 27, 34–37, 39, 41–46, 48–50, 67, 78–80, XXV

- FIB Focused Ion Beam. 6, 30

- FPGA Field Programmable Gate Array. 16, 18, 29, 34, 46, 48, 54–56, 59

- FSM Finite State Machine. 22

- GNBC Gaussian Naive Bayes Classifier. 22, 37, 38, 40-42, XXV

- GPU Graphics Processing Unit. 24

- HDL Hardware Descriptive Language. 16, 47, 56

- HIDS Host-Based Intrusion Detection System. 18, 65, 70, 74, 75, XXVI

- HLS High-Level Synthesis. 33, 46-48

- HSM Hardware Security Module. 10

- HT Hardware Trojan. 4, 7, 12–16, 28, 29, 51–54, 58–64, 78–80, III, IV, XXV, XXVI

- I2C Inter-Integrated Circuit. 69

- IAM Identity Access Management. 21

- IC Integrated Circuit. 4, 11

- ICMP Internet Control Message Protocol. 70

- IDS Intrusion Detection System. 6, 18, 29, 65–71, 74, 75, 79, III, XXVI

- IF Isolation-Forest. 54, 62, 70

- **IoT** Internet of Things. 2, 7, 18, 65, 71, 75, 78, 79, III, XXVI

- IP Internet Protocol. 67

- IR Infra-Red. 69

#### Acronyms

- iSE Integrated Secure Element. 1, 20

- LDR Light-Dependent Resistor. 69

- LFI Laser Fault Injection. 6, 12, 67

- LOF Local Outlier Factor. 54, 62

- LR Logistic Regression. 22

- LRC Logistic Regression Classifier. 37, 38, 59, 61

- LSTM Long Short-Term Memory. 79

- LwM2M Light-weight Machine-to-Machine. 21

- MAC Media Access Control. 67, 68

- MCU Micro-Controller Unit. 20, 66, 75

- MDP Markov Decision Process. 25

- MIMT Man-in-the-Middle. 67

- **ML** Machine Learning. 1, 5–7, 18, 22–31, 33, 34, 36–41, 43, 45–47, 49, 52, 54, 58–66, 69–71, 75, 77–80, III, IV, XXV, XXVI

- MLP Multi-Layered Perceptron. 37, 38, 40, 52, 53, 59, 61, XXV

- **MPFI** Micro-Probing Fault Injection. 6

- MPU Micro-Processor Unit. 20

- MQTT Message Queuing Telemetry Transport. 21

- NIDS Network-Based Intrusion Detection System. 18, 65, 69, 70, 72, 73, 75, XXVI

- NIST National Institute of Standards and Technology. 30

- NN Nearest Neighbor. 31, 38, 53, 59, 61

- **NVM** Non-Volatile Memory. 1

- **OEM** Original Equipment Manufacturer. 5, 16

- OMP Orthogonal Matching Pursuit. 22

- **OS** Operating System. 7, 21, 66, 68, 75, 79

- OSI Open System Interconnection. 21

- P&R Place and Route. 4, 16, 51, 56, XIII, XVIII

- PCA Principle Component Analysis. 27, 70

- PPA Performance, Power and Area. 10

- RAM Random Access Memory. 47

- RBF Radial Basis Function. 53, 54

- RO Ring Oscillator. 29

- RSA Rivest-Shamir-Adleman. 11

- RTL Register Transfer Level. 14, 28, 47, 51, 80, XIII, XVIII

- SCA Side-Channel Analysis. 6, 20

- SCR Smart-car Robot. 66, 68, 69, 74, XXVI

- SE Secure Element. 20

- SFR Security Functional Requirement. 4

- SoC System-on-Chip. 3, 10, 20, 33, 65

- SQL Structured Query Language. 22

- SVM Support Vector Machines. 18, 22, 29, 37, 38, 52-54, 59, 61, 62

- TCP Transmission Control Protocol. 72, 75

- TCP/IP Transmission Control Protocol/Internet Protocol. 68

- TEE Trusted Execution Environment. 1, 10, 20

- TFI Temperature Fault Injection. 6

- TLS Transport Layer Security. 21

- **TOE** Target of Evaluation. 12, 30

- TPM Trusted Platform Module. 20

- TPU Tensor Processing Unit. 25

- USS Ultra-Sonic sensor Spoofing. 74, 75

- V2X Vehicle-to-Anything. 65, 66, 68, 71, 79, XXVI

- VGFI Voltage-Glitch Fault Injection. 6

- WLAN Wireless Local Area Network. 69

- XSS Cross-Site Scripting. 22

# **List of Figures**

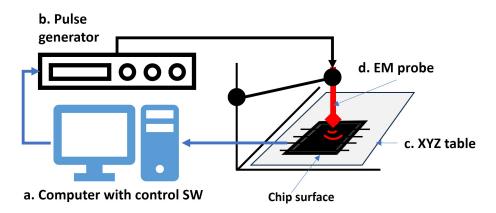

| 2.1 A typical EMFI setup                                                           |                                                                                                                                                                                                                                                                                       | 11 |

|------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 An example of an HT inf                                                        | ected design with manual trigger                                                                                                                                                                                                                                                      | 13 |

| 2.3 Taxonomy of HTs                                                                |                                                                                                                                                                                                                                                                                       | 15 |

| • •                                                                                | sertions within the design at different levels of semicon-                                                                                                                                                                                                                            | 17 |

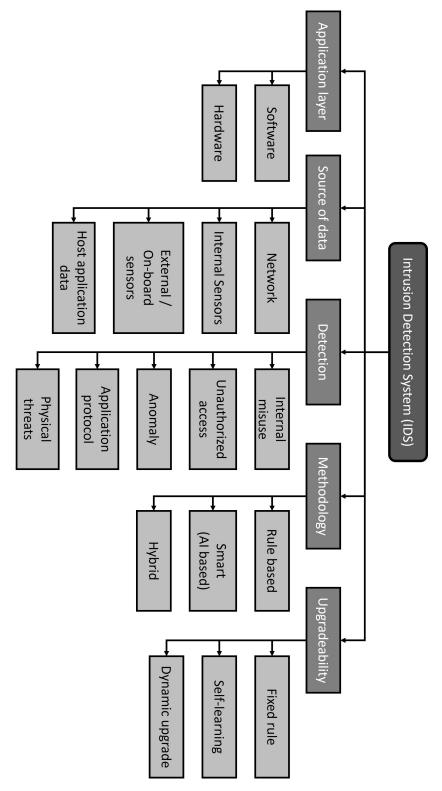

| 2.5 Different forms of Intrusi                                                     | on Detection Systems                                                                                                                                                                                                                                                                  | 19 |

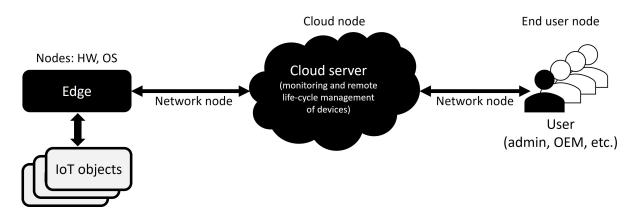

| 2.6 The main nodes and act                                                         | ors in a typical Edge-to-Cloud                                                                                                                                                                                                                                                        | 20 |

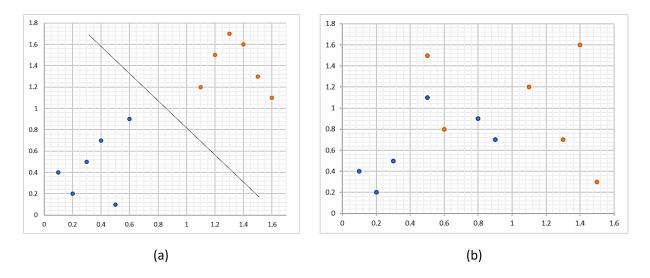

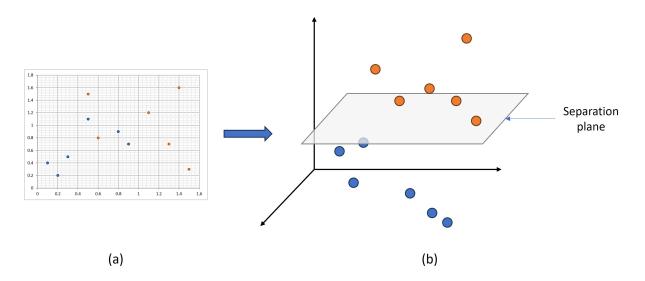

| •                                                                                  | d non linear data with separation. (a) linearly separable parable data                                                                                                                                                                                                                | 23 |

| linearly in two dimension                                                          | near separation. (a) Samples could not be separated ns (b) taking non-linearly separable data into higher di-                                                                                                                                                                         |    |

| mension and separating                                                             |                                                                                                                                                                                                                                                                                       | 23 |

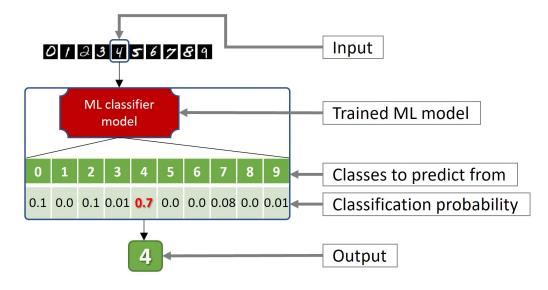

|                                                                                    | ification for handwritten digit classification                                                                                                                                                                                                                                        | 24 |

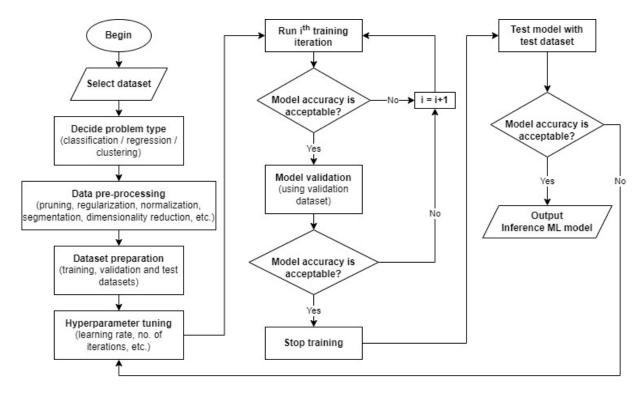

| 2.10 A typical Machine Learn                                                       | ing model training flow                                                                                                                                                                                                                                                               | 26 |

| 3.1 Experimental Setup for I                                                       | EMFI data acquisition                                                                                                                                                                                                                                                                 | 35 |

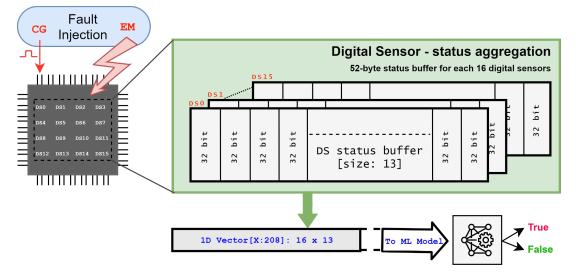

|                                                                                    | sition from multiple sensors (sensor aggregation) for EM and dimension pre-processing for ML algorithms                                                                                                                                                                               | 37 |

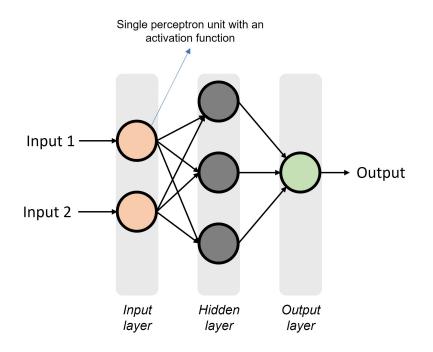

| 3.3 An example MLP                                                                 |                                                                                                                                                                                                                                                                                       | 40 |

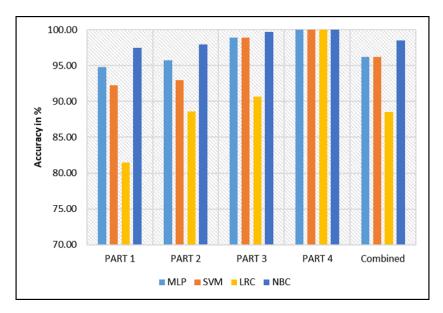

| states over four differen<br>the four different parts of<br>data merged together a | n as accuracy in predicting EM Fault Injection from DS<br>t ML methods. Each method is tested separately over<br>f EMFI dataset, as well as over the combined dataset (all<br>s one and randomized). Naive Bayes Classifier (NBC)<br>ods.                                             | 41 |

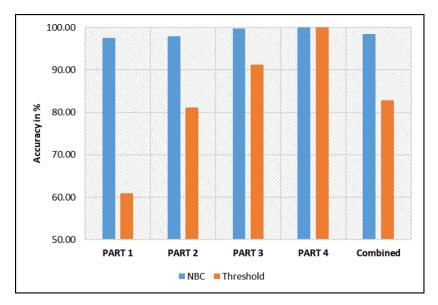

| states, between GNBC a there is minimal differen dataset, the accuracy of          | n in accuracy of predicting EM FIA, from aggregated DS<br>and Threshold based method on the EMFI dataset. While<br>ace in accuracy for the GNBC over different parts of the<br>threshold method is significantly affected and is always<br>at of the linear classification algorithm. | 41 |

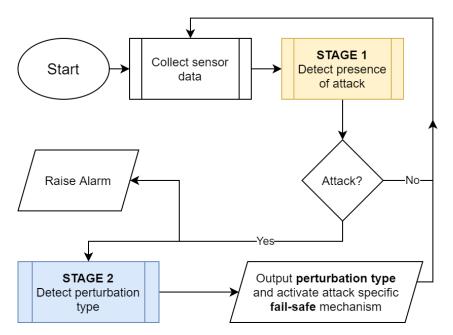

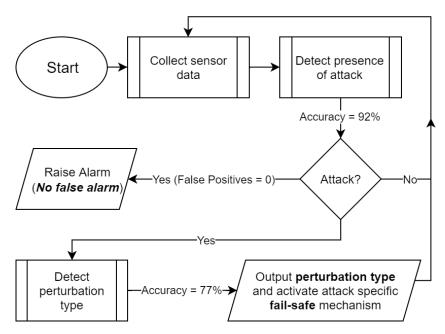

| 3.6 Two stage multi-source l                                                       | FIA detector                                                                                                                                                                                                                                                                          | 43 |

|                                                                                    | e detection framework's modalities of operation and con-                                                                                                                                                                                                                              | 43 |

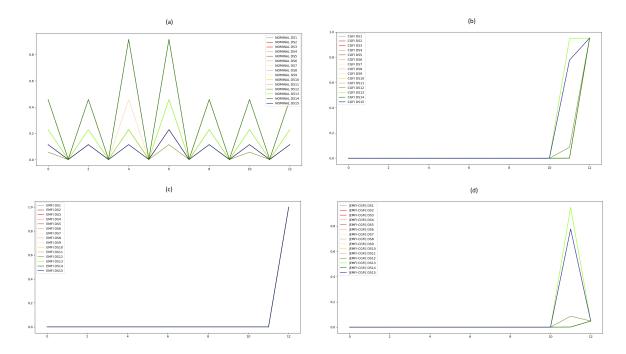

| 3.8                                    | Comparison between states of 16 DSs for nominal as well CGFI and EMFI cases.<br>The x-axis is the status buffer for each DS. (a) represents the nominal state of<br>the DSs when no injection is performed, (b) represents the state of the DSs<br>when CGFI is performed, (c) represents the state of the DSs when EMFI is per-<br>formed, and (d) represents the difference in values of the DSs from CGFI and<br>EMFI cases. It can be seen that some DSs behave similarly in both EMFI and<br>CGFI cases (for example DS12). In case of one DS based system, it would not<br>have been possible to differentiate between the type of attack. Therefore, sen-<br>sor aggregartion provides more features which can be utilized by a classification |                            |

|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 3.9<br>3.10                            | algorithm to differentiate between the type of attack                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 44<br>47<br>48             |

| 3.11                                   | A high level control and data flow diagram of the multi-sourced attack detection<br>with two-stage detector performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 40<br>49                   |

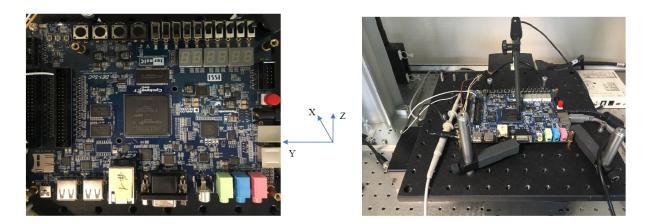

| 4.1                                    | (Left) Top view of Altera board oriented in the plate plan XY. (Right) EM Cartog-<br>raphy trace acquisition setup for HT detection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 56                         |

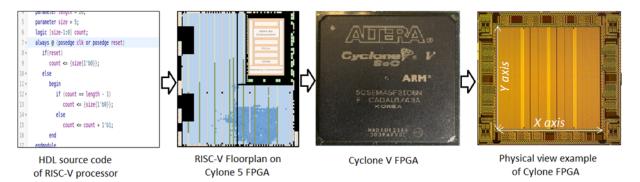

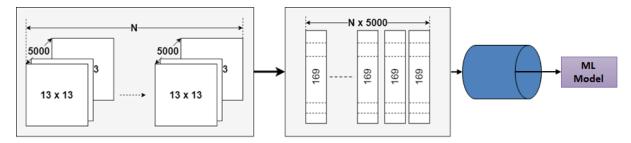

| 4.2<br>4.3                             | Cartography process overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 56<br>57                   |

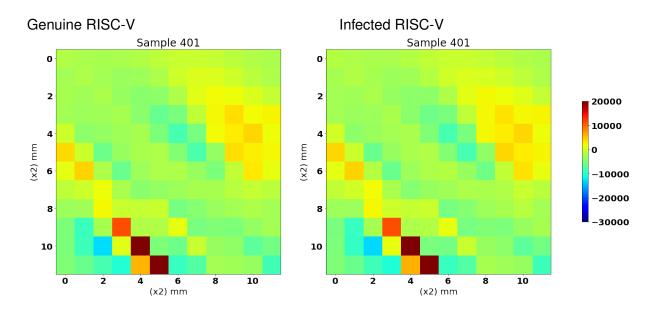

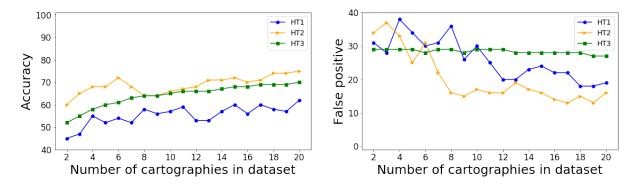

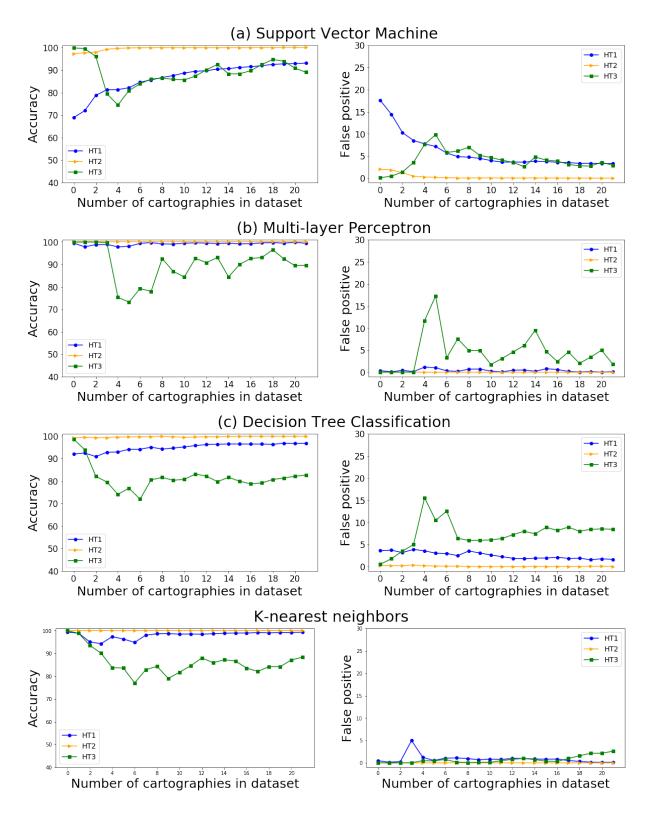

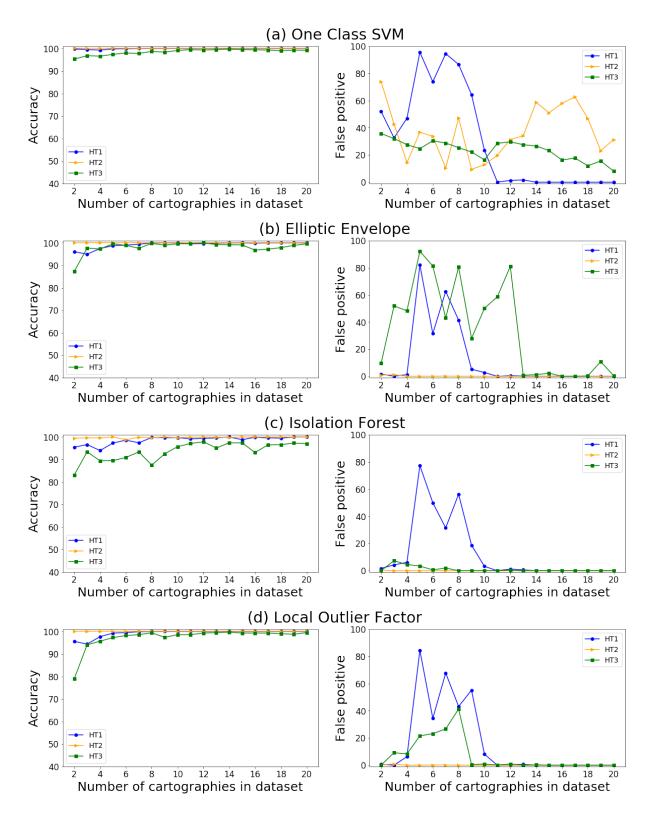

| 4.4<br>4.5<br>4.6<br>4.7<br>4.8        | Detection of HTs using T-test metric                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 57<br>58<br>59<br>60<br>63 |

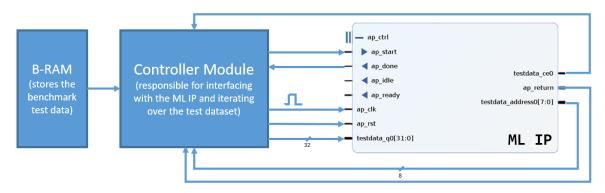

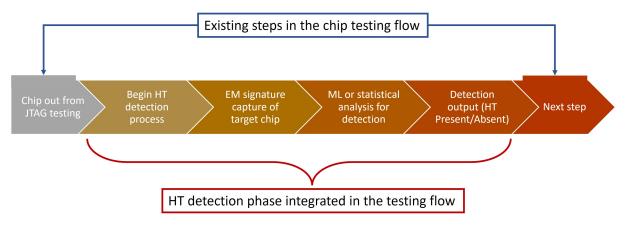

|                                        | flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 64                         |

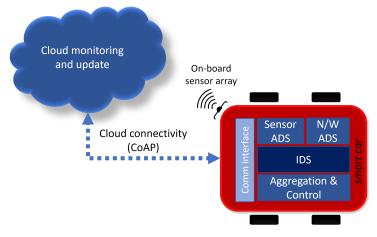

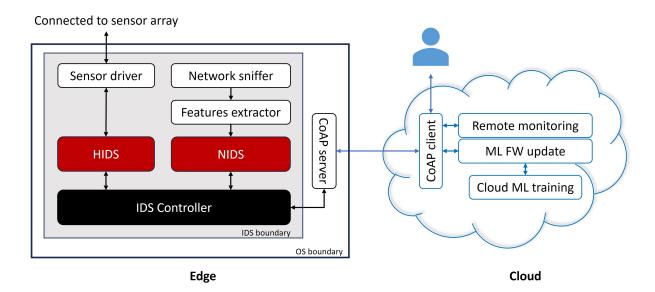

| 5.1<br>5.2                             | High level diagram of the presented V2X IoT emulated environment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 67                         |

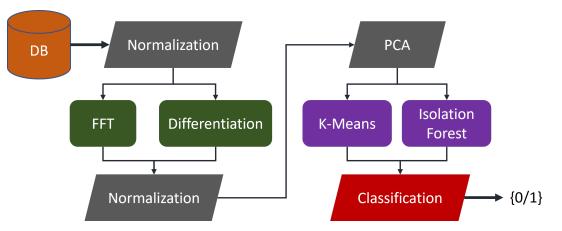

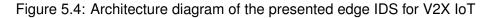

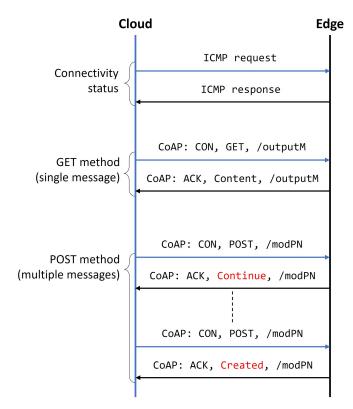

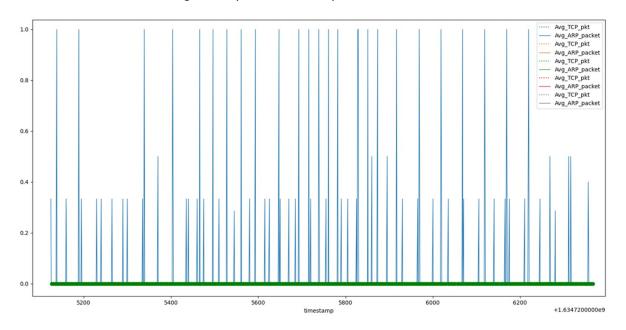

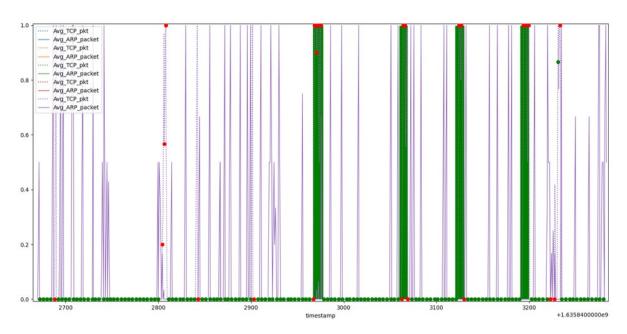

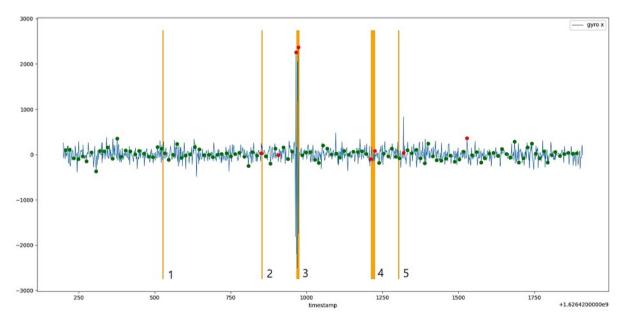

| 5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8 | and network communication units                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 73                         |

| 5.9                                    | tool                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 73<br>74                   |

| 6.1                                    | High level diagram of a circuit-delay characterization based ML HT detector IP $$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 80                         |

## **Chapter 1**

# Introduction

### Contents

| 1.1 | Context                                     | 1        |

|-----|---------------------------------------------|----------|

| 1.2 | Problem definition                          | 3        |

| 1.3 | External Fault Injection                    | <b>5</b> |

| 1.4 | Hardware Trojans                            | 6        |

| 1.5 | Intrusion Detection System                  | 6        |

| 1.6 | Countermeasures using Machine Learning (ML) | 6        |

| 1.7 | Objectives                                  | 7        |

### 1.1 Context

Security and privacy have been a big issue from the time the internet was invented. Since then the concerns have only grown, as attested by new regulations (e.g., NIST SP 800-193 [4] and the forthcoming EU Cyber Resilience Act [5]) and the increasing need of sovereignty in the silicon market. As technology becomes more sophisticated, more methods to fault such systems appear through all the three modalities of actors i.e. white-hat, black-hat and gray-hat originating from state-of-the-art vulnerability analysis research, security testings, and adversarial means. To that end, many cryptographic algorithms and protocols have been designed and globally accepted through standards organizations to tackle cybersecurity threats and issues in various scenarios, such as:

- Critical Security Parameter (CSP) storage and transfer in/from embedded or Integrated Secure Element (iSE) or Trusted Execution Environment (TEE) to the other parts of the chip

- · Critical and sensitive memory area isolation

- · Secure booting of security critical systems

- Secure retrieval and storage of data in and from Non-Volatile Memory (NVM) and other external memories

- Intra-device communication

- Inter-device communication

- Network communication

- Private area network (corporate and public)

- · Device to edge/server

- · Heterogenous protocol communication

- Peer to peer communication

- Industrial Internet of Things (IoT) communication

- · Connected smart healthcare devices to communicate medical data

- and so on.

Not surprisingly, many of these transactions are highly confidential due to their nature, such as that of governmental organizations, critical infrastructure (gas, power grid, smart city, satellite, maritime, etc.), state and private owned agencies for public service, healthcare, etc. and therefore, requires high grade security infrastructure for information interchange and operation.

While thinking of security the most important steps are to identify the assets involved and then the identification of attack surfaces and the attack scenarios in which the likelihood of any threat is theorized. For any connected device systems, the first point of infraction is the device itself which are in-field and highly accessible to any public user or adversary. While the most import aspects of security involve Confidentiality, Integrity and Authenticity (CIA) of the transacted data, there are other aspects involved that is highly critical for the device and chip manufacturers as well as OEMs, such as:

- Reverse engineering

- Compromising the device through malicious modifications in order to lead to Denial of Service (DoS)

- · Sniffing of confidential non-user data through back-doors

- · Injection of malware

This not only compromises a single device, but it has the potential to disrupt the entire production lot leading to decommissioning of the chips and or devices incurring heavy costs through chip re-spinning. This not only consumes time and currency, but also impacts heavily on the market trust of the company and therefore, has the potential to lead to the major damage impacts on the company such as Safety, Financial, Operational & Privacy (SFOP) [6]. Additionally, through reverse engineering attacks as well as overproduction due to outsourced production, counterfeit technologies disrupt global supply chain and market and this has become a serious concern to the market players.

### 1.2 Problem definition

As described in the context, the severity of cybersecurity threats and challenges are not limited to a particular use case and therefore there has been several attempts in security science to manage and mitigate them. As a result of the different challenges faced in the hardware, software, firmware, network and server levels, there are non-profit organizations such as *MITRE* [7, 8] that provide vulnerabilities and weakness database to properly categorize and maintain traceability of such threats for the purpose of improvement in security of the products and applications. However, by only maintaining the database of events and individual resolutions are not sufficient to encounter the threat origins and reduce the numbers and impacts caused by such threats. Therefore, in this thesis is targeted towards providing real-world impacting solutions to generalize as much as possible several security domains to anticipate and mitigate security threats through proactive and reactive approaches.

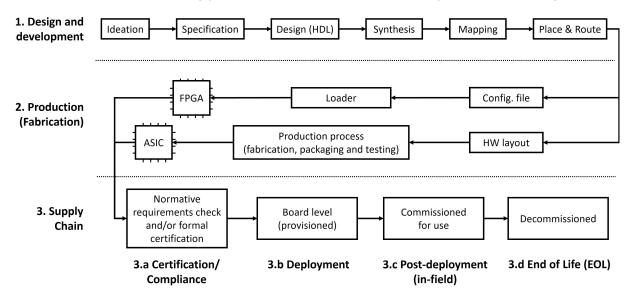

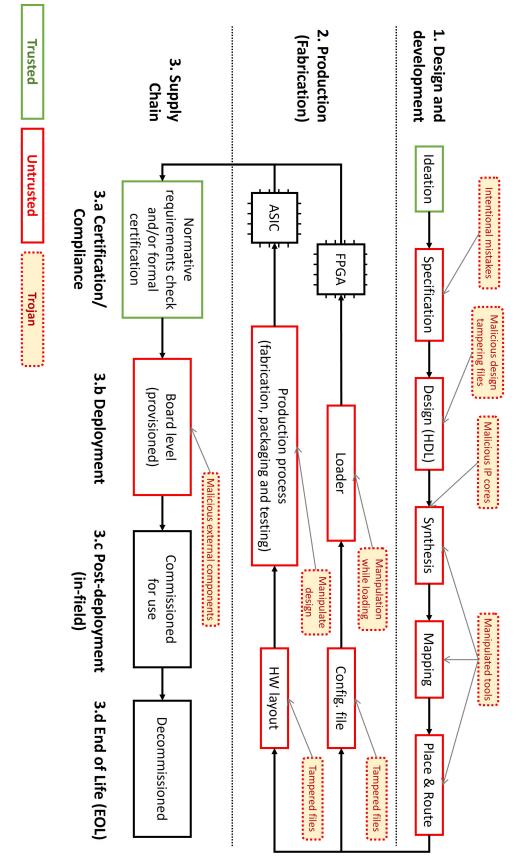

To provide a broader aspect of development of embedded or integrated systems, the entire life-cycle of semiconductor process should be studied. Figure 1.1 provides a high level scenario of the entire development, deployment and decommissioning life-cycle stages in the semiconductor manufacturing process to understand the threat impacts on each stages.

Figure 1.1: High level semiconductor development life-cycle

The Figure 1.1 presents three main phases of development:

- 1. Design and development

- 2. Production

- 3. Supply chain

Let us look at each of these phases individually to understand the various security challenges associated with the same. For the purpose of understanding the challenges within the development process, we shall dub the different phases with either "secure" or "insecure", depending upon their locality in the development process flow and the trust of the people involved. For instance, the "ideation" phase is within the System-on-Chip (SoC) developer's premises and therefore, would be considered as secure.

### 1.2.1 Design and development

The preliminary activity of any semiconductor product is the "idea" where the functional requirements of the product are envisioned. This process is performed by the principal people involved in the product development and therefore, this activity is considered to be secure.

The next step is to design the specification of the functional and Security Functional Requirement (SFR)s with the architecture of the chip or secure element. This step is also considered safe because the specifications directly map to the idea and all the people involved in the idea phase work closely to realize the specification and the architectural design. However, if security aspects are involved, there is a chance of human error to introduce vulnerabilities, even if security design principles are followed. Therefore, this step is slightly insecure with some chances of vulnerability or weakness introduction in the product.

The design and synthesis steps are very prone to cause security abnormalities in the product since in today's industry, Electronic Design Automation (EDA) tools are widely used that could be subject to bugs and vulnerabilities that may automatically introduce design flaws or vulnerabilities that could be exploited in later phases. Additionally, there is a slight chance of the presence of adversarial actors in this stage that might introduce stealthy malicious design modifications that evades the regular testing phases and could aid in the back-door related attacks in the later stages of the product life-cycle. Thereby, this step is slightly more insecure as compared to the previous step.

Finally, in the Place and Route (P&R) step, it is possible to easily introduce some additional logic, remove some wires or logic, or modify certain logical behaviour in the design to enable an adversary to exploit these changes to launch and attack or steal information.

### 1.2.2 Production

This phase is entirely considered insecure since all the steps involved are in an insecure location, usually outsourced to a third-party company or establishment, where it is exceedingly easy to introduce abnormalities in the design in the form of back-doors or Hardware Trojan (HT) circuits, as well as copy designs for counterfeiting, and even overproduction.

Therefore, it is a big challenge in today's semiconductor production process to ensure the integrity of the design and protect the interests of the Integrated Circuit (IC) vendors.

### 1.2.3 Supply-Chain

The go-to-market is facilitated through the supply chain. A crucial aspect that plays a significant role in the security of the product up to the production aspect with all the sites involved in the process is the certification and regulatory compliance verification. The compliance to normative requirements from standards and schemes may comprise in:

- · Verification of design and architecture

- Verification and review of the source code to ensure security principles are respected and required security assurance is reached through sufficient security mechanisms

- · Development process validation through gap analysis and audits

- Standard testing requirements for full coverage of all security features and protection of all assets within the sub-system

However, there are several levels of security levels and assurances and the requirement of higher levels is subject to the market needs, Original Equipment Manufacturer (OEM) and OEM's customer's requirements, as well as governmental regulations. And whilst this provide high assurance to identify potential vulnerabilities in the product, there scope is limited and it does not ensure a hundred percent security against these threats.

Therefore, to address these challenges, different strategies and solution to mitigate, with minor impacts on design, process, and cost, are presented in this thesis and the applicability is shown with real world use-cases while comparing the results to existing state-of-the-art solutions, and also paving a path to further improvements through research and development in this direction to unify the solution utilizing Machine Learning (ML) following compliance to security standards and regulations for secure product development. The major areas covered in this thesis are briefly described in the following sections of this chapter.

### 1.3 External Fault Injection

Perturbation attacks are one of the most disruptive physical attacks on any system or chip. The principle of any external fault injection attack also known as perturbation attacks relies in using external sources such as precisely calculated electro-magnetic or laser probes to inject external pulses to interfere with the internal signal transmission within the chip to interrupt or modify the internal signal behaviour. The intention behind such attacks could be to either:

- · Disrupt the functioning of the chip's subsystem

- · Perform precise modifications in the signals to change the information it carries

- Alter stored information within memory elements such as registers

Indeed, such attacks with a precise purpose are difficult by nature as locality of reference on the chip as well as timing are most crucial factors to launch such attacks. Therefore, not only the attacker needs to know about the target's architectural planning on the chip fabric, but also in the precise time which operation is happening in order to not miss the window of opportunity. This would also call for utilizing sophisticated instruments designed for precise experimentation purposes. The intent of such attacks could be characterized broadly as to:

- create DoS to shut down the system

- · bypass security checks

- · shut down the security protocol within the chip to facilitate coordinated attacks

- · allow unauthorized access to restricted areas on the chip

- alter original functionality of the logic to inject abnormalities that would create access points for adversarial attacks

- · retrieve sensitive information by modeling or profiling based on behaviour

- to demonstrate system weakness against such attacks (1)