# Side Channels in Web Browsers: applications to Security and Privacy

Thomas Rokicki

# ▶ To cite this version:

Thomas Rokicki. Side Channels in Web Browsers : applications to Security and Privacy. Web. INSA de Rennes, 2022. English. NNT : 2022ISAR0026 . tel-04513167

# HAL Id: tel-04513167 https://theses.hal.science/tel-04513167

Submitted on 20 Mar 2024

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

INSTITUT NATIONAL

# THÈSE DE DOCTORAT DE

# L'INSTITUT NATIONAL DES SCIENCES APPLIQUÉES RENNES

ÉCOLE DOCTORALE Nº 601 Mathématiques et Sciences et Technologies de l'Information et de la Communication Spécialité : Informatique

# Par **Thomas ROKICKI**

# Side Channels in Web Browsers : **Applications to Security and Privacy**

Thèse présentée et soutenue à IRISA, Rennes, le 29 Novembre 2022 Unité de recherche : UMR 6074

# **Rapporteurs avant soutenance :**

Jan REINEKE Professeur, Saarland University Billy Bob BRUMLEY Maître de Conférence, Tampere University

# **Composition du Jury :**

| Président :           | Lilian BOSSUET     | Professeur, Université Jean Monnet                    |

|-----------------------|--------------------|-------------------------------------------------------|

| Examinateur·rice·s :  | Jan REINEKE        | Professeur, Saarland University                       |

|                       | Billy Bob BRUMLEY  | Maître de Conférence, Tampere University              |

|                       | Veelasha MOONSAMY  | Chargée de Recherche, Ruhr University Bochum          |

|                       | Walter RUDAMETKIN  | Professeur, Université de Rennes 1                    |

| Dir. de thèse :       | Gildas AVOINE      | Professeur, INSA Rennes, CNRS, IRISA, France          |

| Encadrante de thèse : | Clémentine MAURICE | Chargée de Recherche, Univ Lille, CNRS, Inria, France |

|                       |                    |                                                       |

# Thèse de doctorat de Thomas ROKICKI

Thomas ROKICKI

Supervisor: Clémentine MAURICE

Co-supervisor: Gildas AVOINE

29/11/2022

# Résumé en Français

Les processeurs modernes sont des objets technologiques remarquablement optimisés. La vitesse de traitement étant le principal argument de vente des microprocesseurs, les fabricants se sont attachés à augmenter les performances des processeurs lors de leur développement, chaque année proposant de nouvelles générations dotées de meilleures caractéristiques que les précédentes.

Comme les progrès en matière de taille et de performances des semi-conducteurs ont ralenti dans l'ensemble de l'industrie au cours des dernières décennies, le simple fait d'ajouter des transistors à une puce est devenu insuffisant pour continuer l'augmentation régulière des performances. En réaction, les fabricants de processeurs se sont concentrés sur les optimisations microarchitecturales pour améliorer davantage les performances de génération en génération. Ces optimisations visent à augmenter la vitesse de traitement en proposant plus de parallélisme et en réduisant les temps de latence du matériel. Les processeurs multicœurs, les caches, ou l'exécution spéculative sont quelques exemples d'optimisations microarchitecturales. Chaque génération apporte des modifications à la microarchitecture, avec de plus en plus de caches ou d'unités d'exécutions dans un pipeline complexe. Par conception, ces optimisations visent à apporter plus de performance en accélérant l'exécution. Dans cette course à la performance, la sécurité de la microarchitecture tend à être négligée. En particulier, les effets secondaires de ces optimisations sur l'execution des calculs peuvent entraîner des fuites d'informations sur les valeurs secrètes utilisées par le système dans ce qu'on appelle des *canaux auxiliaires*.

En 1996, Paul Kocher [Koc96] a révélé que l'accélération dynamique apportée par les caches introduit des différences de temps d'exécution dans les implémentations à temps constant des algorithmes cryptographiques. Un utilisateur malveillant peut utiliser ces différences de temps microscopiques pour extraire des secrets telles que des clés privées. Cette découverte de la première attaque par minutage a ouvert la voie à un champ de recherche plus large sur les canaux auxiliaires.

Les canaux auxiliaires physiques ont fait l'objet de nombreuses recherches. Ils exploitent les effets secondaires physiques du processeur pendant le calcul pour en extraire les secrets des calculs délicats. Le premier canal auxiliaire physique exploitait la consommation d'énergie de la puce [KJJ99] pour attaquer les implémentations cryptographiques, mais de nombreuses sources de fuites physiques ont été étudiées, notamment les émissions acoustiques [ST04, GST14], les émissions électromagnétiques [RR01], les émissions optiques [SNK<sup>+</sup>12] ou encore la température [HS13]. Cependant, sauf exception notable [LKO<sup>+</sup>21], ces attaques nécessitent un accès physique au dispositif cible afin de mesurer les effets secondaires du calcul.

Par opposition, les *canaux auxiliaires microarchitecturaux* sont purement logiciels. Ils exploitent les optimisations basées sur les données des processeurs modernes pour déduire des informations privées. Depuis la première attaque temporelle de Kocher [Koc96], les caches ont été la source la plus étudiée de canaux auxiliaires microarchitecturaux, mais la recherche a prouvé que d'autres composants peuvent également être exploités pour monter des attaques par canal auxiliaire. Au cours de la dernière décennie, les chercheurs ont ciblés de nombreux composants microarchitecturaux, en ont compris le fonctionnement, et ont utilisé leur comportement pour en extraire des secrets. Les canaux auxiliaires ont été exploités, entre autres, à partir des prédicteurs de branchement [AKS07], de la DRAM [PGM<sup>+</sup>16], ou de la traduction d'adresses [GRBG18]. Les canaux auxiliaires microarchitecturaux ont été initialement mis en place pour faire fuir les données des implémentations cryptographiques, mais leur portée s'est considérablement élargie, avec notamment des attaques contre l'ASLR [HWH13], la communication entre machines virtuelles [MWS<sup>+</sup>17], la détection des frappes au clavier [GSM15] et la surveillance des utilisateurs [SKH<sup>+</sup>19]. Plus inquiétant encore, les canaux auxiliaires microarchitecturaux constituent une brique essentielle d'une nouvelle classe d'attaques microarchitecturales : les attaques par exécution transiente. Introduites en 2018 avec Spectre [KHF<sup>+</sup>19] et Meltdown [LSG<sup>+</sup>20], ces attaques utilisent les effets secondaires des instructions transientes, i.e., des instructions exécutées mais jamais engagées dans l'architecture, pour faire fuir des données à travers les barrières de sécurité logicielles et matérielles.

Les canaux auxiliaires microarchitecturaux exploitent le partage des composants matériels entre l'attaquant et la victime pour divulguer des informations. Par conséquent, ils ont un prérequis commun : l'attaquant doit exécuter du code sur la machine de la victime. Cette condition préalable essentielle restreint considérablement la surface d'attaque des canaux auxiliaires microarchitecturaux, car les utilisateurs se méfient de plus en plus des logiciels inconnus et ont tendance à ne télécharger des logiciels qu'à partir de sources fiables. Le risque de télécharger des logiciels malicieux est même réduit sur les plateformes mobiles, où les applications sont téléchargées à partir d'un magasin d'applications contrôlé par un éditeur, où chaque morceau de code est soigneusement analysé avant d'être publié. Les chercheurs ont étudié d'autres modèles d'attaques, où l'exécution du code sur le matériel de la victime est plus facile. Un attaquant peut attaquer la victime à distance, souvent via le web, et monter des attaques sur le cache à travers le réseau [BB05, KGA<sup>+</sup>20]. Schwarz et collab. [SSL<sup>+</sup>19] ont montré qu'il est possible de monter une attaque Spectre via le web. Les environnements d'informatique en nuage sont également une cible idéale pour les attaques microarchitecturales. Avec le développement de l'infrastructure en tant que service, les utilisateurs peuvent acheter des machines virtuelles ou des conteneurs fonctionnant sur des services comme Amazon EC2 ou OVHCloud. Toutefois, l'informatique en nuage n'est qu'une couche d'abstraction pour des serveurs colossaux. Bien qu'isolées d'un point de vue purement logiciel, les machines virtuelles contrôlées par différents utilisateurs peuvent être co-résidentes de processeur, c'est-à-dire partager un ou plusieurs processeurs. Un attaquant peut donc acheter de l'espace dans le nuage et monter des attaques sur toutes les machines co-résidentes. Ce scénario a été exploité pour détecter la co-résidence [ZJOR11], attaquer l'ASLR [BRPG15] ou monter des canaux à large bande passante entre deux machines virtuelles isolées [MWS<sup>+</sup>17].

En 2015, Oren et collab. [OKSK15] ont présenté une attaque sur le cache s'exécutant entièrement dans le navigateur. Ce modèle de menace augmente considérablement la surface d'attaque des canaux auxiliaires microarchitecturaux. Comme le web moderne est construit autour de pages web dynamiques et interactives, l'architecture des sites web est séparée en deux composants majeurs. Le côté serveur gère tous les calculs concernant le serveur, la base de données, l'authentification et l'envoi des informations de la page web aux utilisateurs. Le côté client gère la page web telle qu'elle s'affiche dans le navigateur de l'utilisateur. Les langages de script côté client, tels que JavaScript, sont responsables des composants interactifs des sites. Le code côté client est envoyé à l'utilisateur par le serveur et est exécuté dans le navigateur de l'utilisateur, et donc *est exécuté sur la machine de l'utilisateur*. Cela permet à un attaquant d'exécuter un script sur de nombreuses victimes différentes sans effort. Un utilisateur visitant un site web contrôlé par un attaquant téléchargera du code JavaScript et l'exécutera dans son navigateur sans s'en rendre compte, devenant ainsi potentiellement victime d'attaques microarchitecturales. Plus inquiétant encore, un attaquant peut acheter de l'espace publicitaire sur un site web légitime et exécuter le code JavaScript sur tous les utilisateurs qui voient la publicité.

Pour des raisons de sécurité, le code JavaScript s'exécute dans un environnement virtualisé sécurisé de type *bac à sable*. Ce bac à sable empêche l'accès aux adresses mémoire, aux instructions natives ou au système de fichiers. En outre, JavaScript est un langage abstrait de haut niveau, et il est difficile de quantifier son impact microarchitectural. Ces couches de sécurité et d'abstraction rendent difficile la mise en place de canaux auxiliaires microarchitecturaux à partir du bac à sable. Avec son attaque sur le cache en JavaScript, Oren et collab. [OKSK15] ont démontré la possibilité de provoquer et de mesurer des fuites de données microarchitecturales depuis le navigateur. Les caches ne sont pas le seul composant microarchitectural visé, et des chercheurs ont monté des attaques sur la DRAM [SMGM17] ou les unités à virgule flottante [AKM<sup>+</sup>15]. Bien qu'en général, les canaux auxiliaires JavaScript aient tendance à offrir moins de résolution aux attaquants, ils représentent une menace inquiétante pour la sécurité et la vie privée des utilisateurs. Les canaux auxiliaires microarchitecturaux ont été exploités dans le navigateur pour extraire des clés cryptographiques [GPTY18], surveiller les sites parcourus par un utilisateur [OKSK15, SKH<sup>+</sup>19], identifier les utilisateurs [LMD<sup>+</sup>22] ou communiquer en dehors du bac à sable [SMGM17].

Bien que les canaux auxiliaires basés sur le JavaScript aient été grandement étudiés, l'ensemble de leurs implications en matière de sécurité et de confidentialité n'est pas clair. En particulier, plusieurs zones grises subsistent :

- Q1 Depuis les premières attaques sur le cache basées sur le JavaScript, les navigateurs ont évolué, notamment en réaction aux attaques par minutage. Quel est l'état actuel des attaques par minutage dans sur les navigateurs et leurs contre-mesures ? En particulier, les contre-mesures basées sur les minuteurs sont une approche populaire. Cependant, ces mesures ont souvent été adoptées dans l'urgence. Quel est leur impact sur la sécurité et la confidentialité des navigateurs ?

- Q2 Quels autres composants sont vulnérables aux canaux auxiliaires depuis la sandbox JavaScript ?

- Q3 Quelles informations un attaquant peut-iel extraire de ces canaux auxiliaires ?

# Contributions

Cette thèse se concentre sur l'exploration partielle des réponses à ces questions. Les contributions de ce manuscrit sont divisées en deux catégories. La première direction de recherche consistait à redéfinir la portée des attaques par minutage en JavaScript. En particulier, nous avons étudié l'impact de contre-mesures répandues aux attaques par minutage : la suppression de l'accès aux minuteurs à haute résolution. La deuxième catégorie de contributions concerne un type spécifique de canal auxiliaire : la contention des ports du microprocesseur. Dans une première contribution, nous montrons comment, pour la première fois, nous avons implémenté la contention de port dans le bac à sable du navigateur. Dans une deuxième contribution, nous étendons le champ d'application de la contention de port pour changer complètement son modèle de menace. Nous montrons également comment cette nouvelle version du canal auxiliaire peut être utilisée à des fins d'identifications des navigateurs.

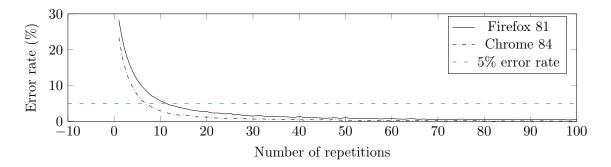

Évaluation méthodique des minuteurs JavaScript (Q1) En réaction à la menace croissante que représentent les attaques par minutage basées sur JavaScript, les développeurs de navigateurs ont proposé diverses contre-mesures. Au milieu de tous ces changements, il peut être difficile de suivre les différentes évolutions des navigateurs. En particulier, l'impact des contre-mesures actuelles sur les attaques décrites dans la littérature n'est pas clair.

Nous présentons l'évolution des attaques par minutage dans les navigateurs, et fournissons des outils statistiques pour caractériser les minuteurs disponibles. Notre objectif est de présenter une vue claire de la surface d'attaque et de comprendre quelles sont les principales conditions préalables et classes d'attaques par minutage dans les navigateurs et quelles sont les principales contre-mesures. Nous fournissons une classification des attaques par minutage dans les navigateurs, en soulignant leurs conditions préalables communes. Nous proposons ensuite une taxonomie des contre-mesures en fonction des ressources qu'elles ciblent. Ces classifications permettent de déterminer dans quelle mesure les changements récents dans les contre-mesures ont un impact sur la sécurité des navigateurs.

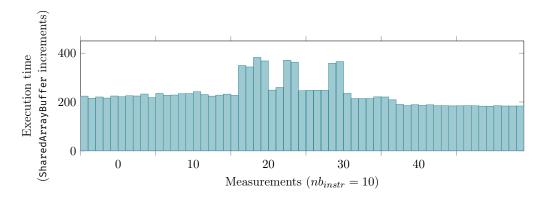

Nous nous intéressons particulièrement à une contre-mesure très répandue : la suppression des minuteurs à haute résolution. L'idée est simple : si les attaquants ne peuvent pas mesurer les différences de temps qui créent les fuites des données, ils ne peuvent pas monter leur attaque par minutage. Nous avons créé des outils analytiques pour évaluer la menace que représente un minuteur. Nous avons développé un système automatique pour évaluer la sécurité des minuteurs dans différentes versions des navigateurs les plus populaires. En particulier, nous montrons que l'évolution de la protection contre les attaques par exécution transientes a rendu possible d'autres attaques, telles que les attaques par canal auxiliaire microarchitectural avec une bande passante plus importante que ce qui était possible il y a seulement quelques années.

Ce travail est le résultat d'une collaboration avec Clémentine Maurice (Univ Lille, CNRS, Inria) et Pierre Laperdrix (Univ Lille, CNRS, Inria). Il a été publié à EuroS&P 2021 [RML21].

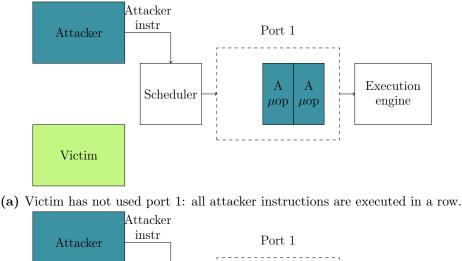

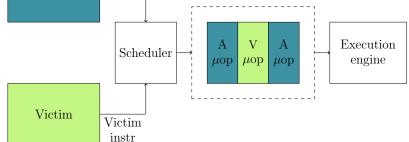

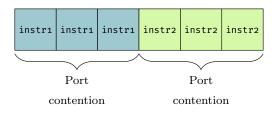

Contention de port dans les navigateur web (Q2,Q3) La contention des ports du processeur est un canal auxiliaire microarchitectural introduit par Aldaya et collab. [ABuH<sup>+</sup>19] en 2019. Il utilise les ports du CPU, un composant du pipeline d'exécution, comme goulot d'étranglement pour créer des différences d'exécution et faire fuir des données confidentielles.

Dans cet article, nous présentons le premier canal auxiliaire de contention de port s'exécutant entièrement dans un navigateur web, malgré un environnement très restreint :

- C1 Les minuteurs JavaScript ont une résolution inférieure à celle des minuteurs matérielles natives, ce qui augmente le bruit de mesure de l'attaquant.

- **C2** L'attaquant n'a aucun contrôle sur le coeur physique sélectionné par l'ordonnanceur pour exécuter le code d'attaque.

- **C3** Dans ce contexte, le code de l'attaquant est écrit dans un langage hautement abstrait qui est converti en code machine par un compilateur.

Alors que C1 a été étudié par des travaux antérieurs [SMGM17, RML21], C2 et C3 nécessitent de nouvelles approches. Pour résoudre C2, nous proposons une heuristique entièrement basée sur JavaScript pour permettre la co-résidence de coeur entre l'attaquant et la victime. C3 est probablement le plus grand défi : nous ne savons pas comment notre code de haut niveau sera traduit en code machine, donc son impact sur la microarchitecture et plus spécifiquement sur les ports du processeur n'est pas clair. Dans ce contexte, nous fournissons un système pour évaluer la contention de port causée par les instructions WebAssembly sur les processeurs Intel, permettant d'augmenter la portabilité des canaux auxiliaires de contention de port. Nous avons trouvé plus de 100 instructions créant de la contention sur 4 ports différents sur des microprocesseurs x86.

Notre attaque peut être utilisée pour construire un canal caché inter-navigateurs avec un débit de 200 bit/s, un ordre de grandeur au-dessus de l'état de l'art. Ce canal caché est inquiétant car il brise le modèle de sécurité d'isolation fondamental des navigateurs, permettant à deux onglets d'échanger des informations de cookies ou de communiquer avec un processus natif pour extraire des données privées. La contention de port web a une résolution spatiale de 1024 instructions natives dans une attaque par canal auxiliaire, ce qui est comparable aux meilleures attaques par cache dans le navigateur.

Nous concluons de notre travail que les attaques par contention de port sont non seulement rapides, mais sont aussi moins sensibles au bruit que les attaques par cache, et sont immunisés contre les contre-mesures implémentées dans les navigateurs ainsi que la plupart des contremesures par canal auxiliaire, qui ciblent le cache dans leur grande majorité.

Ce travail est le résultat d'une collaboration avec Clémentine Maurice (Univ Lille, CNRS, Inria), Marina Botvinnik (Ben-Gurion University of the Negev), et Yossi Oren (Ben-Gurion University of the Negev). Il a été publié à AsiaCCS 2022 [RMBO22].

**Port Contention sans SMT (Q3)** L'un des principaux prérequis de Port Contention est qu'il exploite un composant dépendant du coeur qui doit être partagé entre l'attaquant et la victime. De ce fait, elle s'appuie fortement sur SMT, une technologie permettant de partager un cœur physique entre plusieurs threads. Cependant, certains microprocesseurs n'utilisent pas le SMT, ou certains systèmes d'exploitations le désactivent pour des raisons de sécurité, à l'instar de ChromeOS [Goob] ou RedHat [Lar].

Dans cet article, nous présentons la *contention séquentielle de port*, qui ne nécessite pas de SMT. Au lieu d'exploiter le parallélisme *au niveau du fil d'exécution*, nous exploitons le parallélisme *au niveau de l'instruction*. Il exploite l'ordonnancement sous-optimal des ports d'exécution pour la parallélisation au niveau des instructions. Par conséquent, des séquences d'instructions spécifiquement conçues sur un seul thread souffrent d'une latence accrue. Nous démontrons une mise en œuvre de la contention de port séquentielle native sur les processeurs x86.

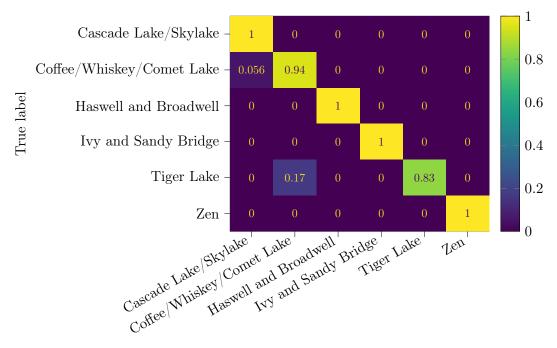

Nous montrons que la contention de port séquentielle peut être exploitée à partir des navigateurs web en WebAssembly, y compris sur les navigateurs orientés vers la confidentialité tels que Tor Browser ou Brave. Nous présentons un système automatisé pour rechercher les séquences d'instructions menant à la contention de port séquentielle pour des générations de microprocesseurs spécifiques, que nous avons évalué sur 50 microprocesseurs différents, y compris x86 et AMD. Un attaquant peut utiliser ces séquences à partir du navigateur pour déterminer la génération de processeur dans les 12 s avec une précision de 92%. Cette empreinte digitale est très stable dans le temps et résistante au bruit du système, ce qui la

rend très précieuse pour compléter les empreintes digitales basées sur des attributs logiciels plus volatiles. En outre, nous montrons que les mesures de protection sont soit coûteuses, soit uniquement probabilistes.

Ce travail est le résultat d'une collaboration avec Clémentine Maurice (Univ Lille, CNRS, Inria) et Michael Schwarz (CISPA Helmholtz Center for Information Security). Il a été publié à ESORICS 2022 [RMS22].

# Contents

| 1.            | Introduction                                                                                                                                                                                                                                                                                                                               | 1                                                                                                                 |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| $\mathbf{Li}$ | st of Productions                                                                                                                                                                                                                                                                                                                          | 9                                                                                                                 |

| 2.            | Background         2.1.       CPU Overview         2.2.       Web Browsers         2.3.       High-Resolution Timers         2.4.       Microarchitectural Attacks         2.5.       Side-Channel Attacks on Software and Browser Resources         2.6.       Countermeasures to Side Channels         2.7.       Browser Fingerprinting | <ol> <li>11</li> <li>12</li> <li>20</li> <li>24</li> <li>26</li> <li>42</li> <li>44</li> <li>51</li> </ol>        |

| 3.            | High Resolution Timers in the Browser3.1. Timing attacks in browsers3.2. Countermeasures in browsers3.3. Evaluation tools3.4. Results3.5. Discussion3.6. Conclusion3.7. Evolution of Timer Security Since The Publication of the Results                                                                                                   | <ul> <li><b>53</b></li> <li>54</li> <li>57</li> <li>58</li> <li>62</li> <li>69</li> <li>71</li> <li>71</li> </ul> |

| 4.            | Port Contention in the Browser4.1. Web-Assembly-Based Port Contention4.2. PC-detector4.3. Side-channel Attack on Artificial Applications4.4. Covert Channel4.5. Discussion4.6. Conclusion                                                                                                                                                  | <b>73</b><br>74<br>77<br>79<br>81<br>87<br>88                                                                     |

| 5.            | Port Contention Without SMT and its Privacy Implications         5.1. Threat Model                                                                                                                                                                                                                                                         | <b>89</b><br>90<br>90<br>94<br>98                                                                                 |

|    | 5.5. Conclusion                                                                                                                              | 100 |

|----|----------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 6. | Conclusion and Perspectives                                                                                                                  | 101 |

| А. | Appendices         A.1. Custom RDTSC implementation         A.2. Port Contention on Other WebAssembly Instructions         A.3. Training set | 107 |

| Bi | ibliography                                                                                                                                  | 109 |

# Introduction

Modern processors are remarkably optimized pieces of technology. As processing speed is probably the major selling point of CPUs, vendors have focused on increasing processors' performances in their development, each year bringing new generations with better features than the last.

As the progress in semiconductors' size and performances slowed industry-wide over the last decades, simply adding more transistors to a chip became insufficient to follow a steady performance rise. In reaction, CPU vendors focused on microarchitectural optimizations to further improve performance from generation to generation. These optimizations aim at increasing processing speed by proposing more parallelism and reducing stall times of the hardware. Examples of microarchitectural optimizations include multi-core processors, caches, hyperthreading, or speculative execution. Each generation sees changes to the microarchitecture, bringing more and more buffers or units in a complex pipeline. By design, these optimizations aim to bring more performance by speeding the execution. The security aspect of the microarchitecture tends to be secondary. In particular, side effects of these optimizations on computation may leak information about secret values used by the system in what are called *side channels*.

In 1996, Paul Kocher [Koc96] discovered that the dynamic speedup brought by caches introduces runtime differences in constant-time implementations of cryptographic algorithms. A malicious user can use these subtle timing differences to extract private information such as decryption keys on Diffie-Hellman. This discovery of the first timing attack paved the way for the broader research field on side channels.

Physical side channels have been heavily investigated. They exploit the physical side effects of the processor during the computation to detect sensible computation. The first physical side channel leveraged the power consumption of the chip [KJJ99] to attack cryptographic implementations, but many sources of physical leakage have been studied, including acoustic emissions [ST04, GST14], electromagnetic emissions [RR01], optical emissions [SNK<sup>+</sup>12] or temperature [HS13]. However, except for notable exceptions [LKO<sup>+</sup>21], these attacks require physical access to the target device to measure the side effects of computation.

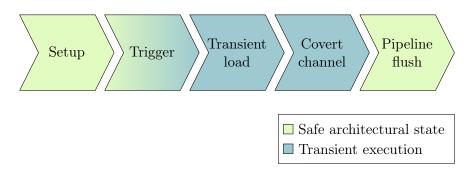

In constrast, *microarchitectural side channels* are purely software-based. They exploit the data-based optimizations of modern processors to infer private information. Since Kocher's first timing attack [Koc96], caches have probably been the most studied source of microarchitectural side channels, but research has proven that other components can also be exploited to mount side-channel attacks. Over the last decade, researchers have picked many microarchitectural components, reversed them, and used their behavior to extract secrets. Side channels have been leveraged, among others, out of branch predictors [AKS07], DRAM [PGM<sup>+</sup>16], or address translation [GRBG18]. Microarchitectural side channels were initially mounted to leak data from constant-time cryptographic implementations, but their scope has vastly broadened, including attacks against kernel-space ASLR [EPA16], cross-VM communication [MWS<sup>+</sup>17], keystroke detection [SLG<sup>+</sup>18b] and user monitoring [SKH<sup>+</sup>19]. Even more worrisome, microarchitectural side channels are an essential building block of a new class of microarchitectural attacks: transient execution attacks. Introduced in 2018 with Spectre and Meltdown, these attacks use the side effects of transient instructions, i.e., instruction executed but never committed to the architecture, to leak data through software and hardware security barriers.

Microarchitectural side channels exploit the sharing of hardware components between the attacker and the victim to leak information. Consequently, they have one common prerequisite: the attacker must run code on the victim's machine. This essential precondition brings severe restrictions to the attack surface of microarchitectural side channels, as system users grow increasingly wary of running unknown code on their personal machines. Awareness campaigns about the risk of unknown code have reached the ears of personal computer users, who tend to only download software from trusted sources. The risk of downloading attacker code is even reduced on mobile platforms, where applications are downloaded from an editor-controlled marketplace, each piece of code being carefully analyzed before release. Researchers have studied other threat models, where running code on the victim's hardware is elementary. An attacker can attack the victim remotely, often through the web, and mount network cache attacks [BB05, KGA<sup>+</sup>20]. Schwarz et al. [SSL<sup>+</sup>19] showed that it is possible to mount a Spectre attack over the web. Cloud environments are also an ideal target for microarchitectural attacks. With the development of Infrastructure as a Service (IaaS), users can buy Virtual Machines (VM) or containers running in the cloud on services like Amazon EC2 or OVHCloud. However, the cloud is just an abstraction layer for colossal servers. Although isolated from a purely software point of view, VMs controlled by different users can achieve processor co-residency, i.e., share one or more processors. This means an attacker can buy space in the cloud and mount attacks on all co-resident machines. This scenario has been exploited to detect co-residency [ZJOR11], reversing ASLR [BRPG15] or mounting high-bandwidth channels between two isolated virtual machines [MWS<sup>+</sup>17].

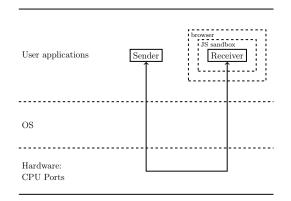

In 2015, Oren et al. [OKSK15] presented a cache attack running entirely in the browser. This threat model considerably enhances the attack surface of microarchitectural side channels. As the modern web is built around dynamic and interactive web pages, the architecture of websites is separated into two major components. The server side, or back-end, handles all computations regarding the server, the database, authentication, and sending the webpage information to the users. The client side, or front-end, handles the webpage as displayed in the user's browser. Client-side scripting languages such as JavaScript are responsible for the interactive components of sites. Client-side code is sent to the user by the server and is executed in the user's browser, and therefore *is executed on the user's machine*. This allows an attacker to run arbitrary code on many different victims effortlessly. A user visiting an attacker-controlled website will download JavaScript code and run it in his browser without noticing, potentially falling victim to microarchitectural attacks. Even more worrisome, an attacker can buy advertisement space on a legitimate website and run JavaScript code on all users seeing the ad.

For security reasons, JavaScript code runs in a secured virtualized environment called a sandbox. This sandbox prevents access to memory addresses, native instructions, or file system accesses. Furthermore, JavaScript is a high-level abstracted language, and it is hard to quantify its microarchitectural impact. These layers of security and abstraction make it hard to mount microarchitectural side channels from the sandbox. With their JavaScript cache attack, Oren

et al. [OKSK15] demonstrated the possibility of causing and measuring microarchitectural data leakage from the browser. Caches are not the only microarchitectural component targeted, and researchers have mounted attacks on DRAM [SMGM17] or floating-point units [AKM<sup>+</sup>15]. Although in general, JavaScript side channels tend to offer less resolution to the attackers, they represent a worrying threat to users' security and privacy. Microarchitectural side channels have been leveraged in the browser to extract cryptographic keys [GPTY18], monitor sites browsed by a user [OKSK15, SKH<sup>+</sup>19], fingerprint users [LMD<sup>+</sup>22] or communicate outside of the sandbox [SMGM17].

Although JavaScript-based side channels have been studied by academia, the entire landscape of their security and privacy implications is unclear. In particular, several gray areas remain:

- **Q1** Since the first JavaScript-based cache attacks, browsers have evolved, including in reaction to timing attacks. What is the current landscape of browser-based attacks and countermeasures?

- Q2 Are other components vulnerable to side channels from the JavaScript sandbox?

- **Q3** What can an attacker extract from these side channels?

# Contributions

This thesis is focused on partially exploring the answers to these questions. The following contributions of this manuscript are split into two categories. The first research direction was to reframe the scope of JavaScript-based timing attacks. In particular, we studied the impact of widespread countermeasures to timing attacks: removing access to high-resolution timers. The second class of contributions concerns a specific type of side-channel: CPU port contention. In a first contribution, we show how, for the first time, we implemented port contention in the browser sandbox. In a second contribution, we extend the scope of port contention to change its threat model completely. We also show how this new version of the side channel can be used in browser fingerprinting.

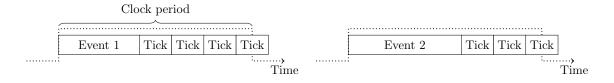

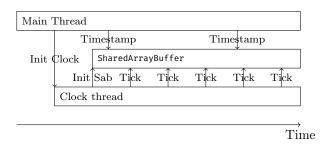

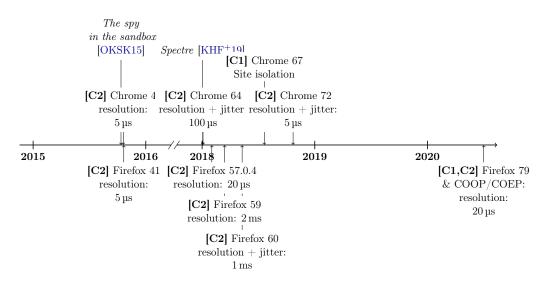

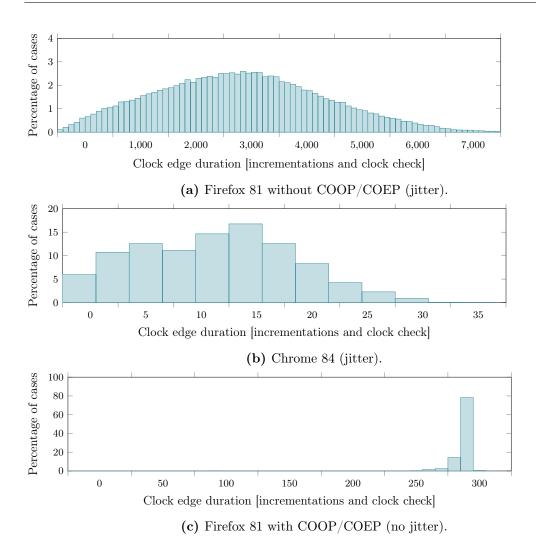

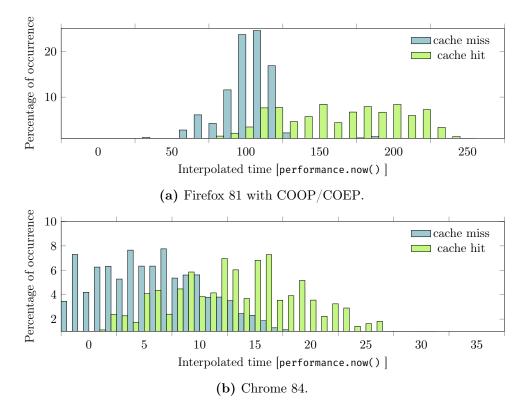

Systematic evaluation of JavaScript timers (Q1) In reaction to the developing threat posed by JavaScript-based timing attacks, browser vendors have proposed various countermeasures. However, as the attack multiplied in the last years, so did the countermeasures, in a cat-and-mouse game fashion. Amid all these changes, it can be hard to keep track of all the different evolutions browsers underwent. Notably, it is unclear how current countermeasures impact the attacks described in the literature.

We present the evolution of timing attacks in browsers, and provide statistical tools to characterize available timers. Our goal is to present a clear view of the attack surface and understand what are the main prerequisites and classes of browser-based timing attacks and what are the main countermeasures. We provide a classification of browser-based timing attacks, highlighting their common prerequisites. We then propose a taxonomy of countermeasures based on the resources they target. These classifications focus on determining to what extent the recent changes in countermeasures impact browser security.

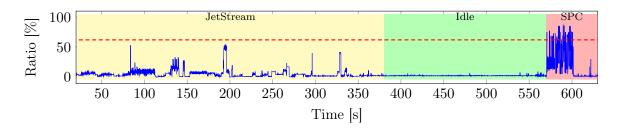

We take a particular interest in a widespread countermeasure: removing high-resolution timers. The idea is simple: if attackers cannot measure data-leaking timing differences, they cannot mount their timing attack. We created analytical tools to evaluate the threat posed by a timer. We developed an automatic framework to evaluate timer security in different versions of the most popular browsers. In particular, we show that the shift in protecting against transient execution attacks has re-enabled other attacks such as microarchitectural side-channel attacks with a higher bandwidth than what was possible just a few years ago.

This work is the outcome of a collaboration with Clémentine Maurice (Univ Lille, CNRS, Inria) and Pierre Laperdrix (Univ Lille, CNRS, Inria). It has been published in the proceedings of EuroS&P 2021 [RML21].

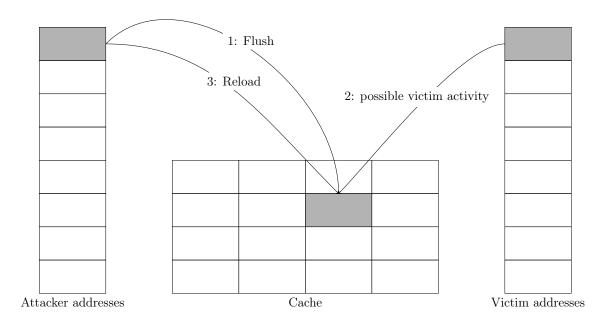

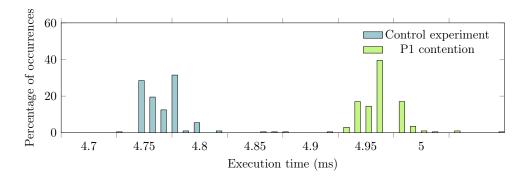

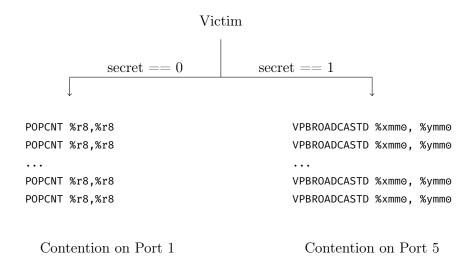

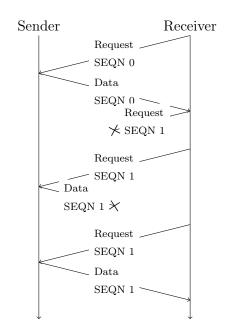

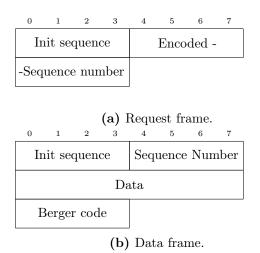

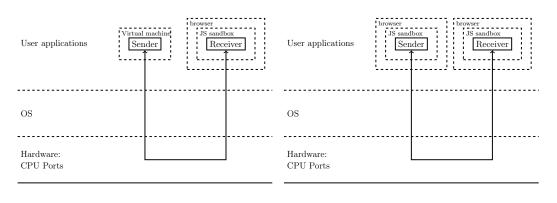

**Port Contention in the Web Browser (Q2,Q3)** CPU Port contention is a microarchitectural side-channel introduced by Aldaya et al. [ABuH<sup>+</sup>19] in 2019. It uses CPU ports, a component of the execution pipeline, as a bottleneck to create runtime differences and leak confidential data.

In this contribution, we present the first port contention side channel running entirely in a web browser, despite a highly challenging environment:

- **C1** Web-based timers have a lower resolution than native hardware-based timers, increasing the attacker's measurement noise.

- **C2** The attacker has no control over the physical core selected by the browser to execute the attack code.

- **C3** In this setting, the attacker's code is written in a highly-abstracted language which is translated into machine code by a just-in-time compiler.

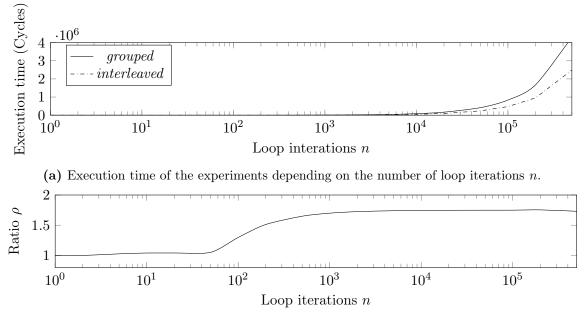

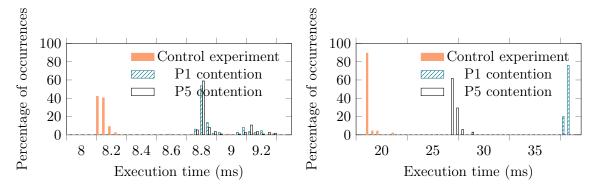

Whereas C1 has been studied by previous work [SMGM17, RML21], C2 and C3 require new approaches. To solve C2, we propose a fully JavaScript-based heuristic to allow core co-residency between the attacker and the victim. C3 is probably the biggest challenge: we do not know how our high-level code will be translated into machine code, thus its impact on the microarchitecture and more specifically on the CPU ports is unclear. To that extent, we provide a framework to evaluate the port contention caused by WebAssembly instructions on Intel processors, allowing to increase the portability of port contention side channels. We found over 100 instructions creating contention on 4 different ports on x86 CPUs.

Our attack can be used to build a cross-browser covert channel with a bit rate of 200 bit/s, one order of magnitude above state of the art. This covert channel is worrisome as it breaks the fundamental isolation security model of browsers, allowing two tabs to exchange cookie information or communicate with a native process to extract private data. Web port contention has a spatial resolution of 1024 native instructions in a side-channel attack, performing on-par with the best cache attacks in the browser.

We conclude from our work that port contention attacks are not only fast, but are also less susceptible to noise than cache attacks, and are immune to countermeasures implemented in browsers as well as most side-channel countermeasures, which target the cache in their vast majority.

This work is the outcome of a collaboration with Clémentine Maurice (Univ Lille, CNRS, Inria), Marina Botvinnik (Ben-Gurion University of the Negev), and Yossi Oren (Ben-Gurion University of the Negev). It has been published in the proceedings of AsiaCCS 2022 [RMBO22].

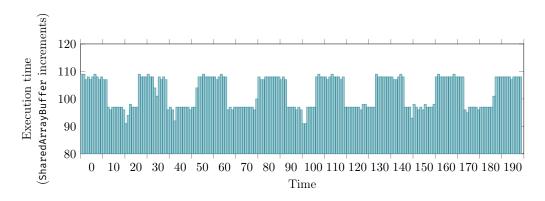

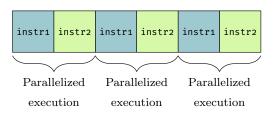

**Port Contentiont Without SMT (Q3)** A major prerequisite of Port Contention is that it exploits an on-core component that must be shared between the attacker and the victim. To that extent, it heavily relies on simultaneous multi-threading (SMT), a technology allowing to share a physical core between several threads. However, certain CPUs do not implement SMT, or operating systems disable it for security purposes, such as ChromeOS [Goob] or RedHat [Lar].

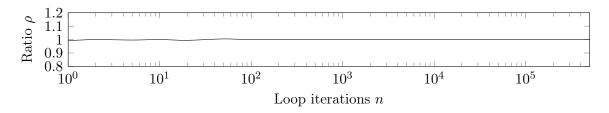

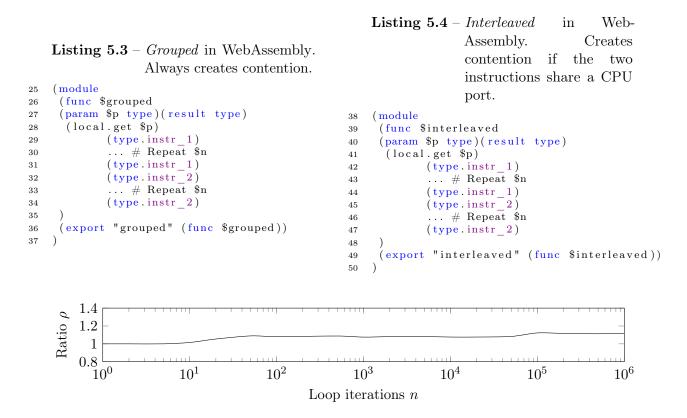

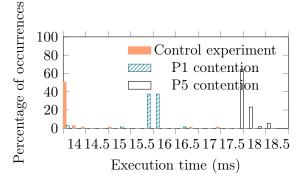

In this contribution, we present *sequential port contention*, which does not require SMT. Instead of exploiting *thread-level* parallelism, we exploit *instruction-level* parallelism. It leverages sub-optimal scheduling to execution ports for instruction-level parallelization. As a result, specifically-crafted instruction sequences on a single thread suffer from an increased latency. We demonstrate an implementation of native sequential port contention on x86 processors.

We show that sequential port contention can be exploited from web browsers in Web-Assembly, including on privacy-oriented browsers such as Tor Browser or Brave. We present an automated framework to search for instruction sequences leading to sequential port contention for specific CPU generations, which we evaluated on 50 different CPUs, including x86 and AMD. An attacker can use these sequences from the browser to determine the CPU generation within 12 s with a 92% accuracy. This fingerprint is highly stable in time and resistant to system noise, making it highly valuable to complement more volatile softwareattribute fingerprinting. Furthermore, we show that mitigations are either expensive or only probabilistic.

This work is the outcome of a collaboration with Clémentine Maurice (Univ Lille, CNRS, Inria) and Michael Schwarz (CISPA Helmholtz Center for Information Security). It has been published in the proceedings of ESORICS 2022 [RMS22].

# Terminology

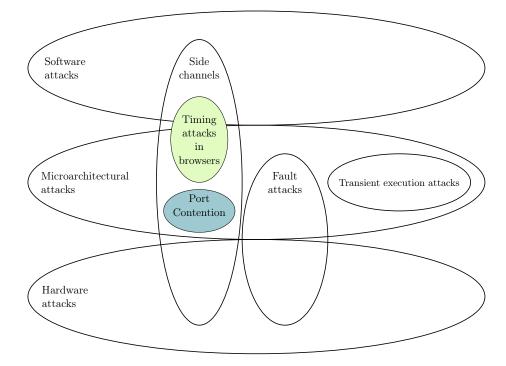

The terminology of classes of attacks explored in this manuscript can be confusing, as classes intertwine and denominations can be orthogonal. This manuscript is generally focusing on three major classes of attacks:

- **Timing Attacks:** They exploit timing differences caused by the execution to infer private data. They can be microarchitectural timing attacks, e.g., cache attacks, but also purely based on timing differences created by software execution.

- Side Channels: They exploit the side effects of execution to infer information about the victim. Timing attacks typically are side-channel attacks, but side channels may exploit other side effects than time differences. They can be physical side channels, e.g., electromagnetic side channels, microarchitectural, e.g., cache attacks, or purely software-based.

- **Microarchitectural attacks:** Microarchitectural attacks exploit the microarchitectural insecure implementation to break security rings. They comprehend microarchitectural side channels, microarchitectural fault attacks, and transient execution attacks.

Figure 1.1 illustrates the relations between these classes of attacks. This manuscript takes a particular interest in microarchitectural side channels with port contention [RMBO22, RMS22] and timing attacks in the browser [RML21].

Figure 1.1. – Visualisation of various attack classes mentioned in this manuscript, and scope of our publications

# Artifacts

Reproducible research is an essential value of this thesis. To that extent, we released all source code and evaluation data for our works. In particular, JavaScript exploits are highly portable by nature, and all client-side attacks can be run in the latest versions of browsers as of 2022. We also provide the various frameworks proposed in that work, hoping it can bring a more systematic approach to web-based side channel research. The artifacts are separated into three repositories:

- Framework, modified browsers, and evaluation data on our survey of timer security [RML21] are available on https://github.com/thomasrokicki/in-search-of-lost-time.

- PoCs and framework of our web-based port contention implementation [RMBO22] are available on https://github.com/MIAOUS-group/web-port-contention.

- PoCs, framework, and classification models for sequential port contention [RMS22] are available on https://github.com/MIAOUS-group/port-contention-without-smt.

# Thesis Outline

The rest of this manuscript is divided into 5 chapters:

• Chapter 2 introduces some fundamental notions to understand the contributions of this manuscript. In particular, Section 2.1 introduces hardware notions about modern

processors, especially Intel CPUs. Section 2.2 describes the architecture of web browsers. Section 2.3 provides a formalization of timers, and examples of timers in native and web environments. Section 2.4 introduces state of the art on microarchitectural attacks while Section 2.5 presents a short overview of other timing attacks with a strong focus on the browser. Section 2.6 presents the different classes of countermeasures proposed by the industry and academia. Finally, Section 2.7 briefly introduces browser fingerprint.

- Chapter 3 details our work on a systematic approach to timing attacks and timers in web browsers. It provides a taxonomy of browser timing attacks and countermeasures, and statistical tools to evaluate timer security in recent versions of browsers.

- Chapter 4 describes our implementation of port contention in the browser's sandbox. It also provides several applications of this side channel: a high-bandwidth covert channel and a side-channel artificial example.

- Chapter 5 introduces sequential port contention, a new development of port contention with fewer prerequisites. We show how sequential port contention can be used in web environments and its implication on the user's privacy via an application on browser fingerprinting.

- Chapter 6 concludes this thesis and opens perspectives to future work.

# 1

# List of Productions

- [RML21] Thomas Rokicki, Clémentine Maurice, and Pierre Laperdrix. Sok: In search of lost time: A review of javascript timers in browsers. In *EuroS&P*, pages 472–486. IEEE, 2021. Artifacts: https://github.com/thomasrokicki/in-search-of-lost-time

- [RMBO22] Thomas Rokicki, Clémentine Maurice, Marina Botvinnik, and Yossi Oren. Port contention goes portable: Port contention side channels in web browsers. In AsiaCCS, pages 1182–1194. ACM, 2022. Artifacts: https://github.com/MIAOUS-group/ web-port-contention

- [RMS22] Thomas Rokicki, Clémentine Maurice, and Michael Schwarz. CPU port contention without SMT. In ESORICS, 2022. Artifacts: https://github.com/ MIAOUS-group/port-contention-without-smt

# Background to appre-

In this chapter, we provide the necessary background to appreciate and discuss the contributions of this manuscript on microarchitectural attacks, especially in the web browser.

It is decomposed in 7 sections:

- Section 2.1 provides an overview of the execution pipeline and memory subsystem of modern Intel processors.

- Section 2.2 presents the architecture of a web browser.

- Section 2.3 introduces an important notion for this manuscript: high-resolution timers. In particular, it explains several techniques to build high-resolution timers in web browsers.

- Section 2.4 explores the state of the art on microarchitectural attacks. In particular, we present microarchitectural side channels, fault attacks and transient attacks. For each class, we present native attacks and attacks running in the browser.

- Section 2.5 presents other timing attacks exploiting software resources, with a strong emphasis on browser-based attacks.

- Section 2.6 explores state of the art countermeasures to side channels.

- Finally, Section 2.7 briefly introduces browser fingerprinting.

# 2.1. CPU Overview

This section presents a high-level overview of a modern Intel processor. CPUs are typically built in a multi-core architecture. These *physical cores* are highly independent and can process data in parallel, effectively multiplying performances. Each core contains its own execution pipeline, able to fetch instructions and execute them, as well as an on-core memory subsystem. Cores communicate with other cores through a ring interconnect. Some components, e.g., the RAM are shared by all physical cores.

# 2.1.1. Execution Pipeline

Pipelining is an essential model of modern processor architecture. A simplified RISC architectural pipeline can be decomposed into 5 stages:

Instruction Fetch: fetches, i.e., loads, an instruction in the pipeline.

Instruction Decode: translates this instruction and address registers.

**Execute:** sends the instruction to execution units and executes it.

Memory: read from memory to a register, or write a register to memory.

Writeback: store the results in a register, committing changes to the architecture.

The main idea of the pipeline is that to retrieve maximal performances, all stages of the pipeline must function at all times. At the first clock cycle, the pipeline fetches instruction  $i_0$ . Then, at the next cycle,  $i_0$  is decoded while the pipeline fetches instruction  $i_1$ . On standard execution, each pipeline stage handles an instruction per cycle. If a stage does not handle an instruction in a cycle, this cycle is effectively lost in terms of performance. This stall propagates to the rest of the pipeline, and is designated as a bubble. Bubbles can be introduced by unavailable resource or by waiting for dependencies. Modern processor implement several mechanism to reduce this stalling times, such as out of order execution or branch prediction.

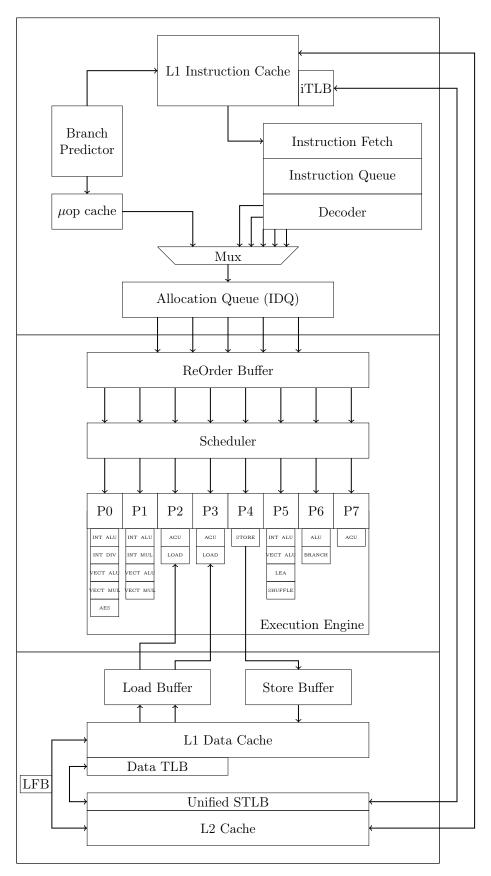

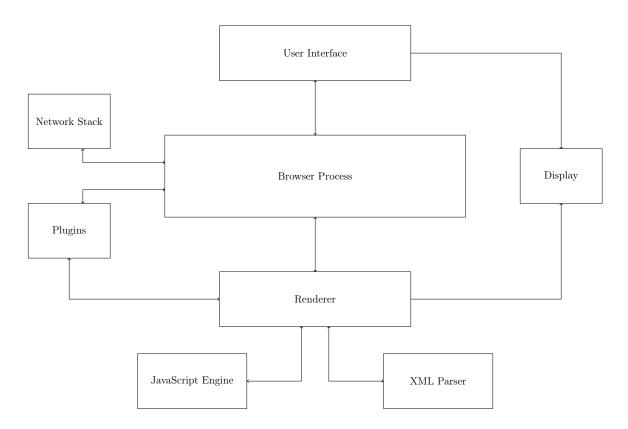

The microarchitectural pipeline is the implementation of this architectural pipeline. Figure 2.1 illustrates Intel's Skylake CPUs execution pipeline. It is separated into a *front end*, handling fetch and decode stages, as well as a *back end*, handling the execute, memory, and writeback stages. Each stage is highly parallelized, meaning several instructions are fetched, decoded, and executed every cycle.

Figure 2.1. – Simplification of the execution pipeline and memory subsystem for a single core in the Skylake microarchitecture.

#### 2.1.1.1. Front End

The front end is responsible for fetching and decoding instructions and forwarding them to the execution engine or back end. The Instruction Fetch Unit fetches data from the L1 instruction cache, reading packets of 16 bytes. These packets are then split into x86 instructions by the predecoder. These macro-operations are then forwarded to the FIFO Instruction Queue (IQ). The IQ implements macro-op fusion. Certain combinations of x86 instructions, e.g., a compare test and a subsequent jump, are merged into a single x86 instruction, saving bandwidth in the rest of the pipeline. At this point, instructions vary greatly in size and can have inconsistent encoding. The decoder decomposes instructions in atomic, fixed-length operations, called *micro-operations* or  $\mu ops$ . This decomposition is deterministic, i.e., a given instruction is decomposed in the same  $\mu$ ops regardless of the context. Abel and Reineke [AR19] have characterized the decomposition of x86 instructions<sup>1</sup>. They propose a benchmarking tool empirically measuring the number of  $\mu$  ops decomposed from the instruction, the instruction's latency, i.e., the number of cycles required to execute all the instruction's  $\mu$ ops [Intc] or the instruction's throughput, i.e., the average number of cycles per instruction when the instruction is repeatedly called  $[F^{+}11]$ . The  $\mu$ ops are then sent to the Instruction Decode Queue (IDQ).

Data or control dependencies can introduce pipeline stalls, reducing the processor's overall performance. For instance, when executing a conditional branch, e.g., if/else instructions, the pipeline has to wait for the conditional instruction to be executed and committed to the architecture before knowing which branch to take. To reduce control-dependencies-based delay, modern CPUs implemented branch prediction. Intel processors handle it with the Branch Prediction Unit (BPU). The BPU predicts, among others, the branch taken in a conditional branch. It implements a Pattern History Table (PHT) recording if a specific branch was taken or not in previous executions. The PHT is indexed according to virtual address bits and a Branch History Buffer (BHB), which stores branch decisions for all branches on the core. The advantage of the PHT is to remember which branch was taken on multiple sequential executions, allowing the identification of this pattern to increase the accuracy of predictions. For instance, if a branch is taken once every two executions, simply choosing the same branch as the last execution is insufficient. However, remembering two or more executions in the PHT allows to identify that pattern. The processor also predicts branch targets of direct or indirect branches before they are actually computed. The Branch Target Buffer (BTB) stores branch targets of previous branch executions. The BTB indexation scheme is not documented, but reverse-engineering [Hor] has shown that it uses a mixture of virtual-address bits of the branch instruction's address as well as previous, core-wide branches stored in the BHB. Return targets have a specific prediction component called the Return Stack Buffer (RSB). Similarly to the BTB, it dynamically stores the latest targets of RET instructions for a function and uses them for prediction. Mispredictions are only detected when the actual dependency is resolved. In that case, the pipeline is flushed, and the architecture is reset to its previous state, then executes the accurate branch.

Due to the inconsistent sizes and forms of x86 instructions, the fetching and decoding steps can be costly in performance and power. To optimize the front end, Intel introduced the Decode Stream Buffer (DSB) or  $\mu$ op cache. The  $\mu$ op cache dynamically stores the decomposition of the most frequent instructions in  $\mu$ ops. It allows bypassing the costly decoding phase, and delivering  $\mu$ ops to the IDQ faster. On Skylake architecture, the  $\mu$ op

<sup>&</sup>lt;sup>1</sup>All the results can be found at uops.info

cache has an 80% hit rate [Intc], significantly boosting performances. Similarly to the standard decode queue, the  $\mu$ ops are then pushed to the IDQ.

The IDQ implements an optimization known as Loop Stream Detector (LSD). It detects tight loops with many iterations and automatically fits all  $\mu$ ops directly in the IDQ without fetching and decoding them. Such small-body-size<sup>2</sup> and high-iterations loops are often found in modern software, e.g., searches or string moves. It allows the prior stages of the front-end to serve on other threads, thus improving overall performances. The IDQ delivers its  $\mu$ ops orderly to the back end.

#### 2.1.1.2. Back End

At this point,  $\mu$ ops from all threads are orderly stored in the IDQ and enter the back end. The goal of the back end is to execute the  $\mu$ ops in the most optimized fashion possible. To take advantage of available resources, the backend promotes parallelism through *Out of Order* execution (or OoO).  $\mu$ ops are not executed in their emission order, but rather as soon as all necessary resources are free.

$\mu$ ops are stored in the Re-Order Buffer (or ROB) until they are retired. The  $\mu$ ops are sent to the scheduler to be executed. It queues the  $\mu$ ops and forwards them to the scheduler. At the same level, the Branch Order Buffer (BOB) keeps track of the previous architectural states before speculation allowing for a fast roll-back in case of mispeculation. The ROB features many optimizations. Move Eliminations eliminates the  $\mu$ ops of register-to-register moves, preventing latency in the back end. Zeroing Idioms, e.g., computing XOR over the same registers, are also eliminated from the ROB. Similarly, One Idioms, i.e.,  $\mu$ ops setting all bits of a register to 1 are removed from the ROB, effectively causing zero latency.

The instructions are then forwarded to the scheduler. The scheduler stores  $\mu$ ops until all necessary resources are available e.g., the execution unit is ready, or all operands have been loaded. The scheduler then forwards  $\mu$ ops to the execution units.

The execution engine is composed of several execution units, each specialized in a specific type of operations, e.g., algebraic operations for the ALUs. The number and types of execution units vary between microarchitectures. Execution units are grouped by *execution ports*. Each port leads to several specialized execution units; therefore, ports are also specialized. Figure 2.2 illustrates the 8-port structure for a Skylake processor. If possible, one  $\mu$ op is forwarded to each available port per cycle. As the decomposition of an x86 instruction in  $\mu$ ops is deterministic, and each  $\mu$ op can only be executed by a specific type of execution unit, we can determine the *port usage* of an instruction, i.e., the ports used by this instruction. For instance, on Skylake processors, the IMUL R32 M32 instruction has a port usage of 1\*p1+1\*p23, i.e., emits a  $\mu$ op on P1 and a  $\mu$ op either on P2 or P3, as both ports can handle memory loads.

After their execution,  $\mu$ ops are retired in an orderly fashion, and changes are committed to the architecture. All the pipeline resources are freed during retirement, including ROB and BOB entries or execution units. Skylake processors can commit up to 6  $\mu$ ops per cycle.

# 2.1.2. Hyperthreading

Modern CPUs are often separated into several physical cores. This boosts performance and grants more parallelism during computation, as each core has its own execution pipeline and low-level caches. However, most standard computation does not exploit all hardware

<sup>&</sup>lt;sup>2</sup>typically 64  $\mu$ ops for Skylake

| Scheduler    |              |              |           |      |      |       |     |  |  |  |

|--------------|--------------|--------------|-----------|------|------|-------|-----|--|--|--|

| P0           | P1           | P5           | P6        | P2   | P3   | P4    | P7  |  |  |  |

| Int/Vect ALU | Int/Vect ALU | Int/Vect ALU | Int ALU   | Load | Load | Store | AGU |  |  |  |

| I/V Mul      | I/V Mul      | Vect Perm    | Int Shift | AGU  | AGU  |       |     |  |  |  |

| I/V Shift    | I/V Shift    |              | Int Logic |      |      |       |     |  |  |  |

| I/V Strings  | I/V Strings  |              | Branch    |      |      |       |     |  |  |  |

| I/V Logic    | I/V Logic    |              |           |      |      |       |     |  |  |  |

| FP Add, Mul  | FP Add, Mul  |              |           |      |      |       |     |  |  |  |

| Div          | LEA          |              |           |      |      |       |     |  |  |  |

| AES          |              |              |           |      |      |       |     |  |  |  |

| Branch       |              |              |           |      |      |       |     |  |  |  |

**Figure 2.2.** – Illustration of the execution unit distribution on ports for a Skylake microprocessor.

resources of a physical core at the same time. To exploit the hardware resources in the most optimized way possible, processor vendors have introduced Simultaneous MultiThreading (SMT). SMT allows multiple independent threads to use the physical resources of a physical core at the same time. The front end fetches instructions from all threads and execute them independently of their origin. All threads on the physical core share their execution pipeline, L1 and L2 caches, and bus. In addition, they have independent interruption systems and data and instruction registers. Sharing physical components between threads can be achieved in two settings:

**Static Sharing:** The component is definitively split, and a part of a component is only used by a single thread

Dynamic Sharing: The whole component is accessible by all threads competitively

This separation of physical cores is abstracted at the OS and software level. The OS considers each of these threads as a **logical core**, independent from the other logical cores. Hyperthreading is the name of Intel's implementation of SMT. It splits each physical core into two logical cores. On Skylake processors, the BPU or execution units are dynamically shared, whereas the IDQ, ROB, or  $\mu$ op cache are statically shared between threads.

# 2.1.3. Memory

During the execution, the CPU requires access to many values stored in the memory. On a single core, the system can handle 2 (P23) memory loads and 1 (P4) memory write per cycle for a Skylake processor. Access time to the memory is crucial as it can be one of the execution bottlenecks. The memory subsystem is highly optimized to reduce latency. This section presents an overview of the different components of the memory subsystem and shared memory focusing on caches as they are an essential component of microarchitectural attacks.

#### 2.1.3.1. Virtual Memory

At the lowest level, RAM is indexed with physical addresses. However, processors introduced virtual memory to bring more isolation between different processes. Processes do not directly use the physical addresses but access them with a level of abstraction through virtual addresses. Modern virtual memory is implemented through pages, i.e., fixed-size memory blocks. The physical memory, respectively virtual memory, is split into physical pages, respectively virtual pages. Intel's processors typically use 4 kB pages, but larger pages can be requested by processes. Both physical and virtual pages are indexed through page numbers. Virtual and physical pages are aligned, i.e., the start of a virtual page is always the size of a physical page. This also means that, for 4 kB pages, the 12 least significant bits of a virtual address are equal to those of the physical address. The translation from virtual to physical address is handled by the Memory Management Unit (MMU). The virtual-physical mapping is decomposed in Page Tables (PT), and follows a 4 or 5-level hierarchical structure. When a processor wants to access a virtual address, the processor looks for the appropriate Page Table Entry (PTE) in Page Tables. This process is called a page walk. As almost any memory operation requires a translation, the translation latency is a significant bottleneck in modern systems. Intel implemented on-core Translation Lookaside Buffers (TLB) to lower this latency, dynamically caching the most frequent translations. A translation served from the TLB is significantly faster than from the standard PT structure. The TLB is often separated into an instruction TLB (iTLB) and a data TLB (dTLB).

Virtual pages are also the base unit for Address-Space Layout Randomization (ASLR), a standard security measure to prevent code-injection attacks. When a process starts or requires new stack allocation, ASLR randomizes the address blocks. This implies that other processes cannot know which virtual memory pages are used by a specific process, thus preventing an attacker from modifying them. ASLR is also implemented on kernel-space addresses (KASLR).

Sharing memory between processes is a critical optimization of the memory space. At the system level, the OS implements *memory deduplication*. It is implemented on a content-based approach: if several memory pages are identical, the OS frees all pages except one. This page is set as copy-on-write, i.e., shared by all processes generating this page before the duplication. When a process tries to write on the page, a page fault is thrown. The page is then duplicated, keeping the original page and the modified copy for the writing process.

#### 2.1.3.2. Caches

Caches are small memories that sit close to the CPU core. They are relatively small, typically in the order of 1 to 10 MB. As they sit close to the execution pipeline, the access latency is significantly smaller than an access to the DRAM. The goal of caches is to dynamically store the most used values to serve most calls from the cache and not the DRAM, thus significantly improving performances.

Modern Intel CPUs often have three levels of caches of different sizes. The L1 cache is the smallest and fastest, while the L3, or last-level Cache, is the biggest and slowest. Both L1 and L2 are private to each physical core, whereas the last-level cache is shared by all cores. The last-level cache is *inclusive* to L1 and L2, meaning that all values in the L1 or L2 are also stored in the last-level cache.

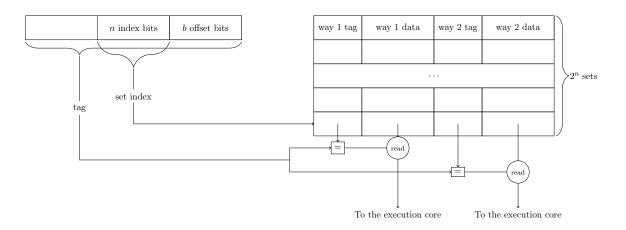

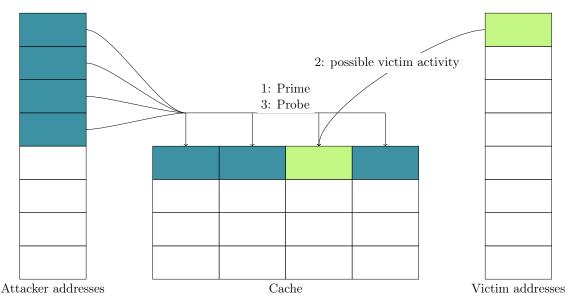

Modern caches follow a set-associative organization illustrated in Figure 2.3. They are

**Figure 2.3.** – Illustration of a 2-way set associative cache with  $2^n$  cache sets

composed of  $2^n$  cache sets, each composed of m ways. Such a cache is called an m-way associative cache. Each way consists of a tag and  $2^b$  bytes of data. Most modern Intel caches use b = 6 and have 64-bytes lines. The tag is computed from the memory address stored in the cache line. The 6 least significant bits of the address are used as an *offset* in the data section of the line. The n middle bits of the addresses are used as a *set index*, indicating in which cache set the data must be stored. Two different addresses with the same set index are stored in the same cache set and are called *congruent* addresses. When the processor fetches an address from the cache, it first computes the set index to find the associated cache set. Then, it checks the tags from all the m lines present in the set and compare them with the tag computed from the wanted address. If one line has the sought tag, the data is served from the cache, causing a cache hit. If no line in the set has the wanted tag, the data is served from the DRAM, causing a cache miss.

The computation for the set index and the tag can be executed on the virtual address or the physical address. In a Virtually-Indexed Virtually-Tagged (VIVT) cache, both the tag and the set index are computed from the virtual address. This is interesting regarding latency, as the processor does not need to translate the virtual address into a physical one. However, this comes at a space cost, as shared memory is not shared in virtual addresses, meaning that some data could occupy several different cache lines. The opposite solution is to use a Physically-Indexed Physically-Tagged (PIPT) cache, where both the tag and the set are computed from the physical address. This grants a physically-unique tag, resulting in optimized use of cache space for shared memory but comes at a latency cost due to address translation. This is the most commonly used addressing mode, particularly in L2 and last-level caches for modern Intel processors. Finally, some vendors proposed a hybrid approach: Virtually-Indexed Physically-Tagged (VIPT) caches. This allows the processor to immediately compute the cache set index to remove the latency. The tag is then computed from the physical address while the set is looked up, thus reducing the latency. This mode is particularly interesting when the index does not use bits from a different page. This means, for a 4 kB page structure, the page offset is 12 bits long. As the line offset is computed of the 6 least significant bits, it leaves 6 bits to calculate the tag and stay on the same page offset. resulting in an optimal cache size of  $2^8$  cache sets. The L1 of most Intel processors follows this optimized structure and is composed of 2 32 kB, 8-way associative VIPT caches, one for

the data and one for the instructions.

The design goal of the cache is to dynamically store values to reduce latency by preventing DRAM calls. To do so, it must store new data constantly and evict previously stored data. When new data is loaded in the cache, the cache uses a *replacement policy* to determine which line must be evicted. An intuitive replacement policy is Least Recently Used (LRU), where the data with the oldest last usage is evicted to store the new data. In practice, as this policy requires the hardware implementation of a timestamp for each cache load, processors used a pseudo-LRU policy with an approximation of last-used timestamps. However, this policy is suboptimal in some instances. For instance, when the user is browsing a congruent set of addresses larger than the cache associativity, all calls will result in a cache miss. Modern processors use more complex and hybrid solutions to adapt to various situations.

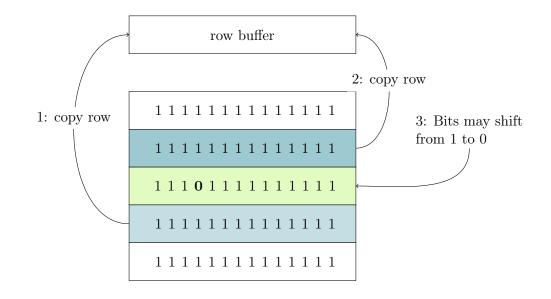

#### 2.1.3.3. DRAM

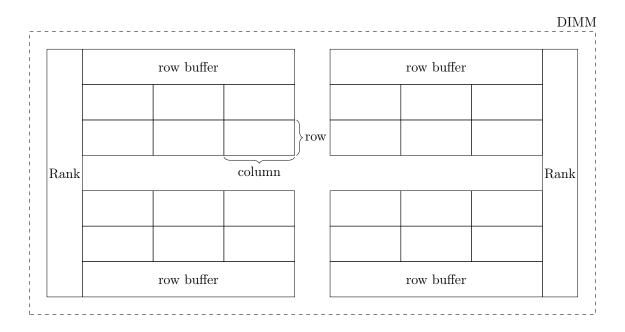

Figure 2.4. – Organization of a DRAM DIMM. It is composed of two ranks, each handling two banks. Each bank is composed of 3 columns and 2 rows.

Dynamic Random Access Memory (DRAM) is the main memory component in modern computer systems. Its access time is significantly higher than the cache's, but it can store more data. When loading an address, the processor first checks if the address is cached. If not, it then loads it from the DRAM. The processor handles DRAM with an on-chip memory controller. The memory controller communicates with the DRAM through one or more parallel channels. The DRAM is organized in Dual Inline Memory Modules (DIMMs). One or more DIMMs can be connected to the same channel. Figure 2.4 illustrates the organization of a DIMM. DIMMs are separated into one or two ranks, corresponding to the physical sides of the module. Each rank handles 16 banks on DDR4 and 32 on DDR5. The bank manages the actual memory, typically decomposed in  $2^{17}$  rows and  $2^{13}$  columns. The mapping of an address to channel, DIMMs, rank, and bank is not documented for Intel but has been reversed by Seaborn et al. [Sea] on a Sandy Bridge processor and by Pessl et al. [PGM<sup>+</sup>16] in 2016 by exploiting a timing side channel. More recently, Wang et al. [WZCN20] introduced DRAMDig, a generic tool to reverse the address mapping of documented Intel processors.

When the processor wants to load a value from the DRAM, it looks for the corresponding channel, DIMM, rank, bank, and row. It then *opens* the row, i.e., copies the whole row to the bank's *row buffer*. The processor then reads the sought-after column from the row buffer. Repeatedly reading data from the same column always loads data from the row buffer without reloading it. However, reading data from the same bank but another row flushes the row buffer and loads the new row.

The DRAM's cells hold a volatile charge that decreases over time. When this charge gets under a threshold, the bit held switches from 1 to 0. Therefore, all the data in a cell is regularly refreshed to prevent data loss. This *refresh interval* is 32 ms in DDR4.

## 2.1.3.4. In-Flight Data

In-Flight Data are pieces of data temporarily stored in special buffers outside of the standard memory subsystem.

Store Buffers (SBs) are small buffers, connected to the store port and the L1 Data Cache. They aim at tracking pending stores. They implement the store-to-load optimization: the processor speculates if a load and a store have the same physical address before their translation from virtual address. If so, it will send data from the store buffer to the load buffer.

The Line-Fill Buffer (LFB) is a small buffer (typically 10 entries) handling outstanding memory accesses. CPU can speculatively load data from the LFB when it is not found in the L1 cache.

## 2.1.4. Hardware Performance Counters

Hardware Performance Counters (HPC) are special registers built in the micro-architecture of modern CPUs. They collect information about microarchitectural events at runtime, and are accessible from the software [Wikb]. They monitor various events, e.g., cache hits, misses,  $\mu$ ops dispatched by ports. Initially used for debugging purposes, they can be used to evaluate the behavior of the microarchitecture at runtime.

# 2.2. Web Browsers

This section provides the necessary background on modern browsers' architecture to understand the attacks described in this manuscript. This thesis mainly focuses on two different browsers: Google Chrome and Mozilla Firefox. To that extent, we will provide more depth about these two browsers, but some generic aspects of browser architecture or microarchitectural attacks may be implementable on more browsers with some fine tuning. Furthemore, many browsers are forks of Chrome (e.g., Brave, Opera, or Microsoft Edge) or Firefox (e.g., ToR Browser) and architectural design or components remain the same. Firefox and Chrome represent 75% of the market share of dekstop browser. If we count all Firefox-based and Chrome-based browsers, this marker share reaches 91%.

Figure 2.5. – Simplification of the structure of a modern web browser

# 2.2.1. Browser Architecture

Browsers are complex software composed of many different processes. Although Chrome and Firefox vary significantly in architecture, they have a similar high-level architecture illustrated in Figure 2.5.

- **Browser process:** The browser process, or browser engine, is the central component of the web browser. Its main task is to allow communication between all components and synchronization and handle privileged options such as local file accesses. It is directly communicating with the User Interface (UI).

- **User Interface:** The UI encompasses all the browser's components presented to the user, e.g., the URL bar, previous and next buttons, or the settings menu.

- **Network stack**: The network stack is responsible for fetching the URLs provided by the user and forwarding the result to the browser process.

- **Rendering engine:** The rendering engine, or renderer, controls the actual webpage in the browser. It is responsible for parsing the HTML/CSS code sent by the server and displaying it. The rendering engine parses all HTML code with the XML parser into a tree-like interface called Document Object Model (DOM). The Document node is the top node of the tree, and each element displayed on the page is a node below in the tree. In the meantime, the rendering engine parses the CSS attributes of the site,

essentially controlling the layout of the displayed page. Both the UI and the rendering engine are responsible for the display component of the browser, i.e., what the users see on their screen. The rendering engine is also responsible for parsing scripts in the page and sending them to the JavaScript engine. Chrome uses the Blink rendering engine, except on iOS versions where it uses WebKit. Firefox's rendering engine is called Gecko and is developed internally by Mozilla.

**JavaScript engine:** The JavaScript engine is the main component of client-side scripting on the web. It inputs client-side scripting code and compiles it to native machine code at runtime. Client-side code handles all interactions between the user and the webpage without communicating with the server. It typically handles forms, animations, modifications to the DOM, and generally makes the page dynamic. We will provide more details on client-side computing in Section 2.2.2.

As the webpage is an interactive environment, the renderer process is highly event-oriented. The browser must react to users' inputs. To handle asynchronicity, the renderer implements an *event loop*. The event loop is a FIFO queue, where each asynchronous event is registered. When browser resources are available, it will pop the first ready asynchronous event and execute the callback function. Modern renderer processes contain several event loops with different priorities, handling DOM events, network requests, or page repaints.

This multi-process architecture is also parallelized in the browsers. Each tab or origin runs its own renderer process, along with JavaScript engine, XML parser, or event loops. This allows more performant browsers, as processes cannot block each other's execution through the event loop. For instance, if a tab goes unresponsive because of heavy computations, the other tabs are not affected by the slowdown. It also grants more isolation between contexts. However, as some common infrastructure, e.g., JavaScript engine, are duplicated, having several processes can result in higher memory usage.

## 2.2.2. Client Side Languages

To enhance user experience with more dynamic pages, most websites encompass scripts aimed at being executed locally in the users' browsers. This provides faster computation, without the delay introduced by network computation, and reduces the servers' workload. JavaScript is the most used client-side scripting language, but other languages are used to fill specific needs. This section presents the necessary background on the principle and execution of JavaScript and WebAssembly, as they are the languages used in our attacks.

#### 2.2.2.1. JavaScript

JavaScript is a lightweight, high-level scripting language. It is used as the client-side scripting language for most websites [w3t], but is also used in back-end programming with Node.js, managing databases, or as a framework to develop webpages. This section focuses on JavaScript's use as a web client-side language. JavaScript is defined by the ECMA standards [ECMc] as a single-threaded scripting language. However, due to its usage in web browsers, it has been enriched with APIs to manage multi-threading, DOM manipulation, animations, and many browser-specific features. Most of these applications are also standardized by the ECMA [ECMd]. For security reasons, JavaScript is executed in a secured environment, also

Figure 2.6. – JavaScript execution in the engine.

called a *sandbox*. JavaScript scripts have no access to virtual or physical addresses, native instructions, reads or writes on the filesystem, or to system information.

JavaScript engines use Just-In-Time compilation, i.e., they compile the code directly at runtime and not beforehand. The translation from JavaScript to machine code in the browser is handled by the JavaScript engine, e.g., v8 [Gooe] for Chrome and SpiderMonkey [Mozb] for Firefox. The translation from JavaScript to executable machine code is decomposed in several stages illustrated in Figure 2.6. The JavaScript is first parsed into an Abstract Syntax Tree (AST), i.e., a formal tree representation of the code. This AST is then used to generate bytecode, i.e., intermediary abstract code. At this point, the code is still portable, but the bytecode is loaded in memory and specific to a JavaScript engine. Both v8 and SpiderMonkey use a stack-like register machine [Mozc, Goof] to be as close to actual machine code as possible. Chrome's v8 use a parser and interpreter called Ignition [vba].

This bytecode is then compiled just-in-time to executable machine code. The JIT compiler introduces many different optimizations to the code, e.g., redundancy elimination, inlining, caching, or speculating on operand types. Firefox's JIT compiler is known as Warpmonkey [Mozb], and Chrome's is known as TurboFan [vbc].

#### 2.2.2.2. WebAssembly