# Optimal Design Methodology for Static Converters -Application to the Aeronautical Context

Jérémy Bourdon

### ▶ To cite this version:

Jérémy Bourdon. Optimal Design Methodology for Static Converters - Application to the Aeronautical Context. Electric power. Institut National Polytechnique de Toulouse - INPT, 2018. English. NNT: 2018INPT0020. tel-04513496

# HAL Id: tel-04513496 https://theses.hal.science/tel-04513496v1

Submitted on 20 Mar 2024

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

Université de Toulouse

# THÈSE

En vue de l'obtention du

# DOCTORAT DE L'UNIVERSITÉ DE TOULOUSE

Délivré par :

Institut National Polytechnique de Toulouse (Toulouse INP)

Discipline ou spécialité :

Génie Electrique

# Présentée et soutenue par :

M. JEREMY BOURDON le mercredi 23 mai 2018

# Titre :

Méthodologie de conception de convertisseurs-statistiques-application à un contexte aéronautique

### École doctorale :

Génie Electrique, Electronique, Télécommunications (GEETS)

**Unité de recherche :** Laboratoire Plasma et Conversion d'Énergie (LAPLACE)

# Directeur de Thèse :

M. THIERRY MEYNARD

#### Rapporteur :

M. FREDERIC GILLON, ECOLE CENTRALE DE LILLE

### Membres du jury :

M. BRUNO ALLARD, INSA LYON, Président MME SANDRA NGUEVEU, TOULOUSE INP, Membre M. THIERRY MEYNARD, CNRS TOULOUSE, Membre

# Acknowledgements

# Abstract

Nowadays, the electrification of on-board functions on planes is growing inevitably, intensified by the study of new programs such as the More Electric Airplane (MEA). This concept - studied by Airbus - involves both improving the device performance and reliability, and lowering operation and maintenance costs. This growing electrification will significantly reduce gas emissions to meet the new energy and environmental challenges of our society. However, in order to achieve these goals, electrical engineering of aircraft should be dramatically improved. Indeed, design requirements have changed due to new architectures and technological constraints. In this context, power electronics have become a key factor to supply, treat and transport electrical energy with efficiency in our embedded networks and systems. The equipment related to this area will be more affordable, efficient, ecological and integrated in order to create the MEA.

This thesis proposes a new way to design and optimize the power equipment, taking into account the many challenges of the MEA. This is possible thanks to the computer-aided and optimal design, also called virtual prototyping. This new approach in power electronics is a digital revolution in our methods of design and sizing. Indeed, virtual prototyping provides easier and quicker fully optimized systems, while meeting the objectives and specific constraints of an application. This software also dramatically improves the pre-design phase of a converter by simplifying complex decisions on technological compromise, materials, shapes and sizes, as well as internal parameters of a converter - switching frequency filtering, regulation, etc. In other words, the optimal design will become an indispensable step to reach quickly and more effectively new levels of performance. Furthermore, although this approach is driven by the aviation industry, it has to remain flexible enough to be extended to any field of study and any industry.

A full software platform methodology of an electrical engineering optimization is presented in this manuscript. The power component sizes up the complete chain of conversion, while going through related issues such as EMC filtering. This methodology is carried out in particular through the creation of appropriate models of the main power devices of a static converter. A complete ecosystem is also proposed, including communication with time and frequency multi-physics solvers. Finally, we focus on applications related to the development of More Electric Aircraft. Thus, we propose several use examples of this tool, taking into account the needs and constraints of this very demanding environment.

#### Key-words

Power Electronics, Virtual Prototyping, Optimal Design, Optimization, Isolated DC/DC power converter, Multilevel converters, Wide Band-gap, SiC, GaN, More electric aircraft, Power converter sizing, Filter sizing, EMC

# Résumé

L'électrification croissante des fonctions à bord des avions est inévitable et s'intensifie avec l'étude de nouveaux programmes tel que l'Avion Plus Electrique (MEA). Ce concept étudié par Airbus implique l'amélioration de la performance des appareils et de leur fiabilité, ainsi que la diminution des frais d'opération et de maintenance. Il permettra de réduire considérablement les émissions de gaz afin de répondre aux nouveaux défis énergétiques et écologiques de notre société. Cependant, pour atteindre ces objectifs, l'état de l'art en génie électrique doit être amélioré. En effet les exigences en terme de conception ont changé, en raison des nouvelles architectures et contraintes technologiques. Dans ce contexte, l'électronique de puissance est devenu un facteur clé pour alimenter, traiter et transporter l'énergie électrique avec efficacité dans nos réseaux et systèmes embarqués. Les équipements relatifs à ce domaine devront donc être plus abordables, performants, écologiques et intégrés afin d'aboutir à la création du MEA.

Pour y parvenir, le but de cette thèse est de proposer une nouvelle façon de concevoir et d'optimiser ces équipements de puissance, tout en prenant en compte les nombreux défis du MEA. Cela est possible grâce à la conception optimale informatisée, aussi appelée prototypage virtuel. Cette nouvelle approche en électronique de puissance promet une révolution numérique de nos méthodes de conception et de dimensionnement. En effet, le prototypage virtuel fournira plus facilement et rapidement des systèmes entièrement optimisés, tout en répondant aux objectifs et aux contraintes spécifiques d'une application. Ces logiciels permettront aussi d'améliorer drastiquement la phase de pré-dimensionnement d'un convertisseur en simplifiant la prise de décisions complexes sur des compromis technologiques, de matériaux, formes et dimensions, ainsi que de paramètres internes à l'utilisation d'un convertisseur fréquence de découpage, filtrage, régulation, etc. En d'autres termes, la conception optimale deviendra une étape indispensable pour atteindre plus efficacement et rapidement de nouveaux niveaux de performances. De plus, bien que cette approche soit poussée par le milieu aéronautique, elle reste suffisamment flexible pour être étendue à n'importe quel domaine d'étude et d'industrie.

Une méthodologie complète de plate-forme logicielle d'optimisation en génie électrique est présentée dans ce manuscrit, du dimensionnement du composant de puissance jusqu'à la chaine complète de conversion, tout en passant par des problématiques connexes tel que le filtrage CEM. Cette méthodologie est réalisée notamment grâce à la création de modèles adaptés des principaux dispositifs de puissance présents à l'intérieur d'un convertisseur statique. Un écosystème complet est aussi proposé, comprenant la communication avec des solveurs multi-physiques temporels et fréquentiels. Finalement, nous nous concentrons sur des applications relatives au développement de l'avion plus électrique. Ainsi, nous proposons plusieurs exemples d'utilisation de cet outil, prenant en compte les besoins et contraintes de ce milieu très exigeant.

Mots-clés : Electronique de Puissance, Prototypage Virtuel, Conception Optimale, Optimisation, Convertisseur isolé DC/DC, multiniveaux, semi-conducteurs grand gap, SiC, GaN, Avion Plus Electrique, Dimensionnement, Filtres, CEM

# **ETHAER** Project

#### Advanced power electronic for aeronautical applications

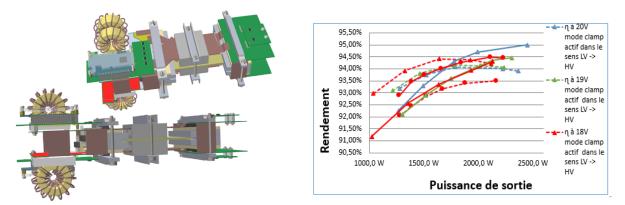

The ETHAER project is at the border of basic research and applied research. It addresses the field of Power Electronics within the frame of the more electrical aircraft that has generated many research over the past five years. The specific aim of this project is to help defining the power electronic converters for the next generation of airplanes (2015-2020). With this aim in view, the project focuses on the interconnection of the LV and HV networks (resp. 28 and 540V) which is definitely a very demanding function. This project includes technological aspects that require experimental check and must be pushed up to the full prototype stage. However, more theoretical aspects aiming at the design and optimisation are also included; dedicated tools aiding the design and the technological choices to be made in order to build the power systems for future aircrafts will also be developed.

#### Electronique de puissance à Très Hautes performances pour l'AERonautique

Le projet ETHAER se situe à l'interface recherche amont/recherche industrielle. Il relève du domaine de l'Electronique de puissance et se situe dans le contexte applicatif de l'avion plus électrique sur lequel se focalisent de nombreuses recherches depuis 5 ans. Il a pour ambition de contribuer à la définition de convertisseurs de puissance électroniques pour les avions de future génération (2015-2025). Pour atteindre cet objectif global, le projet se focalise sur une fonction électrique particulière très contraignante, l'interconnexion réversible et isolée entre les réseaux de bord 28V et +/-270V, ces derniers étant d'ores et déjà définis. Il contient donc un important volet expérimental et technologique qui doit déboucher sur la réalisation de démonstrateurs. Mais il va plus loin, en visant la synthèse de méthodes de conception/optimisation, la construction d'outils associés et la définition de technologies d'intégration susceptibles d'être exploitées dans les autres fonctions de conversion électriques qui vont se multiplier dans les aéronefs.

#### **Partners**/Partenaires

- AIRBUS OPERATIONS SAS

- IES INSTITUT D'ELECTRONIQUE DU SUD

- AMPERE LABORATOIRE AMPERE

- GEEPS GENIE ELECTRIQUE ET ELECTRONIQUE DE PARIS

- LAPLACE LABORATOIRE PLASMA ET CONVERSION D'ENERGIE

# **Table of Contents**

| 1. | Introd           | uction                                                             | 19 |

|----|------------------|--------------------------------------------------------------------|----|

|    | 1.1. The         | • More Electrical Aircraft (MEA)                                   | 20 |

|    | 1.1.1.           | Review of the MEA                                                  |    |

|    | 1.1.2.           | Power Electronics Integration                                      | 21 |

|    | 1.1.3.           | Impact of the new HVDC network                                     | 22 |

|    | 1.2. Con         | nputer-aided design in Power Electronics                           | 24 |

|    | 1.2.1.           | New expectations in Power Electronics                              | 25 |

|    | 1.2.2.           | Digitalization & Virtual Prototyping                               | 26 |

|    | 1.2.3.           | Pre-design VS Detailed-Design                                      |    |

|    | 1.2.4.           | Problematics for sizing a Power Converter                          | 30 |

|    | 1.3. Vec         | tor of improvements in Power Electronics                           | 33 |

|    | 1.3.1.           | Components and Technologies                                        | 33 |

|    | 1.3.2.           | Topologies                                                         |    |

|    | 1.3.3.           | Integration                                                        | 34 |

|    | 1.4. Con         | clusion and Axes of research                                       | 35 |

|    | 1.4.1.           | Chapter 1 – General Introduction                                   | 35 |

|    | 1.4.2.           | Chapter 2 - Optimal Design Methodology                             | 35 |

|    | 1.4.3.           | Chapter 3 & 4: Models of Power Devices                             | 35 |

|    | 1.4.4.           | Chapter 5: Optimization of Power Devices, Topologies and Converter | 36 |

| 2. | Motho            | dology for the Optimal Design of Power Converters                  | 27 |

| 2. |                  |                                                                    |    |

|    |                  | ware Architecture                                                  |    |

|    | 2.1.1.           | Topology, Device and Material                                      |    |

|    | 2.1.2.           | Design pattern                                                     |    |

|    | -                | imization Definition and Process                                   |    |

|    | 2.2.1.           | Strategy of Optimization                                           |    |

|    | 2.2.2.<br>2.2.3. | Continuous Modelling<br>Indirect and Direct Modelling              |    |

|    | 2.2.3.           | Direct vs Inverse Model                                            |    |

|    | 2.2.4.           | Model Granularity                                                  |    |

|    |                  | vers and Excitations computation                                   |    |

|    | 2.3. SOIN        | Solver Simulation                                                  |    |

|    | 2.3.1.           | Analytical Resolution                                              |    |

|    |                  | •                                                                  |    |

|    |                  | development and outlook                                            |    |

|    |                  | Process Management and libraries<br>Graphical User Interfaces      |    |

|    | 2.4.2.<br>2.4.3. | Outlook                                                            |    |

|    |                  |                                                                    |    |

|    | 2.5. Con         | clusion                                                            | 50 |

| 3. | Active           | Part: Analytical models of Semiconductors and Cooling              | 59 |

| Р  | art A: Ser       | niconductors                                                       | 59 |

|    | 3.1. Rev         | iew of Technologies                                                | 60 |

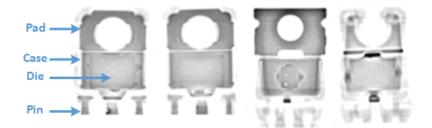

|    | 3.1.1.           | Semiconductor Technologies                                         |    |

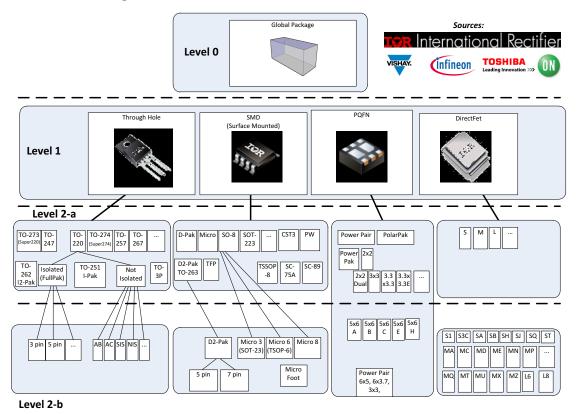

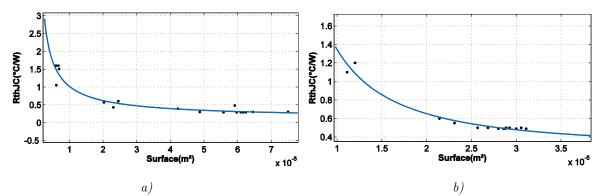

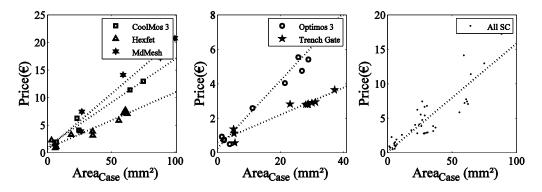

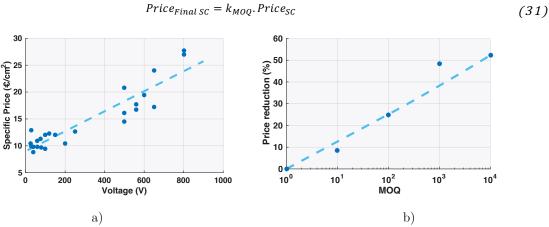

|    | 3.1.2.           | Semiconductor Packaging                                            |    |

| 3.1.1.           |                                                             |     |

|------------------|-------------------------------------------------------------|-----|

| 3.1.2.           |                                                             |     |

|                  | Semiconductor Modelling                                     |     |

| 3.2.1.           |                                                             |     |

| 3.2.2.           |                                                             |     |

| 3.2.3.           |                                                             |     |

| 3.2.1.           |                                                             |     |

| 3.2.2.           |                                                             |     |

| 3.2.3.           | - F                                                         |     |

|                  | Multi-domain Models                                         | -   |

| 3.3.1.           |                                                             |     |

| 3.3.2.           |                                                             |     |

| 3.3.3.<br>3.3.4. |                                                             |     |

|                  |                                                             |     |

|                  | Conclusion                                                  |     |

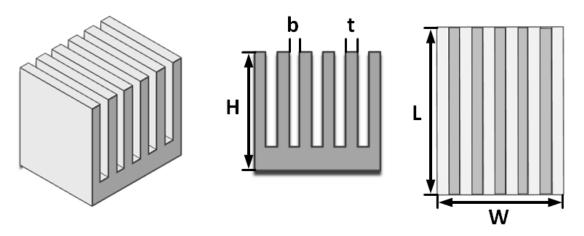

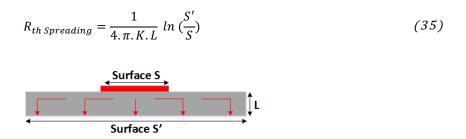

| Part B:          | Cooling                                                     | 87  |

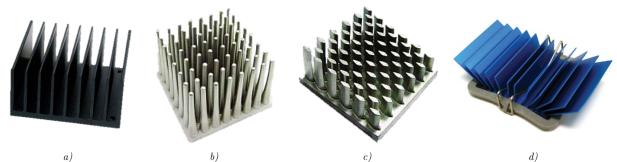

| 3.5.             | Technological Review                                        |     |

| 3.5.1.           | . Air Cooling                                               | 87  |

| 3.5.2.           | . Liquid Cooling                                            | 88  |

| 3.5.1.           | 0                                                           |     |

| 3.5.1.           | . Choice for the modelling work                             | 89  |

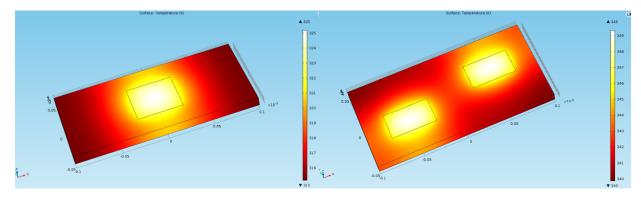

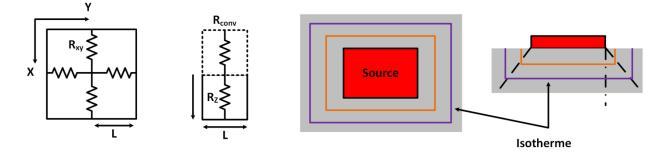

| 3.6.             | Cooling Modelling                                           |     |

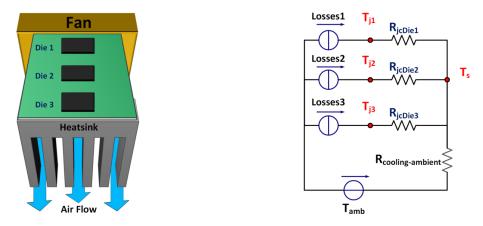

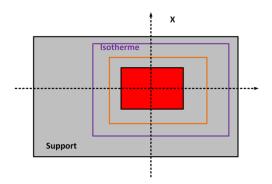

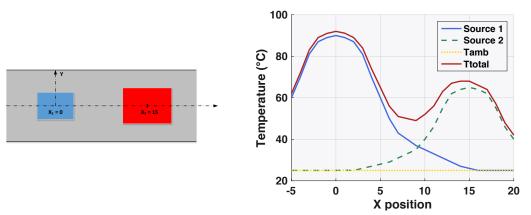

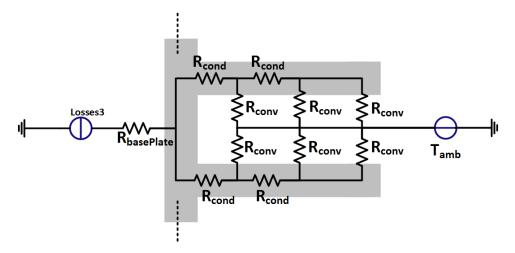

| 3.6.1.           | . Problem Setting                                           | 90  |

| 3.6.2.           | · · · · · · · · · · · · · · · · · · ·                       |     |

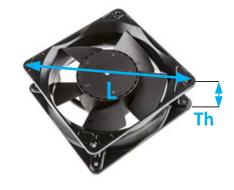

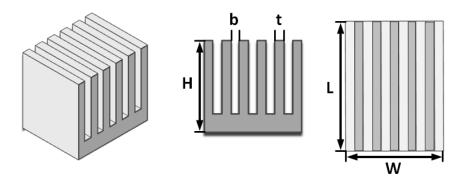

| 3.6.3.           | . Geometrical and Material description                      | 92  |

| 3.7.             | Multi-domain Models                                         |     |

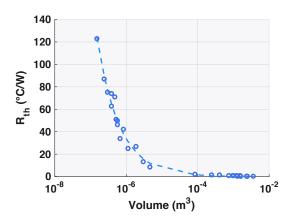

| 3.7.1.           | . Base-Plate                                                | 93  |

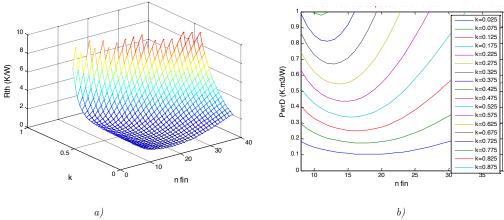

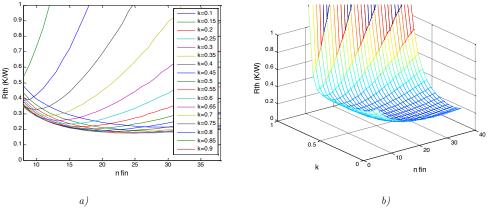

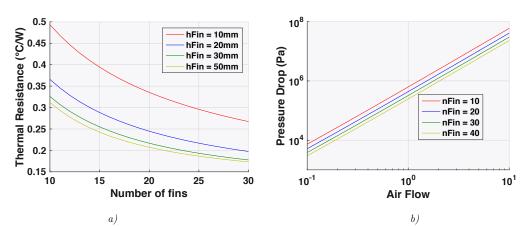

| 3.7.2.           | . Parallel-fins                                             | 98  |

| 3.7.3.           | · · · · · · · · · · · · · · · · · · ·                       |     |

| 3.7.4.           | . Cost models                                               | 107 |

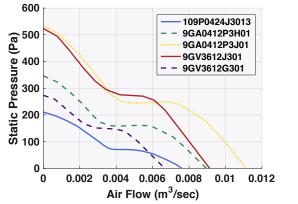

| 3.8.             | Fan Model                                                   | 107 |

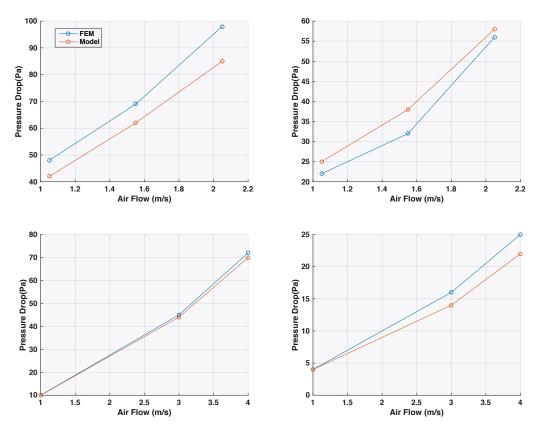

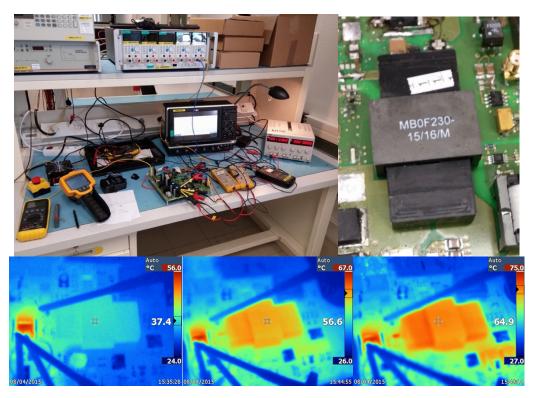

| 3.9.             | Experimental Validation                                     | 109 |

| 3.9.1.           | Forced Convection                                           | 109 |

| 3.9.1.           | . Natural Convection                                        | 110 |

| 3.9.1.           | . Aeronautical Environment                                  | 111 |

| 3.10.            | Conclusion                                                  | 112 |

| 4. Pas           | sive Part: Analytical models of Magnetics, Capacitors and I | GMC |

|                  |                                                             |     |

|                  |                                                             |     |

| Part A:          | Magnetic Devices                                            | 113 |

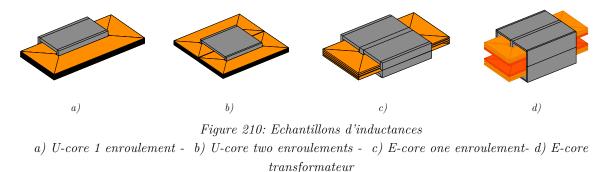

| 4.1.             | Magnetics Objects Overview                                  | 113 |

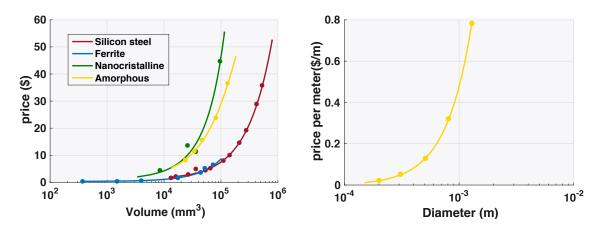

| 4.2.             | Materials                                                   | 115 |

| 4.2.1.           |                                                             |     |

| 4.2.2.           |                                                             |     |

| 4.3.             | Principle of the model                                      |     |

| 4.3.1.           | •                                                           |     |

| 4.3.2.           |                                                             |     |

| 4.3.3.           | •                                                           |     |

| 4.4. Multi-Domain Models                                                                                    |                      |

|-------------------------------------------------------------------------------------------------------------|----------------------|

| 4.4.1. Reluctance model                                                                                     |                      |

| 4.4.2. Losses                                                                                               |                      |

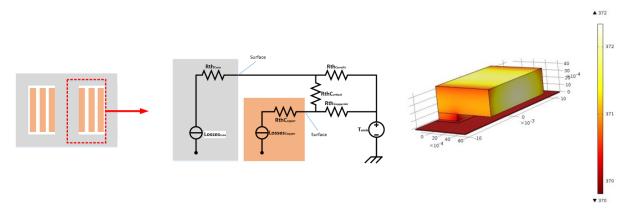

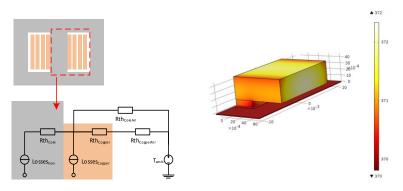

| 4.4.3. Thermal Model                                                                                        |                      |

| 4.4.4. Cost Model                                                                                           |                      |

| 4.5. Validation and Conclusion                                                                              |                      |

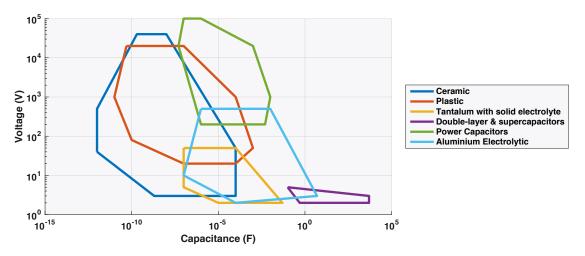

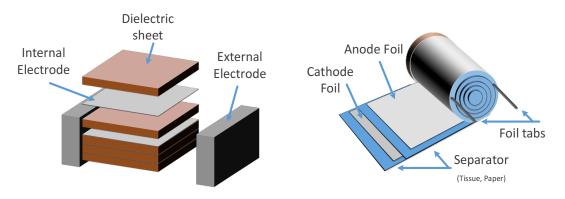

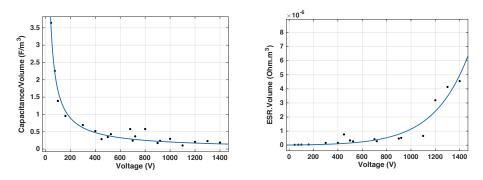

| Part B: Capacitor devices                                                                                   |                      |

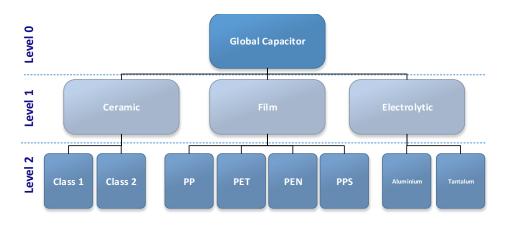

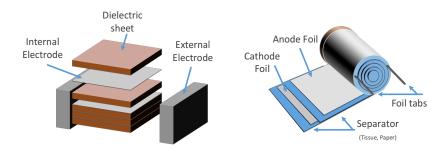

| 4.6. Capacitor Overview                                                                                     |                      |

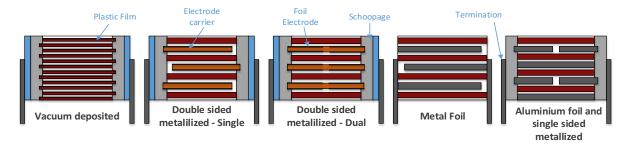

| 4.6.1. Technologies                                                                                         |                      |

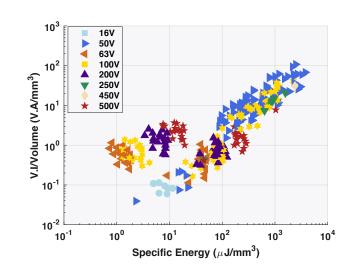

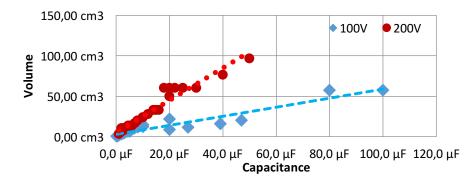

| 4.6.2. Figures of Merit                                                                                     | 134                  |

| 4.7. Principle of the model                                                                                 |                      |

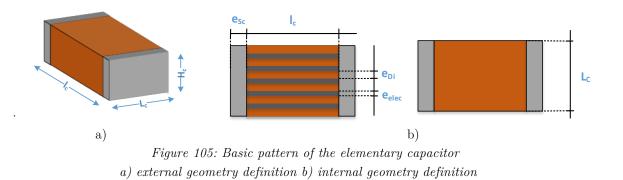

| 4.7.1. Problem Setting                                                                                      |                      |

| 4.7.2. Granularity                                                                                          |                      |

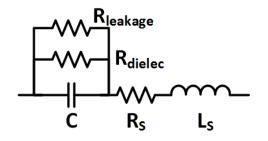

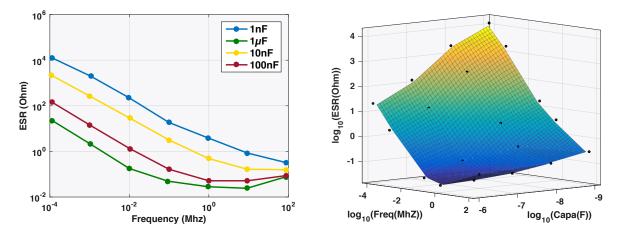

| 4.8. Model Definitions                                                                                      |                      |

| 4.8.1. Inverse Model                                                                                        |                      |

| 4.8.2. Direct Model                                                                                         |                      |

| 4.8.3. Macro-Capacitors and Database selection                                                              |                      |

| 4.9. Multi-Domain Models                                                                                    |                      |

| 4.9.1. Electrical                                                                                           |                      |

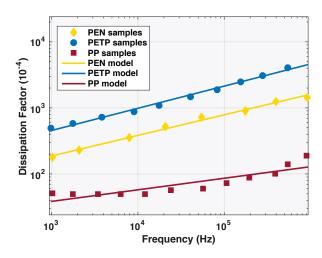

| 4.9.2. Losses Models                                                                                        |                      |

| 4.9.3. Thermal Model                                                                                        |                      |

| 4.9.4. Cost Model                                                                                           |                      |

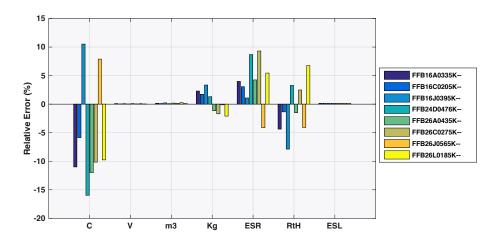

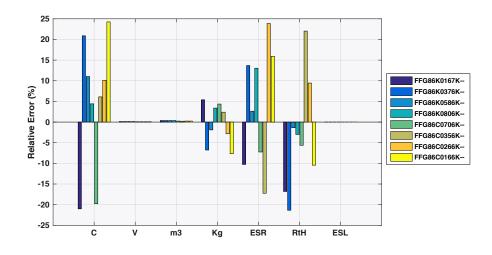

| 4.10. Validation                                                                                            |                      |

| 4.11. Conclusion                                                                                            |                      |

| Part C: EMC Filters                                                                                         |                      |

| 4.12. Perturbations, Standards and Measurement                                                              |                      |

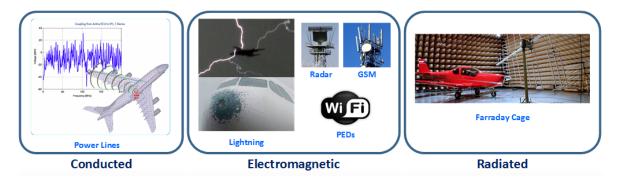

| 4.12.1. Types of EMI in embedded systems                                                                    |                      |

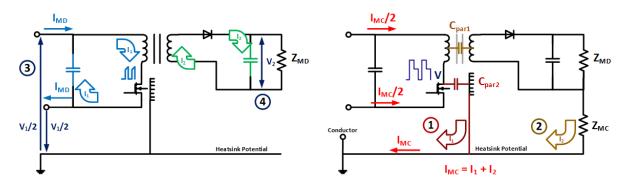

| 4.12.2. Conducted Disturbances in a Converter                                                               |                      |

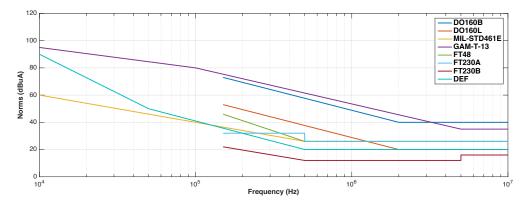

| 4.12.3. Standards                                                                                           |                      |

| 4.12.4. Measurements                                                                                        |                      |

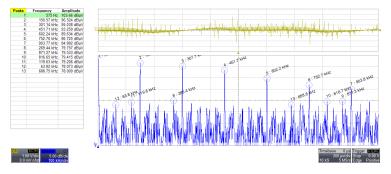

| 4.13. EMI and Filter Models                                                                                 |                      |

| 4.13.1. Filter Topology                                                                                     |                      |

| 4.13.1. Perturbation source Models                                                                          |                      |

| 4.13.2. Source-Path-Victim Description                                                                      |                      |

| 4.13.3. Temporal consideration                                                                              |                      |

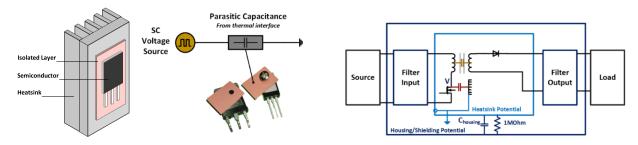

| 4.13.4. Parasitic capacitance Model                                                                         |                      |

| 4.13.5. Validation                                                                                          |                      |

| 4.14. Conclusion                                                                                            |                      |

| 5. Optimizations Examples of power devices, topologies                                                      | s and convortors 171 |

|                                                                                                             |                      |

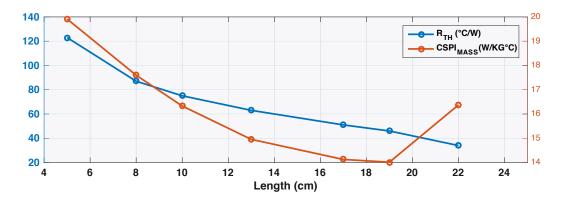

| 5.1. Optimizations of a Single Device                                                                       |                      |

| 5.1.1. Straight-fin Heatsink in Natural Convection<br>5.1.2. Straight-fin Heatsink in Air-Forced Convection |                      |

| 0                                                                                                           |                      |

| 5.2. Optimizations of Topologies                                                                            |                      |

| 5.2.1. Optimizations of a Differential Filter Topology                                                      |                      |

| 5.2.2. Optimizations of Active Topologies                                                                   |                      |

| 5.3. Conclusion                                                                                             |                      |

| 5.3.1. Success                                                                                              |                      |

|      | 5.3.2.             | Missing part                                                 | 196      |

|------|--------------------|--------------------------------------------------------------|----------|

| 6.   | Conc               | lusion and Future Work                                       |          |

|      | 6.1. C             | onclusive summary                                            |          |

|      | 6.2. Fe            | edback and Future Fields of research                         |          |

|      | 6.2.1.             | Collect and Stock Data                                       | 200      |

|      | 6.2.2.             | Domain of Validity                                           | 201      |

|      | 6.2.3.             | Validations of Models                                        | 202      |

|      | 6.2.4.             | Electrical Solvers                                           | 203      |

|      | 6.2.5.             | Model Integration                                            |          |

|      | 6.2.6.             | Convergence of the Solution                                  |          |

|      | 6.2.7.             | Software Considerations                                      |          |

|      | 6.2.8.             | User Interface and User Experience                           |          |

|      | 6.2.9.             | Results Exploitation                                         | 205      |

| 7.   | Refer              | ences                                                        | 207      |

| 8.   | Anne               | xe 1 - Electrical Model SC                                   | 218      |

| 9.   | Anne               | xe 2 – Validation Cooling                                    | 222      |

| 10.  | Anne               | xe 3 – Transfer function approach for the EMC perturb        | ations – |

| Co   | mmon N             | Iode                                                         |          |

| 11.  | Anne               | xe 4 – BBCU Design Challenges                                | 228      |

|      | 11.1.              | Specifications                                               |          |

|      | 11.2.              | Design Challenges for the BBCU                               |          |

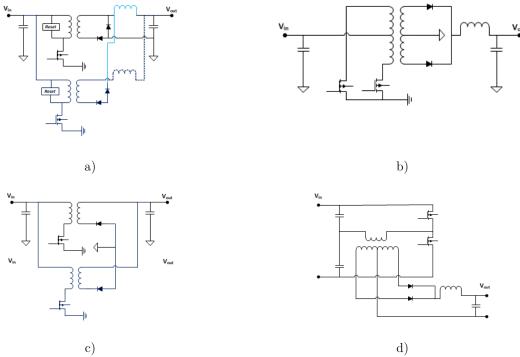

|      | 11.3.              | Annexe 4 – Bidirectional and Isolated DC-DC Converter Review |          |

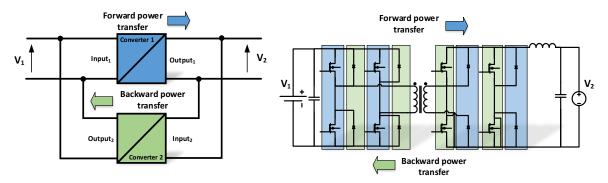

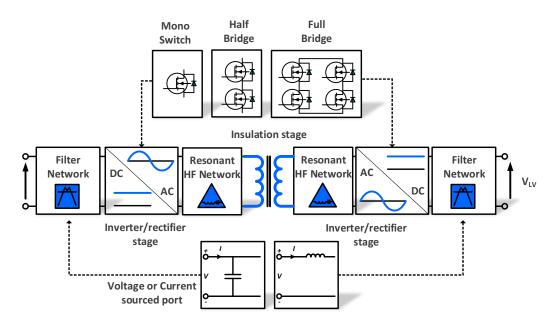

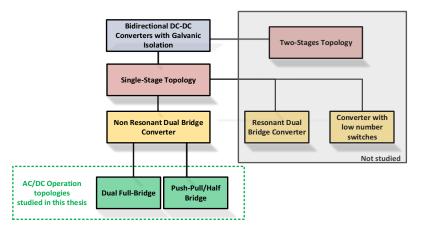

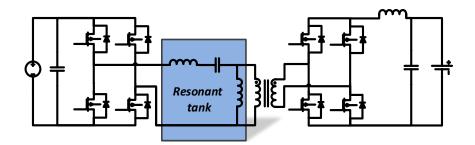

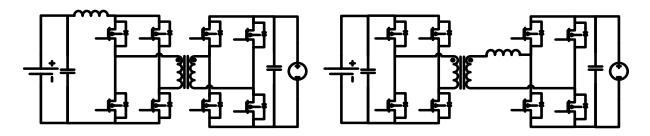

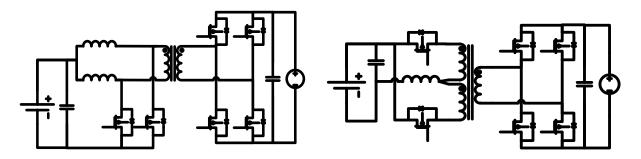

|      | 11.3.1.<br>11.3.1. | Principles                                                   |          |

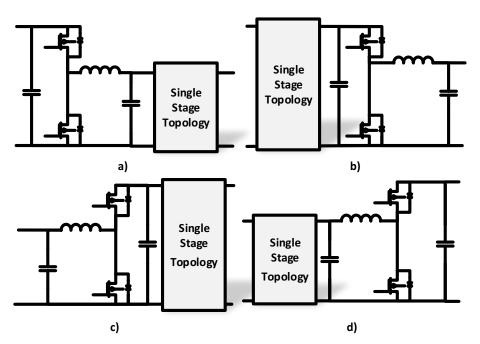

|      | 11.3.1.            | Topologies of Conversion                                     |          |

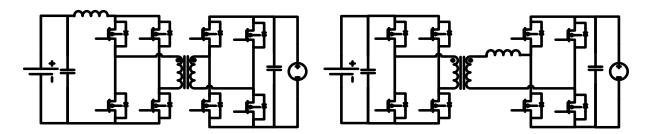

|      | 11.3.3.            | Non Resonant Dual Bridge Converters                          |          |

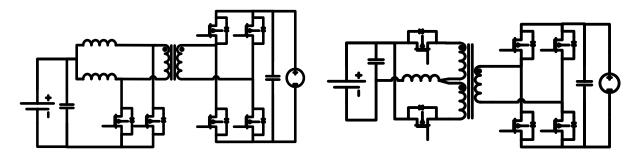

|      | 11.3.4.            | Topology Improvements                                        |          |

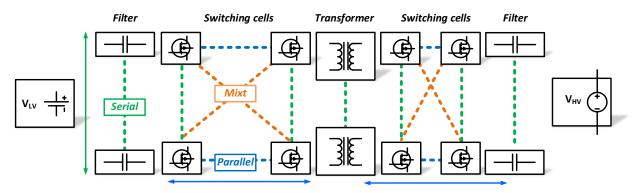

|      | 11.3.5.            | Multi-level Topologies                                       |          |

|      |                    |                                                              |          |

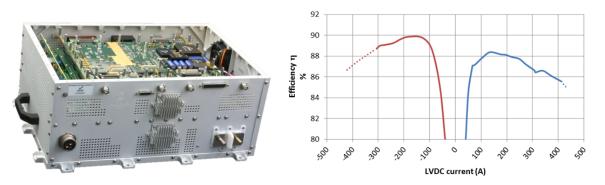

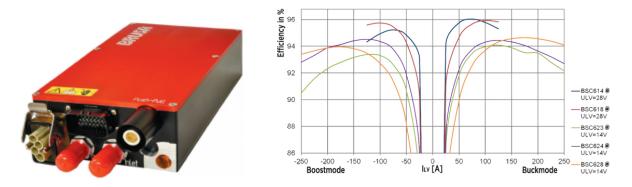

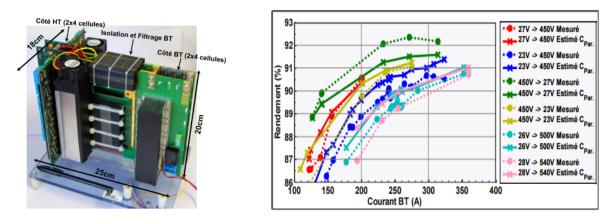

| 12.  | Anne               | xe 5 – Prototypes Review                                     | 238      |

|      | 12.1.1.            |                                                              |          |

|      | 12.1.2.            | Research Laboratory Converters                               | 239      |

|      | Resume             | of the prototypes and comparison                             |          |

| 13.  | $\mathbf{Syntl}$   | nèse en Français                                             | 242      |

| 15.  | 1 Cha              | pitre 1: Contexte de la thèse                                | 242      |

| 15.2 | 2 Cha              | apitre 2 : Méthodologie de design optimal                    | 245      |

| 15.1 | 3 Cha              | apitre 3: Modèles simplifiés des composants actifs           | 250      |

| 15.4 |                    | apitre 4 : Modèles simplifiés des composants passifs         |          |

| 15.  |                    | apitre 5: Optimisation de composants et topologies dédié     |          |

|      |                    | s aéronautiques                                              |          |

| 15.6 ( | Chapitre 6 : | Conclusion et | Perspectives |  |

|--------|--------------|---------------|--------------|--|

|--------|--------------|---------------|--------------|--|

# List of Abbreviations

| AC   | Alternating Current            |

|------|--------------------------------|

| A/C  | Aircraft                       |

| ATA  | Air Transport Association      |

| BBCU | Buck Boost Converter Unit      |

| CAD  | Computer-Aided Design          |

| DBC  | Direct-Bonded Copper           |

| DC   | Direct Current                 |

| DF   | Dissipation Factor             |

| EMC  | Electro Magnetic Compatibility |

| EMI  | Electro Magnetic Interference  |

| FEM  | Finite Element Method          |

| FOM  | Figure of Merit                |

| HV   | High Voltage                   |

| LV   | Low Voltage                    |

| MEA  | More Electrical Aircraft       |

| OOP  | Object-oriented Programming    |

| PCB  | Print Circuit Board            |

| SC   | Semiconductor                  |

| UI   | User Interface                 |

|      |                                |

# Chapter 1

# 1. Introduction

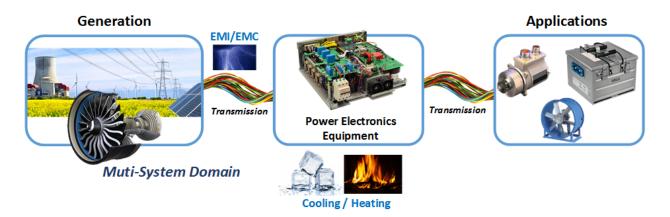

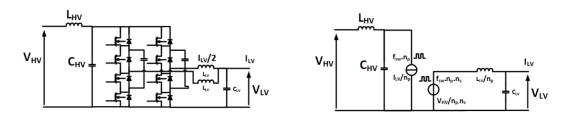

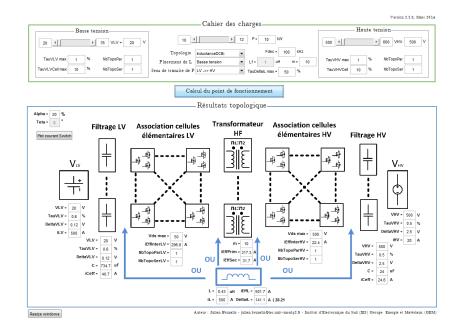

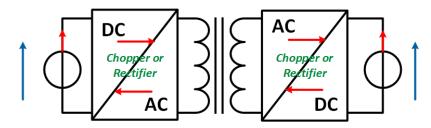

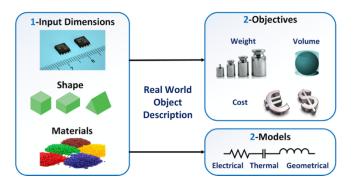

Power electronics is a scientific and technical discipline whose purpose is to convert the electric power from one form to another. As a computer processes information, a power electronics equipment processes power (Figure 1). To realize this conversion, we design static converters which are connected to their sources and must provide processed and suitable electrical power according to demanding specifications and be immune to perturbations like EMC or heat stress. Today the most common approach of designing a converter remains the use of pre-studies with more or less assumptions, the design experience or even the method of "trial-error". However, more and more design tools are available on the market to minimize the conception cycles before getting a final functional product. Yet, no current tools or methods give directly a design accurate enough to define the best topologies, technologies or ideal sizing of components. In addition, this optimization practice has been used for many years in other areas such as mechanics, with for instance the design of the aircraft structures [1] [2], and is called "preliminary design" or "computer-aided optimal design". Consequently, this thesis aims to propose a methodology to perform a similar task in the field of power electronics. Then, this optimal design approach will be used on a challenging application dedicated to new embedded aeronautical converter, like the BBCU. This converter is a centrepiece of the electrical architecture of a future commercial aircraft, called the More Electrical Aircraft.

In this introductive chapter, the context of this study and the problematic of the computer-aided optimal design are developed. First of all, the "More Electrical Aircraft" concept and the implementation of power electronics in commercial aircraft will be exposed, leading to the creation of new converters that require to be optimized, especially from preliminary studies. Then, we will explain the objectives and expectations of the assisted design used to optimize any kind of power converter. Finally, and before revealing the axes of research developed all along this thesis, figure of improvements in power electronics through the optimal design will be introduced.

Figure 1: Power electronics principle schematic

# 1.1. The More Electrical Aircraft (MEA)

### 1.1.1. Review of the MEA

In the last decades, some important steps have already been achieved towards a more electrical airplane, particularly with the increasing role of the electrical energy in aviation board networks. At the beginning, its use was limited to navigation and flight instruments, and then it was gradually increase to improve the comfort and In-Flight Entertainment (lighting, kitchen, video equipment). New applications have emerged to optimize the aircraft operation, such as power management of the flight controls on the Airbus A320 in the 1980s (Fly-by-wire). The development of the Airbus A380 was a further step of innovation in electrical technologies: free AC grid frequency (360-800Hz), electrical emergency system, new electro-hydraulic actuators for flight controls and Solid State Power Controllers for low current ratings.

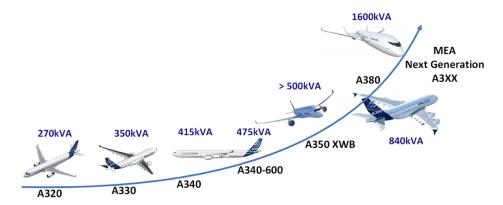

Nowadays, the More Electrical Aircraft (MEA) concept offers high potential for future air transport and is one step towards more efficient planes. Four secondary vectors of energy dedicated to the system servitudes are used on aircraft and are mainly obtained from propulsion engines: mechanical, hydraulic, electrical and pneumatic energy. The MEA aims to replace hydraulic and pneumatic systems by electrical ones, called respectively "Hydraulicless "or "Bleedless" architectures [3] [4], reducing overall system weight and offering an easier maintenance. Moreover, these new architectures imply new propulsion engines that improved the overall efficiency and the implementation of new desirable characteristics of electrical systems, and so increases their number. Indeed, the "MEA" label relates to the potential improvement that could offer electrical systems compared to the other energy forms. In fact, conventional solutions are already optimized and do not indicate significant changes in a close future. Therefore, many technological, industrial, functional and structural improvements are expected for the equipment. As it is connected to electrical networks, the term "Power-by-wire" is then used. Because of all these changes, the global electrical power of the aircraft is continuously increasing (Figure 2).

Figure 2: Electrical generation capacity installed on Airbus A/Cs

#### Introduction

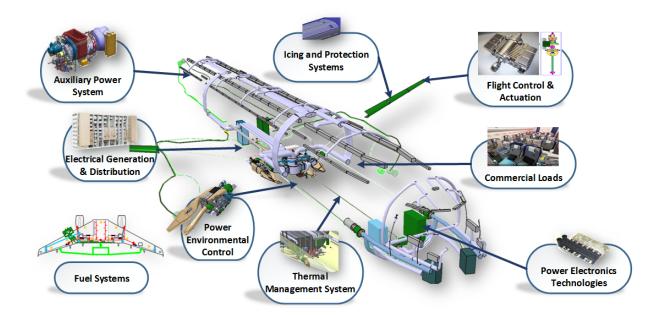

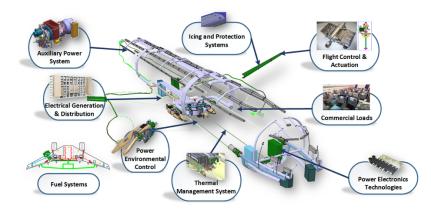

For the next generation of Airbus aircraft (Boeing has already used electrical concepts in the 787 [5]), other functions may be performed electrically, such as wheel braking, air conditioning and engine start (Figure 3). Some examples of characteristics of the electrical systems can be exposed:

- Controllability implying the power on demand

- **Re-configurability**, maintaining the functionality during faults

- Advanced diagnostics and prognostics, which is a more intelligent maintenance to increase the aircraft availability

- **Homogeneous interface** between the different components: electrical, power electronics, electronics types

- Easier replacement of the systems

Moreover, simulations should be more efficient to study the design optimization and get more facts and knowledge for engineering design. In addition, the change to more electrification covering both the aerospace and automotive industries [6] [7], should lead to an equipment standardization, which will reduce the assembly cost and time. The aircraft manufacturing is also facilitated by the greater flexibility of the electrical installation compared to the hydraulic and pneumatic systems. For instance, the installation of pipes and ducts is more restrictive and electrical wiring brings additional degrees of freedom. In a few words, this technical rupture will enhance the aircraft design, whose main purpose is to reduce dramatically the total aircraft weight in order to reduce fuel consumption, operating costs and environmental impact. However, it requires an advanced work on the different electrical and power electronics systems, which are present everywhere in the aircraft.

# 1.1.2. Power Electronics Integration

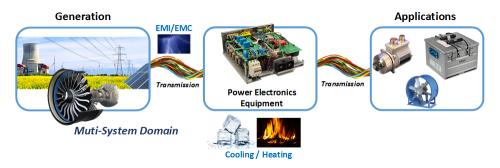

In order to better understand the impact of power electronics in the MEA, it is important to present systems powered and/or controlled by those means. Indeed, current and future developments of electrical architectures are necessarily linked to the development of power electronics applications (Figure 3). In the latest generation of commercial aircraft, the presence of static converters in the network was limited to a reduced amount of systems: food commercial expenses (galleys), rectifiers (115V-400Hz/28V) and emergency inverters (28V/115V-400Hz). With the energy management evolution in the MEA and the increasing power demand, the number of classical AC/DC and DC/AC converters have increased. In other words, power electronics have been identified as a key success factor for the future aircraft generation, and conquer more various systems of the aircraft. These systems are classified in ATA or Air Transport Association [8], a common referencing standard for all commercial aircraft, detailing the different systems and ATA's using power electronics can be found in [9] [10] [11]. In the context of this thesis, we focused on the ATA 24, i.e. the electrical power generation and distribution, with the emergence of a HDVC network [12] [3] in the aircraft due to the new MEA architecture.

Figure 3: Opportunities of Power Electronics on Systems

|        | Definition                                      | Example                                                                                         |

|--------|-------------------------------------------------|-------------------------------------------------------------------------------------------------|

| ATA 21 | Air conditioning & pressurization system        | Fans supplied with high power until 9.8 kVA $$                                                  |

| ATA 24 | Electrical Power Generation<br>and Distribution | Variable Frequency Generator (VFG), Solid-State Power Control (SSPC),<br>new HVDC network       |

| ATA 27 | Flight Control system                           | Increase of electrical systems, electrical actuators                                            |

| ATA 28 | Fuel system                                     | Supply by power converters on free frequency networks                                           |

| ATA 29 | Hydraulic System                                | Each hydraulic circuit includes an electrical pump                                              |

| ATA 32 | Landing Gear Systems                            | Actuators for the extension, retraction and orientation of systems, doors, the front wheel etc. |

| ATA 78 | Thrust reversers                                | Require high power for a short time through an all-electric system (until $25 \text{kVA}$ ).    |

Table 1: Examples of power electronics use within different A/C systems

# 1.1.3. Impact of the new HVDC network

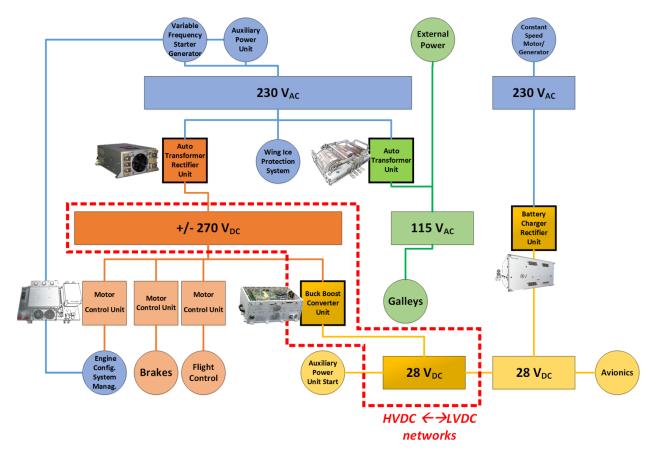

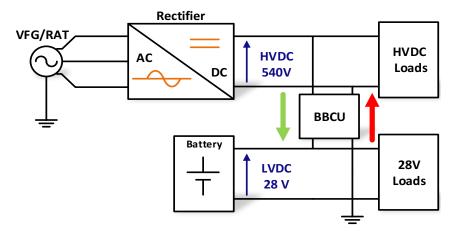

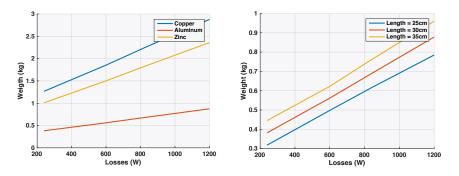

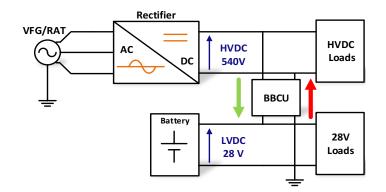

As discussed in previous sections, the number of loads and electrical equipment in commercial aircraft is increasing exponentially. One of the possible answers to this problematic is the creation of an 'HVDC network' [12]. For Airbus, 'HVDC network' means a DC network composed of two rails with potentials equal to respectively +270V and -270V, the reference of potential being the plane structure. Indeed, it allows to not integrate many AC/DC rectifiers as currently done on aircraft embedding an AC network. It obviously implies a significant gain in the global weight of electrical systems [13]. The 'Bleedless' architecture represented in Figure 4 is one of the propositions offering new electrical energy management in the aircraft, including an HVDC network and other

#### Chapter 1

#### Introduction

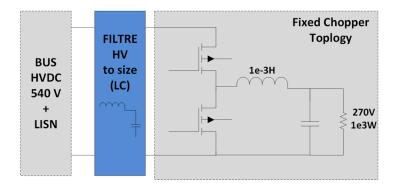

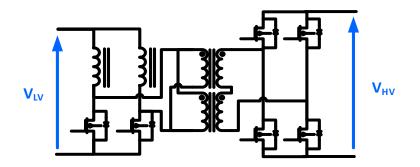

innovations [3]. This network requires the creation of numerous new power converters, and among them one that links the HVDC 540V network to the LVDC (or DC) 28V network. It is the Buck Boost Converter Unit or BBCU, one study case of this thesis introduced in Chapter 5.

Figure 4: Example of a Bleedless architecture with the implementation of the BBCU functions [14]

However, there are high expectations on the converter power density and efficiency because of the ambition to board them in the MEA (Erreur ! Nous n'avons pas trouvé la source du renvoi.). Therefore, a new approach is proposed in this thesis in order to optimize the converter design and sizing. Indeed, a new methodology in power electronics is used here: the computer-aided and optimal design of static converters, also called virtual prototyping. As a conclusion, beyond the HVDC requirements in the MEA, the power converters will have to reach new level of integration and efficiency in order to be compliant with the new expectations, efficiency and higher constraints. Thus, a new global problematic arises in the power electronics field in order to design the most appropriate converters: how to define the best and more appropriate technologies and get the optimal sizing of each component related to a specific application? This optimal design can only be reached thanks the help of computational tools and optimization routines, which is generally referred to as computer-aided design and optimal design.

# 1.2. Computer-aided design in Power Electronics

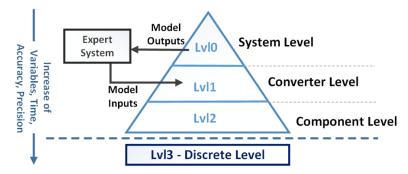

To face these new challenges, specific tools allowing a more efficient and faster design of power converters are needed and this requires working at two different levels;

- Component-level multi-physic models describing the different interactions between the components of a converter that all need to be taken into account in the design process. This includes electrical, thermal, magnetics, and fluid mechanics models. Concerning the electrical model, it should be noted that the losses in each component, though very small compared to the total power flowing through the converter, have a critical influence on design trade-offs and on the performances of the converter. These losses are generally governed by second order phenomena involving complicated physics; (physics ruling conduction and switching losses in semiconductors, physics ruling core losses in magnetic cores, physics ruling AC current distribution and losses in conductors...). Easier but important as well, weight models are also needed since the weight of the converter is important to the user.

- Converter-level formulation and tools to describe the interactions between the components (solver, or solvers for the different physics), the evolution of performances (weight, efficiency...) as a function of design parameters (converter topology, and components values, dimensions, materials or shape....). The trade-offs between performances result of complex interactions between many design parameters (including continuous and discrete variables) and the problems is generally complex enough to give many different local minima. As a consequence, optimization routines are generally needed to address such a problem, and convergence depends widely on the problem formulation and type of algorithm used.

The purpose of this section is to provide definitions and identify the new expectations of the computer-aided optimal design. The aim is to get in a minimum of time a solution that matches all requirements and is close to the best design. It is generally very difficult to guarantee that a global optimum is reached, so although optimization routines are used, it would be better to speak of automated design than optimal design. In future work, a first step would be to switch to algorithm providing boundaries of the objective function in subsets of the design space, which allows deriving an upper bound of the difference between the current objective function and its absolute minimum.

The aim of the present work is to build models and establish formulations giving at least a solution matching all requirements, the requirements being in the way that is most convenient to the designer

Previous studies have been realized on individual components in the Laplace laboratory:

- Optimization of magnetics components [15]

- Design of a DC-DC converter with a succession of local optimizations on the different parts of the converter [16].

These works are used as a basis of this thesis, but they never considered a strategy to create a direct optimization of a global converter, including EMI studies. Thus, the methods have been thoroughly reconsidered.

### **1.2.1.** New expectations in Power Electronics

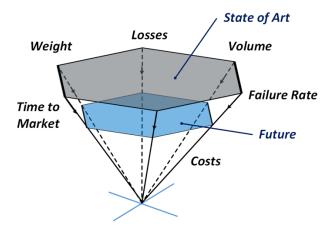

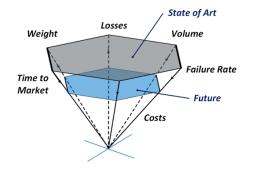

First of all, we need to identify the new expectations on power electronics systems, as demonstrated in [17]. They are used in a wide range of applications, such as industry automation, processes, communication, transportation and lighting. The current static converters are quite mature and design criteria include cost reductions or improved reliability. In order to measure these needs, numerous **performance indices** (Figure 5) are often stated:

- $\circ$  Power density [kW/dm<sup>3</sup>]

- Power per Unit Weight [kW/kg]

- Relative Costs [kW/\$] or [kW/€]

- Relative losses [%]

- Failure Rate [h<sup>-1</sup>]

- $\circ$  Environmental Impact from metal [Kg<sub>material</sub>/kW] or silcon [cm<sub>Si</sub>/kW]

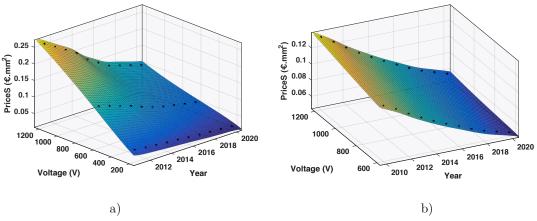

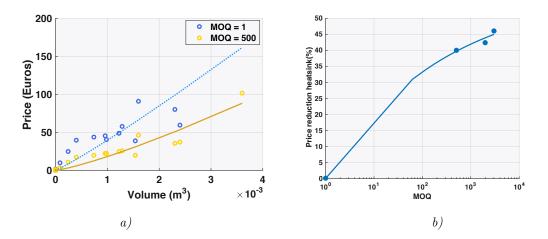

It should be noted that the global cost of a converter is generally the criterium that is the most important, but it is also the most difficult to evaluate since it derives from parameters that depend on time, market, customer/retailer agreements, number of items produced, etc.... Academic research is likely to produce design tools handling physics-based phenomena and performances, but only industry seems to be able to produce relevant cost models. To this extent collaboration between both worlds is a must.

Moreover, in a converter design we rarely consider only one criteria of improvement. Therefore, trade-offs are needed in order to create the best trade-off thanks to multi-objective optimization (Figure 5).

Figure 5: Current and Future Requirements in Power Electronics, extracted from [17]

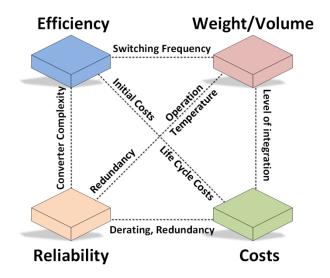

However, all **Performance Indices** cannot be maximized independently (Figure 6). Therefore, designers need to make choices and if advanced design tools a certain flexibility must be provided to allow guiding the design in a given direction, priorizing a given set of performances or using a ponderated sum of basic criteria.

Figure 6: Example of opposite objectives in a power electronic equipment, extracted from [17]

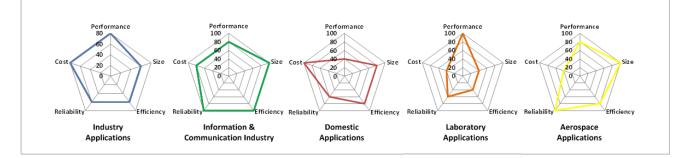

Depending on the field of application, the market to be addressed, or company-specific design rules, different weights of the criteria can be used and quite different solutions can be found (Figure 7). As a conclusion, advanced modelling tools are required to calculate these specific performance profiles quickly and accurately, but also to switch easily from one to another.

Figure 7: Weight repartition on performance indices as a function of the domain application, extracted from

[17]

### 1.2.2. Digitalization & Virtual Prototyping

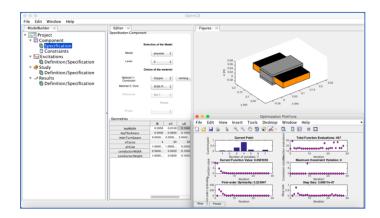

In order to meet previous expectations and performances (1.2.1), new tools such as multi-domain modelling and simulation, optimization and virtual prototyping are required. The transition from hardware prototyping to multi-domain modelling, simulation and optimization has started in R&D laboratories [17] and this is sometimes referred to as "Digitalization" (Figure 8).

Figure 8: The digitalization transition in power electronics thanks to the virtual prototyping, extracted from [17]

In Power Electronics, this digitalization aims at providing software that can improve the converters corresponding to any type of conversion (DC/DC, DC/AC...). The expected features to be included in the computer-aided tool are:

#### **Design Optimizations:**

- Advanced Simulations that allow multi-objective optimization and identify performance limits results, such as "Pareto Fronts "or comparisons. The multiple objectives have to be easily switchable (optimization of different goals) and tuneable if weight are applied on them (each objective has a definite weight).

- Detailed component sizing in terms of shape, dimensions, material, etc. and their operation parameters (frequency, temperature, duty cycle)

- Trade-off Analysis by successive optimizations, with a variation of study parameter like topologies, technologies and key parameters or even sensitivity studies to evaluate the technology advancements and understand possible mutual dependencies of performances

- Solvers and Simulations

#### Models Library:

- New models creation of power components dedicated to virtual prototyping, covering the wide range of custom and COTS (Components-Off-The-Shelf) devices

- Application of specific solutions, like devices (e.g. PCB, Power Module, Chips)

- Comprehensive modelling and physical phenomena (e.g. Cost, EMI, Reliability)

- Minimization of the simulation time with new solvers or strategies like model order reduction, simplification and granularity

#### Posteriori Verification:

Interactive features with commercial and specialized software, such as post-treatment validation (solvers, FEM (Finite Element Modelling), CAD (Computer-Aided Design) etc.)

#### From the equipment to systems:

• Ease of integration into systems to extend gradually the spectrum of the equipment design for a more global optimization. For instance, two systems that have been optimized individually, are not necessarily the optimum when put together. Maybe they can lose all of their assets calculated during their sizing once interconnected, because of negative coupled effects?  Simulation of what cannot (anymore?) be measured in real systems (High Integration Level), e.g. current in a fast switching semiconductor: inserting a current sensor may modify the switching waveforms

#### Big Data:

• Database management, analysis of this data (devices, tests, issues, quality etc.), obsolescence treatment

#### Efficiency:

- o Low Complexity to keep the tool accessible, and modularity / scalability to make it evolve

- o Robustness, quickness and reliability of results

- o Accessible UI (User Interface) and tools for any user, processing all the points of this list

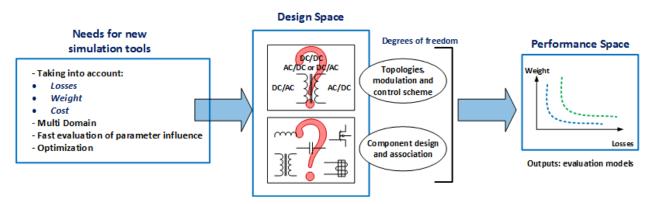

From previous expectations, we can now deduce what should be the degree of freedom left to the user (or to the tool?), in order to get a relevant design and realize any sort of project (Figure 9). Thus, a designer could use and compose with these "objects":

- o Devices

- o Topologies

- o Modulation and Control

- o Design Procedure

- o Modularization / Standardization / Economy of Scale

- o Manufacturing

- New/Custom applications

Figure 9: Requirements for new simulation tools in Power Electronics

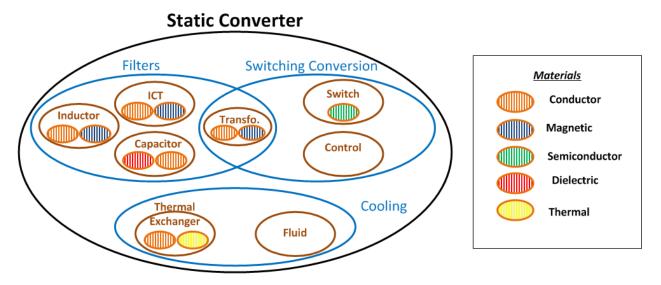

Due to the digitalization of the design process, some engineering and scientific fields are more and more correlated. For instance, in order to realize multi-objective optimizations, we require some expertise from computer sciences, mathematics and electrical engineering. In addition, numerous domains have to be considered when creating power electronics models, in order to represent the different physics or interesting aspects included in a static converter:

• **Electric**, the most obvious in a power electronics converter, which simulates the waveforms of voltage and current.

#### Introduction

- **Magnetic**, in order to simulate an advanced physics inside the magnetic components such as inductors and transformers

- Thermal, to evaluate the heat stress imposed to the component to avoid their destruction

- **Mechanical**, to get an idea of a 3D representation and physical parameters such as the weight and volume

- **Fluidic**, especially for the cooling system where constraints such as pressure drop or maximum flow are sizing the converter

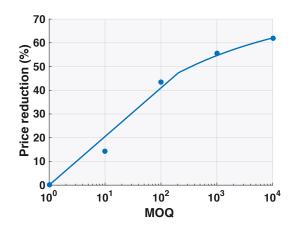

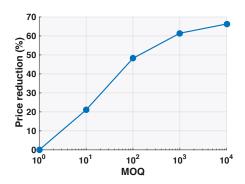

- Economical considerations, which are definitely outside of physics but at least as complex, should also be included. Some of the complexity here is related to the fact that cost can be different for one player or the other... (quantity-dependent prices) as previously introduced.

As a conclusion, the Pre-Design still has some "Remaining Challenge" ahead and numerous functions to build in order to provide an efficient high-level decision-making tool. It should be a pre-design and multi-domain software realizing high level decisions, in addition of the current specialized software. Its aim should not be to substitute the role of current electrical solvers or dedicated physical software such as FEM. However, bridges between predesign, and design software are considered as mandatory in the future to accelerate the designs. Another important point will be to change the habits of Power Electronics designers; it might take some time for these tools to become mature and be accepted by the industry. We can mention "Gecko" as an example, which is an emergent software suite used as an advanced Power Electronics Design Platform. It includes Modelling & design (circuit simulation, thermal simulation, FEM Simulation) [18]. In addition, the virtual prototyping requires a new way to create models, which will be detailed in this thesis. Indeed, components, systems, topologies and controls are concerned by this modelling and need to be quick to compute, with a control on the assumptions and the inaccuracy they may create.

# 1.2.3. Pre-design VS Detailed-Design

Once the needs for computer-aided design in power electronics have been exposed, it is interesting to redefine the difference between detailed design and pre-design. In fact, the detailed design is the final design that will be implemented physically in the equipment, in order to perform a specific function. This phase takes into account all the very specific characteristics of each component. However, it is complicated to get these final characteristics directly in the pre-design phase. The subject of this manuscript is the creation of a tool and a method for the pre-design. The tool should do the same work, but it involves simplified models that are much more simple but less accurate. They involve assumptions – more or less strong -, include a description of only the phenomena that are assumed to be predominant. The final pre-design may need different types of post-processing and checks:

• it must match all requirements, at least within the limits of the accuracy of the models. This basic check is inherent in most optimization routines and expressed as a simple output flag.

- The proposed pre-design might not be the optimal design (global minimum of objective function) but it should at least be a "good" design; a strict formulation of "good" design would be that for this design the objective function is for example less than x% above the global minimum of the objective function. Today we are not able to give such a guarantee, but tools giving such an indication have been identified and they might be used in the future to better evaluate our results. This optimality is also related to the models used to formulate the problem.

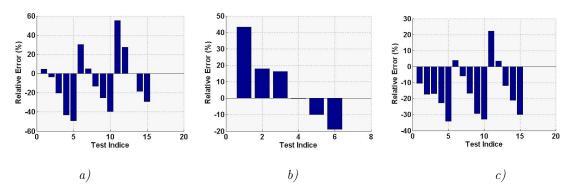

- Another type of post processing is to check that the simplified models are still valid in the conditions of the predesign. This can be done using more sophisticated models at this point only. For example, 3D finite elements simulation can be used to check the losses at the nominal point in a magnetic component that was designed using optimization routine and a much simpler model of magnetic component.

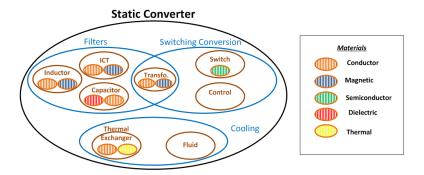

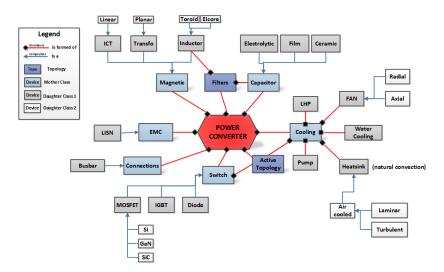

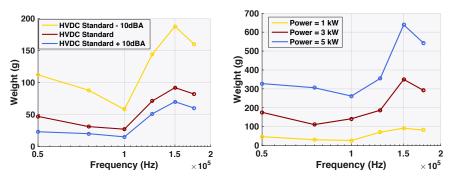

### **1.2.4.** Problematics for sizing a Power Converter

New requirements on the methodology, expected results and functions were presented in the previous part. We can now express in terms of electrical engineering formalism our expectations in resolving an optimal design problem on a power converter. Indeed, the resolution of the design problem must answer to the global and recurrent issues met during a converter sizing. These issues are related to the design (e.g. topology, control) and choice of components (e.g. material, technology) among the whole possibilities, part number and combinations available on the market, where the main ones are defined hereafter. The aim of this approach is to revisit current design methods of power systems. Today manual or local optimizations are realized individually on each component, setting assumptions without knowing the real impact on the global system. On the contrary, the optimal design addresses directly all parameters, components and their combinations in the converter. It leads to the best design by realizing a global trade-off according to one or several objectives. Thus, a global optimum is reached with a well-tuned computational tool. To illustrate this problematic, we have raised open questions. They formulate the different challenges that the optimal design has to solve in order to become an essential design tool for power electronics systems.

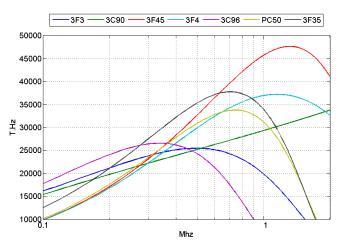

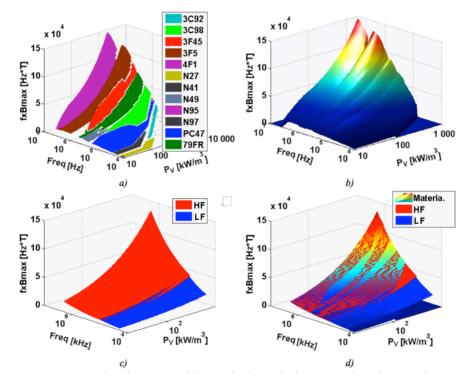

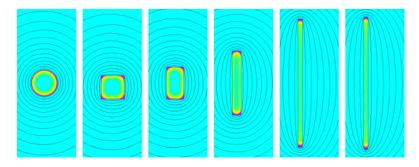

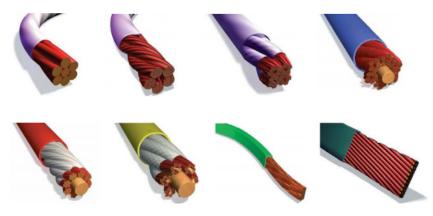

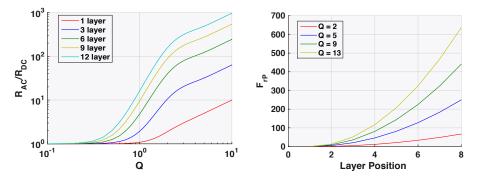

• Which material, technology and geometry should be used to create the different components? Increasing the frequency of the passive components implies the use of components suitable for high frequency [19]. However, it is difficult to find large magnetic cores capable of operating at high power/high frequency (tens of kW, tens or hundreds of kHz), most capacitors also have resonance frequencies around 1 MHz and a simple conductor becomes worse when frequency increases because of skin and proximity effects. Furthermore, a more sophisticated technology is used to switch at higher frequency (stray inductance, gate drivers...) and now that power devices are switching so fast, the calculation time of digital controllers can also be responsible for calculation time limitations. The implementation of the commutation cell becomes more complex and of the regulators switching at higher frequency and even the control technique demands for the semiconductors also rise in terms of speed; thus, the integration becomes an inevitable solution to overcome all these problems [20].

#### Chapter 1

#### Introduction

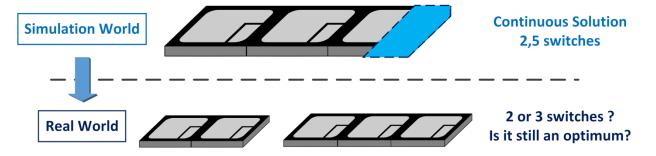

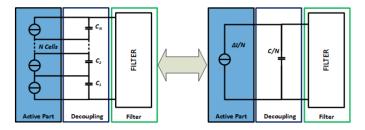

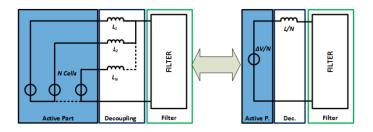

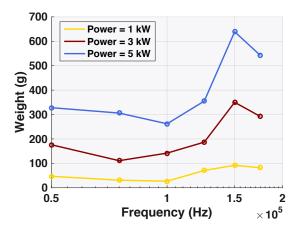

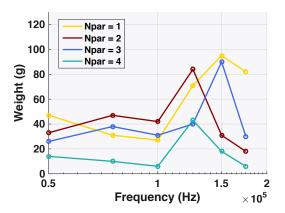

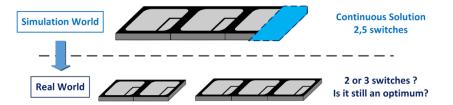

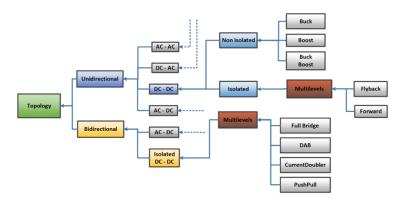

• What is the best conversion topology to be used? And should we use the multilevel concept? If so, how many levels should be used?

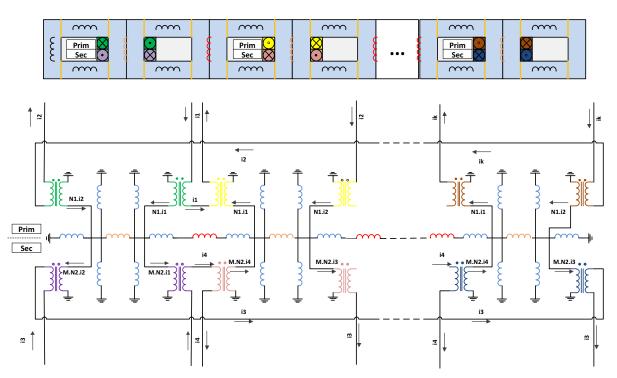

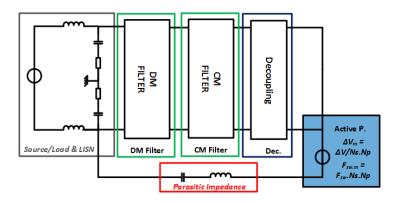

Nowadays, making a trade-off between several topologies for a same application is still a timeconsuming task. Assumptions and simplification are made in order to design a converter and it must be checked that these assumptions are valid in the conditions imposed by final design [21]. Employing multilevel topologies should be explored since it increases the degrees of freedom but it may lead to not so standard conditions and bring unusual design trade-offs [22] [23]. For example, in two-level converter, the trade-off between heatsink and filter weight is governed by switching losses and filter design that depend on the same parameter, the switching frequency; but in multilevel design, the frequency seen by the filters is the switching frequency multiplied by the number of cells and this may change the game. These topologies also allow distributing the voltage and current among several switches and commutation cells. Thus, the use of more efficient semiconductors with reduced sizes is possible, which is in line with a reduction of the size of cooling system and passive components. However, a large number of cells involves more control circuits and therefore a greater complexity of the circuit [24], and it must be checked that voltage and current are respectively balanced between the different series/parallel cells [25].

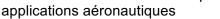

• How far should the switching frequency to be increased to reduce the overall size of the converter?

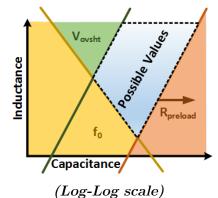

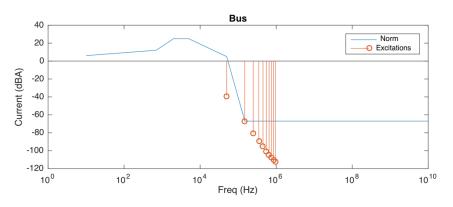

Passives components are often the bulkiest components in a converter, and a widespread idea is to increase the switching frequency of the semiconductors to reduce their volume [26]. This is relevant for components such as isolation transformers, DC bus capacitors, and in general internal filters or filters designed for ripple only, but the behaviour can be quite different when a frequency-domain standard with a salient point is the main criteria (typ. at 150kHz...)the behaviour can be quite different [27].

• How to design filters to reach the application standards?

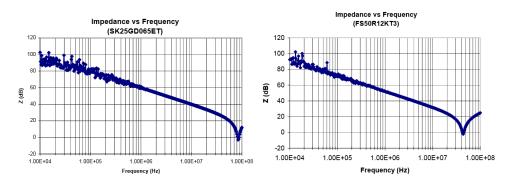

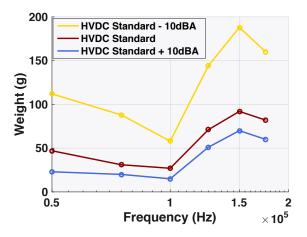

In recent years, the speed of semiconductors has increased, allowing less switching losses thanks to faster switching transitions. However, these faster transitions increase the level of EMC perturbation at high frequency and may put more stress on the EMC filter. In addition, a recent expectation in aeronautics is to relax the current standards so as to reduce the impact of the standard on the global sizing and weight of the systems, and analyse if a better referential exists for our equipment.

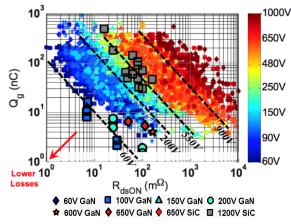

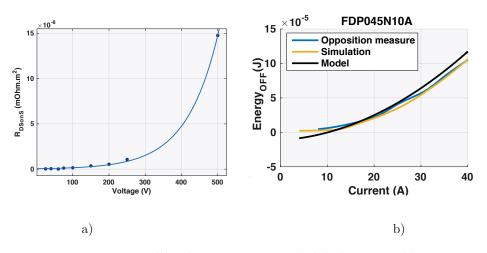

• Is it better to use semiconductors with low conduction, low switching or a trade-off between both?

New semiconductors can be faster with less switching losses. This makes it possible decreasing total losses and using smaller or different cooling systems. On the other hand, increasing the switching frequency may reduce the weight of the filters so there is a trade-off between the weight of filters and cooling system. Another possibility is to employ high temperature components, which accept a higher junction temperature and reduce the requirements on the cooling system. In general increasing the temperature affects reliability, so it should be checked that the technology of high temperature components is mature enough to maintain reliability at an acceptable level [28] [29].

• Has my design reached a global optimum? Is there an easier, more efficient or less expensive solution?

From the previous questioning, it is clear here that a global trade-off has to be calculated. However, it is not easy to perform it theoretically. This is the reason why the construction of a computeraided tool is required. Optimization techniques are a good approach to play automatically with the degrees of freedom and obtain designs that match given requirements; example of such studies can be found in the literature:

- In [30], the author proposes a study of several topologies in order to reduce the overall cost of the system.

- In [31], cost models are proposed for the main components of SMPS in a power range from 5 to 50kW with the objective to integrate them in cost optimization routines.

- In [32] the authors take into account the influence of the weight and volume of passive components to build an optimized converter. They show that the cooling system has a predominant effect on sizing.

- In [33], a converter design platform is provided for the production of integrated system.

- Finally, in [34], the authors present the limits of power electronics by reviewing various options for reducing the mass and volume of converters.

Nevertheless, realizing a complete study from these different papers remains difficult because of the lack of information. Therefore, a new methodology must be created to answer all these problems.

From previous questions, we can establish a synthesis on different axes to take into account in our models and optimization for the virtual prototyping development. We conclude that the optimal design and the computer-aided tools have to follow these factors driving power electronics and innovations. These three vectors of improvement have been studied during the ETHAER project, in different thesis and laboratories, as already introduced earlier in the first pages of this manuscript. We link each topic to the main current publications and partners:

- Evaluation of current/future opportunities in power electronics such as new components and technologies (This thesis, Laplace/Airbus Operations SAS)

- Comparison of the numerous topologies and possible evolutions or improvements with additional circuits or components (This thesis & IES [35])

- Emergence of integration techniques and their simulation (GEEPS & Ampere [36] [37])

Addressing these three bullets, should make it possible to optimize volume, weight and efficiency of static converters. A review of emerging innovations and future developments in power electronics and aeronautics is necessary to define the models to be created in future computational tools.

# **1.3.** Vector of improvements in Power Electronics

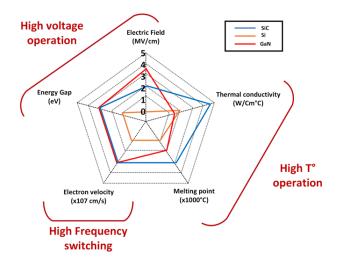

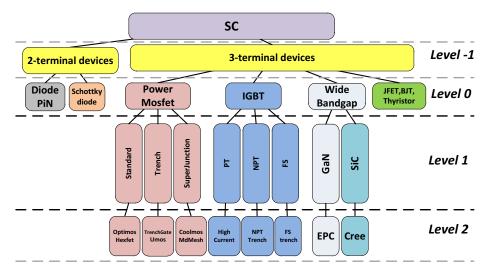

# 1.3.1. Components and Technologies

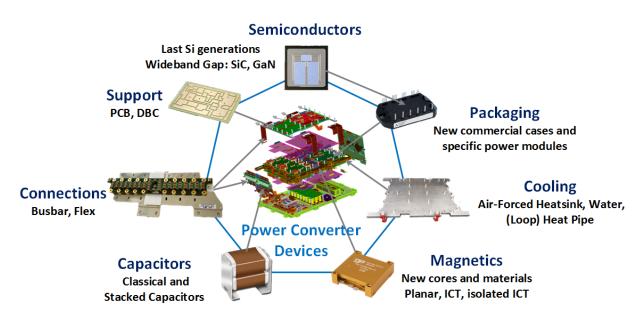

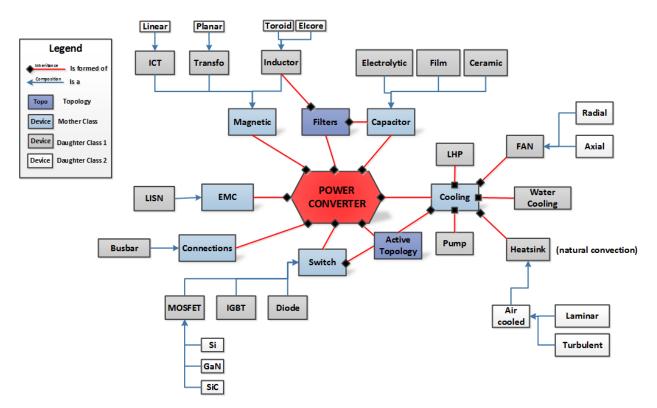

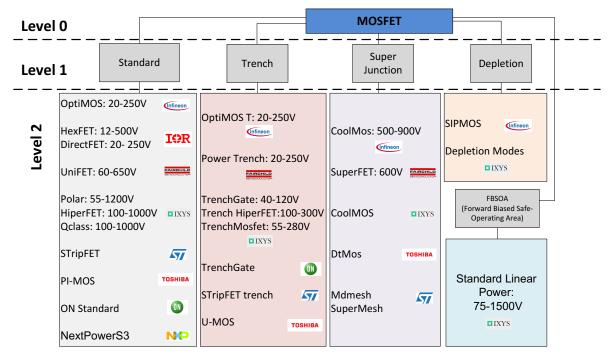

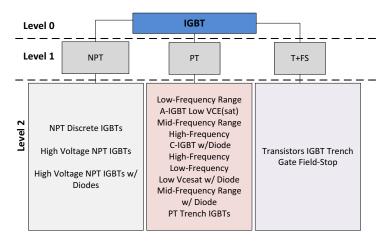

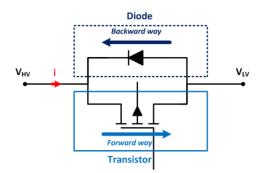

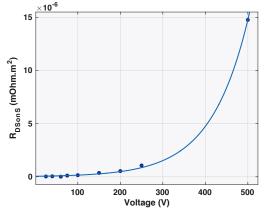

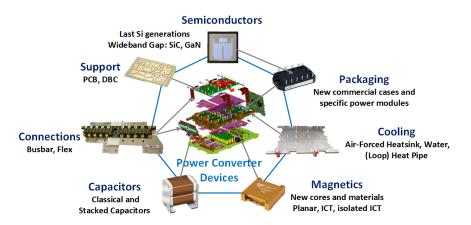

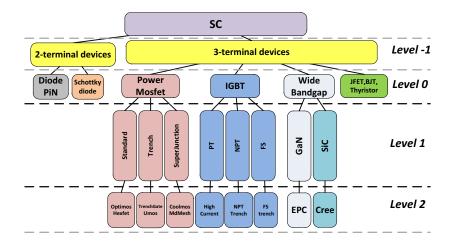

It is mandatory to know precisely what the main types of components are in power electronics to find the optimal design. The most relevant technologies have to be modelled and integrated in the optimization tool. It is natural to think that the last technical concepts will bring benefits on one or some of the chosen objectives. However, they are not always mature enough and the limited possible progress of the coming decades must be taken into account to establish a feasible perspective [38]. Therefore, it is very interesting to measure possible improvements between the current and future solutions and have a glimpse on the perspectives. As a result, the current questioning is to know what are the technologies to be modelled in the optimal design. We have already answered this question in [39]. However, a shortlist of the technologies mentioned in the paper is summarized in Figure 10.

Figure 10: Examples of current and new technologies to be modelled in the computer-aided design tool

# 1.3.2. Topologies

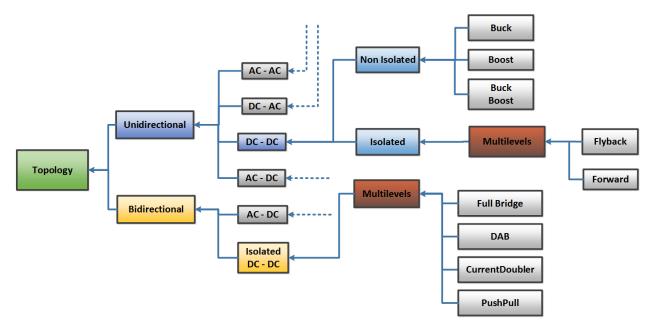

Nowadays the global study of the different topologies has been made and only small innovations can occur in the field of energy conversion. However, choosing the best topology for a given set of specifications is still a very difficult task. Indeed, many variations and strategies on a same topology exist that keep pushing the improvements limits, and based on key factors such as performance, reliability, integration, weight and cost. Classification of these different structures and evolutions must be done in order to make a pre-selection and then use the optimal design approach to compare them. However, it is impossible to choose the best one directly without making a deep study. Now it is clear that a tool computing directly different combinations can make the work of the designer faster and easier while ensuring the relevance of the solution. Such an example is given in chapter 5 and a survey of BBCU topologies in Appendix.

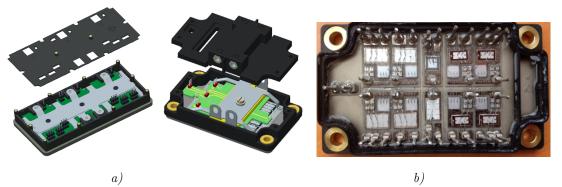

### **1.3.3.** Integration

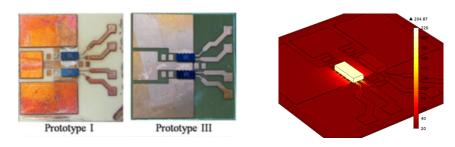

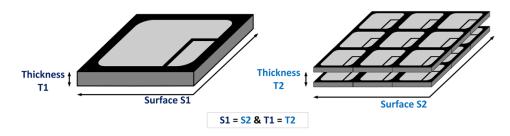

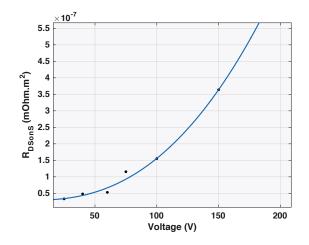

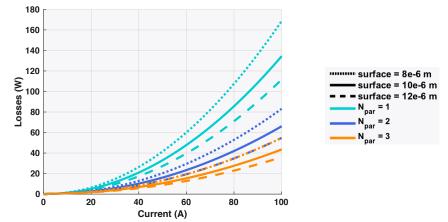

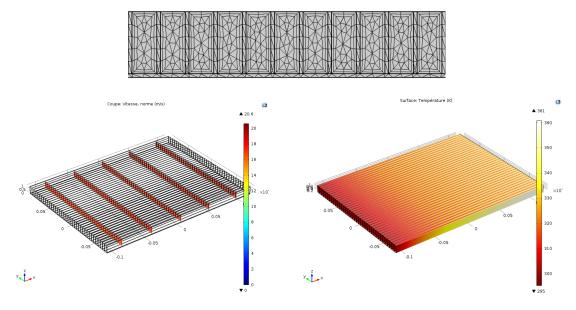

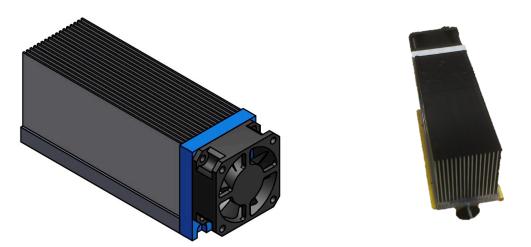

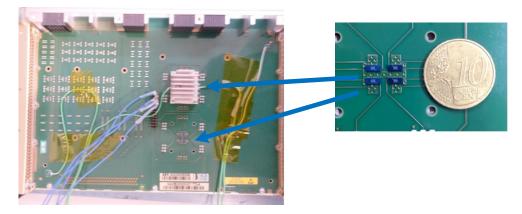

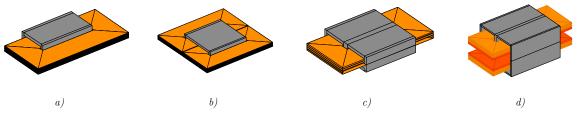

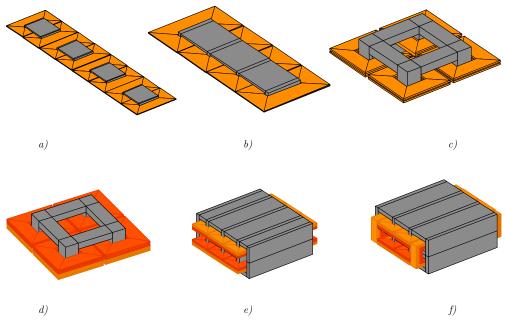

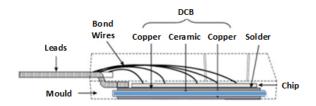

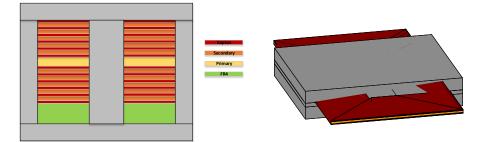

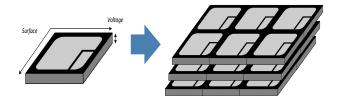

In this memoir the word "integration" means all processes, machines and techniques that can help building smaller and better power converters. Optimizing constructing and assembly can be a way to save weight, but it can be also an absolute requirement to make the system work; for example, with fast switching semiconductors stray inductance can be a killer, and sophisticated assembly techniques can be required to allow safe operation of a commutation cell. In recent years construction techniques have radically evolved, for instance with the Bus Bar and Flex technologies [40]. Other examples are the elimination of packaging creating parasitic inductances [41] and the reduction of the circuit size allowing better electrical performance, eliminating soldering and increasing the reliability [42]. Another approach is to use power modules to increase the level of integration of all active and passive components. The term 'integrated power module' refers to the fact that several components share a single substrate and case. The power modules are the best example of this trend. For instance, the driver commands and possible protections systems are directly incorporated in the module [43]. A demonstrator of a multilevel application with an integrated capacitor is realized in [44] and shows the benefits of power module - reducing the volume, easing the assembly of the converter and improving the thermal management. The last example we can give is the components buried in a PCB (Print Circuit Board) or a DBC (Direct-Bonded Copper). The purpose there is the same as for power modules. As a conclusion, more and more studies consider the integration of methodologies using 3D considerations in order to optimize the integration [45]. More classical techniques and prototypes accepts passives components inside the PCB more easily, like planar capacitors [46]. We can also mention the work of the ETHAER project, to which this thesis belongs. It is a study mainly focused on the semiconductor, package and driver integrations (Figure 11). As an example, several thermal management techniques for GaN transistors have been investigated, with a Wafer-Level Packaging (WLP), mount on DBC ceramic substrates to detail the manufacturing process and get thermal simulations and experimental results. More information are detailed in [36] [37].

Introduction

Figure 11: Photographs of integrated switching cell prototypes and related temperature simulation

# 1.4. Conclusion and Axes of research

# **1.4.1.** Chapter 1 – General Introduction

As a conclusion, this introductive chapter has presented the context of the More Electrical Aircraft. It explains why power electronics is a key factor for future aircrafts and how it is integrated into the electrical architecture. With the increasing power demand and number of power converters, new problematics arise. Therefore, new methods to address them more efficiently are required, especially in relation to digitalization. In this context, new converters have been created due to the emergence of a new HVDC network. Because of the numerous new challenges arising from these designs, this thesis is aiming at creating both a methodology and a computer-aided design tool. It aims at designing automatically whole static converters, for any kind of application. In addition, a review of design issues in power electronics has been reviewed in order to identify the technological locks that the optimal conception has to address. Then, the relevant technologies, topologies and integration processes have been reviewed in order to list the different aspects to be modelled in the final design tool. During this thesis, different axes will be explored and can be presented in four other chapters.

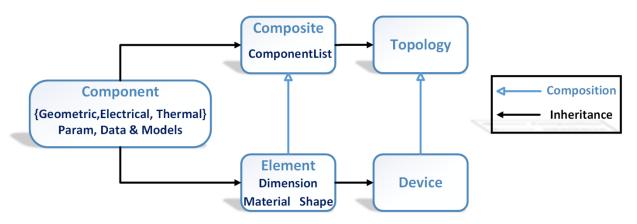

# 1.4.2. Chapter 2 - Optimal Design Methodology

The optimal design in power electronics requires a global methodology to optimize the sizing of a converter. This chapter aims to explain how to set an optimization problem on a power system and how to create the different parts of the virtual prototyping platform (presented in 1.2.2). In other words, it is the backbone of our optimization software dedicated to the power conversion. In addition, rules, pattern and strategies will be presented on the different computational objects that are parts of our libraries: components, composite (assembly of components) and topologies.

# 1.4.3. Chapter 3 & 4: Models of Power Devices

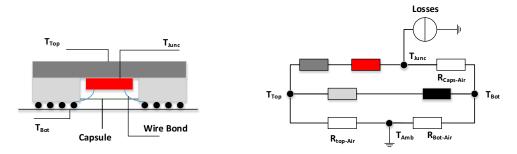

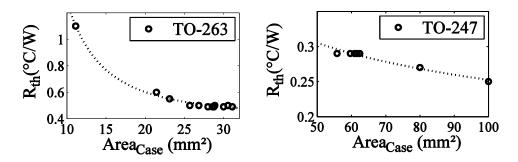

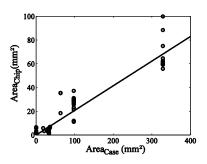

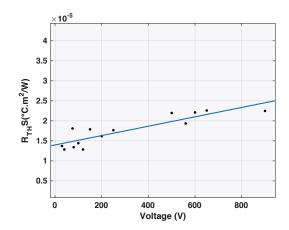

These chapters explain how to create all the main multi-domain models of power devices in a converter, which is useful for the optimization and pre-sizing methodology. For each component, a technological review is done with performance factors allowing to select the best ones in a design. Then, continuous and analytical models are proposed according to different granularities in order to incorporate them in an optimization. To finish, some experimentations have been realized to

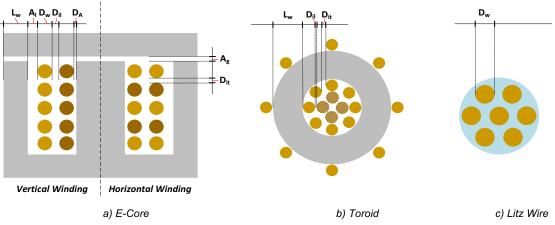

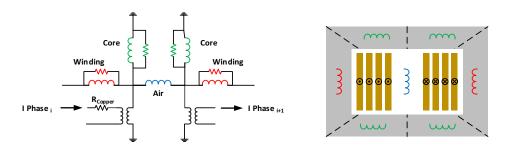

assess the pertinence of our models in the final study case. The chapter 3 deals with the "active part" of a power converter, gathering the switching semiconductors and their associated cooling systems. The chapter 4 deals with the "passive part:" capacitors and magnetic components, including inductors, isolated transformers or not isolated inter-cell transformers (ICT). In addition, the filter sizing is introduced, gathering both previous device families. In each chapter, geometrical, thermal, electrical, cost and losses models are proposed to answer to the needs of the computeraided optimal design. Different shapes, geometries and materials are considered in order to cover all the possibilities of the current technologies used in a static converter.

## 1.4.4. Chapter 5: Optimization of Power Devices, Topologies and Converter

The chapter 5 proposes to optimize several case studies extracted from the power devices constituting the global converter. Firstly, we propose local optimizations of the classical power devices that require a "custom" design, such as heatsinks and magnetic components. Secondly, we demonstrate how we can optimize an assembly of several devices with a filter topology thanks to our methodology and models. Finally, we propose several converter optimizations. We will focus especially on the BBCU converter in order to highlight the limits of our current work on the optimal pre-sizing in power electronics and how to improve it. Concluding remarks are exposed then in order to provide a global overview on this thesis work, but also to provide an outlook and directions for possible future research.

## Chapter 2

## 2. Methodology for the Optimal Design of Power Converters

Optimal and aided design in Power Electronics is a problem as old as the discipline itself. It is also obvious that the virtual prototyping of converters is less advanced than in other fields such as mechanics [1] [2] or electrical machine [47] [48]. Among numerous topologies (multiple converters architectures) and technologies (diversity in terms of components and materials), the optimal choice of a conversion structure dedicated to a specification remains a difficult exercise. Therefore, solving physical problems thanks to optimization algorithms is critical to take decisions more easily and analyse the physical systems in more depth. The purpose here is to find the minimum value of mathematical functions among the set of all feasible solutions, answering to certain conditions or constraints (1).

$$\min_{x \in \mathbb{R}^n} f(x) \text{ subject to } c(x) \ge 0 \tag{1}$$

To set the problem in the Electrical Engineering context, the computation has to find an optimal design and assess trade-offs of components and static converters. In addition, the current analysis and resolution power of computational tools – such as circuit simulators, finite element methods (FEM) and, solvers of all kinds – offer considerable potential that we can no longer ignore. Thus, it is essential to define the needs of computer aided-design in the field of power electronics. In our case, the virtual prototyping is a way to reduce the time needed to design and test prototypes, but mainly centred on the simulation of electric models. Although these simulations are essential to predict the interactions of different circuit elements, they are not sufficient to provide their elementary characteristics such as the mass and volume of the converter. However, some computer-aided design (CAD) software dedicated to printed circuit board or mechanical manufacturing systems can provide this information. Thus, this chapter proposes a new approach to fill in this lack in electrical engineering.

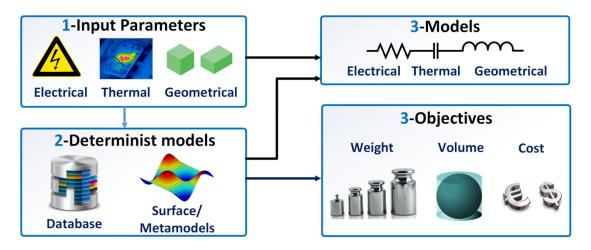

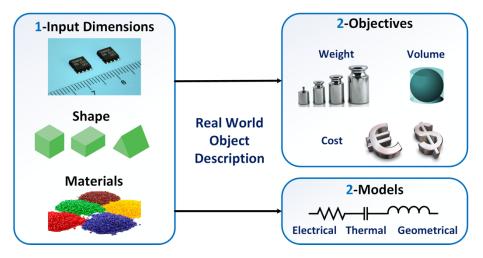

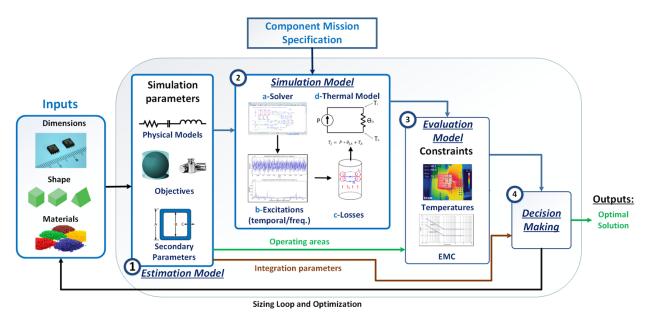

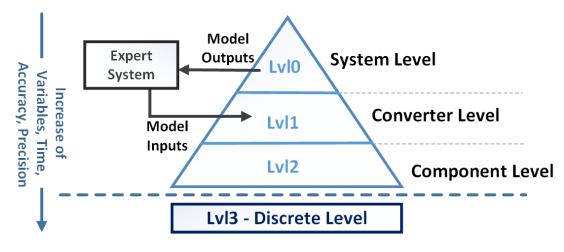

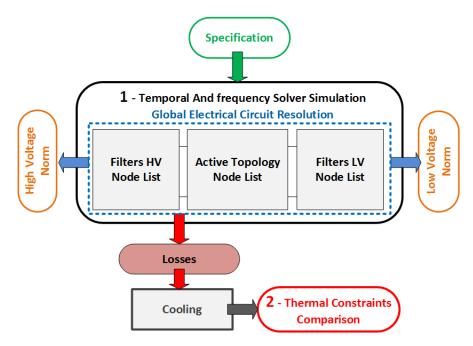

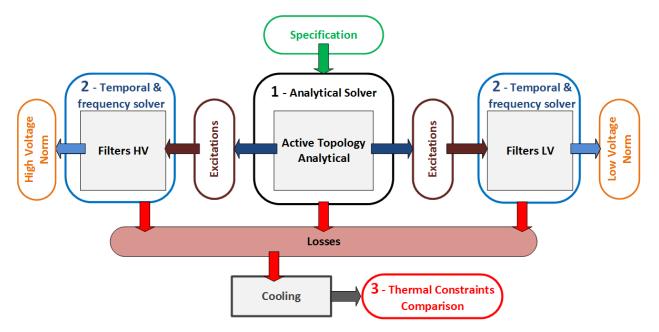

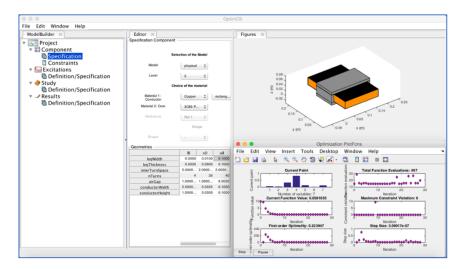

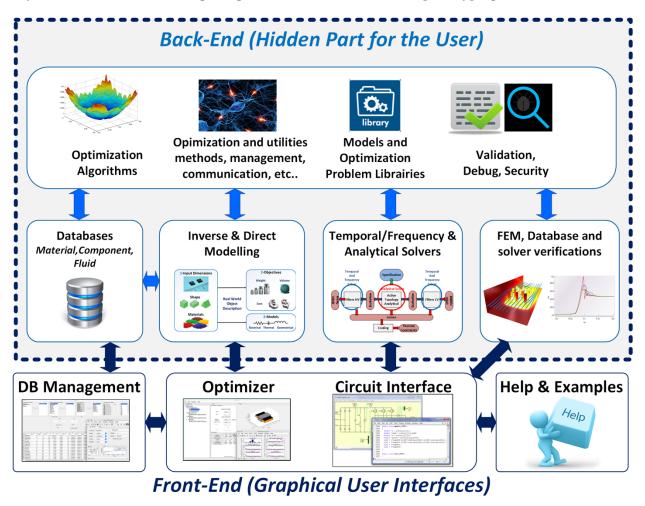

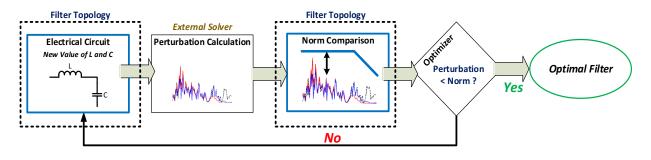

This chapter presents the different steps that have been realized in this thesis to set an optimization problem dedicated to the power electronics systems. First, the global architecture built in order to create a coherent hierarchy in the different elements of the proposed methodology is presented. Then, the strategy is chosen and detailed to solve an optimization problem dedicated to the energy conversion. A definition is also proposed that describes the components, allowing a 3D virtual prototyping based on a direct-model description. Thirdly, a way to assembly these different elements in sub-systems is created, called topologies, in order to perform local optimizations and to size the parts of the converter such as filters or semiconductors and their associated cooling systems. To finish, the environment to compute the models, solvers and optimization algorithms has been created, resolving any sort of local or global optimizations in power electronics, with a graphical interface (GUI).

#### 2.1. Software Architecture

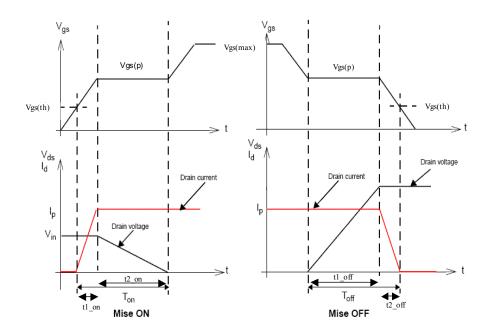

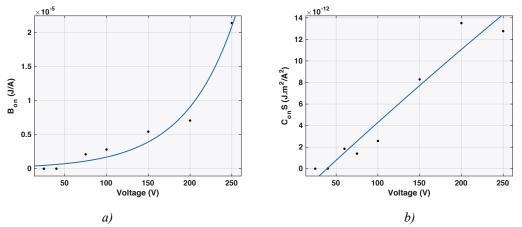

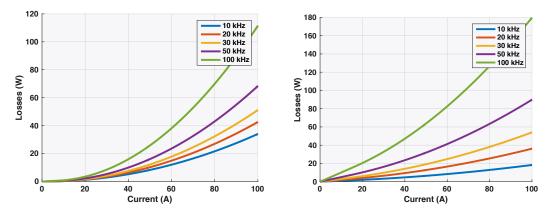

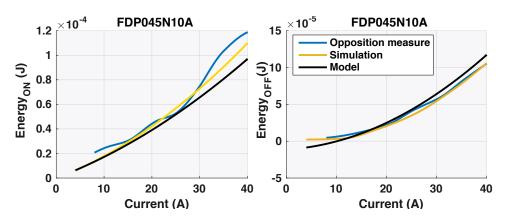

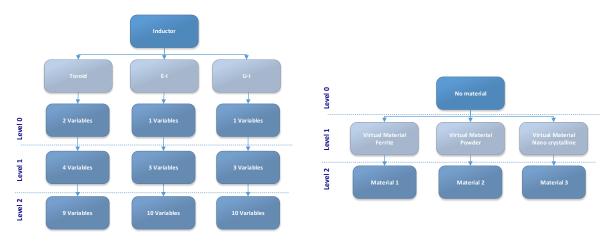

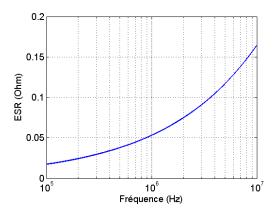

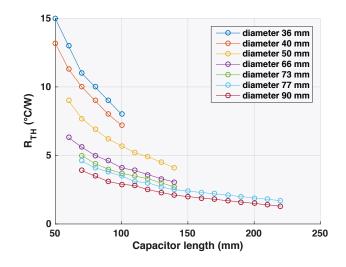

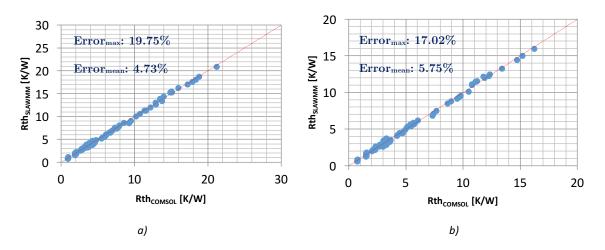

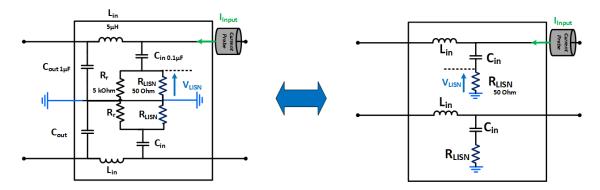

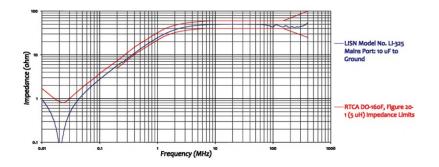

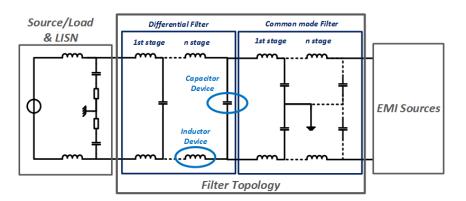

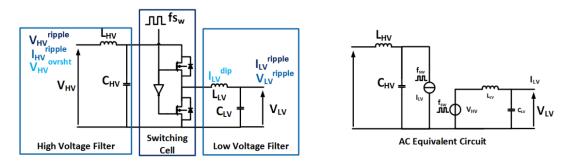

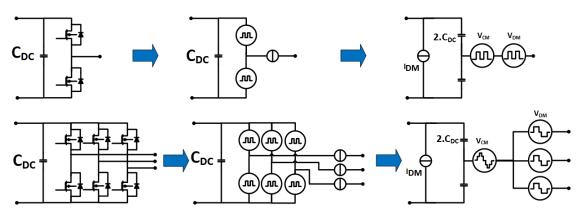

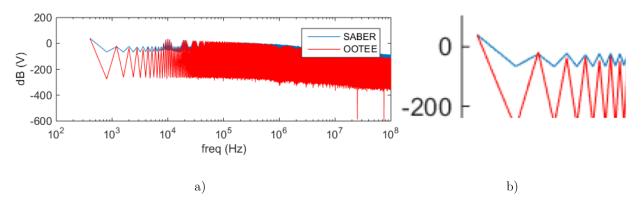

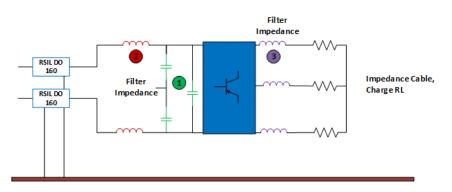

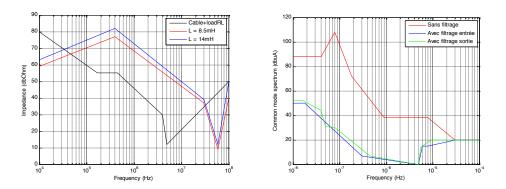

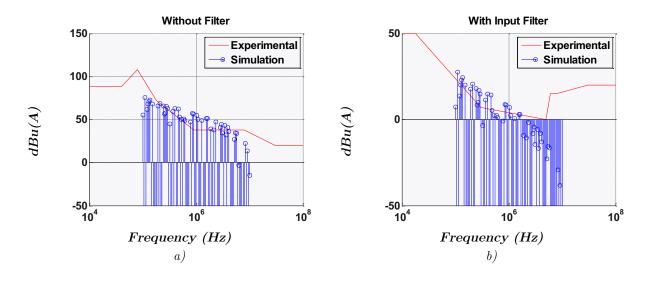

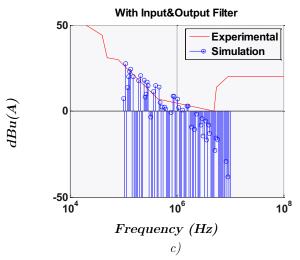

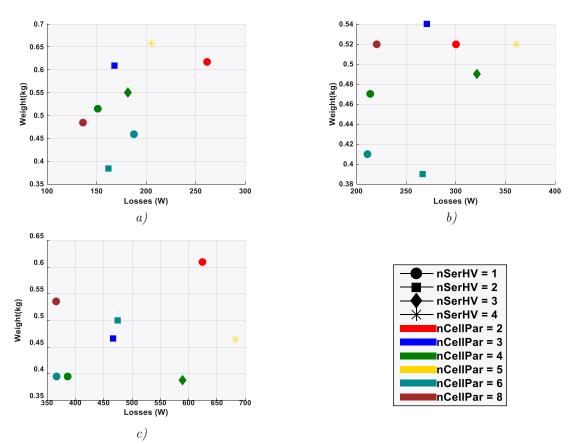

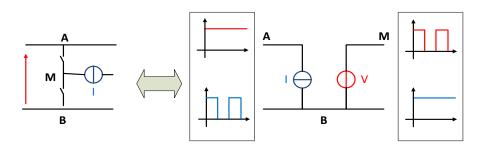

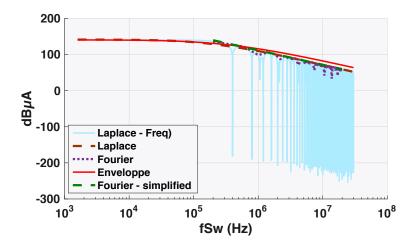

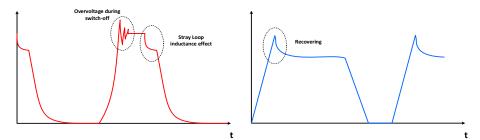

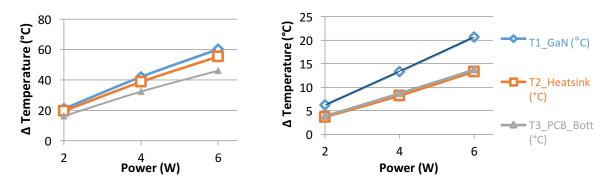

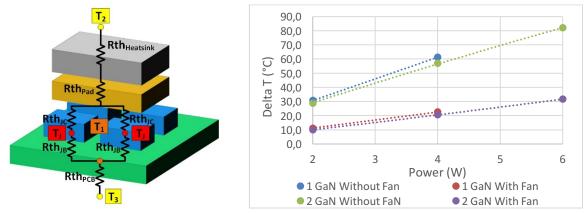

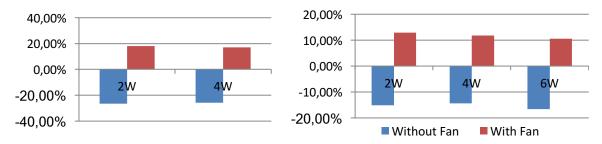

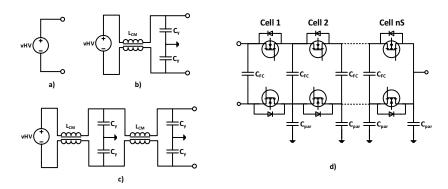

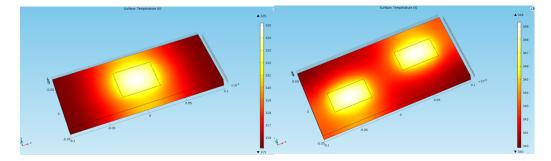

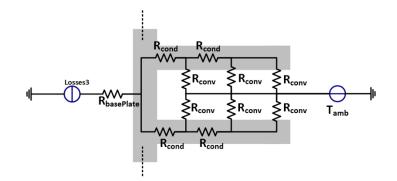

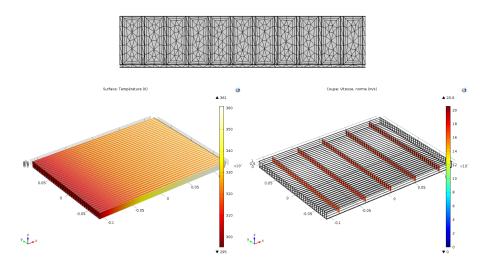

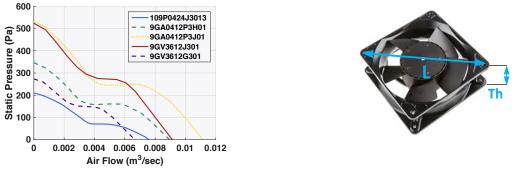

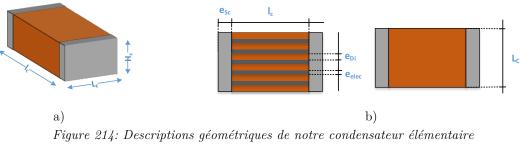

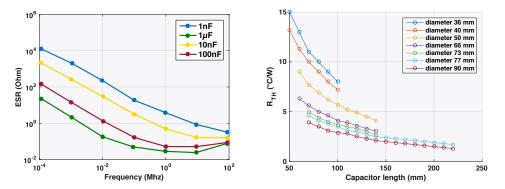

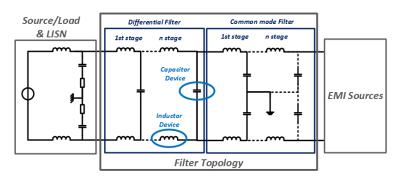

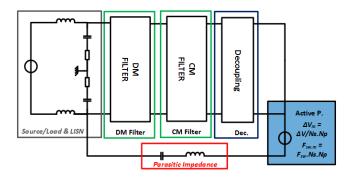

#### 2.1.1. Topology, Device and Material