# Characterization and modelling of MOS transistors from advanced technologies (FDSOI, nanowire, GaN HEMT, LTPS...)

Donghyun Kim

#### ▶ To cite this version:

Donghyun Kim. Characterization and modelling of MOS transistors from advanced technologies (FDSOI, nanowire, GaN HEMT, LTPS...). Micro and nanotechnologies/Microelectronics. Université Grenoble Alpes [2020-...]; Koryŏ taehakkyo. Asea munje yŏn'guso (Séoul, Corée S.), 2023. English. NNT: 2023GRALT086. tel-04531810

# HAL Id: tel-04531810 https://theses.hal.science/tel-04531810

Submitted on 4 Apr 2024

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

THÈSE

Pour obtenir le grade de

### DOCTEUR DE L'UNIVERSITÉ GRENOBLE ALPES et de l'UNIVERSITE KOREA

École doctorale : Electronique, Electrotechnique, Automatique, Traitement du Signal

(EEATS)

Spécialité: NANO ELECTRONIQUE ET NANO TECHNOLOGIES

Unité de recherche : L'Institut de Microélectronique Electromagnétisme et Photonique et

le Laboratoire d'Hyperfréquences et de Caractérisation (IMEP-LAHC)

Caractérisation et modélisation des composants MOS des technologies avancées (FDSOI, nanofil, GaN HEMT, LTPS)

Characterization and modeling of MOS transistors from advanced technologies (FDSOI, nanowire, GaN HEMT, LTPS)

Présentée par :

# KIM, Donghyun

#### Direction de thèse :

Francis BALESTRA

DIRECTEUR DE RECHERCHE, CNRS

Jae Woo LEE

ASSOCIATE PROFESSOR.

Co-Directeur de thèse

Directeur de thèse

Korea University

**Christoforos THEODOROU**

CHARGE DE RECHERCHE, CNRS

Co-Encadrant

#### Rapporteurs:

**Hyun Suk KIM**

FULL PROFESSOR,

Dongguk University

**Pascal MASSON**

PROFESSEUR DES UNIVERSITES,

Université Côte d'Azur

Thèse soutenue publiquement le 05/12/2023, devant le jury composé de :

**Ji-Woon YANG**

FULL PROFESSOR,

Président du jury, Examinateur

Korea University

**Quentin RAFHAY**

MAITRE DE CONFERENCES HDR, Examinateur

Université Grenoble Alpes

Invités:

So Jeong PARK

DOCTEURE EN SCIENCES,

Korean Intellectual Property Office

**Titre**: Caractérisation et modélisation des composants MOS des technologies avancées (FDSOI, nanofil, GaN HEMT, LTPS...)

**Mots clés**: Microelectronique, Caracterisation, MOSFET

Résumé : Dans cette étude, la caractérisation électrique et la modélisation de divers dispositifs électroniques basés sur la structure MOSFET ont été effectuées. La caractérisation électrique des FET à nanofeuillets empilés verticalement sur FDSOI a été réalisée en utilisant une approche statistique. Ces NSFET présentaient diverses dimensions et ont été étudiés à la fois pour les NFET et les PFET. Chaque dispositif a été mesuré dans un grand nombre de matrices, totalisant plus de 170 unités. Les paramètres électriques ont été extraits au moyen de diverses méthodes, notamment la fonction Y et la fonction LW, entre autres. La corrélation entre différents paramètres électriques tels que lon, loff, SS, la mobilité et les facteurs de dégradation de la mobilité a été étudiée. L'écart-type de chaque paramètre électrique a été utilisé pour interpréter la loi de Pelgrom. L'analyse des GaN HEMT jusqu'à la température cryogénique a été effectuée. Une caractérisation électrique détaillée et l'extraction des paramètres du transistor ont été réalisées sur des HEMT GaN/Si compatibles CMOS de 200 mm, même à des températures cryogéniques extrêmement basses. Les principaux paramètres du transistor, tels que la tension de seuil Vth, la mobilité à faible champ μ0, l'oscillation inférieure au seuil SS, et la résistance série source-drain Rsd, ont été extraits dans la région linéaire en utilisant les méthodes de la fonction Y et de la fonction Lambert-W, et ce, pour des longueurs de grille allant jusqu'à 0,1 µm. La méthode de la fonction Y a également été employée dans la région de saturation pour extraire la vitesse de saturation. Les résultats indiquent que ces dispositifs GaN/Si HEMT conservent leur excellent fonctionnement même à très basse température, avec une amélioration de la mobilité et de la pente inférieure au seuil. L'analyse TLM a également révélé que la résistance série source-drain Rsd est davantage limitée par la résistance de contact que par la résistance de la région d'accès 2DEG lorsque la température diminue. Les caractéristiques électriques et le profilage des pièges dans les TFT LTPS par rapport aux substrats rigides et flexibles ont été examinés. Nous avons mené une étude approfondie du transport de porteurs dans des transistors à couches minces en silicium polycristallin de type p (LTPS) sur un substrat flexible, en le comparant avec celui sur un substrat en verre, dans le but d'améliorer les performances du dispositif. Afin de comprendre l'origine du transport des porteurs sur ces substrats différents, nous avons effectué des caractérisations dépendantes de la température pour des paramètres des dispositifs électriques tels que VTH, SS, lon et µeff. Il est bien établi que la taille des grains de poly-Si (Lgrain) et la hauteur de barrière (EB) entre les joints de grains sont les principaux facteurs déterminant le transport dans le silicium polycristallin, et ces paramètres peuvent être extraits en utilisant le modèle de mobilité polycristalline. Cependant, nos études systématiques ont montré que ce n'est pas la taille des grains, mais plutôt la hauteur de la barrière EB, qui a une plus grande influence sur la dégradation des TFT LTPS sur les substrats flexibles. La hauteur de barrière EB sur un substrat flexible est environ 18 fois plus élevée que sur un substrat en verre, tandis que la taille des grains est similaire pour les deux types de substrats. En comparaison avec les TFT LTPS sur substrat en verre, une hauteur de barrière EB plus élevée entraîne une dégradation d'environ 24 % de l'Ion, 30 % de la SS et 21 % de µeff sur le substrat flexible à température ambiante. L'analyse du bruit basse fréquence (LFN) a également révélé que la densité totale de pièges (Nt) sur un substrat flexible est jusqu'à quatre fois plus élevée que sur un substrat en verre, confirmant ainsi la valeur élevée de EB dans le dispositif fabriqué sur le substrat flexible.

**Title:** Characterization and modeling of MOS transistors from advanced technologies (FDSOI, nanowire, GaN HEMT, LTPS...)

**Keywords:** Charactertization, Microelectronics, MOSFET

Abstract: In this study, the electrical characterization and modeling of various electronic devices based on MOSFET structure were carried out. Electrical characterization of 2-vetically stacked Nanosheet FETs on FDSOI by using statistical analysis. NSFETs contained various dimensions were investigated for both NFET and PFET. Each device was measured in a lot of dies over 170 ea. Electrical parameters were extracted using various methods (Y-function and LW function, etc). The correlation of different electrical parameters (Ion, Ioff, SS, mobility, and mobility degradation factors) was investigated. The standard deviation of each electrical parameter was utilized for the interpretation of Pelgrom's law. GaN HEMT analysis down to cryogenic temperature A detailed electrical characterization and transistor parameter extraction on 200 mm CMOS compatible GaN/Si HEMTs was performed down to deep cryogenic temperatures. The main transistor parameters (threshold voltage Vth, low-field mobility µ0, subthreshold swing SS, source-drain series resistance Rsd) were extracted in linear region using the Y-function and the Lambert-W function methods for gate lengths down to 0.1 µm. The Y-function method was also employed in saturation region for the extraction of the saturation velocity. The results indicate that these GaN/Si HEMT devices demonstrate a very good functionality down to very low temperature with improvement of mobility and subthreshold slope. It was also shown by TLM analysis that the source-drain series resistance Rsd is more limited by the contact resistance than by the 2DEG access region resistance as temperature lowered. Electrical characteristics and Trap profiling in LTPS TFT comparing to on rigid and flexible substrates. The carrier transport of p-type low temperature polycrystalline silicon (LTPS) thin-film transistors (TFTs) on flexible substrate has been intensively studied and compared to that on glass substrate in order to improve device performance. To investigate the origin of carrier transport on different substrates, temperature dependent characterizations are carried out for electrical device parameters such as threshold voltage (VTH), subthreshold swing (SS), on-current (Ion) and effective carrier mobility (µeff). The poly-Si grain size Lgrain and the barrier height EB between grain boundaries are well known to be the main parameters to determine transport in polycrystalline silicon and can be extracted based on the polycrystalline mobility model. However, our systemic studies show that it is not grain size but EB that has more influence on the degradation of LTPS TFT on flexible substrates. The EB of flexible substrate is roughly 18 times higher than glass substrate whereas grain size is similar for both devices on different substrates. Compared to the LTPS TFT on glass substrate, higher EB degrades approximately 24 % of lon, 30 % of SS and 21 % of µeff on the flexible substrate at room temperature. From low frequency noise (LFN) analysis, it is observed that the total trap density (Nt) for flexible substrate is up to four times higher than that of glass substrate, which also supports the high value of EB in the device fabricated on the flexible substrate.

# **Doctoral Dissertation**

# Characterization and modeling of MOS transistors from advanced technologies (FDSOI, nanowire, GaN HEMT, LTPS)

## Donghyun KIM

Department of Electronics and Information Engineering

**Graduate School**

Korea University

February 2024

Characterization and modeling of MOS transistors from advanced technologies (FDSOI, nanowire, GaN HEMT, LTPS)

by Donghyun KIM

under the supervision of Professor Jae Woo LEE

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy.

Department of Electronics and Information Engineering

Graduate School Korea University

October 2023

The dissertation of Donghyun KIM has been approved by the dissertation committee in partial fulfillment of the requirements for the degree of Doctor of Philosophy.

December 2023

Committee Chair: Jae Woo LEE

Committee Member: Francis BALESTRA

Committee Member: Ji-Woon YANG

Committee Member: Hyun Suk KIM

So Jeong Park.

Committee Member: So Jeong PARK

# Characterization and modeling of MOS transistors from advanced technologies (FDSOI, nanowire, GaN HEMT, LTPS)

#### by Donghyun KIM

Department of Electronics and Information Engineering under the supervision of Professor Jae Woo Lee

#### **ABSTRACT**

In this study, the electrical characterization and modeling of various electronic devices based on MOSFET structure were carried out. Electrical characterization of 2-vetically stacked Nanosheet FETs on FDSOI by using statistical analysis. NSFETs contained various dimensions were investigated for both NFET and PFET. Each device was measured in a lot of dies over 170 ea. Electrical parameters were extracted using various methods (Y-function and LW function, etc). The correlation of different electrical parameters ( $I_{on}$ ,  $I_{off}$ , SS, mobility, and mobility degradation factors) was investigated. The standard deviation of each electrical parameter was utilized for the interpretation of Pelgrom's law.

A detailed electrical characterization and transistor parameter extraction on 200 mm CMOS compatible GaN/Si HEMTs was performed down to deep cryogenic temperatures. The main transistor parameters (threshold voltage  $V_{th}$ , low-field mobility  $\mu_0$ , subthreshold swing SS, source-drain series resistance  $R_{sd}$ ) were extracted in linear region using the Y-function and the Lambert-W function methods for gate lengths down to 0.1  $\mu$ m. The Y-function method was also employed in saturation region for the extraction of the saturation velocity. The results indicate that these GaN/Si HEMT devices demonstrate a very good functionality down to very low temperature with improvement of mobility and subthreshold

slope. It was also shown by TLM analysis that the source-drain series resistance  $R_{sd}$  is more limited by the contact resistance than by the 2DEG access region resistance as temperature lowered.

Electrical characteristics and Trap profiling in LTPS TFT comparing to on rigid and flexible substrates. The carrier transport of p-type low temperature polycrystalline silicon (LTPS) thin-film transistors (TFTs) on flexible substrate has been intensively studied and compared to that on glass substrate in order to improve device performance. To investigate the origin of carrier transport on different substrates, temperature dependent characterizations are carried out for electrical device parameters such as threshold voltage  $(V_{TH})$ , subthreshold swing (SS), on-current  $(I_{on})$  and effective carrier mobility  $(\mu_{eff})$ . The poly-Si grain size  $L_{grain}$  and the barrier height  $E_B$  between grain boundaries are well known to be the main parameters to determine transport in polycrystalline silicon and can be extracted based on the polycrystalline mobility model. However, our systemic studies show that it is not grain size but  $E_B$  that has more influence on the degradation of LTPS TFT on flexible substrates. The  $E_B$  of flexible substrate is roughly 18 times higher than glass substrate whereas grain size is similar for both devices on different substrates. Compared to the LTPS TFT on glass substrate, higher E<sub>B</sub> degrades approximately 24 % of I<sub>on</sub>, 30 % of SS and 21 % of  $\mu_{eff}$  on the flexible substrate at room temperature. From low frequency noise (LFN) analysis, it is observed that the total trap density  $(N_t)$  for flexible substrate is up to four times higher than that of glass substrate, which also supports the high value of E<sub>B</sub> in the device fabricated on the flexible substrate.

**Keywords:** Electrical characterization, Low frequency noise, MOSFET, Nanowire, Nanosheet, Variability, GaN, HEMT, cryogenic, LTPS, barrier height, Seto model

최신 기술 적용 MOS 트랜지스터의 전기적 특성화 및 모델링 (FDSOI, nanowire, GaN HEMT, LTPS)

김동현

전자·정보공학과

지도교수: 이 재 우

#### **Korean Abstract**

본 연구에서는 MOSFET 구조를 기반으로 하는 다양한 전자소자의 전기적 특성화 및 모델링을 수행하였다. FDSOI 웨이퍼 기판에 제작된 2 개로 수직적층된 Nanosheet (NS) FET 의 전기적 특성 및 통계적 분석을 진행하였다. 다양한 게이트 면적의 NFET 과 PFET을 이용하여 NSFET의 분석을 진행하였다. 각 device는 170 개가 넘는 많은 die 에서 측정되었다. 다양한 방법(Y-function, LW function 등)을 사용하여 다양한 전기적 매개변수를 추출하였다. 다양한 전기적 매개변수 ( $I_{on}$ ,  $I_{off}$ , SS, effective mobility 및 mobility degradation factor)의 상관관계를 조사하였으며, 각 전기적 매개변수의 표준편차를 이용하여 Pelgrom's law 를 이용하여 해석하였다.

200mm CMOS 공정 호환 가능한 GaN/Si HEMT 에 대하여 상세한 전기적 특성화

및 트랜지스터 매개변수 추출이 극저온까지 수행하였다. 주요 트랜지스터 매개변수( $V_{th}$ ,  $\mu_0$ , SS,  $R_{sd}$ )는 게이트 길이가  $0.1~\mu m$  까지인 Y function 및 Lambert-W function 방법을 사용하여 선형 영역에서 추출되었다. Saturation velocity 추출을 위해 포화 영역에서도 Y function 방법을 사용하였다. 결과적으로 GaN/Si HEMT 소자가  $\mu_0$  및 SS 의 개선과 함께 극저온까지 우수한 동작 특성을 가지는 것을 확인하였다. 또한 온도가 낮아짐에 따라  $R_{sd}$ 이 2DEG access region resistance 보다 contact resistance 에 의해 더 크게 영향을 받는다는 것을 TLM 분석을 통해 확인하였다.

Glass 및 flexible 기판에 따라 LTPS TFT 의 전기적 특성 및 trap profiling 을 진행하였다. 소자 성능을 향상시키기 위해 flexible 기판에서 LTPS TFT 의 캐리어 이동특성에 대하여 집중적으로 분석하였으며, glass substrate 에서의 carrier transport 를 비교하였다. Glass 및 flexible 기판에서 carrier transport 의 특성 및 원리를 조사하기 위해  $V_{th}$ , SS,  $I_{on}$  및  $\mu_{eff}$  와 같은 전기적 매개변수에 대해 온도에 따른 특성분석이 진행되었다. poly-Si grain 크기  $L_{grain}$  과 grain 경계 사이의 전기적 barrier 높이  $E_B$  는 다결정 실리콘의 수송을 결정하는 주요 매개 변수로 잘 알려져 있으며 다결정 이동도 모델을 기반으로 추출할 수 있습니다. 체계적인 연구에 따르면 flexible 기판에서 LTPS TFT의 열화는 grain 크기뿐만 아니라  $E_B$ 에 크게 영향을 받는 것을 확인하였다. Flexible 기판의  $E_B$ 는 유리 기판보다 약 18 배 더 높은 반면, grain 크기는 서로 다른 기판의 두 TFT 에서 비슷한 것으로 확인되었다. Glass 기판의 LTPS TFT 와 비교하여 더 높은  $E_B$ 는 실온에서 flexible 기판 동작 특성들의  $I_{on}$  약 24%, SS 30%,  $\mu_{eff}$  21%를 저하시켰다.

저주파 잡음(LFN) 분석에서 Flexible 기판의 총 트랩 밀도( $N_t$ )가 glass 기판보다 최대 4 배 더 높은 것으로 확인되었으며, 이는 또한 flexible 기판에 제작된 TFT 에서 높은  $E_B$  와의 상관관계를 가지고 있다.

중심어: Characterization, Low frequency noise, MOSFET, Nanowire, Nanosheet, Variability, GaN, HEMT, cryogenic, LTPS, barrier height

#### **PREFACE**

All of the work presented was conducted in IMEP-LAHC/UGA at Grenoble and AEDL with co-supervisor program between France and South Korea. All experimental materials and devices were approved by CEA-LETI (2-vertically stacked Nanosheet FET and GaN/Si HEMT) and Samsung Display Corporation (LTPS TFT).

A version of Chapter 3 has been published as two international conferences (2022 Solid State Devices and Materials [SSDM] in Japan and 2023 IEEE Electron Devices Technology and Manufacturing [EDTM] in South Korea).

A version of Chapter 4 has been published [Donghyun Kim, C. Theodorou, A. Chanuel, Y. Gobil, M. Charles, E. Morvan, Jae Woo Lee, M. Mouis, and G. Ghibaudo. "Detailed electrical characterization of 200 mm CMOS compatible GaN/Si HEMTs down to deep cryogenic temperatures." Solid-State Electronics 197 (2022): 108448.]. I was main investigator, responsible for major experiments, data collection and analysis, as well as manuscripts. A. Chanuel, Y. Gobil, M. Charles, and E. Morvan were responsible for the fabrication of GaN/Si HEMT in CEA-LETI. C. Theodorou, Jae Woo Lee, M. Mouis were responsible for co-supervisory authors for manuscript composition. G. Ghibaudo was major supervisory author and management for this project.

A version of Chapter 5 has been published [Donghyun Kim, Jungchun Kim, Haeyong Kang, Jae Won Shim, and Jae Woo Lee. "Influence of flexible substrate in low temperature polycrystalline silicon thin-film transistors: temperature dependent characteristics and low frequency noise analysis." Nanotechnology 31.43 (2020): 435201.]. I was main investigator, responsible for major experiments, data collection and analysis, as well as manuscripts. Jungchun Kim was responsible for experiments and data collection. Haeyong Kang and Jae Won Shim were responsible for co-supervisory authors for manuscript composition. Jae Woo Lee was major supervisory author and management for this project.

With regard to excellence, it is not enough to know,

But we must try to have and use it.

- Aristotle

# TABLE OF CONTENTS

| ABSTRACT        |                                                        | 1  |

|-----------------|--------------------------------------------------------|----|

| Korean Abstract |                                                        | 3  |

| PREFACE         |                                                        | 6  |

| TABLE OF CON    | VTENTS                                                 | 8  |

| LIST OF TABLE   | ES                                                     | 11 |

| LIST OF FIGUR   | ES                                                     | 12 |

| Chapter 1.      | INTRODUCTION                                           | 20 |

| 1.1 Semico      | onductor Market Trend                                  | 20 |

| 1.2 Device      | Scaling Down                                           | 22 |

|                 | Depleted Silicon on Insulator (FDSOI) Technology       |    |

| 1.3.1           | State-of-the-art SOI Technology                        | 26 |

|                 | SOI Wafer Fabrication: Smart-Cut <sup>TM</sup> Process |    |

| 1.4 Overvi      | ew of Power Electronics                                | 32 |

| 1.5 Overvi      | ew of Display Devices                                  | 33 |

| 1.5.1           | Display devices history                                | 33 |

|                 | Display market trend overview                          |    |

|                 | Thin Film Transistors (TFTs)                           |    |

| 1.6 Referen     | nces                                                   | 42 |

| Chapter 2.      | MOSFET physics and characterization methodology        | 45 |

| 2.1 Introdu     | ction                                                  | 45 |

| 2.2 Basic N     | MOSFET operation                                       | 46 |

|                 | Linear Regime (at $V_D < (V_G - V_{th})$ )             |    |

|                 | Saturation Regime (at $V_D > (V_G - V_{th})$ )         |    |

|                 | Transfer characteristics of MOSFET                     |    |

| 2.2.3           | .a Threshold voltage, $V_{th}$                         | 47 |

| 2.2.3           | .b Subthreshold swing, SS                              | 51 |

|                 |                                                        |    |

| 2.3         | 2.3.c Carrier Mobility                                                  | 54      |

|-------------|-------------------------------------------------------------------------|---------|

| 2           | 2.3.d Series Resistance                                                 | 56      |

| 2.3 Fund    | damental noise sources                                                  | 58      |

| 2           | 3.1 Thermal noise                                                       | 58      |

| 2           | 3.2 Shot noise                                                          | 58      |

| 2           | 3.3 Generation-recombination noise                                      | 59      |

| 2           | 3.4 Random-Telegraph-Signal (RTS) noise and 1/f noise                   | 60      |

| 2.4 Refe    | erence                                                                  | 62      |

| Chapter 3.  | Current Variability in 2-vertically Stacked Nanosheet FETs on l         | FDSOI   |

| 3.1 Intro   | oduction                                                                | 64      |

| 3.2 Chai    | racterization of variability                                            | 65      |

|             | eriments and methods                                                    |         |

|             | 3.1 Global variability                                                  |         |

| 3           | 3.1.a Drain current mismatch model from linear to saturation regime     | 68      |

| 3           | 3.1.b Drain current variability including all drain current mismatch so | ources  |

| •••         |                                                                         | 78      |

| 3           | 3.2 Low Frequency noise variability in 2-vertically stacked Nanoshed    | et FETs |

| •••         |                                                                         | 83      |

| 3           | 3.2.a Experiments and methods                                           | 84      |

| 3.4 Cond    | clusion                                                                 | 88      |

| 3.5 Refe    | erences                                                                 | 88      |

| Chapter 4.  | Detailed Electrical Characterization of 200 mm CMOS compati             | ble     |

| GaN/Si HEMT | Γs down to Deep Cryogenic Temperatures                                  | 93      |

|             | oduction                                                                |         |

|             | eriments and methods                                                    |         |

| 4.3 Resu    | ults and discussion                                                     | 97      |

|             | 3.1 Transfer characteristics                                            |         |

|             | 3.2 Y-function based transistor parameter extraction                    |         |

|             | 3.3 Lambert-W-function based transistor parameter extraction            |         |

|             | mary and conclusion                                                     |         |

| 4.5 Referen       | nces                                                       | 109         |

|-------------------|------------------------------------------------------------|-------------|

| Chapter 5.        | Influence of Flexible Substrate in Low Temperature Polyco  | rystalline  |

| Silicon Thin-Film | n Transistor: Temperature Dependent Characteristics and Lo | w Frequency |

| Noise Analysis    | 113                                                        |             |

| 5.1 Introdu       | ection                                                     | 113         |

| 5.2 Device        | Fabrication                                                | 115         |

| 5.3 Results       | and discussion                                             | 117         |

| 5.3.1             | DC Characteristics                                         | 117         |

| 5.3.2             | Low Frequency Noise                                        | 123         |

| 5.4 Conclu        | sion                                                       | 127         |

| 5.5 Referer       | nces                                                       | 127         |

| Summary and Co    | onclusion                                                  | 132         |

| Publication       |                                                            | 134         |

| Conference prese  | entation                                                   | 136         |

# LIST OF TABLES

| Table 1.1 List of Top 10 Largest Semiconductor Companies by and Country in 2023 [3].22 |

|----------------------------------------------------------------------------------------|

| Table 1.2 CE scaling of MOSFET device and circuit parameters [5]24                     |

| Table 1.3 Properties of semiconductor materials used in HEMTs at 300 K [18]33          |

| Table 3.1 Systematic and random variations of MOSFET parameters and their sources66    |

| Table 5.1 Electrical parameters of LTPS TFTs                                           |

| Table 5.2 The extracted parameters fitted by temperature dependent effective mobility  |

| model for polycrystalline Silicon                                                      |

# LIST OF FIGURES

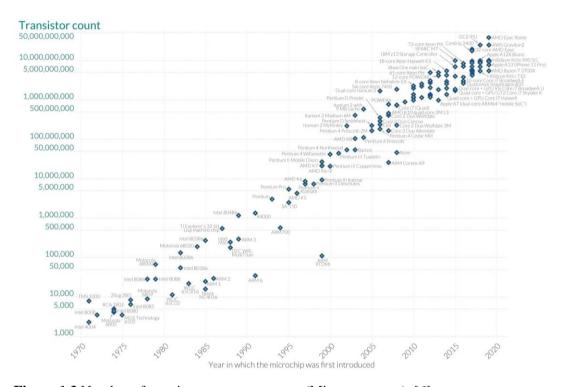

| Figure 1.1 Semiconductor industry revenue worldwide from 2012 to 2024 [1]20                                                                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1.2 Architecture of an n-channel MOSFET and MOSFET constant electric field scaling by a factor of <i>S</i> [4]23                              |

| Figure 1.3 Number of transistors versus per year (Microprocessor). [6]26                                                                             |

| Figure 1.4 Smart-Cut <sup>TM</sup> , an advanced SOI wafer fabrication technique by SOITEC Inc [7].                                                  |

| Figure 1.5 Various utilization of engineered SOI technique for specified commercialized products [8]                                                 |

| Figure 1.6 Changes in display panel's generation LG Display Inc. [20]35                                                                              |

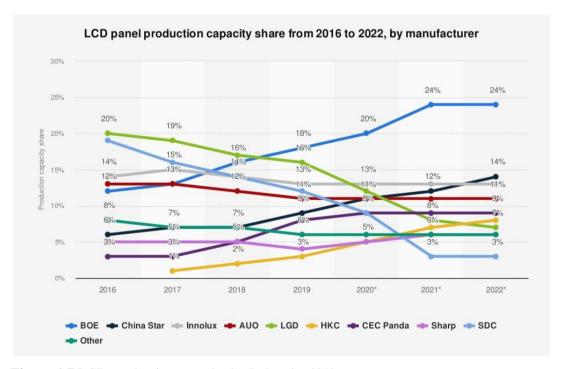

| Figure 1.7 LCD production capacity by Industries [21]                                                                                                |

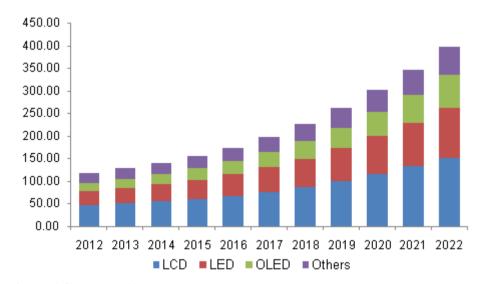

| Figure 1.8 Asia-Pacific electronic display market revenue by technology [22]37                                                                       |

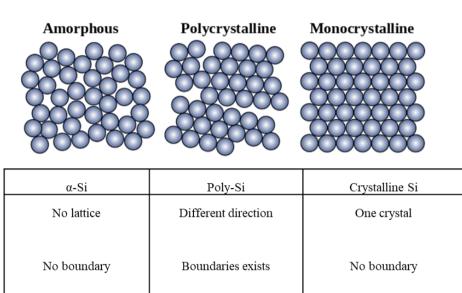

| Figure 1.9 The phase of silicon lattice and properties by silicon phase [23, 24]39                                                                   |

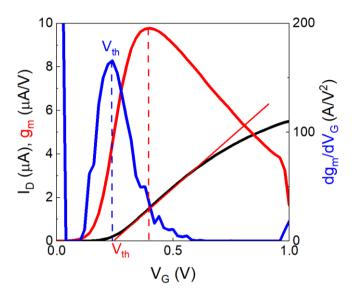

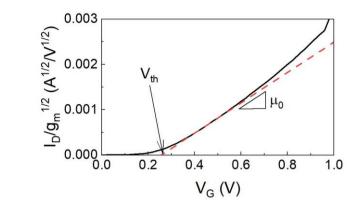

| Figure 2.1 $V_{th}$ determination by linear extrapolation method (Red) and second derivative method (Blue). Data was measured at $V_D$ =30 mV48      |

| Figure 2.2 Y-function $(I_D/g_m^{1/2})$ - $V_G$ characteristic in a n-channel Nanosheet MOSFET with a straight fitting line (red dash line)          |

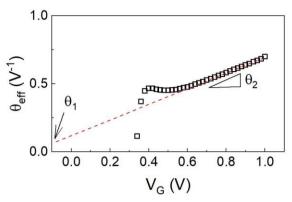

| Figure 2.3 Extracted effective mobility attenuation coefficient $\theta eff$ - $V_G$ from Y-function with a straight line in high inversion region51 |

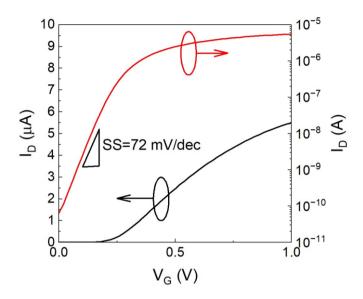

| Figure 2.4 Subthreshold characteristic 2-vertical stacked Nanosheet FET (W=40 nm/L=120             |

|----------------------------------------------------------------------------------------------------|

| nm)52                                                                                              |

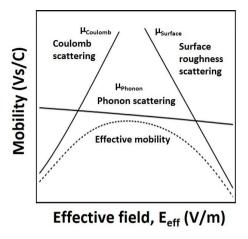

| Figure 2.5 Schematic diagram to the effective field dependence of mobility by three                |

| different scattering mechanism [8]                                                                 |

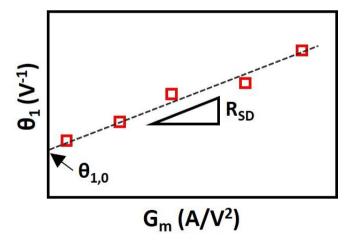

| Figure 2.6 Extraction of the series resistance $R_{SD}$ and intrinsic first order mobility         |

| degradation coefficient $\theta$ 1,0                                                               |

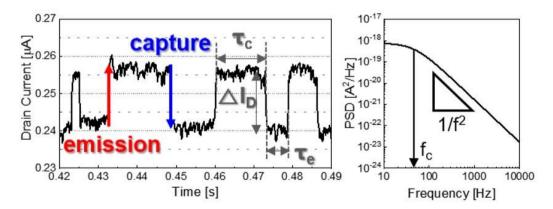

| Figure 2.7 Typical RTS signal in the high-k Omega-gate MOSFET. And, schematic noise                |

| power density spectra: RTS signal described by a Lorentzian function with the corner               |

| frequency f <sub>c</sub> , determined by the average capture and emission times of the trap [14]59 |

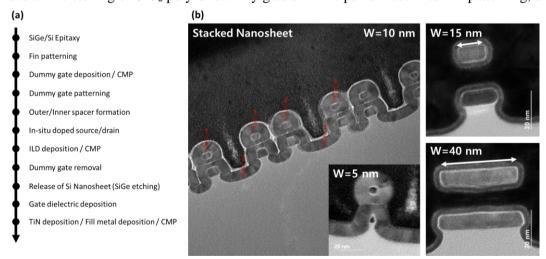

| Figure 3.1 (a) The process flow of 2-vertically stacked NS FETs. (b) TEM images of GAA             |

| NS FETs with 2-vetically stacked channels: top wire has GAA structure and bottom one               |

| has Omega gate shape67                                                                             |

| Figure 3.2 Agilent B1500 semiconductor parameter analyzer and 300 mm Cascade                       |

| MicroTech probe station                                                                            |

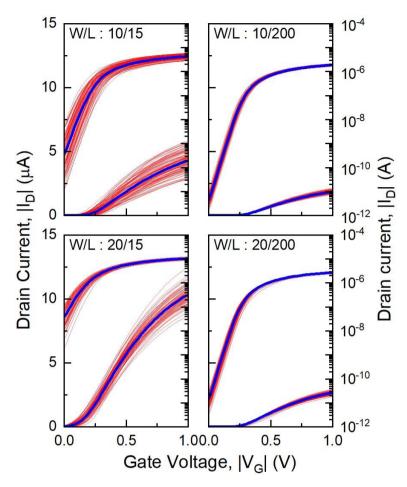

| Figure 3.3 Typical $I_D$ - $V_G$ characteristics (red line) for various geometries on over 90 dies |

| and average values (blue) on measured devices with $W=10$ , 20 nm and $L=15$ , 200 nm71            |

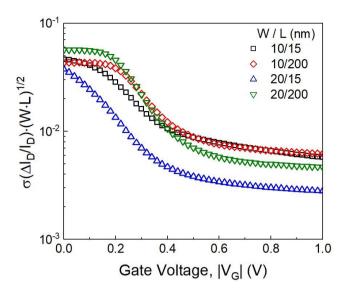

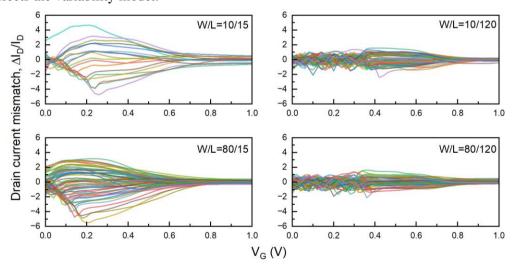

| Figure 3.4 Drain current mismatch of NW FETs according to gate voltage on various                  |

| geometries72                                                                                       |

| Figure 3.5 Normalized standard deviations of the drain current mismatch for different              |

| geometries in linear region                                                                        |

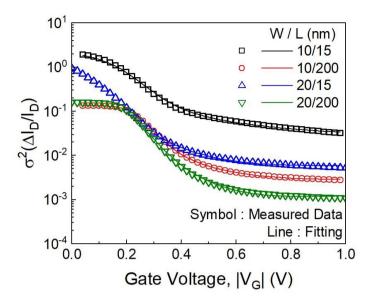

| Figure 3.6 Mismatch variance versus gate voltage for different geometries. Mismatch                |

| fitting model (line) has a good agreement with experimental results (symbol)74                     |

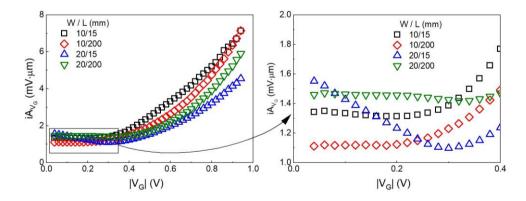

| Figure 3.7 Individual matching parameter $iA\Delta VG$ versus gate voltage $V_G$ extracted by                                                   |

|-------------------------------------------------------------------------------------------------------------------------------------------------|

| measured data for various geometries                                                                                                            |

| Figure 3.8 The standard deviations of each electrical parameter- $(WL)^{-1/2}$ and straight line for extracting the Pelgrom's coefficient $A_s$ |

| extracting the reigion 8 coefficient $A_s$ /C                                                                                                   |

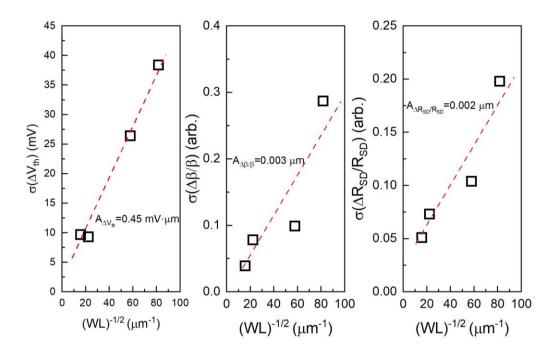

| Figure 3.9 Standard deviation of Mismatch parameters versus the inverse effective area, (a)                                                     |

| $V_{TH}$ , and (b) ideality factor, respectively. Standard deviation of $V_{TH}$ vs. (c) reverse of                                             |

| effective width, and (d) reverse of length, respectively                                                                                        |

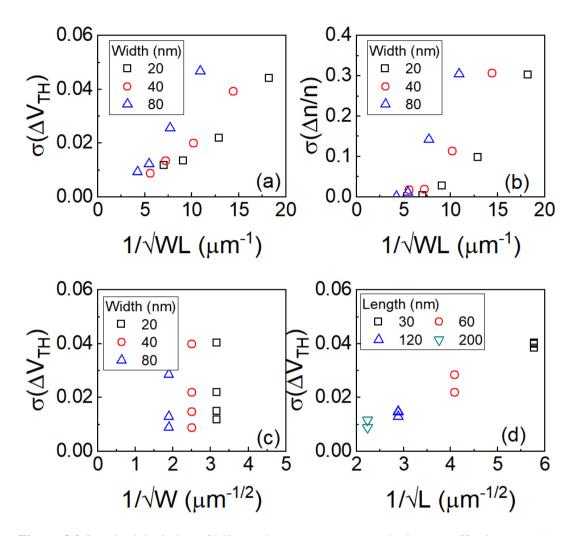

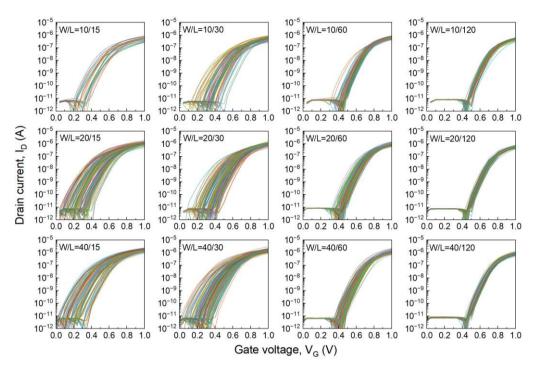

| Figure 3.10 The linear and log scaled transfer characteristics of 2-vertically stacked NS                                                       |

| MOSFETs with variations $W$ =10, 20, 40, and 80 nm and $L$ =15, 30, 60, and 120 nm. Drain                                                       |

| current measurements were carried out on pairs of 165 over 300 mm whole wafer78                                                                 |

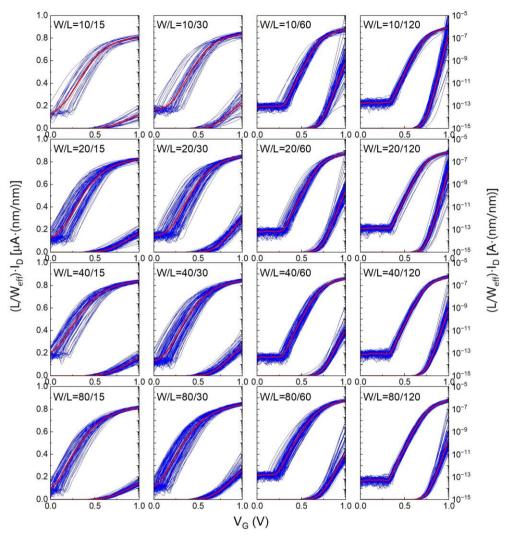

| Figure 3.11 Drain current mismatch curves as a function of gate voltage with different                                                          |

| dimensions                                                                                                                                      |

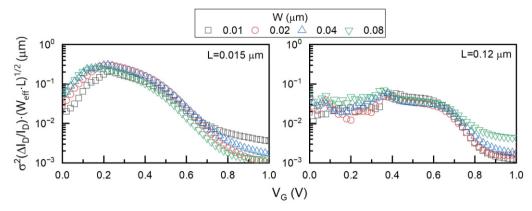

| Figure 3.12 Drain current mismatch variance with normalization of effective device area as                                                      |

| a function of gate voltage80                                                                                                                    |

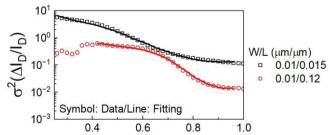

| Figure 3.13 A good agreement with experimental results (Symbol) and fitting (line) with                                                         |

| Length variation 0.015 and 0.12 μm with fixed width=0.01 μm80                                                                                   |

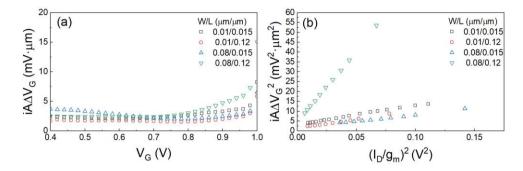

| Figure 3.14 (a) the induvial matching parameter, $iA\Delta V_G^2$ as a function of gate voltage, (b)                                            |

| Individual matching parameter vs. extracted by experimental data, $(I_D/g_m)^2$ with various                                                    |

| device geometries81                                                                                                                             |

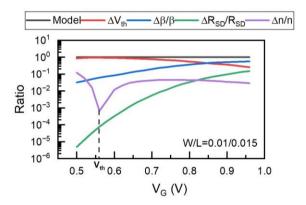

| Figure 3.15 The ratio of each term in the drain variability model                                                                               |

| Figure 3.16 The transfer characteristics of 2-vertically stacked nanosheet FETs with                                                            |

| various dimensions83                                                                                                                            |

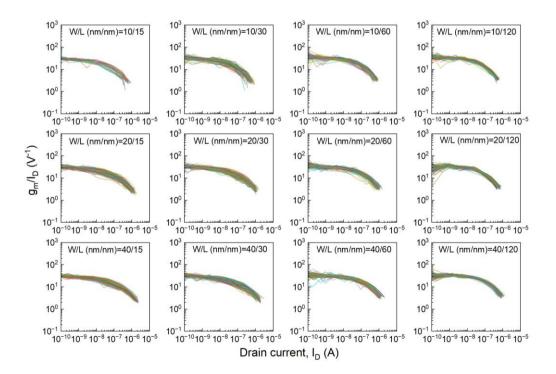

| Figure 3.17 The $g_m/I_D$ of 2-vertical stacked nanosheet FETs with various dimensions. The                       |

|-------------------------------------------------------------------------------------------------------------------|

| dispersion of $g_m/I_D$ considers negligible comparing with drain current variation                               |

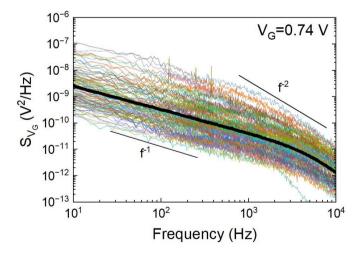

| Figure 3.18 The input-referred gate voltage noises with $V_G$ =0.74 V (various colored lines)                     |

| and logarithmic average gate voltage noise (black line) in the case of device geometry                            |

| (W/L=0.01/0.12 μm/μm)85                                                                                           |

| Figure 3.19 The logarithmic standard deviation of input-referred gate voltage noise vs. (a)                       |

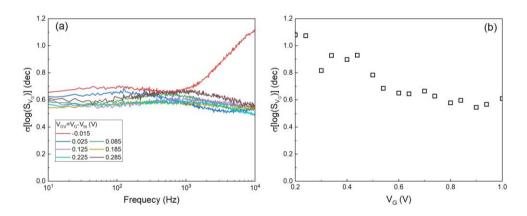

| frequency with 7 points of $V_{OV}$ . (b) gate voltage $V_G$ at $f=10$ Hz86                                       |

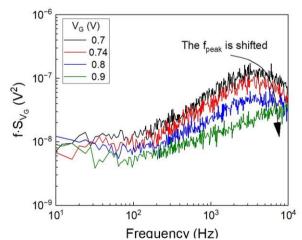

| Figure 3.20 The normalization with frequency of input-referred gate voltage noise vs.                             |

| frequency. There is the shift of f <sub>peak</sub> following gate voltage increasing87                            |

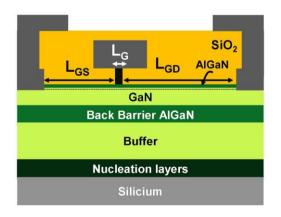

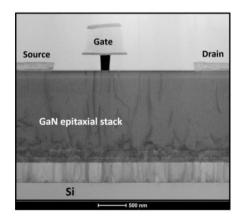

| Figure 4.1 Schematic of the epitaxial stack and TEM cross section of GaN/Si HEMTs93                               |

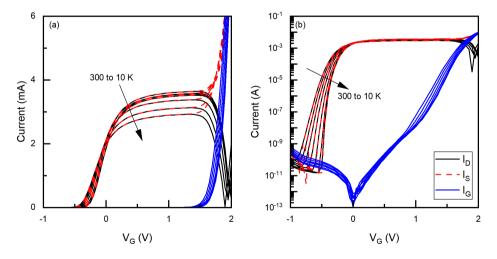

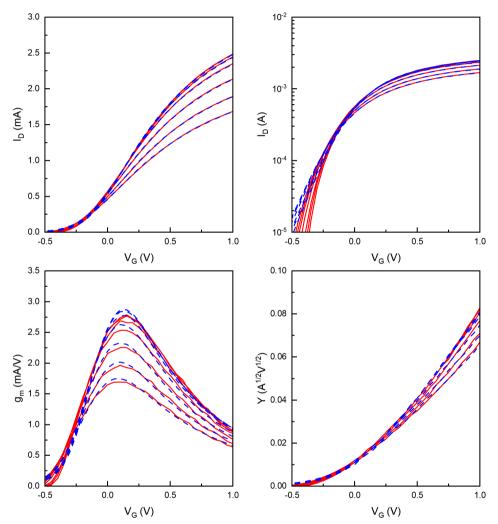

| Figure 4.2. Typical $I_d$ - $V_g$ characteristics in linear (a) and log (b) scale as obtained on                  |

| GaN/Si HEMT devices for various temperatures <i>T</i> =10, 50, 100, 150, 200, 250, and 300 K                      |

| $(V_d=50 \text{ mV}, L_g=150 \text{ nm}, L_{gs}=1  \mu\text{m}, L_{gd}=1.5  \mu\text{m}, W_g=100  \mu\text{m})96$ |

| Figure 4.3. Typical $g_m$ - $V_g$ (a) and Y- $V_g$ (b) characteristics as obtained on GaN/Si HEMT                 |

| devices with various temperatures T=10, 50, 100, 150, 200, 250, and 300 K ( $V_d$ =50 mV,                         |

| $L_g$ =3000 nm, $L_{gs}$ =1 $\mu$ m, $L_{gd}$ =1.5 $\mu$ m, $W_g$ =100 $\mu$ m)98                                 |

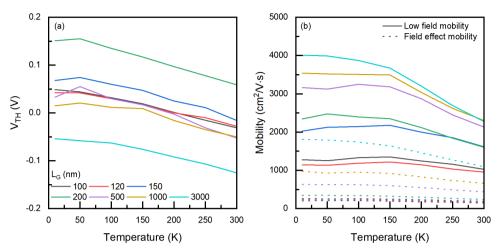

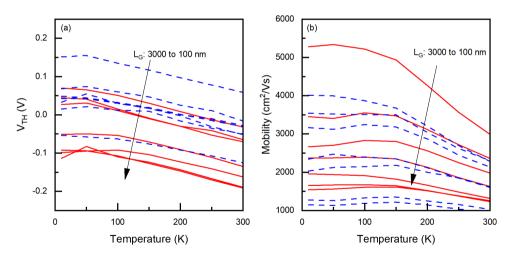

| Figure 4.4. Variations with temperature of a) threshold voltage $V_{th}$ and b) electron low field                |

| mobility $\mu_0$ (red solid line) and $\mu_{femax}$ (blue dashed lines) as obtained on GaN/Si HEMT                |

| devices with various gate lengths $L_g(nm)=100, 120, 150, 200, 500, 1000$ and 3000 ( $V_d=50$                     |

| mV, $L_{gs}$ =1 $\mu$ m, $L_{gd}$ =1.5 $\mu$ m, and $W_g$ = 100 $\mu$ m)                                          |

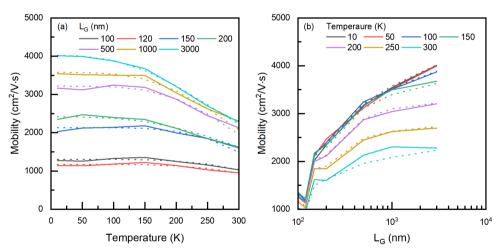

| Figure 4.5. a) Experimental (solid lines) and Eq. (5.6) modeled (dashed lines) variations of                      |

| electron low field mobility $\mu_{\theta}$ with gate length $L_g$ for various temperatures $T=10, 50, 100,$       |

| 150, 200, 250, and 300 K and b) variations of low field mobility $\mu_0$ with temperature $T$ for                 |

| various gate lengths $L_g$ = 100, 120, 150, 200, 500, 1000 and 3000 nm as obtained on                                            |

|----------------------------------------------------------------------------------------------------------------------------------|

| GaN/Si HEMT devices ( $V_d$ =50 mV, $L_{gs}$ =1 $\mu$ m, $L_{gd}$ =1.5 $\mu$ m, $W_g$ = 100 $\mu$ m). Model                      |

| parameters: $\mu_{ph}$ =5000 cm <sup>2</sup> /Vs, $\mu_N$ =4100 cm <sup>2</sup> /Vs, $L_c$ =160 nm, $\alpha$ =3, $\beta$ =1.3100 |

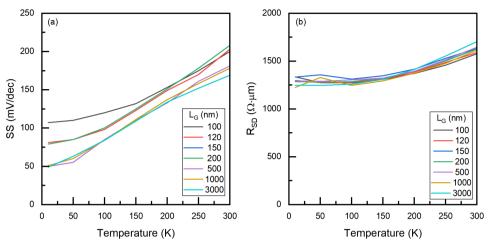

| Figure 4.6. Typical variations with temperature of subthreshold swing SS (a) and access                                          |

| series resistance $R_{sd}$ (b) as obtained on GaN/Si HEMT devices for various gate lengths $L_g$ =                               |

| 100, 120, 150, 200, 500, 1000 and 3000 nm ( $V_d$ =50 mV, $L_{gs}$ =1 $\mu$ m, $L_{gd}$ =1.5 $\mu$ m, $W_g$ =100                 |

| μm)                                                                                                                              |

| Figure 4.7. Experimental (red solid lines) and Lambert-W model fits (blue dashed lines) of                                       |

| the $I_d(V_g)$ , $g_m(V_g)$ and $Y(V_g)$ characteristics for various temperatures $T=10, 50, 100, 150,$                          |

| 200, 250 and 300 K as obtained on GaN/Si HEMT devices ( $V_d$ =50 mV, $L_g$ =3000 nm, $L_{gs}$ =1                                |

| $\mu$ m, $L_{gd}$ =1.5 $\mu$ m, $W_g$ =100 $\mu$ m)                                                                              |

| Figure 4.8. Variations with temperature of a) threshold voltage $V_{th}$ and b) electron low field                               |

| mobility $\mu_0$ , as obtained from LW function extraction (red solid line) and from Y-function                                  |

| method extraction (blue dashed lines) on GaN/Si HEMT devices with various gate lengths                                           |

| $L_g$ = 100, 120, 150, 200, 500, 1000 and 3000 nm ( $V_d$ =50 mV, $L_g$ s=1 $\mu$ m, $L_g$ d=1.5 $\mu$ m,                        |

| $W_g = 100 \ \mu \text{m}$ )                                                                                                     |

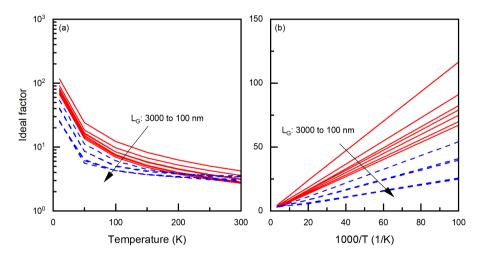

| Figure 4.9. Variations of subthreshold ideality factors $n_L$ (red solid lines) and $n_{SS}$ (blues                              |

| dashed lines) and b) with temperature (a) and reciprocal temperature (b) as obtained on                                          |

| GaN/Si HEMT devices for various gate lengths $L_g$ = 100, 120, 150, 200, 500, 1000 and                                           |

| 3000 nm ( $V_d$ =50 mV, $L_{gs}$ =1 $\mu$ m, $L_{gd}$ =1.5 $\mu$ m, $W_g$ =100 $\mu$ m)                                          |

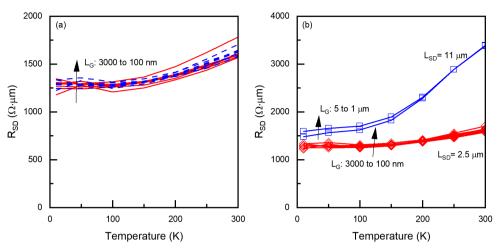

| Figure 4.10. a) Variations with temperature of series resistance values $R_{sd}$ extracted by LW                                 |

| function method (red solid lines) and by Y-function method (blue dashed lines) as obtained                                       |

| on GaN/Si HEMT devices for various gate lengths $L_g$ = 100, 120, 150, 200, 500, 1000 and                                        |

| 3000 nm ( $V_d$ =50 mV, $L_{gs}$ =1 $\mu$ m, $L_{gd}$ =1.5 $\mu$ m, $W_g$ =100 $\mu$ m). b) Variations with temperature          |

| of series resistance values $R_{cd}$ extracted by Y-function method for two access region                                        |

| distances $L_{sd}$ =2.5 µm and 11 µm as obtained on GaN/Si HEMT devices for various gate                              |

|-----------------------------------------------------------------------------------------------------------------------|

| lengths $L_g$ = 1000 and 5000 nm ( $V_d$ =50 mV, $L_{gs}$ =5.5 $\mu$ m, $L_{gd}$ =5.5 $\mu$ m, $W_g$ =125 $\mu$ m)105 |

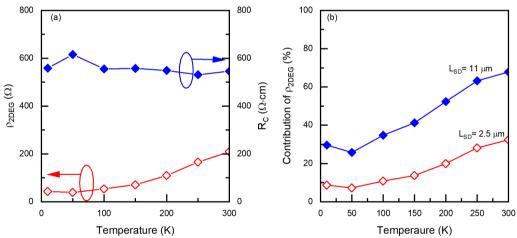

| Figure 4.11. a) Variations with temperature of the 2DEG sheet resistance $\rho_{2DEG}$ (red solid                     |

| lines) and of contact resistance $R_c$ (blue dashed lines) as obtained from $R_{sd}$ TLM analysis                     |

| on GaN/Si HEMT devices with various access region lengths $L_{sd}$ =2.5 and 11 $\mu$ m. b)                            |

| Variations with temperature of percentage contribution of 2DEG access region resistance                               |

| to the total source-drain resistance $R_{sd}$ for two access region distances $L_{sd}$ =2.5 $\mu$ m and               |

| $L_{sd}$ =11 µm as obtained from Figure 4.10(b) data                                                                  |

|                                                                                                                       |

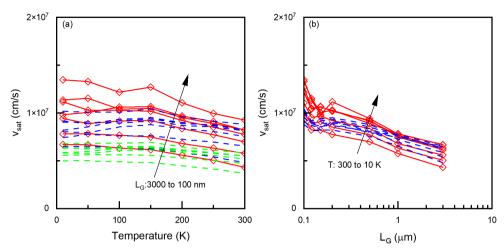

| Figure 4.12. a) Variations with temperature of saturation velocity $v_{sat}$ as extracted from Y-                     |

| function (Eq. (4.4), red solid lines), or using the standard method with (blue dashed lines)                          |

| or without (green dashed lines) $R_{sd}$ correction (Eq. (6)), as obtained for various gate lengths                   |

| $L_g$ = 100, 120, 150, 200, 500, 1000 and 3000 nm ( $V_g$ =1.5 V, $V_d$ =5 V & $V_d$ =50 mV, $W_g$ =100               |

| $\mu$ m). b) Variations with gate length of saturation velocity $v_{sat}$ as extracted from Y-function                |

| (Eq. 4.4, red solid lines), or using the standard method (blue dashed lines) with $R_s$                               |

| correction (Eq. 4.5), as obtained on GaN/Si HEMT devices for various temperatures107                                  |

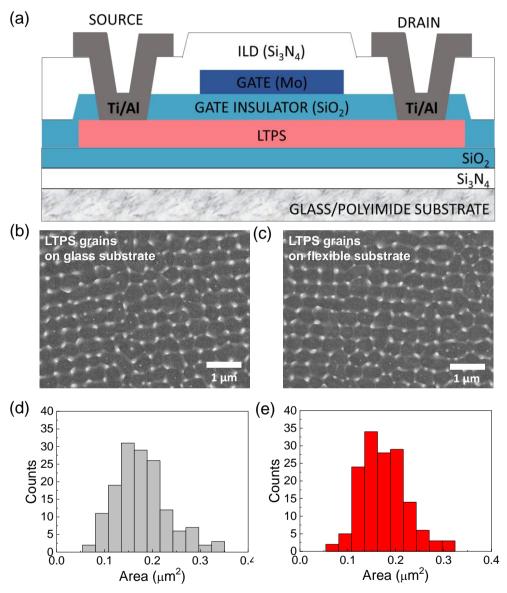

| Eigen 5.1 (a) Cross section of LTDS TETs on along and flowible substrates. EE SEM                                     |

| Figure 5.1. (a) Cross section of LTPS TFTs on glass and flexible substrates. FE-SEM                                   |

| images of LTPS films on (b) glass and (c) flexible substrate. The histogram of grains area                            |

| on (d) glass and (e) flexible substrate shows that mean value is 0.178 and 0.175 $\mu m^2$ ,                          |

| respectively                                                                                                          |

|                                                                                                                       |

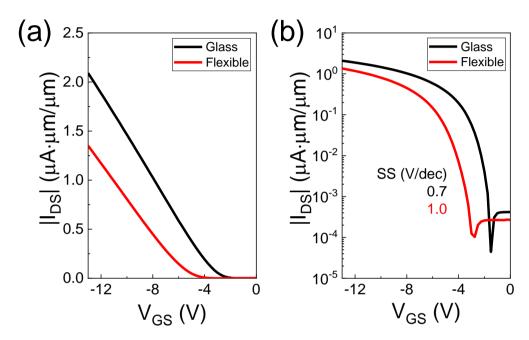

| Figure 5.2. (a) Transfer curves for glass and flexible substrates at 300 K. Drain-to-source                           |

| current $I_{DS}$ for the flexible substrate is approximately 40 % lower than that of the glass                        |

| substrate. By using the flexible substrate, threshold voltage $V_{TH}$ is negatively shifted                          |

comparing to the glass substrate. (b) Subthreshold swing SS of LTPS on the flexible

substrate is 30 % higher than the device on the glass substrate......117

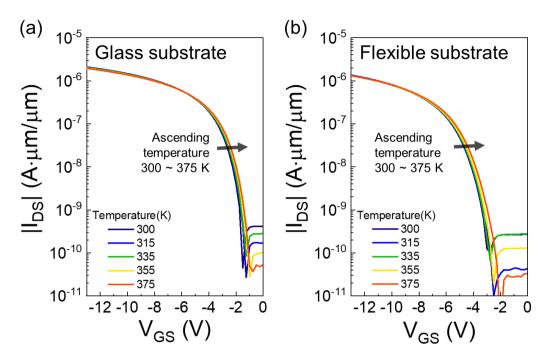

| Figure 5.3. Temperature dependent transfer characteristics of LTPS TFTs on glass and                   |

|--------------------------------------------------------------------------------------------------------|

| flexible substrates. From 300 K to 375 K, $V_{\text{TH}}$ changes in positive direction for both glass |

| and flexible substrates. Higher temperature makes $ I_{DS} $ lower and SS higher118                    |

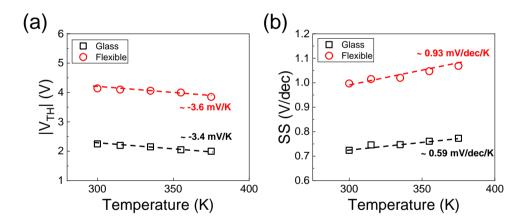

| Figure 5.4. Threshold voltage $V_{TH}$ and subthreshold swing $SS$ as a function of temperature        |

| for LTPS TFTs. (a) The magnitude of $/V_{TH}/$ for the flexible substrate is higher than that of       |

| the glass substrate at each temperature condition, whereas the slope of $/V_{TH}/-$ temperature is     |

| similar. (b) Higher temperature makes SS of LTPS TFT on the flexible substrate increase.               |

| In the case of SS, flexible substrate has roughly 1.5 times larger SS-temperature sensitivity,         |

| which means higher impact of $C_{it}$ and $C_{dep}$                                                    |

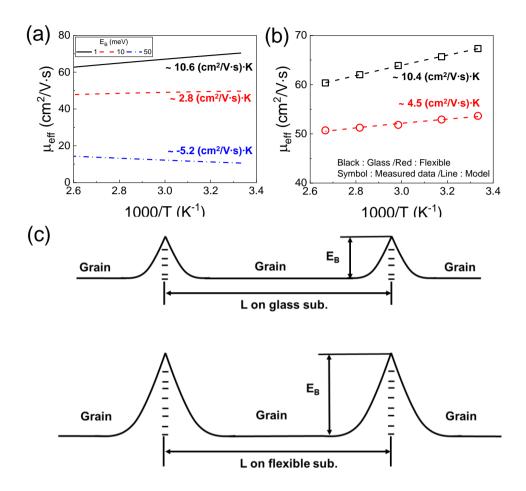

| Figure 5.5. (a) Simulation of temperature dependence of effective mobility $\mu_{eff}$ under           |

| various grain boundary barrier height $E_B$ (1, 10, and 50 meV) for fixed grain size $L_{grain}$ =0.7  |

| μm. (b) The experimental data which are well fitted by the model in the both cases. Less               |

| sensitive temperature dependence of $\mu_{eff}$ was shown in the lower value. (c) Illustration of      |

| LTPS active channels on both glass and flexible substrates by applying extracted $E_B$ and             |

| $L_{grain}$ . By fitting the measured data to model, $E_B$ and $L_{grain}$ can be extracted            |

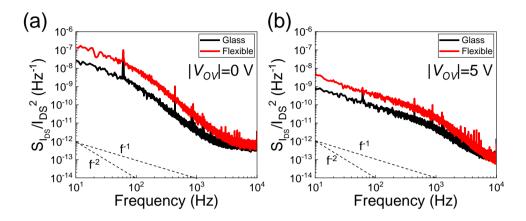

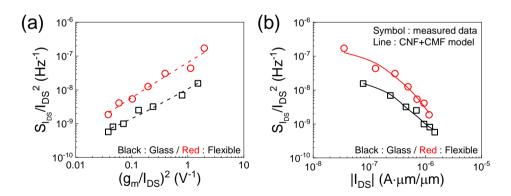

| Figure 5.6. Comparisons of the normalized noise power spectral density PSD at different                |

| overdrive voltages $/V_{OV}/$ (a) 0 V and (b) 5 V. For both $/V_{OV}/$ , flexible substrate shows 1-   |

| order higher noise level than that of glass substrate at 10 Hz. The corner frequencies $(f_c)$         |

| are observed, which is related to carrier trapping/de-trapping time                                    |

| Figure 5.7. Noises spectrum of LTPS TFTs on glass (Black) and flexible (Red) substrates                |

| which were normalized by $I_{DS}$ at frequency f=10 Hz. (a) $S_{IDS}/I_{DS}^2$ is proportional to      |

| $(g_m/I_{DS})^2$ . The carrier number fluctuation correlated carrier mobility fluctuation CNF+CMF      |

| model is a function of $(g_m/I_{DS})^2$ . (b) Measured data (black and red symbols) were well fitted   |

| by CNF+CMF model                                                                                       |

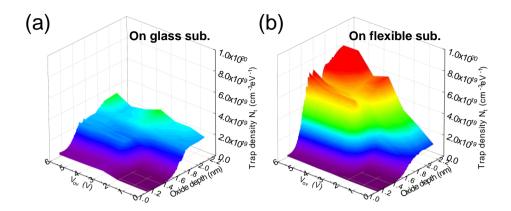

Figure 5.8. 3D Contour of trap density  $N_t$  distribution for oxide depth z and  $|V_{OV}|$  for glass substrate and flexible substrate, respectively. It is observed that LTPS TFTs on both substrates have gate bias dependence. (a) For the LTPS TFT on the glass substrate,  $N_t$  is less depending on  $V_{OV}$  and z compared to the device on the flexible substrate. (b) In contrast, higher  $|V_{OV}|$  increases  $N_t$  for the LTPS TFT on the flexible substrate. Especially at  $|V_{OV}|$ =6 V, peak of  $N_t$  is shown. At this point, flexible substrate shown approximately 4 times higher  $N_t$  than glass substrate.

#### Chapter 1. INTRODUCTION

#### 1.1 Semiconductor Market Trend

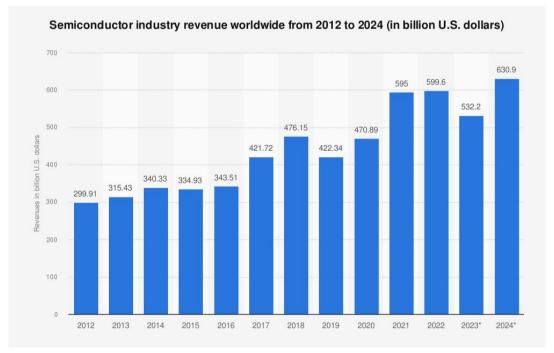

In the current situation, the emergence of technologically advanced devices, such as smartphones and tablet PCs, has significantly impacted the trends within the semiconductor market. The inception of these smart devices can be traced back to the IBM Simon, which was introduced in the year 1993 as the world's first-ever smart device. This revolutionary gadget served as a convergence between a mobile phone and a personal computer, offering a wide range of features such as a schedule manager, an address book, a world clock, a fax machine, various games, and a calculator, among others. Over time, smart devices have continued to evolve, resulting in the development of other notable devices like the personal digital assistant, the iPhone, and the Galaxy Tab. It is worth noting that the introduction of the iPhone and Android smartphones into the market has had a profound impact. These

**Figure 1.1** Semiconductor industry revenue worldwide from 2012 to 2024 [1]

devices have paved the way for the creation of countless smart applications that utilize a simple user interface, a global positioning system (GPS), motion sensors, and Wi-Fi capabilities, among other features. These applications play a crucial role in bridging the gap between human users and smart devices, enhancing the overall user experience, and facilitating seamless interaction.

The exponential growth of smart devices in the market is a result of the harmonious combination between applications and hardware. It has been predicted that the smartphone and tablet PC markets will experience a significant increase in growth. This increased demand for smart devices has led to changes in the trends of the semiconductor memory market. For instance, there has been a shift from PC Dynamic Random Access Memory (DRAM) to mobile DRAM and from Hard Disk Driver (HDD) to Solid-State Drives (SSDs) and NAND flash memory. A prime example of this shift is the expected growth of the market share of mobile DRAM in the DRAM market in early 2010s, which is projected to increase from 5.5% in 2010 to 7.1% in 2011, resulting in a total growth rate of over 100% [2]. In order to be utilized in mobile devices, mobile DRAM must be both cost-effective and possess high device density. Additionally, it must be developed to have high performance capabilities while maintaining low power consumption. On the other hand, the non-memory (specifically, system IC) device market is also experiencing changes due to the expansion of the smart device market.

The system IC market is experiencing growth, with a particular focus on the application processor (AP) for smart devices. In line with this trend, a strategic industrial feature known as the 'fabless company' has emerged, as shown in Tabel 1.1. This term refers to a semiconductor vendor that engages in the design, testing, and selling of chips without having its own semiconductor manufacturing facilities. Instead, it relies on other foundries to carry out the fabrication of the chips. While memory devices require an integrated device manufacturer, non-memory devices necessitate the capability to cater to customer requests through small quantity batch production. Consequently, fabless companies that prioritize chip design serve as the promising business core for the non-memory device sector.

Despite being one of the more recent trends in non-memory devices, the fabless company plays a crucial role in the research and development of device scaling down and advanced transistor technology. This includes the exploration of FinFETs, Fully Depleted Silicon-on-Insulator (FDSOI) and gate-all around (GAA) nanowires MOSFETs, such as the ones studied in the present thesis. These advancements in transistor technology remain of utmost importance as they contribute significantly to the improvement of fabrication yield, low power consumption, and overall device performance, among other factors. In essence, the fabless company's efforts in exploring these technologies and techniques are vital in driving progress in the field of non-memory devices.

Table 1.1 List of Top 10 Largest Semiconductor Companies by and Country in 2023 [3]

| Rank | Company  | Country       |

|------|----------|---------------|

| 1.   | Intel    | United States |

| 2.   | Samsung  | South Korea   |

| 3.   | TSMC     | Taiwan        |

| 4.   | SK Hynix | South Korea   |

| 5.   | Micron   | United States |

| 6.   | Qualcomm | United States |

| 7.   | Broadcom | United States |

| 8.   | Nvidia   | United States |

| 9.   | TI       | United States |

| 10.  | Infineon | Germany       |

#### 1.2 Device Scaling Down

As the dimensions of devices decrease, the task of fabricating these devices becomes more challenging. This can be observed in the case of integrated circuits, which become denser and more intricate as devices are scaled down. Consequently, various issues arise in areas such as lithography, interconnects, and processing. Scaling down the device size is

essential in order to enhance device performance, including augmented switching speed and reduced power consumption. For instance, the delay time  $\tau$  of a circuit can be decreased by adjusting the gate length L, which is expressed as a function of the parameter S in Figure 1.2.

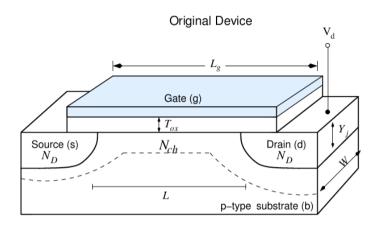

**Figure 1.2** Architecture of an n-channel MOSFET and MOSFET constant electric field scaling by a factor of S [4].

There are two theories regarding the scaling of Metal-Oxide-Semiconductor (MOS) devices: Constant Electric (CE) field scaling and Constant Voltage (CV) scaling. The CE scaling theory suggests that in order to effectively manage the short channel effect, it is necessary to reduce both the horizontal and vertical dimensions of the device. Furthermore, it is proposed that the applied voltage should be decreased and the substrate doping concentration should be increased proportionally. These recommendations are summarized

in Figure 1.2, which provides a visual representation of the proposed scaling approach.

The CV theory, which is a theory that retains the same scaling down as the CE, does not alter the power supply voltage. This means that in order to maintain the charge-field, the doping densities are increased by a factor of  $S^2$ . However, it is important to note that the CV scaling inherently leads to a continuous increase of the transistor's internal electric field. This increase can potentially result in reliability problems such as electron migration, hot carrier degradation, and oxide breakdown in recent CMOS process generations. As a consequence, since the 0.5  $\mu$ m MOS technology, the industry's preferred scaling methodology has been the CE.

**Table 1.2** CE scaling of MOSFET device and circuit parameters [5]

| Parameter                             | 1/S Constant Field Scaling | 30% Scaling Field Scaling |

|---------------------------------------|----------------------------|---------------------------|

| Physical Device Dimension             | 1/S                        | 0.7                       |

| Supply and threshold voltage          | 1/S                        | 0.7                       |

| $C_{ox} = (\varepsilon Area)/T_{ox}$  | 1/S                        | 0.7                       |

| Gate Capacitance=WL/Tox               | 1/S                        | 0.7                       |

| $Current=(W/L)(1/T_{ox}V_{DD}^{2})$   | 1/S                        | 0.7                       |

| Propagation Delay=CV <sub>DD</sub> /I | 1/S                        | 0.7                       |

| Frequency                             | S                          | 1.43                      |

| Dynamic Power= $CV_{DD}^2 f_{clk}$    | $1/S^2$                    | 0.5                       |

| Leakage Power                         | Exponential                | Exponentail               |

| Energy                                | $1/S^3$                    | 0.34                      |

The fundamental principle underlying the CE theory is predicated upon the notion that the various physical attributes, namely the gate length, transistor width, and oxide thickness, as well as the voltages surrounding the power supply and the threshold, are accordingly and accurately adjusted and modified in accordance with a scaling factor of 1/S, where S denotes a value greater than unity (S > 1).

Consequently, the current, gate capacitance, and propagation delay also scale by a factor of 1/S. Hence, with a 30% reduction of all the device parameters (1/S = 0.7), improvements,

close to 50% in the operation frequency, are achieved for each generation. Table 1.2 lists the CE scaling rules for various device parameters and circuit performance factors. Evidently, the resulting switching energy scales by  $I/S^3$ , whereas the dynamic power scales by  $I/S^2$ . However, for a constant die size, the power dissipation due to the dynamic switching currents remains relatively constant with scaling, because the number of switching elements for the same die size increases by a factor of  $S^2$ . The negative effect of the CE is that the subthreshold current increases exponentially, as the threshold voltage scales. For example, consider a device with a  $V_{th}$  of 400 mV that is to be scaled by 0.7. For a constant die size, scaling provides around a 43% (S = 1.43) frequency improvement and doubles the number of devices. The dynamic power dissipation scales by unity, but the leakage current increases by a factor of  $1.43 \times 10(V_{th}/S^{(1-0.7)}) = 45$ .

Since the primary drivers behind the scaling of technology are mainly centered around improving performance and achieving efficient device integration, the comprehensive understanding and application of the CE scaling theory becomes a crucial and indispensable blueprint. However, with the continuous reduction in the dimensions and voltages of these devices, the emergence of leakage power as a prominent obstacle in both current and future technologies cannot be ignored. Consequently, the process of scaling VLSI technology gives rise to an array of complex and formidable challenges, encompassing power dissipation, effective management of leakage, and the adverse impacts of short channel effects. This multifaceted problem is further worsened in the context of portable energy-constrained VLSI applications, where the unnecessary drainage of battery power during extended idle periods poses a significant concern.

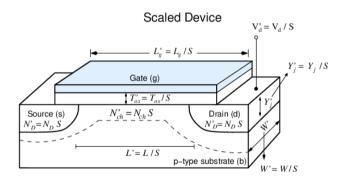

Gordon Moore, the co-founder of Intel, posits that the quantity of transistors present on a single chip shall increase twofold approximately every two years, a phenomenon commonly recognized as Moore's law, which has been widely acknowledged for a period of roughly 40 years, and has consequently propelled the industry forward (as depicted in Figure 1.3). This principle appears to have been effective thus far; however, it must be noted that the scaling limit of device dimensions is nearing its conclusion. At present, the Intel 7 nm

process node in 2023 has been utilized for mass production. In accordance with Moore's law, it is predicted that within several years, gate lengths on the order of a few nanometers, which represents the inherent physical constraint of the MOSFET, will be employed. Hence, the introduction of a novel conceptual framework for device scaling becomes essential in order to keep advancing in device yield and performance beyond the confines of Moore's law.

Figure 1.3 Number of transistors versus per year (Microprocessor). [6]

#### 1.3 Fully Depleted Silicon on Insulator (FDSOI) Technology

#### 1.3.1 State-of-the-art SOI Technology

The process of scaling bulk CMOS technology faces several significant obstacles, which has led to the exploration of alternative technologies such as FinFET, GAA nanowire

FET, and FDSOI. Among these alternatives, the FDSOI MOSFET stands out as a highly promising candidate for future technology nodes due to its potential advantages in terms of reduced variability and improved electrostatic integrity. This type of device is composed of a remarkably thin, fully depleted transistor body that is positioned on top of a buried oxide (BOX) layer, effectively sandwiched between the channel and the substrate. By employing an very lightly doped body, the floating body effect is eliminated, thereby providing immunity to variations in threshold voltage caused by random dopant fluctuations (RDF). Additionally, the body thickness ( $T_{si}$ ) plays a crucial role in ensuring optimal electrostatic control by the gate.

FDSOI technology emerged as a progression of partially depleted SOI technology with the aim of eliminating the memory effect. FDSOI devices are characterized by having thin body structures, wherein the body is either rarely doped or completely undoped. Positioned beneath the channel, a BOX layer, which may be either thick (100 nm) or thin (10 nm), serves as an insulator, that also gives the possibility of bottom gate biasing to control the threshold voltage. In contemporary FDSOI processes, the source and drain regions are typically heightened and configured with facets, while the gate of the device is composed of metal gate stacks and high-k dielectric materials. Furthermore, in instances where a thin BOX is employed, doping beneath the BOX, known as ground plane (GP) doping, is sometimes implemented.

The advantages of FDSOI technology bound low variability, which related to the consistent and predictable behavior of the devices, good electrostatic control, which ensures reliable and stable operation, and the ability to integrate multiple threshold devices, allowing for enhanced flexibility in circuit design. However, any attempt aimed at enhancing the manufacturing process of FDSOI technology would be rendered meaningless if it does not coincide with improvements in circuit design, performance, and reliability. It is imperative that advancements in both the manufacturing process and circuit design are pursued in combination to fully capitalize on the potential benefits of FDSOI technology.

The current trend in the field of digital circuit design is focused on achieving maximum

performance while consuming low power. It has been previously mentioned that with FDSOI technology, high performance can be attained by reducing the threshold voltage. This reduction can be achieved through two methods: metal gate work-function engineering or back-biasing. However, it is important to note that lowering the threshold voltage poses a risk of forward biasing the diode between two adjacent ground planes, which in turn complicates the overall circuit design process.

Another potential advantage of FDSOI technology lies in its ability to have very low junction capacitances, particularly in the case of a thick BOX. However, it is worth mentioning that the raised source and drain structures introduce additional capacitance to the gate. One way to mitigate this issue is by changing the shape of the source and drain regions to a faceted shape, which aids in reducing the gate capacitance. However, it should be noted that even with this modification, the gate capacitance may still be higher compared to bulk technology. Therefore, unless the capacitance can be lowered through appropriate process engineering, there is no clear speed advantage of FDSOI over bulk technology in terms of capacitance.

Finally, it is important to consider the impact of Drain-Induced Barrier Lowering (DIBL) technology on the performance of FDSOI devices. A device with lower DIBL technology, exhibits a better subthreshold slope and consequently a higher linear current when compared to a device optimized for the same  $I_{ON}$  and  $I_{OFF}$  in a higher-DIBL technology. This suggests that the effective current in FDSOI technology has the potential to be higher compared to bulk technology, especially in scenarios involving complex gates and stacked devices.

A more apparent advantage of FDSOI technology lies in its potential applications in low-power systems. One of the primary reasons for this is the elimination of the source and drain pn-junctions, which effectively suppresses any possibility of junction leakage. In addition, the control over short-channel effects can be achieved by adjusting the body and BOX thickness. This control allows for a more conservative scaling of the gate dielectric, mitigating the concerns related to gate-induced leakage. Furthermore, the reduction in  $V_{th}$  roll-off and the utilization of light channel doping contribute to a decrease in threshold

voltage variation. Consequently, this improvement in threshold voltage variation enables the design of high-yield systems even at lower supply voltages. Consequently, the overall potential of FDSOI technology for low-power design is highly promising.

#### 1.3.2 SOI Wafer Fabrication: Smart-Cut<sup>TM</sup> Process

UNIBOND SOI wafers are manufactured through the utilization of the Smart-Cut<sup>TM</sup> process, as mentioned in the study conducted by [7]. The fundamental aspect of this process lies in the combining of ion implantation process and wafer bonding techniques, which facilitates the successful transference of a delicate sheet of the semiconductor material onto a dielectric layer that subsequently transforms into the BOX layer. This particular technology, which was initially formed at the CEA-LETI, has gained widespread popularity and is currently employed on an industrial scale for the production of SOI wafers. The Smart-Cut<sup>TM</sup> process has undergone progressive expansion over time, enabling its utilization in the creation of different variations of SOI wafers. As a testament to its effictiveness, the process has been entrusted to SOITEC, an industry leader in the manufacturing of SOI wafers.

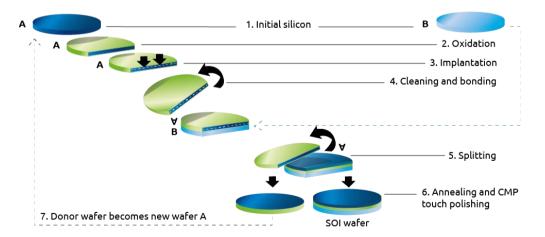

**Figure 1.4** Smart-Cut<sup>TM</sup>, an advanced SOI wafer fabrication technique by SOITEC Inc [7].

The Smart-Cut<sup>TM</sup> process, which is depicted in Figure 1.4 can be comprehensively

elucidated as follows: Primarily, it necessitates the utilization of two wafers, namely wafer 'A', which is referred to as the 'donor' wafer, and wafer 'B', also known as the 'handling' wafer. It is of utmost importance to note that the donor wafer 'A' is subjected to an oxidation process prior to the hydrogen implantation stage, resulting in the formation of an oxide layer on its upper surface, subsequently serving as the BOX layer. The next step entails the precise implantation of hydrogen atoms into the donor wafer 'A' at a specific depth, thereby facilitating the subsequent splitting of the two wafers. Moving on, the handling wafer 'B' can either be in its pristine state or it can be oxidized. The handling wafer plays a essential role in acting as a mechanical support for the SOI structure, ultimately aiding in the successful execution of the Smart-Cut process.

In order to initiate the direct wafer bonding, the wafer 'A' is positioned in a face-down manner onto the wafer 'B'. Subsequently, a two-phase heat treatment is meticulously carried out. During the first phase, which is conducted at an approximate temperature of 500 °C, the donor wafer 'A' undergoes a splitting process along a predetermined plane defined by the range of hydrogen ion implantation. Consequently, the thickest part of wafer 'A' is effectively separated from the bonded wafer structure. This consequential outcome gives rise to two distinct components: firstly, a thin layer consisting of single-crystalline silicon on top of the handle wafer 'B', which is underlaid by the oxide layer, and secondly, the remaining portion of the donor wafer 'A'. It is notable that this residual portion of the donor wafer can be recycled and employed once again as a donor wafer. The second phase of the heat treatment is subsequently implemented at a higher temperature, serving the purpose of strengthening the bond that exists between the Si/BOX layers and the handling wafer 'B'.

Upon the completion of the previous steps, a touch-CMP (Chemical-Mechanical Polishing) process is conducted, which is aimed at ensuring the attainment of optimal uniformity of the silicon films. It is significant to recognize that the process itself is highly

**Figure 1.5** Various utilization of engineered SOI technique for specified commercialized products [8].

adaptable and can be accurately engineered in various ways in order to yield SOI wafers that are specifically tailored to cater to the exigencies of distinct applications, including but not limited to RF (Radio Frequency) switches or photonics. This versatility is vividly illustrated in Figure 1.5, thereby emphasizing the diverse possibilities offered by the Smart-Cut process.

The utilization of SOI technology exhibits significant potential in surpassing the scaling limit of CMOS technology through its distinctive characteristics. One of the key advantages of SOI technology is the ability to minimize or completely eliminate parasitic elements. Many undesired effects that are observed in bulk silicon devices arise from the interaction between the device and the substrate. It is evident that SOI devices are exempt from such interactions with the supporting substrate due to the presence of the BOX layer. Consequently, the implementation of SOI substrates ensures robustness against the latch-up phenomenon, which is commonly observed in bulk devices due to the feedback between the two inherent bipolar transistors.

The Smart-Cut<sup>TM</sup> technique has emerged as the predominant method for producing standard and innovative SOI wafers. This technique is progressively being adopted within the CMOS industry. Its utilization allows for the design and fabrication of novel multi-gate

architectures, enabling the enhancement of device performance and electrical properties.

## 1.4 Overview of Power Electronics

Silicon has been the dominant semiconductor material ever since the advent of solidstate power conversion [9]. However, there has been a consistent rise in the need for greater power capabilities and higher frequencies. Consequently, the investigation of an alternative technology becomes vitally important in order to surpass the constraints of silicon-based electronics. Transistors fabricated from direct bandgap materials, notably III-V compounds like gallium arsenide (GaAs), indium phosphide (InP), and gallium nitride (GaN), present higher electron mobilities, sustain higher voltage magnitude, and exhibit the capability to function at higher frequencies and temperatures in contrast to silicon-based devices.

The high electron mobility transistor (HEMT), which is fabricated from III-V materials, has gathered considerable attention in recent times. In 1980, T. Mimura made the first HEMT utilizing GaAs [10]. GaN has emerged as the preferred option for HEMTs in numerous applications up to 100 GHz. This preference stems from the enhanced capabilities of GaN in delivering superior performance for high power HEMTs, owing to its high carrier density and electron mobility within the channel. Additionally, GaN exhibits higher breakdown and operating high temperature attributed to its larger bandgap [11]. These distinguished properties can make GaN HEMTs the most promising high power amplifier technology for a lot of applications ranging from mobile/wireless applications, radar systems to satellite communication and power systems [12,13,14,15]. The first report of GaN HEMTs were documented in 1993 [16], developing continuously during the last 27 years. Furthermore, during the last decade, these devices have been investigated extensively for their applicability in power electronics [17].

The material characteristics of semiconductors are presented in Table 1.3, in contrast to GaN. [18]. The parameters specified in Table 1.1 are assessed under the condition of 300 K.

The band gaps, relative dielectric constants, and breakdown fields are provided specifically for unintentionally doped (UID) bulk materials.

**Table 1.3** Properties of semiconductor materials used in HEMTs at 300 K [18]

|                                                     | Si   | GaAs | InP  | 4H-SiC | GaN  | SiC  |

|-----------------------------------------------------|------|------|------|--------|------|------|

| Bandgap (eV)                                        | 1.12 | 1.43 | 1.34 | 3.2    | 3.44 | 3.26 |

| Relative dielectric constant, $\epsilon_{r}$        | 11.9 | 12.5 | 12.4 | 10     | 9.5  | 9.7  |

| Breakdown electric field (MV/cm)                    | 0.3  | 0.4  | 0.45 | 3.5    | 3.3  | 3    |

| Saturation electron velocity (10 <sup>7</sup> cm/s) | 1    | 1    | 1    | 2      | 2.5  | 2    |

| Electron mobility (cm²/Vs)                          | 1500 | 8500 | 5400 | 700    | 900  | 700  |

One of the specific benefits of GaN is its easier capacity to form the heterojunction with wider band gap materials, such as aluminium gallium nitride (AlGaN) and aluminium nitride (AlN). It generates a quantum well, commonly referred to as a two-dimensional electron gas (2DEG) channel. This channel is characterized by a significantly high electron density, exceeding 10<sup>13</sup>/cm², and exhibits electron mobility up to 2000 cm²/Vs. Even though GaAs and InP own higher electron mobility, the significantly higher 2DEG density in GaN caused a lower sheet resistance which is the crucial characteristic for applications demanding high power at high frequencies. Additionally, GaN exhibits distinguished properties of higher band gap and breakdown field comparing to different semiconductor such as Si and InP, which empower high voltage operation with GaN HEMTs. Due to its ability to operate at high voltage, GaN HEMTs utilized in high line power converters as well as photovoltaic power converters. Also, with its wide band gap, GaN power electronics were applied in various industries such as automotive, military, and oil industries, etc [19].

## 1.5 Overview of Display Devices

## 1.5.1 Display devices history

The study of display is a fundamental area of research for individuals who reside in this

current era of abundant information. Simultaneously, great advancements have been made in the realm of display technology.

The Plasma Display Panel (PDP), which was once a fascinate spectacle, has its origins in the year 1964, thanks to the ingenuity of Donald B. and Jinslotto. Similar to the fluorescent lamp, the PDP operates by utilizing the concept of a phosphor being placed accurately between two glass plates, upon which a voltage is applied to stimulate the emission of visible light. Comparable to the Liquid Crystal Display (LCD) in terms of possessing a wide viewing angle and a remarkable display of colors and saturation, the PDP finds itself lagging behind in the market due to a rather unfortunate drawback - its propensity for high power consumption and the subsequent generation of heat. This fatal flaw has rendered it somewhat less attractive to consumers. Furthermore, one cannot ignore the ongoing progress and advancements being made in the realm of LCD and Organic Light Emitting Diode (OLED) technology, resulting in the recent developments witnessed in these fields.

The origin and subsequent advancement of LCDs can be attributed to the field of biology. It was in 1888 that F. Reinitzer, an esteemed researcher from Austria, made the groundbreaking discovery of liquid crystal. This crucial moment sparked a series of constant and meticulous research efforts, peaking in the creation of the world's inaugural LCD in the United States in 1971. The fundamental principle of an LCD requires the placement of a meticulously arranged panel containing liquid crystals on the front side, followed by the strategic positioning of a backlight situated behind it. As the backlight traverses through each individual liquid crystal, it undergoes refraction, resulting in an array of distinct and diverse patterns. The consequential passage of light through the color filter and polarizing filter, located at the forefront of the liquid crystal panel, yields the emergence of pixels that exhibit varying hues and intensities, contingent upon the specific refraction pattern encountered. Collectively, these pixels seamlessly amalgamate to form a cohesive and visually captivating screen. While LCDs have undoubtedly superseded CRTs in popularity and usage, it is essential to acknowledge the inherent drawbacks associated with this technology, namely its relatively limited lifespan and propensity for high power

consumption.

## 1.5.2 Display market trend overview

## **Display Generation Dimensions**

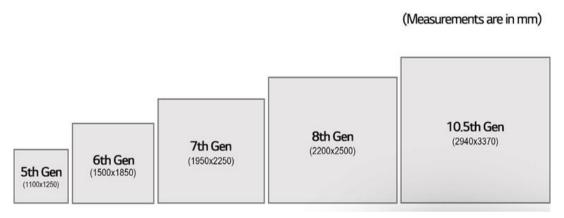

**Figure 1.6** Changes in display panel's generation LG Display Inc. [20]

The Thin Film Transistor (TFT)-LCD industry has witnessed a remarkable growth trajectory due to its strategic expansion of the size of the mother glass, which is commonly referred to as the mother of the panel. This mother glass size, also known as "generation (GEN)" as depicted in Figure 1.6, plays a pivotal role in determining the dimensions of the panel itself, consequently influencing both the size and quantity of panels that can be produced. It is worth noting that, owing to the inherent differences in the panel sizes produced by individual companies, the corresponding sizes of glass substrates may exhibit slight variations across generations [20]. Consequently, it becomes evident that the entirety of display applications are merely mere fragments emanating from the mother glass. For instance, in the context of the 7th generation, we observe the existence of 42-inch panels in quantities of 8 sheets, alongside 47-inch panels in quantities of 6 sheets. Thus, it becomes

evident that the mother glass size predominantly serves as a mere indication of the essential components required for the production of panels by each respective manufacturer, while simultaneously striving to minimize the generation of discarded parts.