# Exploration of security threats in In-Memory Computing Paradigms

Pietro Inglese

## ▶ To cite this version:

Pietro Inglese. Exploration of security threats in In-Memory Computing Paradigms. Micro and nanotechnologies/Microelectronics. Université Grenoble Alpes [2020-..], 2023. English. NNT: 2023GRALT089. tel-04532188

# HAL Id: tel-04532188 https://theses.hal.science/tel-04532188

Submitted on 4 Apr 2024

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### THÈSE

Pour obtenir le grade de

### DOCTEUR DE L'UNIVERSITÉ GRENOBLE ALPES

École doctorale : EEATS - Electronique, Electrotechnique, Automatique, Traitement du Signal (EEATS)

Spécialité : Nano électronique et Nano technologies

Unité de recherche : Techniques de l'Informatique et de la Microélectronique pour l'Architecture des systèmes intégrés

# Exploration des menaces de sécurité dans les paradigmes de calcul en mémoire

# **Exploration of security threats in In-Memory Computing Paradigms**

Présentée par :

### Pietro INGLESE

## Direction de thèse :

Giorgio DI NATALE

DIRECTEUR DE RECHERCHE, Université Grenoble Alpes

Elena-loana VATAJELU

CHARGEE DE RECHERCHE, Université Grenoble Alpes

Directeur de thèse

Co-directrice de

thèse

#### Rapporteurs:

Alberto BOSIO

PROFESSEUR DES UNIVERSITES, École centrale de Lyon

Jean-Michel PORTAL

PROFESSEUR DES UNIVERSITES. IM2NP. Aix-Marseille Université

### Thèse soutenue publiquement le 7 décembre 2023, devant le jury composé de :

Giorgio DI NATALE Directeur de thèse

DIRECTEUR DE RECHERCHE, CNRS

Alberto BOSIO Rapporteur

PROFESSEUR DES UNIVERSITES, École centrale de Lyon

Jean-Michel PORTAL Rapporteur

PROFESSEUR DES UNIVERSITES, IM2NP, Aix-Marseille Université

Marie-lise FLOTTES Examinatrice

CHARGEE DE RECHERCHE, CNRS

Vincent BEROULLE Président

PROFESSEUR DES UNIVERSITES, Grenoble INP - Esisar, UGA

#### Invités:

Arnaud VIRAZEL

PROFESSEUR DES UNIVERSITES, Université de Montpellier / LIRMM

**Bastien GIRAUD**

SCIENTIST, Commissariat à l'énergie atomique et aux énergies alternatives

To all those who have enabled my personal growth, encouraged me to strive for betterment, and provided me with unwavering support.

Pietro

# Contents

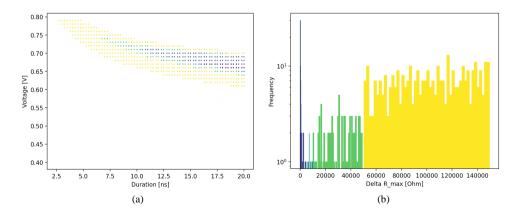

| Su | Summary xiii<br>Sommaire xv |           |                                           |      |  |

|----|-----------------------------|-----------|-------------------------------------------|------|--|

| So |                             |           |                                           |      |  |

| 1  | Intr                        | roduction |                                           |      |  |

|    | 1.1                         | Backg     | round & Context                           | . 1  |  |

|    |                             | 1.1.1     | Computer Architecture                     | . 5  |  |

|    |                             | 1.1.2     | Computer Memory Technologies              | . 5  |  |

|    |                             | 1.1.3     | Computing in Memory                       | . 15 |  |

|    |                             | 1.1.4     | Hardware Security                         | . 20 |  |

|    | 1.2                         | Thesis    | contributions                             | . 25 |  |

| 2  | Log                         | ic In M   | emory (LIM)                               | 27   |  |

|    | 2.1                         | Memri     | istor                                     | . 27 |  |

|    | 2.2                         | LIM So    | olutions                                  | . 30 |  |

|    |                             | 2.2.1     | LIM Array Stateful Logic                  | . 34 |  |

|    |                             | 2.2.2     | LIM Array + Periphery, Stateful Logic     | . 39 |  |

|    |                             | 2.2.3     | LIM Array + Periphery, Non Stateful Logic | . 41 |  |

|    | 2.3                         | State o   | of the art solutions and comparison       | . 41 |  |

| 3  | Sim                         | ulation   | n Environment                             | 47   |  |

|    | 3.1                         | VTEA      | M                                         | . 48 |  |

|    | 3.2                         | LIM In    | nstruction Set                            | . 50 |  |

|    |                             | 3.2.1     | Code examples                             | . 52 |  |

|    |                             | 3.2.2     | Supported operations                      | . 54 |  |

iv Contents

|   | 3.3  | State C  | Observer                                                    | 58  |

|---|------|----------|-------------------------------------------------------------|-----|

|   | 3.4  | Param    | etric Sweep using Cadence Virtuoso                          | 62  |

|   | 3.5  | Results  | s extraction and plots                                      | 62  |

|   | 3.6  | Final f  | ramework and capabilities                                   | 65  |

| 4 | Elec | trical S | Simulation of Boolean Operations with Ideal Memristive Ele- |     |

|   | men  |          | •                                                           | 67  |

|   | 4.1  | Motiva   | ation                                                       | 68  |

|   | 4.2  | Simula   | ation environment and preliminary analysis                  | 71  |

|   | 4.3  | Introd   | uction of <i>non-ideal values</i> and thresholds            | 73  |

|   | 4.4  | Conca    | tenation of operations                                      | 75  |

|   |      | 4.4.1    | MAGIC-based XOR                                             | 77  |

|   |      | 4.4.2    | FELIX-based XOR                                             | 78  |

|   |      | 4.4.3    | IMPLY-based XOR                                             | 79  |

|   | 4.5  | Param    | etric Sweep                                                 | 81  |

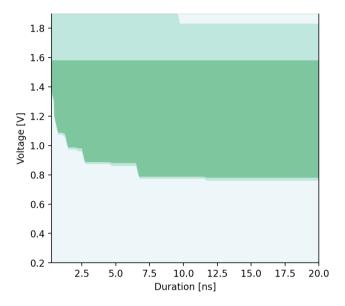

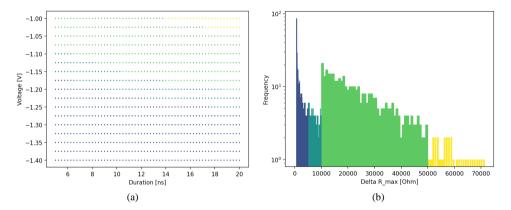

|   |      | 4.5.1    | MAGIC NOT and NOR                                           | 82  |

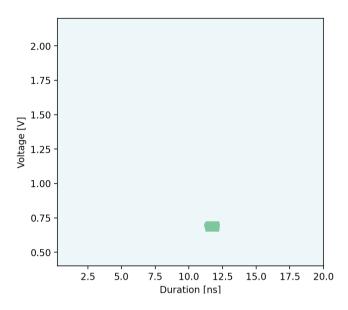

|   |      | 4.5.2    | FELIX NAND                                                  | 84  |

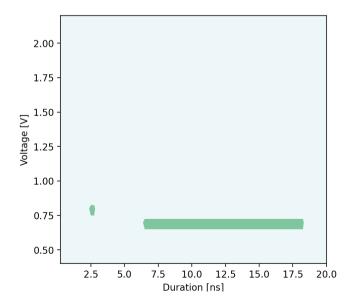

|   |      | 4.5.3    | FELIX OR                                                    | 85  |

|   |      | 4.5.4    | FELIX XOR                                                   | 86  |

|   |      | 4.5.5    | IMPLY                                                       | 88  |

|   | 4.6  | Conclu   | ısion                                                       | 89  |

| 5 | Elec | trical / | Analysis of Boolean Operations with Non-Ideal Memristive    |     |

| • |      | nents    |                                                             | 91  |

|   | 5.1  | Simula   | ation environment and preliminary analysis                  | 93  |

|   | 5.2  |          | etric Sweep                                                 | 98  |

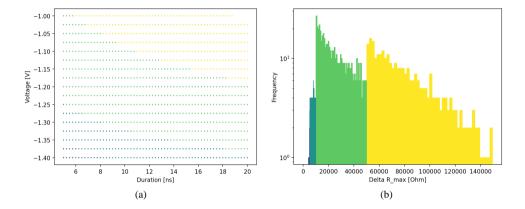

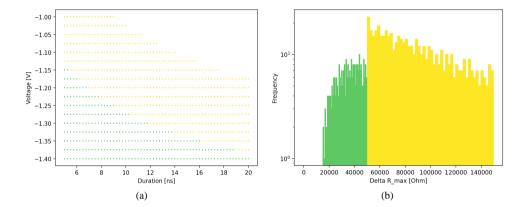

|   |      | 5.2.1    | MAGIC NOT and NOR                                           | 100 |

|   |      | 5.2.2    | FELIX NAND                                                  | 104 |

|   |      | 5.2.3    | FELIX OR                                                    |     |

|   |      | 5.2.4    | FELIX XOR                                                   |     |

|   |      | 5.2.5    | IMPLY                                                       |     |

Contents

|     | 5.3     | Discus     | ssion and Conclusion                   | . 114 |

|-----|---------|------------|----------------------------------------|-------|

|     |         | 5.3.1      | Comparison among XOR implementations   | . 114 |

|     |         | 5.3.2      | Conclusion                             | . 115 |

| 6   | Secu    | ırity As   | spects of LIM Solutions                | 117   |

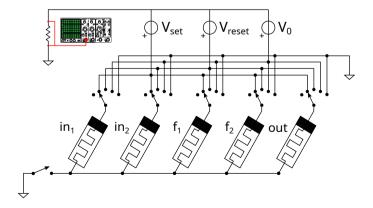

|     | 6.1     | MAGI       | C-based XOR                            | . 118 |

|     | 6.2     | Side C     | Channel Attacks on MAGIC-based XOR     | . 120 |

|     |         | 6.2.1      | Current consumption of MAGIC-based XOR | . 121 |

|     |         | 6.2.2      | DPA on MAGIC-based XOR                 | . 122 |

|     | 6.3     | Fault A    | Analysis on MAGIC-based XOR            | . 124 |

|     |         | 6.3.1      | Fault Analysis of MAGIC-based XOR      | . 124 |

|     | 6.4     | Conclu     | usion                                  | . 127 |

| 7   | Con     | cludin     | g Remarks and Future Directions        | 129   |

| Lis | st of l | Publica    | ations                                 | 133   |

| Pa  | rticip  | pation i   | in Local and International Activities  | 135   |

| Bi  | bliog   | raphy      |                                        | 137   |

| Gl  | ossar   | · <b>y</b> |                                        | 160   |

# List of Figures

| 1.1  | IRDS - 40 years of Microprocessor Trend Data. From [1]                    | 2   |

|------|---------------------------------------------------------------------------|-----|

| 1.2  | Fundamental components in a computer                                      | 5   |

| 1.3  | Computer Memory types                                                     | 7   |

| 1.4  | A six-transistor (6T) Complementary Metal-Oxide-Semiconductor Field-      |     |

|      | Effect Transistor (CMOS) Static Random-Access Memory (SRAM) cell. From [2 | 2]. |

| 1.5  | Dynamic Random-Access Memory (DRAM) cell                                  | 10  |

| 1.6  | RRAM cell                                                                 | 12  |

| 1.7  | Schematic of the switching mechanism of conductive bridge RRAM            | 13  |

| 1.8  | PCM cell                                                                  | 14  |

| 1.9  | STT-MRAM cell                                                             | 16  |

| 1.10 | Memory array and memory cells                                             | 17  |

| 1.11 | Computing in Memory categories scheme.                                    | 18  |

| 1.12 | Generic memory scheme                                                     | 21  |

| 1.13 | Classical Computing vs LIM types                                          | 22  |

| 2.1  | Memristor's symbol and convention. From [3]                               | 29  |

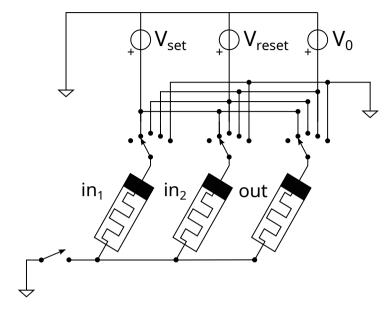

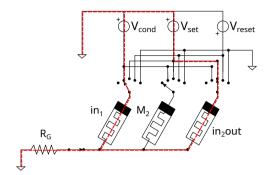

| 3.1  | Basic netlist for operations with up to 3 memristors                      | 52  |

| 3.2  | NOP operation on a 3-memristor circuit.                                   | 54  |

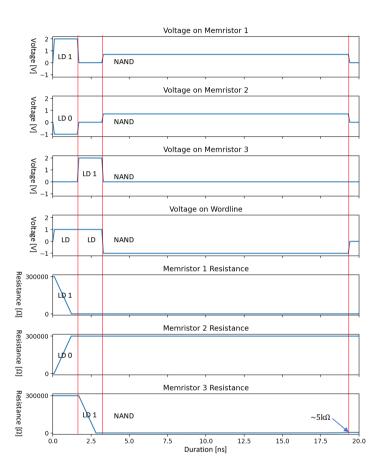

| 3.3  | MAGIC NOT operation on a 3-memristor circuit                              | 55  |

| 3.4  | MAGIC NOR and FELIX NAND operations on a 3-memristor circuit              | 55  |

| 3.5  | FELIX OR operation on a 3-memristor circuit.                              | 56  |

| 3.6  | FELIX XOR operation on a 3-memristor circuit.                             | 57  |

viii List of Figures

| 3.7  | IMPLY operation on a 3-memristor circuit. $V_{SET}$ and $V_{COND}$ are in the             |    |

|------|-------------------------------------------------------------------------------------------|----|

|      | opposite direction to the previous cases because the IMPLY gates has the                  |    |

|      | memristors in the opposite direction to the other solutions                               | 58 |

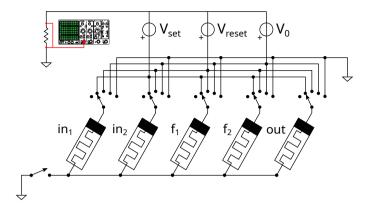

| 3.8  | State Observer (on the right top corner), represented by an oscilloscope                  |    |

|      | connected to a 5-memristor netlist.                                                       | 59 |

| 3.9  | Schema showing the possible input choices for the plots                                   | 65 |

| 4.1  | Waveform of a FELIX NAND operation not reaching the nominal resistive                     |    |

|      | state                                                                                     | 70 |

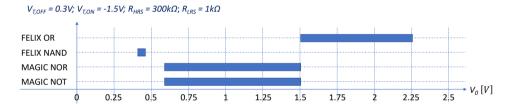

| 4.2  | Theoretical ranges of the control voltages $\mathcal{V}_0$ that allow a correct operation |    |

|      | for MAGIC NOT and NOR, and FELIX NAND and OR operations                                   | 71 |

| 4.3  | Results of the preliminary simulation of the NOR Operation                                | 72 |

| 4.4  | Results of the preliminary simulation of the NAND operation with non-                     |    |

|      | ideal Low Resistive State (LRS)=1.3 $k\Omega$ and non-ideal High Resistive State          |    |

|      | (HRS)=290 k $\Omega$                                                                      | 74 |

| 4.5  | Results of the preliminary simulation of the NAND operation with non-                     |    |

|      | ideal LRS=50 $k\Omega$ and non-ideal HRS=150 $k\Omega.$                                   | 74 |

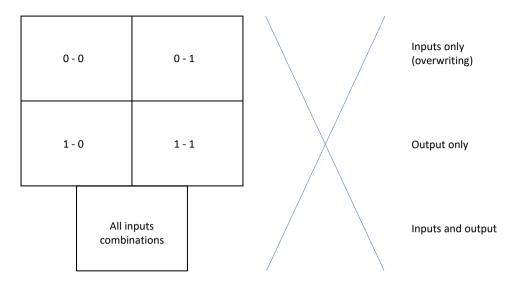

| 4.6  | Key for the plots.                                                                        | 82 |

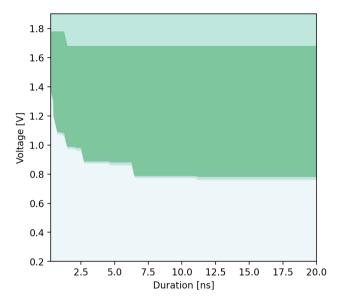

| 4.7  | Results of the simulation of the MAGIC NOT operation                                      | 83 |

| 4.8  | Results of the simulation of the MAGIC NOR operation                                      | 83 |

| 4.9  | Results of the simulation of the FELIX NAND operation                                     | 84 |

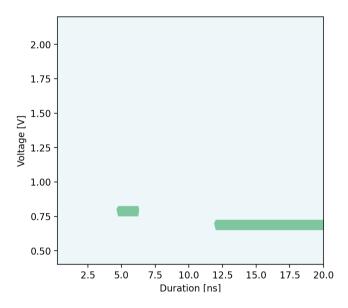

| 4.10 | Results of the simulation of the FELIX OR operation                                       | 85 |

| 4.11 | Results of the simulation of the FELIX XOR operation                                      | 87 |

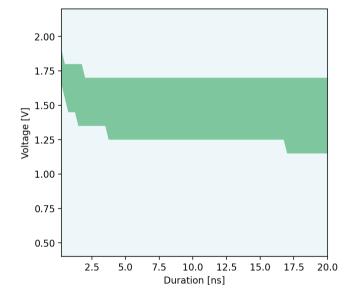

| 4.12 | Results of the simulation of the IMPLY operation                                          | 88 |

| 5.1  | Waveform of a FELIX NAND operation not reaching the nominal resistive                     |    |

|      | state                                                                                     | 94 |

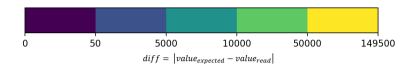

| 5.2  | Results of the preliminary simulation of the NOR operation with non-ideal                 |    |

|      | state inputs (1225 $\Omega,~297.5k\Omega)$ and with non-ideal LRS=1.3 $k\Omega$ and non-  |    |

|      | ideal HRS=290 k $\Omega$                                                                  | 95 |

List of Figures ix

| 5.3  | Results of the preliminary simulation of the NAND operation with non-                                         |     |

|------|---------------------------------------------------------------------------------------------------------------|-----|

|      | ideal state inputs (1225 $\Omega,~297.5k\Omega)$ and with non-ideal LRS=1.3 $k\Omega$ and                     |     |

|      | non-ideal HRS=290 k $\Omega.$                                                                                 | 96  |

| 5.4  | Results of the preliminary simulation of the NOR operation with non-ideal                                     |     |

|      | state inputs (5 $k\Omega,300k\Omega)$ and with non-ideal LRS=50 $k\Omega$ and non-ideal                       |     |

|      | HRS=150 k $\Omega$                                                                                            | 96  |

| 5.5  | Results of the preliminary simulation of the NAND operation with non-                                         |     |

|      | ideal state inputs (5 k $\!\Omega\!$ , 300 k $\!\Omega\!$ ) and with non-ideal LRS=10 k $\!\Omega\!$ and non- |     |

|      | ideal HRS=290 k $\Omega$                                                                                      | 97  |

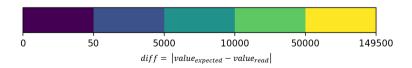

| 5.6  | Key for the plots                                                                                             | 99  |

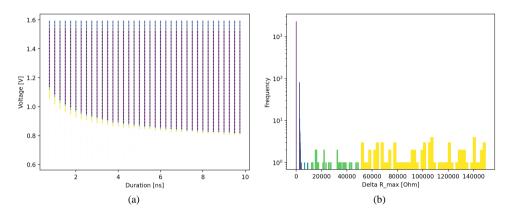

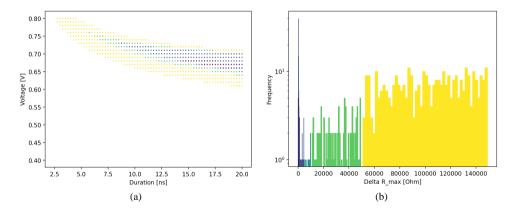

| 5.7  | Results of the simulation of the MAGIC NOT operation with non-ideal                                           |     |

|      | input values (HRS = 299.5 k $\Omega$ , LRS = 1025 $\Omega$ )                                                  | 100 |

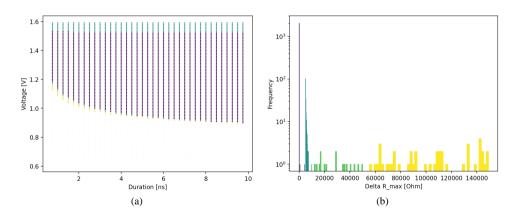

| 5.8  | Results of the simulation of the MAGIC NOR operation with non-ideal                                           |     |

|      | input values (HRS = 299.5 k $\Omega$ , LRS = 1025 $\Omega$ )                                                  | 101 |

| 5.9  | Results of the simulation of the MAGIC NOT operation with non-ideal                                           |     |

|      | input values (HRS = 297.5 k $\Omega$ , LRS = 1225 $\Omega$ )                                                  | 101 |

| 5.10 | Results of the simulation of the MAGIC NOR operation with non-ideal                                           |     |

|      | input values (HRS = 297.5 k $\Omega$ , LRS = 1225 $\Omega$ )                                                  | 102 |

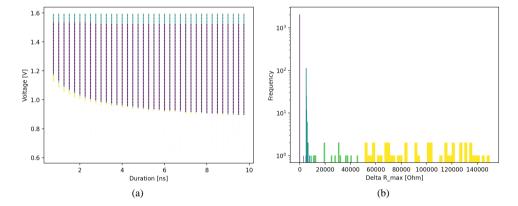

| 5.11 | Results of the simulation of the MAGIC NOT operation with non-ideal                                           |     |

|      | input values (HRS = 295 k $\Omega$ , LRS = 1500 $\Omega$ )                                                    | 102 |

| 5.12 | Results of the simulation of the MAGIC NOR operation with non-ideal                                           |     |

|      | input values (HRS = 295 k $\Omega$ , LRS = 1500 $\Omega$ )                                                    | 103 |

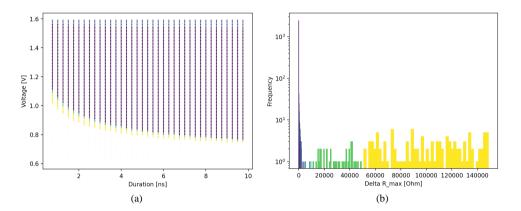

| 5.13 | Results of the simulation of the FELIX NAND operation with non-ideal                                          |     |

|      | input values (HRS = 299.5 k $\Omega$ , LRS = 1025 $\Omega$ )                                                  | 104 |

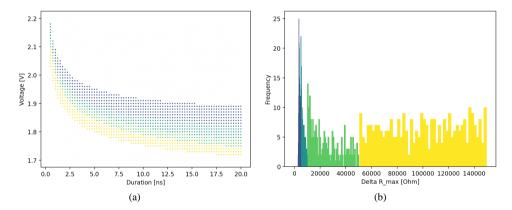

| 5.14 | Results of the simulation of the FELIX NAND operation                                                         | 105 |

| 5.15 | Results of the simulation of the FELIX NAND operation                                                         | 105 |

| 5.16 | Results of the simulation of the FELIX OR operation with non-ideal input                                      |     |

|      | values (HRS = $299.5 \text{ k}\Omega$ , LRS = $1025 \Omega$ )                                                 | 106 |

| 5.17 | Results of the simulation of the FELIX OR operation with non-ideal input                                      |     |

|      | values (HRS = $297.5 \text{ k}\Omega$ , LRS = $1225 \Omega$ )                                                 | 107 |

x List of Figures

| 5.18 | Results of the simulation of the FELIX OR operation with non-ideal input   |

|------|----------------------------------------------------------------------------|

|      | values (HRS = $295 \text{ k}\Omega$ , LRS = $1500 \Omega$ )                |

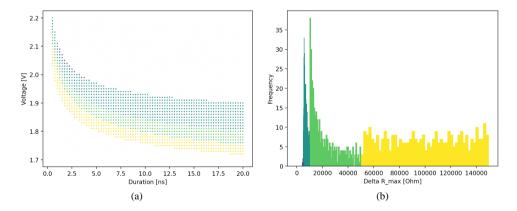

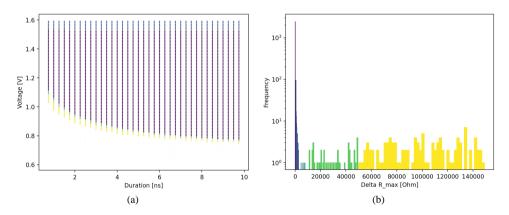

| 5.19 | Results of the simulation of the FELIX XOR operation with non-ideal input  |

|      | values (HRS = 299.5 k $\Omega$ , LRS = 1025 $\Omega$ )                     |

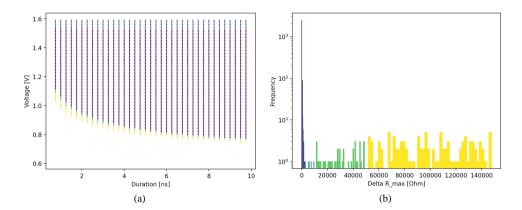

| 5.20 | Results of the simulation of the FELIX XOR operation with non-ideal input  |

|      | values (HRS = 297.5 k $\Omega$ , LRS = 1225 $\Omega$ )                     |

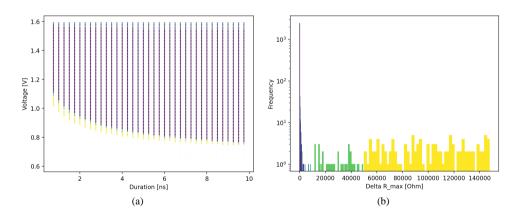

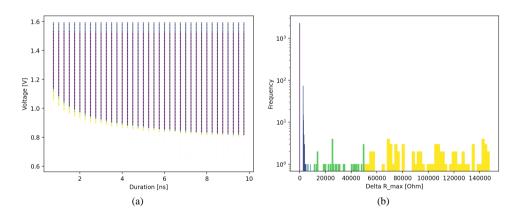

| 5.21 | Results of the simulation of the FELIX XOR operation with non-ideal input  |

|      | values (HRS = 295 k $\Omega$ , LRS = 1500 $\Omega$ )                       |

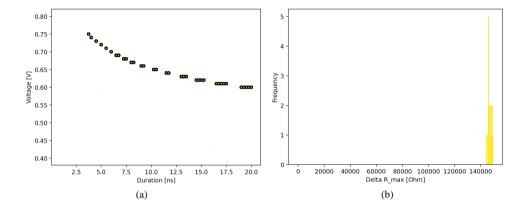

| 5.22 | Results of the simulation of the IMPLY operation with non-ideal input val- |

|      | ues (HRS = 299.5 k $\Omega$ , LRS = 1025 $\Omega$ )                        |

| 5.23 | Results of the simulation of the IMPLY operation with non-ideal input val- |

|      | ues (HRS = 297.5 k $\Omega$ , LRS = 1225 $\Omega$ )                        |

| 5.24 | Results of the simulation of the IMPLY operation with non-ideal input val- |

|      | ues (HRS = 295 kΩ, LRS = 1500 Ω)                                           |

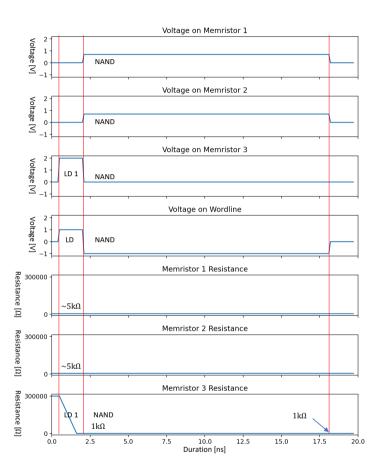

| 6.1  | MAGIC-based XOR netlist                                                    |

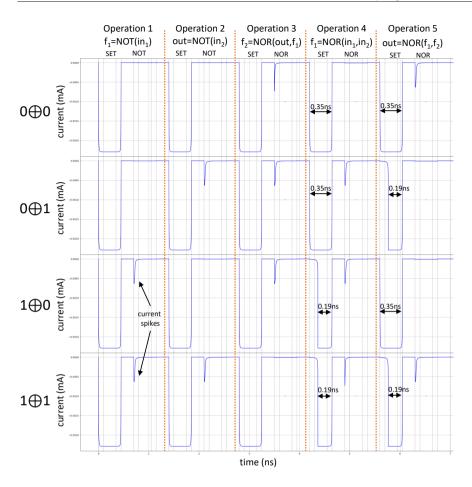

| 6.2  | MAGIC-based XOR current curves                                             |

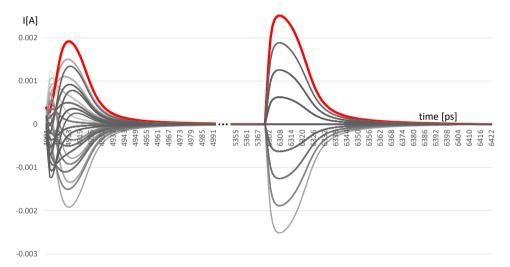

| 6.3  | DPA result on eight 2-bit XOR operations                                   |

# List of Tables

| 2.1  | Logic-In-Memory (LIM) Primitive logic gates.                             | 31 |

|------|--------------------------------------------------------------------------|----|

| 2.2  | LIM implementations overview                                             | 32 |

| 2.3  | MAGIC NOT basic steps                                                    | 35 |

| 2.4  | MAGIC NOR basic steps                                                    | 35 |

| 2.5  | FELIX NAND basic steps                                                   | 37 |

| 2.6  | FELIX OR basic steps                                                     | 37 |

| 2.7  | FELIX XOR basic steps                                                    | 37 |

| 2.8  | IMPLY basic steps                                                        | 38 |

| 2.9  | ORNOR3 basic steps.                                                      | 39 |

| 2.10 | Number of memristors and number of operations per Boolean function       | 43 |

| 2.11 | Mapping of all considered Boolean functions on LIM primitive operations. | 45 |

| 3.1  | VTEAM model parameters                                                   | 49 |

| 4.1  | MAGIC-based AND basic steps.                                             | 75 |

| 4.2  | FELIX-based AND basic steps                                              | 76 |

| 4.3  | IMPLY-based AND basic steps                                              | 76 |

| 4.4  | RMAJ-based AND basic steps.                                              | 77 |

| 4.5  | MAGIC-based XOR steps                                                    | 77 |

| 4.6  | MAGIC-based XOR steps and values. Under the steps are the resulting      |    |

|      | values of each operation.                                                | 78 |

| 4.7  | FELIX-based XOR steps                                                    | 78 |

| 4.8  | FELIX-based XOR steps and values.                                        | 79 |

| 4.9  | IMPLY-based XOR steps.                                                   | 79 |

| 4.10 | IMPLY-based XOR steps - unfolded version                                 | 80 |

xii List of Tables

| 5.1 | Table showing the operation time, the possible input ranges and the chosen    |

|-----|-------------------------------------------------------------------------------|

|     | inputs for the analysed operations                                            |

| 6.1 | MAGIC-based XOR steps and values. Under the steps are the resulting           |

|     | values of each operation                                                      |

| 6.2 | MAGIC NOT and NOR behaviour for control voltages affected by external         |

|     | perturbations                                                                 |

| 63  | Results of the attack on the XOR gate for the 3 proposed attack scenarios 126 |

# Summary

Computation in Memory (CIM) is a groundbreaking concept that involves performing computations directly within the memory itself, eliminating the need to transfer data back and forth between the memory and Central Processing Unit (CPU). This approach deviates from the traditional Von Neumann architecture, aiming to overcome its limitations and bottlenecks, ultimately driving technological advancement.

Various CIM solutions leverage existing memory technologies, capitalising on physical attributes, organisation, peripheral components, and control logic of the memory. These paradigms enable logic and arithmetic operations within the memory, significantly reducing latency and energy consumption by eliminating data transfers to the CPU. Furthermore, they pave the way for enhanced parallelism through dense arrays of memory elements that support computation.

The thesis explores the potential of memristive-based memories to redefine the integration of logic and memory. The research delves into different LIM implementations, analysing their advantages and disadvantages, with a particular focus on security considerations.

The primary objective is to efficiently synthesise a range of Boolean operations within the LIM framework, from basic 2-bit operations to the Full Adder. Simultaneously, the thesis introduces a Simulation and Analysis environment to support parallel simulations and parametric sweep. The research work compares various LIM technologies in terms of memory resource requirements and the number of operations needed to implement fundamental Boolean functions. These preliminary findings highlight the potential of memristive-based LIM technologies, but they also emphasise the importance of the respect of electrical characteristics and operation times.

To gain a deeper understanding of LIM solutions, we developed a toolkit to easily analyse electrical behaviour, generate netlist inputs, run Cadence simulations, and collect simula-

xiv Summary

tion data. Thanks to this automatic tool, we revealed some weaknesses of certain solutions, particularly concerning deviations in output memristor resistance from ideal values. The research explored therefore operations under non-ideal conditions, focusing on the role of input memristor resistance in determining correct operation ranges. It highlights the potential for incorrect results when chaining operations, especially from non-ideal inputs, prompting the consideration of refresh cycles for stability.

The thesis finally explored security properties of such LIM solutions, by looking at side-channel and fault analyses. The study revealed several vulnerabilities, mainly due to the large resistive difference between Low Resistive State (LRS) and High Resistive State (HRS), and the lack of robustness when operations are performed under non-ideal conditions. In summary, the research explores the exciting possibilities of memristive-based LIM, offering insights into their potential, but also showing their limits and vulnerabilities.

# Sommaire

Le calcul en mémoire est un concept révolutionnaire qui consiste à effectuer des calculs directement dans la mémoire elle-même, éliminant ainsi la nécessité de transférer des données entre la mémoire et l'unité centrale. Cette approche s'écarte de l'architecture Von Neumann traditionnelle et vise à en surmonter les limites et les goulets d'étranglement, pour finalement favoriser le progrès technologique.

Diverses solutions de calcul en mémoire exploitent les technologies de mémoire existantes, en capitalisant sur les attributs physiques, l'organisation, les composants périphériques et la logique de contrôle de la mémoire. Ces paradigmes permettent d'effectuer des opérations logiques et arithmétiques au sein de la mémoire, ce qui réduit considérablement la latence et la consommation d'énergie en éliminant les transferts de données vers l'unité centrale de traitement. En outre, ils ouvrent la voie à un parallélisme accru grâce à des réseaux denses d'éléments de mémoire qui prennent en charge le calcul.

La thèse explore le potentiel des mémoires à base de memristors pour redéfinir l'intégration de la logique et de la mémoire. La recherche plonge dans différentes implémentations de Logique en Mémoire (LIM), analysant leurs avantages et leurs inconvénients, en mettant particulièrement l'accent sur les aspects de sécurité.

L'objectif principal est de synthétiser efficacement une gamme d'opérations booléennes. Parallèlement, la thèse introduit un environnement de simulation et d'analyse pour permettre les simulations parallèles et les balayages paramétriques. Le travail de recherche compare diverses technologies LIM en termes de besoins en ressources mémoire et du nombre d'opérations nécessaires pour mettre en œuvre des fonctions booléennes fondamentales. Ces résultats préliminaires mettent en lumière le potentiel des technologies LIM à base de memristors, tout en soulignant l'importance du respect des caractéristiques électriques et des temps d'opération.

xvi Sommaire

Pour mieux comprendre les solutions LIM, nous avons développé une boîte à outils permettant d'analyser facilement le comportement électrique, de générer des entrées de netlist, d'exécuter des simulations Cadence et de recueillir des données de simulation. Grâce à cet outil automatisé, nous avons révélé certaines faiblesses de certaines solutions, en particulier en ce qui concerne les écarts de résistance des memristors par rapport aux valeurs idéales.

La recherche a donc exploré les opérations dans des conditions non idéales, en mettant l'accent sur le rôle de la valeur de la résistance initiale du memristor dans la détermination des plages d'opération correctes. Elle met en évidence le risque d'obtenir des résultats incorrects lors de l'enchainement d'opérations, en particulier à partir de valeurs initiaux non idéaux des memristors, ce qui incite à envisager des cycles de rafraîchissement pour la stabilité des opérations.

Finalement, la thèse a exploré les propriétés de sécurité de ces solutions LIM, en examinant les analyses des canaux auxiliaires et des attaques en fautes. L'étude a révélé plusieurs vulnérabilités, principalement dues à la grande différence de résistance entre les états de faible résistance (LRS) et les états de haute résistance (HRS), ainsi qu'au manque de robustesse lorsque les opérations sont effectuées dans des conditions non idéales.

En résumé, la recherche explore les possibilités de la technologie LIM à base de memristors, en offrant des perspectives sur leur potentiel, tout en montrant également leurs limites et leurs vulnérabilités.

1

# Introduction

# 1.1 Background & Context

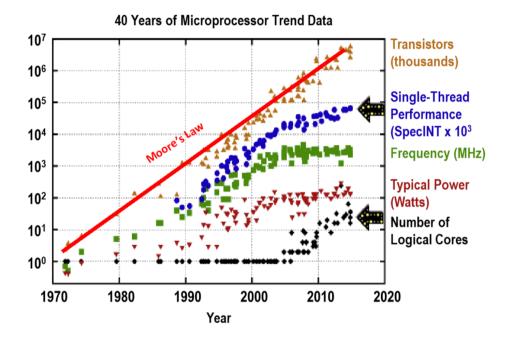

The progress in the semiconductor industry has stimulated numerous innovations and improvements in all of its domains, from devices to computing paradigms. The evolution of transistors has been described by Gordon Moore, the co-founder of Intel and Fairchild Semiconductors, stating in 1965 that the number of transistors on a microchip doubles about every year (occupying the same area); hence, the cost of microchip is halved [4]. According to Moore, this operating principle and, at the same time, commitment, should have gone on for at least ten years. Ten years later, in 1975, Moore revised the forecast to grow double every almost two years [5]. Over time, this simple prediction became a law, taking the name of its inventor: Moore's law. This law has become a guideline for the semiconductors industry to trace a path for the evolution of computers.

In 1974, Robert H. Dennard at IBM stated the so-called Dennard scaling [6], where, as the size of Metal-Oxide-Semiconductor Field-Effect Transistor (MOS) transistors shrinks, the power density remains constant, and therefore the power consumption will remain proportional with the area. Furthermore, according to Dennard, each new process generation

2 1 Introduction

would lead to a 0.7x reduction of the Metal-Oxide-Semiconductor Field-Effect Transistor (MOSFET) gate length and width, the power supply voltage, and the gate oxide. The end of Dennard scaling arrived in 2003 when the introduction of multi-core processors guaranteed the continuity of Moore's law. Presently, CMOS technology is close to its physical limits and, therefore, it is harder to scale down the size and improve the performance: we are witnessing the end of Moore law [7].

Figure 1.1: IRDS - 40 years of Microprocessor Trend Data. From [1].

In parallel to the MOSFETs, computer architectures evolved as well: since the appearance of modern computers, the widely adopted computing architecture has been based on the separation between the computing unit (or processor) and the memory, i.e., the Von Neumann architecture [8]. This architecture implies that a single bus is connecting the processor and the memory, meaning that the memory is accessed at least twice for every instruction (fetch of the instruction, read/write of data). This problem is known as the Von Neumann bottleneck [9].

The first solution that has been adopted to address the Von Neumann bottleneck is the

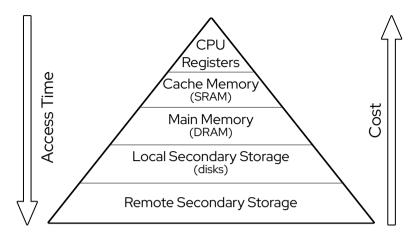

Harvard architecture [10], where program and data are stored on separate memories that are connected to the processor by two separate buses. However, this solution has limited efficiency, as in modern computers, the separation between processor and memory has become an issue due to the uneven evolution of processing speed and memory access times (also known as the memory wall) [11, 12]. This inability of the memory to match the speed of processors has been an issue since the early '70s and has first been addressed with the introduction of the cache memory [13]: a faster memory used to store a subset of the main memory content. The partitioning of the memory content between the cache (fast and high cost) and main memory (slower and cheaper) is the best approach to guarantee high performance and low cost.

However, with technological advancements, the memory wall continued to be an increasingly important issue. This has led to the introduction of various levels of cache to compensate for the speed disparity while maintaining low cost. The movement of data becomes ubiquitous in CPU operations, where parts of data are moved from memory to processor, processed, and finally sent back. This data movement is currently costlier in terms of power than the computation itself, e.g., a DRAM access consumes 200 times more energy than a floating point operation [14].

Another important issue regarding the power efficiency is related to static power. Today, the main memories are implemented in DRAM (compact and cheap), while caches are implemented in SRAM (fast and expensive). These are both volatile memories, i.e., in order to retain information, they need to be connected to a power supply, thus consuming energy even when the memory is not accessed. In fact, for small technology nodes (below 32 nm), static power consumption has become dominant over dynamic power consumption. These power efficiency issues are known as the power wall [15]. A solution to the static power problem could be to change the technology adopted and switch to the use of Non-Volatile Memories (NVMs), which will significantly reduce the static power consumption since the stored data are kept even in the absence of a power supply. However, traditional flash memories are too slow to replace the DRAM as the main memory or the SRAM as the cache memory. In this context, research has been conducted on different materials and devices to identify NVM solutions with speed matching the requirements of

the main memory or even low levels of cache. Among the best candidates, there are the socalled emerging memories, which include Resistive Random Access Memory (RRAM) [16], Phase Change Memory (PCM) [17], Spin-Transfer Torque Magnetic Random Access Memory (STT-MRAM)) [18] and Ferroelectric Field-Effect Transistor (FeFET) [19]. These are all resistive-based memories, i.e., the information is stored as a resistance value and not as a charge value, as is the case for conventional CMOS memories. The NVMs, already tackling issues such as power consumption, also showed interesting physical capabilities. Indeed, changing from charge-based (as SRAM or DRAM) to resistive-based memories enables new scenarios where the physical capabilities of the memory can be exploited to perform logic or arithmetic operations directly inside the memory array, therefore bypassing the memory wall via the CIM paradigm. Emerging memory technologies, along with new computation paradigms, can in fact provide a convenient way to mitigate the limitations of traditional memories: moving the computation inside the memory tackles both the memory and the power wall. In fact, having the possibility to perform operations directly inside the memory means being able to avoid the data movement to and from the CPU, saving time and energy. Among the existing CIM solutions, the ones based on memristors are of particular interest, since these are the only devices, up to now, which offer the possibility to perform computation and store the result within the memory array without any need for external manipulation of data. In addition, the memristor (used for RRAMs) has the advantage of having a very simple structure, being compatible with the CMOS process, having low area occupancy and theoretical high switching speed, and being non-volatile. Depending on the target application, two main CIM approaches exist: (i) analog-CIM mostly developed for accelerating Multiply-Accumulate (MAC) operations, and (ii) digital-CIM mostly used for performing Boolean operations. The focus of this thesis is on digital-CIM, more precisely on LIM.

The remainder of the chapter is organised as the following: an overview of the basic computer architecture is presented, followed by a foreword to the main memory technologies, and an introduction on the different types of CIM solutions. Finally, we introduce hardware security aspects.

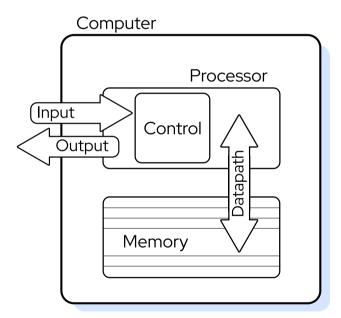

## 1.1.1 Computer Architecture

The fundamental components of a computer architecture (see figure 1.2) are the CPU, memory, and Input/Output (I/O). The system's main component, the processor (CPU), is in charge of executing instructions. Data and processor instructions are stored in memory. I/O is in charge of transferring data from between the processor and external devices like a printer or a keyboard. Additional parts of a computer system are the bus, which connects the other parts of the architecture, and the instruction pipeline, which tracks the instructions that the processor is following. The CPU is responsible for executing instructions and managing the operations of the system. For our scope, the most interesting part of the computer architecture is the memory.

Figure 1.2: Fundamental components in a computer.

# 1.1.2 Computer Memory Technologies

This section presents the memory, its types, and their usage. It is followed by a brief overview of the various memory technologies and how CIM can be enabled with them. The goal is to highlight the differences and capabilities of the possible implementations,

6 1 Introduction

showing the issues and the limitations of each memory. There are several types of memory present inside a computer:

- · CPU registers,

- Read Only Memory (ROM),

- Cache memory,

- Primary / Main memory,

- Secondary memory / Mass storage.

The CPU registers are high-speed memories built in the processor to enable the fastest data access. These are groups of flip-flops (latch-type circuit with two stable states, representing logic 1 and 0) [20]. ROM, or permanent memory, is a non-volatile memory. It is non-modifiable and it is used to perform the Power On Self Test (POST): the diagnostic test done at the computer start-up. Finally, secondary memory, also known as external memory, it is a memory that is not directly connected to the CPU and that can often be attached and connected as the user wishes. Common types of secondary memories are Optical Drive memories (CD-ROM, CD-RROM, DVD, etc.), Magnetic storage memories (Hard Disk Drive (HDD), magnetic tape, floppy disk) and Solid-State Drive memories (Universal Serial Bus (USB) memory memory stick or USB flash drive).

In the following, there is a more detailed explanation of certain of the above-mentioned memories.

#### **ROM**

ROM (Read Only Memory), or permanent memory is a non-volatile memory that cannot be modified by the user. It is where the operating instructions of the system are stored. The data that is stored inside these memories, as the name says, can only be read. It uses fuses that can be set to store a certain piece of data. Therefore, the data are binary-formatted. It is primarily used to store the Basic Input-Output System (BIOS) and other firmware that are essential for a system to start and function properly. It is typically found in the BIOS chip of a motherboard, which contains the instructions that the computer needs to boot up. ROM memories can be divided into more types, introduced in the next paragraphs.

1

Figure 1.3: Computer Memory types.

**PROM** Programmable Read-Only Memory (PROM) is a type of ROM that starts without written data on it. It can be written and, therefore, used by means of a PROM programmer. It is only programmable once, and it is typically used to create firmware for a chip.

**EPROM** Erasable Programmable Read-Only Memory (EPROM) is a type of ROM chip that can be written onto (as the PROM), but it can as well be erased and therefore reprogrammed. The erase operation is done by means of Ultraviolet (UV) light exposing it on a quartz crystal window at the top of the chip. The erase operation slightly damages the memory, so there is a limited amount of erase and write operations, and it has to be manually done, making it a time consuming operation.

**EEPROM** Electrically Erasable Programmable Read-Only Memory (EEPROM) is a type of ROM chip whose goal is substituting the PROM and EPROM chips. It is also erasable, but this time the erasing process is done by means of an electric field: it is quicker and it does not damage the memory. In fact, the chip does not need to be removed from the memory, whereas EPROM chips need to be removed from the computer to be erased.

#### **RAM**

Random-Access Memory (RAM) is a vital component of modern computing systems, serving as the primary means of temporary data storage and retrieval. It is a type of volatile

memory, meaning that its contents are lost when power is removed from the system.

There are two main types of classic RAM: dynamic RAM (DRAM) and static RAM (SRAM). DRAM is the most widely used type of RAM and is characterised by its ability to be repeatedly written and read. It is also relatively inexpensive compared to SRAM. On the other hand, SRAM is a type of RAM that is faster than DRAM and is primarily used in high-performance systems such as servers and high-end computers.

SRAM is a type of memory that uses a combination of transistors and capacitors to store data. On the other hand, DRAM is a type of memory that uses a capacitor to store data. Unlike SRAM, DRAM needs to be refreshed periodically to retain data, which means that it depends on a supply voltage and that it can preserve information without being refreshed only for a short period of time. This makes DRAM less reliable than SRAM, as it is more susceptible to data loss in the event of a power outage or other failure.

Other RAM types have been studied and developed, to improve performance and reduce costs, and these memories are called Emerging Memories, as introduced.

Among them are RRAM [16], PCM [17], and STT-MRAM) [18].

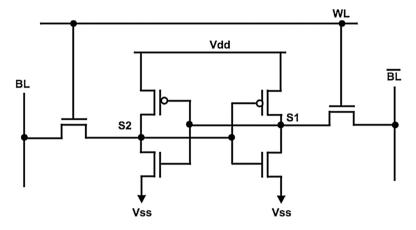

SRAM SRAM is a bistable circuit that exploits two crossed-coupled inverters to retain an electric charge that represents the stored value. This value will be kept until the opposite value is written in the same cell. The circuit of a 6T SRAM is shown in figure 1.10. It uses two access transistors that allow access to the cell to ensure data retention and perform read and write operations. The SRAM cell is big: its size is more than  $60 F^2$ . As a consequence, the cost of SRAM is high. When the size of the transistors is reduced, the yield drops, and therefore the faster the cell, the more expensive its fabrication is. The read and write access time of an SRAM cell is less than 3 ns. Being a volatile memory, data is retained until the power is on. On the other hand, there is the static power consumption to take into account. The endurance is greater than  $10^{15}$  cycles. SRAM does not need to be refreshed, which means that it can retain data indefinitely as long as power is supplied. This makes SRAM faster and more reliable than DRAM, as it does not suffer from the same performance degradation over time. Another advantage of SRAM is its low power consumption. Because SRAM does not need to be refreshed, it uses less power than DRAM, making it a popular choice for mobile devices such as laptops and smartphones.

Figure 1.4: A six-transistor (6T) CMOS SRAM cell. From [2].

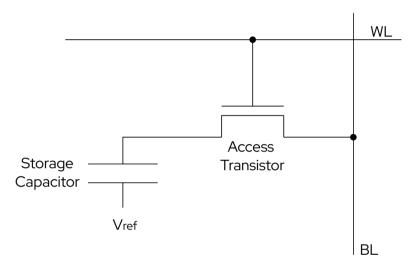

**DRAM** DRAM retains the charge thanks to a capacitor whose access is managed through a transistor, as shown in figure 1.10. The capacitor charge represents the value stored in the memory. Although the dimensions of the DRAM circuit are smaller than the SRAM, the access time is higher than the SRAM's, and it suffers of leak currents because of the capacitor, requiring then the value in the memory to be often refreshed (around 50 times per second). The consequence is a slower access time.

The read and write access time of a DRAM cell is between 7 and 20 ns. Being a volatile memory, the data is retained until the power is on. On the other hand, there is the static power consumption to take into account. The endurance is higher than  $10^{15}$  cycles. The cell size is between 4 and 6  $F^2$ .

Despite its drawbacks, DRAM is still the most widely used type of memory in modern computing systems. One of the main reasons for this is its low cost. DRAM is much cheaper to produce than SRAM, which makes it a more cost-effective option for many applications.

Another advantage of DRAM is its high storage capacity. Because DRAM uses a capacitor to store data, it can store more data in a smaller area than SRAM. This makes DRAM a popular choice for use in main memory, where high storage capacity is more important than speed.

In summary, SRAM and DRAM are both RAM types that are used for temporary data

1

1 Introduction

storage and retrieval. SRAM is faster and more reliable than DRAM, but it is also more expensive and has lower storage capacity. DRAM is slower and less reliable than SRAM, but is also cheaper and has larger storage capacity. The choice of SRAM or DRAM will depend on the specific needs and requirements of the application. High-performance computing applications such as servers and supercomputers will typically use SRAM, while lower-performance applications such as desktops and laptops will use DRAM.

Figure 1.5: DRAM cell.

#### **NVRAM**

In the ever-evolving landscape of data storage technologies, the demand for higher capacities, faster access times, and improved energy efficiency has been a driving force behind innovative solutions. Non-Volatile Random-Access Memory (NVRAM) [21] has emerged as a promising class of memory technology that combines the benefits of non-volatility, byte-addressability, and low-latency read/write operations. With the potential to revolutionise data storage and computing systems, NVRAM holds great promise for enabling next-generation persistent memory architectures. NVRAM provides the ability to retain information even in the absence of power. This non-volatility makes NVRAM a desirable option for a wide range of applications, including data centres, enterprise storage, embedded systems, and mobile devices. By bridging the gap between storage and memory,

NVRAM has the potential to overcome the limitations of existing technologies and open up new avenues for data-centric computing.

NVRAM encompasses a variety of memory technologies, each with its own unique characteristics and underlying principles.

Phase Change Memory (PCM): it uses the reversible phase transition of chalcogenide materials between the amorphous and crystalline states. This technology offers fast read and write access times, high endurance, and scalability, making it a promising candidate for future memory systems.

Magnetic Random-Access Memory (MRAM): it uses the magnetic properties of ferromagnetic materials to store data. It offers non-volatility, high endurance, low power consumption, and fast read and write speeds. MRAM has gained significant attention due to its potential for integration with existing complementary metal-oxide-semiconductor (CMOS) processes.

Resistive Random-Access Memory (RRAM): also known as resistive switching memory, it relies on the reversible modulation of resistance in thin film structures. It offers fast switching speeds, low power consumption, and high endurance.

Ferroelectric Random-Access Memory (FeRAM): it utilises ferroelectric materials to store data as polarisation states. It offers non-volatility, low power consumption, fast write speeds, and high endurance. FeRAM holds promise for applications that require frequent data updates and low-latency access.

The emergence of these new NVRAM paradigms presents interesting opportunities to advance the field of persistent data storage. By combining the advantages of non-volatility, byte-addressability, and low-latency access, NVRAM has the potential to redefine memory hierarchies, blur the lines between storage and memory, and fundamentally transform the way data are stored, processed, and retrieved.

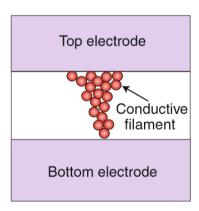

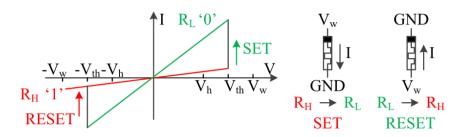

**RRAM** The RRAM element is a variable resistance, whose value represents the bit logic value. It is a 3-layer device, made of two metal electrodes with a dielectric in between. The dielectric is used to conduct by means of a conduction path formed applying a sufficiently high voltage. This is made possible during the fabrication phase, where defects are introduced in a controlled way in the dielectric. There are unipolar and bipolar RRAM:

the unipolar switches depending on the amplitude of the voltage applied on the memory, while the bipolar takes into account the voltage polarity as well. The switching, i.e., the change of resistance, takes place with the creation or rupture of conductive filaments inside the dielectric. There are also non-filamentary RRAM devices that exploit different physical systems, like charge trapping and de-trapping and redistribution of oxygen vacancies. Possible operations are set (from HRS to LRS, from logic 0 to logic 1) or reset (from LRS to HRS, from logic 1 to logic 0), which are done, respectively, by forming or breaking the conductive path. A small voltage bias is applied to the cell for reading its data, i.e., to check the resistive state, to then compare the current with a Sense Amplifier (SA). The read and write access time of an RRAM cell is less than 10 ns, with a data retention time greater than 10 years. The endurance is about  $10^{12}$  cycles. The write energy, expressed in Joules per bit, is 0.1 pJ

The RRAM can be implemented via a memristive crossbar. RRAM has garnered interest for its compatibility with CMOS processes and potential for high-density storage.

Resistance range =  $10^3$ – $10^7$ Access time (write) = 10ns – 100ns Endurance =  $10^6$ – $10^9$

Figure 1.6: An RRAM device at LRS where the Conductive Filament (CF) comprises a large concentration of defects for example oxygen vacancies in metal oxides or metallic ions injected from the electrodes. By the application of appropriate voltage pulses, the defects can be migrated back to the top electrode thus disconnecting the CF and reaching a HRS. From [22].

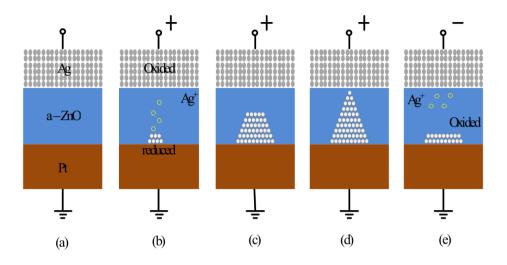

Figure 1.7: Schematic of the switching mechanism of conductive bridge RRAM. a) Pristine state of the RRAM device. b,c) Oxidation of Ag and migration of Ag\* cations towards cathode and their reduction. d) Accumulation of Ag atoms and Pt electrode leads to growth of highly conductive filament. e) Filament dissolution takes place on applying voltage of opposite polarity. From [16, 23].

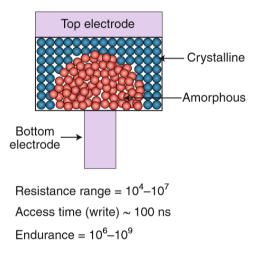

PCM The Phase Change Memory (PCM) [17, 24–26] device is, as the RRAM, a variable resistance, and its resistance represents the logic value. It utilises the reversible phase transition of chalcogenide materials between amorphous and crystalline states. It is made by the phase change material, encapsulated inside two electrodes, as shown in figure 1.10. To access the device, a transistor is usually implemented. Phase Change memories exploit materials, typically compounds of Ge, Sb and Te, that can reversibly switch from amorphous and crystalline phases, both having different resistance values. The high resistive state (logic 0) is achieved having the amorphous phase of the memory, while the low resistive state (logic 1) is present during the crystalline phase. The difference between the two states can be up to three or four orders of magnitude. This technology offers fast read and write access times, high endurance, and scalability, making it a promising candidate for future memory systems.

The set and reset operations are performed by applying current pulses through the device. As a consequence, the device heats up. The reset happens once the current pulse that makes the material melt, is stopped abruptly, since it causes the molten material to go

14 1 Introduction

into the amorphous phase. The melting temperature is around 600 °C. The set occurs, being the device in amorphous phase, applying a current pulse. This causes the crystallisation of a part of the amorphous region. The crystallisation temperature corresponding the the highest crystallisation rate is  $\approx 400$  °C. Applying current pulses to a PCM device results in significant heating due to Joule heating. The read happens similarly to the RRAM, applying a small voltage that does not change the inner status of the memory and sensing its current.

The read access time of a Phase Change RAM (PCRAM) cell is less than 10 ns and the write access is 50 ns. The data retention time is higher than 10 years. The endurance is about  $10^8$  cycles. The write energy, expressed in Joules per bit, is  $10 \, \text{pJ}$

Figure 1.8: A mushroom-type PCM device at HRS where the amorphous phase blocks the bottom electrode. To create this state, a RESET pulse is applied that can melt a significant portion of the phase change material. When the pulse is stopped abruptly, the molten material quenches into the amorphous phase due to glass transition. When a current pulse of lesser amplitude is applied to the PCM device at HRS, a part of the amorphous region crystallises. By fully crystallising the phase change material, the LRS is obtained. From [22].

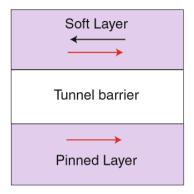

**MRAM** The MRAM data storage element is a variable resistance. The Magnetic Tunnelling Junction (MTJ) device is a tunnelling oxide barrier sandwiched in two ferromagnetic layers. One ferromagnetic layer has a fixed magnetic orientation, while the other has free magnetic rotation (free layer).

The conductance, and therefore the logic value, depend on the magnetisation of the layers:

Parallel orientation is the High Conductance State, logic 0, while the Anti-parallel orientation is the Low Conductance State, corresponding to the logic 1. This is the opposite convention with respect to the one used in RRAM and PCM.

To reverse the magnetic orientation (perform write operations), the thermally activated magnetic is used: at finite temperature, there is a finite probability for the magnetisation reverse its direction (Néel-Brown theory). This is also a reliability risk: there is a chance of spontaneous state reversal.

Among the different types of MRAM devices, STT-MRAM is widely used. It exploits a spin-polarised current to flip the magnetisation direction of a ferromagnetic layer. When a current passes through the fixed layer, it becomes spin polarised. Then, passing through the oxide and entering the free layer, it changes the orientation of the polarity of the latter. Writing a logic 0, a current flows from the fixed to the free layer, making the transition from anti-parallel to parallel happen. Writing a logic 1, the current has to flow on the other direction, i.e., from the free to the fixed layer, resulting in a transition from parallel to anti-parallel relative magnetisation.

The read and write access time of a STT-MRAM cell is less than 10 ns. The data retention time is higher than 10 years. The endurance is about  $10^{16}$  cycles. The write energy, expressed in Joules per bit, is  $0.1\,\mathrm{pJ}$

# 1.1.3 Computing in Memory

CIM, as the name suggests, refers to the capability of performing computation directly inside the memory, without therefore resorting to the CPU to have the results and then to write them back to the memory. It represents a non-Von Neumann approach, since it allows to compute in the memory itself. The main idea is to avoid moving data into a processing unit and to therefore break the memory wall. To tackle the issues and bottlenecks we have introduced, a wide variety of solutions exists which are based on existing memory technologies, all of them relying on the physical attributes of the memory, its organisation, its periphery and the control logic. These paradigms enable logic and/or arithmetic operations directly inside the memory boundaries. The operations are indeed performed without the need of transferring data to and from the CPU, thus reducing latency and en-

16 1 Introduction

1

Resistance range =  $10^3$ – $10^4$ Access time (write) < 10 ns Endurance >  $10^{14}$

Figure 1.9: An STT-MRAM device with two ferromagnetic layers (pinned and free) separated by a tunnel oxide layer. The magnetic polarisation of the free layer can be changed upon writing. Depending on whether the ferromagnetic polarisations are parallel or anti-parallel, the device assumes a low or high resistance, respectively. The transition to the parallel state takes place directly through conduction electrons, which are previously spin-polarised by the pinned layer. Subsequently, the magnetic polarisation of the free layer is rotated using magnetic momentum conservation. To switch to the anti-parallel state, an opposite voltage, and hence current direction, is employed. From [22].

ergy consumption. Moreover, it lays the foundations for heavily increasing parallelism by having dense arrays of memory elements enabling computation.

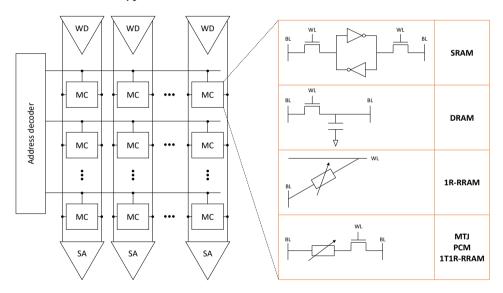

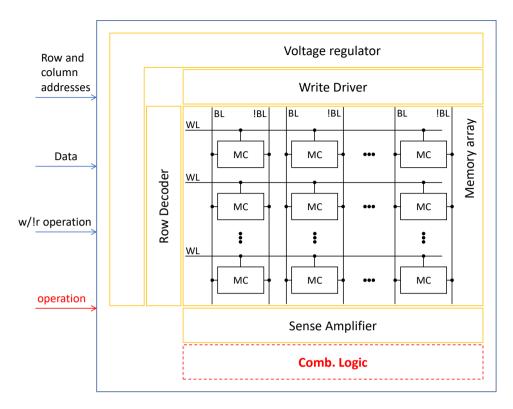

Generically, they exploit the physical characteristics of the memory and the insertion of control and, if needed, computational elements in the peripheral logic (e.g., Write Driver (WD) and SA). In fact, the various implementations can be more or less invasive for the architecture and for the memory array: there are CIM solutions that work with any kind of memory, volatile or non-volatile, or that work just with non-volatile memories.

The state of the art is mainly divided on levels of abstraction: (i) device level – to identify the optimum material combination to achieve the desired device behaviour; (ii) circuit level – to design logic gates, a.k.a., LIM [27–31], vector-matrix multiplications [32–34], neuromorphic computing synapse and/or neurons [35–37]; (iii) system level – to map applications on memory arrays, parallelise computations, design accelerators [38]. De-

pending on the solution, CIM can be enabled on different memory technologies: among them, there are the conventional non-volatile and emerging non-volatile memories.

The basic memory array is formed of rows and columns (2-D array) that are independently controlled with memory cells (bit cells) in the cross-points. A simplified view can be seen in figure 1.10. The bit cells contain the information associated to 1 bit of data and the memory cells are connected by means of Wordlines (WLs) and Bitlines (BLs). The bit cells can be connected together in various ways (also depending on the technology used), i.e., there are different types of memory arrays that handle how to access and use the bit cells. The most used types are the 1T1R and the crossbar.

Figure 1.10: Memory array and memory cells.

A generic memory architecture can be described as shown in figure 1.10. A memory cell is selected by means of address decoders, it is written into by the WD and read from with the help of the SA. The voltage levels required to enable the operations on the memory cell are set by the voltage regulators. One memory array communicates with the processor or other memory arrays by means of bus connections. In order to enable CIM, several changes need to be implemented to the memory array or/and to its peripheral circuitry. In this context, the peripheral circuitry consists of standard memory periphery (SA, WD, Address Decoder (AD), etc.) and any additional logic that might be required.

18 1 Introduction

Moreover, in some cases, additional logic is added to facilitate computation. Several proposals exist in the literature enabling the computation in memory. Some implementations are generic, and can be used with any memory technology, such as several Near Memory Computing implementations [39]; some can be used with modified CMOS technology to have Computation via Look-up Table (LUT), needing a different memory array; and finally a subcategory of CIM implementations [30, 32, 40–47], modifying the memory periphery, allow to "enhance" a standard memory core with computing capabilities. All the previously said implementations need more or less modifications to parts of the memory array or the periphery, while others take advantage of device physics and are only suitable to be implemented in a specific technology, such as emerging memory technologies.

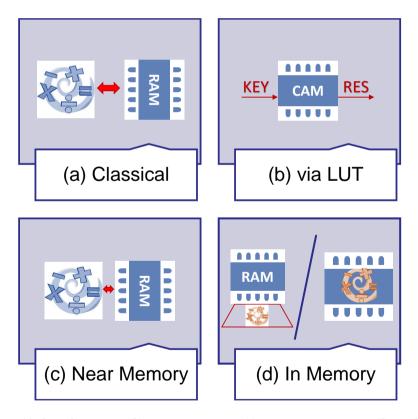

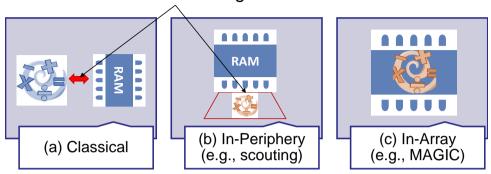

Figure 1.11: (a) Classical Computing, (b) Computation via LUT, (c) Near Memory Computing, (d) CIM (here are illustrated two different paradigms: the one exploiting the periphery and the LIM).

Depending on the way the inputs are stored (the memory content, or an electrical

signal) and where the operations are performed (in the memory array, or in the periphery), the existing solutions can be classified in three main categories:

### • Computation via LUT

A LUT is used to store pre-calculated operations directly in the memory, to avoid moving data to perform operations. This means storing the results of selected operations directly inside the memory, which will be an Application-Specific Integrated Circuit (ASIC). This can be implemented with a CMOS technology. This method can be useful in applications where the same operations are often executed; otherwise, it would be unnecessary and expensive. The state of the art has many scientific articles on this technique and these are the main implementations [48–55].

### • Computation Near Memory

It is often referred to as Processing In Memory (PIM) [56]. The memory core is placed as close as possible to the CPU. It still remains a Von Neumann architecture, but it permits having a shorter bus and therefore decreasing the latency. This can be done by exploiting every main memory technology, but is usually implemented in DRAM technology. The Computation Near Memory reduces the slowdown due to the bus communication speed, but not the speed of the memory itself: the memory wall is therefore not mitigated. The state of the art has many articles and these are the main implementations: [55, 57–63].

### • CIM

CIM enables logic and/or arithmetic operations directly inside the memory boundaries. It allows performing operations without the need of transferring data to/from the CPU, thus saving time and energy. This can be achieved by exploiting the physical characteristics of the memory and/or inserting computational elements into the peripheral logic (SA).

This thesis work is focused on CIM and, more specifically, LIM, since it is the most disruptive and promising solution.

To better explain how a memory can be used to perform CIM operations, in the following are described the operations of a classical memory array and the necessary modifications to make it compatible with CIM.

From the memory array, there are several circuits that enable memory functioning and control.

The WD is in charge of write data on the memory cells, therefore handling the write-1 (SET) and write-0 (RESET) operations at the wanted address. The row and column decoders are used to select the cell corresponding to the wanted address.

The voltage regulator sets the voltages used to carrying out the operations and to assure the correct functioning of the memory. The SAs are used to read the wanted data. Finally, the connection with the external circuitry is allowed by the bus connection, that is composed by the row and column address buses, the data bus and the write/!read bit.

The classical memory needs to be modified to enable CIM, based on the technology used and the implemented features. The circuitries that have to be modified (or added) are:

- WD and voltage regulator, to have different voltages to enable CIM operations.

- Row decoder, to simultaneously activate more than one WD.

- SA, to enable logic operations inside it.

- Bus connection to add the operation bus to enable the control of logical operations.

# 1.1.4 Hardware Security

Hardware security is a vital aspect of computer security that involves protecting hardware components from unauthorised access, tampering, and theft. Hardware security measures are designed to ensure that the hardware devices and systems that we rely on every day are secure and can withstand attacks from hackers and cybercriminals.

It is becoming increasingly important, nowadays being crucial for data security and protection; this led to the evolution of hardware-based cryptography and more prominent threats and hardware attacks.

Depending on the type of computing architecture, the cryptographic operations can differ. In classical architectures (see figure 1.13a), data and cryptographic keys are stored

Figure 1.12: Generic memory scheme.

in the main memory, and they are moved towards the processor to execute the cryptographic functions. Therefore, confidential information will transit unencrypted from the memory to the processor through the communication buses, and it could be susceptible of information leakage. In the context of CIM, the encryption and decryption could be performed without resorting to data transfer, therefore mitigating the risk of data leakage and avoiding exposure to attacks. Nonetheless, not all CIM solutions are equal. The CIM solution which works over all technologies, i.e., the Scouting Logic (figure 1.13b) is based on the activation of multiple rows of the memory array to perform logic computation in specially-designed SAs. The result of the computation (that will be an electrical signal, i.e., the output of the SA) will have to be written back to the memory retaining some vulnerability to data leakage. To completely avoid data manipulation outside the memory array, thus reducing observable information leakage, there are in-array computation solutions

1 Introduction

# Information leakage

Figure 1.13: (a) Classical computing, (b) IMC In-Periphery, (c) IMC In-Array.

(figure 1.13c). These are the focus of this thesis.

Hardware security threats can take many forms, ranging from physical attacks to software-based attacks. Physical attacks on hardware devices involve attempts to damage or tamper with hardware components, such as memory chips, processors, and storage devices. Physical attacks can include methods such as disassembling a device, exposing it to extreme temperatures or electromagnetic radiation, or using brute force to gain access to the device (among them there are the Fault Attacks (FAs), exploiting erroneous behaviour). On the other hand, side-channel attacks are a type of software-based attack that involves analysing the electromagnetic emissions or power consumption of a device to extract sensitive information, such as cryptographic keys.

#### **Side Channel Attacks**

Side Channel Attacks leverage the nuances of physical leakage, exploiting variations in power consumption, electromagnetic emanations, or timing discrepancies to extract sensitive information. Among the Side Channel Attack methodologies there are the Power Analysis Attacks (PAAs), the Electromagnetic Analysis Attacks, Timing Attacks and Acoustic Analysis Attacks.

**PAA** PAAs [64] constitute one of the most well-studied and impactful categories of side channel attacks. These attacks are rooted in the variations in power consumption exhibited

by a device during its operation. By monitoring the power consumption patterns during cryptographic computations, adversaries can discern critical information, such as secret keys. PAAs are further subdivided into Simple Power Analysis (SPA), Differential Power Analysis (DPA), and Higher-Order Differential Power Analysis, each exploiting different aspects of power consumption fluctuations.

SPA is based on the visual examination of graphs of the current used by the device under exam over time. Variations in power consumption (and therefore in the leakage current) occur as the device performs different operations.

DPA covers a spectrum of methodologies, each exploiting different aspects of power consumption leakage to extract cryptographic secrets. These range from Simple Differential Power Analysis (SDPA) to more advanced approaches such as Higher-Order DPA and Template Attacks. Moreover, the use of machine learning algorithms in DPA is often referred to as Machine Learning DPA and represents the intersection between cutting-edge AI techniques and side channel attacks. SDPA is based on the statistical analysis of the power consumption measured from a device. This attack is more resistant to noise that would make SPA impossible to perform.

**Electromagnetic Analysis (EMA)** EMA [65, 66] attacks are based on the electromagnetic emanations produced by computing devices during their operation. These emanations, resulting from variations in current flow, can be captured and analysed to extract sensitive information. EMA attacks encompass both electromagnetic radiation analysis and electromagnetic fault injection, demonstrating the potential for adversaries to manipulate hardware behaviour through controlled electromagnetic interference.

**Timing Attacks** Timing attacks [67] exploit variations in the execution time of cryptographic operations. By meticulously measuring the time it takes a device to perform certain operations, attackers can infer information about the underlying cryptographic computations. Such attacks often exploit subtle timing differences that arise due to conditional branches or memory access patterns.

**Acoustic analysis attacks** Acoustic analysis attacks are a less explored approach and work by analysing the acoustic emissions generated by a computing device during its operation: this can allow adversaries to deduce information about internal computations.

#### **Fault Attacks**

FAs [68–71] are a class of attacks that exploit weaknesses in a system by introducing controlled faults or errors in its operation. The goal of a FA is to cause the system to behave in an unintended way, reveal sensitive information, or breach its security measures. In hardware, FAs can be performed by manipulating the physical environment in which the system operates, such as temperature, voltage, electromagnetic radiation, or clock signals. By doing so, an attacker can cause the system to skip or repeat certain operations, change the values of internal variables, or induce hardware failures that can be used to extract secret information. In software, FAs can be performed by injecting faults into the program execution, for example, by modifying the program code, manipulating its input or output data, or exploiting software vulnerabilities. FAs are commonly used to attack cryptographic systems, where they can be used to bypass encryption or signature verification, recover secret keys, or break authentication protocols. To prevent FAs, hardware and software designers need to implement countermeasures that can detect and recover from errors introduced by the attacker or that can make the system less vulnerable to fault injection.

A Differential Fault Attack (DFA) [72, 73] is a type of FAs that is particularly effective against cryptographic systems. DFA exploits the differential behaviour of a system under normal and faulty conditions to recover secret information. In a DFA, the attacker injects a fault into two or more cryptographic computations and compares the results. By analysing the differences between the faulty and correct outputs, the attacker can obtain information about the internal state of the cryptographic algorithm, such as secret keys or intermediate variables. DFA is a powerful attack because it does not require complete knowledge of the system's internal workings but only differential behaviour under faulty conditions. Additionally, DFA can be performed on a single target without requiring multiple attempts or observations. To defend against DFA, cryptographic systems can employ various countermeasures, such as error-correcting codes, redundancy, and randomisation

of inputs and outputs. Hardware and software designers can also use techniques such as duplication, triplication, and comparison of computations to detect and recover from faults. Additionally, cryptographic algorithms can be designed to be resistant to DFA, such as by avoiding branch operations, using constant-time implementations, or limiting the number of computations per key.

Safe Error Attack (SEA) [74, 75] are a type of FA that targets hardware implementations of cryptographic algorithms. In SEA, an attacker introduces faults into the computation of an Error Correcting Code (ECC) algorithm, causing it to generate a "safe error" that has the effect of reducing the security of the system. The attacker then uses the safe error to recover the private key used by the system. A safe error is a special type of fault that does not cause the system to completely fail or produce incorrect results, but instead introduces a small, intentional error that is difficult to detect. The safe error is designed to bias the internal state of the system in a way that is favourable to the attacker, allowing them to recover the private key more easily. To defend against SEA, hardware designers can use techniques such as error-detection and correction codes, redundancy, and fault tolerance. Additionally, cryptographic algorithms can be designed to be resistant to SEA by avoiding branch operations, using constant-time implementations, or limiting the number of computations per key. Overall, SEA is a relatively new and sophisticated type of fault attack that requires a deep understanding of the internal workings of the cryptographic system. As such, it is important for hardware and software designers to remain vigilant and to implement strong countermeasures to protect against these types of attacks.

# 1.2 Thesis contributions

As introduced, modern computer architectures have important bottlenecks and issues. The first of them is the Von Neumann Bottleneck, together with the memory and power wall. CIM promises to help solving these issues, and together with emerging non-volatile memories, the resulting technologies can tackle, or at least limit the power wall, together with an increased security. The increased security would come from the whole process hap-

pening in the memory instead of resorting to the bus to bring the information back and forth to the CPU, and by having to use the CPU itself to perform the calculation, risking therefore information leakage, hardware trojans and malwares that could sniff and/or observe the data. Therefore, the first choice has been targeting non-volatile memories, with an interested eye on memristive devices. We therefore did a study of the possible CIM implementations, being our goal to choose the most interesting for our use case. Memristive LIM has been the most interesting implementation, for several reasons explained in this manuscript, and we performed several studies on a chosen subset of implementations.

The main thesis contributions are as follows:

- A framework to synthesise Boolean operations on a computing memory array using the state of the art LIM solutions (we show all basic 2-bit operations and the Full Adder) including an efficient and fast method to evaluate the area (number of memristors) and latency (number of cycles and sub-operations needed) of every implementation. This is described in chapter 2.

- Development of a Simulation and Analysis Environment based on an automatic tool

that handles parallel simulations to perform parametric sweeps. This is reported in

chapter 3.

- Electrical-level design and analysis of selected LIM operations assuming ideal memristors. This is presented in chapter 4.

- Electrical-level design and analysis of selected LIM operations assuming non-ideal memristors and the demonstration, for the first time, of the difficulties and limitations of concatenating logic operation in memory. Details are given in chapter 5.

- Demonstration of MAGIC vulnerabilities to side channel and fault attacks. This is detailed in chapter 6.

2

# Logic In Memory (LIM)

This chapter presents an overview of the existing LIM solutions and the technologies enabling them. The chapter starts with a detailed description of the memristive device and its operation. The second part of this chapter presents the state-of-the-art LIM solutions with their descriptions, area and latency evaluation (in terms of required memristors and number of cycles to complete an operation) as well as a comprehensive comparison between them.

#### 2.1 Memristor

In the quest to push the boundaries of electronic memory and computing, researchers have been exploring novel technologies that can overcome the limitations of traditional devices. Among the most promising advancements in this pursuit is the discovery and development of memristors, a fourth fundamental circuit element alongside resistors, capacitors, and inductors. Memristors, short for memory resistors, exhibit unique properties that hold the potential to revolutionise the fields of memory storage and computing systems.

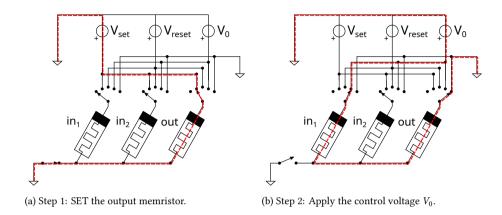

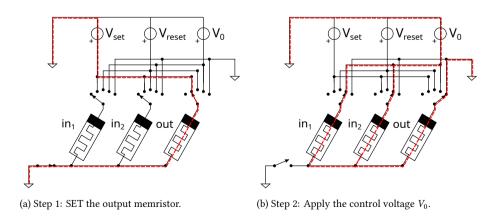

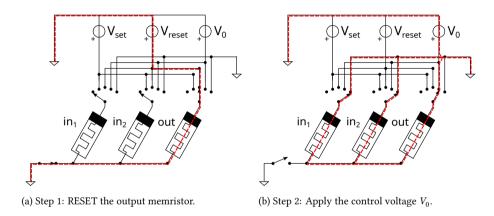

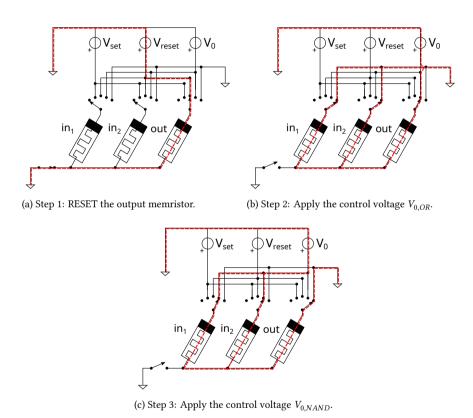

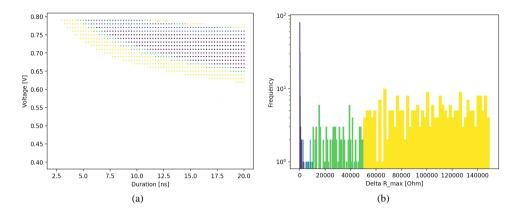

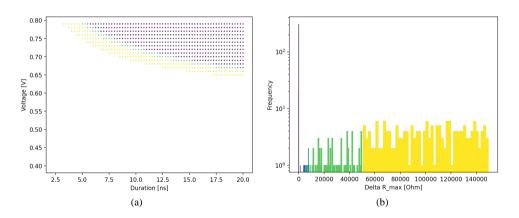

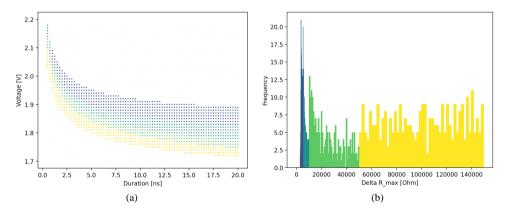

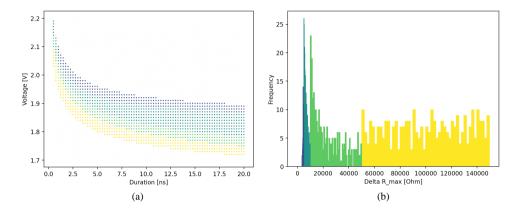

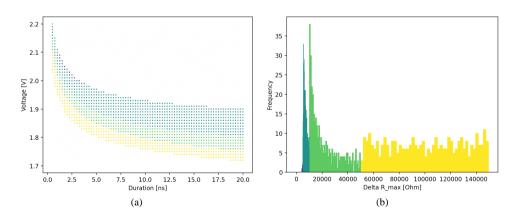

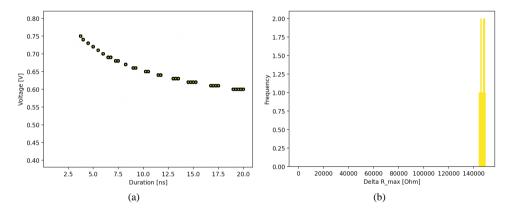

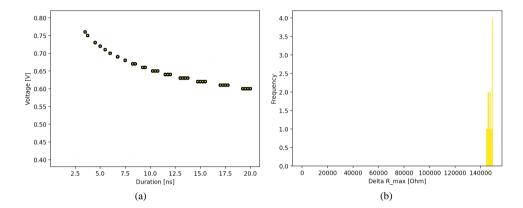

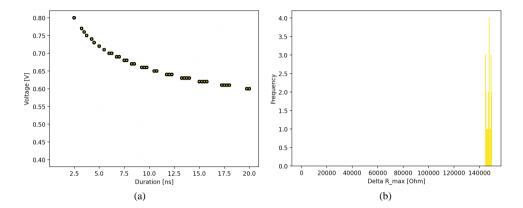

First theorised by Leon Chua in 1971 [76, 77], it wasn't until the early 2000s that mem-