# Circuits intégrés millimétriques en bande Ka pour une antenne à pointage électronique pour les télécommunications avec des satellites géostationnaires ou des constellations de satellites

Elmo Luiz Fechine Sette

### ▶ To cite this version:

Elmo Luiz Fechine Sette. Circuits intégrés millimétriques en bande Ka pour une antenne à pointage électronique pour les télécommunications avec des satellites géostationnaires ou des constellations de satellites. Electronique. Université de Limoges, 2024. Français. NNT: 2024LIMO0002. tel-04540938

# HAL Id: tel-04540938 https://theses.hal.science/tel-04540938v1

Submitted on 10 Apr 2024

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Thèse de doctorat

# Université de Limoges

ED 653 - Sciences et Ingénierie (SI)

Faculté des Sciences et Techniques – Institut de Recherche XLIM

Thèse pour obtenir le grade de

Docteur de l'Université de Limoges

Électronique des Hautes Fréquences, Photonique et Systèmes

Présentée et soutenue par

Elmo Luiz FECHINE SETTE

Le 9 janvier 2024

Circuits intégrés millimétriques en bande Ka pour une antenne à pointage électronique pour les télécommunications avec des satellites géostationnaires ou des constellations de satellites

Thèse dirigée par Bruno BARELAUD et Julien LINTIGNAT

# JURY:

Président du jury

M. Cyrille MENUDIER, Professeur des Universités, Institut XLIM – Univ. de Limoges

#### Rapporteurs

M. Philippe FERRARI, Professeur des Universités, Laboratoire TIMA – Univ. Grenoble Alpes

M. Christian PERSON, Professeur des Universités, LABSTICC, IMT Atlantique

#### Examinateurs

M. Bruno BARELAUD, Professeur des Universités, Institut XLIM – Univ. de Limoges

M. Julien LINTIGNAT, Maître de Conférences, Institut XLIM – Univ. de Limoges

M. Anaël LOHOU, Ingénieur hyperfréquences, Safran Data Systems, La Teste-de-Buch

M. Bernard JARRY, Professeur des Universités, Institut XLIM – Univ. de Limoges

M. Vincent ARMENGAUD, Ingénieur hyperfréquences, CNES, Toulouse

# Invités

M. Christophe MELLE, Responsable Antennes, Safran Data Systems, La Teste-de-Buch

M. François DEBORGIES, Expert Technologie RF, ESA-ESTEC

# A minha família

# Seja sempre humilde e grato **Um sábio**

#### Remerciements

Tout d'abord, je tiens à remercier ma famille pour son soutien inconditionnel, sans lequel je n'aurais certainement pas été en mesure d'achever ce long parcours. *Obrigado família!*

Ensuite, j'adresse mes remerciements à mes encadrants pour ces trois années de thèse. Je tiens à remercier sincèrement mon directeur de thèse, M. Bruno Barelaud, pour le suivi continu de mes études, pour sa patience et sa sagesse qui m'ont beaucoup aidé tout au long de ce travail. Merci, Bruno, pour la confiance que tu m'as toujours accordée depuis le début.

Je tiens également à remercier mon co-directeur de thèse, M. Julien Lintignat, pour son immense savoir qui a été très important pour le bon déroulement de cette thèse. Merci pour toutes les idées qui m'ont encouragé à chercher de nouveaux points de vue pour ce travail.

Je tiens à exprimer ma sincère gratitude à mon tuteur industriel chez *Safran Data Systems*, M. Anaël Lohou, pour son soutien constant sur le plan académique, industriel et personnel. Son expertise et sa sagesse, associées à sa bonne humeur, ont été fondamentales pour que je puisse mener à bien ce travail. Merci d'avoir été un excellent tuteur ainsi qu'un ami.

Je remercie également M. Philippe Ferrari et M. Christian Person d'avoir accepté d'être rapporteurs et pour leurs remarques pertinentes. Merci également à M. Bernard Jarry, M. Vincent Armengaud, M. Cyrille Menudier et M. François Deborgies d'avoir accepté de faire partie du jury de cette thèse et pour l'intérêt que vous avez porté à mon travail.

J'adresse également mes remerciements à mes anciens professeurs, M. Antonio de Souza et M. Emmanuel Dupouy, sans qui je n'aurais certainement pas suivi cette voie de recherche.

Ensuite, je souhaite exprimer ma gratitude envers M. Stéphane Bila, directeur de l'Institut de Recherche XLIM, pour m'avoir accueilli au sein de ce laboratoire. Étant donné que cette thèse découle d'une convention CIFRE, je tiens également à adresser mes remerciements à l'ANRT pour avoir accepté de cofinancer ces travaux, ainsi qu'à M. Jean-Marie Bétermier, directeur de *Safran Data Systems*, pour m'avoir accueilli au sein de cette entreprise.

Je tiens sincèrement à remercier M. Christophe Mellé et M. Alain Karas, chef et ancien chef de service chez *Safran Data Systems*, ainsi que mes collègues Benoît, Charlotte, Fabien, Paul, Alain et Pascal pour l'accueil chaleureux qu'ils m'ont réservé depuis mon arrivée au service RF. Ce sera un réel plaisir pour moi de continuer à travailler avec vous.

Je remercie également l'ensemble du personnel du laboratoire XLIM. En particulier, je remercie Marie-Claude Lerouge, secrétaire de l'équipe C2SNL, pour son efficacité, sa bonne humeur et pour m'avoir aidé même quand je pensais que ce n'était pas vraiment son travail. Je remercie également Damien Passerieux et Clément Hallepee pour leur aide lors des mesures dans le laboratoire XLIM.

Je tiens à remercier mes collègues de bureau pour toutes les discussions, les pauses café et les bons moments passés ensemble. Je tiens particulièrement à remercier Rémy Bouché pour son soutien et son amitié depuis mon arrivée en France. Ce fut un plaisir de travailler avec toi et cela continue d'être un plaisir chaque fois que nous nous rencontrons, mon ami. J'en profite pour remercier tous les doctorants d'XLIM avec qui j'ai partagé de bons moments.

Last but not least, je tiens à remercier tous mes amis brésiliens, dont beaucoup avec qui j'ai tissé des liens d'amitié à Limoges, à Toulouse et dans toute la France, et qui ont contribué d'une manière ou d'une autre à m'aider à arriver là où je suis aujourd'hui. Obrigado amigos !

# **Droits d'auteurs**

Cette création est mise à disposition selon le Contrat :

« Attribution-Pas d'Utilisation Commerciale-Pas de modification 3.0 France » disponible en ligne : http://creativecommons.org/licenses/by-nc-nd/3.0/fr/

# Table des matières

| Table des illustrations                                                 | 15 |

|-------------------------------------------------------------------------|----|

| Table des tableaux                                                      | 21 |

| Liste des sigles et acronymes                                           | 23 |

| Introduction                                                            | 25 |

| Chapitre I. Contexte de l'étude                                         | 29 |

| I.1. Télécommunication par satellite                                    |    |

| I.1.1. Historique : du télégraphe au satellite                          |    |

| I.1.2. Les réseaux satellitaires                                        |    |

| I.2. Antennes à dépointage électronique                                 |    |

| I.2.1. Dépointage électronique : Principe                               |    |

| I.2.2. Architectures pour la formation de faisceau                      |    |

| I.2.3. État de l'art des systèmes existants et en développement         |    |

| I.3. Cadre de la thèse                                                  |    |

| I.3.1. Objectif du projet                                               |    |

| I.3.2. Spécifications du système                                        |    |

| I.3.3. Objectifs de la thèse                                            |    |

| I.4. Choix de la technologie                                            |    |

| I.4.1. Le transistor HBT et la technologie BiCMOS                       |    |

| I.4.2. Les technologies BiCMOS9MW et SG13G2 : un bref aperçu            | 56 |

| I.4.2.1. Niveaux de métallisation (BEOL)                                |    |

| I.4.2.2. Transistor HBT                                                 | 57 |

| I.4.2.3. Transistor MOSFET                                              | 58 |

| I.4.2.4. Résistances                                                    | 58 |

| I.4.2.5. Capacités                                                      | 59 |

| I.4.2.6. Inductances                                                    | 59 |

| I.4.3. Bilan                                                            | 59 |

| Chapitre II. Conception de l'Amplificateur de Puissance à Gain Variable | 63 |

| II.1. Amplificateurs à Gain Variable                                    | 63 |

| II.1.1. Introduction.                                                   |    |

| II.1.2. Paramètres de performance                                       |    |

| II.1.2.1. Puissance de sortie, de saturation et bilan de puissance      |    |

| II.1.2.2. Efficacité énergétique                                        |    |

| II.1.2.3. Gain de puissance                                             |    |

| II.1.2.4. Bande passante et plage de gain dynamique                     |    |

| II.1.2.5. Linéarité                                                     |    |

| II.1.3. État de l'art des VGA en bande Ka                               |    |

| II.2. Conception du VGPA                                                |    |

| II.2.1. Cahier des charges                                              |    |

| II.2.2. Choix de l'architecture                                         |    |

| II.2.3. Conception de l'étage de puissance                              |    |

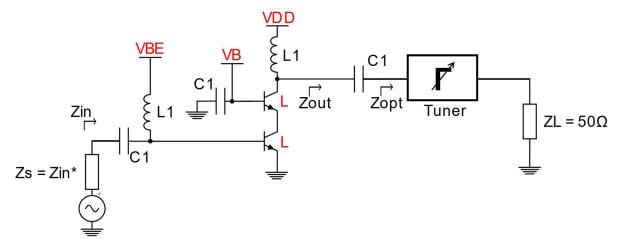

| II.2.3.1. Choix de la topologie                                         | 77 |

| II.2.3.2. Adaptation d'impédance en grand signal                                  | 79  |

|-----------------------------------------------------------------------------------|-----|

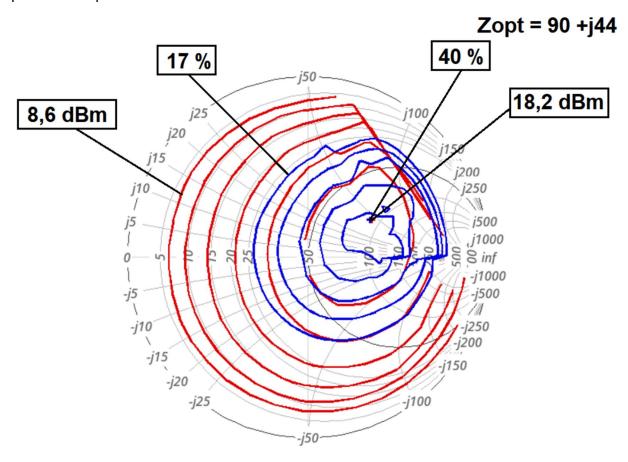

| II.2.3.2.1. Analyse <i>Load-Pull</i>                                              | 79  |

| II.2.3.3. Conception du layout                                                    | 83  |

| II.2.3.3.1. Méthodologie de simulation <i>post layout</i>                         | 83  |

| II.2.3.3.2. Résultats <i>post-layout</i>                                          | 85  |

| II.2.4. Conception de l'étage à gain variable                                     | 86  |

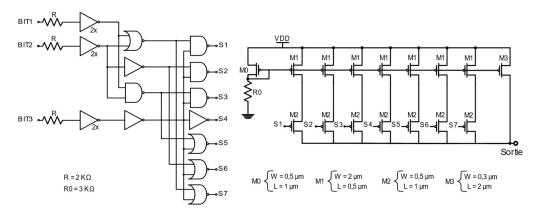

| II.2.4.1. Conception de l'étage de contrôle (Convertisseur Numérique Analogique). |     |

| II.3. Simulations post-layout                                                     |     |

| II.3.1. VGPA complet                                                              |     |

| II.3.2. Comparaison avec le cahier des charges                                    |     |

| II.3.3. Comparaison avec l'état de l'art                                          |     |

| Chapitre III. Conception des déphaseurs                                           | 97  |

| III.1. Déphaseurs en bande Ka                                                     | 97  |

| III.1.1. Introduction                                                             | 97  |

| III.1.2. Types de déphaseur                                                       | 97  |

| III.1.2.1. Ligne à retard et filtres commutées                                    |     |

| III.1.2.2. Ligne à charge variable                                                |     |

| III.1.2.3. Déphaseur en réflexion                                                 |     |

| III.1.2.4. Modulateur Vectoriel                                                   |     |

| III.1.3. Paramètres de performance                                                |     |

| III.1.4. État de l'art des déphaseurs                                             |     |

| III.1.5. Cahier de charges                                                        |     |

| III.1.6. Choix de la topologie et de l'architecture du déphaseur                  |     |

| III.2. Topologie 1                                                                |     |

| III.2.1. Conception A                                                             |     |

| III.2.1.1. Conception du 1 <sup>er</sup> étage : <i>Balun</i>                     |     |

| III.2.1.2. Conception du 2 <sup>eme</sup> étage : Réseaux I/Q                     |     |

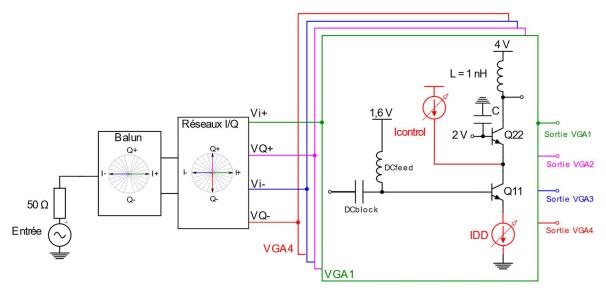

| III.2.1.3. Conception du 3 <sup>eme</sup> étage (4VGA)                            |     |

| III.2.1.4. Circuit et <i>layout</i>                                               |     |

| III.2.1.5. Simulations <i>post-layout</i>                                         |     |

| III.2.1.6. Résultats de mesure                                                    |     |

| III.2.2. Conception B                                                             |     |

| III.2.2.1. Conception du 1 <sup>er</sup> étage : <i>Balun</i>                     |     |

| III.2.2.2. Conception du 2 <sup>eme</sup> étage : Réseaux I/Q                     |     |

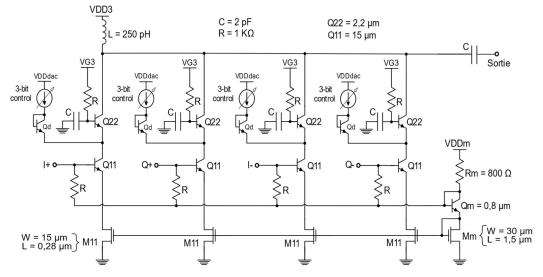

| III.2.2.3. Conception du 3 <sup>eme</sup> étage (4VGA)                            |     |

| III.2.2.4. Circuit et <i>layout</i>                                               |     |

| III.2.2.5. Simulations post-layout                                                |     |

| III.3. Topologie 2                                                                |     |

| III.3.1. Conception C                                                             |     |

| III.3.1.1. Circuit et <i>layout</i>                                               |     |

| III.3.1.2. Simulations post-layout                                                |     |

| III.4. Comparaison et discussion                                                  |     |

| III.4.1. Comparaison entre les conceptions                                        |     |

| III.4.2. Discussion par rapport au cahier des charges                             |     |

| III.4.3. Comparaison avec l'état de l'art                                         |     |

| Conclusion Générale et Perspectives                                               | 147 |

| - 1                                                                               |     |

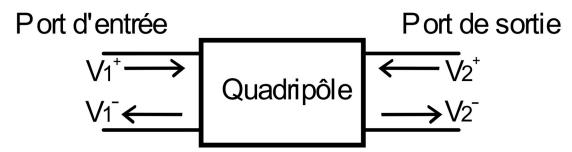

| Annexe I. Paramètres S: The Scattering Parameters    | .153 |

|------------------------------------------------------|------|

| Annexe II. L'abaque de Smith: <i>The Smith chart</i> | .155 |

| Annexe III. Critères d'analyse de stabilité          | .157 |

| Publications                                         | .159 |

| Références bibliographiques                          | .161 |

# Table des illustrations

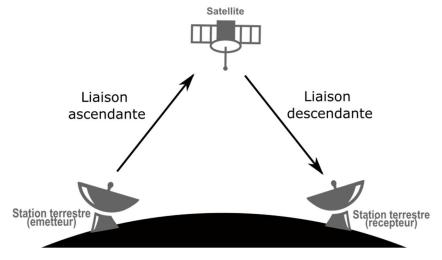

| Figure I.1 : Schéma de liaison satellite conventionnelle                                                                                                                                                                                                            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

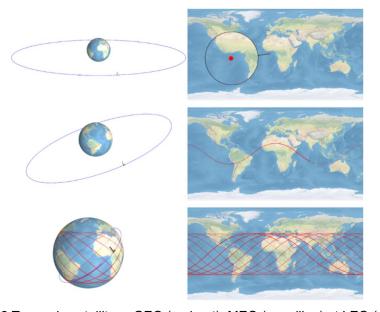

| Figure I.2 Types de satellites : GEO (en haut), MEO (au milieu) et LEO (en bas)31                                                                                                                                                                                   |

| Figure I.3 : Types de satellites et leurs caractéristiques32                                                                                                                                                                                                        |

| Figure I.4 : Antennes à positionneur mécanique                                                                                                                                                                                                                      |

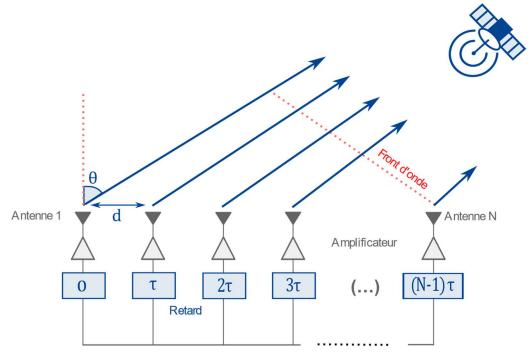

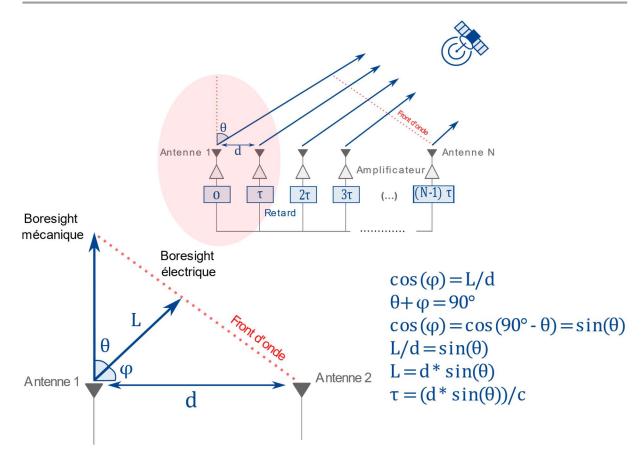

| Figure I.5 : Réseau d'antennes à N éléments avec retard temporel34                                                                                                                                                                                                  |

| Figure I.6 : La dérivation du retard temporel35                                                                                                                                                                                                                     |

| Figure I.7 : Dépointage du faisceau sur deux axes orthogonaux35                                                                                                                                                                                                     |

| Figure I.8 : Réseau d'antennes à N éléments avec décalage de phase36                                                                                                                                                                                                |

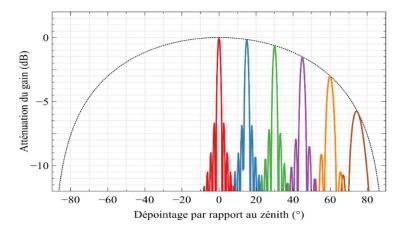

| Figure I.9 : Diagramme de rayonnement normalisé d'un réseau d'antennes de 64 éléments en fonction du dépointage (rouge 0°, bleu 15°, vert 30°, violet 45°, orange 60°, marron 75°) 37                                                                               |

| Figure I.10 : Formation de faisceau analogique (Voie RF)                                                                                                                                                                                                            |

| Figure I.11 : Formation de faisceau analogique (Voie LO)                                                                                                                                                                                                            |

| Figure I.12 : Formation de faisceau voie analogique (Voie IF)39                                                                                                                                                                                                     |

| Figure I.13 : Formation de faisceau numérique40                                                                                                                                                                                                                     |

| Figure I.14 : Formation de faisceau hybride (Voie RF)41                                                                                                                                                                                                             |

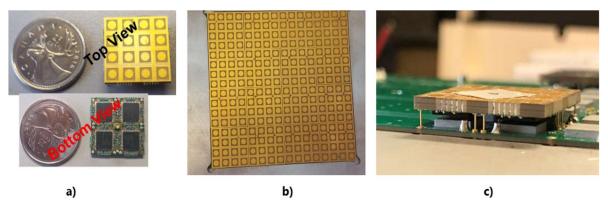

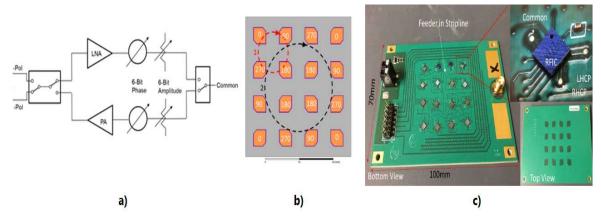

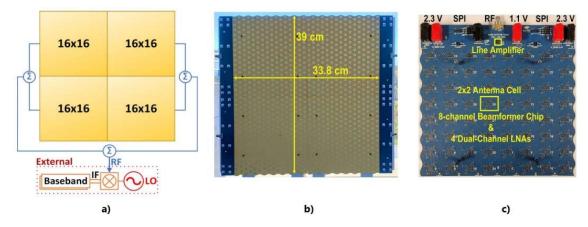

| Figure I.15 : Module de 16 éléments (4x4) pour la bande Ka (30 GHz). Démonstrateur de 256 éléments composé de 16 modules (a) vue de dessus (b) intégration des modules (c) [49]                                                                                     |

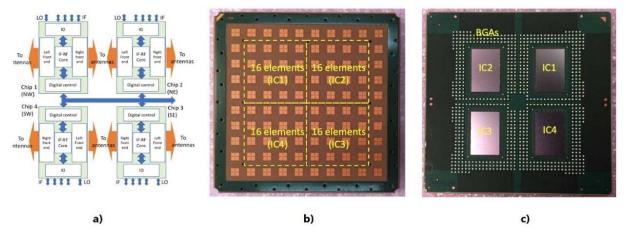

| Figure I.16 Module transcepteur de 64 éléments à 28 GHz. Schémas de signalisation sur le module d'antenne à 4 puces (a). Démonstrateur (b) vue de dessus (c) vue de dessous [50]42                                                                                  |

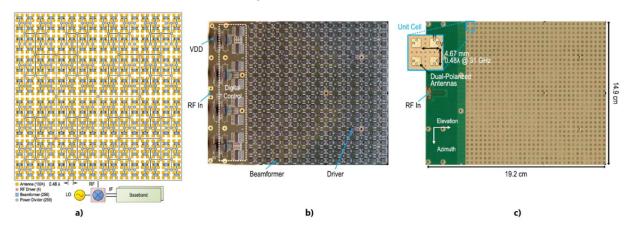

| Figure I.17 : Réseau d'antennes (émetteur) de 1024 éléments à 30 GHz. Architecture (a) vue de dessous (b) et vue de dessus (c) [32]                                                                                                                                 |

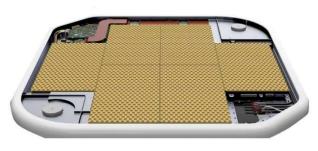

| Figure I.18 : Architecture du RFIC Anokiwave AWMF-0117 (a). Configuration du réseau d'antennes montrant la rotation séquentielle imbriquée appliquée (b). Prototype émetteur-récepteur d'antenne réseaux en bande Ku/Ka (c) [51]44                                  |

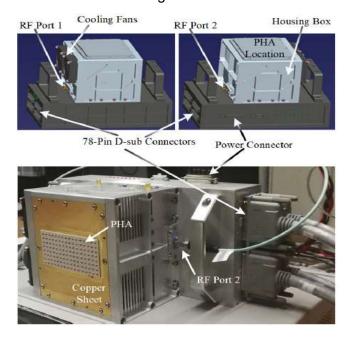

| Figure I.19 : Démonstrateur du système d'antenne hybride à 26 GHz avec 16 × 8 éléments rayonnants [53]44                                                                                                                                                            |

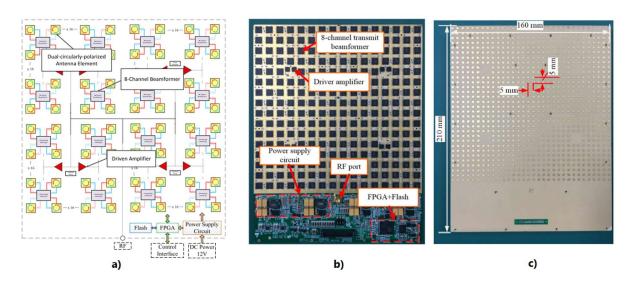

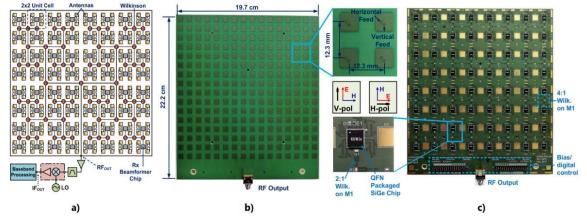

| Figure I.20 : Module émetteur d'antenne réseau de 1024 éléments en bande Ku. Architecture (a) vue réseaux d'antenne (b) et côté composants (c) [54]45                                                                                                               |

| Figure I.21 : Module récepteur d'antenne réseau de 256 éléments en bande Ku (a). Vue de dessus (b) et de dessous (c) du démonstrateur réalisé [33]45                                                                                                                |

| Figure I.22 : Module récepteur à double polarisation pour SATCOM en bande Ku. Système d'antenne avec 1024 éléments, basé sur quatre matrices de 16 x 16 éléments chacune (a). Vue côté réseaux d'antenne (b) et côté composants (c) du démonstrateur réalisé [24]46 |

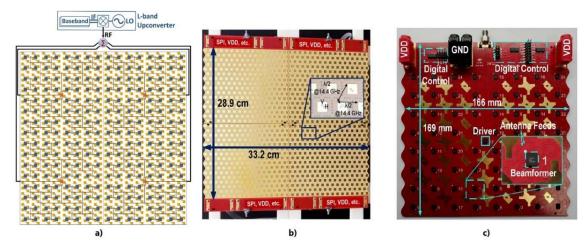

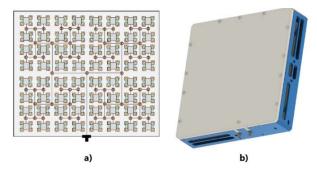

| Figure I.23 : Module émetteur de 256 éléments en bande Ku. Diagramme bloc (a) et46                                                                                                                                                                                  |

| Figure I.24 : Module émetteur de 1024 éléments en bande Ka. Architecture (a) vue côté composants (b) et côté réseaux d'antenne (c) [56] | 47    |

|-----------------------------------------------------------------------------------------------------------------------------------------|-------|

| Figure I.25 : Antennes à dépointage électronique dédiées à la connectivité des terminaux mobiles et aéronautique                        |       |

| Figure I.26 : Cadre de la thèse                                                                                                         | 53    |

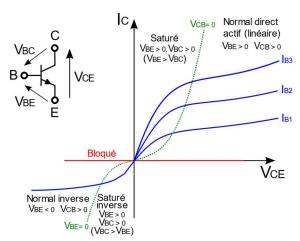

| Figure I.27 : Régimes de fonctionnement du transistor bipolaire                                                                         | 55    |

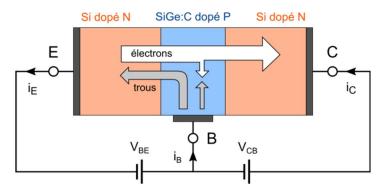

| Figure I.28 : Bilan des courants dans le transistor en régime normal direct                                                             | 56    |

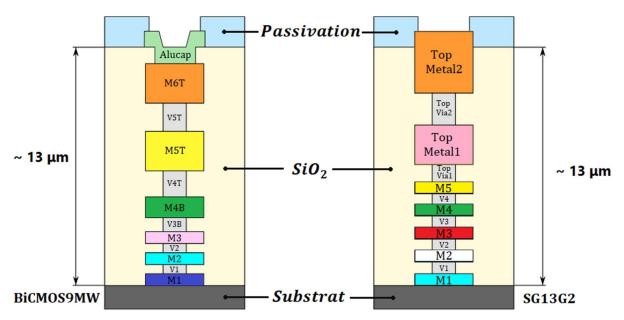

| Figure I.29 : BEOL de la technologie BiCMOS9MW et SG13G2                                                                                | 57    |

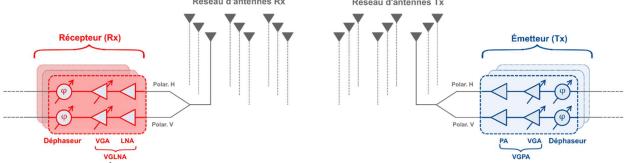

| Figure II.1 Émetteur-récepteur (Rx/Tx) à dépointage électronique (front-end) en bande Ka                                                | .63 s |

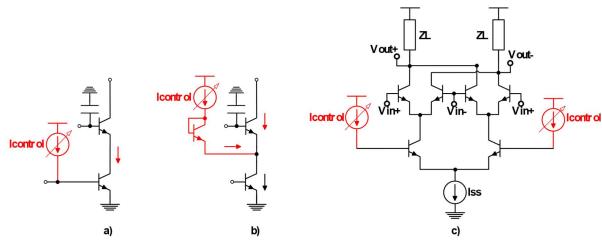

| Figure II.2 Topologies classiques des VGAs. Topologies émetteur commun (a), cascode current-steering (b) et cellule de Gilbert (c)      | 64    |

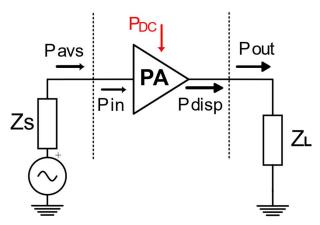

| Figure II.3 Bilan de puissance de l'amplificateur de puissance                                                                          | 65    |

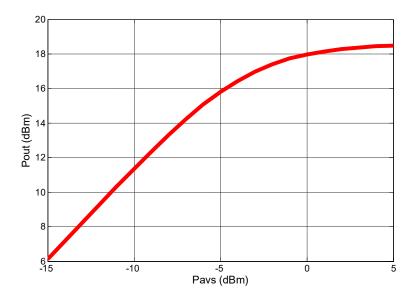

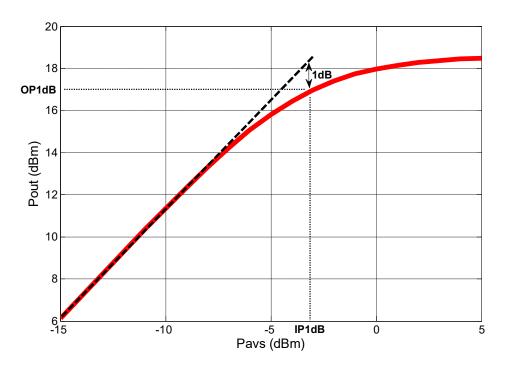

| Figure II.4 Puissance de sortie ( $P_{out}$ ) et puissance de sortie saturée ( $P_{sat}$ )                                              | 66    |

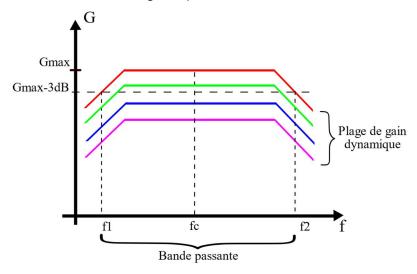

| Figure II.5 Bande passante et plage de gain dynamique                                                                                   | 67    |

| Figure II.6 Point de compression de 1 dB. Rouge (fondamental), noir (extrapolation)                                                     | 68    |

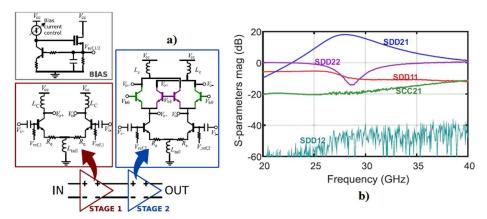

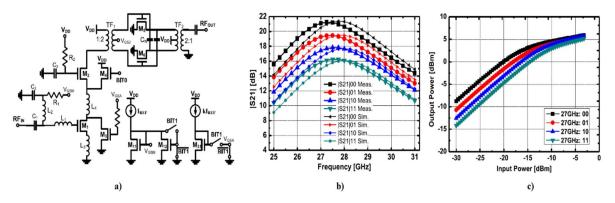

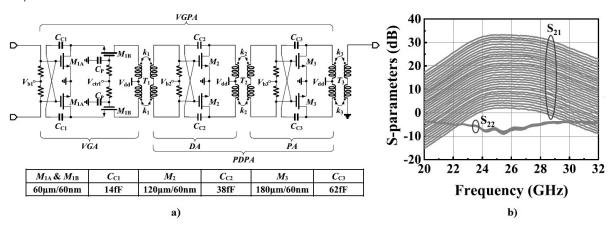

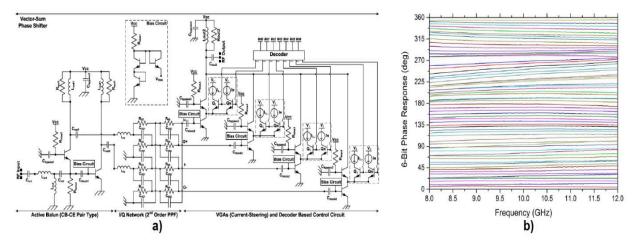

| Figure II.7 Schéma électrique (a) et résultats mesurés en paramètres S (b) du travail [78]                                              | 70    |

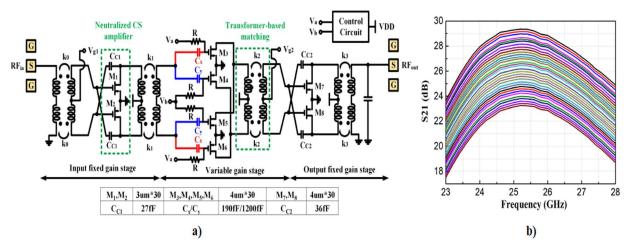

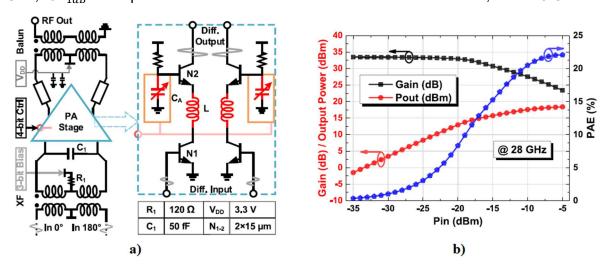

| Figure II.8 Schéma électrique (a) gain dynamique mesuré en paramètres S (b) et puissan de sortie (c) du travail [73]                    |       |

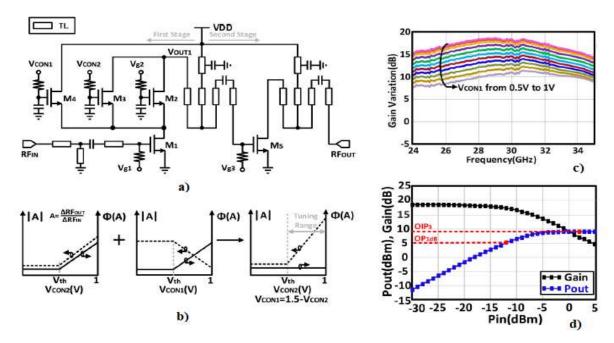

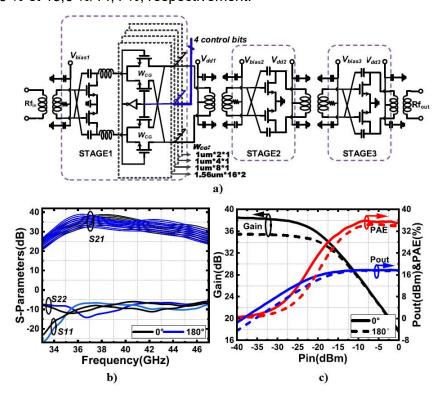

| Figure II.9 Schéma électrique (a) et gain dynamique mesuré en paramètres S du travail [7                                                |       |

| Figure II.10 Schéma électrique (a), variation d'amplitude (b), gain dynamique (c) et puissance/gain en fonction de Pin du travail [80]  | 72    |

| Figure II.11 Schéma électrique (a) et gain dynamique mesuré du travail [81]                                                             | 72    |

| Figure II.12 Schéma électrique (a) et gain dynamique mesuré du travail [82]                                                             | 73    |

| Figure II.13 Schéma électrique (a) et Pout/Gain/PAE mesuré en fonction de Pin du travail [74]                                           |       |

| Figure II.14 Schéma électrique (a) gain dynamique mesuré (b) et Pout/Gain/PAE mesuré fonction de Pin du travail [83]                    |       |

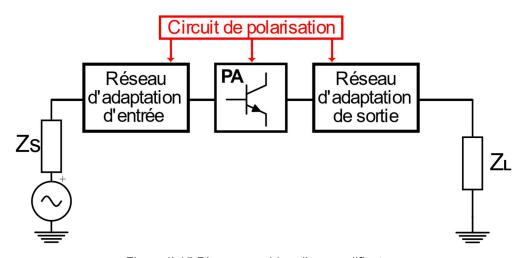

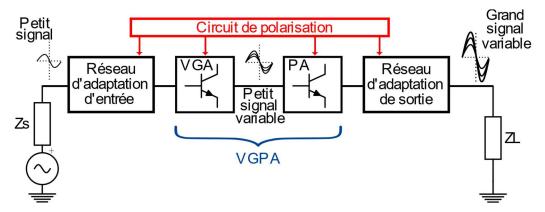

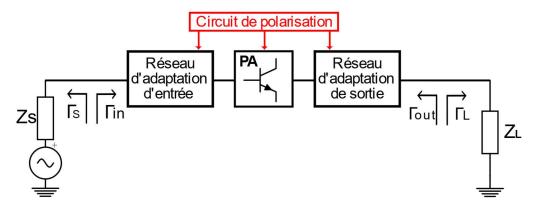

| Figure II.15 Diagramme bloc d'un amplificateur                                                                                          | 76    |

| Figure II.16 Diagramme bloc d'un VGA complet                                                                                            | 77    |

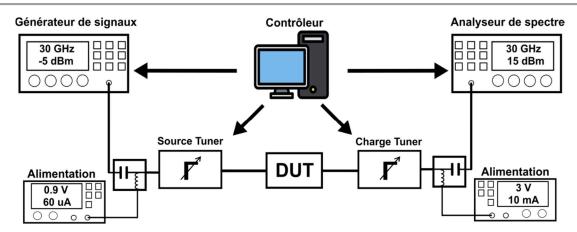

| Figure II.17 Setup Load-Pull en mesure                                                                                                  | 80    |

| Figure II.18 Setup <i>Load-Pull</i> en simulation                                                                                       | 80    |

| Figure II.19 Diagram de Load-Pull. Contours de puissance (en rouge) et de PAE (en bleu                                                  | ).81  |

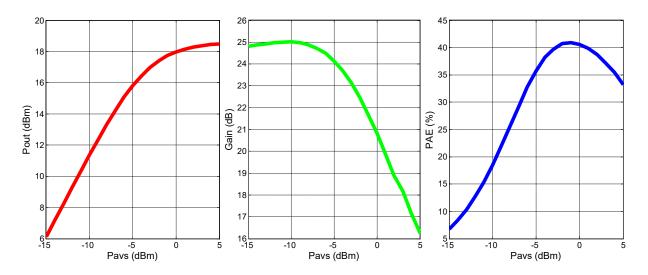

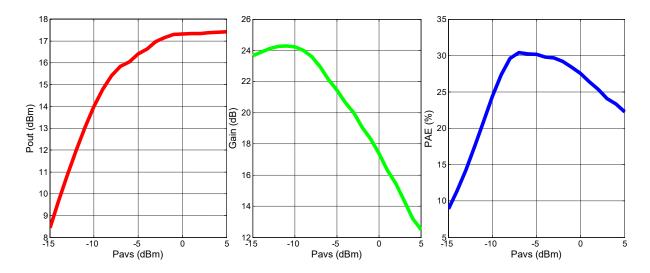

| Figure II.20 $P_{sat}$ (rouge), Gain (vert) et PAE (bleu) en schéma                                                                     | 82    |

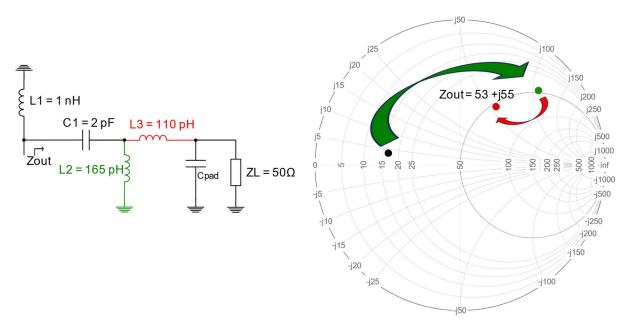

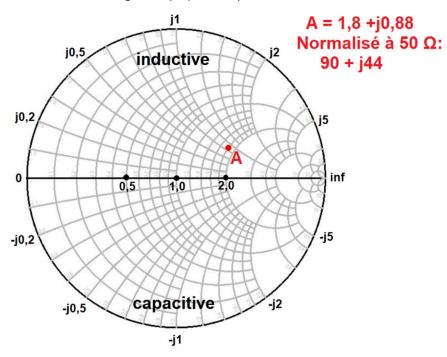

| Figure II.21 Synthèse du réseau de sortie                                                                                               | 82    |

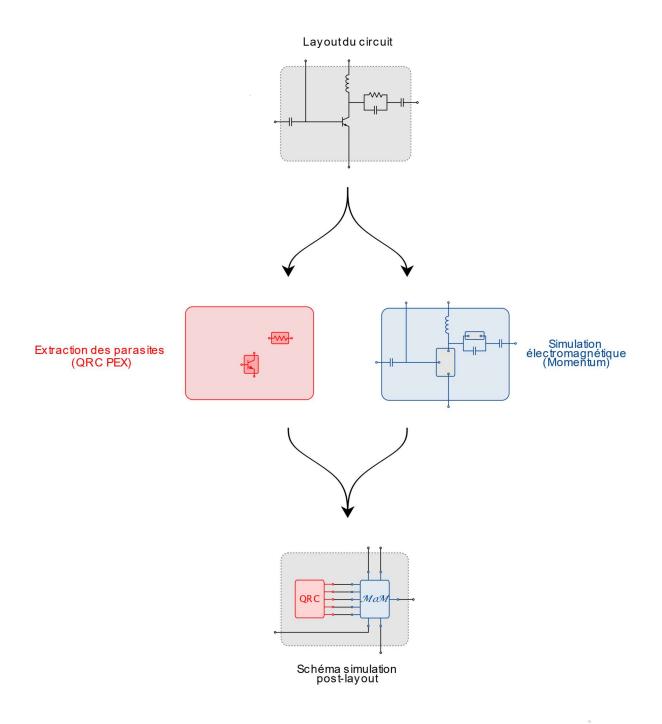

| Figure II 22 Simulations post-layout                                                                                                    | 84    |

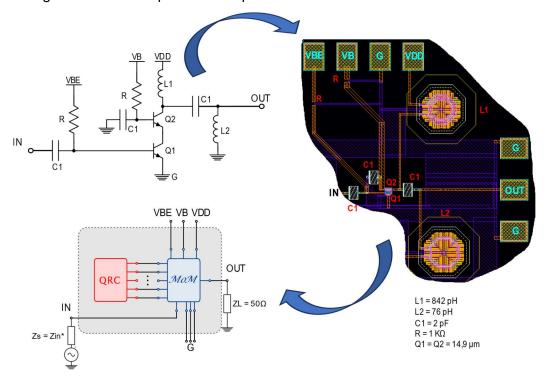

| Figure II.23 Schéma et <i>layout</i> de l'étage de puissance, et <i>setup</i> de simulation                                     | 85            |

|---------------------------------------------------------------------------------------------------------------------------------|---------------|

| Figure II.24 $P_{sat}$ (rouge), Gain (vert) et PAE (bleu) en <i>post-layout</i>                                                 | 85            |

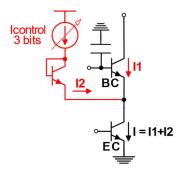

| Figure II.25 Topologie cascode current-steering                                                                                 | 86            |

| Figure II.26 Circuit et <i>setup</i> de simulation de l'étage à gain variable                                                   | 86            |

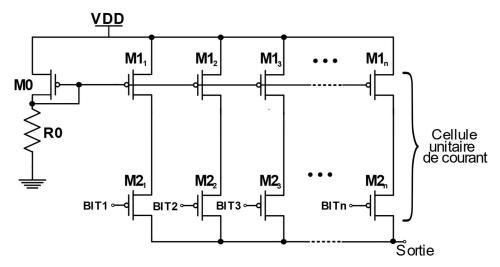

| Figure II.27 Topologie générique d'un DAC                                                                                       | 87            |

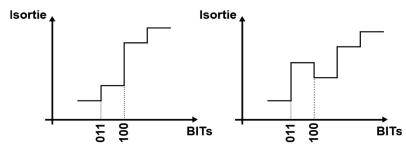

| Figure II.28 Sauts ou non-monotonie dans les caractéristiques du DAC à pondérati                                                |               |

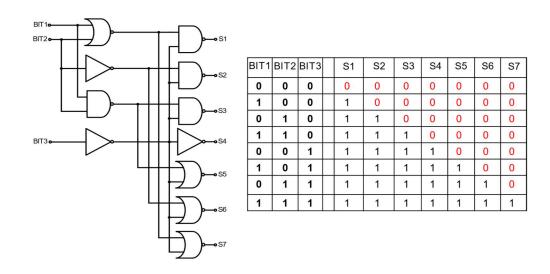

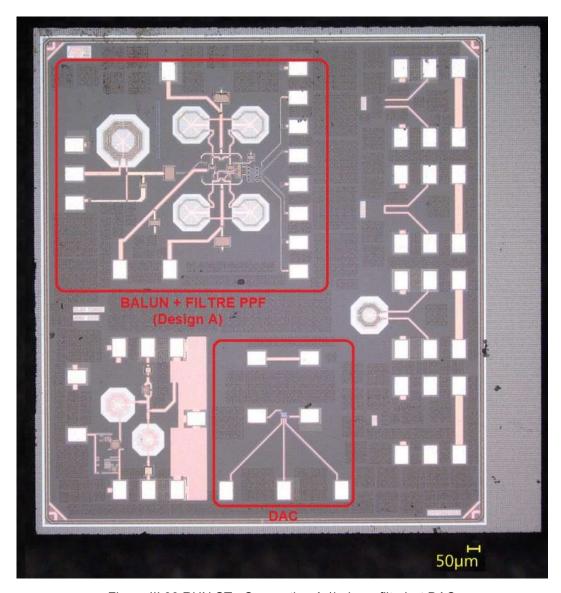

| Figure II.29 Décodeur 3 bits ( <i>Binary-Thermometer Decoder</i> )                                                              |               |

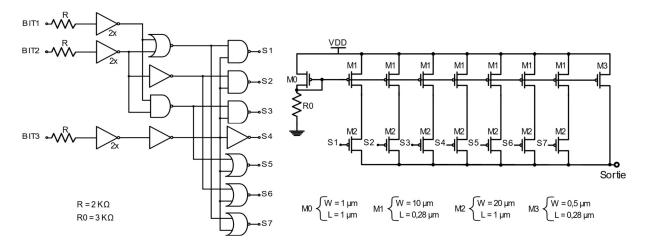

| Figure II.30 Convertisseur Numérique Analogique 3 bits                                                                          | 88            |

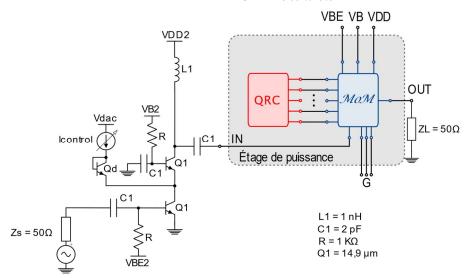

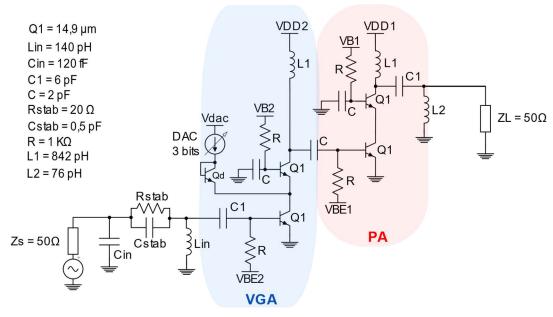

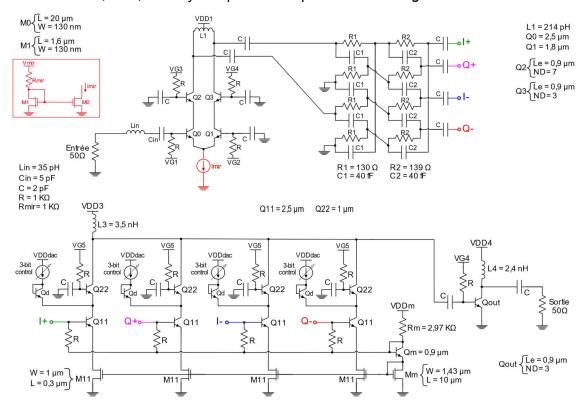

| Figure II.31 Circuit complet du VGPA                                                                                            | 89            |

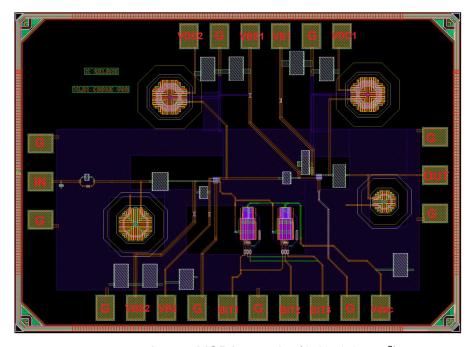

| Figure II.32 Layout VGPA complet (1,4 x 0,9 mm²)                                                                                | 89            |

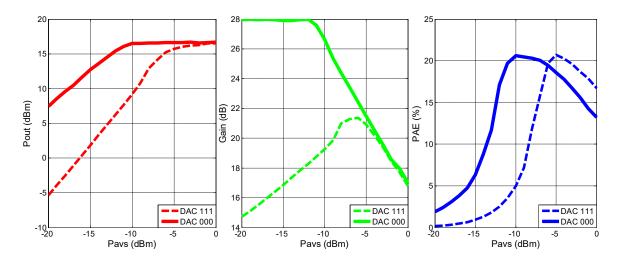

| Figure II.33 $P_{sat}$ (rouge), Gain (vert) et PAE (bleu) du VGPA complet. DAC en 111 maximum gain et DAC en 000 = minimum gain |               |

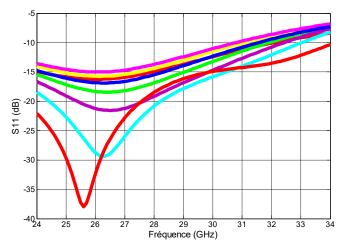

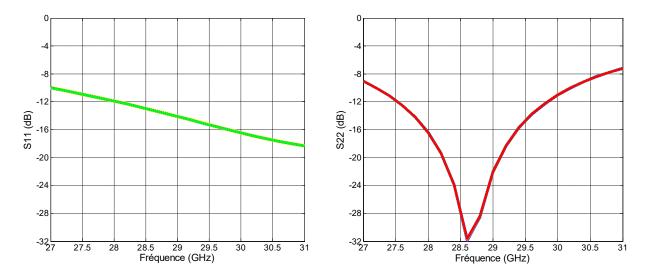

| Figure II.34 S <sub>11</sub> du VGPA pour les 8 états de gain                                                                   | 90            |

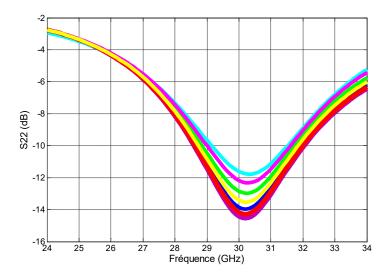

| Figure II.35 S <sub>22</sub> du VGPA pour les 8 états de gain                                                                   | 91            |

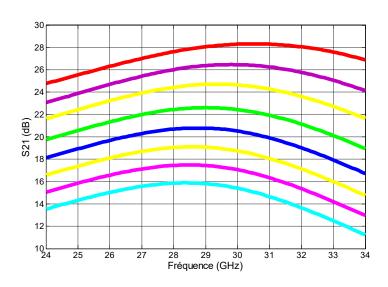

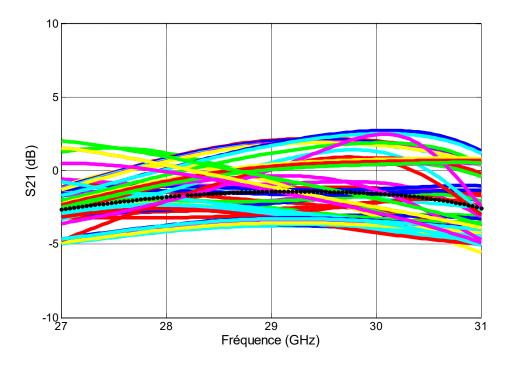

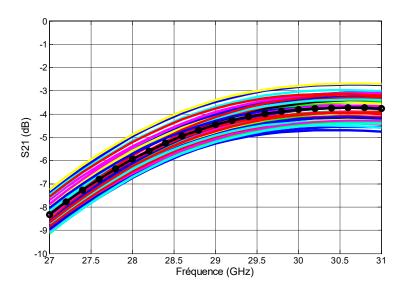

| Figure II.36 S <sub>21</sub> du VGPA pour les 8 états de gain                                                                   | 91            |

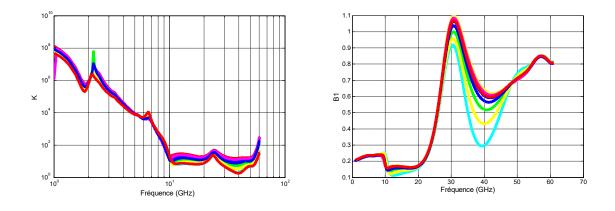

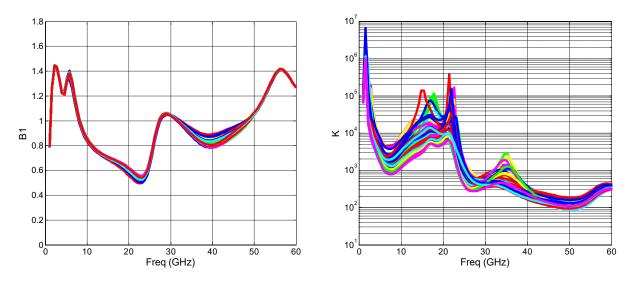

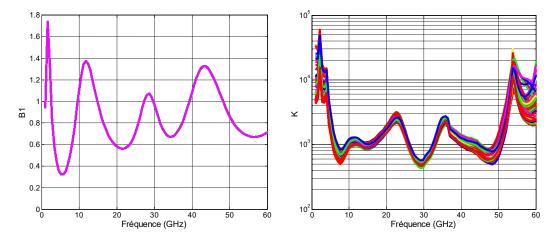

| Figure II.37 Analyse de stabilité K et B1 pour les 8 états de gain                                                              | 91            |

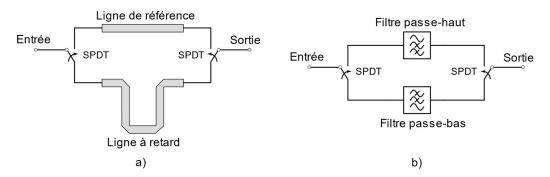

| Figure III.1 Ligne à retard commutée a) et Filtres commutées b)                                                                 | 97            |

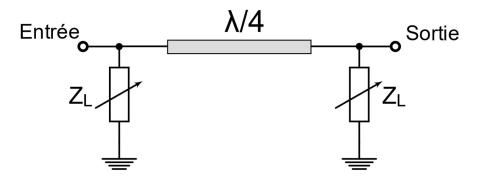

| Figure III.2 Ligne chargée                                                                                                      | 99            |

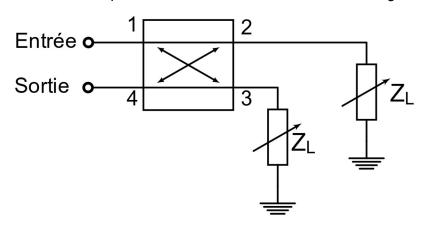

| Figure III.3 Déphaseur en réflexion (RTPS)                                                                                      | 99            |

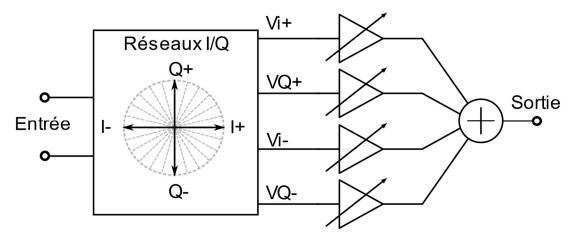

| Figure III.4 Modulateur Vectoriel                                                                                               | 100           |

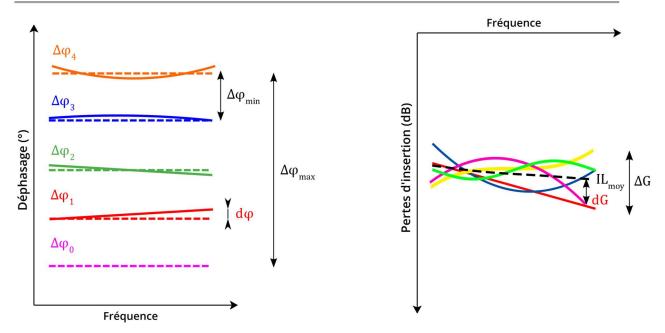

| Figure III.5 Critères de performance des déphaseurs                                                                             | 102           |

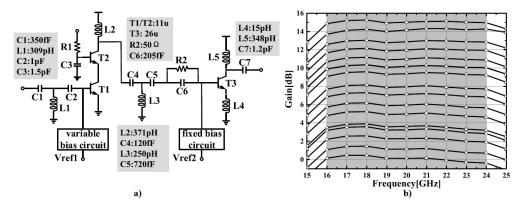

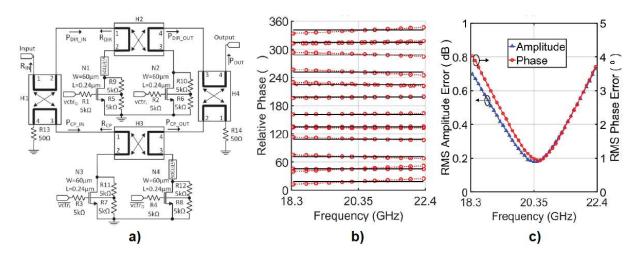

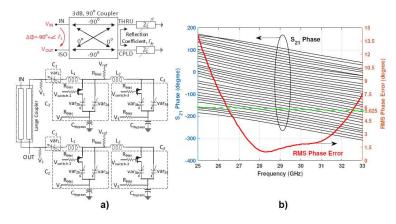

| Figure III.6 Schéma électrique (a) et phase relative (c) du travail [95]                                                        | 104           |

| Figure III.7 Schéma électrique (a) phase relative (c) et erreurs RMS du travail [94]                                            | 104           |

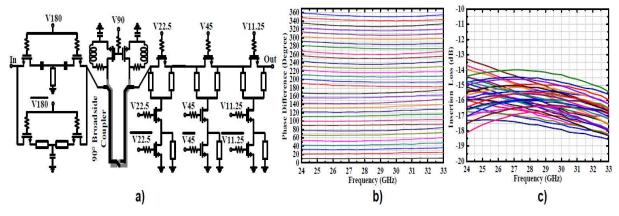

| Figure III.8 Schéma électrique (a) phase relative (b) et perte d'insertion (c) du trava                                         | ail [96] .105 |

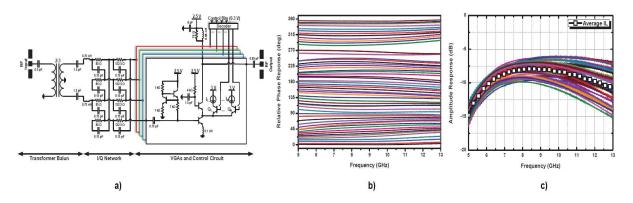

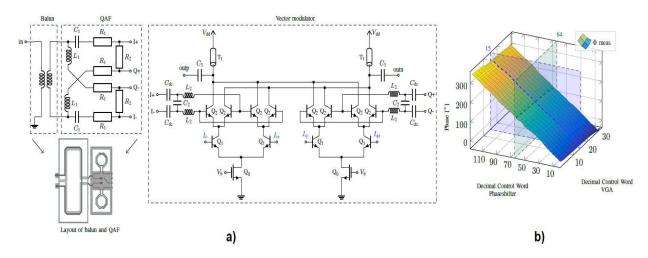

| Figure III.9 Filtre polyphase RC (a), VGAs (b), phase relative (c) et perte d'insertior [97]                                    |               |

| Figure III.10 Architecture proposée (a), phase relative et perte d'insertion (b) du tra                                         |               |

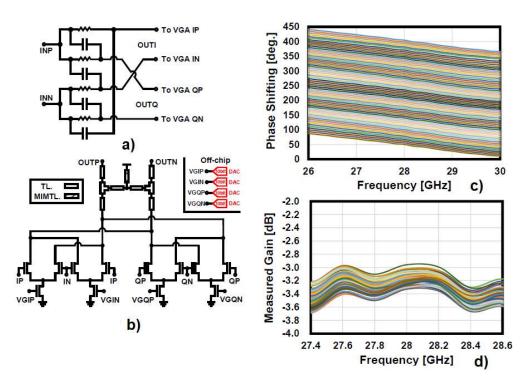

| Figure III.11 Schéma proposée (a), phase relative et erreur de phase RMS (b) du t                                               | ravail [99]   |

| Figure III.12 Schéma proposé (a) et réponse en phase en fonction des bits du VM/du travail [100]                                | ` '           |

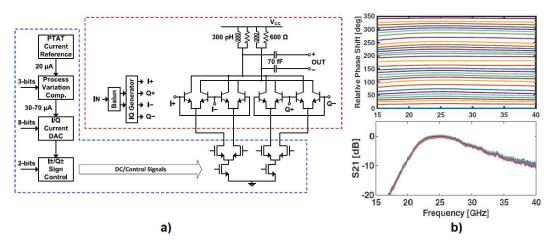

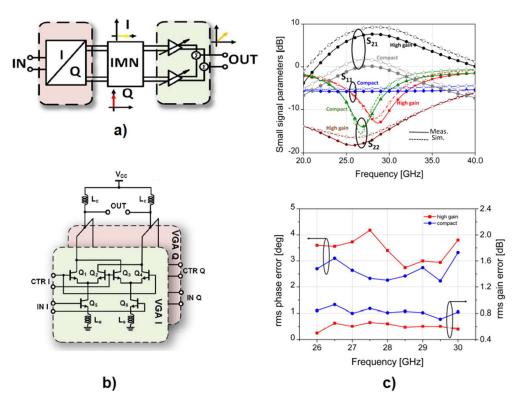

| Figure III.13 Schéma électrique (a) phase relative (b) et perte d'insertion (c) du trav                                         |               |

| Figure III.14 Architecture proposée (a), cellules de Gilbert (b) et réponse des paramé erreur de phase e d'amplitude pour VM1 et VM2 du travail [102]            |          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Figure III.15 Architecture classique d'un modulateur vectoriel                                                                                                   | 110      |

| Figure III.16 1 <sup>er</sup> étage de la conception A                                                                                                           |          |

| Figure III.17 Gain de tension (a) et déphasage relative (b) du 1er étage de la concept                                                                           | ion A112 |

| Figure III.18 Réseaux I/Q : coupleur hybride (a), filtre passe-tout QAF (b) et filtre pol<br>(c)                                                                 |          |

| Figure III.19 Types de filtres polyphases                                                                                                                        | 114      |

| Figure III.20 Filtre polyphase RC de 2 <sup>ème</sup> ordre de la conception A                                                                                   | 114      |

| Figure III.21 Phase relative à la sortir du filtre PPF de la conception A                                                                                        | 115      |

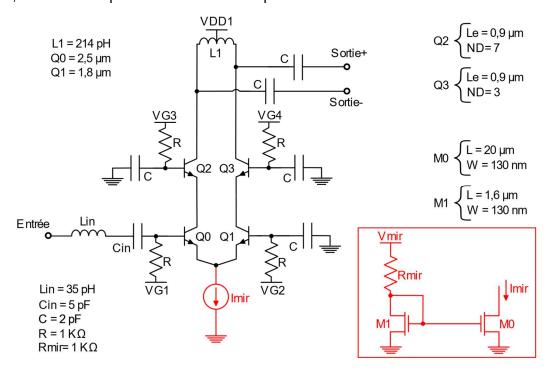

| Figure III.22 Schéma du modulateur vectoriel (conception A)                                                                                                      | 115      |

| Figure III.23 Configuration de simulation des VGAs isolés                                                                                                        | 116      |

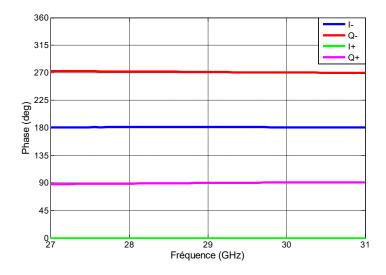

| Figure III.24 Phase relative à la sortie des VGAs isolés                                                                                                         | 116      |

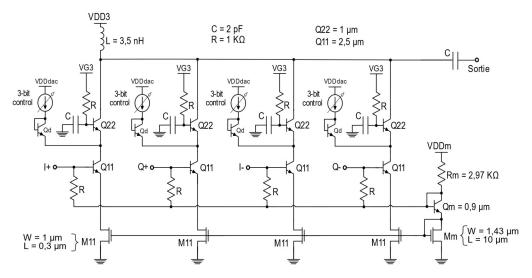

| Figure III.25 Topologie 4VGA                                                                                                                                     | 117      |

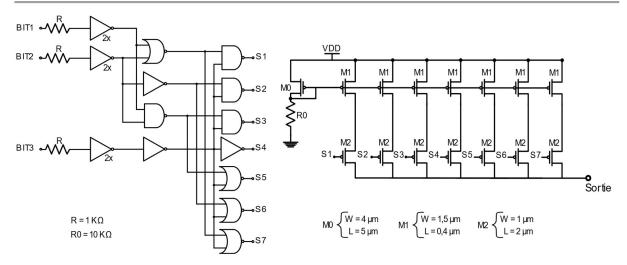

| Figure III.26 DAC de la conception A                                                                                                                             | 117      |

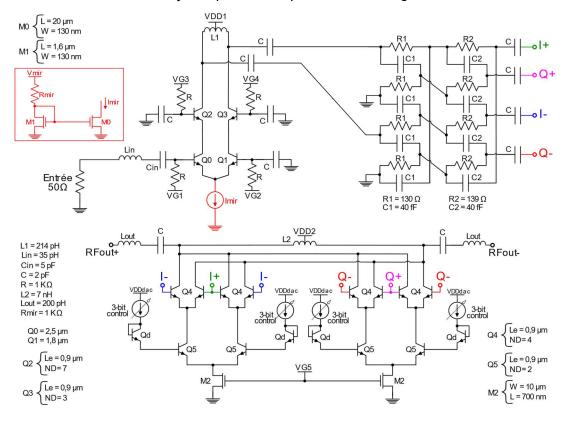

| Figure III.27 Schéma électrique de la conception A                                                                                                               | 118      |

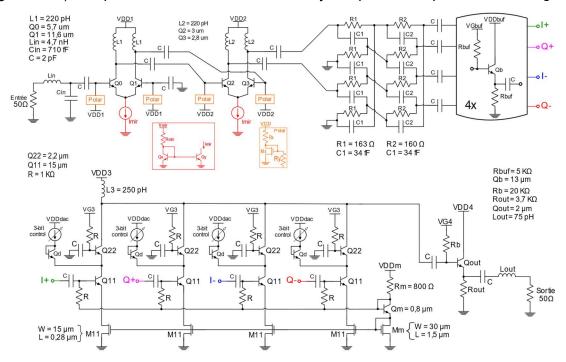

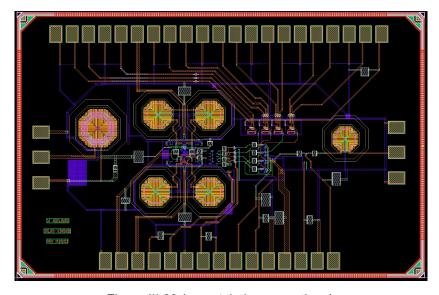

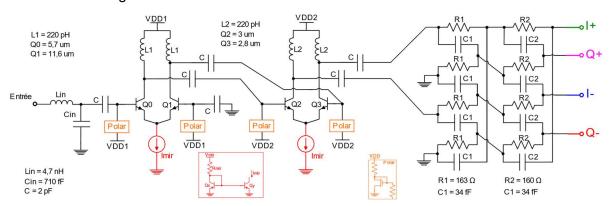

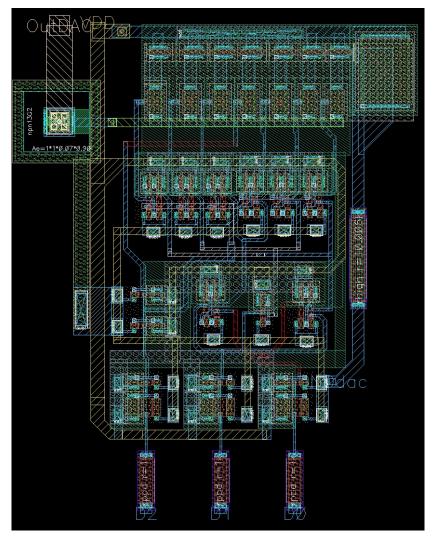

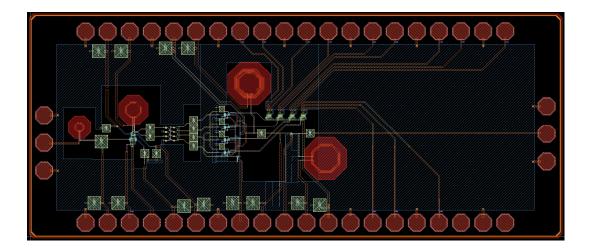

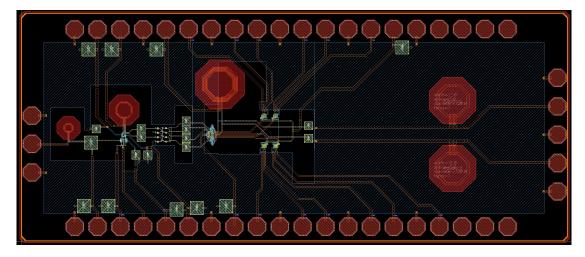

| Figure III.28 <i>Layout</i> de la conception A                                                                                                                   | 118      |

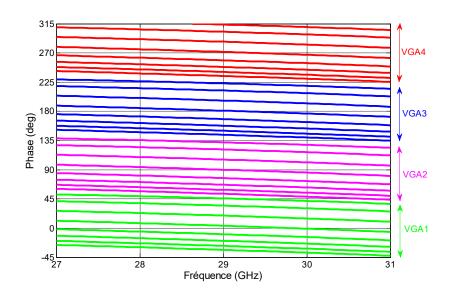

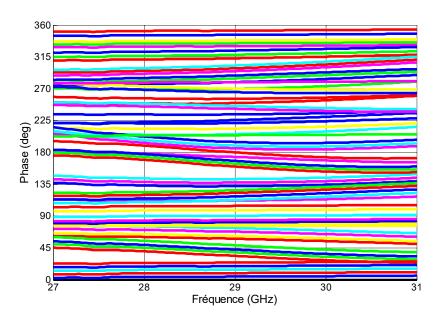

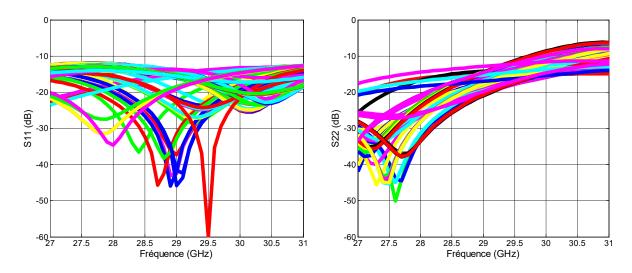

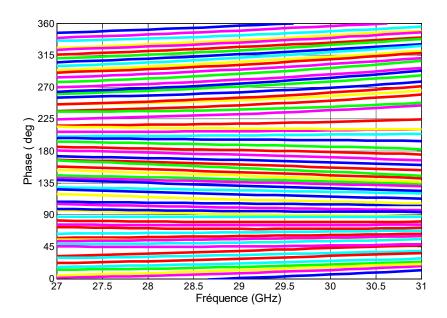

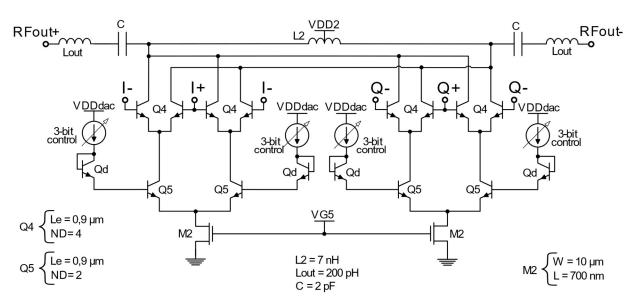

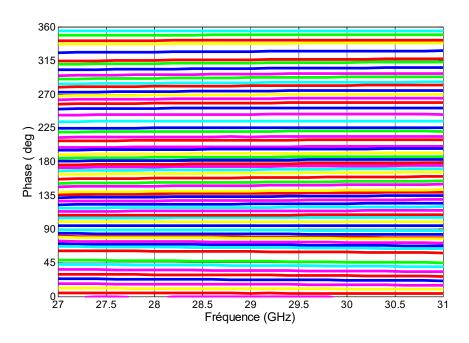

| Figure III.29 Phase relative de la conception A                                                                                                                  | 119      |

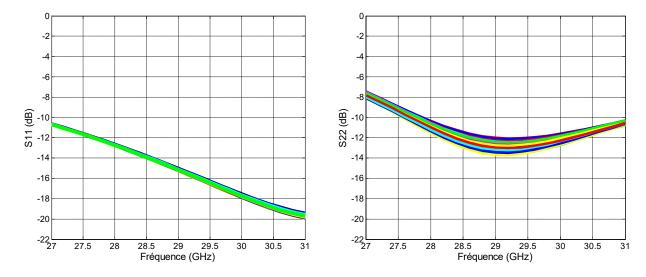

| Figure III.30 Adaptation d'entrée $(S_{11})$ et de sortie $(S_{22})$ de la conception A                                                                          | 119      |

| Figure III.31 Pertes d'insertion ( $S_{21}$ ) de la conception A                                                                                                 | 120      |

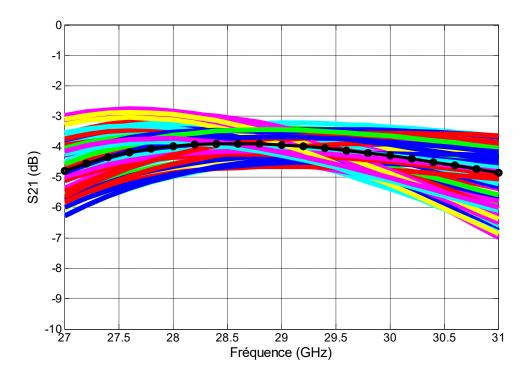

| Figure III.32 Paramètres de stabilité (B1 et K) de la conception A                                                                                               | 120      |

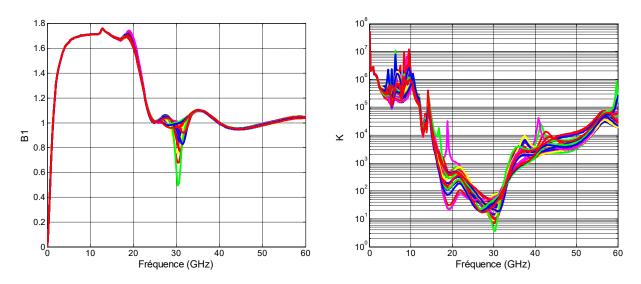

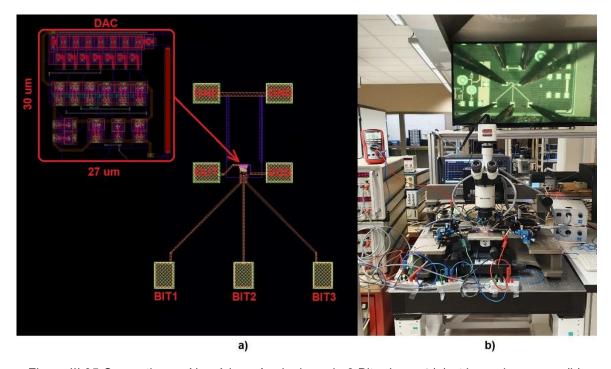

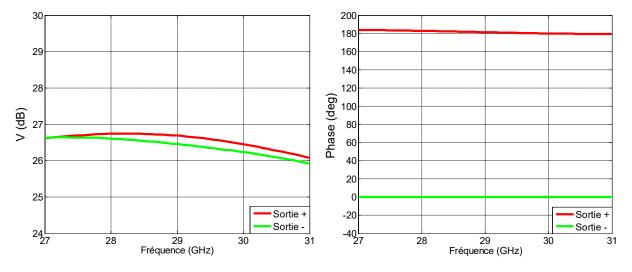

| Figure III.33 RUN ST : Conception A ( <i>balun</i> + filtre) et DAC                                                                                              | 121      |

| Figure III.34 DAC de la conception A fabriqué                                                                                                                    | 122      |

| Figure III.35 Convertisseur Numérique Analogique de 3 Bits. <i>Layout</i> (a) et banc de n<br>(b)                                                                |          |

| Figure III.36 Circuit schématique de la conception A (balun + filtre) fabriqué                                                                                   | 123      |

| Figure III.37 Conception A ( <i>balun</i> + filtre) en mesure                                                                                                    | 123      |

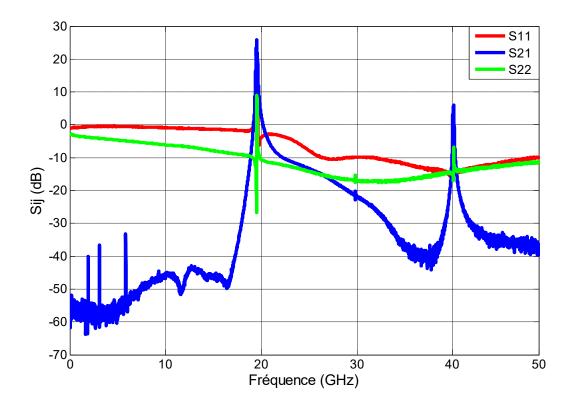

| Figure III.38 Résultats de mesure de la conception A dans des conditions de polaris<br>nominales                                                                 |          |

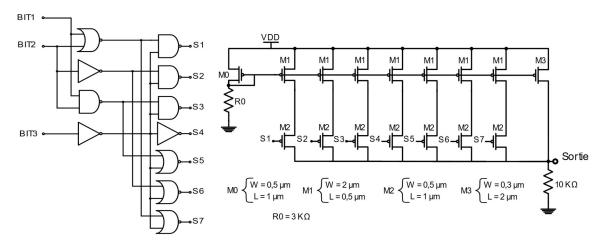

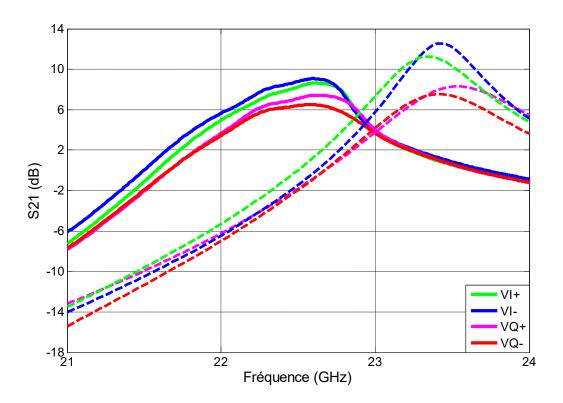

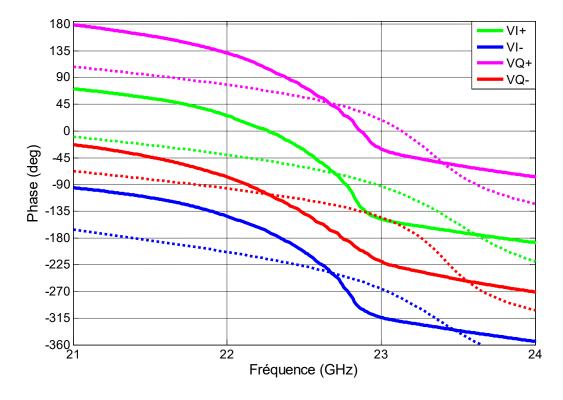

| Figure III.39 Résultats de mesure (ligne continue) et <i>post-layout</i> (ligne pointillée) de les quatre voies de la conception A ( <i>balun</i> + filtre)      | •        |

| Figure III.40 Résultats de mesure (ligne continue) et <i>post-layout</i> (ligne pointillée) de pour les quatre voies de la conception A ( <i>balun</i> + filtre) | •        |

| Figure III.41 1 <sup>er</sup> étage de la conception B                                                                                                           | 126      |

| Figure III.42 Gain de tension (a) et déphasage relative (b) du 1er étage de la concept                                                                           | ion B127 |

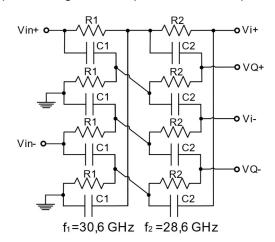

| Figure III.43 Filtre polyphase RC de 2ème ordre de la conception B                                                                                               | 128      |

| Figure III.44 Phase relative à la sortir du filtre PPF de la conception B                     | 128 |

|-----------------------------------------------------------------------------------------------|-----|

| Figure III.45 Topologie 4VGA (conception B)                                                   | 129 |

| Figure III.46 DAC de la conception B                                                          | 130 |

| Figure III.47 <i>Layout</i> du DAC de la conception B (33 μm x 42 μm)                         | 130 |

| Figure III.48 Schéma électrique de la conception B                                            | 131 |

| Figure III.49 <i>Layout</i> de la conception B                                                | 131 |

| Figure III.50 Phase relative de la conception B                                               | 132 |

| Figure III.51 Adaptation d'entrée ( $S_{11}$ ) et de sortie ( $S_{22}$ ) de la conception B   | 132 |

| Figure III.52 Pertes d'insertion ( $S_{21}$ ) de la conception B                              | 133 |

| Figure III.53 Paramètres de stabilité (B1 et K) de la conception B                            | 133 |

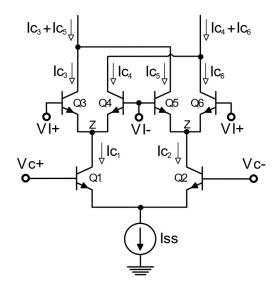

| Figure III.54 Cellule de Gilbert                                                              | 134 |

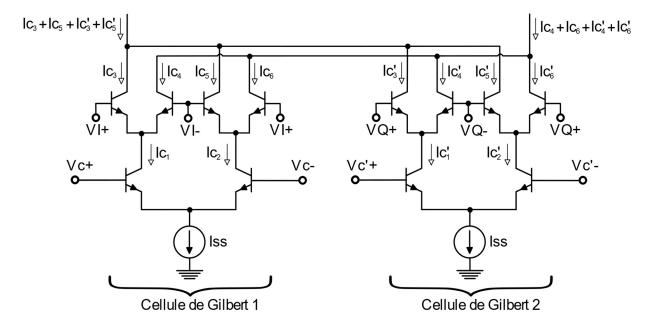

| Figure III.55 Double cellule de Gilbert                                                       | 136 |

| Figure III.56 Topologie proposée (GC)                                                         | 137 |

| Figure III.57 Schéma électrique de la conception C                                            | 138 |

| Figure III.58 Layout de la conception C                                                       | 138 |

| Figure III.59 Phase relative de la conception C                                               | 139 |

| Figure III.60 Adaptation d'entrée ( $S_{11}$ ) et de sortie ( $S_{22}$ ) de la conception C   | 139 |

| Figure III.61 Pertes d'insertion (S <sub>21</sub> ) de la conception C                        | 140 |

| Figure III.62 Paramètres de stabilité (B1 et K) de la conception C                            | 140 |

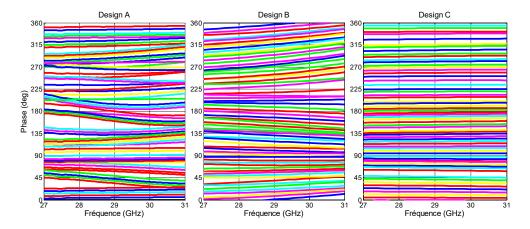

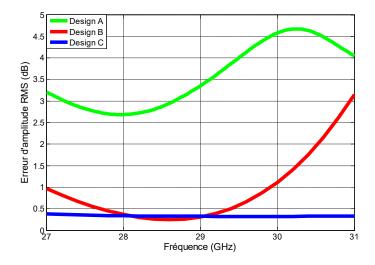

| Figure III.63 Comparaison entre les phases relatives des conceptions A, B et C                | 141 |

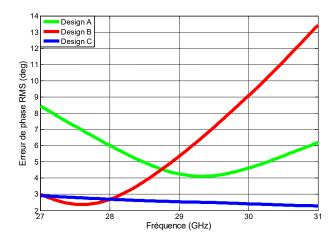

| Figure III.64 Erreur de Phase RMS des conceptions A, B et C                                   | 141 |

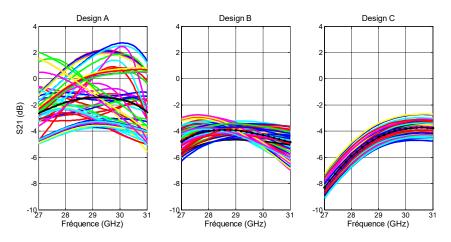

| Figure III.65 Comparaison entre les pertes d'insertion ( $S_{21}$ ) des conceptions A, B et C | 142 |

| Figure III.66 Erreur d'amplitude RMS des conceptions A. B et C                                | 142 |

# Table des tableaux

| Tableau I-1 État de l'art des systèmes d'antennes à dépointage électronique en bande k                        |          |

|---------------------------------------------------------------------------------------------------------------|----------|

| Tableau I-2 Spécifications du système                                                                         | 52       |

| Tableau I-3 Caractéristiques des transistors HBT dans les technologies BiCMOS9MW (ebbeu) et SG13G2 (en rouge) | en<br>58 |

| Tableau I-4 Caractéristiques des résistances dans les technologies BiCMOS9MW (bleu)                           | •        |

| Tableau II-1 État de l'art des VGA en bande Ka                                                                | 69       |

| Tableau II-2 Spécifications préliminaires du VGA                                                              | 76       |

| Tableau II-3 Comparatif des topologies [84]                                                                   | 78       |

| Tableau II-4 Paramètres et impédances obtenus après Load-Pull avec optimisation                               | 81       |

| Tableau II-5 Comparatif au cahier des charges du VGA                                                          | 92       |

| Tableau II-6 Comparaison avec l'état de l'art                                                                 | 93       |

| Tableau II-7 Comparaison avec l'état de l'art concernant la FOM et le GBP                                     | 94       |

| Tableau III-1 État de l'art des déphaseurs en bande X/Ka                                                      | 103      |

| Tableau III-2 Spécifications du déphaseur                                                                     | 109      |

| Tableau III-3 Comparaison entre les résultats <i>post-layout</i> (QRC) et les mesures du DAC                  | 122      |

| Tableau III-4 Comparaison avec les spécifications du déphaseur                                                | 143      |

| Tableau III-5 Comparaison avec l'état de l'art                                                                | 144      |

# Liste des sigles et acronymes

5G

5ème génération de téléphonie mobile

6G

6ème génération de téléphonie mobile

ABF Analog BeamForming

AC Alternating current

ACLR Adjacent Channel Leakage Ratio

AiP Antenna-in-package

AR Axial Ratio

BALUN Balanced-to-Unbalanced

BEOL Back End Of Line

BGA Ball Grid Array

BiCMOS Bipolar CMOS

BJT Bipolar Junction Transistor

**CAO** Conception Assistée par Ordinateur

CB Common Base

CE Common Emitter

**CMOS** Complementary Metal Oxyde Semiconductor

DBF Digital Beamforming

DC Direct Current

**DRA** Direct Radiating Array

ETSI European Telecommunication Standards Institute

**EVM** Error Vector Magnitude

**EUTELSAT** European Telecommunications Satellite Organisation

FCC Federal Communications Commission

G/T Gain / Température

GaAs Arséniure de Gallium

**GaN** Nitrure de Gallium

**GEO** Geostationary Equatorial Orbit

HBF Hybrid Beamforming

**HBT** Heterojunction Bipolar Transistor

HTS High Throughput Satellite

**IF** Intermediary Frequency

**IFC** In–Flight Connectivity

InP Phosphure d'Indium

ITRS International Technology Roadmap for Semiconductors

**LEO** Low Earth Orbit

LHCP Left-Handed Circular Polarization

LNA Low Noise Amplifier

MEO Medium Earth Orbit

MIM Metal Insulator Metal

MOSFET Metal Oxide Semiconductor Field-Effect Transistor

NF Noise Figure

PCB Printed Circuit Board

PGS Pattern Ground Shield

PIRE Puissance Isotrope Rayonnée Équivalente

PPF Polyphase Filter

QFN Quad Flat No-Leads

RADAR Radio Detection and Ranging

RF Radiofréquence

RFIC Radio Frequency Integrated Circuit

RHCP Right-Handed Circular Polarization

RMS Root Mean Square

Rx Réception

**SATCOM** Satellite Communications

**SiGe** Silicium-Germanium

SIW Substrate Integrated Waveguide

SNR Signal-to-Noise Ratio

SOI Silicon on Insulator

**SOTM** SATCOM On The Move

**SPDT** Single Pole Double Throw

TTD True Time Delay

Tx Transmission

VM Vector Modulator

#### Introduction

Au cours de la dernière décennie, l'industrie des communications par satellite (SATCOM) a connu une croissance significative, principalement stimulée par la demande croissante de dispositifs sans fil. De nos jours, assurer une connectivité continue est devenu essentiel pour répondre à la demande croissante des consommateurs qui, de plus en plus, font face à de grandes quantités de données et avec des débits très élevés. En effet, le trafic de données des réseaux mobiles a augmenté de 36 % entre le T1 2022 et le T1 2023 [1] .

Dans le contexte des applications aéronautiques, des solutions de connectivité innovantes sont en plein essor. Depuis quelques années, de nombreuses compagnies aériennes ont progressivement équipé leurs avions de systèmes d'antennes dédiés aux satellites, dans le but d'offrir une connexion Internet haut débit aux passagers. Cette tendance a marqué l'essor du marché de la connectivité aéronautique, communément désigné sous l'acronyme IFC (*In-Flight Connectivity*). Néanmoins, offrir un accès à Internet aux passagers représente un défi à la fois économique et technologique. Ces services nécessitent des terminaux embarqués compacts, flexibles, économiques et fiables, capables de résister à des conditions environnementales difficiles tout en occupant peu d'espace. De plus, ces terminaux doivent être équipés d'antennes à faible profil, permettant un suivi rapide et continu d'un satellite, tout en assurant un trafic de données à haut débit.

L'émergence de satellites à haut débit en bande Ka, d'une part, et les avancées de l'industrie des semi-conducteurs, caractérisées par la miniaturisation des dispositifs et la réduction des coûts de fabrication, d'autre part, ouvrent la voie à l'utilisation de réseaux d'antennes à dépointage électronique. Ce type d'antenne offre une traînée aérodynamique réduite, tout en permettant un dépointage rapide du faisceau avec une grande fiabilité.

Dans ce contexte, *Safran Data Systems*, une filiale du prestigieux équipementier aéronautique *Safran*, a décidé de développer sa propre solution d'antenne à dépointage électronique dédiée aux communications satellitaires. Cette initiative marque une nouvelle orientation pour l'entreprise, qui était jusqu'alors spécialisée dans la conception de stations sol. Pour mener à bien ce projet ambitieux, *Safran Data Systems* a opté pour une collaboration avec le laboratoire XLIM en raison de son expertise avérée dans ce domaine. Ce partenariat a donné lieu à la création du laboratoire commun nommé X-SELANS (*Xlim-Safran Electronics Lab for ANtennaS*). Cette collaboration a abouti à la réalisation de quatre thèses : la première portant sur la modélisation de grands panneaux rayonnants, la deuxième sur le développement de circuits actifs en arséniure de gallium pour la chaîne de réception, la troisième sur la conception de circuits actifs en silicium-germanium également pour la chaîne de réception, et enfin la quatrième sur la co-simulation des circuits actifs et des éléments rayonnants.

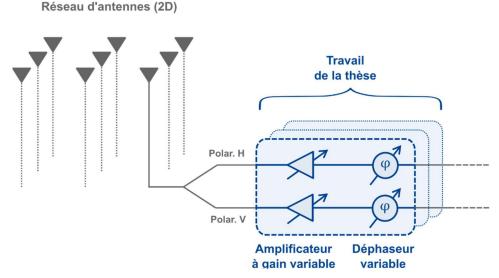

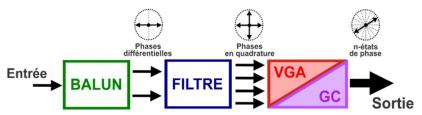

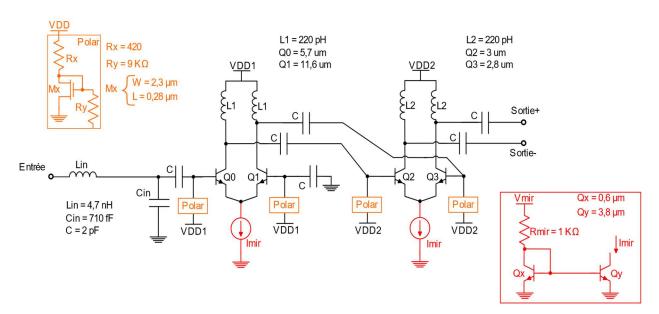

Le travail de cette thèse de doctorat se concentre notamment sur la conception des circuits actifs intégrés en silicium-germanium pour la chaîne d'émission (27 ~ 31 GHz). Deux blocs fondamentaux seront abordés et conçus : le premier est un amplificateur variable, et le second est un déphaseur pilotable. L'intégralité de ce travail est exposée dans ce manuscrit, structurée en trois chapitres :

- ➤ Le premier chapitre sert d'introduction en présentant le contexte et les objectifs du projet au sein duquel cette thèse prend place. Il commence par présenter une synthèse de l'évolution des télécommunications par satellite suivie du principe de fonctionnement d'une antenne à dépointage électronique, ainsi que des architectures possibles et un état de l'art des systèmes existants. Ensuite, il explore le cadre de la thèse et offre un exposé détaillé des spécifications préliminaires du système dans le cahier des charges. Enfin, le choix technologique est justifié et différents aspects des technologies BiCMOS9MW (STMicroelectronics) et SG13G2 (IHP) choisies sont comparés.

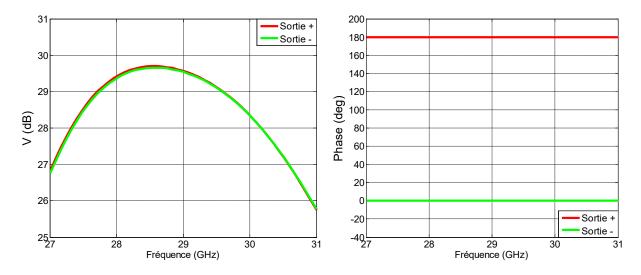

- Le deuxième chapitre présente l'approche adoptée pour concevoir l'amplificateur de puissance à gain variable (VGPA : Variable Gain Power Amplifier). Il commence par présenter une introduction à ce type d'amplificateur suivi de la définition des paramètres de performances, pour ensuite présenter un état de l'art. Dans un deuxième temps, le cahier des charges est défini puis la méthodologie de conception des différents étages de l'amplificateur est détaillée. Enfin, ce chapitre se termine par la présentation des résultats de simulation post-layout du VGPA complet.

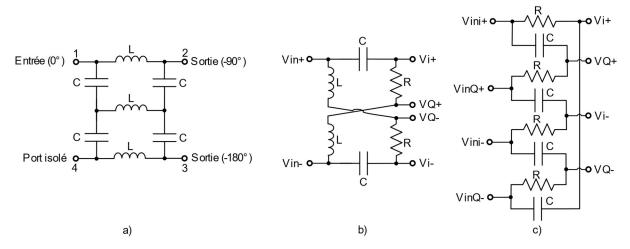

- Le troisième et dernier chapitre aborde la partie de la conception des déphaseurs. Dans un premier temps, le chapitre commence par présenter une introduction aux types de déphaseurs, passant en revue les paramètres de performances qui caractérisent ce type de circuit, présentant l'état de l'art, puis définissant les spécifications et justifiant le choix de la topologie. Dans un deuxième temps, la conception de trois circuits utilisant deux topologies différentes est détaillée. Les résultats de simulation post-layout et certaines mesures sont ensuite présentés. Enfin, ce chapitre se termine en présentant une comparaison entre les résultats post-layout des trois conceptions avec le cahier des charges et à l'état de l'art.

# Chapitre I

# Contexte de l'étude

# **Sommaire**

| Chapitre I. Contexte de l'étude                                 | 29 |

|-----------------------------------------------------------------|----|

| I.1. Télécommunication par satellite                            |    |

| I.1.1. Historique : du télégraphe au satellite                  | 29 |

| I.1.2. Les réseaux satellitaires                                | 31 |

| I.2. Antennes à dépointage électronique                         | 33 |

| I.2.1. Dépointage électronique : Principe                       | 34 |

| I.2.2. Architectures pour la formation de faisceau              | 37 |

| I.2.3. État de l'art des systèmes existants et en développement |    |

| I.3. Cadre de la thèse                                          |    |

| I.3.1. Objectif du projet                                       | 50 |

| I.3.2. Spécifications du système                                | 50 |

| I.3.3. Objectifs de la thèse                                    | 53 |

| I.4. Choix de la technologie                                    | 53 |

| I.4.1. Le transistor HBT et la technologie BiCMOS               | 54 |

| I.4.2. Les technologies BiCMOS9MW et SG13G2 : un bref aperçu    | 56 |

| I.4.2.1. Niveaux de métallisation (BEOL)                        | 56 |

| I.4.2.2. Transistor HBT                                         | 57 |

| I.4.2.3. Transistor MOSFET                                      | 58 |

| I.4.2.4. Résistances                                            | 58 |

| I.4.2.5. Capacités                                              | 59 |

| I.4.2.6. Inductances                                            |    |

| I.4.3. Bilan                                                    | 59 |

# Chapitre I. Contexte de l'étude

#### I.1. Télécommunication par satellite

# I.1.1. Historique : du télégraphe au satellite

La communication a été cruciale pour le développement de la société humaine depuis le début. Au fur et à mesure que la civilisation humaine progressait, il est devenu de plus en plus nécessaire de développer de nouvelles méthodes de communication qui dépassent les limites de la parole et de l'écriture traditionnelles. En effet, avec les explorations maritimes et la mondialisation, il est devenu de plus en plus important de transmettre des informations sur de longues distances et à des vitesses plus rapides.

Ce besoin n'était pas possible jusqu'au début du XIXème siècle, lorsque le premier système de télécommunication est apparu : le télégraphe. Développé par Samuel Morse et d'autres inventeurs, il a permis la première transmission transatlantique [2], marquant une percée dans l'histoire des télécommunications.

Quelques années plus tard, Alexander Graham Bell, Antonio Meucci et d'autres ont développé les premiers dispositifs électriques capables de transmettre la voix humaine. Le téléphone a été une étape importante dans l'évolution des télécommunications en permettant des conversations directes sur de longues distances [3].

En 1888, Heinrich Hertz a expérimentalement démontré l'existence des ondes électromagnétiques prédites par James Clerk Maxwell [4], ouvrant la voie à la naissance de la communication sans fil.

À la fin du XIXème siècle, des personnalités telles que Guglielmo Marconi [5], Ferdinand Braun [6] et Roberto Landell de Moura [7] ont apporté de grandes contributions dans le domaine de la communication sans fil en développant les tout premiers émetteurs-récepteurs radio. La radio a joué un rôle important dans l'histoire de la communication en permettant la transmission d'informations et de divertissements à un large public.

Le milieu du XX<sup>ème</sup> siècle a vu une transformation majeure dans le domaine de la radiodiffusion avec l'introduction de la télévision, qui a révolutionné l'industrie en ajoutant des médias visuels au format audio traditionnel.

La prochaine étape majeure dans l'histoire de la communication a été introduite avec la proposition de la communication par satellite (SATCOM) par Arthur C. Clarke en 1945. Clarke a proposé un système de diffusion utilisant des satellites, dispositifs qui permettent de relier deux points extrêmement éloignés l'un de l'autre, placés en orbite circulaire à une distance spécifique de la Terre dans le plan équatorial [8]. La miniaturisation de l'électronique suivant l'invention du transistor en 1947 a permis à John Robinson Pierce de proposer les systèmes de communication par satellite tels que nous les connaissons aujourd'hui en 1955 [9].

Le premier satellite artificiel de l'histoire, Spoutnik I, a été lancé par l'Union soviétique en 1957. Cela marque le début de la course à l'espace entre les États-Unis et l'URSS. Cependant, ce premier satellite n'avait pas de capacité de communication. Ce n'est que quelques années plus tard, en 1960, que les Américains ont lancé le premier satellite de communication, Echo I. Ce satellite a été utilisé pour réfléchir les signaux radio à travers le monde, ouvrant la voie à la communication mondiale par satellite.

La communication par satellite repose sur deux éléments principaux : le segment spatial, qui englobe le satellite équipé d'antennes et des circuits d'émission-réception, et le segment sol, qui comprend les stations terrestres de transmission et de réception. Ces stations sol, fixes ou mobiles, sont responsables de la transmission de signaux de communication entre les utilisateurs et le satellite en orbite, ainsi que de la gestion et du contrôle du satellite lui-même. Dans une liaison satellite conventionnelle, telle que celle illustrée dans la Figure I.1, la transmission d'un signal s'effectue depuis une station terrestre vers un satellite, ce qui correspond à la liaison ascendante. Le satellite reçoit ensuite le signal, l'amplifie et le retransmet vers une autre station terrestre, correspondant à la liaison descendante. Dans ce contexte, le satellite joue le rôle d'un répéteur, permettant de transmettre des signaux sur des distances plus longues que ce qui serait possible avec une liaison directe entre les deux stations terrestres.

En 1962, les Américains ont lancé le premier satellite de communication actif, Telstar, qui a permis la transmission en direct d'images télévisées à travers l'Atlantique. Cette technologie a été utilisée pour retransmettre les événements de la Coupe du monde de football de 1966 en direct à la télévision dans le monde entier [10].

En 1965, le satellite Early Bird (Intelsat I) a été lancé, devenant le premier satellite commercial de communication par satellite [11]. Cette innovation a permis de développer des réseaux de communication internationaux qui ont ouvert de nouvelles perspectives commerciales et ont accéléré la mondialisation.

En 1983, l'Organisation européenne des télécommunications par satellite (EUTELSAT) a lancé son premier satellite de communication à grande échelle, l'EUTELSAT I-F1 [12]. Grâce à ce satellite, les pays européens ont pu se connecter les uns aux autres et aux États-Unis, élargissant considérablement leur capacité de communication à l'échelle internationale.

La communication par satellite est aujourd'hui essentielle dans notre vie quotidienne, étant utilisée pour de multiples applications telles que la télévision, la téléphonie et l'internet. Des entreprises privées, comme SpaceX, OneWeb [13] et Blue Origin [14], sont également impliquées dans le lancement de satellites pour des applications commerciales, notamment pour fournir l'accès à internet haut débit dans les zones reculées et pour la surveillance de la Terre et de l'espace lointain. Un véritable réseau, ou constellation de satellites comme on l'appelle, est en plein essor. Cela pose de nouveaux défis et ouvre de nouvelles perspectives pour l'avenir de la communication par satellite et de l'exploration spatiale.

Figure I.1 : Schéma de liaison satellite conventionnelle

#### I.1.2. Les réseaux satellitaires

Les communications par satellite ont été initialement introduites pour répondre principalement aux besoins de diffusion des médias (téléphonie, télévision et internet), des applications de défense et plus récemment des applications de *backhauling* [15].

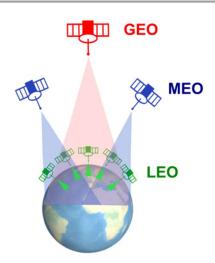

Ces services ont d'abord été exploités via des satellites géostationnaires pour offrir une couverture étendue. Un satellite positionné à une altitude de 35 786 km (orbite géostationnaire) au-dessus de la surface de la Terre reste immobile par rapport à la Terre. Cette orbite spécifique permet à une antenne terrestre de communiquer avec le satellite à tout moment sans avoir besoin de modifier sa position, car le satellite apparaît comme étant stationnaire dans le référentiel terrestre. Grâce à ces satellites GEO (Geostationary Earth Orbit), il est possible de desservir une zone régionale ou continentale sans avoir besoin de plusieurs satellites pour assurer une couverture continue.

Cependant, leur altitude élevée entraîne un important temps de latence dans les communications, car les signaux doivent parcourir une distance importante, ce qui peut causer des retards dans les communications en temps réel, comme les appels téléphoniques, la télévision ou plus récemment les jeux en ligne. Cette demande croissante de services à faible latence a poussé au développement de satellites en orbite plus basse que l'orbite géostationnaire : ce sont les satellites à défilement.

Les satellites MEO (*Medium Earth Orbit*) sont en orbite à une altitude d'environ 5 000 à 20 000 km au-dessus de la Terre, tandis que les satellites LEO (*Low Earth Orbit*) sont en orbite à une altitude comprise entre environ 320 et 1200 km. En conséquence, ils mettent moins de temps pour compléter une rotation autour de la Terre par rapport à la période de rotation de la Terre sur elle-même. Ils peuvent donc effectuer plusieurs tours de la Terre par jour et couvrir une zone plus restreinte pendant leur déplacement.

Dans ce contexte, l'idée d'une constellation de satellites pour pallier cet inconvénient est de plus en plus explorée ces dernières années. La Figure I.2 montre les trois types de satellites et leur trajectoire autour de la planète, tandis que la Figure I.3 illustre certaines caractéristiques propres à chaque type de constellation, telles que leur altitude, leur zone de couverture, leur latence, leur vitesse, leur puissance, etc.

Figure I.2 Types de satellites : GEO (en haut), MEO (au milieu) et LEO (en bas)

|                                                      | GEO          | MEO            | LEO        |

|------------------------------------------------------|--------------|----------------|------------|

| Altitude (km)                                        | 35 786       | 5 000 ~ 20 000 | 320 ~ 1200 |

| Nombre de satellites pour<br>une couverture mondiale | 3            | 6              | > 100      |

| Zone de couverture                                   | Continentale | Régionale      | Locale     |

| Latence (ms)                                         | > 450        | 25 ~ 450       | 3 ~ 30     |

| Vitesse de suivi                                     | Stationnaire | ~ 1 heure      | < 10min    |

| Puissance                                            | Haute        | Moyenne        | Faible     |

| Taille                                               | Grand        | Moyenne        | Petit      |

Figure I.3 : Types de satellites et leurs caractéristiques

Les constellations dédiées à la navigation, comme le GPS américain et le concurrent européen Galileo, ainsi que celles consacrées à la téléphonie, comme Iridium [16] et Globalstar [17], sont des exemples des constellations MEO et LEO qui sont largement utilisées de nos jours. Bien que l'utilisation de plusieurs satellites dans une constellation permette de couvrir une zone plus étendue, elle peut également rendre plus difficile la gestion du trafic de données. En effet, des problèmes de *hand-over*, qui se produisent lorsqu'un utilisateur passe d'un satellite à un autre en cours de communication, peuvent se poser.

Les constellations LEO les plus récentes peuvent fournir des services à large bande pour la téléphonie 5G, avec une latence aussi faible que 3 ms, grâce à leur altitude aussi basse que 320 km [18]. De plus, ce méga-constellations LEO peuvent avoir des exigences moins contraignantes en termes de puissance isotrope rayonnée équivalente (PIRE), G/T et de domaine de balayage par rapport à leurs homologues GEO, ce qui se traduit par une réduction significative des coûts et de la taille du terminal utilisateur.

Cependant, le fait de se déplacer à grande vitesse et de ne pas pouvoir assurer une couverture optimale d'une zone donnée que pendant une durée limitée pose d'autres exigences strictes en termes d'antenne. En particulier, les antennes doivent être agiles et capables de diriger leur faisceau principal sur un large champ de vision (nombre de satellites). De plus, le coût élevé du déploiement de ces constellations, en raison du grand nombre de satellites à lancer, peut s'avérer être un facteur limitant. Dans ce contexte, les satellites MEO peuvent offrir un meilleur compromis entre la latence, le coût et la complexité.

Avec des constellations déjà pleinement opérationnelles [19] et le lancement de milliers de satellites prévu au cours des prochaines années, ces constellations offriront d'importantes opportunités de marché pour l'industrie, qui attirent à leur tour de nouveaux investissements publics et privés. La forte demande de services SATCOM est en parfait accord avec l'évolution de l'industrie des semi-conducteurs, qui se caractérise par la miniaturisation des dispositifs et la réduction des coûts de fabrication. Cette croissance stimule le développement de nouvelles antennes à dépointage électronique dans les bandes Ka, permettant ainsi une adaptation plus souple aux besoins des utilisateurs et une meilleure efficacité spectrale.

En effet, la bande Ka dispose d'une capacité accrue de débit, grâce à l'usage de la diversité spatiale et de la réutilisation des fréquences, qui permettront d'une part de répondre au besoin en capacité de ces services, et d'autre part de diminuer significativement le coût de transmission.

### I.2. Antennes à dépointage électronique

Au cours de la dernière décennie, l'industrie des communications sans fil a connu une croissance énorme en raison de l'augmentation de la demande d'appareils de communication sans fil. Il est donc important de pouvoir rester connecté en permanence pour répondre à une demande croissante des consommateurs qui, de plus en plus, font face à de grandes quantités de données et avec des débits très élevés.

En effet, les services de télécommunications par satellites avec des terminaux mobiles (SOTM : SATCOM On The Move) terrestres, maritimes, aériens et les services de connectivité aéronautique (IFC : In-Flight Connectivity) ont tendance à exploser. Ces services requièrent des terminaux embarqués compacts, flexibles, économiques et fiables, qui puissent supporter des conditions environnementales difficiles tout en prenant peu de place. Ces terminaux doivent être équipés d'une antenne plate mobile de taille minimale, leur permettant de dépointer vers un satellite faisant partie d'une constellation et de fournir des communications haut débit pour différents types de systèmes de transport.

Au début, les antennes utilisées pour assurer ces services étaient des réflecteurs paraboliques montés sur un positionneur mécanique (Figure I.4a). Ces antennes sont largement utilisées pour les stations terrestres de communication par satellite en raison de leur conception bien maîtrisée et de leurs bonnes performances. Toutefois, la présence d'un radôme autour de ce type d'antenne a un impact négatif sur l'aérodynamisme des terminaux mobiles. Cela devient encore plus préoccupant pour les applications aéronautiques, car la consommation de carburant est considérablement augmentée. Plus tard, des réseaux passifs montés sur un positionneur ont été développés pour améliorer l'encombrement de ces systèmes (Figure I.4b).

(a) Antenne à réflecteur [20]

(b) Réseau passif Ku/Ka bande [21]

Figure I.4 : Antennes à positionneur mécanique

Grâce aux avancées technologiques alliées à la baisse des coûts, il a été possible de concevoir des réseaux d'antennes à dépointage électronique. Ces antennes présentent de nombreux avantages par rapport aux antennes sur positionneur, tels que la possibilité d'utiliser plusieurs faisceaux, un changement instantané d'angle de dépointage, une plus grande résistance à l'usure mécanique et une faible perturbation aérodynamique.

Les antennes à dépointage électronique sont aujourd'hui la solution optimale pour le suivi des satellites, en particulier lorsqu'une opération fiable et agile est souhaitée. En effet, la technique de dépointage électronique est particulièrement avantageuse pour les systèmes SOTM et IFC, qui nécessitent des antennes plates pouvant rapidement se réorienter vers le satellite pour compenser le mouvement de la plateforme. Avant de passer à la discussion sur l'état de l'art des systèmes d'antenne à dépointage électronique, le principe de fonctionnement et les types d'architectures seront brièvement exposés ci-dessous.

### I.2.1. Dépointage électronique : Principe

La technique de dépointage électronique, également connue sous le nom de formation de faisceau électronique, trouve ses racines au début du XXème siècle avec les travaux de Karl Ferdinand Braun. Cette technique est devenue particulièrement intéressante pour le secteur militaire à l'époque et a été stimulée pendant la Seconde Guerre mondiale avec l'apparition des premiers systèmes RADAR (*Radio Detection and Ranging*).

Le dépointage électronique est réalisé en utilisant des réseaux d'antennes comportant plusieurs éléments d'antenne, chacun ayant un contrôle sur le signal qui leur parvient. Le dépointage du faisceau peut être atteinte en retardant le signal de chaque élément individuel de manière qu'ils s'additionnent de manière constructive dans la direction choisie  $\theta$ .

Supposons que le signal dans le nième élément soit retardé de  $(N-1)\tau$  avec un espacement d entre les éléments d'antenne (Figure I.5), le signal transmis par tous les éléments aurait des retards différents entre eux. En utilisant une construction géométrique (Figure I.6), il est possible de calculer le décalage temporel  $\tau$  entre chaque élément du réseau à partir du décalage spatial L et de la célérité c de l'onde :

$$\tau = \frac{L}{c} = \frac{d \cdot \sin(\theta)}{c} \tag{E-1}$$

En effet, le temps de retard nécessaire pour orienter le faisceau est égal au temps nécessaire pour que le front d'onde traverse cette distance *L*. En appliquant un retard approprié à chaque voie, il est donc possible d'orienter le faisceau de l'antenne dans la direction souhaitée, permettant ainsi la réalisation d'un dépointage électronique.

Ce principe peut être étendu à un réseau d'antennes à deux dimensions, permettant de dépointer le faisceau sur deux axes orthogonaux  $(\theta, \phi)$  pour atteindre n'importe quelle position dans le ciel Figure I.7. Cette technique est valable aussi bien en réception qu'en transmission grâce à la réciprocité des antennes.

Figure I.5 : Réseau d'antennes à N éléments avec retard temporel

Figure I.6: La dérivation du retard temporel

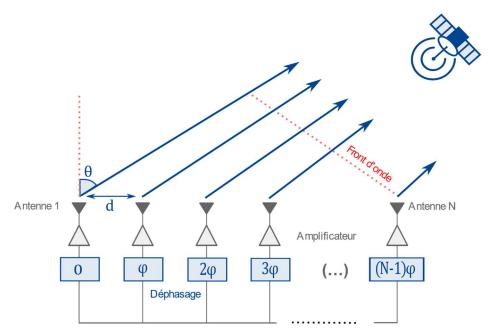

Bien que des solutions pour implémenter de retards temporels constants appliqués sur les différentes voies (TTD : *True Time Delay*) existent, la plupart des architectures analogiques sont souvent contraintes d'utiliser des déphaseurs pour ajuster les phases des signaux plutôt que d'appliquer ces retards. En effet, pour les signaux à bande étroite, les retards temporels peuvent être approximés par des déphasages. Si nous considérons L comme une fraction de la longueur d'onde, alors un décalage de phase pourrait être substitué à ce retard temporel. En utilisant cette approche, le dépointage électronique peut être réalisé en ajustant les phases de chaque voie pour générer un faisceau directionnel dans une direction spécifique. On utilise donc une antenne réseau à N éléments, tel qu'illustré dans la Figure I.8, d'une façon que le signal appliqué à chaque élément de l'antenne est déphasé de manière progressive : le signal du nième élément dans ce réseau subit un décalage de phase de  $(N-1)\varphi$ .

Figure I.7 : Dépointage du faisceau sur deux axes orthogonaux

Figure I.8 : Réseau d'antennes à N éléments avec décalage de phase

Dans ce cadre, l'équivalent de l'équation ( (E-1) destinée à calculer le déphasage relatif entre deux éléments consécutifs du réseau pour dépointer le faisceau d'un angle  $\theta$  dépend du nombre d'onde k, et donc de la longueur d'onde  $\lambda$  considérée :

$$\beta = k \cdot d \cdot \sin(\theta) = \frac{2\pi}{\lambda} \cdot d \cdot \sin(\theta)$$

(E-2)

L'espacement entre les éléments du réseau d'antennes, représenté par d, a également un impact sur le diagramme de rayonnement de l'antenne. Quand on dépointe, si cet espacement dépasse la demi-longueur d'onde, des lobes de rayonnement multiples apparaissent dans le diagramme de rayonnement, avec une magnitude similaire à celle du lobe principal (*Grating lobes*). Ces lobes sont indésirables car ils transmettent de l'énergie dans une direction non souhaitée, ce qui entraîne une perte de signal et peut également causer des interférences avec les signaux d'autres utilisateurs.

L'utilisation de déphaseurs est efficace pour les systèmes à bande passante étroite, mais leur efficacité diminue pour les systèmes à bande passante très large. En effet, en raison de la variation de la longueur d'onde au sein de la bande de fréquences, un déphasage constant ne produit pas un retard temporel constant. Cela peut entraîner une dérive fréquentielle de l'angle de dépointage, qui limite la bande passante instantanée du système et provoque une divergence du faisceau, appelée *beam squint*. Pour pallier ce problème, des solutions de traitement de signal numérique en temps réel peuvent être utilisées.

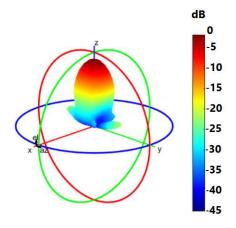

De plus, lorsque l'antenne est dépointée, les performances de la communication peuvent être dégradées. En effet, la théorie des réseaux d'antennes montre que le diagramme de rayonnement d'un réseau d'antennes est le produit du diagramme élémentaire des éléments rayonnants et du facteur de réseau. Dans le cas d'une antenne réseau plane, la directivité maximale est limitée par le diagramme élémentaire de l'élément rayonnant unitaire, qui suit une loi en cosinus, ce que diminue la directivité de l'antenne à mesure que le faisceau s'éloigne du zénith (Figure I.9). Cela rend les angles de dépointage élevés inexploitables et limite généralement le dépointage maximal des systèmes à environ ±70°.

Figure I.9 : Diagramme de rayonnement normalisé d'un réseau d'antennes de 64 éléments en fonction du dépointage (rouge 0°, bleu 15°, vert 30°, violet 45°, orange 60°, marron 75°)

# I.2.2. Architectures pour la formation de faisceau

Le choix de la technique de formation de faisceau exerce une influence considérable sur l'architecture du système. En plus des solutions de formation de faisceau entièrement analogiques [22]–[24] ou numériques [25]–[27], diverses topologies de formation de faisceau hybrides avec des différences sur la partie analogique/numérique sont trouvées dans la littérature [28]–[30].

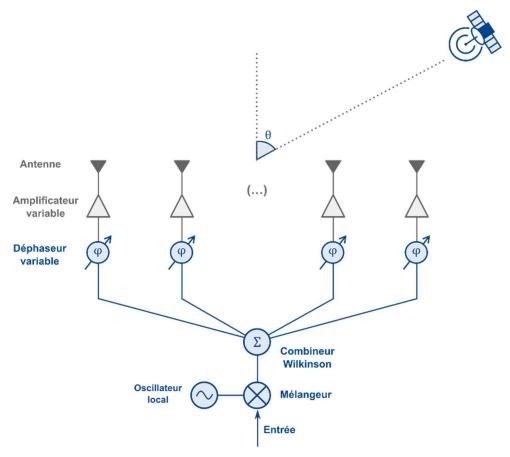

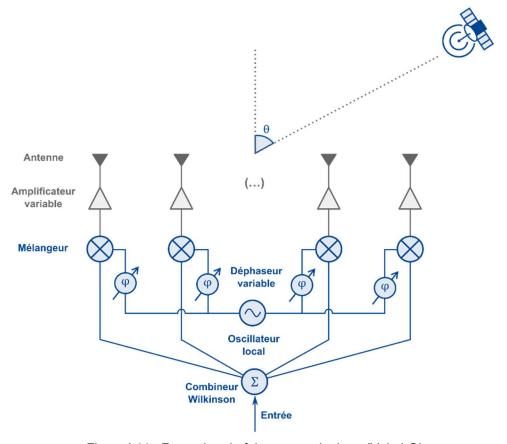

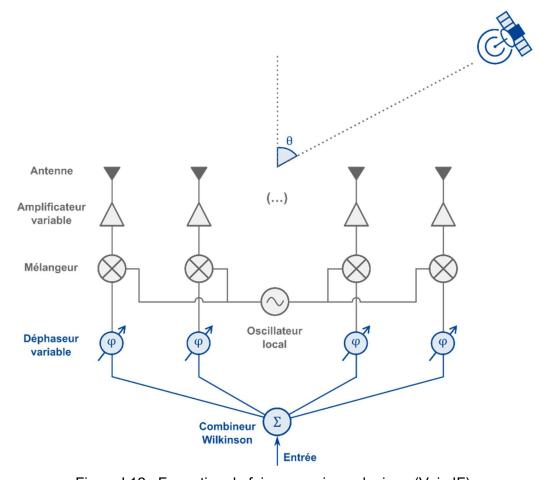

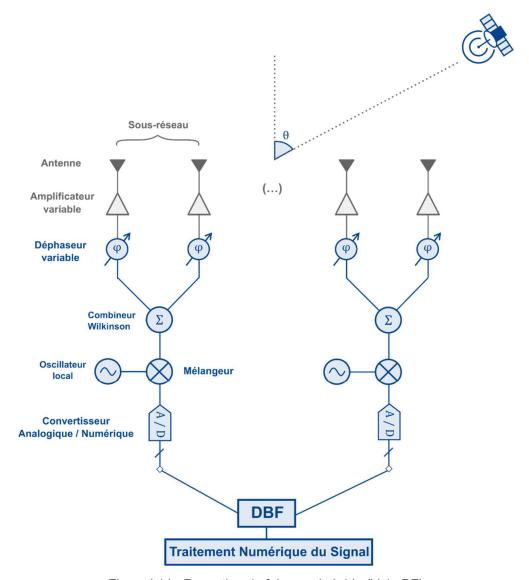

La méthode la plus simple parmi les architectures, consiste à combiner les signaux des différentes voies de manière analogique (ABF : *Analog Beamforming*). En effet, les ABF sont largement utilisés dans les systèmes d'antenne réseaux dans lesquels les signaux aux éléments rayonnants sont manipulés en amplitude et en phase par des circuits analogiques. Selon l'endroit où le déphaseur est implémenté dans ce système, Il est courant de distinguer trois types de formation de faisceau analogique: déphasage sur la voie radiofréquence (RF *Phase Shifting*) [31]–[35], sur la voie de l'oscillateur local (LO *Phase Shifting*) [22], [36], [37] et sur la voie de la fréquence intermédiaire (IF *Phase Shifting*) [38]–[41].

Dans cette première architecture, dans le cas de la transmission (Figure I.10), le signal en fréquence intermédiaire est transposé à la fréquence RF à l'aide d'un mélangeur et d'un oscillateur local, avant d'être divisé en plusieurs voies. Chaque élément rayonnant est équipé d'un amplificateur et d'un déphaseur, ce qui permet le contrôle de l'amplitude et de la phase des signaux sur chaque voie. Bien que cette configuration soit très courante, principalement en raison du faible nombre de circuits nécessaires par rapport aux autres architectures ABF [42], elle présente un inconvénient majeur lié à la complexité de l'intégration du déphaseur aux fréquences millimétriques. De plus, le dépointage électronique exclusivement dans le domaine RF s'avère être un fardeau important lors de la conception de systèmes d'antennes multifaisceaux, car le nombre de circuits nécessaires pour la formation de faisceau analogique augmente en proportion du nombre de faisceaux qu'il doit prendre en charge.

Dans la deuxième solution (Figure I.11), les pertes et les non-linéarités des déphaseurs ont moins d'impact sur la performance en transmission, ce qui allège les contraintes liées à sa conception. En effet, le déphasage sur la voie LO a un impact minimal sur le rapport signal à bruit (SNR) et le gain du système, car les exigences de bruit et de linéarité sur l'oscillateur local sont plus faciles à respecter [43]. Cependant, cette configuration nécessite un grand nombre de mélangeurs, en plus des déphaseurs, ce qui impacte sur la complexité du routage et sur la consommation totale.

Figure I.10 : Formation de faisceau analogique (Voie RF)

Figure I.11 : Formation de faisceau analogique (Voie LO)

Enfin, dans la dernière architecture (Figure I.12), un mélangeur est placé sur chaque voie en amont du déphaseur, ce qui augmente la consommation électrique et la surface du circuit. Néanmoins, la conception du déphaseur en fréquences intermédiaires est mieux maîtrisée.

Bien que la formation de faisceau analogique offre une bonne capacité à réaliser des réseaux d'antennes à faisceau unique, avec une complexité et une consommation d'énergie relativement faibles, elle pose des défis lors de la conception de systèmes d'antennes multifaisceaux. En effet, le nombre de réseaux de déphaseur doit être le même que le nombre de faisceaux indépendants souhaités [44].

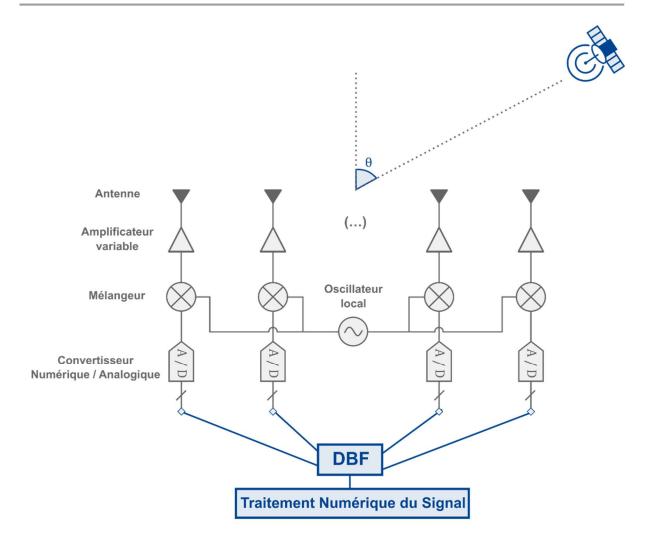

Dans ce cas, la formation de faisceau numérique (DBF: Digital Beamforming) peut être plus attractive puisqu'elle déplace entièrement la fonction de contrôle du faisceau vers la partie numérique à l'aide de convertisseurs numérique-analogique/analogique-numérique (CNA/CAN) (Figure I.13). Cela peut simplifier le circuit RF, qui ne nécessite plus qu'un amplificateur et un mélangeur pour la transmission/réception (aucun déphaseur n'est nécessaire). En effet, puisque chaque voie est numérisée dans cette architecture, les retards temporels peuvent être utilisés, contrairement au cas de la formation de faisceau analogique.

Bien que cette solution devienne de plus en plus attractive pour des applications à large bande et/ou multifaisceaux, elle n'est pas encore bien adaptée aux applications à fréquences millimétriques en raison de son coût élevé, la difficulté à transposer et de sa consommation importante de composants. Pour ces raisons, la formation de faisceaux analogiques est aujourd'hui préférée dans de nombreuses applications d'un point de vue performance/économie.

Figure I.12 : Formation de faisceau voie analogique (Voie IF)

Figure I.13 : Formation de faisceau numérique

Il existe également un troisième groupe de techniques de formation de faisceaux, basé sur un traitement conjoint analogique et numérique, dont l'architecture dépend des propriétés du canal de propagation [15]. On parle de la formation de faisceau hybride (HBF: *Hybrid Beamforming*).

Ces architectures peuvent représenter un compromis intéressant entre la complexité du système et sa performance, par rapport aux architectures précédentes. L'architecture HBF à sous-réseaux, illustrée dans la Figure I.14, est couramment utilisée en raison de son compromis performance/coût. Dans cette configuration, l'antenne est divisée en sous-réseaux qui sont recombinés de manière analogique. Le signal numérique est traité en bande de base (déphasage/combinaison) et puis converti en signal analogique à l'aide des convertisseurs et mélangeurs.

Les formateurs de faisceau hybrides sont une solution prometteuse pour les systèmes multifaisceaux de téléphonie 5G et 6G [45]–[47], car les efforts de traitement des données, et donc la consommation d'énergie globale, sont significativement réduits par rapport à leurs contreparties entièrement numériques. Cependant, ces architectures ne sont actuellement pas largement déployées dans les systèmes d'antennes multifaisceaux pour les terminaux SATCOM nécessitant à la fois un suivi et des transferts (hand-over) de satellite à satellite pour maintenir la connectivité [48].

Figure I.14: Formation de faisceau hybride (Voie RF)

Pour choisir l'architecture mieux adaptée à une application, les concepteurs doivent se baser sur les spécifications techniques du système. En effet, les spécifications prédéfinies telles que le nombre d'éléments du réseau, le coût, la consommation électrique ou même la complexité de l'architecture, orienteront le choix vers l'une des architectures décrites précédemment.

#### 1.2.3. État de l'art des systèmes existants et en développement

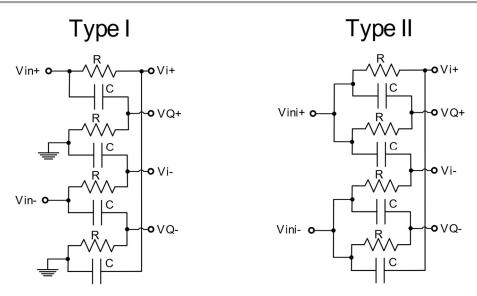

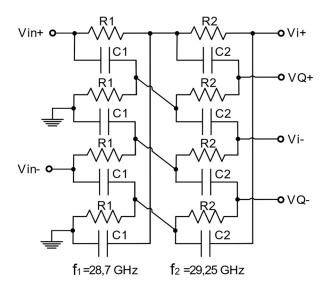

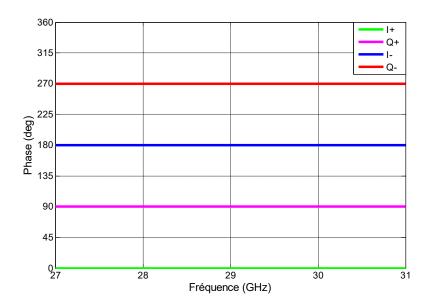

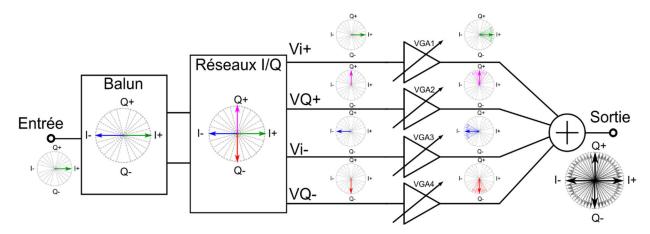

Il existe plusieurs topologies de réseaux d'antennes pour le dépointage électronique dont les antennes à rayonnement direct (DRA : *Direct Radiating Array*) sont les plus maîtrisées et couramment utilisées.