## Characterization of low thermal budget silicon MOSFETs for Digital and High frequency application on 3D sequential integration systems

Tadeu Mota Frutuoso

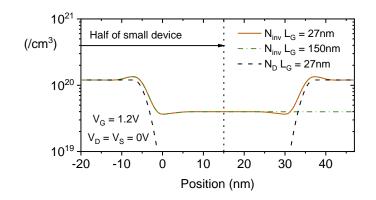

### ▶ To cite this version:

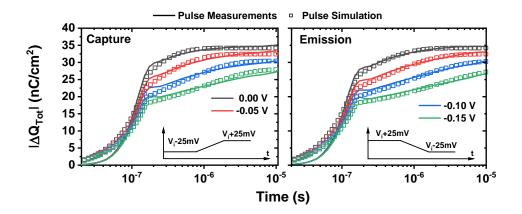

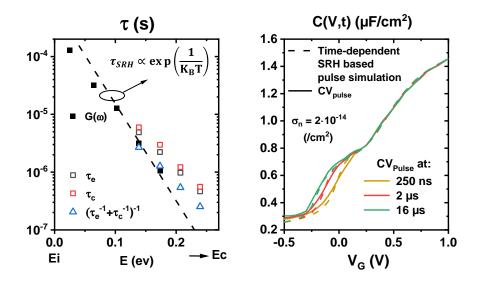

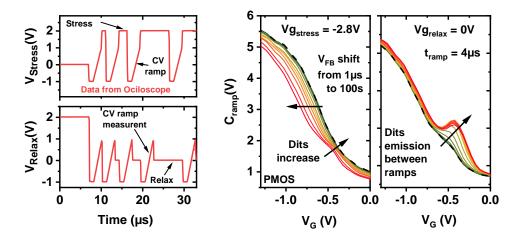

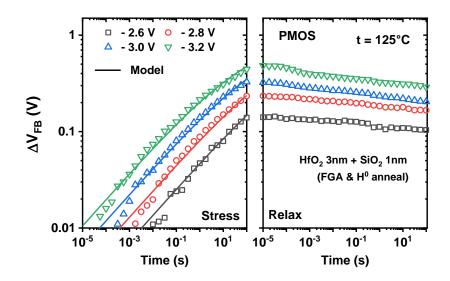

Tadeu Mota Frutuoso. Characterization of low thermal budget silicon MOSFETs for Digital and High frequency application on 3D sequential integration systems. Micro and nanotechnologies/Microelectronics. Université Grenoble Alpes [2020-..], 2023. English. NNT: 2023GRALT054. tel-04543962

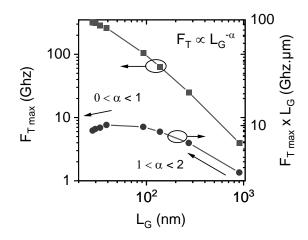

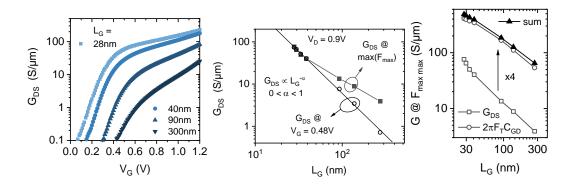

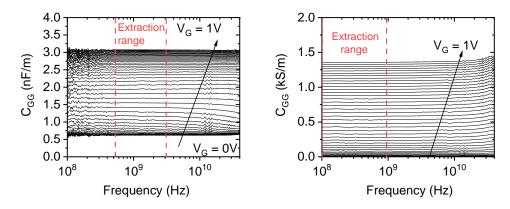

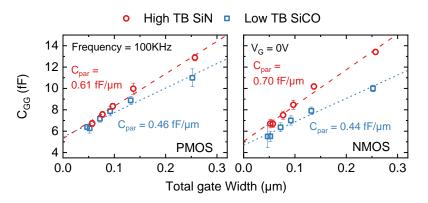

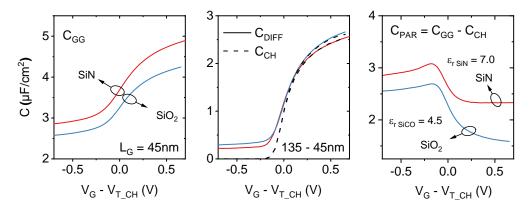

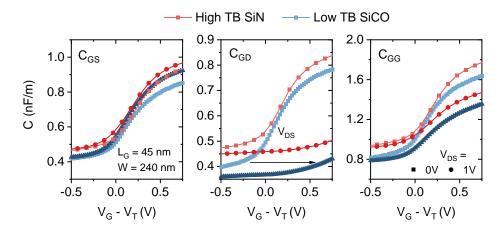

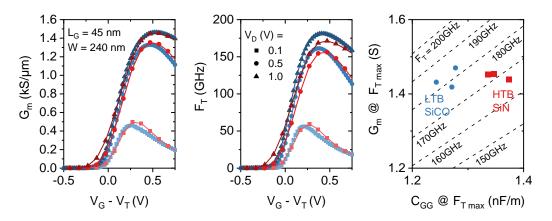

## HAL Id: tel-04543962 https://theses.hal.science/tel-04543962v1

Submitted on 12 Apr 2024  $\,$

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés. THÈSE

Pour obtenir le grade de

### DOCTEUR DE L'UNIVERSITÉ GRENOBLE ALPES

École doctorale : EEATS - Electronique, Electrotechnique, Automatique, Traitement du Signal (EEATS) Spécialité : Nano électronique et Nano technologies Unité de recherche : Laboratoire d'Electronique et de Technologie de l'Information (LETI)

## Caractérisation des mosfets en silicium à budget thermique réduit pour applications numériques et haute fréquence sur des systèmes d'intégration séquentielle 3D

## CHARACTERIZATION OF LOW THERMAL BUDGET SILICON MOSFETS FOR DIGITAL AND HIGH FREQUENCY APPLICATION ON 3D SEQUENTIAL INTEGRATION SYSTEMS

Présentée par :

### **Tadeu MOTA FRUTUOSO**

### Direction de thèse :

Philippe FERRARI

Directeur de thèse

Professeur des universités, Université Grenoble Alpes

Directeur de thèse

José LUGO ALVAREZ

Co-encadrant de thèse

CEA-Leti

Co-encadrant de thèse

Xavier GARROS

Co-encadrant de thèse

Ingénieur HDR CEA-E5, CEA

Co-encadrant de thèse

### Rapporteurs :

Jean-Pierre RASKIN PROFESSEUR, Université Catholique de Louvain Jean-Michel SALLESE SENIOR SCIENTIST, Ecole Polytechnique Fédérale de Lausanne

### Thèse soutenue publiquement le 27 septembre 2023, devant le jury composé de :

| Philippe FERRARI                                                   | Directeur de thèse |

|--------------------------------------------------------------------|--------------------|

| PROFESSEUR DES UNIVERSITES, Université Grer                        | noble Alpes        |

| Florence PODEVIN                                                   | Présidente         |

| PROFESSEURE DES UNIVERSITES, Université Gre                        | enoble Alpes       |

| Jean-Pierre RASKIN<br>PROFESSEUR, Université Catholique de Louvain | Rapporteur         |

| Jean-Michel SALLESE                                                | Rapporteur         |

| SENIOR SCIENTIST, Ecole Polytechnique Fédérale                     | de Lausanne        |

### Invités :

Xavier Garros directeur de recherche CEA, CEA-LETI Chevalier Pascal INGENIEURE DOCTEUR, STMicroelectronics

# CHARACTERIZATION OF LOW THERMAL BUDGET SILICON MOSFETS FOR DIGITAL AND HIGH FREQUENCY APPLICATION ON 3D SEQUENTIAL INTEGRATION SYSTEMS

Tadeu Mota Frutuoso

**Xavier GARROS**

Jose LUGO

**Philippe FERRARI**

University of Grenoble Alpes 2023

Tadeu Mota Frutuoso - Characterization and optimization of low thermal budget silicon MOSFETs for Digital and High frequency application on 3D sequential integration systems

## Abstract

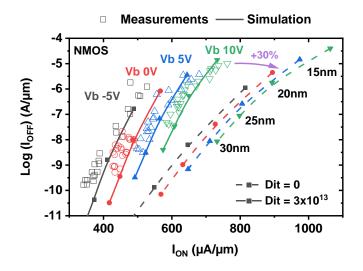

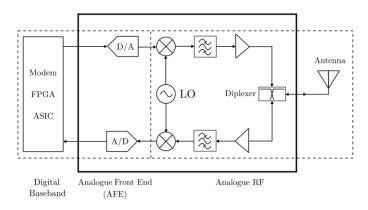

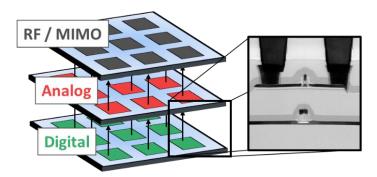

3D sequential integration (3DSI) consists of sequentially stacking active device layers using vertical interconnections with similar dimensions as standard Back-End-Of-Line contacts (<100nm). It allows the co-integration of different systems on separated layers with a high interconnection density and it eliminates costly trade-offs coming from the optimization of different devices on the same substrate. Likewise, the reduced interconnection parasitic and heterogeneous integration offer great potential for 5G millimeter-wave (mmW) applications.

However, 3D stacked devices come along with new process challenges. Top-tier transistors need to be processed at low temperatures ( $\leq 500^{\circ}$ C) to preserve the integrity of devices on lower tiers. Standard CMOS integration with low thermal budget (LTB) leads to substantial performance degradation. Nevertheless, new breakthroughs in the silicon LTB integration process open the path to the development of devices that reach the same performance of their high temperature counterparts. Therefore, the objective of this Ph.D. work is to analyze the effects of those new processes on the electrical characteristics of LTB MOSFET devices and draw guidelines for further optimization.

The manuscript for this Ph.D. introduces the main results obtained from the recent development of this technology and it is presented on three parts:

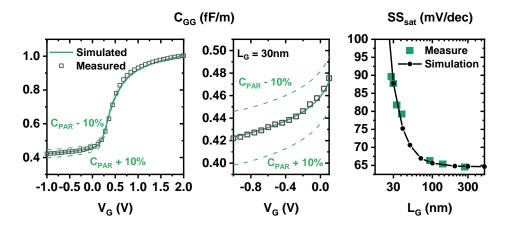

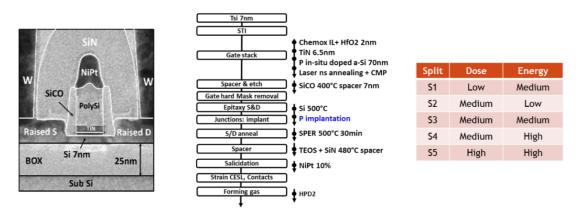

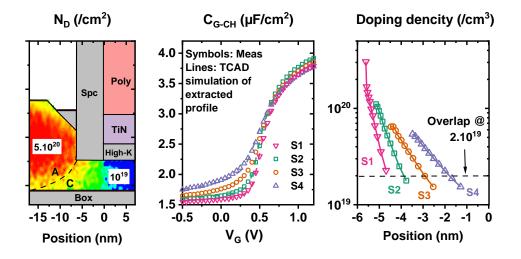

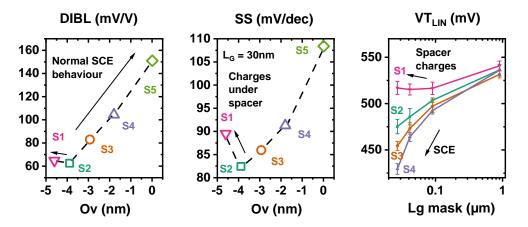

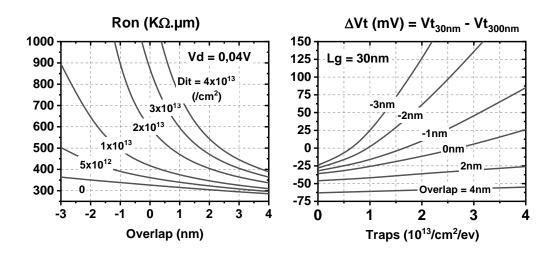

Activation of source and drain dopants near the junction using a low temperature Solid State Epitaxy Recrystallization (SPER) anneal. The study is performed with an estimation of the junction profile using a novel nondestructive CV technique coupled to as improved conformal mapping model of the transistors fringe capacitances. The results are used to understand the electrical behavior and degradation mechanisms of the devices as function of the overlap position.

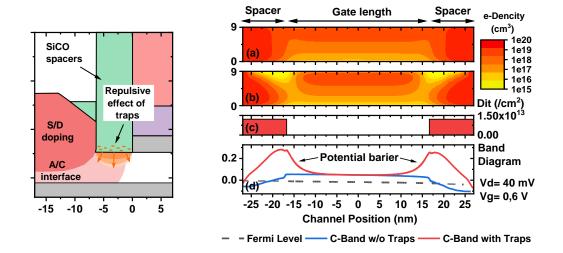

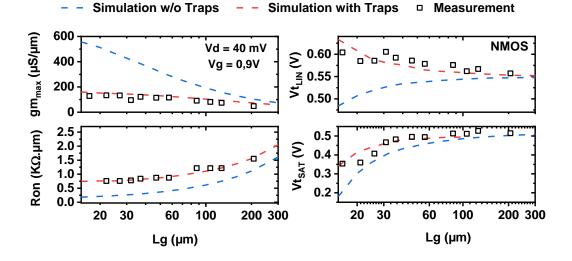

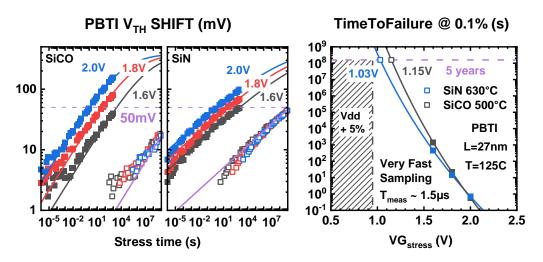

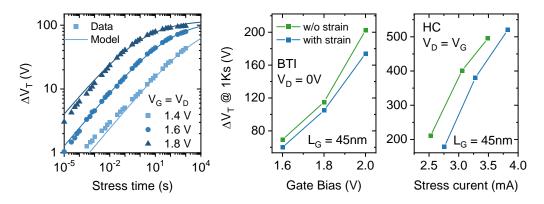

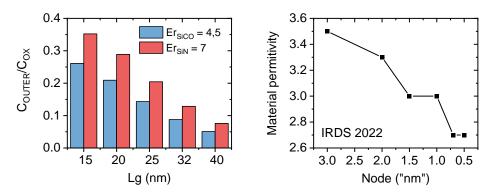

Trapping properties of the low permittivity material (SiCO) used for the low temperature gate spacer oxide and its effects on the transistor performance. Two trapping mechanisms are identified on this material: Fast Silicon interface traps, related to the quality of the native oxide, and slow deep defects distributed in the bulk of the SiCO oxide. The effect of those traps near the access region of the electrical performance transistor are studied.

Tadeu Mota Frutuoso - Characterization and optimization of low thermal budget silicon MOSFETs for Digital and High frequency application on 3D sequential integration systems

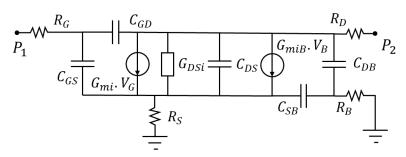

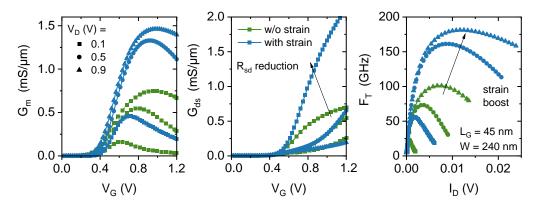

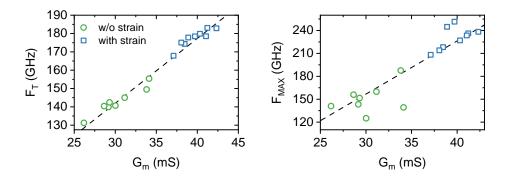

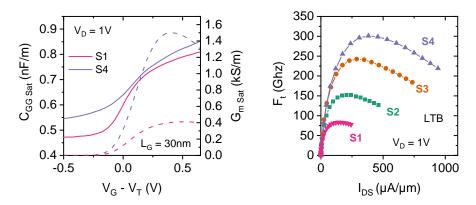

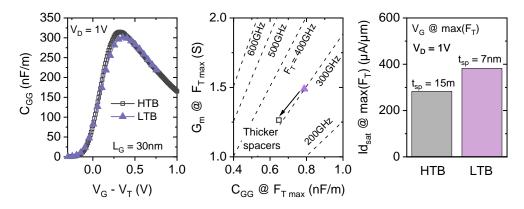

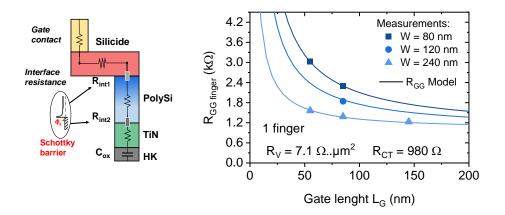

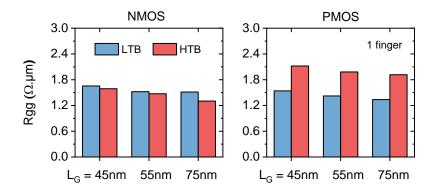

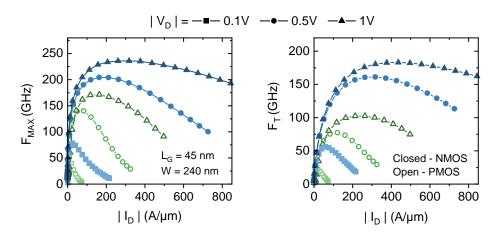

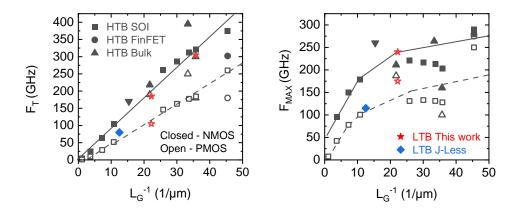

Effect of key low temperature process steps of the devices RF FoMs. The objective is to evaluate the performance of the devices at high frequencies. The lower parasitic capacitances from SiCO spacers, low gate resistance from the UV nanoseconds laser anneal and high mobility from the CESL tensile stain are key low thermal budget steps contributing to high-performance RF transistors with similar FoMs to HTB counterparts.

### Table des matières

| Chap | pter 1: Introduction                                                                                                                                               | 9              |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 1.1  | <ul><li>3D Sequential Integration</li><li>1.1.1 Context for 3D integration</li><li>1.1.2 Monolithic 3D integration</li></ul>                                       | 9              |

|      | 1.1.2 Mononunc SD integration         1.1.3 FD-SOI Transistor                                                                                                      |                |

| 1.2  | LTB MOSFET Fabrication<br>1.2.1 Description of the 28nm Integration process<br>1.2.2 Extension-first vs Extension-Last<br>1.2.3 Low vs High thermal budget process | 15<br>21       |

| 1.3  | Purpose of this thesis                                                                                                                                             | 24             |

| Chap | oter 2: Characterization and Optimization of the Junctions                                                                                                         | 26             |

| 2.1  | Electrical characteristics of the access region                                                                                                                    |                |

| 2.2  | <ul> <li>Active Junction Profile Extraction methodology</li></ul>                                                                                                  | 35<br>38<br>43 |

| 2.3  | Study of LTB devices                                                                                                                                               | 48             |

|      | 2.3.1 Phosphorous implant effects on NMOS devices                                                                                                                  | 48             |

|      | 2.3.2 Effects of etching of the sacrificial oxide on NMOS devices                                                                                                  |                |

|      | <ul><li>2.3.3 Effect of germanium amorphization on PMOS devices</li><li>2.3.4 X-first without amorphization</li></ul>                                              |                |

| 2.4  | Impact of the junction profile on device reliability.                                                                                                              | 59             |

| 2.5  | Conclusion                                                                                                                                                         | 65             |

| 2.6  | References                                                                                                                                                         | 67             |

| Chap | oter 3: Characterization of low-K spacer Oxides                                                                                                                    | 68             |

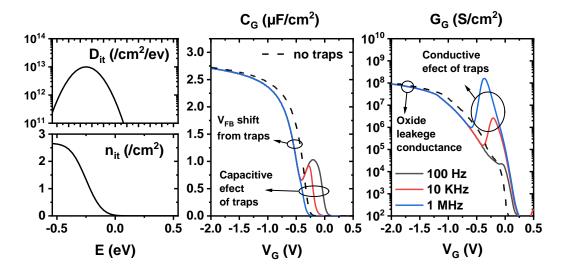

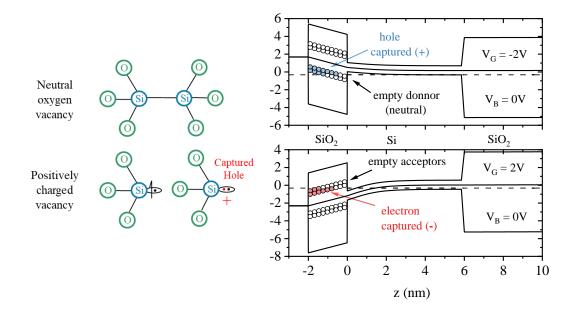

| 3.1  | Trap characterization                                                                                                                                              | 69             |

|      | 3.1.1 Interface traps                                                                                                                                              |                |

|      | 3.1.2 Oxide traps                                                                                                                                                  |                |

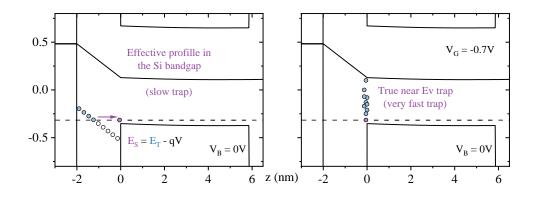

|      | 3.1.3 Slow oxide border traps vs fast Near-Band Si traps                                                                                                           |                |

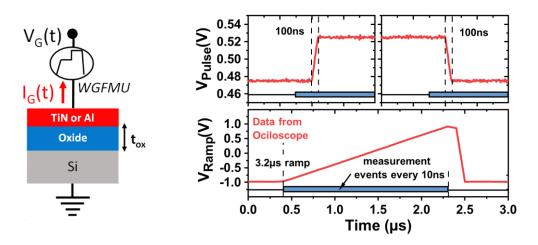

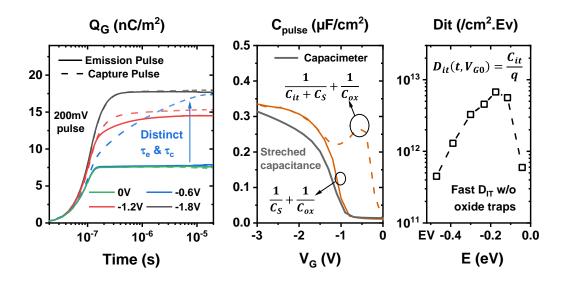

| 3.2  | Ultra fast CV methods                                                                                                                                              |                |

|      | <ul><li>3.2.1 Ultra-Fast CV measurement patterns</li><li>3.2.2 Interface States Spectroscopy using pulsed pattern</li></ul>                                        |                |

|      | 3.2.3 BTI reliability using ramp pattern                                                                                                                           |                |

| 3.3  | Low temperature spacer material                                                                                                                                    | 86             |

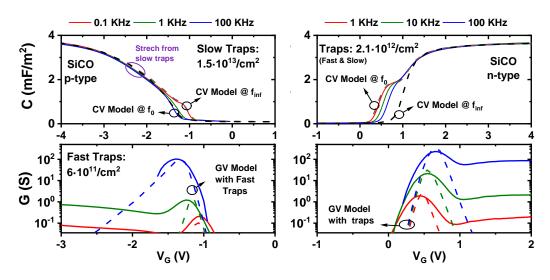

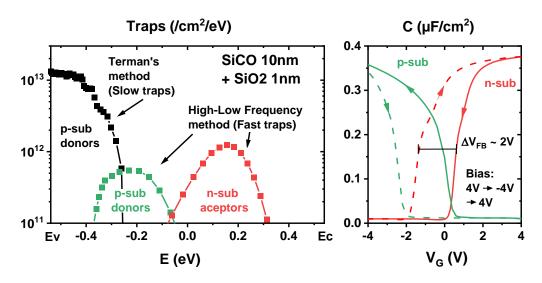

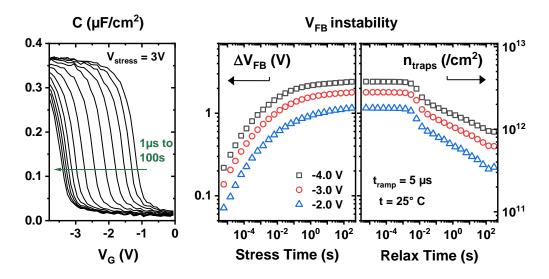

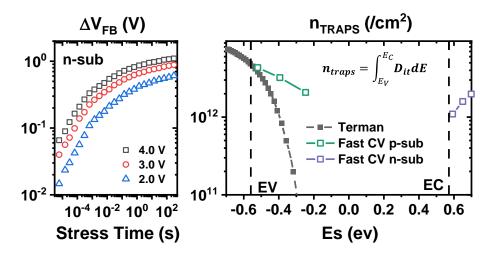

|      | 3.3.1 SiCO trapping properties                                                                                                                                     | 86             |

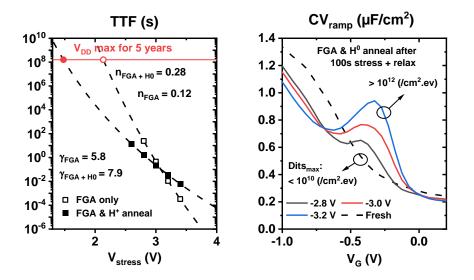

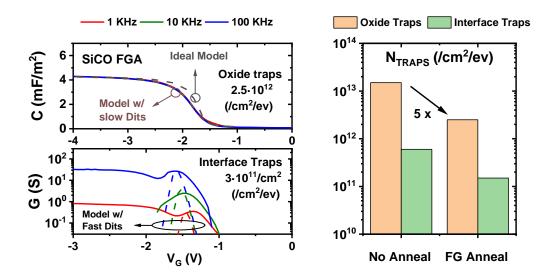

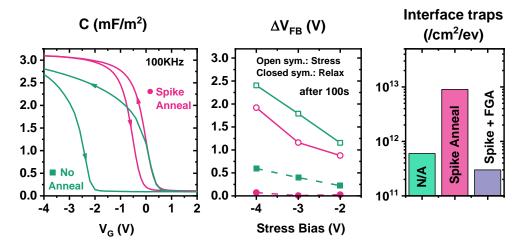

|      | 3.3.2 Annealing effects on SiCO oxides                                                                                                                             |                |

|      | 3.3.3 Conclusion on SiCO trapping properties                                                                                                                       | 95             |

| 3.4  | Effects of spacer charges on device performance                                                                                                                    |                |

|      | 3.4.1 Impact on transistor IV performance                                                                                                                          |                |

|      | 3.4.2 Impact on transistor BTI performance 1                                                                                                                       | 01             |

6 Tadeu Mota Frutuoso - Characterization and optimization of low thermal budget silicon MOSFETs for Digital and High frequency application on 3D sequential integration systems

| 3.5           | Conclusion            |                                                                                                                                                                   |            |

|---------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 3.6           | References            |                                                                                                                                                                   |            |

| Chaj<br>devie | pter 4:<br>ces        | High Frequency performance of Low Thermal Budget 105                                                                                                              |            |

| 4.1           | Introduct             | ion                                                                                                                                                               | 105        |

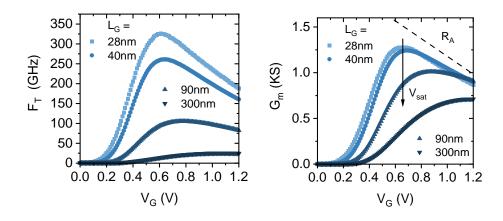

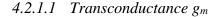

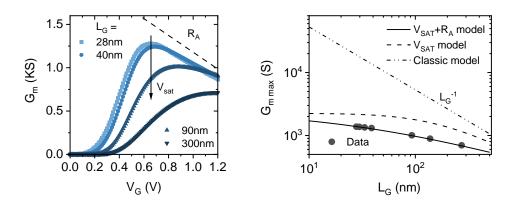

| 4.2           | 4.2.1 Ft f            | es of Merit<br>requency<br>x frequency                                                                                                                            | 109        |

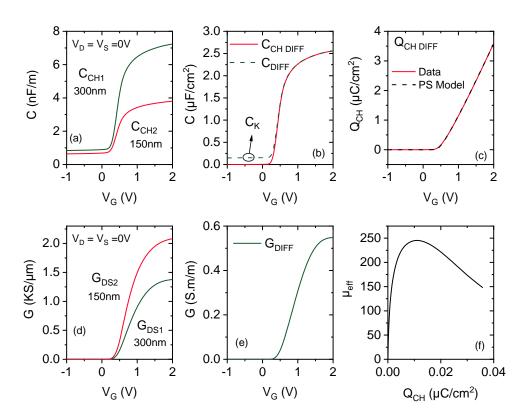

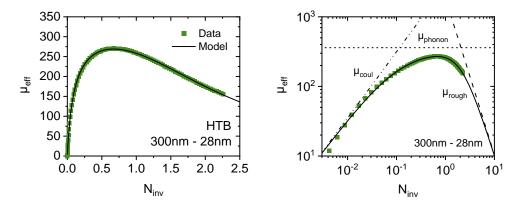

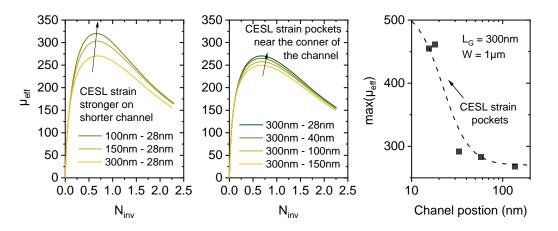

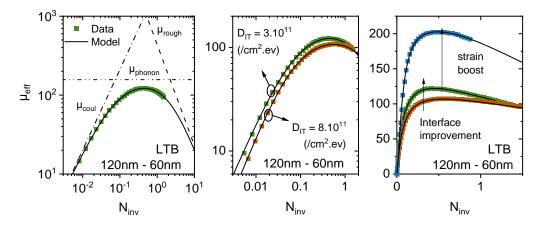

| 4.3           | 4.3.1 Mo<br>4.3.2 Mo  | nnel mobility<br>bility extraction with a revisited CV-split method<br>bility extraction from high frequency measurements<br>bility effect of strained LTB device | 115<br>119 |

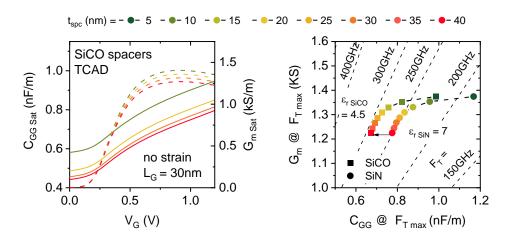

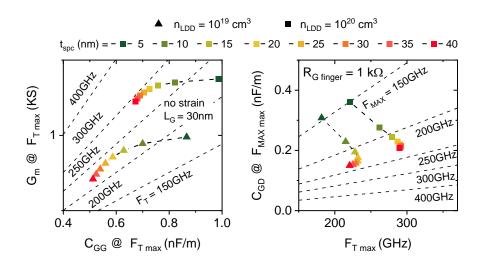

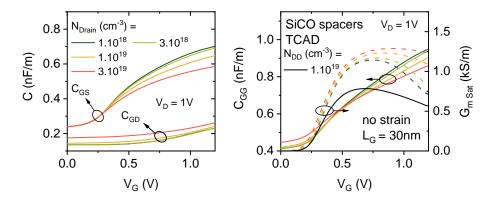

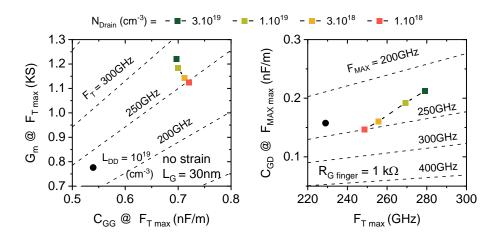

| 4.4           | Low perr              | nitivity spacers performance                                                                                                                                      | 127        |

| 4.5           | 4.5.1 Spa<br>4.5.2 No | nce and resistance Trade-Offs<br>ncer thickness<br>n-symmetrical source and drain junction profiles<br>erlap position                                             | 131<br>134 |

| 4.6           | Nano-sec              | ond LAser anneal on Gate resistance                                                                                                                               | 139        |

| 4.7           | State of t            | he art RF FoMs of ltb transistors                                                                                                                                 | 141        |

| 4.8           | Conclusi              | on                                                                                                                                                                | 143        |

| 4.9           | Referenc              | es                                                                                                                                                                | 144        |

| Chaj          | pter 5:               | Conclusion                                                                                                                                                        | 147        |

## **Statement of Original Authorship**

The work contained in this thesis has not been previously submitted to meet requirements for an award at this or any other higher education institution. To the best of my knowledge and belief, the thesis contains no material previously published or written by another person except where due reference is made.

Signature:

Date:

8

## **Chapter 1: Introduction**

### 1.1 3D SEQUENTIAL INTEGRATION

#### **1.1.1 Context for 3D integration**

As the scaling of logic nodes continues, each new generation must add more functions in order to maintain profit margins by reducing assembly costs. However, as the number of CMOS-compatible functions available decreases, traditional scaling methods are expected to reach their limits. So far, the number of devices per unit footprint is expected to increase by the end of the decade. This is primary due to reductions in gate and metal pitches as well as the introduction of a third dimension. However, this scaling route may become increasingly challenging as the gate pitch, gate length, and the number of stacked devices reach 40nm, 12nm and 4 respectively. This is due to the increase of process complexity, which also come along yield reduction and in turn increased cost. [IRDS and A. Mallik].

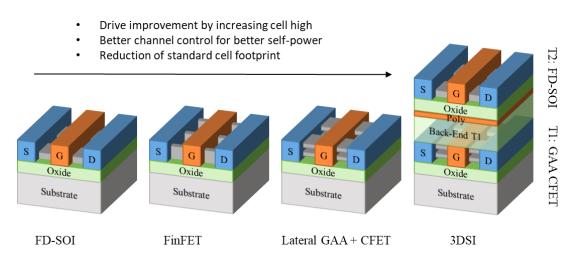

Figure 1-1 Sketch illustrating the evolution the device architecture of digital nodes. As cost and area reductions diminish, 3D sequential integration is expected to bring cost-advantage by adding SoCs complementary functions on top tiers that are integrated using non-scaled technologies.

With the saturation of the pitch reduction, there will be no room for further 2D geometry scaling of a System on a Chip (SoC). To overcome these limitations, the development of 3D integration process such as device-over-device stacking, fine-pitch layer transfer, or monolithic 3D is necessary. These strategies will not only maintain system performance and power gains, but also potentially preserve cost advantages by

Tadeu Mota Frutuoso - Characterization and optimization of low thermal budget silicon MOSFETs for Digital and High frequency application on 3D sequential integration systems

integrating non-scaled components on different layers. Furthermore, it allows the use of the most appropriate technology (high mobility Ge and III-V, 2D materials) for the heterogeneous integration of each layer of the system. As predicted by the International Roadmap for devices and Systems, the transition to 3D integration of complementary System-on-Chip (SoC) functions is expected to take place by 2031, after the deployment of CFET GAA 1.5nm nodes. The transition from 2D to 3DVSLI is projected to evolve trough the following generations: (1) Logic 3D SRAM or MRAM stack; (2) Analog, RF and I/O stack (3) True-3D VLSI: Clustered functional stacks.

Increasing the memory density in a device through the integration of logic 3D SRAM (Static Random Access Memory) and MRAM (Magnetic Random Access Memory) stack is a promising strategy for 3D integration. By stacking memory layers on top of a logic layer in a 3D configuration, the integration of memory and logic functions can be achieved on a single chip, resulting in improved performance, power efficiency and cost savings. 3D parallel stack on memory over logic is favovarble to increase High Band Width Memory (HBM), but does not allow to completely break the memory wall. On the other hand, the 3D sequential integration flow would allow the fabrication of Logic immersed in memory systems that could improve near memory computing. This is because 3DSI authorizes an unique fine grain memory and logic partitioning that thereby reduces interconnection length between logic and memory. Additionally, the use of MRAM technology provides non-volatility and fast switching, which are highly desirable features in memory applications. [Refs]

3D integration is also promising is a method for integrating analog, radio frequency, and input/output functions on a single chip using a three-dimensional configuration. This approach can improve performance, power efficiency, and costeffectiveness by allowing for the integration of functions on multiple layers. It also allows for the optimization of each function's characteristics by using different technology nodes. As example, the RF function, which includes the transmitter and receiver for wireless application, could be implemented using a technology node optimized for high frequency performance and power efficiency. The Analog function, which includes the power management circuit, could be implemented using a technology node optimized for improved linearity and low noise performance. By

Tadeu Mota Frutuoso - Characterization and optimization of low thermal budget silicon MOSFETs for Digital and High frequency application on 3D sequential integration systems

using different technology nodes for each function, the overall performance and power efficiency of the device can be improved. [Refs]

True-3D VLSI (Very Large Scale Integration) refers to the integration of digital logic, memory, and interconnects in a three-dimensional (3D) configuration on a single chip. This approach allows for the stacking of multiple layers of transistors, memory, and interconnects, resulting in increased device density and improved performance. True-3D VLSI is particularly useful for digital applications such as high-performance computing. Clustered functional stacks is a way of organizing the different functions in a 3D structure for better performance, power efficiency and cost savings. This is possible thanks to an independent optimization of the different technologies and materials used at each level. [Refs]

All of these approaches have been actively researched and have been demonstrated to have great potential in achieving high integration density and high performance. However, there are still many challenges to overcome before 3D sequential integration is widely adopted in commercial applications. Amongst them, we can cite high cost, high thermal density, and the need for new packaging technologies. Overall, the state of the art in 3D sequential integration is rapidly advancing, with new research and development efforts focused on addressing the challenges and enabling the widespread adoption of this technology.

### **1.1.2 Monolithic 3D integration**

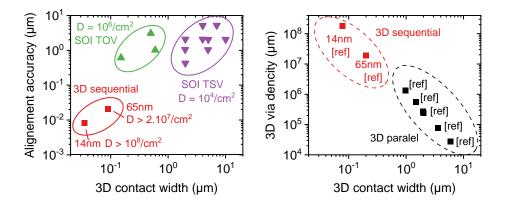

3D integration refers to two types of 3D stacking: *the parallel integration*, in which the different layers are manufactured separately before being stacked together, and *the sequential or monolithic integration*, in which the layers are manufactured successively on top of each other on the same substrate as illustrated in **Erreur ! Source du renvoi introuvable.** The main difference between the two options arises from the alignment process. For parallel integration, the alignment of the different layers occurs during the bonding process between the two plates. For the sequential integration, the alignment is, this time, achieved during the manufacturing of the second layer. This results in a higher precision for the latter approach, which is closer to a traditional back-end lithography step. As a result, the minimum spacing between contacts, which is dependent on the misalignment between the layers, is much smaller for 3D sequential integration. This allows for a higher density of contacts, with 10<sup>8</sup>

contacts per mm<sup>2</sup> possible under 14nm design rules, resulting in several orders of magnitude higher density of 3D contacts that is limited to 10<sup>6</sup> contacts per mm<sup>2</sup> (fig.**Erreur ! Source du renvoi introuvable.**).

The increase in 3D interconnection for a sequential integration scheme is attractive for more than Moore applications, since it increases device density beyond device scalability itself. The implementation of different systems on separated layers is attainable thanks to the 3DSI high contact density. Its main interest is the elimination of costly trade-offs coming from the optimization of different devices on the same substrate by separating different functions on separate layers [Batude IEDM 17].

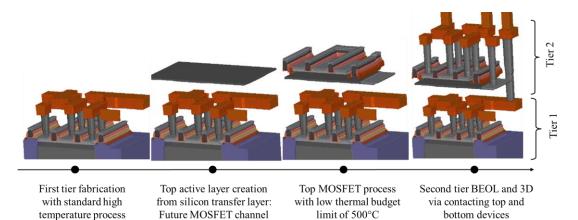

Figure 1-2 3D sequential integration process steps. After the fabrication of the first tier using standard high temperature process, the active layer is transferred above the finished back end. This crystalline silicon layer is used for the fabrication of the second tier using a low temperature process. Finally, both tiers are connected using 3D interconnections.

Figure 1-3 Alignment accuracy (left) and 3D contact density vs 3D contact pitch for different technologies obtained from parallel packaging and sequential integration. [Brunet16]

The first challenge in integrating the second tier using a sequential integration scheme is the formation of the silicon film used for the transistor channel. The most

consistent and performant solution is to transfer an SOI wafer onto the initial substrate through molecular bonding between two oxides. This method is a highly attractive approach as it can be performed at low temperatures (400°C) while yielding defectfree material with exceptional thickness uniformity control [A. Mallik IEDM]. The substrate and buried oxide from the donor wafer are trimmed to the required dimensions to form the active region of the second tier. Although this process consumes a whole SOI wafer, which increases the cost of the second layer, it is currently necessary to obtain a high-quality monocrystalline region with minimal crystallography defects and low density of interface traps.

Another method is being developed that uses a bulk-Si donor substrate with embedded etch-stop layers for uniformity and thickness engineering, it does not consume the whole wafer and requires less mechanical and chemical trimming of the active layer. However, the drawback of this approach is that it results in a lower interface quality from the bottom channel that degrades MOSFET mobility [VLSI Brunet22].

Another suggested method is the formation of a polycrystalline active layer using silicon amorphous deposition that is crystallized using a nanosecond laser anneal [ref]. This approach is less expensive, but the polycrystalline channel produces devices with inferior quality and bigger variability. Alternatively, the channel could be formed from a crystalline seed on the second tier that is epitaxially grown through channels opened on the backend of the first tier [ref]. This approach preserves the crystalline structure from the seeds, but it occupies an area that cannot be used for device fabrication on both tiers, reducing the density of integrated components. Additionally, the recrystallization rate obtained with low temperature anneals may not be fast enough for recrystallization of large surfaces.

The second challenge in 3D integration is the fabrication of the second tier devices without damaging the lower layers. This requires careful management of the thermal budget during the manufacturing process, as high temperatures can damage the transistors and intermediate BEOL (back-end of line) metal lines below. Therefore, it is essential to establish the maximum thermal budget for the upper layer, taking into account the thermal tolerance of the lower layers, to prevent any degradation of their electrical performance.

Tadeu Mota Frutuoso - Characterization and optimization of low thermal budget silicon MOSFETsfor Digital and High frequency application on 3D sequential integration systems13

Previous studies [Claire, IEDM, 2014 and Camila VLSI 2020] have investigated the effects of different furnace annealing temperatures on state-of-the-art FDSOI bottom CMOSFET transistors. The results showed that an annealing temperature of 500°C for 5 hours had no impact on the  $I_{ON}$  at a fixed  $I_{OFF}$ , DIBL, and for both NMOS and PMOS devices. However, metal gate work-function shift and silicide instability were observed at temperatures above 500°C. There were also no effects observed on the BEOL stability. The Time to Breakdown (TBD) of bottom tier transistors remained unchanged after a maximum annealing of 525°C for 2 hours, but began to degrade after a 2 minute anneal at 600°C. Yield analyses on 5 Mbit and 1 million flip-flops circuits also showed no yield loss for anneals up to 500°C. Therefore, it is possible to fabricate top-tier CMOS transistors above BEOL with 28nm by limiting the thermal budget to 500°C without requiring the integration of alternative materials for the Cu interconnections such as Co or W.

### 1.1.3 FD-SOI Transistor

Fully-Depleted Silicon-On-Insulator (FD-SOI) transistors are a type of MOSFET (Metal-Oxide-Semiconductor Field-Effect Transistor) device that are fabricated with a silicon film thickness under 20nm. The silicon channel layer is separated from the substrate by a buried oxide (BOX) layer. Due to the thin silicon layer, the channel becomes fully depleted, which allows a better electrostatic control of the channel and reduced fringe capacitances, leakage current and process variation from random dopant fluctuations. Additionally, FDSOI transistors have the ability for dynamic back biasing for threshold voltage modulation. As a result, FDSOI, a planar technology, is able to achieve the advantages of reduced silicon geometries and simplify the manufacturing process at the same time. This technology has been recognized as a leading silicon technology for applications involving low power, microwave and radio frequency.

These SOI substrates can be obtained using the SmartCut<sup>TM</sup> technology developed by Soitec, which is based on the implantation of hydrogen ions through an oxide. The oxidized plate is then bonded above another plate and annealed, allowing the substrate to be separated at the level of the implanted hydrogen layer, resulting in a thin film of monocrystalline silicon on a BOX of variable thickness [Bruel95].  $\mu$

Tadeu Mota Frutuoso - Characterization and optimization of low thermal budget silicon MOSFETs for Digital and High frequency application on 3D sequential integration systems

#### **1.2 LTB MOSFET FABRICATION**

### 1.2.1 Description of the 28nm Integration process

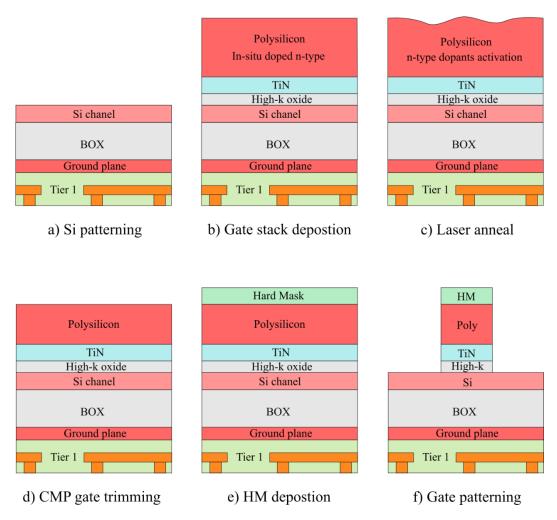

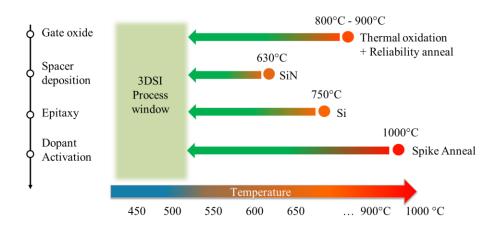

The first step in the 3D sequential fabrication process begins with transferring an SOI wafer to the back end of the first tier (as shown in figure 1-4-a). The active region is then patterned on the silicon film using a step lithography process, followed by plasma etching. This patterning defines the geometry of the active region for each device, including the source and drain, and isolates different transistors to prevent latch-up.

The gate stack is then deposited over the entire wafer (**Erreur ! Source du renvoi introuvable.**-b). The gate oxide is the first layer of the stack and is composed of a thin interfacial silicon oxide layer (~1nm) followed by a thicker (~2nm) high permittivity (High-k) HfO<sub>2</sub> layer. The oxide layer improves the interface quality with the crystalline silicon film, while the thicker high permittivity HfO<sub>2</sub> layer reduces leakage current from direct tunneling between the channel and the gate while maintaining good electrostatic control. The stack of both materials can be interpreted as a single insulator with the same permittivity as silicon oxide (k=3.9) and an equivalent oxide thickness (EOT). The digital devices measured for this thesis have an EOT between 0.9 and 1.3nm.

The gate stack is followed by the deposition of titanium Nitrate (TiN) a metallic material useful for fixing the flat band voltage of the device and avoiding depletion of the polysilicon layer on strong inversion. Then, the formation of the polysilicon layer is performed with the deposition of an amorphous silicon layer in-situ, meaning the silicon material is deposited at the same time as the impurities for a homogenous doping profile. In other to crystalize the amorphous silicon layer and activate the insitu dopants, a high temperature anneal is required. However, due to the thermal limitations from the sequential integration scheme, a classic high temperature anneal is not possible. In order to solve this problem, nanosecond UV laser annealing (UV-NLA) has been developed, which allows the wafer to be heated only in the upper layers (**Erreur ! Source du renvoi introuvable.**-c).

The short annealing time from the fast UV-NLA pulses strongly limits the diffusion of thermal energy from the annealed surface to the lower layers, potentially allowing temperatures above 1000°C to be reached for the upper layer without

Tadeu Mota Frutuoso - Characterization and optimization of low thermal budget silicon MOSFETsfor Digital and High frequency application on 3D sequential integration systems

exceeding the thermal budget limit for the lower layers. Previous studies showed that a temperature of 1200°C can be reached at the top level while keeping the temperature of the bottom level below 500°C. The non-vertical uniformity of this anneal ensures the integrity of the bottom layers while the upper layers can be annealed at high temperatures.

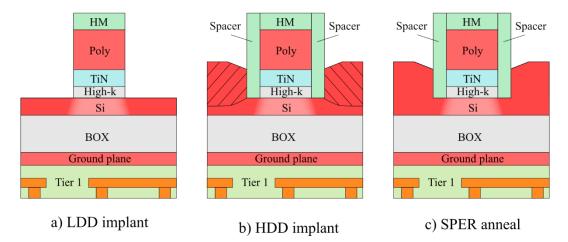

Figure 1-4 Top tiers low thermal budget fabrication steps (a to f). (a) Patterning of the silicon film to define the geometry of the active region of each devices. (b) Gate stack formation including the deposition of High-k and IL gate oxide materials, titanium nitrate metal gate and polysilicon layer. (c)

Activation of polysilicon dopants using nano-second UV laser anneal. (d) Chemical-mechanical polishing to trim the annealed polysilicon surface. (e) Deposition of the hard-mask on top of the stack. (f) Etching of the stack to define the pattern of gate of each device.

It is important to note that the UV-NLA step also has drawbacks. In peculiar, the uniformity of the annealing depends on the geometry of the patterns present at the surface, because of the short wavelength of the laser. While the polysilicon is deposited above the whole wafer, the polysilicon thermal energy absorption is homogeneous and independent on the position. However, in the following steps, after the patterning of the devices, it is not yet a reliable method as it highly dependent on the transistor

geometry and heat absorption rate from different material stacks. Recent studies are been performed to improve the performance of UV-NLA annealing on patterned devices, but are still under development [ref].

Thus, nanosecond laser annealing is a promising technique for activating the gate dopants while limiting damage to lower components. On the other hand, the energy and number of pulses used on this process must be carefully optimized to control the activation temperature and avoid melting the polysilicon layer. The rugosity of the polysilicon layer is greatly increased after the LNA step, resulting in a non-uniform surface on the vertical axis. Therefore, the laser anneal is followed by a chemical mechanical polishing (CMP) that flattens the polysilicon surface and trims it to the required gate height (**Erreur ! Source du renvoi introuvable.**-d).

A hard mask (HM) composed of Silicon Nitrate (SiN) is then deposited above the trimmed surface (**Erreur ! Source du renvoi introuvable.**-e). This material is necessary to isolate the gate from the step of epitaxy of source and drain that will be performed latter and to improve the gate etching selectivity. Because the resist mask can degrade during the plasma etch, the resolution of the image patterned into the dielectric layer is reduced. This type of imperfect image transfer compromises the semiconductor device's performance. As high etch selectivity can be achieved between the hard mask layer and the over-coated patterned resist, image transfer imperfections can be avoided. The gate stack is finally etched to the gate geometries from the mask (**Erreur ! Source du renvoi introuvable.**-f).

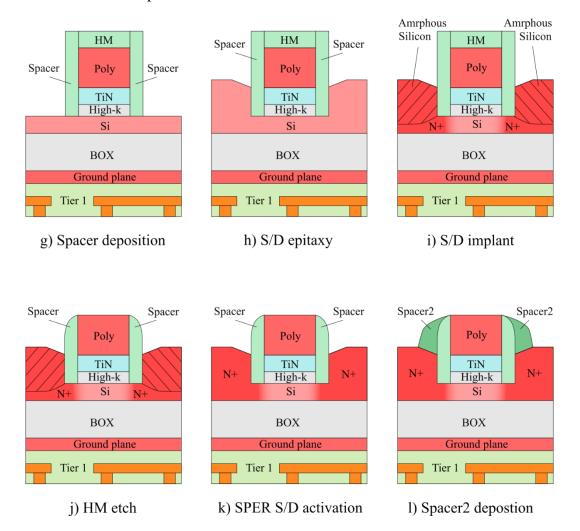

After deposition and etching of the gate stack, the lateral part of the gate must be protected from the following epitaxy process. For this, a dielectric is first deposited and etched in order to form spacers that electrically isolate the gate from future source and drain accesses (**Erreur ! Source du renvoi introuvable.-**g). This spacer is created with the deposition of an insulator above the whole wafer surface followed by an anisotropic plasma etching that consumes the insulator material mostly in one direction. Next, the insulator is vertically etched until the hard mask and silicon film are cleared. Only the material deposited at the lateral of the gate stack remains at the end of this process step. On high temperature devices, the spacers is formed using the same material from the hard-mask, SiN, which has a permittivity equal to 7. However, the electrostatic performance of the transistor can be improved with a material with lower permittivity like SiCO. The main advantages of SiCO material are (1) the high

Tadeu Mota Frutuoso - Characterization and optimization of low thermal budget silicon MOSFETsfor Digital and High frequency application on 3D sequential integration systems17

etching selectivity when compared to amorphous and crystalline silicon (2) a lower permittivity equal to 4.5 (3) its low temperature deposition (400°C), that makes it compatible with a LTB process deposition process [Benoit IEDM 15].

Because the silicon film is very thin (5nm - 10nm), a step of raising the sources and drains is then necessary in order to create the source and drain contacts. This step is accomplished through epitaxial growth. (**Erreur ! Source du renvoi introuvable.**-h). Because of the previous hard mask and spacer deposition, parasitic growth of Si above the gate stack that would lead to short the S/D and the Gate is not possible. On traditional high temperature epitaxy process, the crystalline film is growth through a selective silicon deposition at 750°C.

Figure 1-5 Top tiers low thermal budget fabrication steps (g to l). (g) Deposition of SiCO spacers to electrically insulate the gate and avoid parasitic growth during the epitaxies. (h) Source and drain epitaxies in order to improve access contact. (i) Source and drain doping and amorphization implant (j) removal of hard mask. (k) Activation of dopants from source and drain with SPER anneal. (l) Deposition of spacer2 to limit the reach of the silicidation step.

Tadeu Mota Frutuoso - Characterization and optimization of low thermal budget silicon MOSFETs for Digital and High frequency application on 3D sequential integration systems

A new epitaxial process at was developed at LETI [Lu] where the temperature of two critical process were reduced to 500°C: the surface preparation and the epitaxial growth. The surface preparation is performed by a wet HF clean followed by an insitu Siconi. The siconi process remove the surface oxide and is done at the same chamber from the epitaxy step. A Cyclic and Deposition Etch (CDE) was also developed for the low temperature process flow. The LTB epitaxy deposition phase is non-selective, where amorphous silicon is deposited above the oxide layers in addition to the crystalline region growth. Therefore, a deposition followed by an amorphous silicon etch is performed in sequence until the total epitaxy thickness is obtained.

For high temperature process, the following step would be the source and drain dopants implantation and activation. At this stage, the choice of the dopant species will determine the type of transistor: phosphorus or arsenic implantation for nMOS or boron implantation for pMOS. Annealing is then carried out in order to provide the energy necessary for the dopants to substitute an atom of the semiconductor, activate them electrically, and recrystallize the region that becomes amorphous from the implantation. Once again, this step is not possible for the fabrication of top tier devices using the classic process because of the high thermal budget required for the activation of the dopants i.e. Spike anneal requires temperatures above 1000°C.

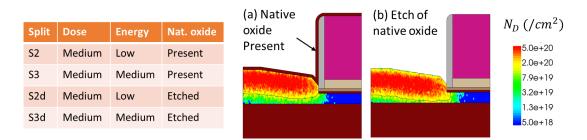

The alternative to high temperature annealing is the SPER technique, or Solid Phase Epitaxy Regrowth. The technique consists of recrystallizing an amorphized silicon layer from a monocrystalline layer (called the seed), allowing the crystalline orientation to remain unchanged. The amorphous layer is created either from the dopants or from germanium implantation (**Erreur ! Source du renvoi introuvable.**i). For nMOS, the amorphization and doping is performed at the same step with phosphorous implantation. On the other hand, for pMOS, a pre-amorphization is performed by Germanium implantation, prior to the Boron implantation for doping. This is necessary, as the boron atom is not heavy enough to create a deep amorphization at the source and drain epitaxies.

Before the recrystallization of source and drain, the remaining SiN hard mask above the gate must first be removed. In order to achieve this, temporary SiO<sub>2</sub> spacers are deposited and etched anisotopically. This is required to protect the SiCO spacers during the removal of the hard mask. (**Erreur ! Source du renvoi introuvable.**-j). The Hard-Mask is then selectively removed typically in an H3PO4 solution, which has

Tadeu Mota Frutuoso - Characterization and optimization of low thermal budget silicon MOSFETsfor Digital and High frequency application on 3D sequential integration systems19

a small effect on the SiO<sub>2</sub>. Following the removal of the hard mask this temporary SiO<sub>2</sub> spacers are also etched.

After the hard mask removal, the SPER activation step is performed (**Erreur** ! **Source du renvoi introuvable.**-k). During the recrystallization, the atoms reorganize and the dopants integrate the silicon matrix in a substitutional position, becoming electrically active donor or acceptor dopants. A major difference between a low and high temperature activation lies on the dopant diffusion. During a high thermal budget process, the high temperature activation anneal allows the dopants to diffuse from the implantation region throughout the area underneath the spacers. However, no dopants diffusion happens with the low temperature SPER anneal. Therefore, the dopants must be placed directly at its final position under the spacer with a tilted implant.

Figure 1-6 Top tiers low thermal budget fabrication steps (m to o). (m) Silicidation of contact regions of source, drain and gate.(n) Deposition of Contact Etch Stop Layer and Inter-Metal Dielectric layers above the finished device. (o) Fabrication of the back end layers

Following the activation of source and drain, a second set of spacers (Spacer2) is deposited and etched around the first spacers (**Erreur ! Source du renvoi introuvable.**-1). This step is necessary to distance the silicidation region from the channel in other to improve the access resistance. The silicidation is a formation of an alloy between the silicon and a metal and it is performed on the exposed silicon region of the source, drain and gate. The first step is the deposition of a NiPt alloy on the entire plate. Then a first anneal is performed so the silicon reacts with the metal to form the silicide NiPtSi. The anneal is followed by a selective wet removal of the silicide metal and then by a second anneal to optimize the resistivity of the silicide

(Erreur ! Source du renvoi introuvable.-m). The silicide is an important step to reduce the source and drain access resistance of the transistor. In addition to the reduction of the local resistivity, it suppresses the schottky diode, initially formed between the metal and the semiconductor. This done by a reduction of the barrier height between the metal work function and the Fermi level of Si in the access region. [ref]

A Contact Etch Stop Layer (CESL) is then deposited to encapsulate the transistor and is followed by the deposition of an Inter-Metal Dielectric (IMD) (**Erreur ! Source du renvoi introuvable.**-n). The CESL is an insulator layer that improves the control of the etch depth for the contacts by reducing its dependence on the on the local topography. In essence, the CESL material has a low sensibility to the solution used for IMD etch. A first contact etch will remove the IMD material until the CESL layer. A second careful etch step is performed on the CESL with a different solution to reach the silicide region. Etched cavities are then filled by a Ti/TiN barrier and tungsten material (**Erreur ! Source du renvoi introuvable.**-o). In addition to the improved etching control, the CESL can introduce mechanical compressive or tensile stress on the transistor in order to improve the carrier mobility in the channel.

### **1.2.2 Extension-first vs Extension-Last**

As mentioned before, the issue with the SPER anneal is the non-diffusion of dopants at low temperatures and its dependence on the amorphization region for the activation of dopants. Yet, it is not trivial with a single implant to place the dopants under the spacers at their right position. The high implantation energies generates stronger variability and the spacer thickness is limited by the maximum distance traveled by the dopants. In addition, due to the activation dependence on the recrystallization, only the dopants present in the initially amorphized layer are activated during SPER.

Co-optimizing the implantation step is a challenging task due to the conflicting effects that arise. If the implantation is too strong, it will result in the absence of a crystalline silicon seed, which is necessary for SPER recrystallization. On the other hand, if the implantation is too low, it will lead to a limited amount of dopants under the spacers, increasing the source and drain access resistance. Despite these challenges, there is limited understanding of the actual need to amorphize the region under the access in order to achieve a high activation level. Recent studies suggest that even a low-temperature anneal at 500°C may be sufficient to activate the dopants under the spacers due to their proximity to the oxide interfaces of the spacers and the BOX.

The process flow presented so far is called extension-last, where the source and drain implantations are performed after the source and drain epitaxies. Another potential solution exists to carefully optimize the junction based on a so-called extension-first integration flow. In that case, the implantation is performed, prior to the raising of the source and drain or even before the formation of the gate spacers. A first LDD (lightly doped) implantation before the spacer deposition or with a thinner spacer (2-3nm) allows placing dopants near the channel with smaller implantation energies (**Erreur ! Source du renvoi introuvable.**-a) [ref Pasini16b]. Then, a second HDD (Highly doped) implantation is performed after thicker spacers' deposition and epitaxy of source and drain (**Erreur ! Source du renvoi introuvable.**-b). The HDD implants are then activated with the recrystallization from the SPER anneal (**Erreur ! Source du renvoi introuvable.**-c). This last integration has been demonstrated [Pasini16] on a 14FDSOI technology from STMicroelectronics with a maximum thermal budget of 600°C. The device presented electric performances close to a reference at high temperature on nMOS and pMOS.

### 1.2.3 Low vs High thermal budget process

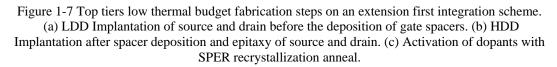

**Erreur ! Source du renvoi introuvable.** summarizes the several integration steps required for the fabrication of low temperature silicon MOSFET transistors.

Tadeu Mota Frutuoso - Characterization and optimization of low thermal budget silicon MOSFETs for Digital and High frequency application on 3D sequential integration systems

Firstly, the deposition of the gate oxide stack and the reliability anneal that are normally performed between 800°C and 900°C are reduced to 500°C using a method developed at LETI [ref?].

In addition, the deposition of the spacers that are classically fabricated using a 630°C silicon nitride deposition are switched to a low temperature 400°C SiCO deposition , which also benefits of a lower permittivity. The epitaxy of source and drain is another step that was re-developed specifically for this technology where the deposition of crystalline silicon and etching of amorphous layers are done separately in cyclic steps. Finally, the activation and diffusion anneal that is normally done at temperatures above 1000°C is replaced by the SPER amorphization and recrystallization anneal that allows for a high activation of impurities under 500°C in the epitaxial region of source and drain.

Figure 1-8 Representation of key technological steps that are re-developed at LETI for the low thermal budget integration. The deposition of the gate stack, formation of spacers, source and drain epitaxies and activation anneal are performed under 500°C to avoid degradation and guarantee the stability of transistors and interconnections from lower tiers.

The studies performed during this thesis focus on two of those re-developed processes. Firstly, the impact of the low temperature SPER technique on the S/D junction properties is fully characterized. In particular, the thermal activation of Bore and Phosphorus impurities implanted in the non-recrystallized region and its impact on the access resistance and short channel effects is explored. In addition, the quality of the SiCO oxide used for the formation of the spacers is also studied on low thermal budget MOSFET devices. This has been done by analyzing the trapping behavior of the oxide and its detrimental effects on device performance. Both studies resulted in the development of novel characterization methods that have been used to provide a

Tadeu Mota Frutuoso - Characterization and optimization of low thermal budget silicon MOSFETsfor Digital and High frequency application on 3D sequential integration systems23

deeper understanding of the effects of those new fabrication methods on the electric behavior of the devices.

### **1.3 PURPOSE OF THIS THESIS**

The objective of this thesis is to explore the effects of low temperature integration process developed for the fabrication of 3D-SI FD-SOI MOSFET transistors and to propose optimization paths for the performance improvements of digital technologies in the high frequency domain. The studies were performed using low temperature devices fabricated at LETI and are currently compared to devices fabricated using a classic high thermal budget. All the studies have been made on single tier MOSFET wafers fabricated within a low thermal budget, representative of the budget required for the processing of the top tiers of a 3DSI integration. The objective is therefore to characterize the effects of the low temperature process on the electric behavior of the device and improve its fabrication at low temperature.

This manuscript is divided in 3 parts following this introduction. The second chapter focuses on the optimization of the junction position on an extension first integration scheme. A novel method for the extraction of the junction profile on ultrathin FD-SOI MOSFET transistors is developed and validated against classic high thermal budget devices. Then, the method is used to determine the level of activation obtained from different implantation conditions on NMOS and PMOS transistors, and to correlate it to their electric behavior. Based on the obtained results, new integration schemes are proposed to improve access resistance, reduce variability and parasitic capacitances of future devices.

The third chapter focuses on the SiCO spacers developed for the LTB technology. If the main material properties of the SiCO oxide, such as conformal deposition, etching robustness, were well known at the beginning of the thesis, only few studies were performed so far on its electrical properties. We therefore choose to determine the main electrical properties of this material, and, how they affect the device performance. For this, two new ultra short capacitance measurement methods are developed that allowed to fully characterize the complex trapping behavior of this material. The method were also applied on high temperature oxides used on the development of thermal budget devices. Finally, the effects of hydrogen and high temperature anneals were characterized using the same methods.

The fourth chapter describes the interest of 3DSI for RF application. The fey RF FoMs ( $f_t$  and  $f_{max}$ ) are extracted on our LTB transistors and are compared to the HTB

counterpart. A full ac modeling of LTB device in the RF domain is also provided to determine the process leverages for a further boost of RF device performance. As conclusion, a path for improving the performance of the transistors for high frequency applications is proposed where the devices could be used for a specialized high frequency layer for the development of transceiver SoCs.

# Chapter 2: Characterization and Optimization of Junctions of FD-SOI transistor

Traditionally, during the MOSfet integration process, dopants of the source and drain are introduced to the silicon substrates by ion implantation. In this method, impurities are ionized into a plasma and then are accelerated by an electrical field under a strong vacuum into the substrate surface. When an ion strikes the substrate, it collides with atoms in the lattice, taking a random scattered path before being completely stopped. After the implantation, a vertical Gaussian profile of impurities concentration is obtained that depends on the beam energy, dose and the implanted species. The implanted ions will not necessarily occupy substitutional positions in the silicon lattice. Meaning that it will not be electrically active on the semiconductor gap. In addition, the collision with the substrate atoms can create localized crystalline defects generating silicon vacancies and interstitials. Therefore, a post-implant anneal is necessary to activate the dopants by substituting the impurities atom into crystal lattice sites and to repair any damage done to the silicon crystal. This high temperature short time anneal is also responsible for the diffusion of the impurities inside the crystal. This mechanism is important for the fabrication of MOSfet devices because it allows dopants to be electrically active and to diffuse under the gate spacers required to form a low resistivity path connecting the source and drain access to the channel. [Fundamentals of semiconductor Manufacturing and process control].

For 3D sequential integration, a low thermal budget (<500°C) is required for the fabrication of devices of the top layers. This restriction prohibits the use of traditional high temperature methods for activation and diffusion of dopants. Therefore, on LTB devices the activation step is performed by a different method called Solid Phase Epitaxial Regrowth (SPER). It is based on a layer-by-layer recrystallization phenomenon that happens on amorphous/crystalline (A/C) silicon interfaces that can be triggered at lower temperatures. During the crystal regrowth, the dopants impurities present on the substrate are incorporated into the lattice where they become electrically active.

Tadeu Mota Frutuoso - Characterization and optimization of low thermal budget silicon MOSFETsfor Digital and High frequency application on 3D sequential integration systems27

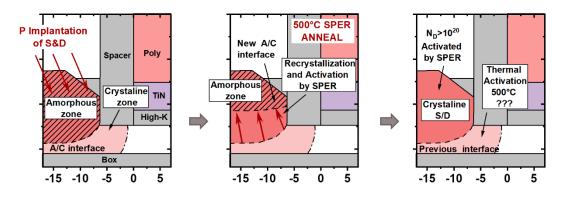

Figure 2-1 Sketch illustrating the principle of the SPER recrystallization anneal on n-type LTB devices.

The strategy for dopants activation on LTB devices is presented on **Erreur**! **Source du renvoi introuvable.** It consists in the creation of an A/C interface on the source and drain epitaxial regions and the subsequent activation of the impurities of the amorphous zone by crystal regrowth. The transformation from a crystalline to an amorphous phase is performed by ion implantation. If the implantation is strong enough, it can trigger collision cascade effects near the surface that transforms the region from crystalline to amorphous. On n-type devices, this is performed directly by the phosphorous implantation. Therefore, the formation of the amorphous region and the introduction of dopants is performed on the same step. On the other hand, for p-type devices, a pre-amorphization step must be performed. This is necessary because boron atoms are not able to break the crystal, because of their lighter atomic mass. Then, boron ions are introduced to the substrate with a second ion implantation step.

After the SPER, a high amount of dopants of the amorphous region can be activated, throughout the recrystallization process. Because the dopants are incorporated into the lattice in a metastable equilibrium, their initial concentration can largely exceed the solid solubility limit of these impurities on silicon at low temperatures. These solubilities have been determined experimentally by [Passini] and correspond to an activation level at 600°C of  $10^{21}$  cm<sup>-3</sup> for phosphorous and  $9 \cdot 10^{20}$  cm<sup>-3</sup> for boron and at 500°C of  $6 \cdot 10^{20}$  cm<sup>-3</sup> for phosphorous and  $5 \cdot 10^{20}$  cm<sup>-3</sup> for boron, respectively. On the order hand, the activation of dopants confined in the region that remained crystalline after the implantation are limited by the thermodynamic equilibrium solubility of the specie. The solubility of dopants at crystalline silicon can be modelled by an Arrhenius behaviour, and it is much smaller

at T=500°C ie approximately  $10^{19}$ cm<sup>-3</sup> and  $10^{18}$ cm<sup>-3</sup> for phosphorous and boron respectively [Passini].

The low theoretical solubility limit at low temperatures makes challenging the formation of the junction using the SPER technique. On one hand, a depth amorphization is necessary to properly activate the dopants under the spacer region during the SPER. On the order hand, it is important to preserve a crystalline seed of around 2nm on the bottom of the silicon layer to trigger the recrystallization process. In addition, the preamorphization followed by recrystallization step also induces End of Range (EoR) Defects on the silicon film. These defects are interstitial type dislocation loops that are formed under the crystalline/amorphous (A/C) interface. They originate from the presence of highly saturated interstitial Si atoms that become dislocated after the implantation. [C. Bonafos,]. The presence of these defects can negatively affect the electrical performances of the transistors. They reduce the activation of dopants near the (A/C) interface, and increase the gate induced drain leakage (GiDL) by trap assisted tunnelling [ref].

A second solution that have been explored is the activation of the access region using the Nano-second laser annealing (NLA). This method allows highly increasing the temperature on the top layer structures without affecting the bottom tiers. However, it imposes several challenges; Firstly, it can create a highly uneven silicon surface that must be treated using a chemical-mechanical planarization (CMP) step. In addition, the increase in temperature depends on the dimension and capability for heat dissipation of the targeted structures at the surface. Therefore, this anneal can induce different effects between small and large devices.

The last integration scheme is yet the most reliable solution for the LTB process. Recently, devices presenting high FoM and low access resistance were demonstrated [VLSI] without amorphization of the region under the spacers, and, despite the theoretical low solubility limit. Therefore, a more in-depth study on the maximum solubility and the activation phenomena of dopants on ultra-thin crystalline silicon films must be performed.

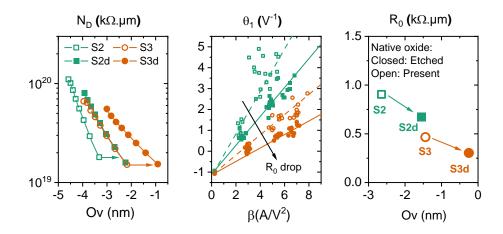

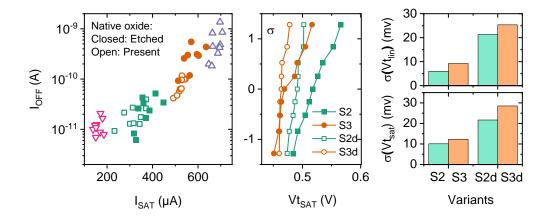

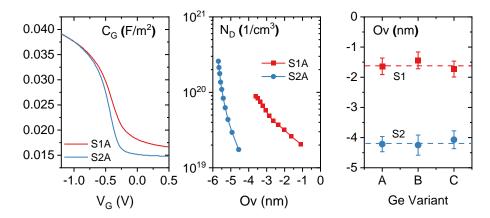

In this chapter, the junction position and the density of dopants that are activated with the LTB SPER method are studied. To evaluate the efficiency of activation under the spacer region, we developed a novel technique called CV-AJP to extract the junction active profile in FDSOI devices using capacitance measurements. Then a study of the correlation between the electrical performances of the device and the junction position is performed for NMOS and PMOS devices. Finally, based on the results, a new source and drain implantation solution for the extension first integration flow is proposed.

### 2.1 ELECTRICAL CHARACTERISTICS OF THE ACCESS REGION

#### 2.1.1 Impact of the junction profile on device electrical features

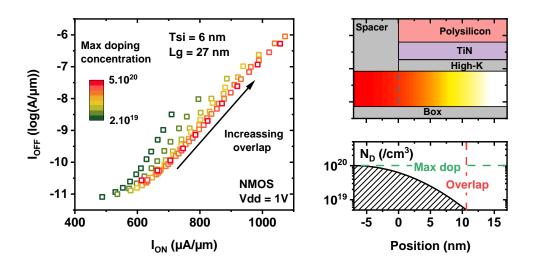

**Erreur ! Source du renvoi introuvable.** presents the effects of the junction profile on the Ion/Ioff FoM for a 27nm MOSfet transistor. The device was simulated for several Gaussian profiles with different values of overlap and density of dopants. A device with an overlapped junction will suffer from stronger Short Channel Effects (SCE). The threshold voltage in saturation ( $Vt_{sat}$ ) decreases and the subthreshold slope (SS) increases. On Ion/Ioff FOMs, the change of the overlap position (points with same colour) produces an Ion/Ioff variation, similar to one produced a variation of the channel length. On the other hand, the doping density has a direct effect on the access resistance. Increasing the doping level increases the carrier density in the access region, that, in turn reduces the access resistance, and the slope of the Ion/Ioff characteristics.

Figure 2-2 TCAD simulation of a 27nm channel length MOSfet at different Gaussian profiles for the source and drain junctions (Left) Ion/Ioff at  $V_{dd} = 1V$  FoM for each profile condition (Right) The Gaussians profile parameters are the maximum amount of dopants and the overlap position. The overlap is arbitrarily set at the position where the doping density is equal  $5 \cdot 10^{18}$  cm<sup>-3</sup>.

**Erreur ! Source du renvoi introuvable.** also illustrates how SCE are dependent on both the density of dopants and on the overlap position. This can be better visualized at **Erreur ! Source du renvoi introuvable.** where the values of saturation Threshold voltage ( $Vt_{sat}$ ), Drain induced Barrier lowering (DiBL) and Subthreshold slope (SS) are extracted for each profile condition. Increasing the overlap also increases the short channel effects regardless of the junction profile. Nevertheless, devices containing a

Tadeu Mota Frutuoso - Characterization and optimization of low thermal budget silicon MOSFETsfor Digital and High frequency application on 3D sequential integration systems31

smaller concentration of dopants in the access region also exhibit a reduced DiBL and SS at same fixed overlap.

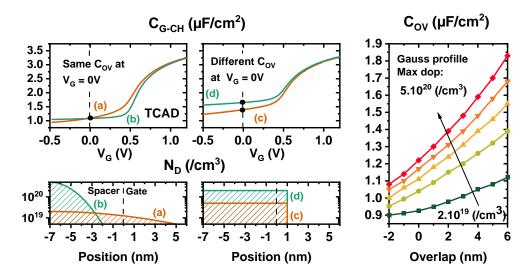

The same analysis can be performed from gate capacitance simulation. **Erreur** ! **Source du renvoi introuvable.** illustrates how the depletion capacitance ( $C_{dep}$ ) at  $V_G = 0V$  changes as the function of the doping profile. **Erreur** ! **Source du renvoi introuvable.** (Left) reports the simulated capacitance for distinct junction conditions. For the first case, an overlapped profile containing a small density of dopants (a) is compared against an overlapped profile with a high density of dopants (b). Even though the capacitance curve is very distinct on depletion, both profiles present the same value of  $C_{dep}$  at  $V_G = 0V$ . Alternatively, a second case shows two profiles (c and d) with the same overlap but with different doping densities. The capacitance in depletion is different between c and d despite the same junction position indicating that the depletion capacitance by itself is a misleading parameter to determine properly the overlap position. Finally, **Erreur** ! **Source du renvoi introuvable.** (Right) present the values of  $C_{dep}$  obtained from different access profiles. Similarly to the IV simulations, the capacitance is also dependent on both the overlap position and density of dopants near the junction.

Figure 2-3 Standard device parameters extracted from IV TCAD simulation of a 27nm MOSfet for different S/D junction profiles. (Left) Vt<sub>sat</sub>. (Middle) DiBL. (Right) Linear SS.

The fact that electrostatic parameters like SS and  $C_{dep}$  are not exclusively dependent on the junction position is explained by a difference between the metallurgic junction and the carrier junction. The metallurgic junction is related to the amount of dopants on the access. Traditionally, it is defined by the exact position where the

density of acceptors equals the one of donors. However, this definition becomes less useful in the most advanced technological nodes, when the channel is much less doped. Moreover, there is no wide accepted minimal value of dopants for the metallurgic junction on intrinsic channels so on this manuscript we will use the density value of  $10^{19}$  cm<sup>-3</sup> to define the metallurgic junction.

The true electrical junction, on the other hand, is not only related to the profile of dopants but also to the electrical characteristics of the device, such as bias conditions for instance. Basically, in MOSfet devices, a depletion region is formed on both sides of the metallurgic junction that depends on the junction parameter (dopant concentration and abruptness) as well as the control produced by the gate through V<sub>G</sub>. This depletion in the access region will strongly depends on the values of  $V_{GD}$  and  $V_{GS}$ , and therefore on the corresponding regime for the transistor i.e. channel depleted  $V_G < V_T$  or inverted  $V_G > V_T$ . The device electrostatic is directly linked to the variation of the depleted zone in the access region since it corresponds to a conductive limit of the access in depletion regime. In this manuscript, the electrical position of the junction will be defined as the point where the free carrier density equals to the doping density.

Figure 2-4 CV parameters extracted from TCAD simulation of a 27nm MOSfet at different profiles. (Left) CV curve obtained from distinct doping profiles presenting the same value of  $C_{dep}$  for profiles with different overlap positions and different values of  $C_{dep}$  for profiles containing the same overlap position (Right)  $C_{dep}$  for several profiles.

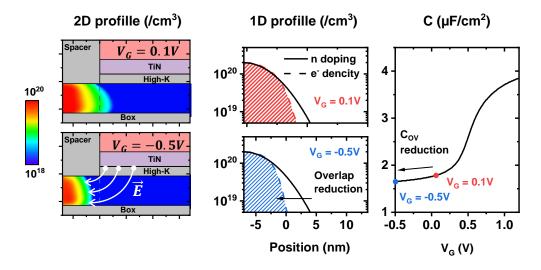

**Erreur ! Source du renvoi introuvable.** illustrates what is the real difference between metallurgic and electrical junction based on free carriers density, and its impacts on device capacitance. **Erreur ! Source du renvoi introuvable.** (left) presents the density of free carriers at two different gate biases chosen in the depletion

Tadeu Mota Frutuoso - Characterization and optimization of low thermal budget silicon MOSFETsfor Digital and High frequency application on 3D sequential integration systems33

regime of the transistor. When  $V_G$  is reduced, a depleted region is formed on the access region beneath the spacers shifting the conductive region in the direction of the S/D. This phenomenon corresponds to a variation of the carrier junction position and a reduction of the inner and outer field capacitance. Obviously, the shift is going to be dependent on the density of dopants on the access. The lower is the doping, the larger is the volume that must be depleted in the access to counter the increase in the electrical field induced by the gate. This also induces a stronger variation of the capacitance value in depletion (**Erreur ! Source du renvoi introuvable.** c and d). Therefore,  $C_{dep}$ is not constant over  $V_G$ , its absolute value depends on the carrier junction position and its variation depends on the density of dopants.

For most of the cases, the effective channel length  $(L_{eff})$  is the preferred metric to evaluate the overlap. Nevertheless, determining the effective channel length becomes challenging in very short channel devices. The several methods to extract  $L_{eff}$ , from the subthreshold slope, gate capacitance and the channel resistance over the device length become less appropriate for devices with a very small gate length. The reasons for that are manyfold. (1) the mobility changes from long to short devices (2) the access resistance is not negligible and (3) fringe parasitic capacitances are no longer constant as function of the physical length.

Beyond the extraction of the effective channel length from electrical parameters, there are physical-mechanical characterization methods that allows measuring the density of dopants directly from the device. Most notably, the scanning spreading resistance microscopy (SSRM) and the off-axis dark field electron holograph are the most promising techniques for the extraction of the profile.

The SSRM is an advanced atomic force microscope (AFM) characterization method that uses a small conductive tip to measure the local spreading resistivity. The density of dopants is then extracted by the direct correlation between carrier's density, mobility and resistivity. It has a spatial resolution typically of 1-3nm and can even perform 2D mapping of the dopants density [refs].

Off-axis electron holograph involves measuring the phase shift of an electron wave passing through the sample using a Transmission Electron Microscopy TEM setup. The phase shift of the incident wave is expressed as function of the inner electric potential of the specimen. Then, the junction position is extracted from the position of

Tadeu Mota Frutuoso - Characterization and optimization of low thermal budget silicon MOSFETs for Digital and High frequency application on 3D sequential integration systems

a step in potential induced by the variation of dopant density. This technique presents very interesting results for sub µm bulk devices but fails to provide meaningful resolution on ultra-thin film advances FDSOI nodes. Additionally, SIMS and atom probe tomography are also very valuable but they measure only the total quantity of dopants atoms and not the electric active ones. [refs]

Figure 2-5 Illustration of the depletion of source and drain dopants on depletion regime ( $V_G = 0.1V$ and  $V_G = -0.5V$ ). (Left) 2D and (middle) 1D Carrier's density at the source for two gate biases on depletion with  $V_D = V_S = 0V$ .

Nevertheless, those sophisticated physical-mechanical methods are expensive. In addition to the use of an AFM or TEM setup, they requires a tedious preparation the sample consisting in polishing, cleaving or milling. Moreover, none of those methods provides the necessary accuracy to study a device with 27nm gate length and 7nm silicon film thickness. Therefore, in the next session, we present a novel methodology for an accurate extraction of the source and drain doping metallurgic profile on UT-FDSOI directly from the electric measurements.

Tadeu Mota Frutuoso - Characterization and optimization of low thermal budget silicon MOSFETs for Digital and High frequency application on 3D sequential integration systems 35

#### 2.2 ACTIVE JUNCTION PROFILE EXTRACTION METHODOLOGY

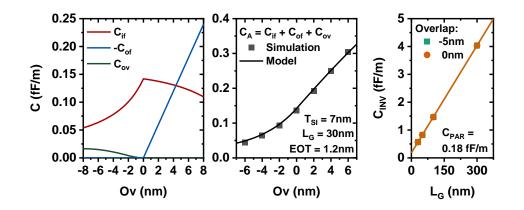

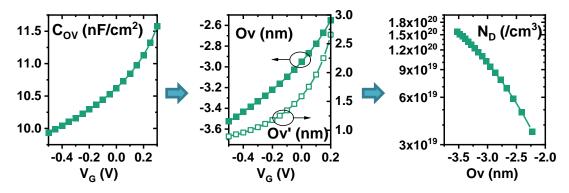

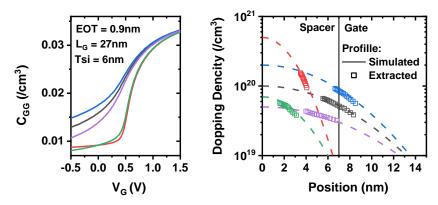

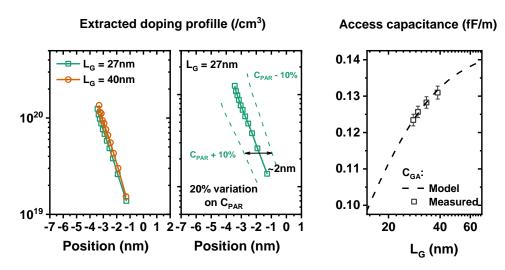

In this part, a novel methodology, called CV-AJP for Active Junction Profile is proposed to extract the source and drain junction profile based on CV measurements and modelling. In essence, from the model it is possible to obtain the overlap position that gives the value of measured capacitance at for each  $V_G$  bias in depletion. From that, we obtain the depletion junction position over gate bias. The density of dopants is then obtained from the variation of this parameter over  $V_G$ . For that, a precise extraction and modeling of the parasitic capacitances of a UT-FDSOI MOSFET device is prerequisite.

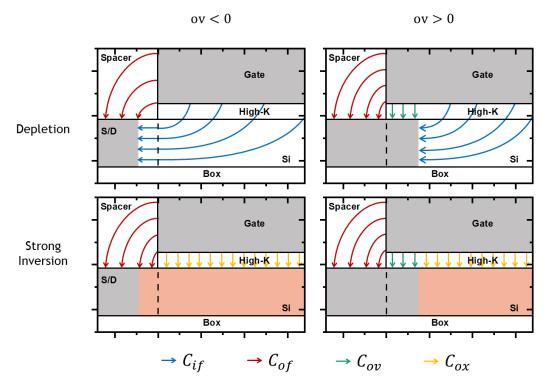

#### 2.2.1 Extraction of parasitic capacitances

The first step of this method is to separate the parasitic components form the measurements using the variation of inversion capacitance over device length. Erreur ! Source du renvoi introuvable. presents the different capacitive components of the device on different regimes. The inner fringe capacitance  $(C_{if}^{W})$  is related to the electrical field traversing the gate oxide into the depleted silicon film until the junction and it is screened out by the formation of the channel in strong inversion. The outer fringe capacitance  $(C_{of}^{W})$  corresponds to the zone of the spacers between the lateral part the gate and the access. It is important to note that the value outer fringe capacitance in underlapped devices is different from inversion to depletion regime. Because the channel also inverts under the spacers, the value of  $C_{of}^W$  increases from depletion to inversion regime. As illustrated at Erreur ! Source du renvoi introuvable., when the channel is completely inverted, the value of  $C_{of}^W$  is practically independent on the overlap. The oxide capacitance  $C_{ox}^{s}$  exists only on inversion regime and corresponds to the coupling between the gate and the channel. The box capacitance  $C_{box}^W$  is related to the coupling between the silicon channel and the substrate through the box. The (w) and (s) superscript indicates that the capacitance is given by width or surface length respectively; i.e. the total value is divided by the device width or surface. In addition, two capacitive components are independent of gate and drain bias  $V_G \& V_D$ .  $C_{2D}^w$ denotes the 2D parasitic capacitance due to coupling between the gate and the source and drain and proportional to the device width. Note that  $C_{2D}^{w}$  is itself the sum of two contributions: (1)  $C_{G-Ctc}^{W}$  due to coupling between the gate and the contacts through the thick gate dielectric (2)  $C_{G-S/D}^{w}$  the capacitance between gate and epitaxial region.

Tadeu Mota Frutuoso - Characterization and optimization of low thermal budget silicon MOSFETs for Digital and High frequency application on 3D sequential integration systems

C<sub>3D</sub> denotes the 3D fringe capacitance due to coupling between the gate and the source and drain contacts and back-end interconnections.

Figure 2-6 Sketch illustrating the different capacitive components that are dependent on the device bias ( $C_{if}$ ,  $C_{of}$  and  $C_{ov}$ ). The capacitive components are illustrated for overlapped (top) and underlapped (bottom) devices at strong inversion (right) and on depletion (left) regimes.

The total capacitance at the extreme of both regimes ( $C_{dep}$  for  $V_G \ll V_T$  and  $C_{inv}$  for  $V_G \gg V_T$ ) can be represented by the sum of the components presented on equations 2-1 and 2-2. Those equations consider that the devices capacitance is measured only between gate and access. As the box is connected to the ground and not to the capacimeter,  $C_{box}$  component does not contribute to the CV measure and is therefore not considered on equation 2-2

$$C_{inv} = WL_G C_{ox}^S + 2W C_{of}^W (ov = 0) + WC_{2D}^W + C_{3D}$$

(2-1)

$$C_{dep} = 2WC_{if}^{W}(L_G) + 2WC_{of}^{W}(ov) + WC_{2D}^{W} + C_{3D}$$

(2-2)

Then the methodology then consists in:

- 1. Plotting the measured capacitance in depletion  $C_{dep}$  vs W to extract the external gate contact to S/D contact capacitance C<sub>3D</sub> (see Fig 2-7 (a))

- 2. Extracting  $C_{ox}$  and  $2C_{of}(ov = 0) + WC_{2D}^W$  by plotting the inversion capacitance  $C_{inv} C_{3D}$  versus gate length  $L_G$ .  $C_{ox}$  is directly proportional to

the slope whereas  $2C_{of}(ov = 0) + C_{par}$  is the interception at  $L_G = 0$ . (see Fig. 2-7) The value of  $C_{inv}$  is obtained at a fixed overdrive bias  $(V_G - V_T)$ .

3. Deducing the access fringe depletion capacitance  $C_{ga}$  without *bias independent* parasitic components (eq. 2-3).

$$C_{ga}^{w} = \frac{C_{dep}(L_{G}) - C_{inv}(L_{G} = 0)}{2W} = C_{if}^{W}(L_{G}) + C_{of}^{W}(ov) - C_{of}^{W}(ov = 0)$$

$$= C_{if}^{W}(L_{G}) + \Delta C_{of}^{W}(ov)$$

(2-3)

The  $\Delta C_{of}^{W}(ov)$  component arises from the variation of the outer fringe components between inversion and depletion regimes. In addition, because  $C_{of}^{W}$  is maximized at strong inversion, the value of  $\Delta C_{of}^{W}$  will always be zero for overlapped and negative for underlapped devices.

Figure 2-7(Left) Variation of depletion capacitance over width for devices with gate length of 30nm. The interception gives the 3D parasitic capacitance that is not dependent on the device length. (Middle) Variation of inversion capacitance over device length. The slope gives the value of  $C_{ox}$  while the intercept correspond to  $C_{2D}$ . (Right) Gate capacitance components of a 27nm MOSFET. The channel capacitance increases from zero to  $C_{ox}$  while the access capacitance decrees to zero in strong inversion.

The extraction of the parasitic capacitances from the linear fit of  $C_{inv} \& C_{dep}$  is an important step in the complete process of the junction profile extraction. A large range of device lengths must be used for a better accuracy witch can become unmanageable. Nonetheless, the parasitic extraction can be uncomplicated by using two large devices (W > 1µm) of short and long ( $L_G > 1µm$ ) gate lengths. For the long devices, the fringe and parasitic capacitance components are much smaller than the oxide capacitance and can be considered as negligible. Similarly, the 3D component is negligible on both short and large devices. Therefore, the  $C_a$  component is obtained from only two measurements using eq. 2-4.

$$C_{ga}^{w} = \frac{C_{dep\_short} - \left(C_{inv\_sort} - \frac{L_{G\_short}}{L_{G\_long}}C_{inv\_long}\right)}{2W}$$

(2-4)

It is also important to note that this description considers a symmetrical device. However, the transistor can sometimes be asymmetrical. This is the case when the source is internally connected to the substrate or when the source sees a different implant condition than the Drain. For those cases, the devices must be measured between the gate and only one of the access and the factor 2 on the previous equations must be adjusted accordingly.

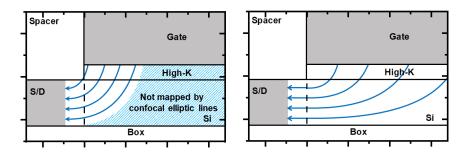

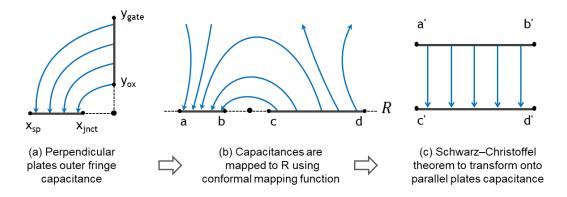

#### 2.2.2 Depletion capacitance modelling based on conformal mapping

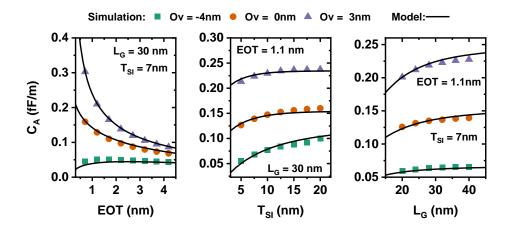

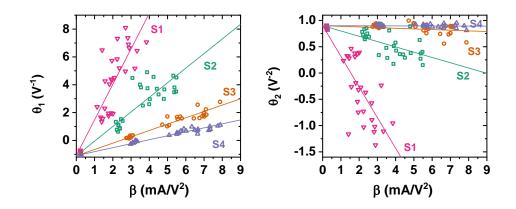

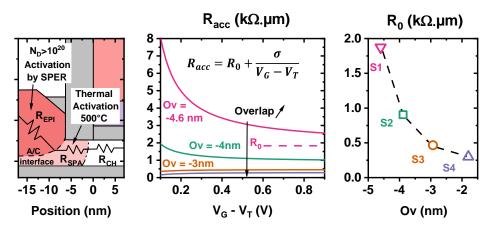

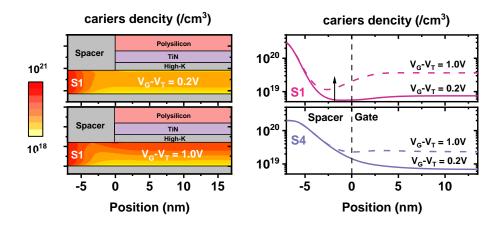

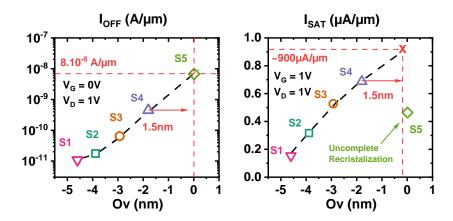

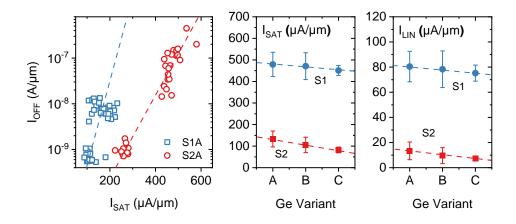

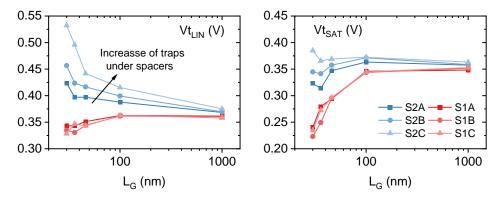

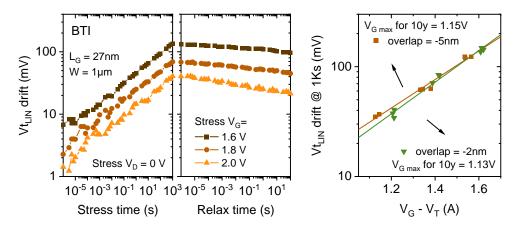

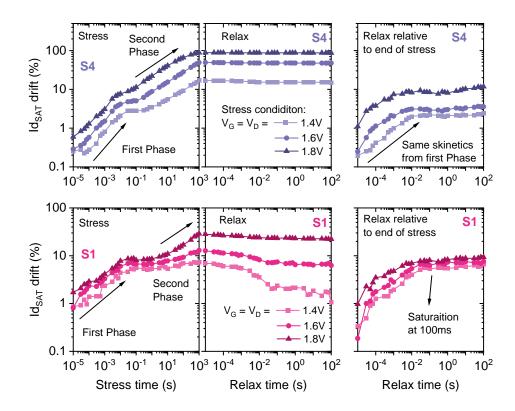

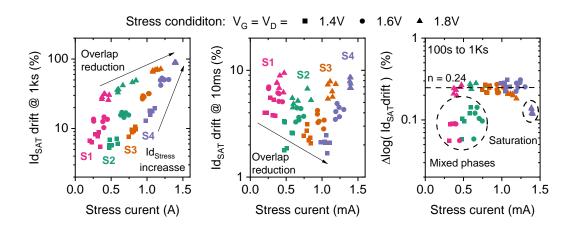

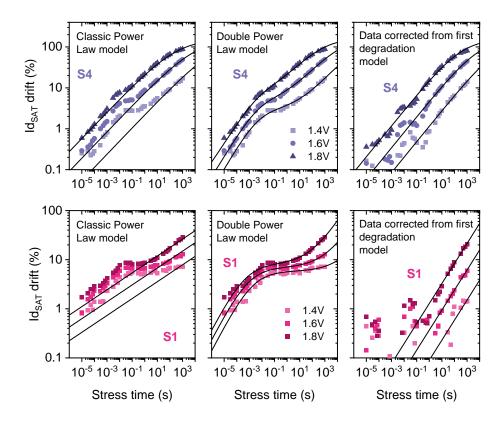

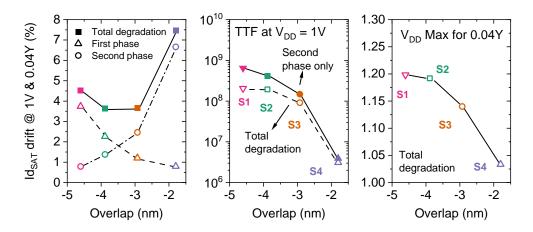

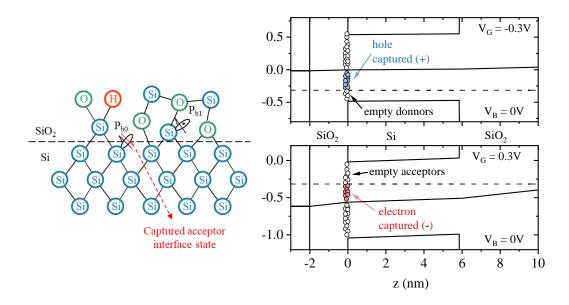

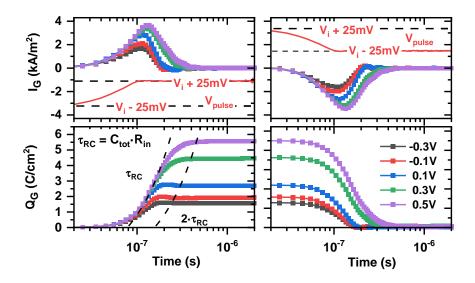

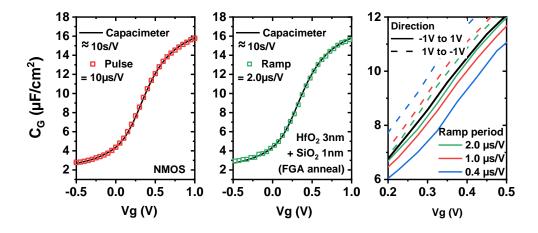

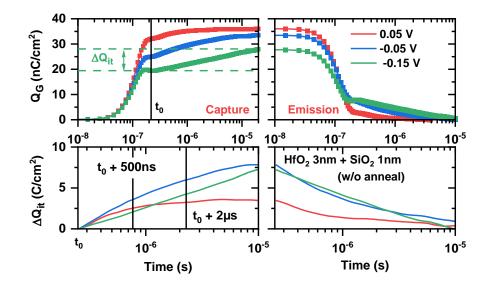

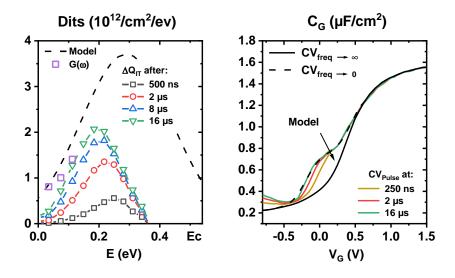

To obtain a precise but simple model for the fringe capacitance between gate and access we need to separate it in elementary components. Each element can then be approximated by parallel or perpendicular plate capacitors. **Erreur ! Source du renvoi introuvable.** presents the three capacitive components for the MOSfet that are dependent on the junction position. For complete modelling of the device whether its junction position, it is necessary to consider the overlap capacitance ( $C_{ov}$ ) in addition of  $C_{of}$  and  $C_{if}$ . This parasitic component exists only when the junction overlaps the gate. It corresponds to the plate capacitor between the overlap region in the channel and the gate oxide (see Fig 2.6). Other parasitic capacitances, like the coupling between gate and epitaxial regions and interconnections are not dependent on the junction position. Those fixed components have been subtracted from raw measurements using the former pre-step i.e. the interception at zero from the capacitance at strong inversion over gate length.