### Étude CEM d'un driver de MOSFET SiC 1,7 kV

#### Hadiseh Geramirad

#### ▶ To cite this version:

Hadiseh Geramirad. Étude CEM d'un driver de MOSFET SiC 1,7 kV. Other. Université de Lyon, 2020. English. NNT: 2020LYSEC031 . tel-04548440

### HAL Id: tel-04548440 https://theses.hal.science/tel-04548440v1

Submitted on 16 Apr 2024

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

N°d'ordre NNT: 2020LYSEC031

### THESE de DOCTORAT DE L'UNIVERSITE DE LYON Opérée au sein de l'Ecole centrale de Lyon

Ecole Doctorale N° 160 (Ecole Doctorale d'Electronique, Electrotechnique, Automatique)

> Spécialité de doctorat : Génie Electrique Discipline : Electronique

Soutenue publiquement le 25/11/2020, par : Hadiseh GERAMIRAD

### EMC study of a 1.7 kV SiC MOSFET gate driver

#### Devant le jury composé de :

CLAVEL, Edith/ Maître de Conférences Université de Grenoble CANAVARO, Flavio/ Professeur Université Politecnico di Torino

IDIR, Nadir/ Professeur Université de Lille Costa, François/ Professeur Université de Paris Est Créteil

VOLLAIRE, Christian/ Professeur Université de Lyon

BREARD, Arnaud/ Professeur Université de Lyon MOREL, Florent/ Dr SuperGrid Institute LEFEBVRE, Bruno/ Dr SuperGrid Institute Rapporteure Rapporteur

Examinateur Examinateur

Directeur de thèse

Encadrant Encadrant Invité

### Abstract

The growing market for renewable energy technologies results in a fast growth in power electronic technologies. Most of the renewable energy technologies produce DC power therefore power electronic converters are needed to convert DC into AC power. Power electronic converters are widely used in voltage range up to +/-1MV and up to several GW power. Given the recent rapid growth in the performance of power semiconductors like Si, SiC and GaN power devices for high-efficiency power applications, there is a need for dedicated gate drivers to deal with SiC semiconductors in new converter generations. To meet the development of these applications, this research work has been carried out on the power electronic field presenting a gate driver for a half-bridge SiC MOSFET power module to be applied in a medium/high voltage power converter.

The principle of operation of converters operation is based on switching. SiC MOSFETs as the switching elements of converters offer many advantages including low conduction losses, high speed and high voltage switching which increase the efficiency and power density. However, it brings some challenges for converter designers like increasing electromagnetic interferences which disturb the converter operation. Gate drivers provide interfaces between the control signal and switching actions in converters. They are also a path for electromagnetic interferences due to their isolated power supply. Gate drivers can be one of the elements which can act on switching transitions and reduce the generated electromagnetic interferences in converters. This reduce also the electromagnetic interferences passing through gate drivers. Therefore to keep the converter in its safe operation, this study targets two main objectives. First protecting gate drivers by limiting the amount of interferences passing through them in order to achieve the operation of the converter at rated value. Secondly reducing the generated electromagnetic interferences by means of gate driver at the semiconductor level by modifying the voltage waveform applied for driving semiconductors. Reaching these objectives results in improving the electromagnetic compatibility of converters.

At first, a commercial 1.7 kV SiC MOSFET half-bridge device is used as a switching leg in a 100 kW Dual Active Bridge DC/DC converter. The device is controlled by a commercial gate driver. The investigation in the converter prototype shows the importance of the conducted electromagnetic interferences passing through the gate drivers. The uncontrolled magnitude of the conducted electromagnetic interferences disturbs the triggering of the semiconductors. This phenomenon is called "self-disturbance". It prevents the proper operation of the converter at rated voltage and power. Self-disturbance phenomenon highlights the effect of the gate drivers on the operation of the converter. This part of the study shows the need of new gate driver techniques to reduce the interferences from semiconductors.

The second contribution addresses the challenge of gate perturbation due to fast switching in SiC MOSFET based converters. A well-known gate voltage perturbation issue due to the fast switching of semiconductors results in self-disturbance phenomenon. This problem is solved by a new circuit implemented in a classical gate driver architecture. It is proposed to filter the parasitic current flowing into the gate by a bifilar common-mode choke in addition of the classical protection circuit. Thanks to this proposed method, the electromagnetic interferences passing through gate drivers are reduced. This part shows the sensitivity of the SiC MOSFET gate drivers design to parasitic elements and measurement probes. The performance of the classical differential probe is compared with optical isolated voltage probe by measuring the gate-source voltage of semiconductors. It clarifies how the parasitic elements of the measurement probes affect the measurements and it allows the optimization of the gate driver design.

The final contribution is the development of a new driving technique. A new inductive feedback gate driver is designed based on the direct drain/source current measurement of the SiC MOSFET power module. The dynamic adjustment of the gate current with this new gate driver technique reduces the generated interferences thanks to moderate switching voltage and current slops. The proposed gate driver achieves a better trade-off between losses and conducted emissions compared to the classical series-connected passive resistors for SiC MOSFET gate drivers.

### Résumé

Le marché croissant des énergies renouvelables entraîne un développement rapide des technologies de l'électronique de puissance. Une large partie de la production d'énergie renouvelable se fait en courant continu ou à fréquence variable, c'est pourquoi des convertisseurs électroniques de puissance sont nécessaires pour obtenir du courant alternatif à fréquence fixe.

Les convertisseurs en électronique de puissance sont largement utilisés dans des applications de tension allant jusqu'à +/-1MV et de puissance allant jusqu'à plusieurs GW. Étant donné les améliorations rapides et récentes des semi-conducteurs de puissance comme les modules Si, SiC et GaN pour les applications à haut rendement, il est nécessaire de disposer des nouvelles commandes de ces interrupteurs.

Le principe de fonctionnement des convertisseurs est basé sur la commutation des interrupteurs. Ceux-ci offrent de nombreux avantages, notamment de faibles pertes en conduction, une vitesse de commutation élevée, et une bonne tenue en tension qui augmentent l'efficacité et la densité de puissance. Cependant, ils posent certains défis, tels que l'augmentation des interférences électromagnétiques qui perturbent le fonctionnement du convertisseur. Les circuits de commande de grille (driver) fournissent des interfaces entre le signal de commande et les semiconducteurs, et constituent également une voie de passage pour les interférences électromagnétiques en raison des éléments parasites de leur alimentation isolée. Ceux-ci font partie des éléments qui peuvent agir sur les commutations et réduire les interférences électromagnétiques générées par les interrupteurs dans les convertisseurs. Premièrement, ils protègent les circuits de commande de grille en limitant la quantité d'interférences qui les traversent et qui permettent de maintenir leur fonctionnement des convertisseurs. Deuxièmement, ils réduisent les interférences électromagnétiques générées par les circuits de commande au niveau des semiconducteurs en modifiant la forme d'onde de la tension de grille.

Tout d'abord, un demi-pont MOSFET SiC 1,7 kV du commerce est utilisé dans un convertisseur continu/continu de type dual active bridge (DAB) de 100 kW, contrôlé par un driver du commerce. L'amplitude incontrôlée des interférences électromagnétiques perturbe la fermeture des semi-conducteurs. Ce phénomène est ici appelé "auto-perturbation" et empêche le fonctionnement du convertisseur à tension et puissance nominales. Cette partie de l'étude montre la nécessité de nouvelles techniques de commande de grille pour réduire les interférences liées aux commutations.

La deuxième contribution, traite du défi que représente la perturbation de la grille due à la commutation rapide dans les convertisseurs à base de MOSFET SiC. Un problème bien connu de perturbation de la tension de grille lors des commutations des semi-conducteurs entraîne un phénomène d'auto-perturbation. Ce problème est résolu par l'ajout d'un élément à un circuit de commande classique. Il est proposé de filtrer le courant parasite entrant dans la grille par une inductance bifilaire en mode commun. Grâce à cette méthode, les interférences électromagnétiques traversant les drivers sont également réduites. Cette partie montre la sensibilité de la conception des circuits de driver et des sondes de mesure. Les performances d'une sonde de tension optique isolée sont évaluées en mesurant la tension grille-source des semi-conducteurs. Cela clarifie la manière dont les éléments parasites des sondes de mesure affectent les mesures et permet d'optimiser la conception des circuits de commande de grille.

La dernière contribution est le développement d'une nouvelle technique de circuit driver. Un nouveau driver doté d'une boucle inductive est conçu sur la base de la mesure du courant de drain ou de source des MOSFETs. L'ajustement dynamique du courant de grille réduit les interférences générées grâce à une tension et un courant de commutation modérés. La commande de grille proposée permet un meilleur compromis entre les pertes et la CEM par rapport aux méthodes classique d'ajout de résistances en série.

## Contents

| 1        | Inti                   | roduction                                                  | 1  |

|----------|------------------------|------------------------------------------------------------|----|

|          | 1.1                    | General introduction                                       | 1  |

|          | 1.2                    | Why SiC MOSFET based converter?                            | 3  |

|          | 1.3                    | Gate drivers for controlling power SiC MOSFETs switching   | 5  |

|          |                        | 1.3.1 Classical gate driver for SiC MOSFET                 | 5  |

|          |                        | 1.3.2 SiC MOSFET switching-transition                      | 7  |

|          |                        | 1.3.3 Conduction and switching losses                      | 11 |

|          |                        | 1.3.4 EMI reduction and trade-off with losses              | 13 |

|          | 1.4                    | EMC definition                                             | 18 |

|          |                        | 1.4.1 Conducted and radiated emissions                     | 18 |

|          | 1.5                    | EMC in power electronic converters                         | 20 |

|          |                        | 1.5.1 Conducted emissions in a switching cell              | 20 |

|          |                        | 1.5.2 Voltage/current overshoot in switching transition    | 22 |

|          |                        | 1.5.3 EMI phenomenon related to gate drivers               | 26 |

|          | 1.6                    | Thesis objectives                                          | 28 |

|          |                        | 1.6.1 Academic objectives                                  | 28 |

|          |                        | 1.6.2 Industrial objectives                                | 29 |

|          | 1.7                    | Thesis outline                                             | 30 |

| <b>2</b> | $\mathbf{E}\mathbf{M}$ | II study of the 1.7 kV SiC MOSFET gate driver in a 1200 V, |    |

|          | 100                    | kW three-phase DC/DC converter                             | 33 |

|          | 2.1                    | Introduction                                               | 33 |

|          | 2.2                    | Experimental set-up                                        | 34 |

|          | 2.3                    | Review of EMI investigations in DC/DC converters           | 36 |

|          |                        | 2.3.1 EMI reduction from the source                        | 36 |

|          |                        | 2.3.2 Optimised propagation paths                          | 37 |

|          | 2.4                    | Problem statement                                          | 38 |

|   | 2.5                      | OM C                                                                                    | irrent investigation in DAB                                  | 42                                                                   |

|---|--------------------------|-----------------------------------------------------------------------------------------|--------------------------------------------------------------|----------------------------------------------------------------------|

|   | 2.6                      | Propo                                                                                   | sed solution to reduce the EMI through the gate driver       | 45                                                                   |

|   | 2.7                      | Concl                                                                                   | usion                                                        | 48                                                                   |

|   | 2.8                      | Perspe                                                                                  | ectives                                                      | 49                                                                   |

| 3 | Dot                      | ıble pı                                                                                 | alse test-bench and EMI modelling                            | 51                                                                   |

|   | 3.1                      | Introd                                                                                  | uction of double pulse test-bench                            | 52                                                                   |

|   | 3.2                      | Half-b                                                                                  | ridge switching steps                                        | 54                                                                   |

|   | 3.3                      | State                                                                                   | of the art of EMI modeling in power electronics              | 56                                                                   |

|   |                          | 3.3.1                                                                                   | Exhaustive approach                                          | 57                                                                   |

|   |                          | 3.3.2                                                                                   | Behavioural modelling                                        | 57                                                                   |

|   |                          | 3.3.3                                                                                   | Chosen EMI modelling for this work                           | 59                                                                   |

|   | 3.4                      | Doubl                                                                                   | e pulse test elements and modelling                          | 60                                                                   |

|   |                          | 3.4.1                                                                                   | Passive components                                           | 60                                                                   |

|   |                          | 3.4.2                                                                                   | LISN modelling                                               | 67                                                                   |

|   |                          | 3.4.3                                                                                   | Active components modelling                                  | 68                                                                   |

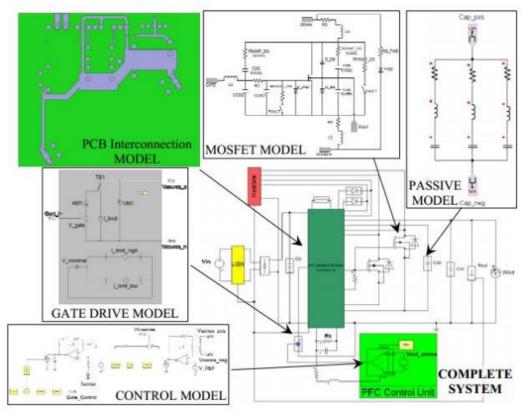

|   | 3.5                      | Simula                                                                                  | ation in LTspice                                             | 69                                                                   |

|   | 3.6                      | Concl                                                                                   | usion                                                        | 74                                                                   |

|   |                          |                                                                                         |                                                              |                                                                      |

| 4 | Mit                      | igation                                                                                 | of the self-disturbance phenomena in a half-bridge           |                                                                      |

| 4 |                          | _                                                                                       | n of the self-disturbance phenomena in a half-bridge<br>dule |                                                                      |

| 4 |                          | ver mo                                                                                  | dule                                                         | 76                                                                   |

| 4 | pow                      | ver mo<br>Introd                                                                        | dule uction                                                  | <b>76</b> 76                                                         |

| 4 | <b>pow</b> 4.1           | ver mo Introd Proble                                                                    | dule auction                                                 | <b>76</b> 76 77                                                      |

| 4 | <b>pow</b> 4.1           | ver mo Introd Proble 4.2.1                                                              | dule auction                                                 | 76<br>76<br>77<br>77                                                 |

| 4 | pow<br>4.1<br>4.2        | Ver mo Introd Proble 4.2.1 4.2.2                                                        | dule auction                                                 | 76<br>76<br>77<br>77<br>79                                           |

| 4 | <b>pow</b> 4.1           | Ver mo Introd Proble 4.2.1 4.2.2 Contri                                                 | dule nuction                                                 | 76<br>76<br>77<br>77<br>79<br>80                                     |

| 4 | 90w<br>4.1<br>4.2<br>4.3 | Ver mo Introd Proble 4.2.1 4.2.2 Contri                                                 | dule auction                                                 | 76<br>76<br>77<br>77<br>79                                           |

| 4 | 90w<br>4.1<br>4.2<br>4.3 | Ver mo Introd Proble 4.2.1 4.2.2 Contri                                                 | dule  auction                                                | 76<br>76<br>77<br>77<br>79<br>80<br>84                               |

| 4 | 90w<br>4.1<br>4.2<br>4.3 | Ver mo Introd Proble 4.2.1 4.2.2 Contri State 4.4.1                                     | dule nuction                                                 | 76<br>76<br>77<br>77<br>79<br>80<br>84<br>85                         |

| 4 | 90w<br>4.1<br>4.2<br>4.3 | Proble 4.2.1 4.2.2 Contribute 4.4.1 4.4.2 4.4.3                                         | dule nuction                                                 | 76<br>76<br>77<br>77<br>79<br>80<br>84<br>85<br>86                   |

| 4 | 4.1<br>4.2<br>4.3<br>4.4 | Proble 4.2.1 4.2.2 Contribute 4.4.1 4.4.2 4.4.3                                         | dule nuction                                                 | 76<br>76<br>77<br>77<br>79<br>80<br>84<br>85<br>86<br>88             |

| 4 | 4.1<br>4.2<br>4.3<br>4.4 | Ver mo Introd Proble 4.2.1 4.2.2 Contri State 4.4.1 4.4.2 4.4.3 Measu                   | dule  duction                                                | 76<br>76<br>77<br>77<br>79<br>80<br>84<br>85<br>86<br>88             |

| 4 | 4.1<br>4.2<br>4.3<br>4.4 | Ver mo Introd Proble 4.2.1 4.2.2 Contri State 4.4.1 4.4.2 4.4.3 Measu 4.5.1 4.5.2       | dule nuction                                                 | 76<br>76<br>77<br>77<br>79<br>80<br>84<br>85<br>86<br>88<br>96       |

| 4 | 4.1<br>4.2<br>4.3<br>4.4 | Ver mo Introd Proble 4.2.1 4.2.2 Contri State 4.4.1 4.4.2 4.4.3 Measu 4.5.1             | dule uction                                                  | 76<br>76<br>77<br>77<br>79<br>80<br>84<br>85<br>86<br>88<br>96<br>96 |

| 4 | 4.1<br>4.2<br>4.3<br>4.4 | Ver mo Introd Proble 4.2.1 4.2.2 Contri State 4.4.1 4.4.2 4.4.3 Measu 4.5.1 4.5.2 4.5.3 | dule uction                                                  | 76<br>76<br>77<br>77<br>79<br>80<br>84<br>85<br>86<br>88<br>96       |

| 5 | Nev | w approach for EMI reduction by means of gate driver                | 112   |

|---|-----|---------------------------------------------------------------------|-------|

|   | 5.1 | Introduction                                                        | 112   |

|   | 5.2 | State of the art: EMI reduction by means of gate driver             | 113   |

|   |     | 5.2.1 Conventional passive approach to deal with EMI by means of    |       |

|   |     | gate driver                                                         | 113   |

|   |     | 5.2.2 Active Gate Driver (AGD) to deal with EMI by means of gate    |       |

|   |     | driver                                                              | 115   |

|   |     | 5.2.3 Inductive gate driver                                         | 120   |

|   | 5.3 | Proposed inductive feedback gate driver for EMI reduction           | 122   |

|   |     | 5.3.1 Operation principles and circuit configuration                | 122   |

|   |     | 5.3.2 Rogowski coil design and specification                        | 125   |

|   |     | 5.3.3 Experimental validation of rogowski coil                      | 130   |

|   |     | 5.3.4 Gate driver with integrated rogowski coil, simulation and ex- |       |

|   |     | perimental results                                                  | 133   |

|   |     | 5.3.5 Trade-off comparison between the proposed method and clas-    |       |

|   |     | sical increasing gate resistance                                    | 143   |

|   | 5.4 | Conclusion                                                          | 147   |

| • |     |                                                                     | 1 40  |

| 6 |     | nclusion and perspectives                                           | 149   |

|   | .1  | A 1' 1                                                              | 1 5 0 |

|   | 0   | Appendix chapter 2                                                  | 153   |

|   | .2  | Appendix chapter 3                                                  | 156   |

|   | .3  | Appendix chapter 5                                                  | 100   |

|   | .5  | Appendix chapter 4                                                  | 161   |

|   | .4  | Appendix chapter 4                                                  | 101   |

|   | .4  | Appendix chapter 5                                                  | 169   |

|   |     |                                                                     | 102   |

# List of Figures

| 1.1  | Converter applications in integrating the renewable energies to trans- |    |

|------|------------------------------------------------------------------------|----|

|      | mission and distribution grids [145]                                   | 2  |

| 1.2  | WBG comparison for high/medium voltage application [11]                | 3  |

| 1.3  | Converter energy loss per year for different solutions [87]            | 4  |

| 1.4  | Control unit and gate driver for medium/high voltage power semi-       |    |

|      | conductor                                                              | 5  |

| 1.5  | Control unit and intermediate gate driver circuit with push-pull for   |    |

|      | medium/high voltage power semiconductor                                | 6  |

| 1.6  | Turn-on transition of SiC MOSFET with push-pull circuit                | 7  |

| 1.7  | Turn-on transition intervals of SiC MOSFET                             | 8  |

| 1.8  | Turn-off transition of SiC MOSFET with push-pull circuit               | 9  |

| 1.9  | Turn-off transition intervals of SiC MOSFET                            | 10 |

| 1.10 | Switching transition considering switching losses and conduction       |    |

|      | losses                                                                 | 11 |

| 1.11 | Switching and conduction losses                                        | 12 |

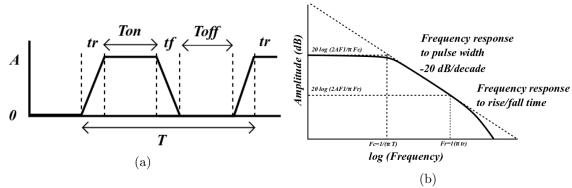

| 1.12 | Square waveform (a) Time domain representation (b) Frequency do-       |    |

|      | main spectral                                                          | 14 |

| 1.13 | Trapezoidal waveform (a) Time domain representation (b) Frequency      |    |

|      | domain spectral                                                        | 14 |

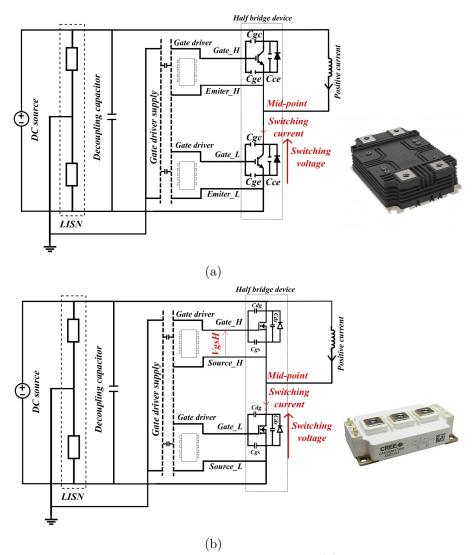

| 1.14 | Semiconductor characterising circuit (a) SiC MOSFET characteris-       |    |

|      | ing (b) IGBT characterising                                            | 15 |

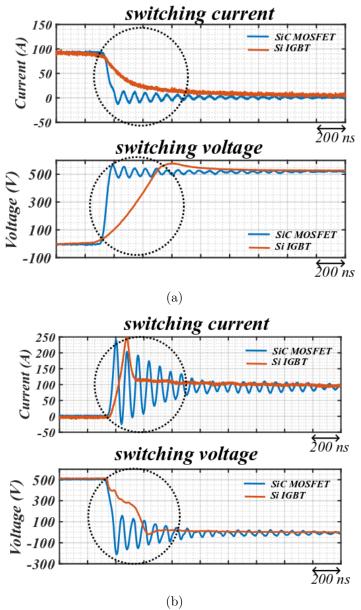

| 1.15 | Experimental comparison between switching characteristic of Si         |    |

|      | IGBT and SiC MOSFET in 500 V DC voltage, 100 A of load current         |    |

|      | (a) Turn-off transition (b) Turn-on transition                         | 16 |

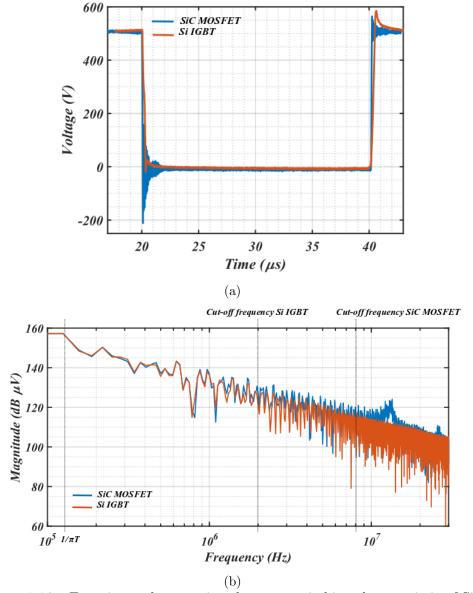

| 1.16 | Experimental comparison between switching characteristic of Si               |    |

|------|------------------------------------------------------------------------------|----|

|      | IGBT and SiC MOSFET in 500 V DC voltage, 100 A of load cur-                  |    |

|      | rent (a) Voltage time domain representation (b) Voltage frequency            |    |

|      | domain representation                                                        | 17 |

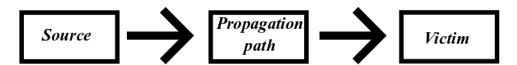

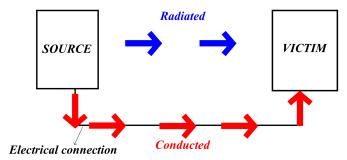

| 1.17 | Elements of EMC study                                                        | 18 |

| 1.18 | Conducted and radiated emissions                                             | 19 |

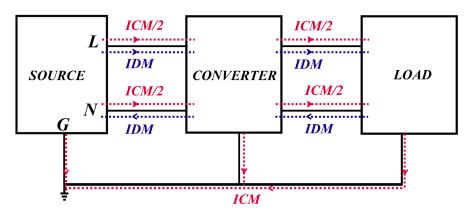

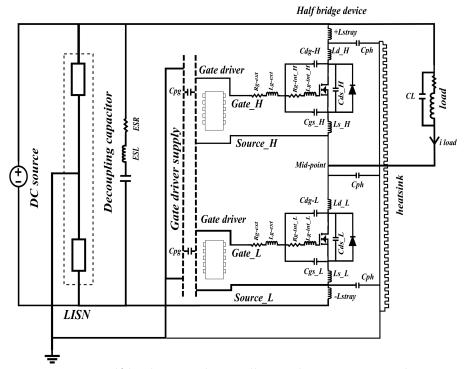

| 1.19 | Differential and Common-Mode in converter                                    | 19 |

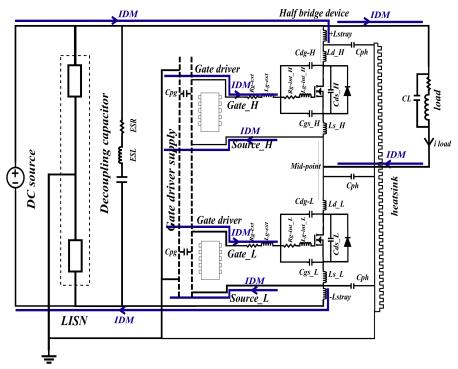

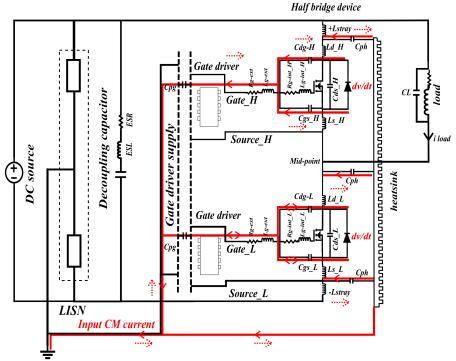

| 1.20 | Half bridge switching cell considering parasitic elements                    | 21 |

| 1.21 | Conducted emission, differential noise in switching cell                     | 22 |

| 1.22 | Conducted emission, common-mode noise in switching cell                      | 23 |

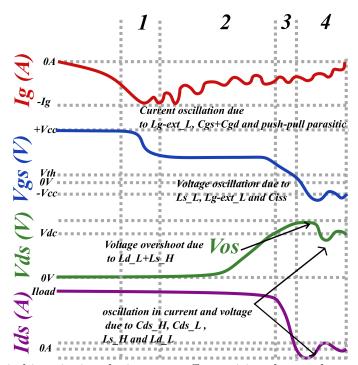

| 1.23 | Switching ringing during turn-on transition due to the parasitic ele-        |    |

|      | ments                                                                        | 24 |

| 1.24 | Switching ringing during turn-off transition due to the parasitic ele-       |    |

|      | ments.                                                                       | 25 |

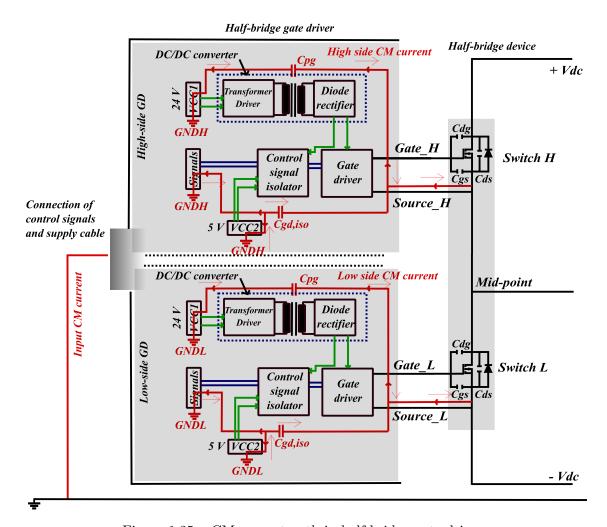

| 1.25 | CM current path in half-bridge gate driver                                   | 27 |

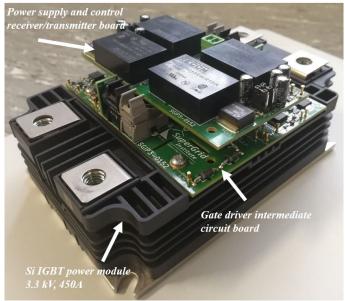

| 1.26 | IGBT gate driver prototype integrated with Si IGBT power module.             | 30 |

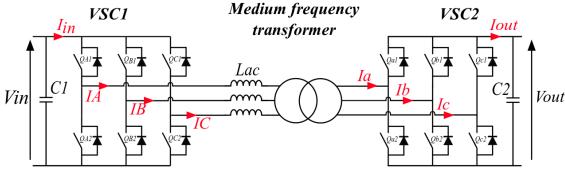

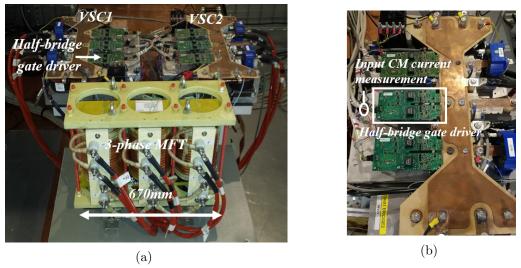

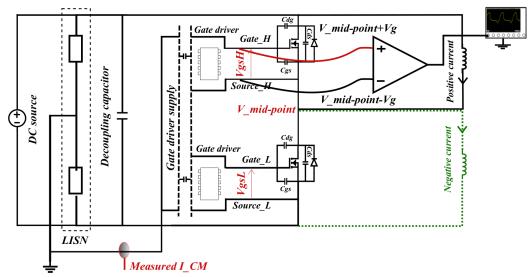

| 2.1  | DAB3 schematic                                                               | 35 |

| 2.2  | DAB3 prototype (a) Converter structure (b) Input CM current mea-             |    |

|      | surement                                                                     | 35 |

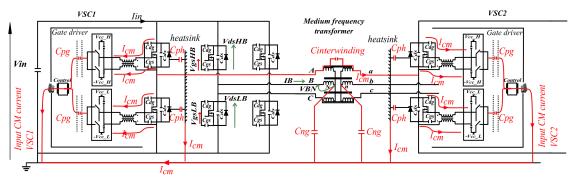

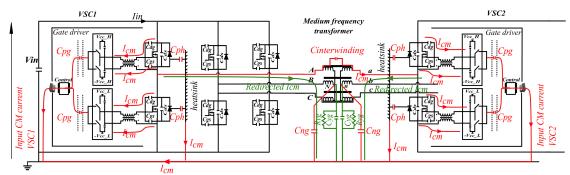

| 2.3  | Main CM current paths in a DAB3                                              | 39 |

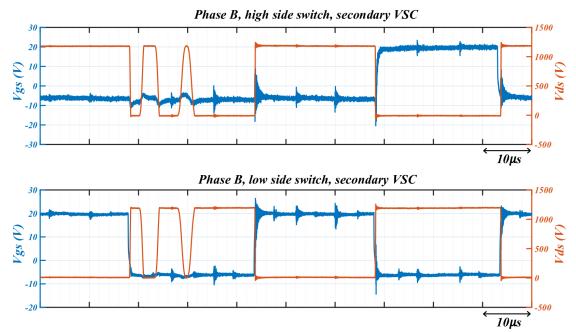

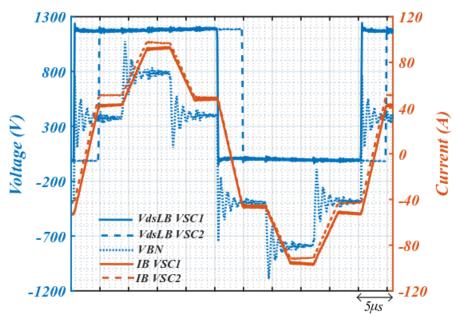

| 2.4  | Experiemental result of false triggering of SiC MOSFET in DAB3, 1200V, 100kW | 40 |

| 2.5  | Experimental results, input CM current, phase B of DAB3, 800V,               | 40 |

| 2.0  | 0kW                                                                          | 41 |

| 2.6  | Experimental results, input CM current, phase B of DAB3, 800V,               | 41 |

| 2.0  | 100kW                                                                        | 41 |

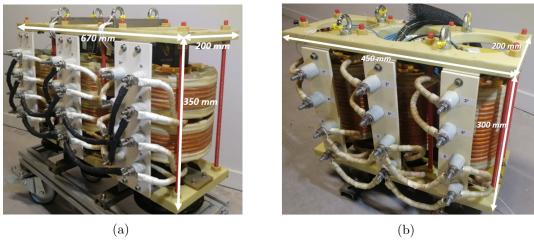

| 2.7  | Transformer prototypes, (a) T1 (b) T2                                        | 43 |

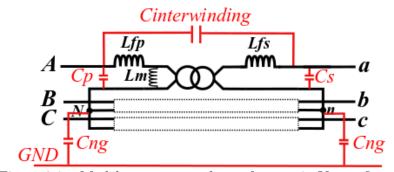

| 2.8  | Model parameters of transformers in Yy configuration                         | 43 |

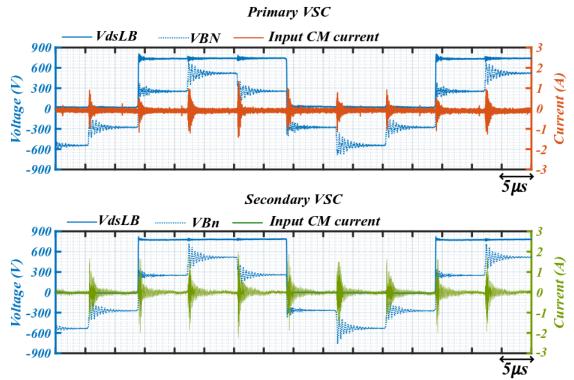

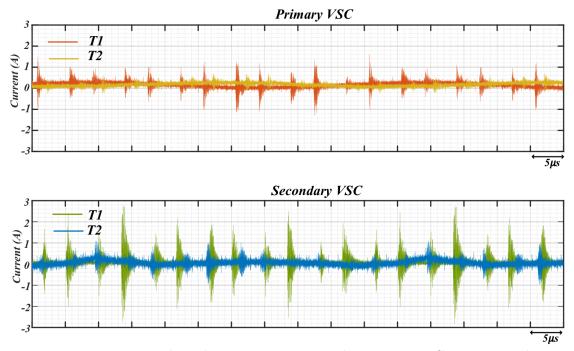

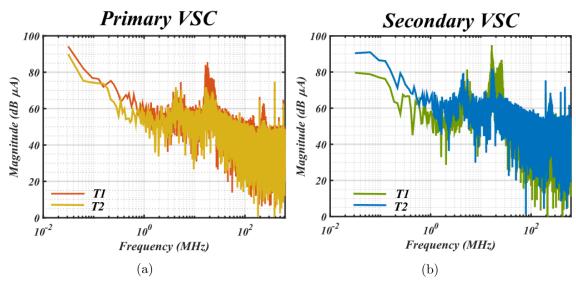

| 2.9  | Experimental results comparison, time domain, input CM current,              |    |

|      | phase B of DAB3 with two transformers, 800V, 100kW                           | 44 |

| 2.10 | Experimental results comparison, frequency domain, input CM cur-             |    |

|      | rent, phase B of DAB3 with two transformers, 800V, 100kW                     | 45 |

| 2.11 | Proposed ground layout modification for DAB3 (added components               |    |

|      | in green)                                                                    | 46 |

| 2.12 | Simulation results, DAB3, 800 V, 100 kW with proposed ground                 |    |

|      | layout modification (a) phase B, voltage across transformer (b) Phase        |    |

|      | B. current.                                                                  | 47 |

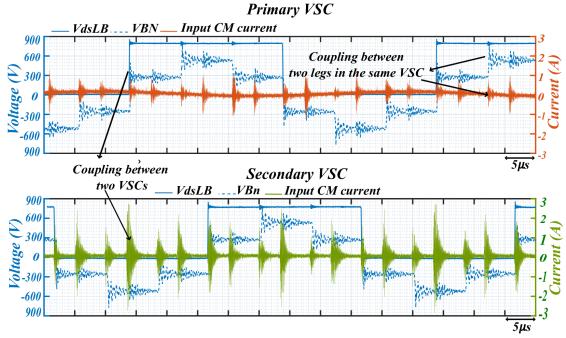

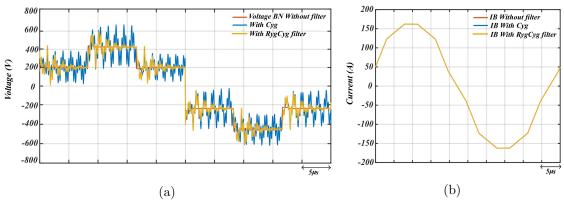

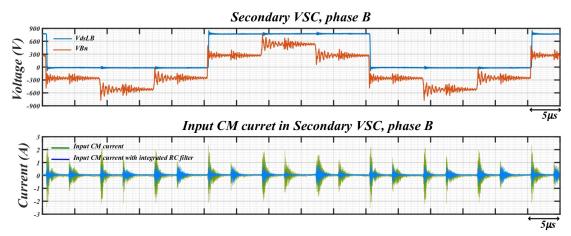

| 2.13 | Experimental results, time domain, DAB 3, 800 V, 100 kW, input CM current reduction in VSC2 and voltage in VSC1 and VSC2. |

|------|---------------------------------------------------------------------------------------------------------------------------|

| 2 14 | Experimental results, frequency domain, DAB3, 800 V, 100 kW, in-                                                          |

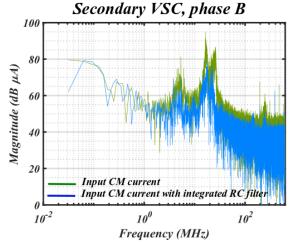

| 2.11 | put CM current reduction in VSC2 without RC filter and with RC                                                            |

|      | filter                                                                                                                    |

| 2.15 | Experimental results, DAB3, 800 V, 100 kW with proposed ground                                                            |

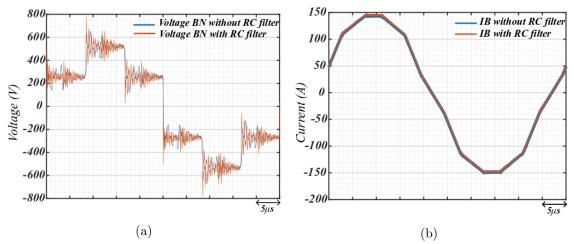

| 2.10 | layout modification (a) phase B, voltage across transformer (b) Phase                                                     |

|      | B, current                                                                                                                |

| 2.16 |                                                                                                                           |

| 2.10 | modification, 1200V, 100kW and T1 in Yy configuration                                                                     |

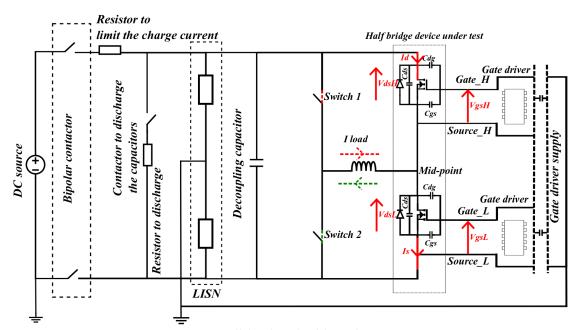

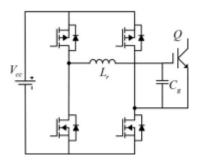

| 3.1  | Full-bridge double pulse test bench configuration                                                                         |

| 3.2  | Full-bridge double pulse test circuit                                                                                     |

| 3.3  | Double pulse inductive voltage and current waveform                                                                       |

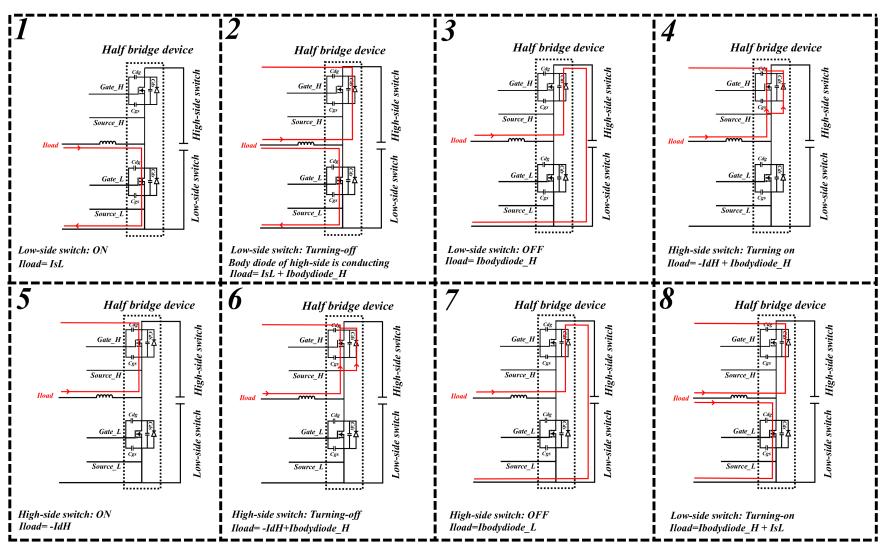

| 3.4  | Different steps in inductive double pulse test circuit                                                                    |

| 3.5  | Example of exhaustive EMI modelling [13]                                                                                  |

| 3.6  | Behavioural EMI modelling with 5 parameters (black box)                                                                   |

| 3.7  | Load impedance measurement (a) Impedance measurement (b)                                                                  |

|      | Equivalent circuit of load impedance                                                                                      |

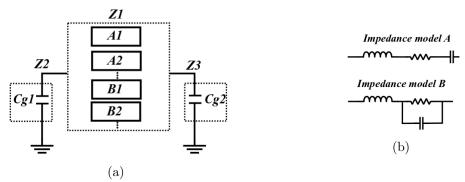

| 3.8  | Load model (a) load impedance structure (b) equivalent impedance                                                          |

|      | model generated by curve-fitting                                                                                          |

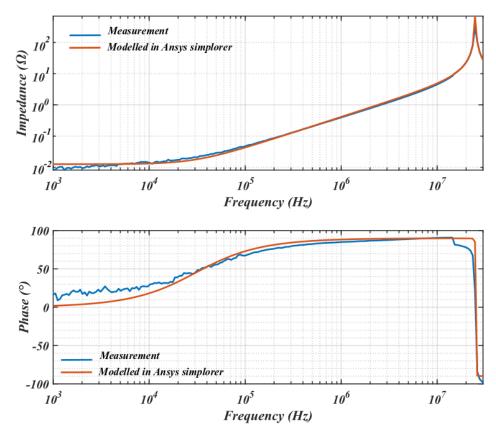

| 3.9  | Inductor modelling and comparison with impedance measurement                                                              |

|      | between the terminals of the load.                                                                                        |

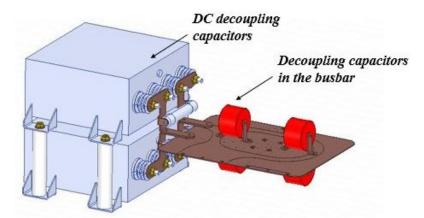

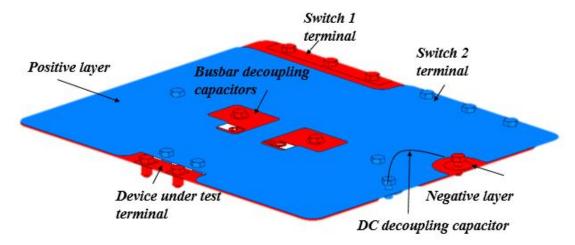

| 3.10 | Decoupling capacitors implemented into the busbar of the double                                                           |

|      | pulse test                                                                                                                |

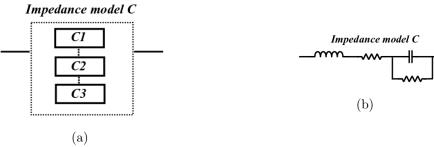

| 3.11 | Decoupling capacitors model (a) Capacitor impedance structure (b)                                                         |

|      | equivalent series resistance and inductance model                                                                         |

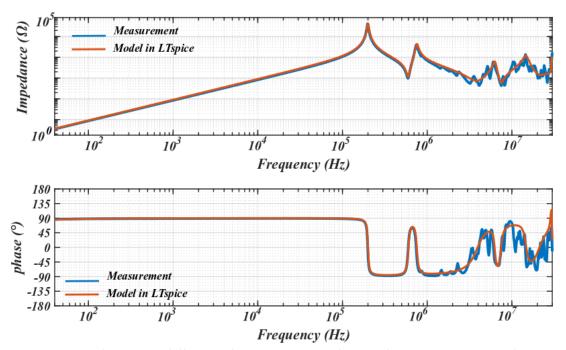

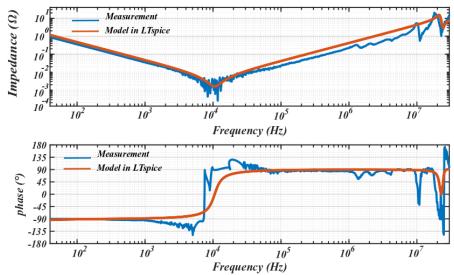

| 3.12 | Modelled decoupling capacitor, comparison of impedance measure-                                                           |

|      | ment and LTspice AC simulation.                                                                                           |

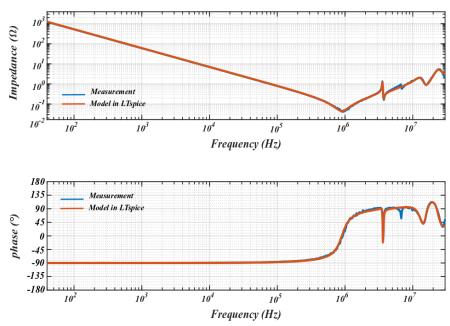

| 3.13 | Modelled decoupling capacitor in the busbar, comparison of                                                                |

|      | impedance measurement and LTspice AC simulation of calculated                                                             |

|      | equivalant model up to 30 MHz.                                                                                            |

| 3.14 | Busbar Q3D modelling                                                                                                      |

| 3.15 | Comparison of Modelled busbar and impedance measurement be-                                                               |

|      | tween the terminals of the device under test                                                                              |

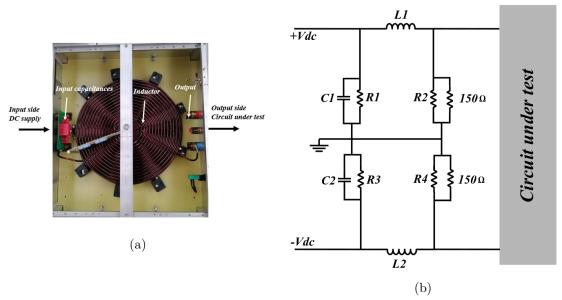

| 3.16 | Line Impedance Stabilization Network (a) Internal structure (b)                                                           |

|      | Equivalent circuit.                                                                                                       |

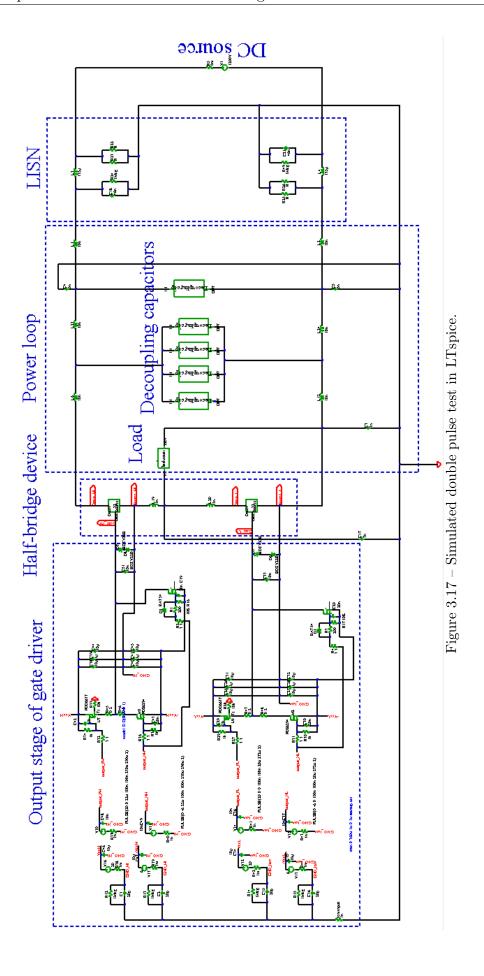

| 3.17 | Simulated double pulse test in LTspice.                                                                                   |

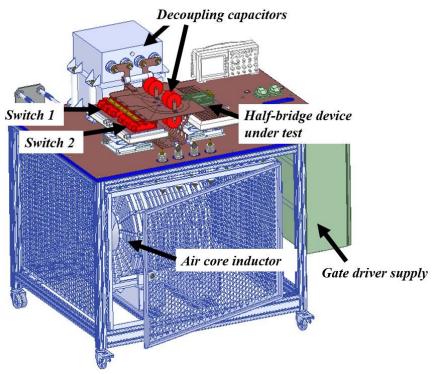

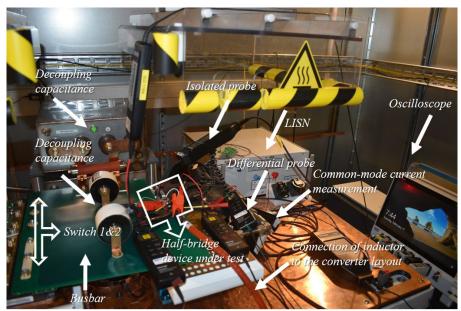

| 3.18 | Double pulse test bench, set-up                                                                                                                                                                                                                                                              | 71       |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

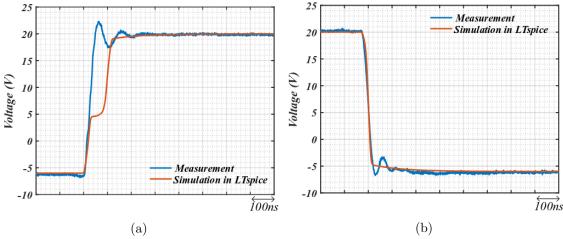

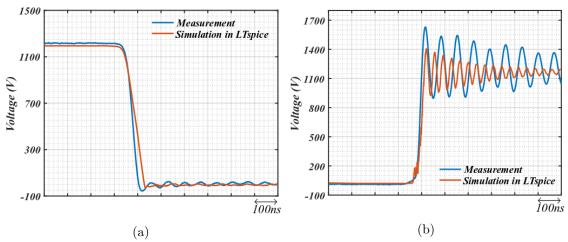

| 3.19 | Comparison between modelled double pulse test circuit and measurement, 1200 V, -200 A switching characteristics, uncontrolled switch (soft-switching condition) VgsL (a) Turn-on transition (b) Turn-off                                                                                     |          |

|      | transition                                                                                                                                                                                                                                                                                   | 71       |

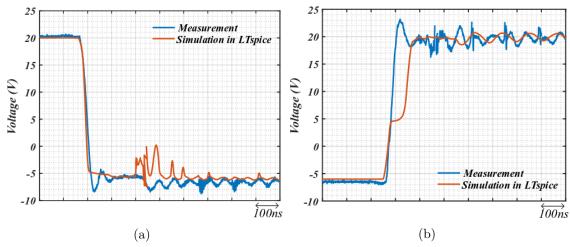

| 3.20 | Comparison between modelled double pulse test circuit and measurement, 1200 V, -200 A switching characteristics, controlled switch (hard-switching condition) VgsH (a) Turn-off transition (b) Turn-on transition                                                                            | 72       |

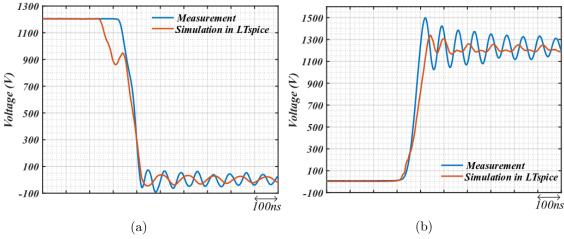

| 3.21 | Comparison between modelled double pulse test circuit and measurement, $1200~\rm V$ , $-200~\rm A$ switching characteristics, controlled switch (hard-switching condition), VdsH (a) Turn-on transition (b) Turn-off                                                                         |          |

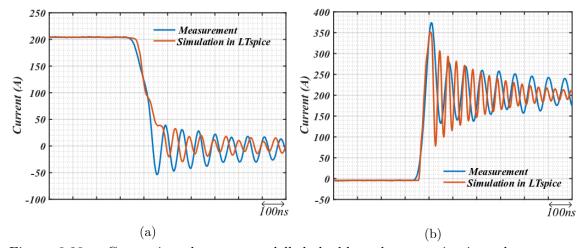

| 3.22 | transition                                                                                                                                                                                                                                                                                   | 72<br>73 |

| 3.23 | Comparison between modelled double pulse test circuit and measurement, 1200 V, -200 A switching characteristics, controlled switch (hard-switching condition) IdsH (a) Turn-off transition (b) Turn-on transition                                                                            | 73       |

| 3.24 | Comparison between modelled double pulse test circuit and measurement, 1200 V, -200 A switching characteristics, uncontrolled switch (soft-switching condition) IdsL (a) Turn-on transition (b) Turn-off transition                                                                          | 74       |

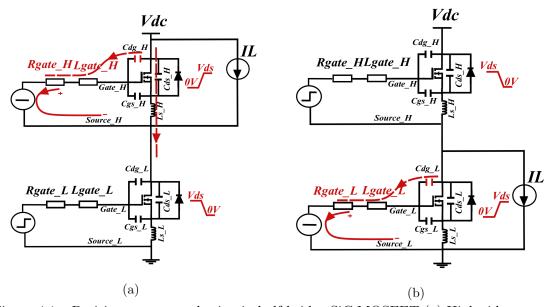

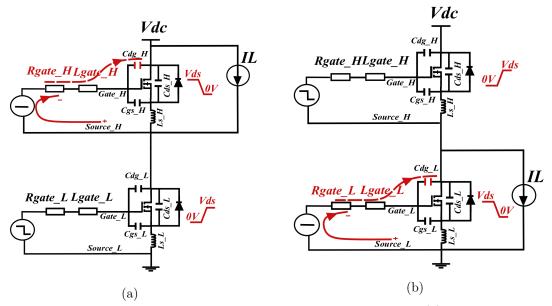

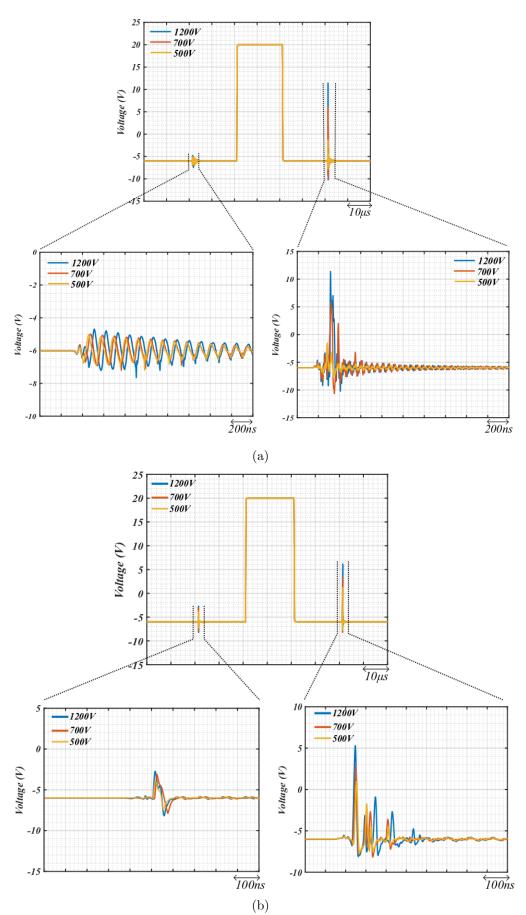

| 4.1  | Positive gate perturbation in half-bridge SiC MOSFET (a) High-side perturbation (low-side switch is controlled and high-side switch is in soft switching condition) (b) Low-side perturbation (high-side switch is controlled and low-side switch is a soft switching and live side switch). | 70       |

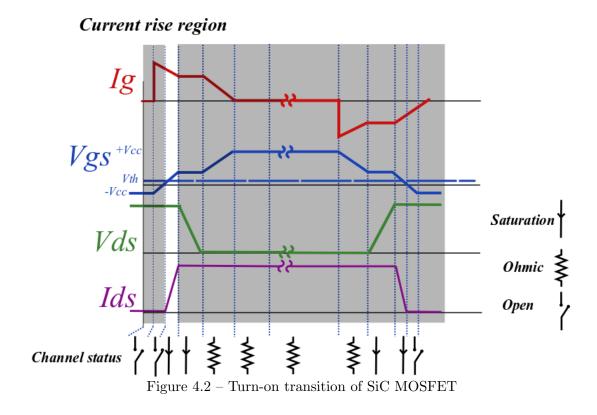

| 4.2  | is controlled and low-side switch is in soft switching condition) Turn-on transition of SiC MOSFET                                                                                                                                                                                           | 78<br>78 |

| 4.2  | Negative gate perturbation in half-bridge SiC MOSFET (a) High-side perturbation (low-side switch is controlled and high-side switch is in soft switching condition) (b) Low-side perturbation (high-side                                                                                     | IC       |

|      | switch is controlled and low-side switch is in soft switching condition).                                                                                                                                                                                                                    | 79       |

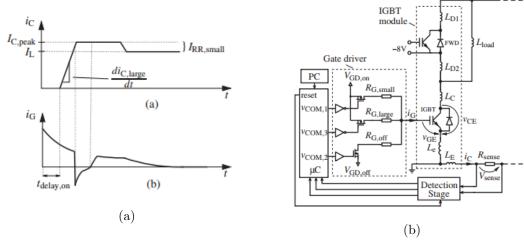

| 4.4  | Double pulse test set up for IGBT and MOSFET                                                                                                                                                                                                                                                 | 81       |

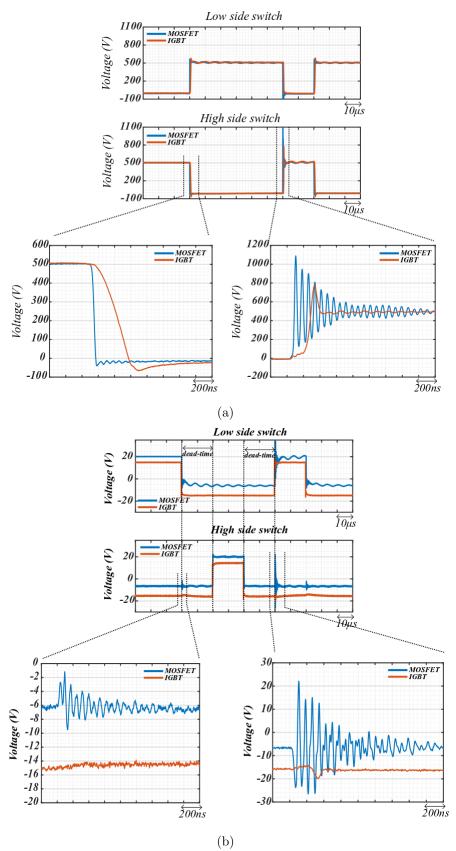

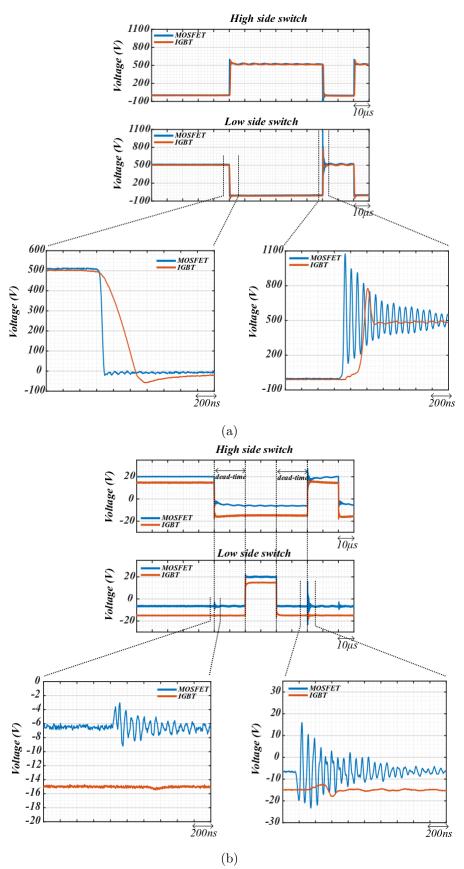

| 4.5  | Comparison between IGBT and MOSFET in double pulse test,                      |    |

|------|-------------------------------------------------------------------------------|----|

|      | 500  V, $+150  A$ (low-side switch is controlled in hard switching condi-     |    |

|      | tion, high-side switch is synchronous in soft-switching condition) (a)        |    |

|      | drain-source voltage comparison (b) gate-source voltage comparison.           | 82 |

| 4.6  | Comparison between IGBT and MOSFET in double pulse test,                      |    |

|      | 500 V, -150 A (high-side switch is controlled in hard switching con-          |    |

|      | dition, low-side switch is synchronous in soft-switching condition)(a)        |    |

|      | drain-source voltage comparison (b) gate-source voltage comparison.           | 83 |

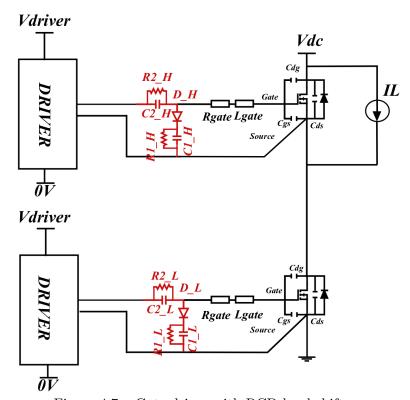

| 4.7  | Gate driver with RCD level shifter                                            | 85 |

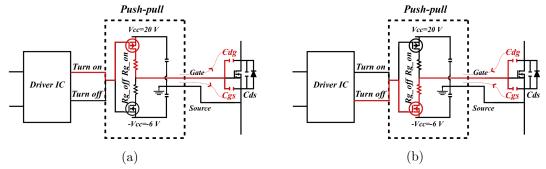

| 4.8  | Output stage of gate driver with push-pull (totem-poll) (a) Turn-on           |    |

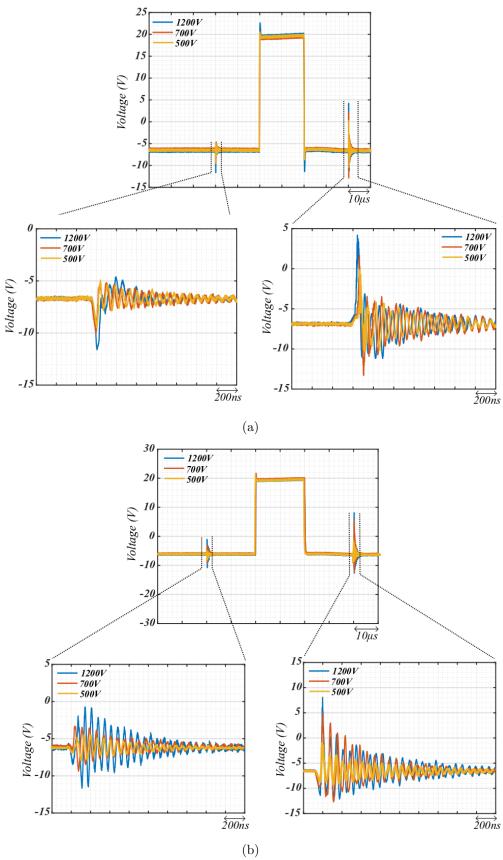

|      | transition in push-pull (b) Turn-off transition in push-pull                  | 87 |

| 4.9  | Gate driver with integrated assistant circuit for self-disturbance [184].     | 87 |

| 4.10 | Gate driver with integrated assistant circuit for self-disturbance [184].     | 88 |

| 4.11 | Gate driver with proposed integrated Miller clamp protection assis-           |    |

|      | tant circuit.                                                                 | 89 |

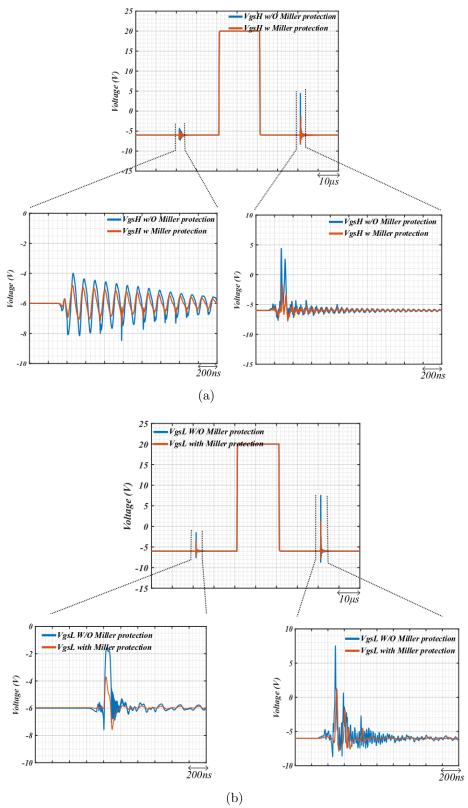

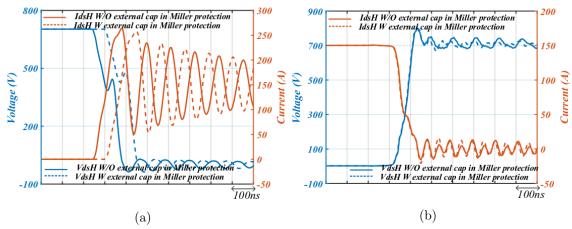

| 4.12 | Simulation results of comparison between the gate driver with (W)             |    |

|      | with Miller clamp integrated circuit and without $(W/O)$ Miller clamp         |    |

|      | integrated circuit, double pulse test, $500~\mathrm{V}$ (a) VgsH (synchronous |    |

|      | switch, soft switching condition) in +150 A (b) VgsL (synchronous             |    |

|      | switch, soft switching condition) in -150 A                                   | 90 |

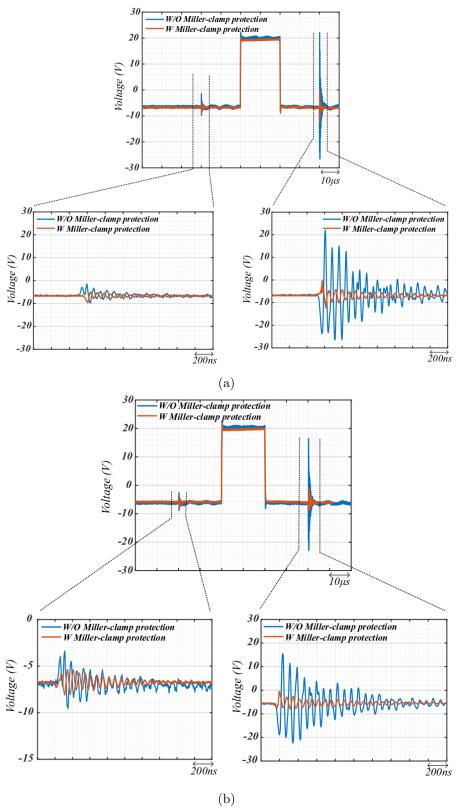

| 4.13 | Experimental results of comparison between the gate driver with (W)           |    |

|      | with Miller clamp integrated circuit and without $(W/O)$ Miller clamp         |    |

|      | integrated circuit, double pulse test, $500~\mathrm{V}$ (a) VgsH (synchronous |    |

|      | switch, soft switching condition) in $+150~\mathrm{A}$ (b) VgsL (synchronous  |    |

|      | switch, soft switching condition) in -150 A                                   | 92 |

| 4.14 | Simulation results with Miller clamp integrated circuit, double pulse         |    |

|      | test, 500 V, 700 V, 1200 V (a) VgsH in +150 A (b) VgsL in -150 A.             | 93 |

| 4.15 | Experimental results with Miller clamp integrated circuit, double             |    |

|      | pulse test, 500 V, 700 V, 1200 V (a) VgsH in $+150$ A (b) VgsL in             |    |

|      | -150 A                                                                        | 94 |

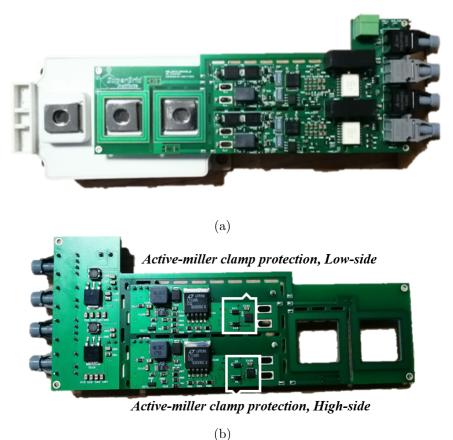

| 4.16 | Miller clamp protection circuit with added capacitance in green. $\ .$ $\ .$  | 95 |

| 4.17 | Gate driver with proposed integrated Miller clamp protection assis-           |    |

|      | tant circuit (a) front view (b) back view                                     | 95 |

| 4.18 | Double pulse test schematic during VgsH measurement                           | 97 |

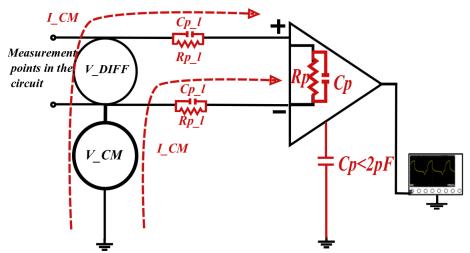

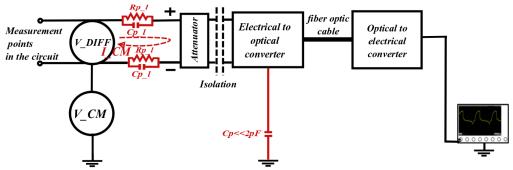

| 4.19 | Conventional differential probe                                               | 98 |

| 4.20 | Isolated differential probe                                                   | gg |

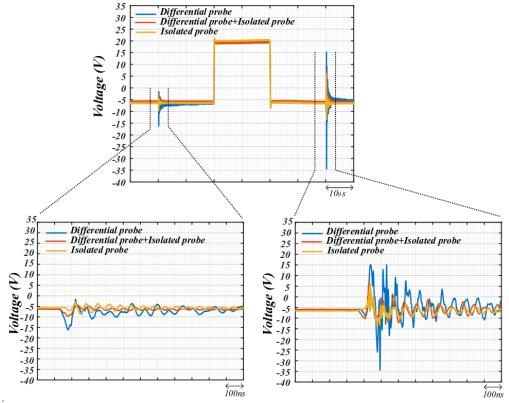

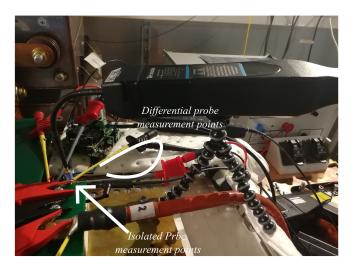

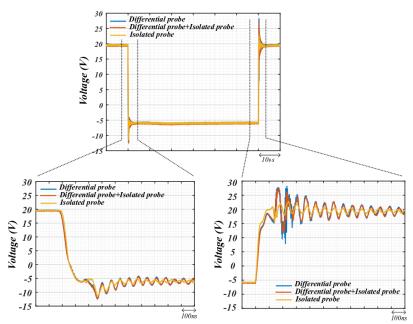

| 4.21 | VgsH experimental comparison of conventional differential probe and             | 100 |

|------|---------------------------------------------------------------------------------|-----|

| 4.00 | isolated probe, double pulse test, 1200 V, +150 A                               | 100 |

| 4.22 | Compare the inductance loop due to measurement techniques (a)                   |     |

|      | twisted probe lead in conventional differential probe (b) inductance            | 101 |

|      | loop comparison between two technologies of the differential probe.             | 101 |

| 4.23 | Shielded solid metal connector system for isolated differential mea-            |     |

|      | surement [149]                                                                  | 101 |

| 4.24 | VgsH experimental comparison between conventional differential                  |     |

|      | probe and isolated probe, double pulse test, 1200 V, -150 A                     | 102 |

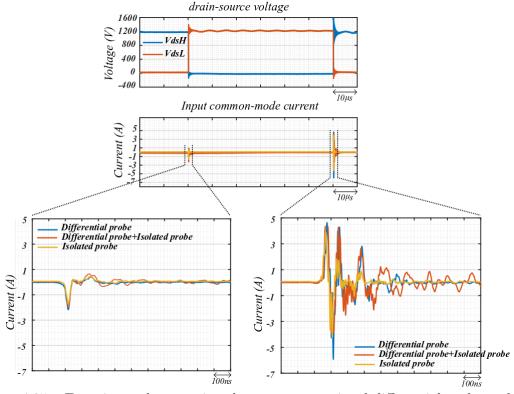

| 4.25 | Experimental comparison between conventional differential probe                 |     |

|      | and isolated probe, Common-mode current of gate driver, in 1200 V,              |     |

|      | +150  A double pulse test.                                                      | 102 |

| 4.26 | Gate driver with proposed integrated Miller clamp protection assis-             |     |

|      | tant circuit for self-disturbance and proposed solution in green                | 104 |

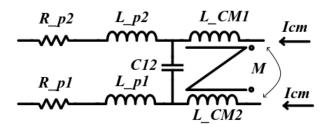

|      | Equivalent circuit model of a CM inductor                                       | 104 |

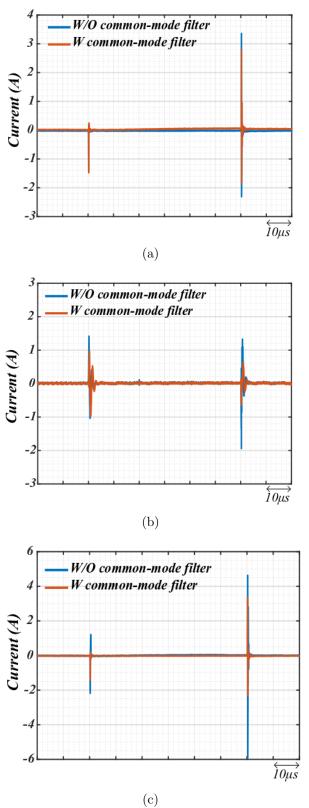

| 4.28 | Experimental comparison of ICM between the gate driver without                  |     |

|      | (W/O) CM choke and the gate driver with (W) CM choke, Double                    |     |

|      | pulse test, 1200 V, +150 A (a) ICMH (b) ICML (c) ICM-input                      | 105 |

| 4.29 | Experimental comparison of ICM between the gate driver without                  |     |

|      | (W/O) CM choke and the gate driver with (W) CM choke, Double                    |     |

|      | pulse test, 1200 V, -150 A (a) ICMH (b) ICML (c) ICM-input                      | 106 |

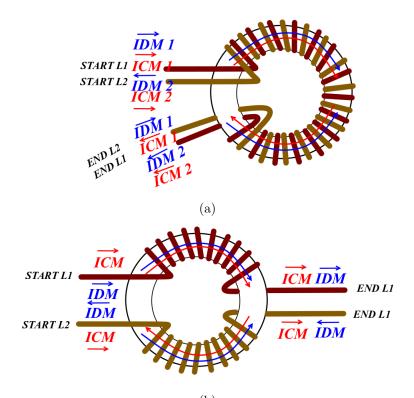

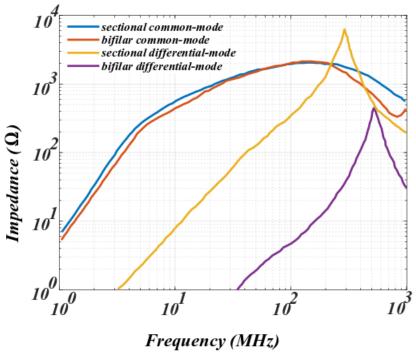

| 4.30 | CM inductor (a) Bifilar winding (b) Sectional winding                           | 107 |

| 4.31 | Impedance comparison                                                            | 108 |

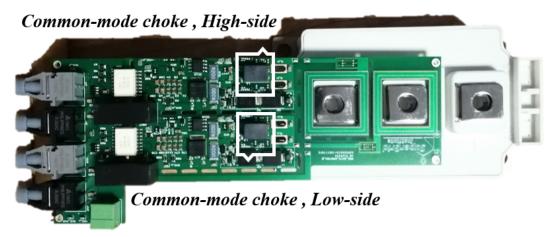

| 4.32 | Embedded CM choke in gate drive prototype                                       | 108 |

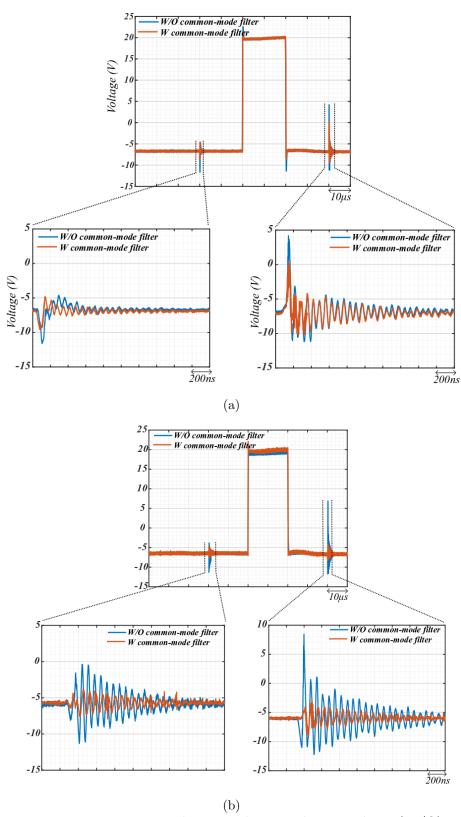

| 4.33 | Vgs comparison between the gate driver without (W/O) integrated                 |     |

|      | CM choke and the gate driver with (W) integrated CM choke, Double               |     |

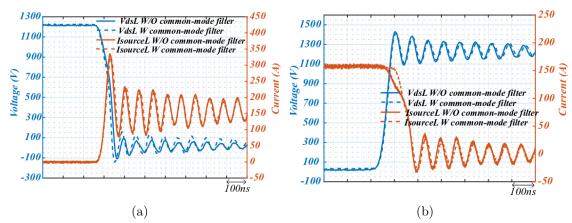

|      | pulse test in 1200 V(a) VgsH at +150 A (b) VgsL at -150 A $$                    | 109 |

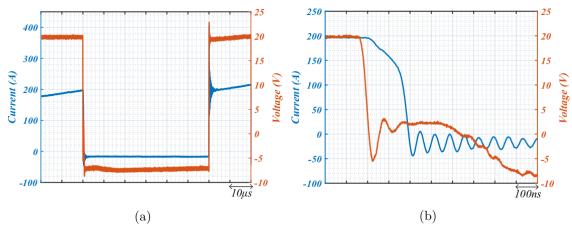

| 4.34 | ${ m Vds}$ and ${ m Is}$ comparison between the gate driver without (W/O) inte- |     |

|      | grated CM choke and the gate driver with (W) integrated CM choke,               |     |

|      | Double pulse test in 1200 V, $+150$ A (a) VdsL Vs. IdsL turn-on tran-           |     |

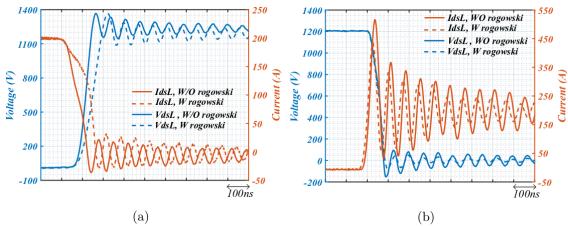

|      | sition (b) VdsL Vs with Ids turn-off transition                                 | 110 |

| 4.35 | Vds and Id comparison between the gate driver without (W/O) inte-               |     |

|      | grated CM choke and the gate driver with (W) integrated CM choke,               |     |

|      | -150 A (a) VdsH with IdH turn-on transition (b) VdsH Vs. IdsH                   |     |

|      | turn-off transition                                                             | 110 |

| 5.1  | Resonant current gate-driver circuit [42]                                       | 114 |

| 5.2  | Open-loop concept gate driver.                                                  | 115 |

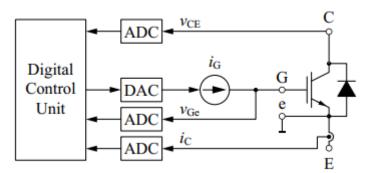

| 5.3  | Gate driver with open-loop control and discrete gate resistance      | 116  |

|------|----------------------------------------------------------------------|------|

| 5.4  | Miller-plateau regions in MOSFET switching transition                | 116  |

| 5.5  | Digital gate driver unit with Analogue to Digital converters (ADC)   |      |

|      | for measuring current and voltage of device and Digital to Analogue  |      |

|      | converters (DAC) for controlling the gate current [101]              | 117  |

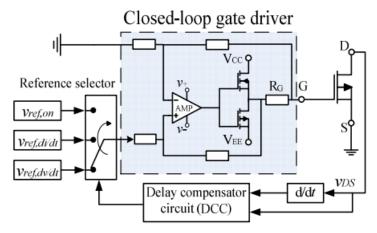

| 5.6  | Schematic of Closed-loop SiC MOSFET gate driver [123]                | 118  |

| 5.7  | Block diagram of the proposed control schematic [130]                | 118  |

| 5.8  | Negative Gate Current closed-loop approach (a) main principal (b)    |      |

|      | control schematic [24]                                               | 119  |

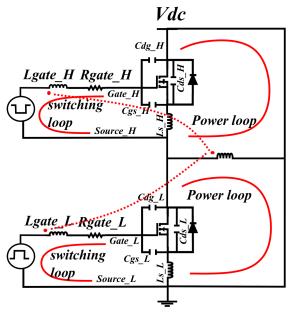

| 5.9  | Switching loop and power loop in a half-bridge device                | 120  |

| 5.10 | Inductive boost gate driver approach schematic [44]                  | 121  |

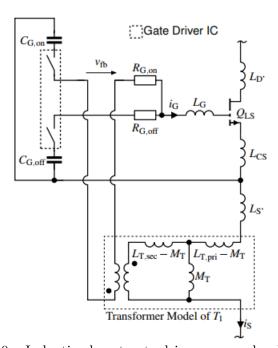

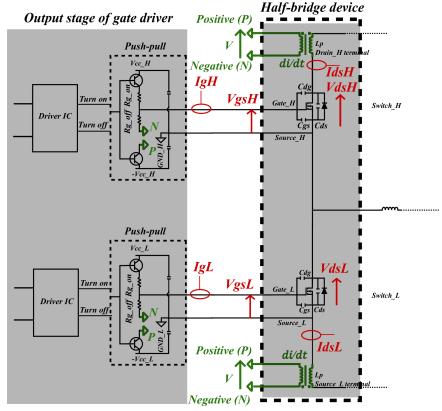

| 5.11 | Inductive feedback gate driver                                       | 123  |

| 5.12 | Inductive feedback gate driver, turn-on transition (proposed method  |      |

|      | modification in green)                                               | 124  |

| 5.13 | Inductive feedback gate driver, turn-off transition (proposed method |      |

|      | modification in green)                                               | 125  |

| 5.14 | Equivalent circuit of a rogowski coil                                | 126  |

| 5.15 | Device under test terminals, 1.7 kV SiC MOSFET power module [168]    | .126 |

| 5.16 | Different winding of PCB rogowski coil (a) With return-wire winding  |      |

|      | (b) Bifilar winding [62]                                             | 127  |

| 5.17 | PCB rogowski winding process                                         | 127  |

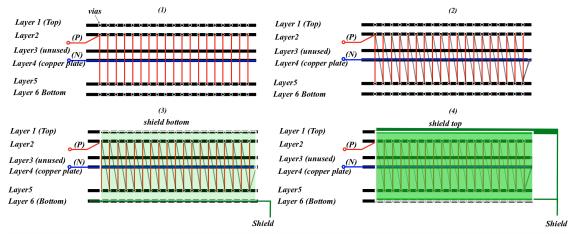

| 5.18 | PCB rogowski coil (a) top view (b) cross-section view                | 128  |

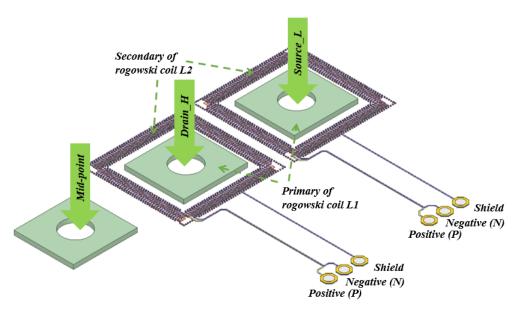

| 5.19 | Implementing Rogowski to the terminal of device                      | 128  |

| 5.20 | Shielded rogowski coil                                               | 129  |

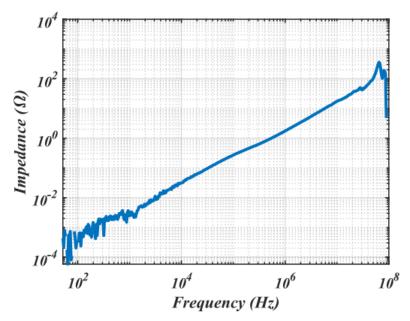

| 5.21 | Impedance measurement of PCB Rogowski                                | 130  |

| 5.22 | Measuring created voltage by means of rogowski coil                  | 131  |

| 5.23 | Experimental results of generated voltage with rogowski coil, double |      |

|      | pulse test, 1200 V, $+50$ A, $+100$ A, $+200$ A. (a) IdsL (b) VpnL   | 132  |

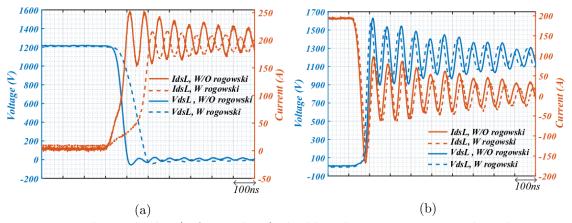

| 5.24 | VgsH with IgH, double pulse test, simulation, 1200 V, -200 A, com-   |      |

|      | paring between without coupling (W/O) and with coupling (W) (a)      |      |

|      | Turn-on transition (b) Turn-off transition                           | 133  |

| 5.25 | VdsH with IdsH, double pulse test, simulation, 1200 V, -200 A, com-  |      |

|      | paring between (W/O) without coupling and (W) coupling (a) Turn-     |      |

|      | on transition (b) Turn-off transition                                | 134  |

| 5.26 | VdsL with IdsL, double pulse test, simulation, 1200 V, -200 A, com-  |      |

|      | paring between (W/O) without coupling and (W) coupling (a) Turn-     |      |

|      | off transition (b) Turn-on transition                                | 134  |

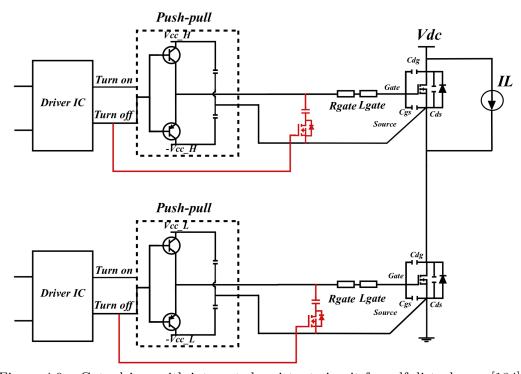

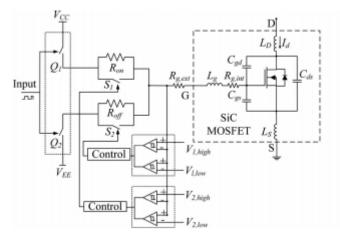

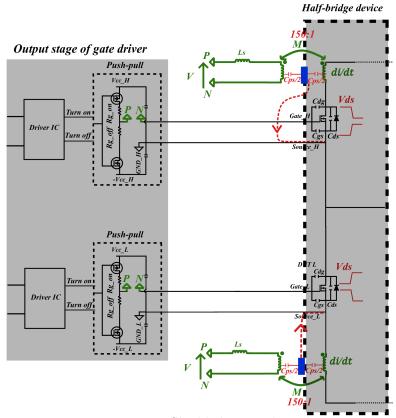

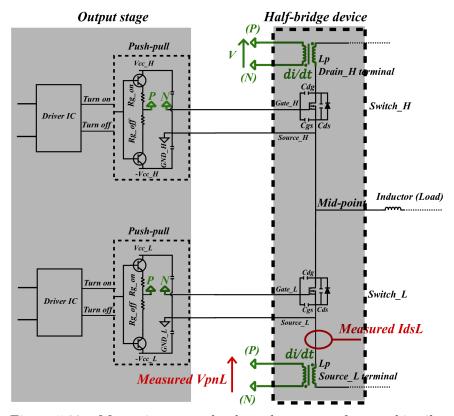

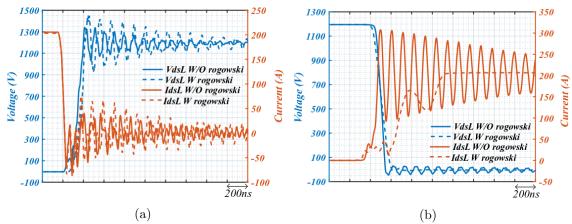

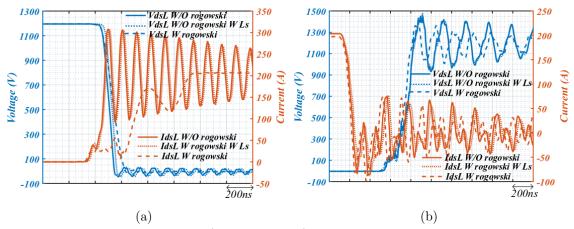

| 5.27 | Integrating the rogowski coil to turn-off path of push-pull in output                                       |     |

|------|-------------------------------------------------------------------------------------------------------------|-----|

|      | stage of gate driver                                                                                        | 135 |

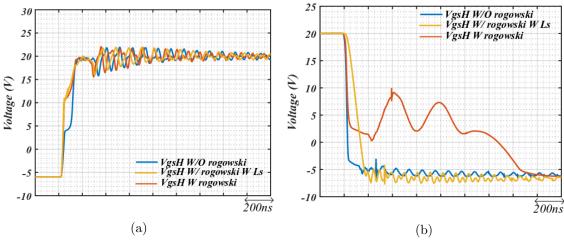

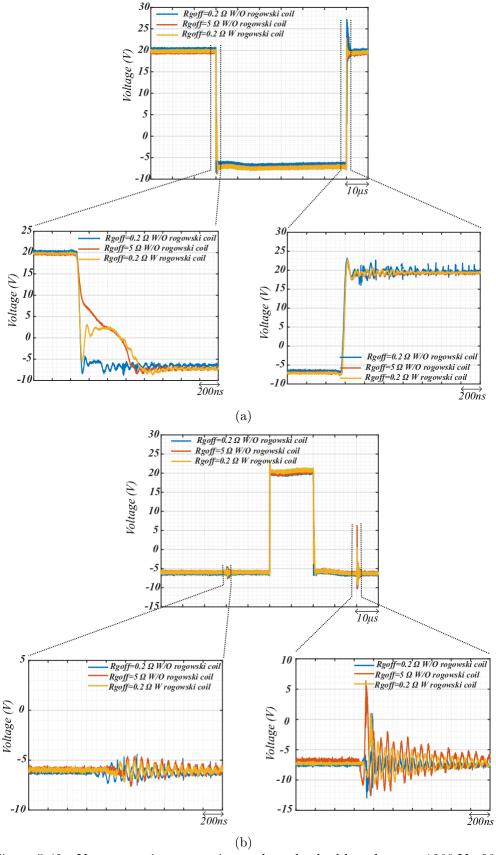

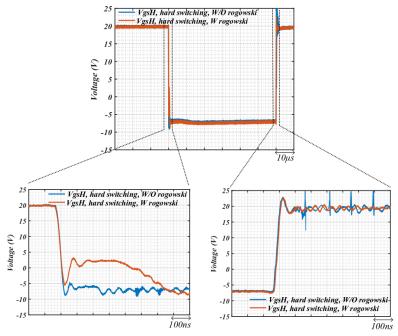

| 5.28 | Vgs comparison (hard switching), double pulse test, simulation, 1200                                        |     |

|      | V, -200 A, comparison between (W/O) without coupling, (W) with                                              |     |

|      | added inductor due to secondary of rogowski (Ls) and (W) coupling,                                          |     |

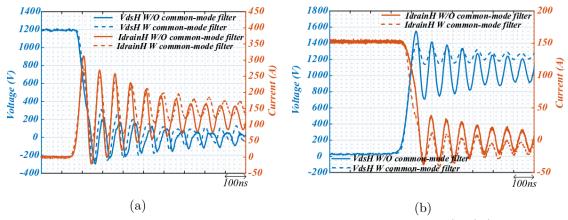

|      | (a) Turn-on transition (b) Turn-off transition                                                              | 136 |

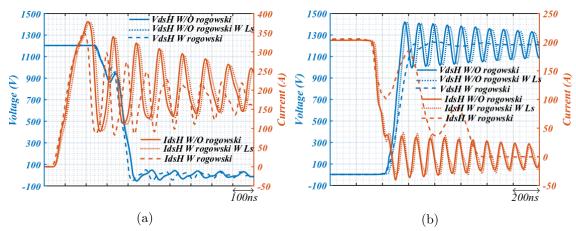

| 5.29 | VdsH with IdH (hard switching), double pulse test, simulation, 1200                                         |     |

|      | V, -200 A, comparison between (W/O) without coupling, (W) with                                              |     |

|      | added inductor due to secondary of rogowski (Ls) and (W) coupling,                                          |     |

|      | (a) Turn-on transition (b) Turn-off transition                                                              | 136 |

| 5.30 | VdsL with IdsL (soft switching), double pulse test, simulation, 1200                                        |     |

|      | V, -200 A, comparison between (W/O) without coupling, (W) with                                              |     |

|      | added inductor due to secondary of rogowski (Ls) and (W) coupling,                                          |     |

|      | (a) Turn-on transition (b) Turn-off transition                                                              | 137 |

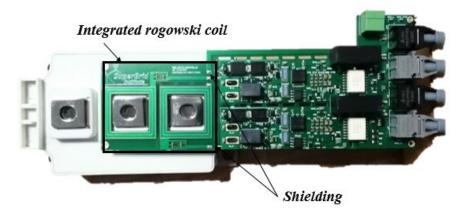

| 5.31 | Gate driver for SiC MOSFET with integrated rogowski coil                                                    | 137 |

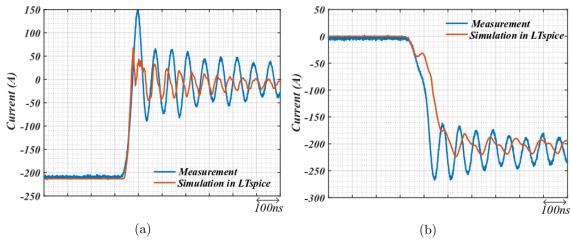

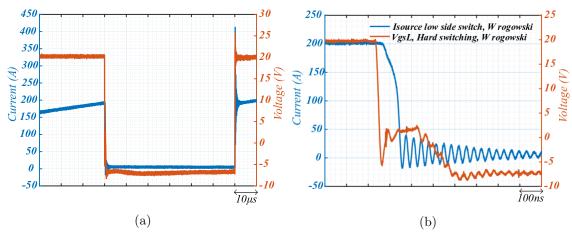

| 5.32 | VgsL with IsL (hard switching), experimental result, double pulse                                           |     |

|      | test, 1200 V, +200 A, rogowski coil integrated to gate driver (a)                                           |     |

|      | switching transition (b) Turn-off transition                                                                | 138 |

| 5.33 | VgsL comparison (hard switching), experimental result, double pulse                                         |     |

|      | test, 1200 V, $+200$ A, Comparison VgsL (W/O) rogowski coil and                                             |     |

|      | (W) with rogowski coil integrated to gate driver                                                            | 138 |

| 5.34 | VdsL with IsL, double pulse test, experimental result, $1200 \text{ V}$ , $+200 \text{ V}$                  |     |

|      | A, comparing between (W/O) without rogowski coil and (W) ro-                                                |     |

|      | gowski coil integrated to gate driver, (a) Turn-off transition (b) Turn-                                    |     |

|      | on transition                                                                                               | 139 |

| 5.35 | VdsH with IdH, double pulse test, experimental result, $1200 \text{ V}$ , $+200 \text{ V}$                  |     |

|      | A, comparing between (W/O) without rogowski coil and (W) ro-                                                |     |

|      | gowski coil integrated to gate driver, (a) Turn-on transition (b) Turn-                                     |     |

|      | off transition                                                                                              | 139 |

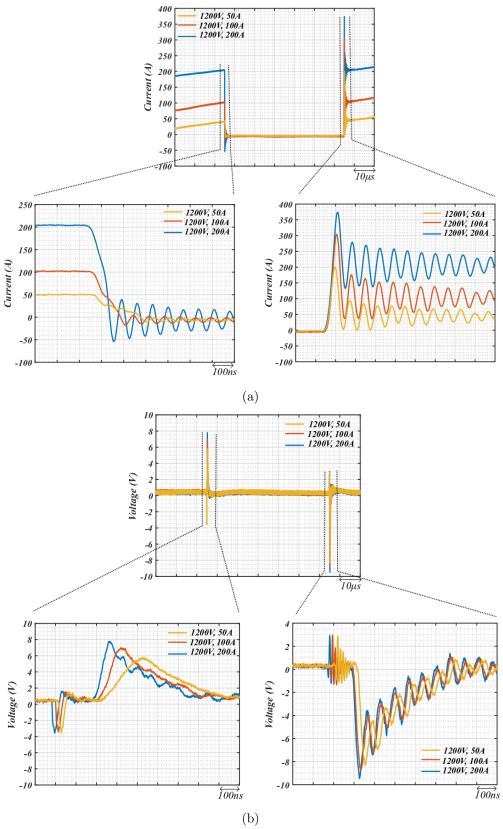

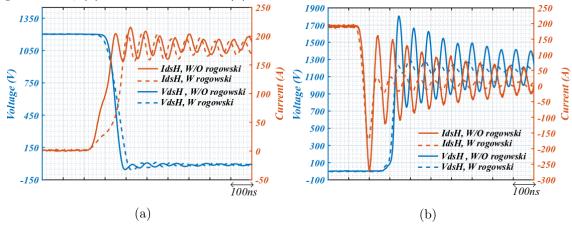

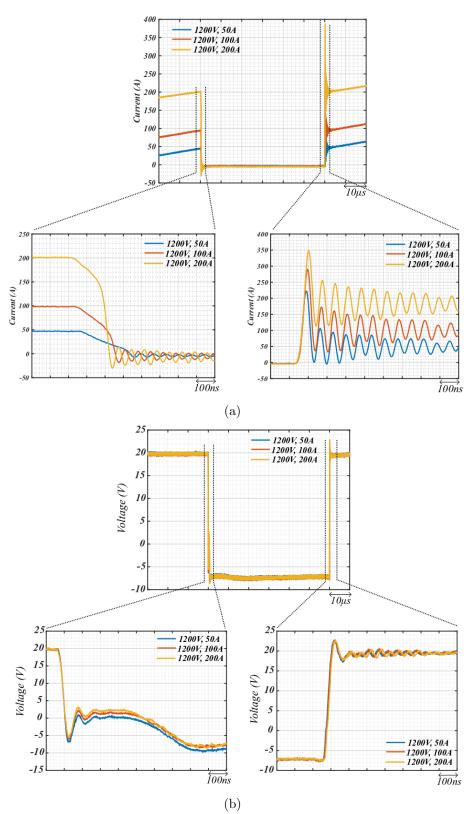

| 5.36 | IsL and VgsL (hard switching), experimental result, double pulse                                            |     |

|      | test, gate driver with integrated rogowski coil, $1200 \text{ V}$ , $+50 \text{ A}$ , $+100 \text{ C}$      |     |

|      | A, +200 A (a) IdsL (b) VgsL                                                                                 | 140 |

| 5.37 | Vds measurement, experimental result, double pulse test, gate driver                                        |     |

|      | with integrated rogowski coil, $1200 \text{ V}$ , $+50 \text{ A}$ , $+100 \text{ A}$ , $+200 \text{ A}$ (a) |     |

|      | VdsH (soft switching) (b) VdsL (hard switching)                                                             | 141 |

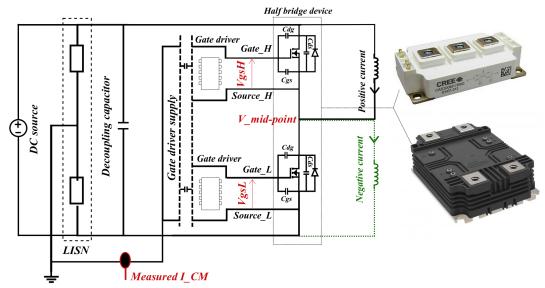

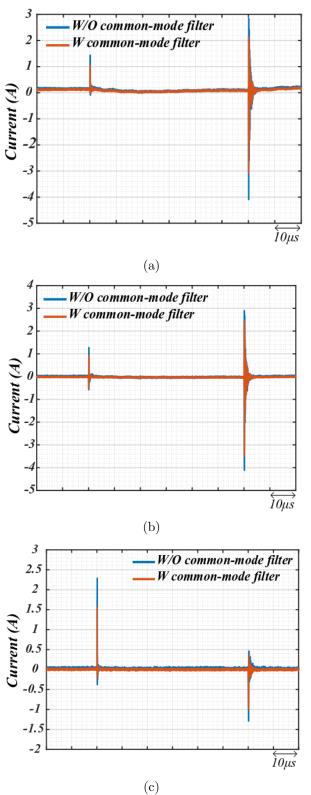

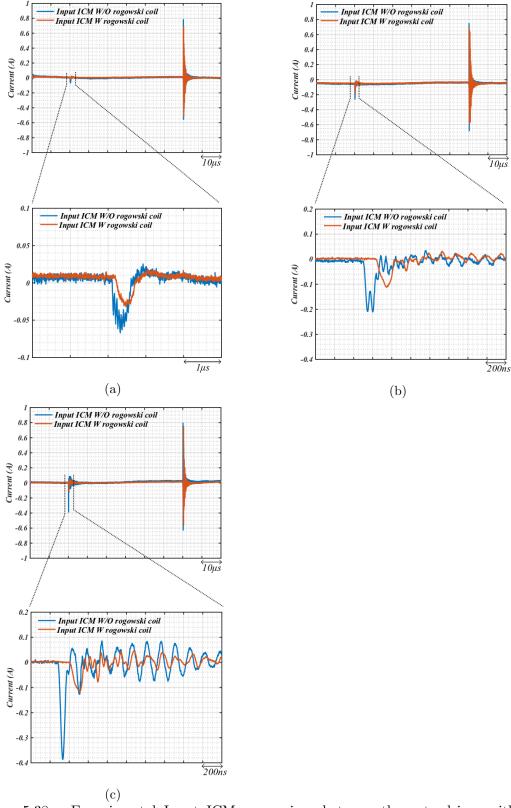

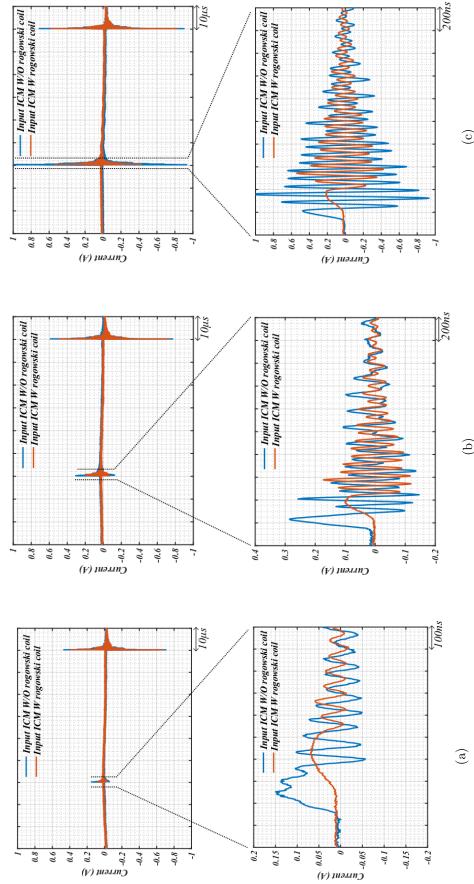

| 5.38        | Experimental Input ICM comparison between the gate driver with-              |      |

|-------------|------------------------------------------------------------------------------|------|

|             | out (W/O) integrated rogowski coil and with gate driver with (W)             |      |

|             | integrated rogowski coil, Double pulse test, 1200 V (a) +50 A (b)            | 1.40 |

| <b>-</b> 00 | +100 A (c) +200 A                                                            | 142  |

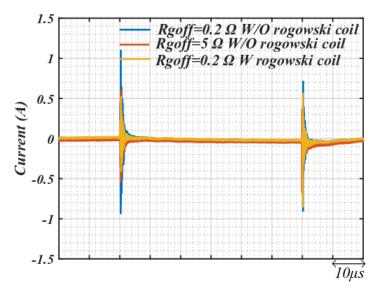

| 5.39        | Input CM current comparison, experimental result, double pulse test,         |      |

|             | 1200V, -200A                                                                 | 143  |

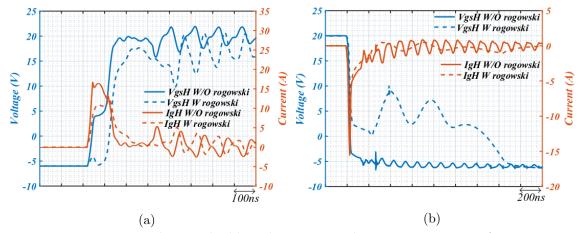

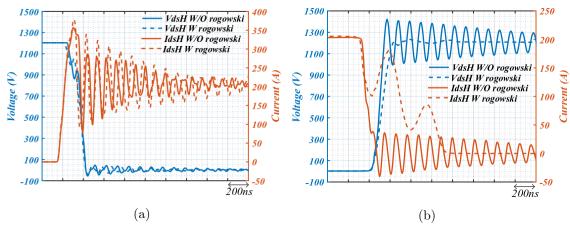

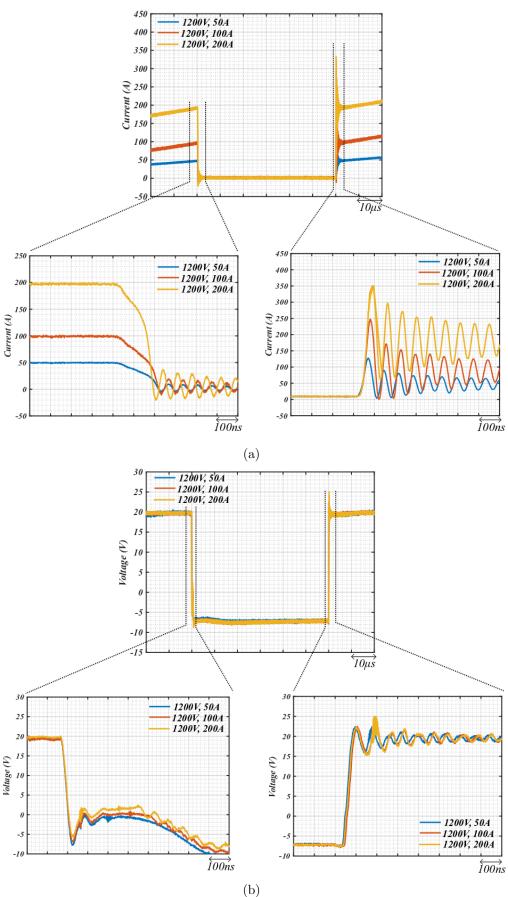

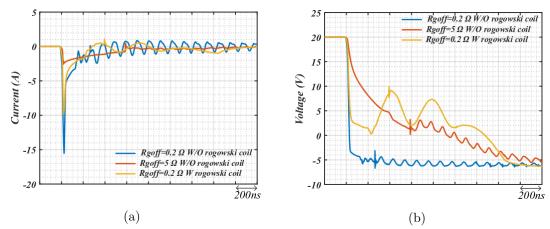

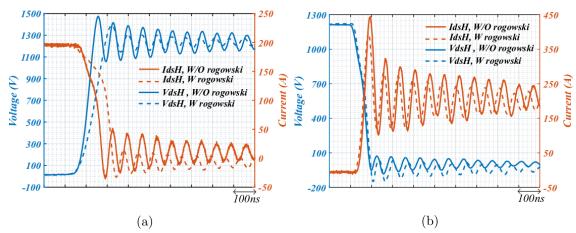

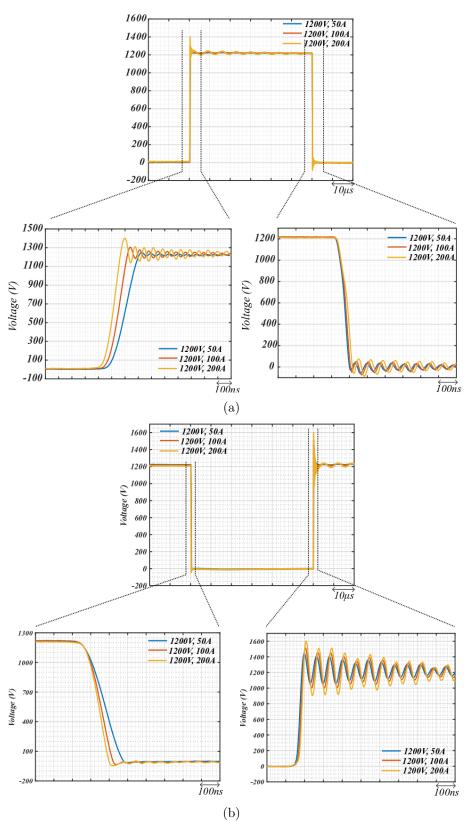

| 5.40        | VdsH with IdsH comparison (hard switching), experimental result,             |      |

|             | double pulse test, 1200 V, -200 A, comparison between gate driver            |      |

|             | (W/O) without rogowski and (W) with integrated rogowski coil (a)             |      |

|             | VdsH comparison (b) IdsH comparison                                          | 144  |

| 5.41        | IgH and VgsH (hard switching) during turn-off transition, simula-            |      |

|             | tion result, double pulse test, 1200 V, -200 A, comparison between           |      |

|             | gate driver (W/O) without rogowski and Rgoff=0.2 $\Omega$ , (W/O) with       |      |

|             | increased Rgoff=5 $\Omega$ and gate driver (W) with integrated rogowski      |      |

|             | with Rgoff=0.2 $\Omega$ (a) IgH comparison (b) VgsH comparison               | 145  |

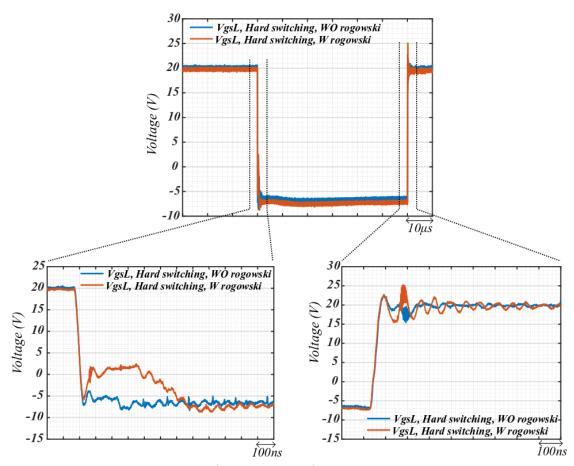

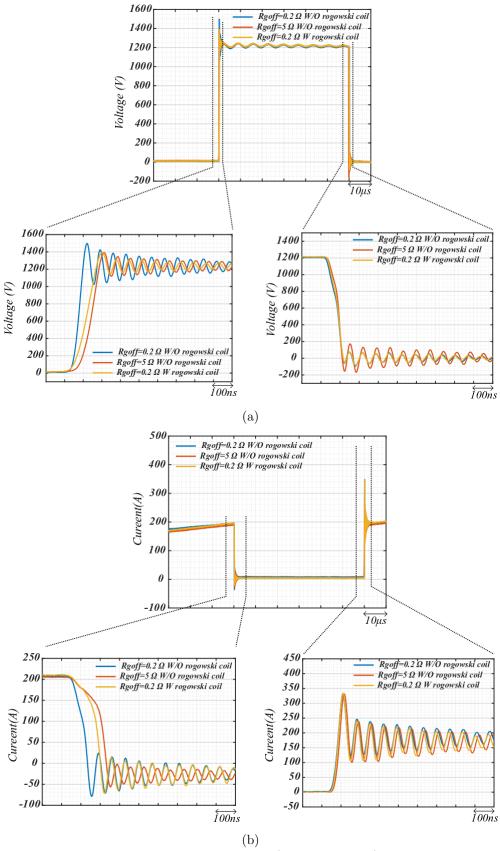

| 5.42        | Vgs comparison, experimental result, double pulse test, $1200~\mathrm{V},$ - |      |

|             | 200 A, comparison between gate driver (W/O) without rogowski and             |      |

|             | (W) with integrated rogowski coil (a) VgsH (hard switching) (b)              |      |

|             | VgsL (soft switching)                                                        | 146  |

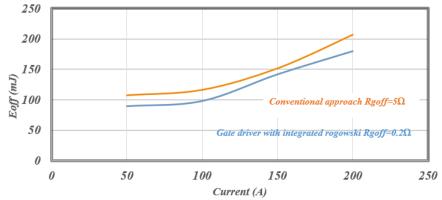

| 5.43        | Comparison of the turn-off losses between conventional approach and          |      |

|             | proposed gate driver                                                         | 147  |

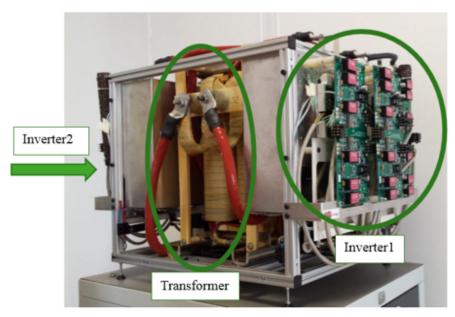

| 1           | Single phase DAB prototype, 1200V, 100kW, 1.7 kV SiC MOSFET                  |      |

|             | as a switch                                                                  | 154  |

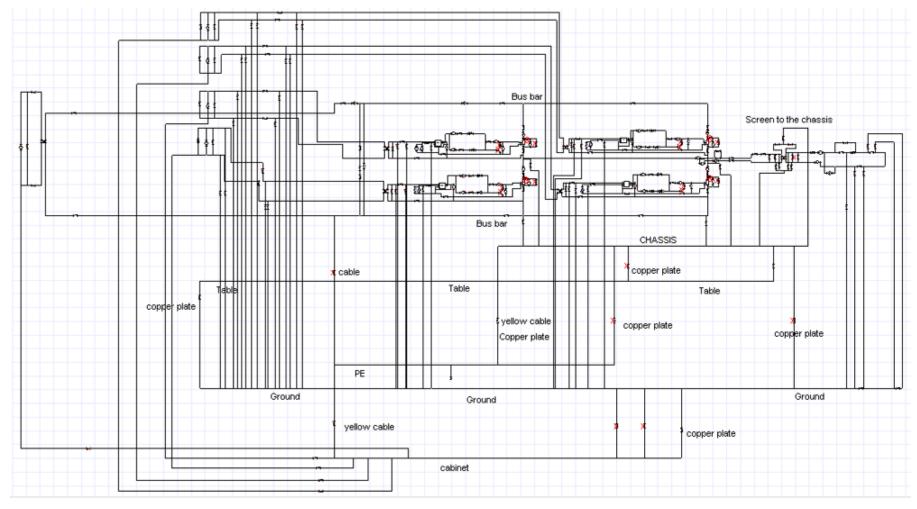

| 2           | Single phase VSC1 simulation schematic in simplorer                          | 155  |

| 3           | Single phase DAB prototype ground modification, screen of trans-             |      |

|             | former to ground                                                             | 156  |

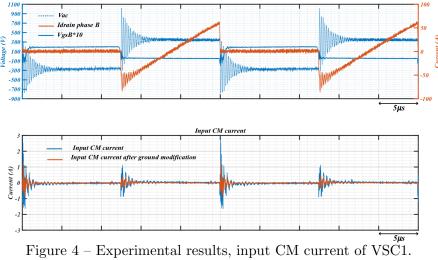

| 4           | Experimental results, input CM current of VSC1                               | 156  |

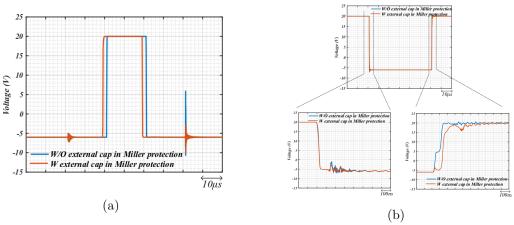

| 5           | Simulation results of comparison between the gate driver with Miller         |      |

|             | clamp integrated circuit without (W/O) external capacitance and              |      |

|             | the gate driver with Miller clamp integrated circuit with (W) 40             |      |

|             | nF external capacitance, double pulse test, 700 V, 150 A (a) VgsH            |      |

|             | (b) VgsL                                                                     | 161  |

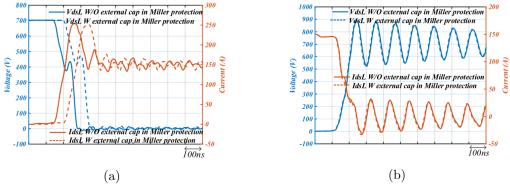

| 6           | Simulation results of comparison between the gate driver with                |      |

|             | Miller clamp integrated circuit without (W/O) external capaci-               |      |

|             | tance and the gate driver with Miller clamp integrated circuit               |      |

|             | with (W) 40nF external capacitance (a) VdsL Vs. IdsL, on tran-               |      |

|             | sition (b) VdsL Vs. IdsL off transition                                      | 161  |

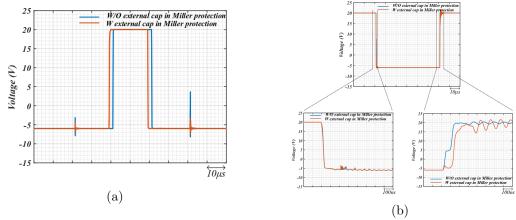

| 7  | Simulation results of comparison between the gate driver with Miller                      |     |

|----|-------------------------------------------------------------------------------------------|-----|

|    | clamp integrated circuit without $(W/O)$ external capacitance and the                     |     |

|    | gate driver with Miller clamp integrated circuit with (W) 40nF ex-                        |     |

|    | ternal capacitance, double pulse test, 700V, 150A (a) VgsL (b) VgsH                       | 162 |

| 8  | Simulation results of comparison between the gate driver with Miller                      |     |

|    | clamp integrated circuit without (W/O) external capacitance and the                       |     |

|    | gate driver with Miller clamp integrated circuit with (W) 40nF ex-                        |     |

|    | ternal capacitance (a) VdsH Vs. IdsH, on transition (b) VdsH                              |     |

|    | Vs. IdsH, off transition.                                                                 | 162 |

| 9  | VgsH comparison (hard switching), experimental result, double pulse                       |     |

|    | test, 1200V, -200A, Comparison Vgs<br>L $(\mathrm{W/O})$ rogowski coil and $(\mathrm{W})$ |     |

|    | with rogowski coil integrated to gate driver (a) Switching transition                     |     |

|    | (b) Turn-off transition                                                                   | 163 |

| 10 | VgsH comparison (hard switching), experimental result, double pulse                       |     |

|    | test, 1200V, -200A, Comparison Vgs<br>L $(\mathrm{W/O})$ rogowski coil and $(\mathrm{W})$ |     |

|    | with rogowski coil integrated to gate driver                                              | 163 |

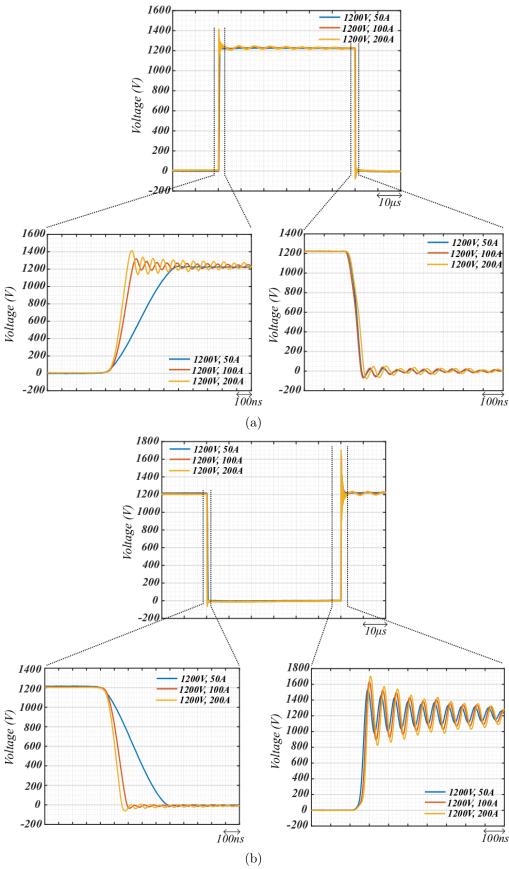

| 11 | VdsH with IdsH (hard switching), double pulse test, experimental                          |     |

|    | result, $1200V$ , $-200A$ , comparing between $(W/O)$ without rogowski                    |     |

|    | coil and (W) rogowski coil integrated to gate driver (a) Turn-on tran-                    |     |

|    | sition (b) Turn-off transition                                                            | 164 |

| 12 | VdsL with IdsL (soft switching), double pulse test, experimental re-                      |     |

|    | sult, 1200V, -200A, comparing between (W/O) without rogowski coil                         |     |

|    | and (W) rogowski coil integrated to gate driver (a) Turn-on transition                    |     |

|    | (b) Turn-off transition                                                                   | 164 |

| 13 | IdsH and VgsH, experimental result of gate driver with integrated                         |     |

|    | rogowski coil, double pulse test, 1200V, -50A, -100A, -200A (a) IdsH                      |     |

|    | (b) VgsH                                                                                  | 165 |

| 14 | Vds, experimental result of gate driver with integrated rogowski coil,                    |     |

|    | double pulse test, $1200V$ , $-50A$ , $-100A$ , $-200A$ (a) VdsL (b) VdsH                 | 166 |

| 15 | Experimental Input ICM comparison between the gate driver with-                           |     |

|    | out (W/O) integrated rogowski coil and with gate driver with (W)                          |     |

|    | integrated rogowski coil, Double pulse test, 1200<br>V (a) -50<br>A (b) -100<br>A $$      |     |

|    | (c) -200A                                                                                 | 167 |

# List of Tables

| 2.1 | Parameters of the transformers based on impedance measurement in |    |

|-----|------------------------------------------------------------------|----|

|     | Yy configuration [41]                                            | 44 |

| 3.1 | Parameter values of the modelled inductor                        | 62 |

| 3.2 | Values of the modelled inductor for configuration B              | 63 |

| 3.3 | Values of the modelled parasitic capacitances to the ground      | 63 |

| 3.4 | Values of the model of the DC decoupling capacitances            | 63 |

| 3.5 | Test bench decoupling capacitance value in double pulse set-up   | 65 |

| 4.1 | Electrical characteristic of the considered MOSFET and IGBT mod- |    |

|     | ule [168] and [3]                                                | 81 |

#### 1.1 General introduction

Electricity is the fastest-growing type of the end-use energy consumption [78]. In addition electricity generation is one of the leading cause of industrial pollution all over the world because it is mostly produced from coal, nuclear and non-renewable power plants [78]. Renewable energy sources can be used to produce electricity with fewer environmental impacts. To achieve more clean energy, Europe announced the 2030 climate and energy framework. Its objectives include [140]:

- 1. At least 40% cuts in greenhouse gas emissions (from 1990 levels).

- 2. At least 32 % share for renewable energy.

- 3. At least 32.5 % improvement in energy efficiency.

One of the solutions is that energy industry integrates more and more renewable energy resources. For Europe to meet ambitious de-carbonisation targets, renewable energy sources are expected to increase significantly in final energy consumption by 2030 [140].

To integrate renewable energies to the grid, the new grid requires the development of new technologies. That made power electronics systems increasingly popular [86]. Power electronics can change renewable energies from being minor energy source to act as important power sources [16]. Hence, the power electronics which

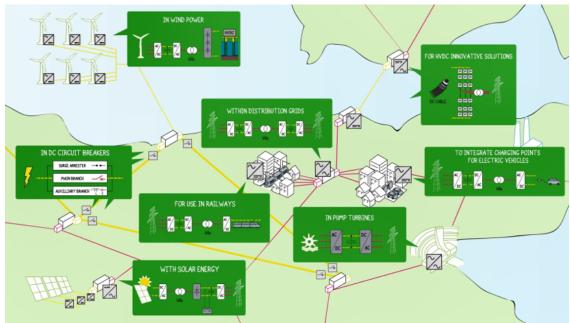

control the flow and conversion of electrical energy is an important research area for integrating renewable energies [121]. To achieve this objective High/Medium Voltage Direct Current (HVDC/MVDC) technology offers several advantages compared to Alternating Current (AC) transmission such as power transmission between unsynchronised AC distribution [115]. For this purpose, DC/DC converter is an expected technology for MVDC/HVDC transmission systems (see Fig. 1.1). The converter excellent features fit various HVDC projects [59, 127].

Figure 1.1 – Converter applications in integrating the renewable energies to transmission and distribution grids [145].

High frequency power electronic converters based on solid state transformer (SST) gain considerable attention due to their numerous functions including regulation, power quality, power control, efficient interface for distributed generation and storage management [93, 95, 129]. Figure 1.1 shows examples of converter applications in future electrical networks.

Converters are composed of semiconductor devices operating in switching modes. The power quality in a distribution system with high penetration of renewable energy resources highly relies on power converter switching transients [17]. Using high frequency switching components such as SiC MOSFET offers a solution to improve power density of converters but due to its fast switching nature it increases the level of interferences [82].

In converters, gate drivers serve as an interface between the control strategy (switching sequences) and the power switching action. So gate drivers are one of

the elements that can help converter designer to advance through fast switching and increase the converter efficiency.

In this chapter, the necessity of the present work in the field of power electronic to develop renewable energy integration to grid and energy transmission is explained. SiC MOSFET switching steps will be explained in details. Then the role of gate driver in switching transition is explained. Moreover, it lays the basic information for the material presented in chapters 2 to 5 which focus on the gate driver design, the electromagnetic interferences of the gate drivers and switching transitions.

### 1.2 Why SiC MOSFET based converter?

Previous section explained the important role of power electronic converters in electricity industry. This section explains how new technology of semiconductors can improve the efficiency and power density of converters. The switching elements of the converters enable to regulate the level of current and voltage. Widebandgap (WBG) power semiconductors as switching elements of converters allow power electronic converters to reach higher power density and efficiency and thus they recently appear in commercial products. Silicon-carbide metal-oxide-semiconductors field-effect transistors (SiC MOSFET), as one type of WBG devices is able to switch higher voltages faster and with higher switching frequency. Faster switching leads to less losses [94].

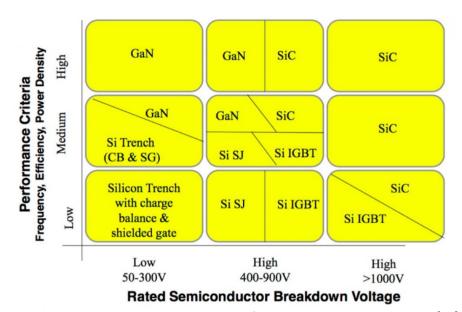

Figure 1.2 – WBG comparison for high/medium voltage application [11].

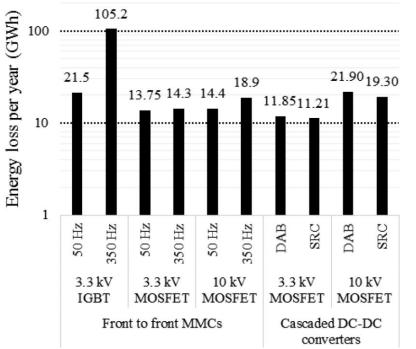

Figure 1.3 – Converter energy loss per year for different solutions [87].

The SiC material characteristics provide devices with a very high-blocking voltage (see Fig. 1.2). These characteristics make it very attractive for MVDC/HVDC application as an enabling factor to answer the constantly increasing demand for higher power density and higher efficiency in many power-electronic applications. Industrial fields such as rail traction, grid transmission and distribution system are currently working on R&D development on these devices.

SiC MOSFET power devices are expensive, so the benefit of using them rather than another cost-effective technologies has to be huge [11]. The comparative investigation reported in [87] presents an example of the energy losses per year for different converters comparing two different technologies of semiconductors for HVDC applications. The big amount of energy saving by using SiC MOSFET is not negligible as reported in figure 1.3. In this survey the cost of energy per year has been considered as  $150 \frac{\$}{MWh}$ . It is shown by using 3.3 kV SiC MOSFET for front to front MMC, it can save more than 13 M\$ per year. This gain can be increased by Dual Active Bridge DC/DC converter. In this estimation the price of SiC MOSFET is not considered, however, by ongoing development on the SiC MOSFET semiconductors, the price is decreasing yearly [105].

One of the good examples that is commercially mature is the 1.7 kV SiC MOS-FET power module from Wolfspeed manufacturer [168]. This device provides low on-resistance resulting in low power losses compared with Si devices in a same ranges [47, 128]. The device is well established and well cost-optimized in the range

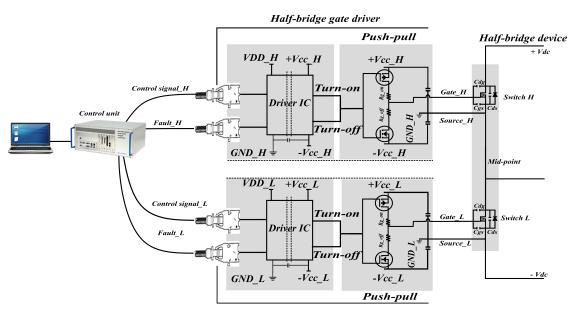

Figure 1.4 – Control unit and gate driver for medium/high voltage power semiconductor.

of 1200 V to 1700 V which makes it as a suitable choice to replace Si IGBT in medium voltage range converters.

### 1.3 Gate drivers for controlling power SiC MOS-FETs switching

### 1.3.1 Classical gate driver for SiC MOSFET

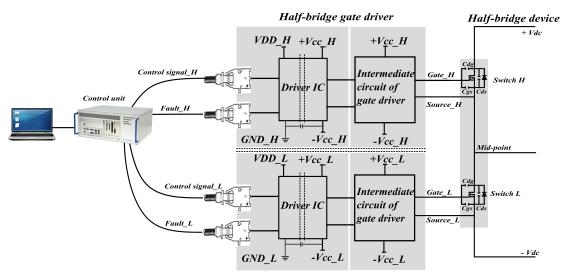

In power electronics applications, the control signals are provided by a controller unit (DSP, FPGA, etc). Depending on the application, the signal can be transferred through fibre optics or by wires (see Fig. 1.4). The control signal is synthesized and transferred to the semiconductors by a gate driver unit. So with the help of gate drivers, power switches turn-on/off and that is how converters can regulate the voltage and current.

For small power/low voltage application, the control signal is provided by the ICs with voltages in the range of 3.3 V to 5 V. Very few power devices can be directly driven by the digital outputs [143]. For medium/high voltage applications, an intermediate circuit is needed to convert the low power signals to higher voltages/currents to drive the power switches. The intermediate circuit receives the turn-on/off signals from IC and convert it to the suitable level of voltage/current for turning on/off the power semiconductors (see Fig. 1.4).

The basic function of an IC driver in a gate driver unit mainly includes following tasks:

1. Provide sufficient current/voltage levels to an intermediate circuit of gate driver.

- 2. Provide protection units including Desaturation and Miller clamp for power switching devices under certain conditions (sending fault signals to controller in figure 1.4).

- 3. Provide isolation for control signals from the large signal swings of the power switching devices.

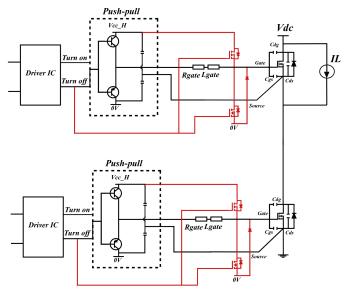

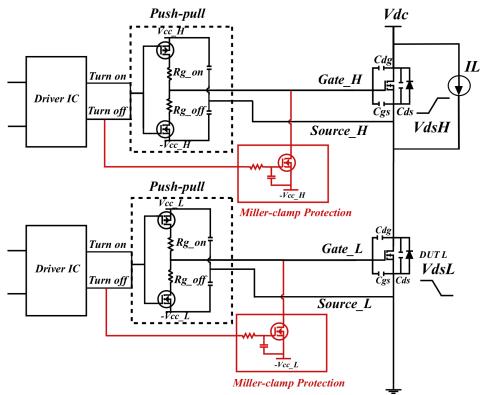

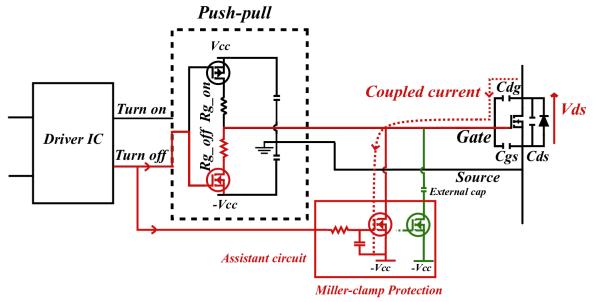

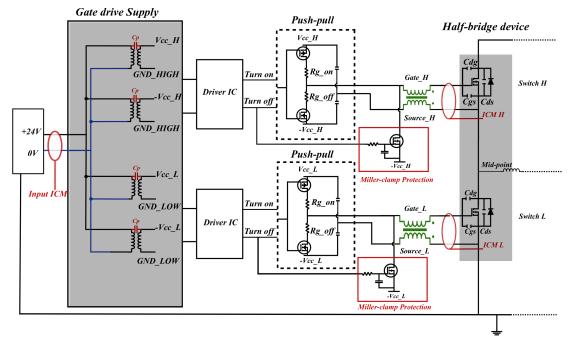

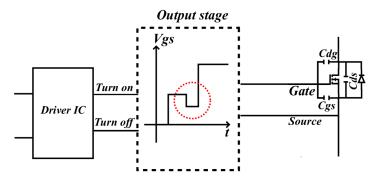

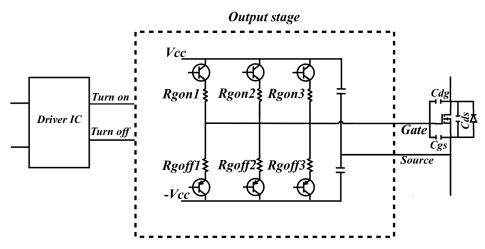

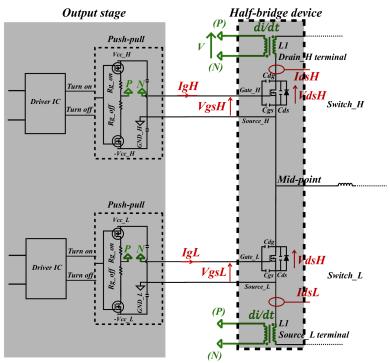

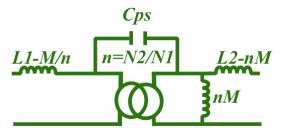

There are many IC drivers for power devices on the market. In case of normally off field-effect components like SiC MOSFETS, the drivers are called "FET IC drivers" [139]. As it has been explained for medium/high voltage semiconductors, the device is turned-on/off with bigger voltage bias. Then the needed current/voltage to turn-on/off the device is provided by the "push-pull" electronic circuit. There are many commercial IC drivers called push-pull (totem-pole) driver [14, 15]. The push-pull structure is adapted to the structure of the intermediate circuit of the gate driver (see Fig.1.5) which provides enough voltage bias for fast turn-on/off transition of the power switch.

Figure 1.5 – Control unit and intermediate gate driver circuit with push-pull for medium/high voltage power semiconductor.

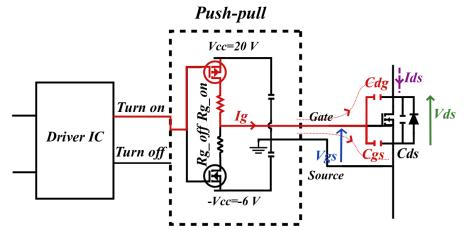

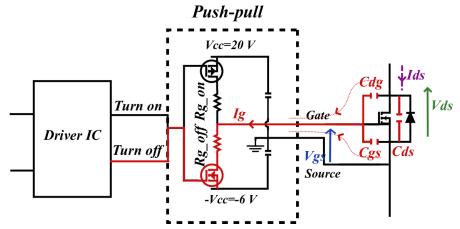

Switching transition of the SiC MOSFET involves charging and discharging the parasitic elements which are due to the physics of the semiconductor (see parasitic capacitors  $C_{dg}$ ,  $C_{gs}$  and  $C_{ds}$  in Fig. 1.14). For medium/high power semiconductor, in order to have minimum switching transition time, it is necessary to provide enough current/voltage bias to charge and discharge these input and output capacitances of the power SiC MOSFET. This current/voltage is provided by the push-pull circuit

Figure 1.6 – Turn-on transition of SiC MOSFET with push-pull circuit.

in the intermediate gate driver circuit. Figure 1.5 shows the classical push-pull output stage of the gate driver. The combination of NMOS and PMOS transistors constitutes the push-pull circuit. In this structure, the gate of these transistors are controlled and tied to each other in order to receive the on/off orders from IC drivers. The drain nodes of the push-pull transistors are connected to each other to form the gate current and gate bias voltage of the power semiconductors. The SiC MOSFET switching transition with the help of intermediate circuit is detailed in following section.

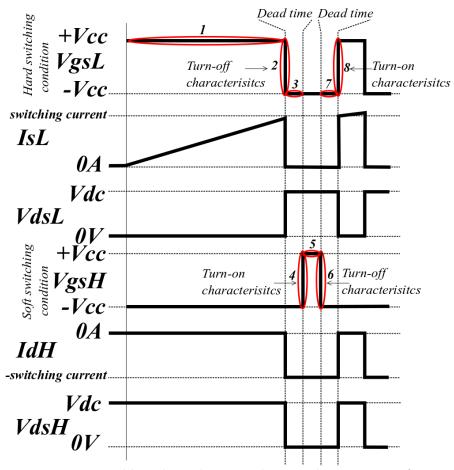

### 1.3.2 SiC MOSFET switching-transition

In this part, turn-on/off transitions of the SiC MOSFET with the help of the pushpull gate driver are described. Understanding the role of each element of gate drivers in addition to the parasitic elements of semiconductor which act during switching transition is necessary. It gives a basis to control the switching transition and to achieve an optimised gate driver.

#### 1.3.2.1 Turn-on transition of SiC MOSFET

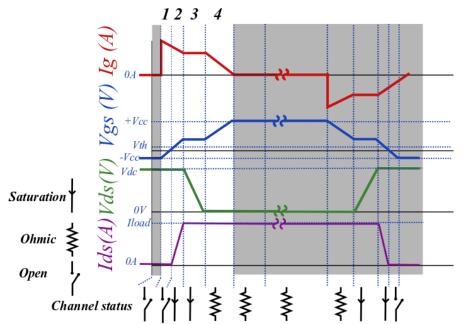

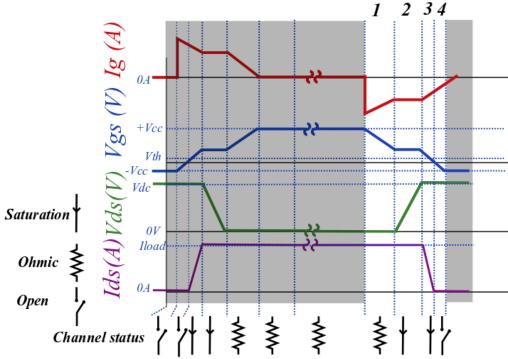

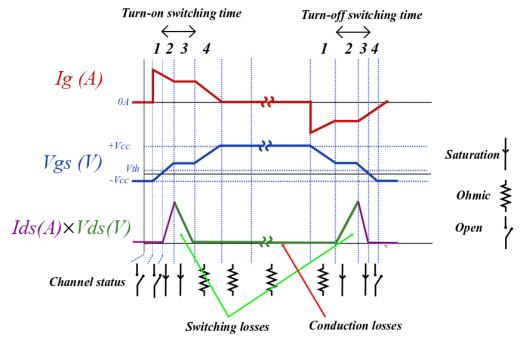

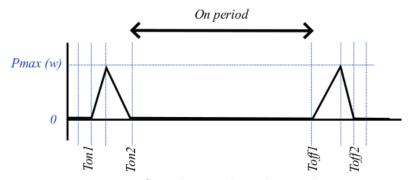

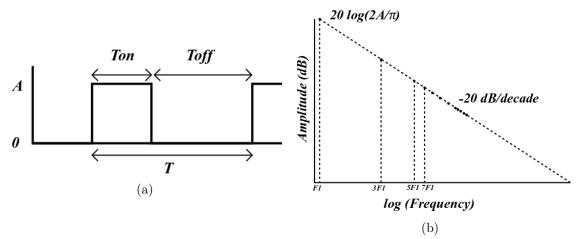

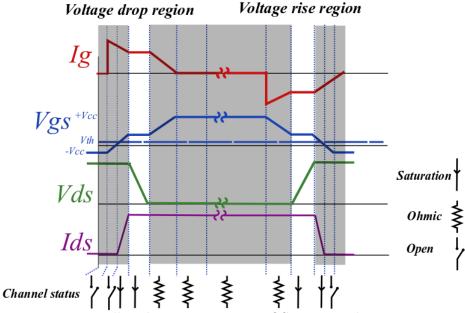

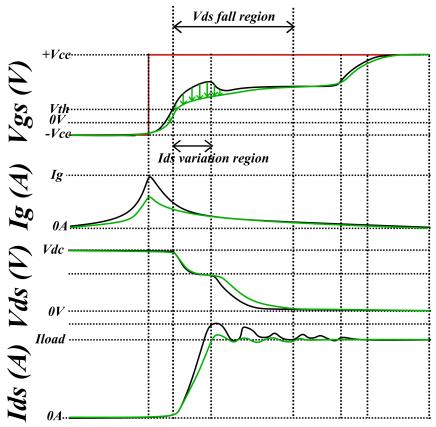

Turning on the PMOS in the push-pull circuit will charge the output node and pull up the output potential to turn-on the power device (see Fig. 1.6). The turn-on event of the SiC MOSFET semiconductor can be divided into four intervals as depicted in figure 1.7.

In the first step the input capacitance of the device is charged from 0 V to  $V_{th}$ . The big amount of current provided at the beginning of this period is needed to transfer the channel status from open to saturation state. During this time slot, most of the gate current is charging the  $C_{qs}$  capacitance. A small current flows

through the  $C_{dg}$  also (see Fig. 1.6). As the voltage increases at the gate terminal, the voltage across  $C_{dg}$  is faintly reduced. This period is called turn-on delay. During this period both  $I_{ds}$  and  $V_{ds}$  remained without changes.

Figure 1.7 – Turn-on transition intervals of SiC MOSFET.

Once the gate is charged to the threshold voltage  $(V_{th})$ , the MOSFET is ready to carry the current. Therefore, in the second step, the gate bias is rising from  $V_{th}$  to the Miller level. On the gate side, the current is flowing into the  $C_{gs}$  and  $C_{gd}$  capacitors like during the first time slot and that is how the gate bias voltage is increasing (see Fig. 1.6). On the output side of the device,  $I_{ds}$  is increasing while  $V_{ds}$  is constant (off-level). Until  $I_{ds}$  is totally transferred into the MOSFET and the  $V_{ds}$  stays in its off level.

In the third period, the gate is already charged to the sufficient voltage  $(C_{gd})$  and  $C_{gs}$  are charged completely), therefore, the device is ready to carry the entire load current  $(I_{ds})$ . This allows  $V_{ds}$  to fall. During the  $V_{ds}$  falling period,  $V_{gs}$  stays constant. This is the Miller region in the gate voltage waveform and this is the time interval where the gate driver can affect the switching transition. It can be seen how the duration of this period in  $V_{gs}$  waveform can change the conduction of the drain current. All the gate current available from the driver is diverted to discharge the  $C_{gd}$ . This discharge facilitates the rapid voltage change of  $V_{ds}$ . Therefore, if the gate current varies at the beginning of this period, the  $I_{ds}$  rising would have changed also. The  $V_{ds}$  drop also depends on the  $I_{ds}$  current.

Figure 1.8 – Turn-off transition of SiC MOSFET with push-pull circuit.

The forth step is called "fully turn-on" period. To fully enhance the conducting channel of the MOSFET, it is needed to apply a higher gate voltage. Therefore, in this period, the gate reaches the final value of the gate bias.

$V_{gs}$  increases from the Miller region to the final value (here for 1.7 kV SiC MOSFET, the value is equal to 20V). This step is accomplished by charging  $C_{gs}$  and  $C_{gd}$ , therefore, the  $I_g$  is split between these two capacitors. As long as these capacitors are charged,  $I_{ds}$  is still constant and  $V_{ds}$  is decreasing as the on resistance of the device (in the physics of the device) is being reduced. When the gate bias reaches Vcc,  $V_{ds}$  drops to almost zero. In this step  $I_{ds}$  is the full load current and  $V_{ds}$  is defined by the  $I_{ds} * Rds_{on}$  ( $Rds_{on}$  is the drain-source on resistance in the physics of the device).

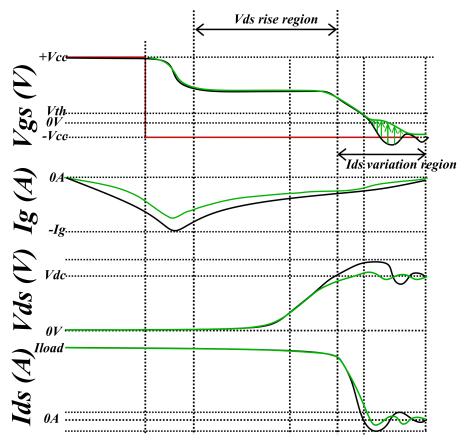

#### 1.3.2.2 Turn-off transition of SiC MOSFET