## Integration of mid-infrared lasers on silicon photonic integrated circuits

Andres Remis Janez

#### ▶ To cite this version:

Andres Remis Janez. Integration of mid-infrared lasers on silicon photonic integrated circuits. Electronics. Université de Montpellier, 2023. English. NNT: 2023UMONS041. tel-04552858

## HAL Id: tel-04552858 https://theses.hal.science/tel-04552858

Submitted on 19 Apr 2024

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THÈSE POUR OBTENIR LE GRADE DE DOCTEUR DE L'UNIVERSITÉ DE MONTPELLIER

Spécialité : Électronique

École doctorale : Information, Structures, Systèmes (I2S)

Unité de recherche : Institut d'Électronique et des Systèmes – UMR CNRS 5214

# Integration of mid-IR lasers on silicon photonic integrated circuits

## Présentée par Andres REMIS Le 4 décembre 2023

Sous la direction de Eric TOURNIE et Jean-Baptiste RODRIGUEZ

## Devant le jury composé de

Delphine MORINI, Professeur, Université Paris-Saclay, C2N Günther ROELKENS, Professeur, Ghent University, Belgium Frédéric BŒUF, ST Fellow, R&D Director, STMicroelectronics Philippe COMBETTE, Professeur, Université de Montpellier Jean-Baptiste RODRIGUEZ, CR-CNRS, Université de Montpellier Eric TOURNIE, Professeur, Université de Montpellier Rapporteur Rapporteur Examinateur Examinateur Co-directeur de thèse Directeur de thèse

# Acknowledgments

This thesis has been a meaningful experience in my life, contributing to both my growth as a professional and as a person. I would like to express my gratitude to everyone without whom this work would not have been possible.

First of all, I am deeply thankful to my family, whose support has been a constant throughout my educational journey. I would like to thank my parents and my whole family from Guatemala who, despite being on the other side of the world, made me feel supported every day. I also want to thank my family from Spain for encouraging me to set ambitious goals in my professional career. Special thanks go to my two brothers, whose support fueled my desire and motivation to pursue a PhD. A big part of this success lies in the education received by my family since childhood, so there are really no words to thank you all.

I want to thank also all my close friends who, despite never understing what my thesis topic was about, always showed admiration, which was a great encouragement and motivation for me.

My sincere thanks to all the members of the jury for accepting to participate in my PhD defense. Thanks Delphine Morini, Günther Roelkens and Frédéric Boeuf for the interesting reviews and questions. I also extend my gratitude to Philippe for assuming the role of president during my defense.

I would like to thank the entire nanoMIR team for their invaluable help during these three years. Thank you specially everyone involved in the clean room: Fred, Michele, Laura, Daniel, Zeineb, Ariane, Renaud and Jean-Marie. Their help and trainings were essential to my work. Very special thanks go to Lolo who helped me in difficult moments and was like a third supervisor for me. I also made great friendships within this group, and I am very grateful for their support and the special moments we have shared.

Finally, I wish to express my deepest gratitude to my supervisor, Eric Tournié, and my co-supervisor, Jean-Baptiste Rodriguez, who gave me an exceptional guidance throughout my thesis, helped me to feel confident about my work and taught me how to be a real scientist.

¡Muchas gracias a todos!

Integration of mid-IR lasers on silicon photonic integrated circuits

# Index

| LIST OF FIGURES III |          |                                                                          | . 111 |

|---------------------|----------|--------------------------------------------------------------------------|-------|

| LI                  | ST OF TA | BLES                                                                     | VII   |

| LI                  | ST OF EC | QUATIONS                                                                 | VII   |

| IN                  | ITRODU   | CTION                                                                    | 1     |

| 1                   | CHA      | PTER 1. STATE OF THE ART AND MOTIVATIONS                                 | 3     |

|                     | 1.1      | SILICON PHOTONIC INTEGRATED CIRCUITS                                     | 3     |

|                     | 1.1.1    | Photonic integrated circuit                                              | 3     |

|                     | 1.1.2    | Silicon photonics                                                        | 4     |

|                     | 1.2      | LIGHT SOURCES                                                            | 5     |

|                     | 1.2.1    | Group-IV semiconductor lasers                                            | 5     |

|                     | 1.2.2    | III-V semiconductor lasers                                               | 5     |

|                     | 1.3      | INTEGRATION APPROACHES                                                   | 6     |

|                     | 1.3.1    | Heterogeneous integration                                                | 6     |

|                     | 1.3.2    | Monolithic integration                                                   | 8     |

|                     | 1.4      | COUPLING CONFIGURATIONS                                                  | . 10  |

|                     | 1.5      | APPLICATIONS OF SI PICS                                                  | . 12  |

|                     | 1.5.1    | Optical sensing in the mid-infrared                                      | . 12  |

|                     | 1.5.2    | Mid-IR lasers                                                            | . 13  |

|                     | 1.6      | CONCLUSION                                                               | . 17  |

| 2                   | CHAI     | PTER 2. DISCRETE GASB-BASED DIODE LASERS GROWN ON GASB AND SI SUBSTRATES | 19    |

|                     | 2.1      | DIODE LASER HETEROSTRUCTURE                                              | 19    |

|                     | 2.2      | MBE GROWTH                                                               |       |

|                     | 2.3      | LASER FABRICATION PROCESS                                                |       |

|                     | 2.3.1    |                                                                          |       |

|                     | 2.3.2    | -                                                                        |       |

|                     | 2.3.3    | -                                                                        |       |

|                     | 2.3.4    |                                                                          |       |

|                     | 2.4      | LASER CHARACTERIZATIONS                                                  |       |

|                     | 2.4.1    |                                                                          |       |

|                     | 2.4.2    |                                                                          |       |

|                     | 2.5      | THEORETICAL GAIN MODEL                                                   |       |

|                     | 2.6      | Discussion                                                               | . 35  |

|                     | 2.7      | CONCLUSION                                                               | . 37  |

| 3                   | СНА      | PTER 3. INTEGRATION OF GASB-BASED DIODE LASERS ON A SI PIC               | 38    |

|                     | 3.1      | CONFIGURATION                                                            | .38   |

|                     | 3.2      | CHALLENGES                                                               |       |

|                     | 3.3      | ETCHED-FACET DLs                                                         |       |

|                     | 3.3.1    |                                                                          |       |

|                     | 3.3.2    |                                                                          |       |

|                     | 3.3.3    |                                                                          |       |

|                     | 3.4      | FABRICATION OF SIN-BASED WAVEGUIDES                                      |       |

|                     | 3.5      | Oxide Removal For Later growth                                           |       |

|                     | 3.5.1    |                                                                          | -     |

|                     | 3.5.2    | -                                                                        |       |

|                     | 3.6      | EPITAXIAL GROWTH                                                         |       |

|                     |          |                                                                          |       |

| 3.7 POLYCRYSTAL REMOVAL                                           | 67                            |  |  |  |

|-------------------------------------------------------------------|-------------------------------|--|--|--|

| 3.8 LASER PROCESS ON THE SI PIC                                   |                               |  |  |  |

| 3.8.1 Facet definition                                            |                               |  |  |  |

| 3.8.2 Ridge definition                                            |                               |  |  |  |

| 3.8.3 Bottom contact definition                                   |                               |  |  |  |

| 3.8.4 Insulation and opening                                      |                               |  |  |  |

| 3.8.5 Metallization                                               |                               |  |  |  |

| 3.8.6 Substrate thin-down and cleavage                            |                               |  |  |  |

| 3.9 CHARACTERIZATIONS OF DLS ON THE RECESSED SI                   |                               |  |  |  |

| 3.10 LIGHT COUPLING MEASUREMENT                                   |                               |  |  |  |

| 3.11 Simulations                                                  |                               |  |  |  |

| 3.12 CONCLUSION                                                   |                               |  |  |  |

| 4 CHAPTER 4. INCREASING THE COUPLING EFFICIENCY OF THE INTEGRA    | ATED GASE DIODE LASERS ON THE |  |  |  |

| SI PIC                                                            |                               |  |  |  |

|                                                                   |                               |  |  |  |

| 4.1 FILLING THE GAP                                               |                               |  |  |  |

| 4.1.1 Simulations                                                 |                               |  |  |  |

| 4.1.2 Filling the gap with PMMA                                   |                               |  |  |  |

| 4.2 LASER PROCESS OPTIMIZATION TO REDUCE THE GAP                  |                               |  |  |  |

| 4.2.1 Polycrystal removal optimization                            |                               |  |  |  |

| 4.2.2 Laser facet definition                                      |                               |  |  |  |

| 4.2.3 Thin III-V peak removal                                     |                               |  |  |  |

| 4.3 Alternative approaches                                        |                               |  |  |  |

| 4.3.1 Waveguide fabrication on etched-facet laser by e-beam evapo |                               |  |  |  |

| 4.3.1 Waveguide fabrication on etched-facet laser by PECVD        |                               |  |  |  |

| 4.4 CONCLUSION                                                    |                               |  |  |  |

| GENERAL CONCLUSION AND PERSPECTIVES                               |                               |  |  |  |

| 5 APPENDIX                                                        | 110                           |  |  |  |

| 5.1 Type-I quantum well diode lasers                              |                               |  |  |  |

| 5.2 PROCESS TECHNIQUES                                            |                               |  |  |  |

| 5.2.1 UV photolithography                                         |                               |  |  |  |

| 5.2.2 ICP etching                                                 |                               |  |  |  |

| 5.2.3 PECVD                                                       |                               |  |  |  |

| 5.2.4 Electron beam evaporation                                   |                               |  |  |  |

| REFERENCES                                                        |                               |  |  |  |

|                                                                   |                               |  |  |  |

| IST OF PUBLICATIONS 12                                            |                               |  |  |  |

# List of figures

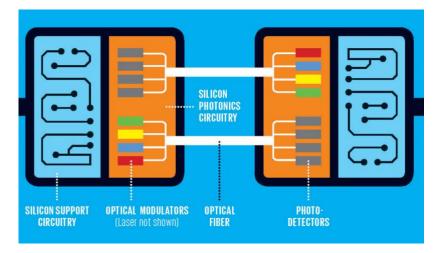

| Figure 1. Representation of a Silicon photonic chip.[15]                                                    | 4   |

|-------------------------------------------------------------------------------------------------------------|-----|

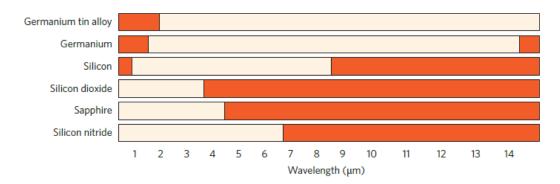

| Figure 2. Transmission window of different waveguide materials. The white areas are the wavelen             |     |

| range over which waveguide propagation loss is less than 2 dB/cm. The orange areas are the                  | 0-  |

| wavelength range over which loss is high.[8]                                                                | 5   |

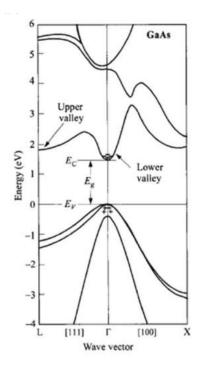

| Figure 3. Energy band structure of GaAs, an example of direct bandgap.                                      |     |

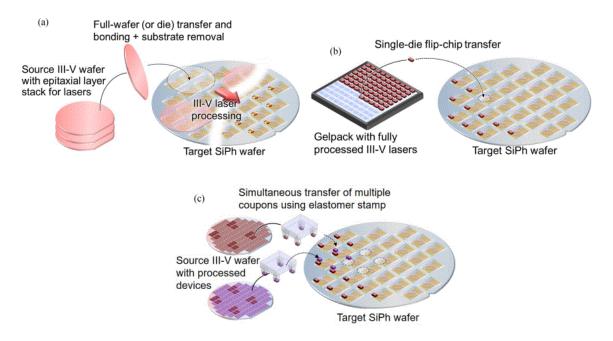

| Figure 4. III-V-on-Si heterogeneous integration approaches. a) Wafer-bonding. b) Flip-chip                  |     |

| integration. c) Micro-transfer printing.[39]                                                                | 7   |

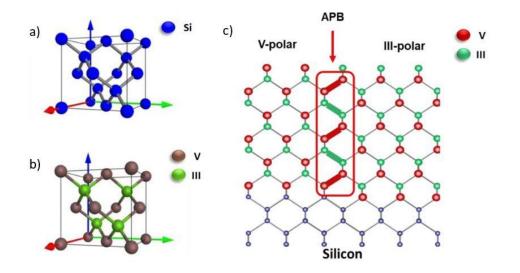

| Figure 5. a) Silicon crystal structure. b) III-V crystal structure. c) Sketch of a V-polar domain and a II  |     |

| polar domain separated by the antiphase boundary (III-III and V-V bonds).[59]                               |     |

| Figure 6. Energy gap and wavelength vs. lattice constant for some elementary and binary                     | 9   |

|                                                                                                             | 0   |

| semiconductor materials.                                                                                    |     |

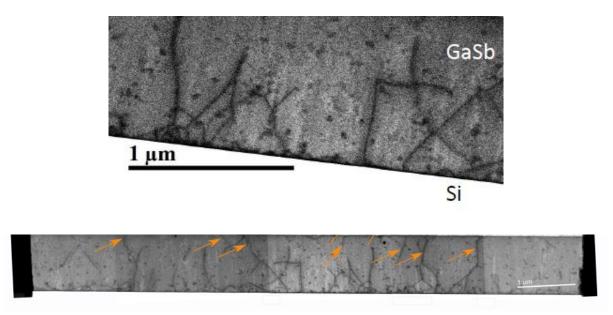

| Figure 7. TEM pictures of GaSb layer grown on Si substrate where threading dislocations are visible         |     |

| (Courtesy of Karl Graser, PDI Berlin).                                                                      |     |

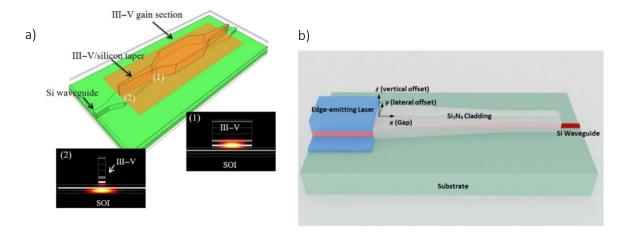

| Figure 8. The two main light coupling configurations. a) Evanescent coupling of a III-V laser into a S      | 51  |

| waveguide thanks to a taper section.[69] b) Butt-coupling configuration of a laser into a Si                |     |

| waveguide.[72]                                                                                              |     |

| Figure 9. a) 2-5-μm mid-IR spectrum.[79] b) Mid-IR sensors applications.[85]                                |     |

| Figure 10. Band structure alignments for a selection of unstrained III-V binaries at 300 K.[88]             |     |

| Figure 11. Band alignments and recombination mechanisms of QW diode lasers, interband cascade               |     |

| lasers and quantum cascade lasers                                                                           | 14  |

| Figure 12. L-I-V curves of different types of lasers grown on on-axis Si substrates. a) ICL. b) QCL. c)     | DL. |

| [62]–[64]                                                                                                   | 15  |

| Figure 13. Threshold current densities vs. wavelength of different types of mid-IR lasers.[81]              | 16  |

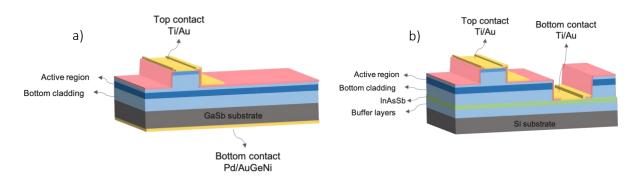

| Figure 14. Structure design of the diode lasers grown on a) GaSb substrates and on b) Si substrates         | S   |

| containing different number of QWs in the active zones for each substrate (1-4 QWs)                         | 20  |

| Figure 15. Band structure details of the design for a DL grown on Si. a) A band structure detail for t      | the |

| entire structure. b) A band structure detail for the QWs[62]                                                | 21  |

| Figure 16. a) 20x20 μm <sup>2</sup> AFM image of the 2-QWs laser surface. b) Omega-2theta high-resolution 3 |     |

| ray diffraction scan of the same laser.                                                                     |     |

| Figure 17. Sketch of the final device after processing. a) DL on native GaSb substrate. b) DL on Si         |     |

| substrate.                                                                                                  | 23  |

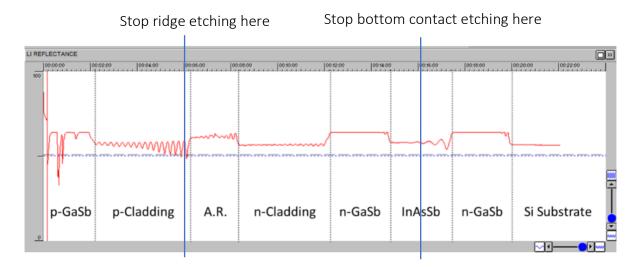

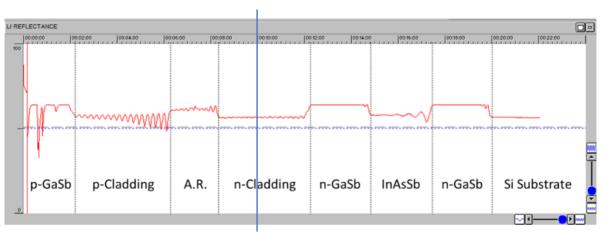

| Figure 18. Tracking signal of the etching for the whole heterostructure: reflectance vs. etching tim        |     |

|                                                                                                             |     |

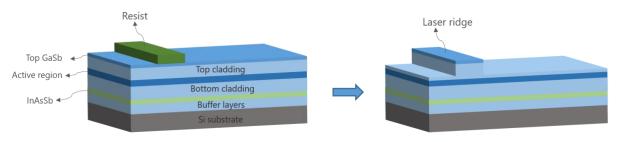

| Figure 19. Sketch of the fabrication step of the laser ridge                                                |     |

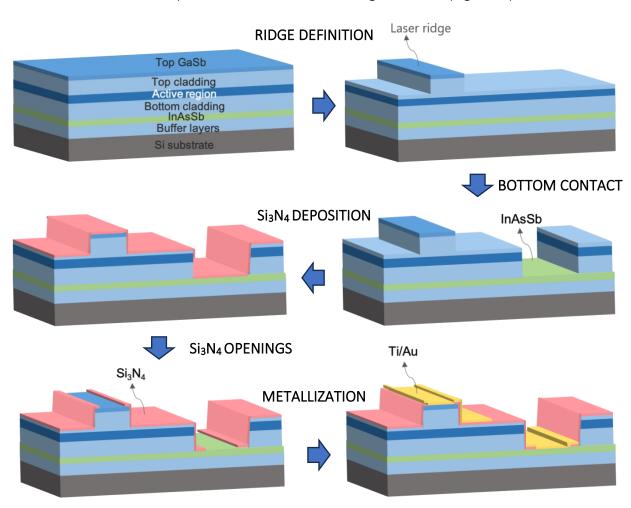

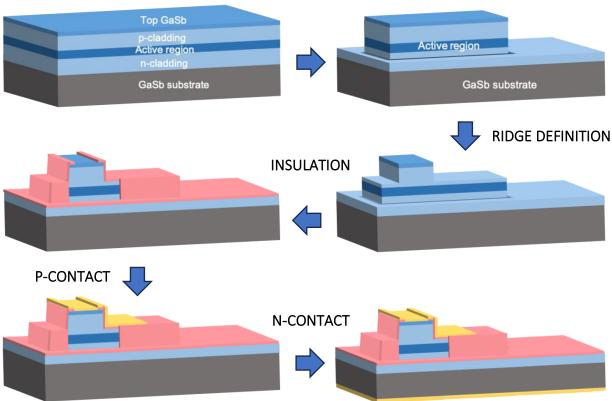

| Figure 20. Sketch of the fabrication process of DLs on Si.                                                  |     |

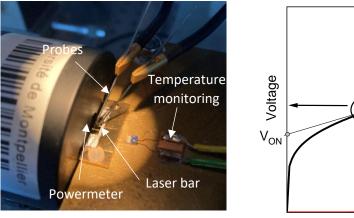

| Figure 21. Representation of a L-I-V curve from a laser characterization.                                   |     |

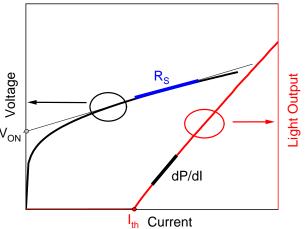

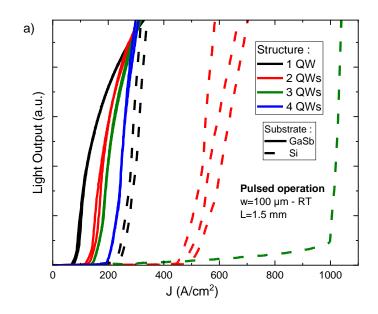

| Figure 22. Broad-area laser characteristics in pulsed operation for the two series. Light output vers       |     |

| current density curves of 1.5 mm-long DLs with different numbers of QW.                                     |     |

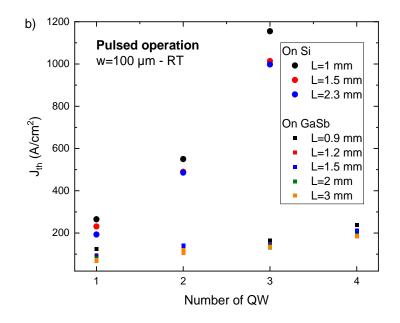

|                                                                                                             |     |

| Figure 23. Broad-area laser characteristics in pulsed operation for the two series. Threshold currer        |     |

| density versus the number of QWs for different cavity lengths                                               |     |

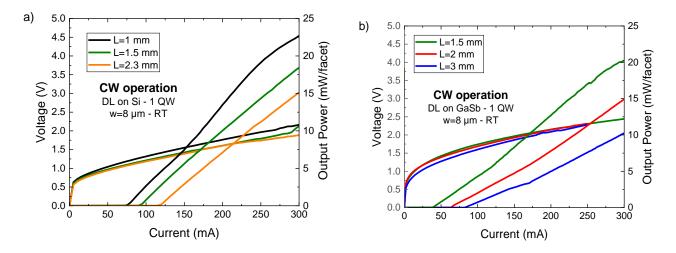

| Figure 24. L-I-V data in CW for 1-QW DLs with an 8 $\mu$ m-wide ridge and different cavity lengths. a) C    |     |

| Si substrate. b) On GaSb substrate.                                                                         |     |

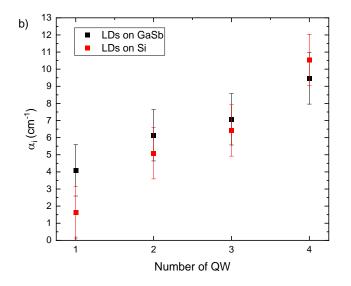

| Figure 25. Extracted internal losses versus the number of QWs for the two series.                           |     |

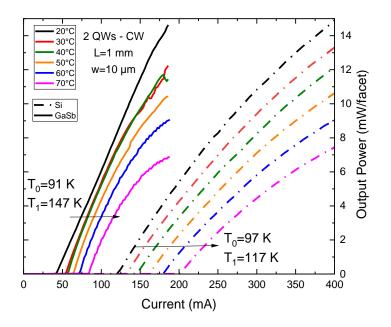

| Figure 26. L-I data for 2-QWs DLs on Si and GaSb with a 10- $\mu$ m wide ridge and 1-mm long cavity fo      |     |

| different measurement temperatures                                                                          |     |

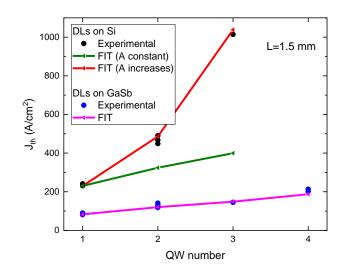

| Figure 27. Fits of the threshold current density for the two series for the 1.5-mm long DLs                 | 35  |

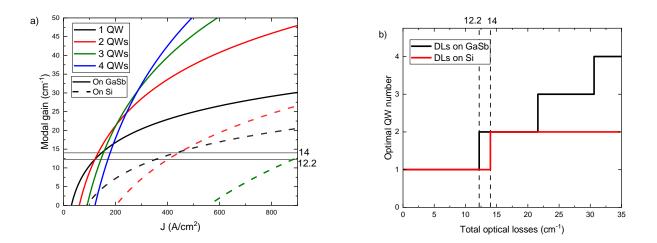

| Figure 28. The gain model calculations for the two series. (a) Modal gain vs current density curves f  | for  |

|--------------------------------------------------------------------------------------------------------|------|

| different number of QWs. (b) The optimal number of QWs vs the total optical losses                     | .36  |

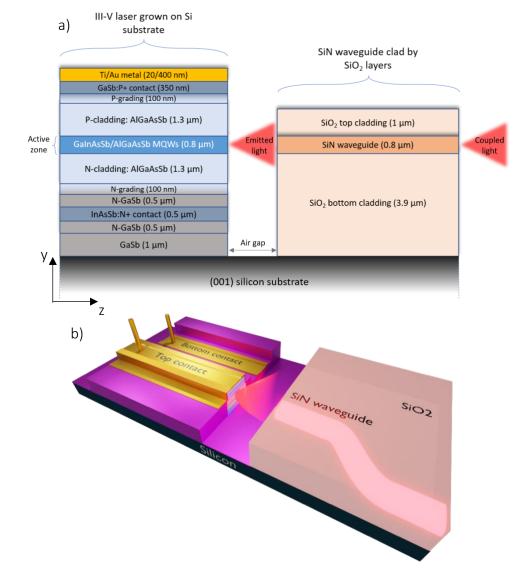

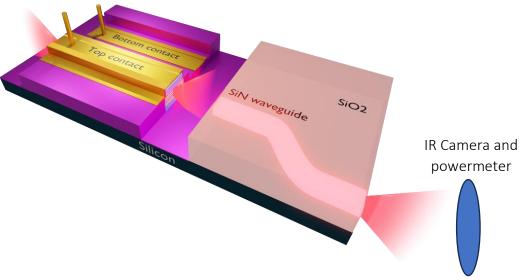

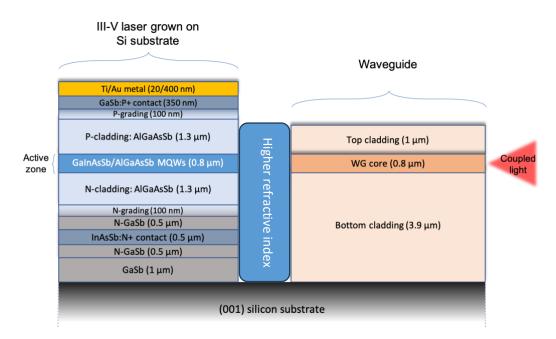

| Figure 29. a) Cross-section and b) 3D sketch of an integrated GaSb DL on a Si PIC with light coupled   | 1    |

| from the active zone of the DL to the core of the waveguide                                            | . 39 |

| Figure 30. Cross-section sketch of challenging fabrication steps of the integration of the DL on the S | Si   |

| PIC in order to couple light from the active zone of the DL to the core of the SiN waveguide           | .40  |

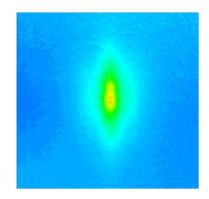

| Figure 31. Light beam output of a DL taken with an IR camera.[119]                                     |      |

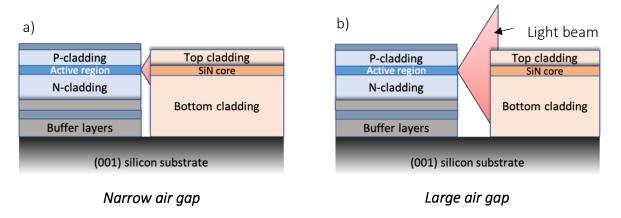

| Figure 32. Cross-section sketch of the effect of the air gap on the light coupling                     | .41  |

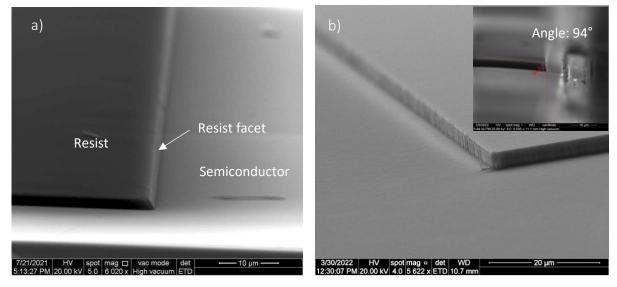

| Figure 33. Resist profile after a standard lithography using a) soft contact and b) vacuum contact     | .43  |

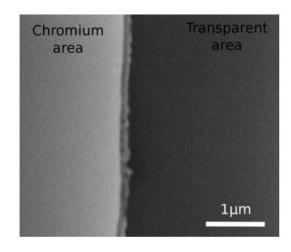

| Figure 34. SEM image of the chromium mask used during photolithography.[119]                           | .44  |

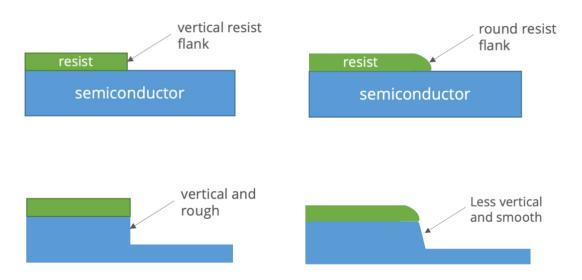

| Figure 35. Sketch of the influence of the hard bake on the resist and semiconductor flanks. a) no ha   | ard  |

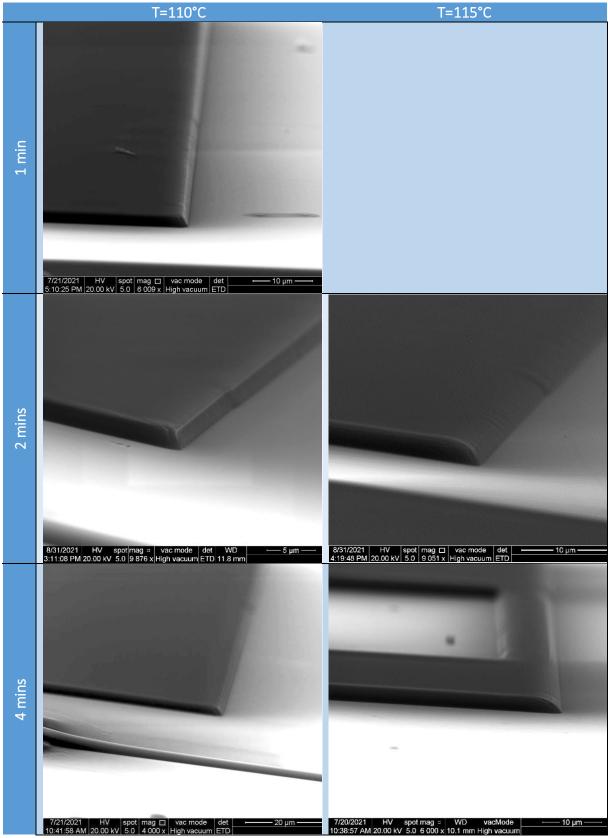

| bake is performed. b) hard bake is performed.                                                          |      |

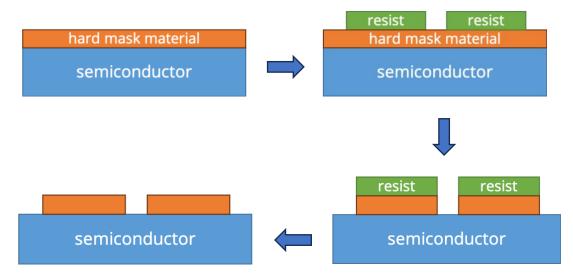

| Figure 36. Sketch of the fabrication of a hard mask.                                                   | .47  |

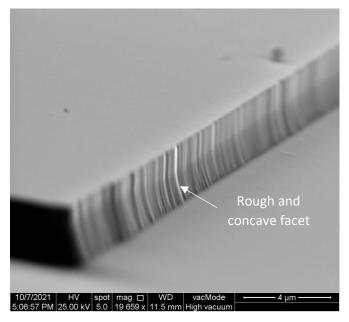

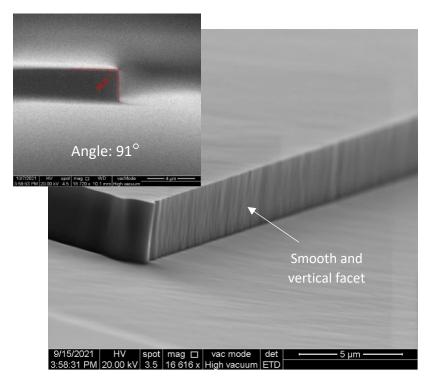

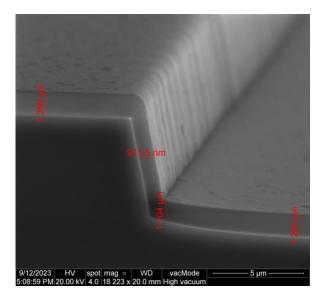

| Figure 37. SEM image of the semiconductor flank using SiN hard mask with no hard bake of the res       |      |

| Figure 38. SEM image of the semiconductor flank using SiN mask and a hard bake at 110°C during 4       |      |

| minutes                                                                                                |      |

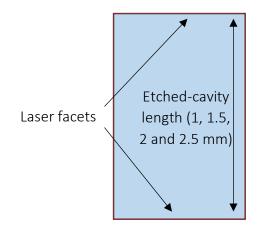

| Figure 39. Mask design of the laser facet.                                                             |      |

| Figure 40. ICP etching tracking signal                                                                 |      |

| Figure 41. SEM images of the laser facet.                                                              |      |

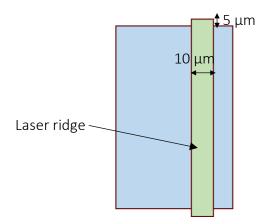

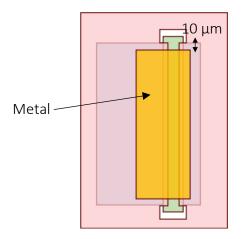

| Figure 42. Mask design of the laser ridge.                                                             |      |

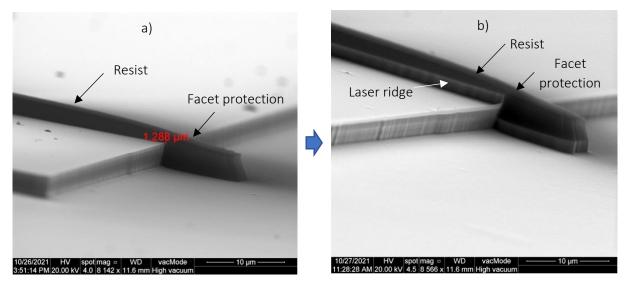

| Figure 43. SEM images of the laser ridge definition step. a) after lithography and before ICP etching  |      |

| b) after ICP etching                                                                                   |      |

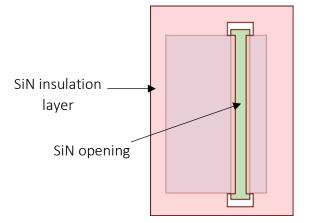

| Figure 44. Mask design of the electrical insulation.                                                   |      |

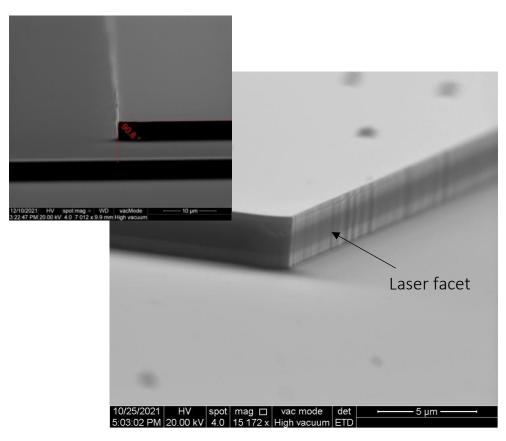

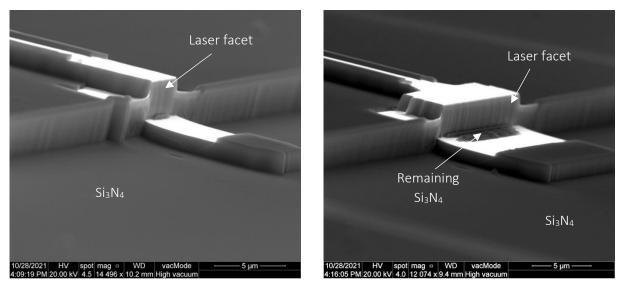

| Figure 45. SEM images of the laser facet after the electrical insulation and opening.                  |      |

| Figure 46. Mask design of the metal deposition                                                         |      |

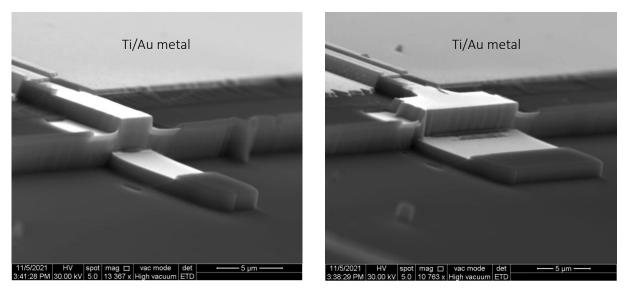

| Figure 47. SEM images of the final device after the metallization step                                 |      |

| Figure 48. Sketch of the etched-facet DL process flow                                                  |      |

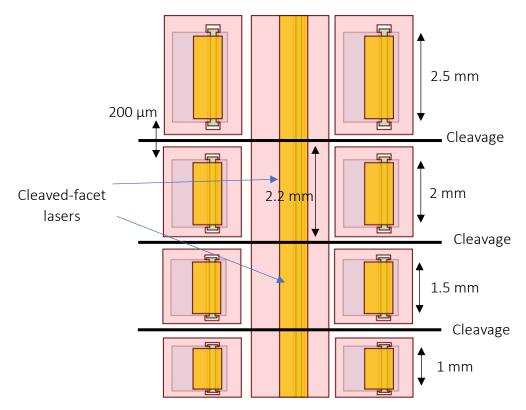

| Figure 49. Sketch of the cleavage step. Etched- and cleaved-facet lasers are obtained on the same      |      |

| bar                                                                                                    | .56  |

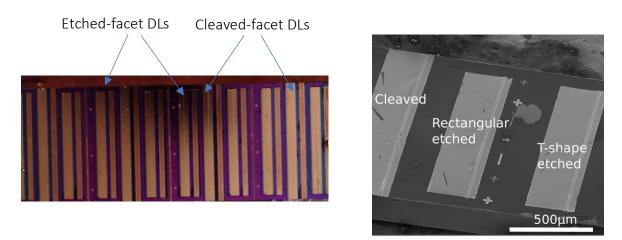

| Figure 50. Images of a laser bar with several etched-facet lasers and cleaved lasers. a) optical image | e.   |

| b) SEM image[119]                                                                                      | .56  |

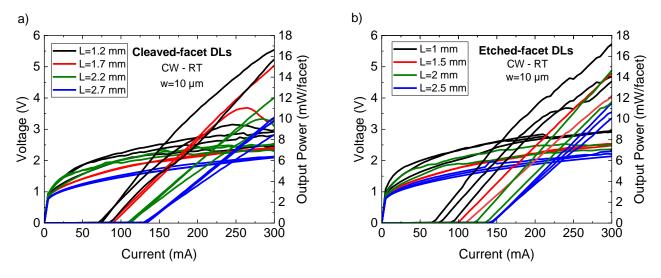

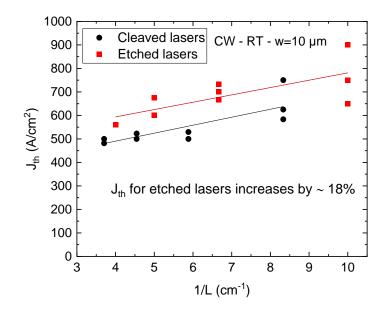

| Figure 51. L-I-V curves in CW operation at RT of DLs grown on GaSb substrate with a) cleaved facet     | S    |

| and b) etched-facets                                                                                   | .57  |

| Figure 52. Threshold current density as a function of the cavity length in CW and RT for etched- and   | d    |

| cleaved-facet DLs                                                                                      | .58  |

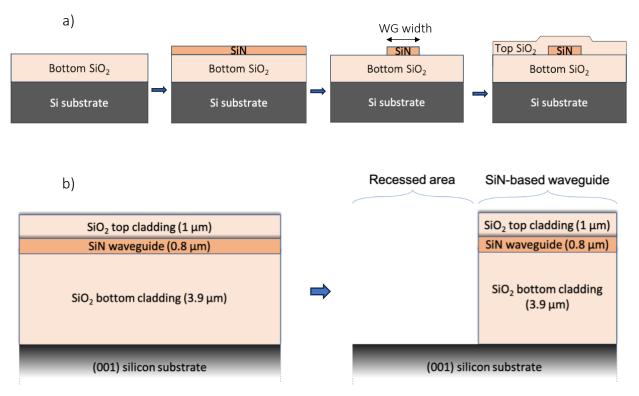

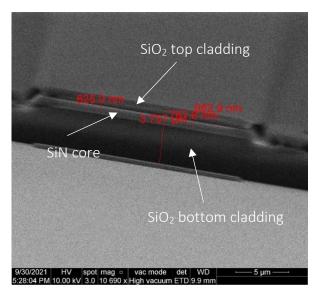

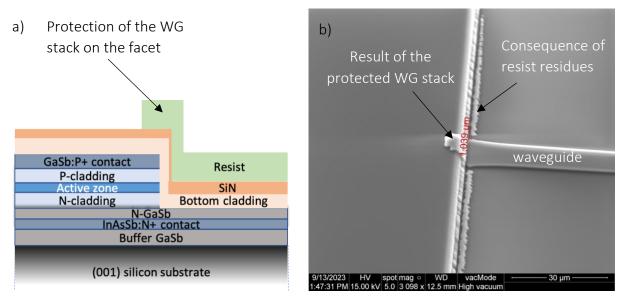

| Figure 53. a) Front and b) cross section view sketch of the SiN WGs fabrication.                       | . 59 |

| Figure 54. SEM image of the front of the WG                                                            | .60  |

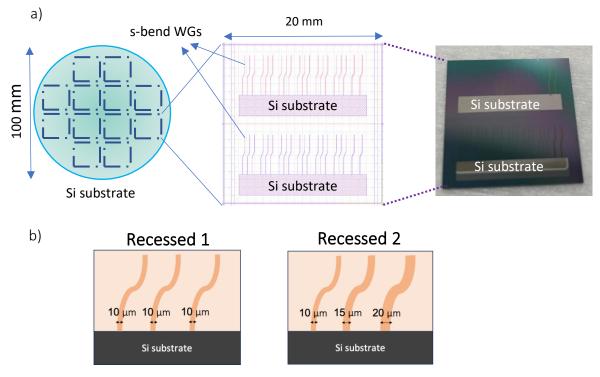

| Figure 55. Schematic of the Si PICs: the pattern of the 100 mm wafers is organized with several 20x    |      |

| mm <sup>2</sup> dies, each one containing two recessed areas together with 20 SiN waveguides each one  | .61  |

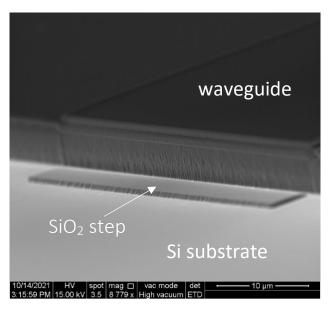

| Figure 56. SEM image of the SiN waveguide with a remaining SiO <sub>2</sub> step on the Si substrate.  | .61  |

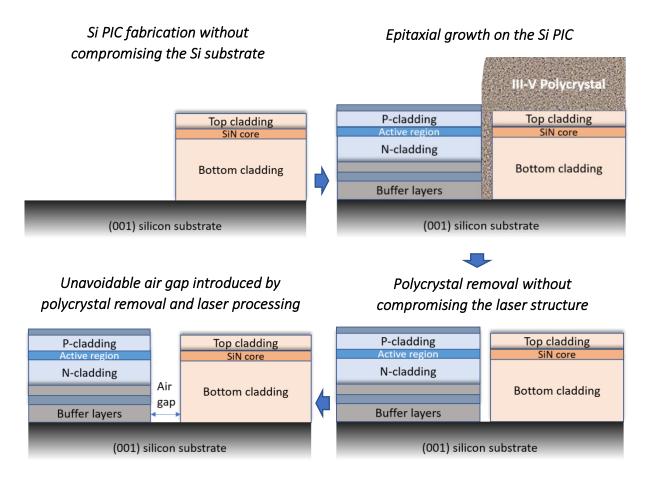

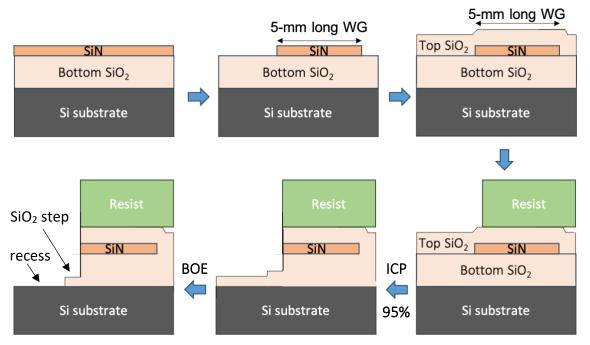

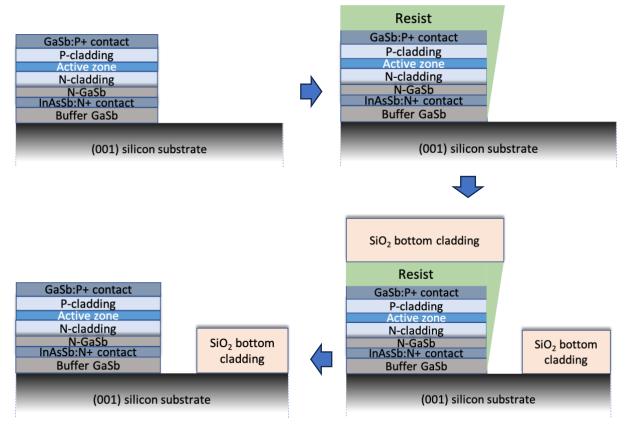

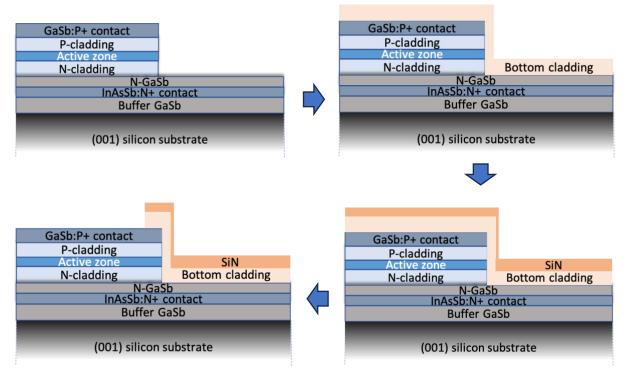

| Figure 57. Cross-section view sketch of the PIC fabrication.                                           | .62  |

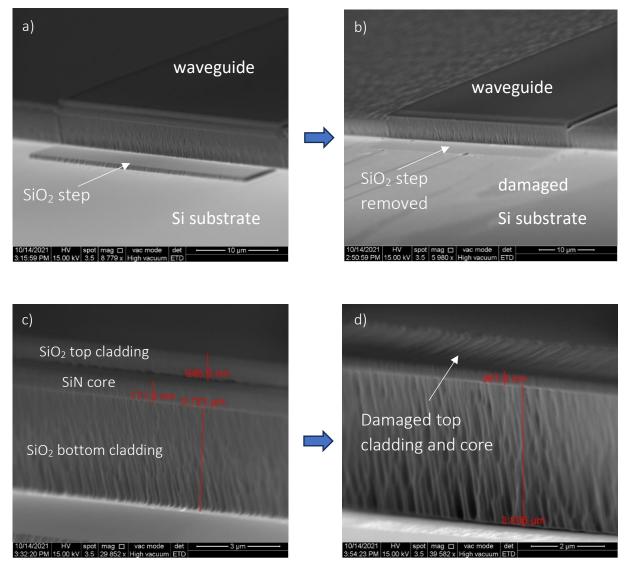

| Figure 58. SEM images of the removal SiO2 step attempts with HF solution. a) before etching. b) af     | ter  |

| 18 minutes etching with a damaged Si substrate. c) zoomed image on the WG stack before etching         | 5    |

| and d) after etching                                                                                   | .63  |

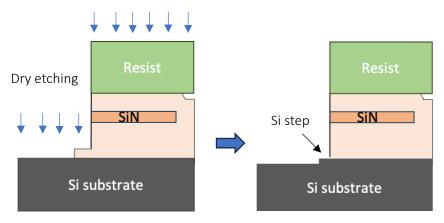

| Figure 59. Process sketch of the oxide removal by ICP dry etching                                      | .64  |

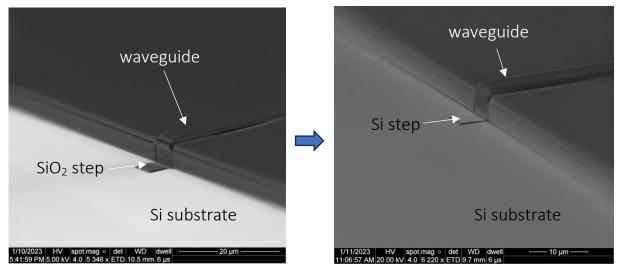

| Figure 60. SEM images of the SiO $_2$ step removal by ICP dry etching                                  | .64  |

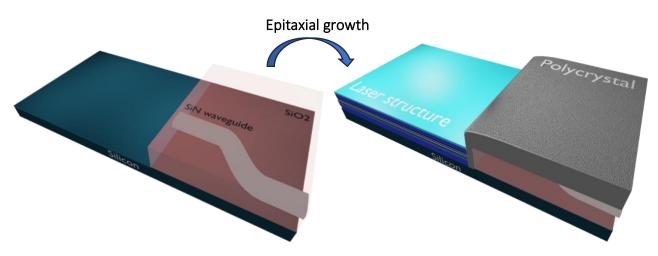

| Figure 61. 3D sketch of the epitaxial growth step.                                                     | .65  |

| Figure 62. a) Top view of the die before and after the epitaxial growth. b) high-resolution X-ray                        |

|--------------------------------------------------------------------------------------------------------------------------|

| diagram measured in the laser growth. c) AFM image taken on top of the laser structure                                   |

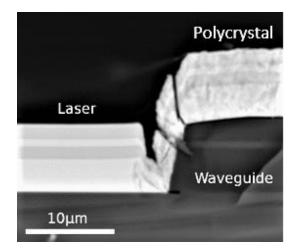

| Figure 63. Cross-section SEM image of a similar Si PIC after the epitaxial growth.[119]67                                |

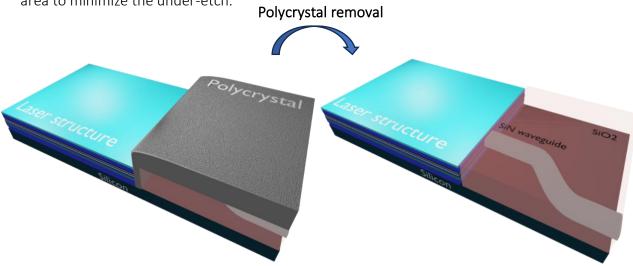

| Figure 64. 3D sketch of the polycrystal removal step                                                                     |

| Figure 65. Different mask protections for the polycrystal removal step. The green rectangles                             |

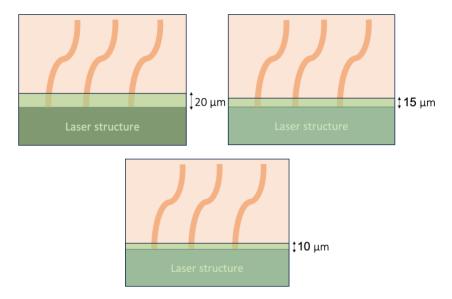

| correspond to the resist                                                                                                 |

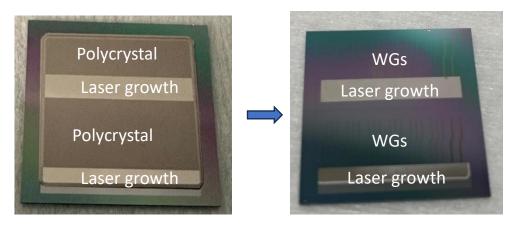

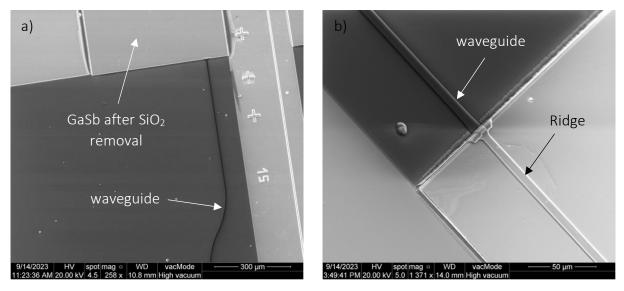

| Figure 66. Pictures of a die before and after the polycrystal removal                                                    |

| Figure 67. SEM images of the sample after the polycrystal removal for different masks. a) The                            |

| protection goes 20 $\mu$ m into the WG stack, b) 15 $\mu$ m and c) 10 $\mu$ m                                            |

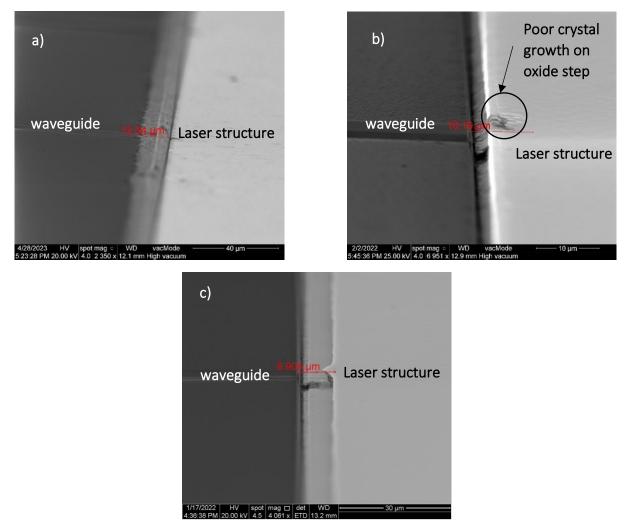

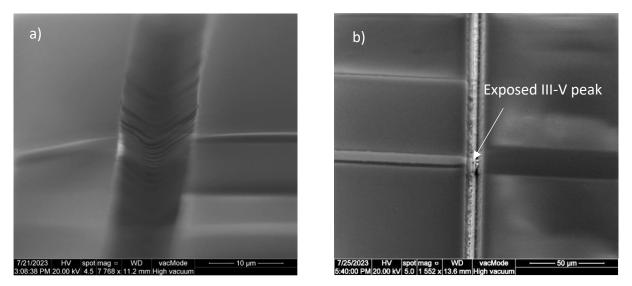

| Figure 68. Facet definition photolithography using the same parameters as those of discrete etched-                      |

| facet lasers                                                                                                             |

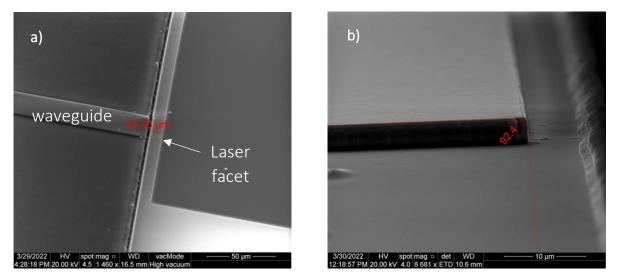

| Figure 69. SEM images of the laser facet definition. a) Top view of the sample after hard mask                           |

| opening. b) Facet angle measurement after facet etching                                                                  |

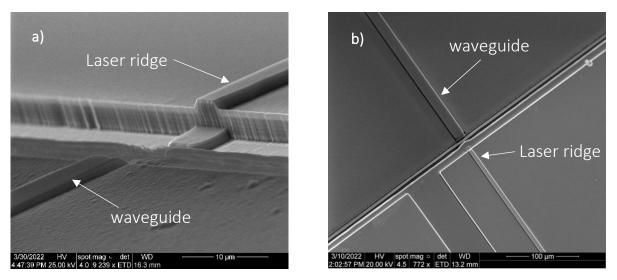

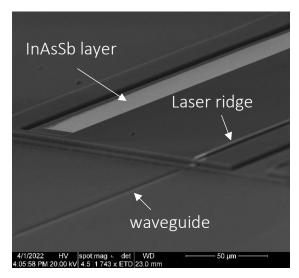

| Figure 70. SEM images of the ridge definition step. a) angled view. b) top view                                          |

| Figure 71. SEM image of the bottom contact next to the laser ridge                                                       |

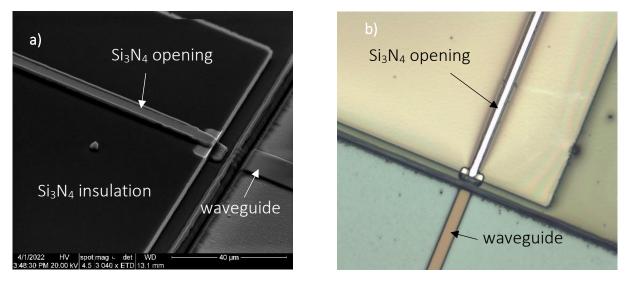

| Figure 72. a) SEM and b) optical image of the electrical insulation step                                                 |

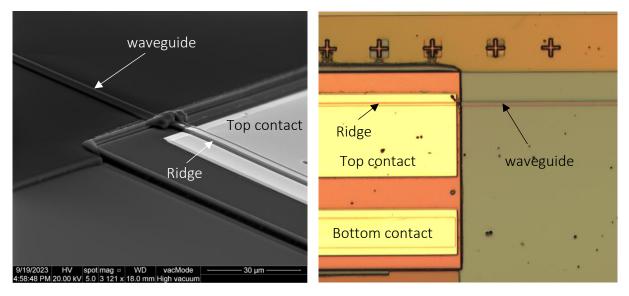

| Figure 73. a) SEM and b) optical image of the device after the metallization step                                        |

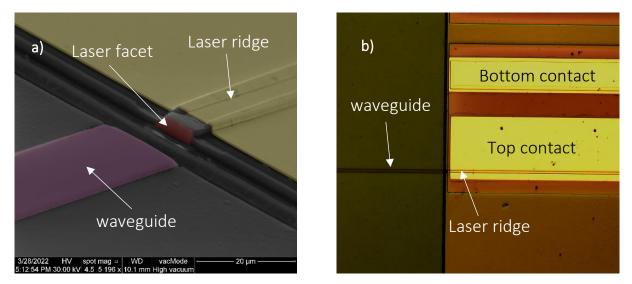

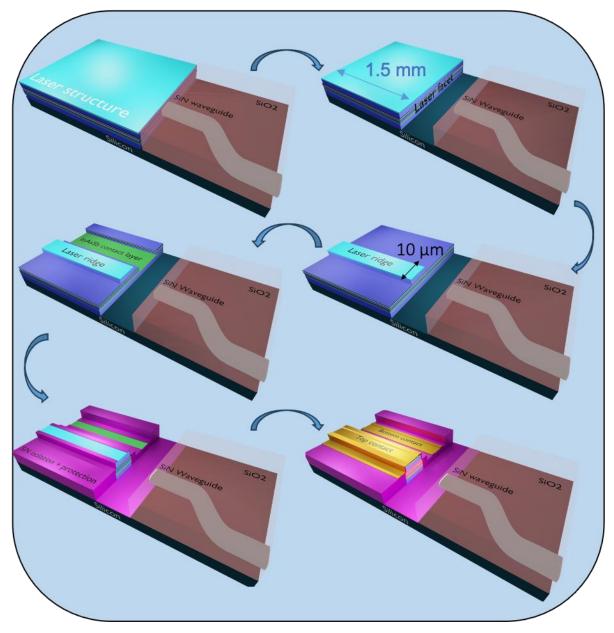

| Figure 74. Sketch of the laser process flow on the Si PIC. The different process steps are facet etching,                |

|                                                                                                                          |

| laser ridge, bottom contact, electrical insulation and metallization                                                     |

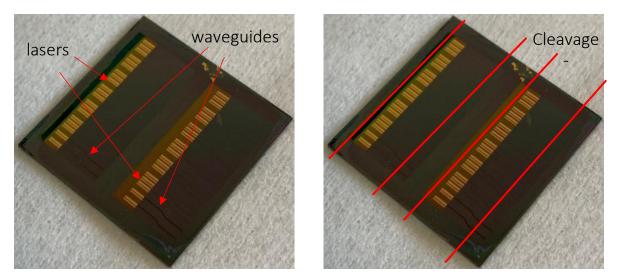

| Figure 75. Images of the final die showing a) the two series of lasers and waveguides and b) the                         |

| cleavages performed after polishing                                                                                      |

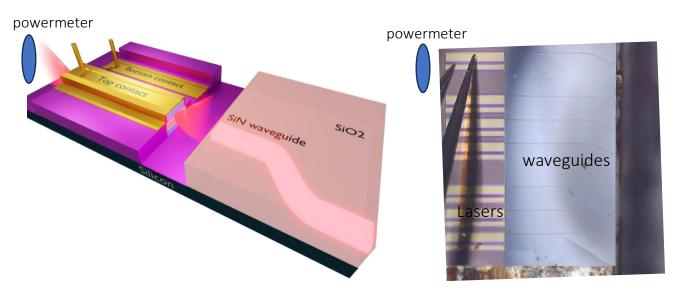

| Figure 76. a) 3D sketch of the final device and DL characterizations. b) Top view image of the bar                       |

| mounted on a Cu heat sink and measured on a probe station                                                                |

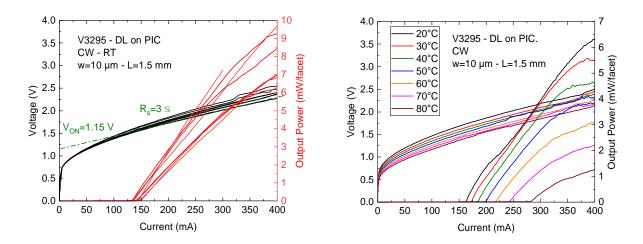

| Figure 77. a) L-I-V curves of the DLs on the Si PIC taken in the CW regime at RT for a series of 8 DLs. b)               |

| L-I-V curves taken at different temperatures between 20 and 80 C (setup limited) for a typical DL77                      |

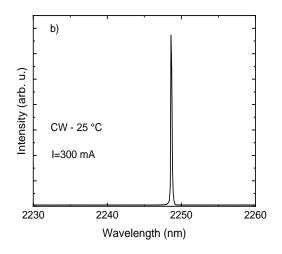

| Figure 78. Emission spectrum recorded from the DL at RT in the CW regime at $\sim$ 2 x I <sub>th</sub> drive current. 77 |

| Figure 79. 3D sketch of the light coupling characterizations78                                                           |

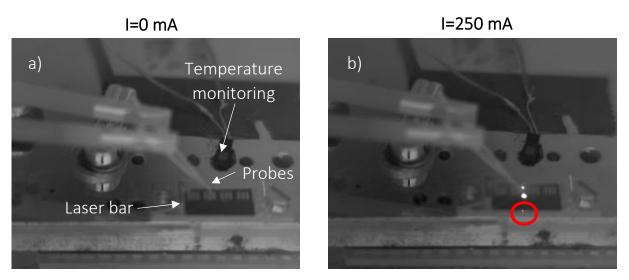

| Figure 80. IR image of the laser bar on the probe station with a) zero drive current and b) 250-mA                       |

| drive current                                                                                                            |

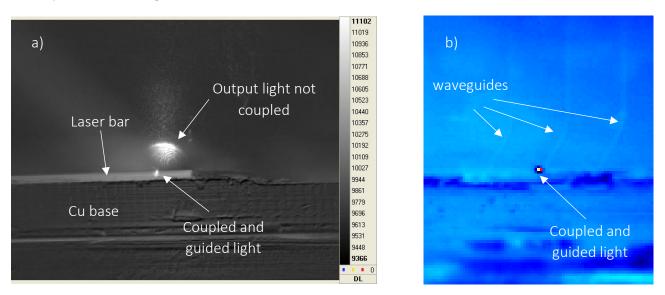

| Figure 81. IR images at the output of the waveguide with the laser operating at 250 mA. a) front                         |

| view. b) angled view79                                                                                                   |

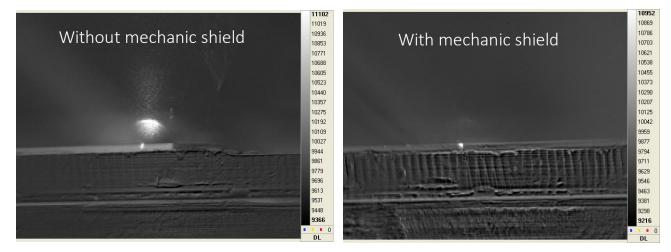

| Figure 82. IR images at the output of the waveguide with the laser operating at 250 mA. a) without                       |

| the mechanic shield. b) with the mechanic shield80                                                                       |

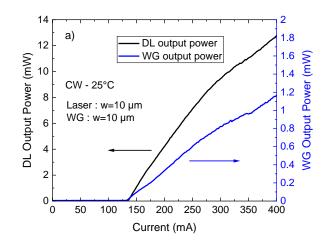

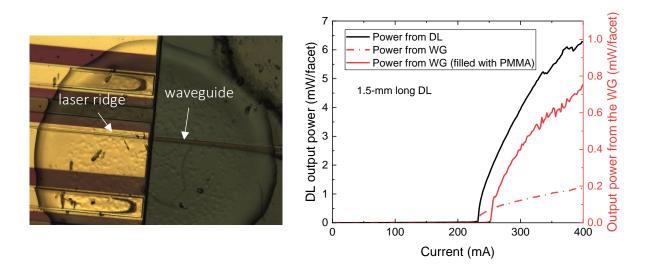

| Figure 83. L-I curves of a DL-WG pair where both laser ridge and WG are 10 $\mu m$ wide, taken in the CW                 |

| regime at RT                                                                                                             |

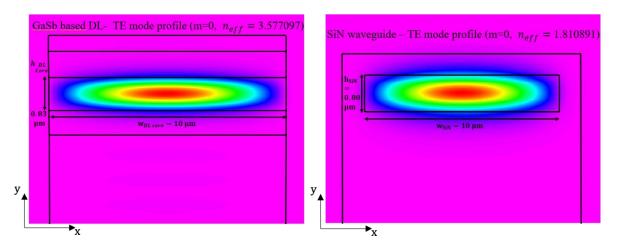

| Figure 84. 2D TE mode profiles supported in the DL ridge and in the SiN WG.[70]81                                        |

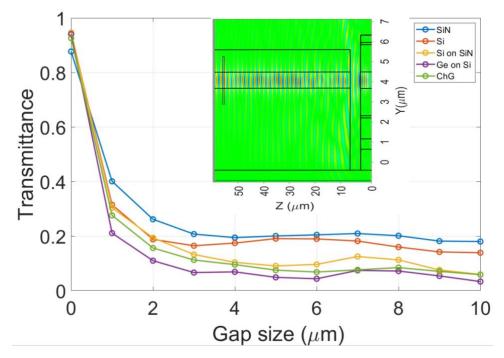

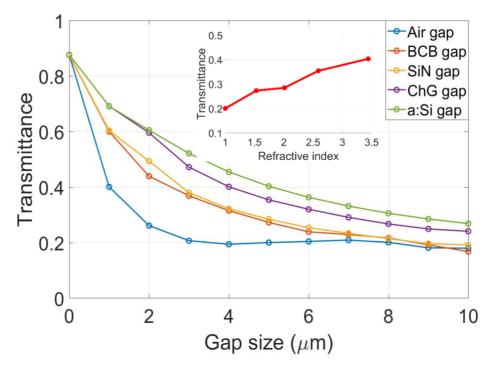

| Figure 85. Transmittance as a function of the air gap for different passive core materials.[70]82                        |

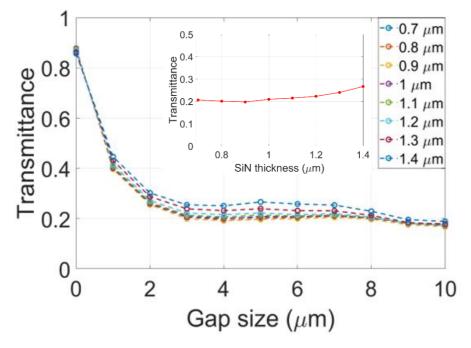

| Figure 86. Transmittance as a function of the air gap for a SiN/SiO2 waveguide and for different                         |

| passive core thicknesses.[70]83                                                                                          |

| Figure 87. Cross-section sketch of the DL butt-coupled with the WG with a filled gap with a material                     |

| with a higher refractive index                                                                                           |

| Figure 88. FDTD simulations of the transmittance as a function of the gap size for different gap                         |

| materials                                                                                                                |

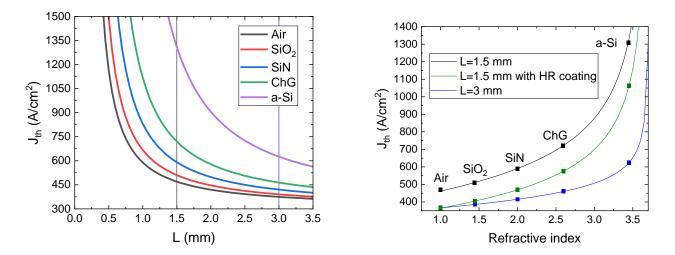

| Figure 89. a) Threshold current density as a function of the cavity length for different materials filling               |

| the gap. b) Threshold current density as a function of the refractive index of the material filling the                  |

| gap for a cavity length of 1.5 mm with and without HR coating and a cavity length of 3 mm without                        |

| HR coating                                                                                                               |

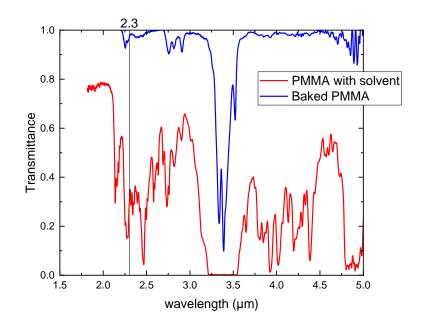

| Figure 90. Absorption measurement of a PMMA drop as a function of the wavelength with and without a bake                                                                                                                    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 91. a) Optical image of the PMMA drop deposited on the sample. b) L-I curves after filling the gap with PMMA of a DL-WG pair91                                                                                       |

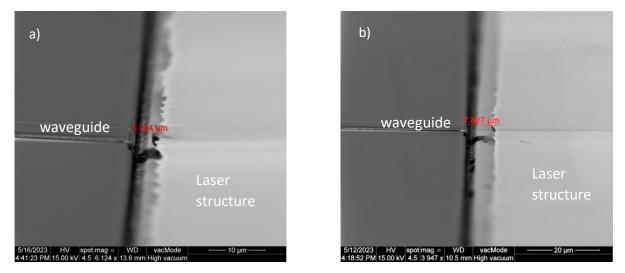

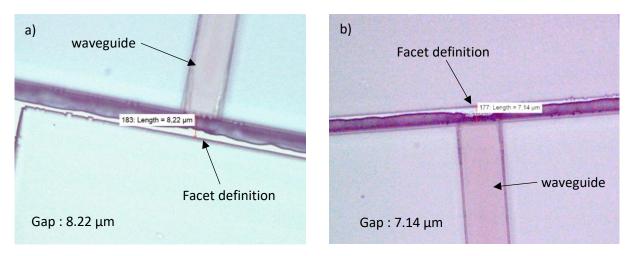

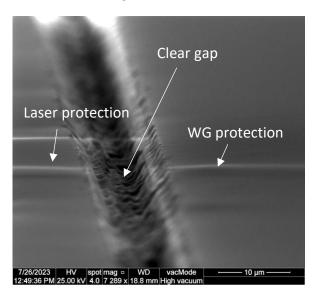

| Figure 92. Optimized polycrystal removal step for two different mask alignments resulting in different gaps                                                                                                                 |

| Figure 93. SEM pictures after the lithography of the laser facet of two samples a) and b) where the gap was reduced                                                                                                         |

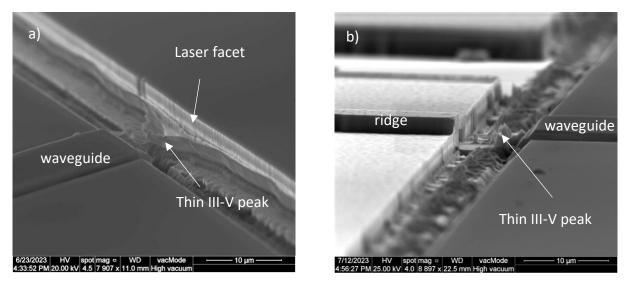

| Figure 94. SEM images of the samples. a) image after the facet etching, b) after the laser ridge93<br>Figure 95. SEM image of the lithography result using the same parameters as the bottom contact                        |

| etching                                                                                                                                                                                                                     |

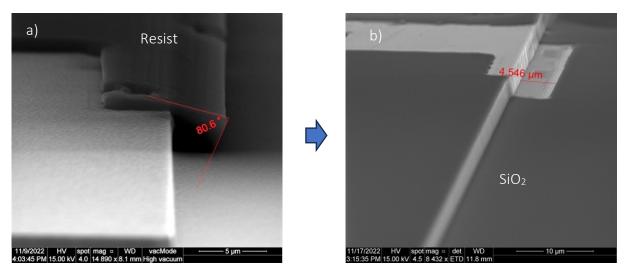

| Figure 97. Sketch of the process technique to deposit the WG layers by lift-off technique after the DL fabrication                                                                                                          |

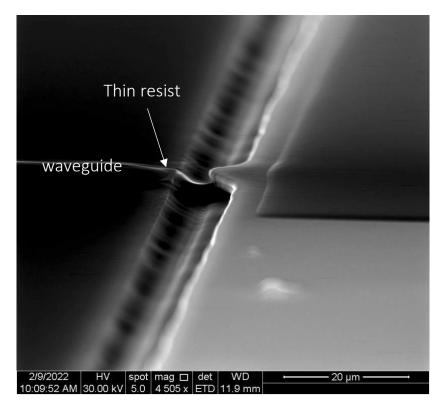

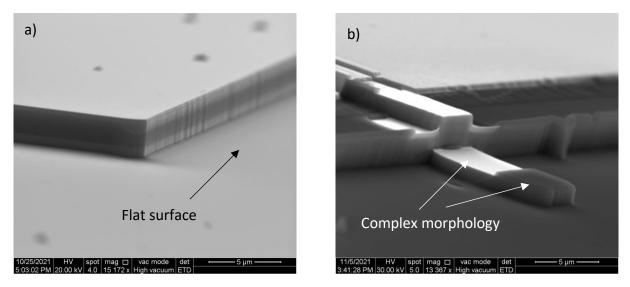

| Figure 98. SEM images of a first test. a) Resist profile after the lithography. b) Device after the lift-off                                                                                                                |

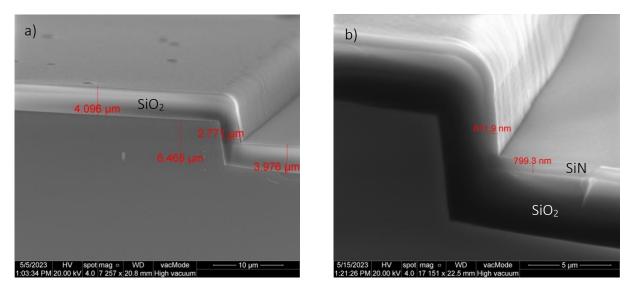

| Figure 99. SEM images of PECVD depositions on a 6.5- $\mu$ m depth etched facet. a) Deposition of 3.9 $\mu$ m of SiO <sub>2</sub> . b) Deposition of 0.8 $\mu$ m of SiN on top of the 3.9- $\mu$ m SiO <sub>2</sub> layer97 |

| Figure 100. Sketch of the process steps to fabricate the WGs integrated with the etched-facet lasers with a $SiO_2$ gap                                                                                                     |

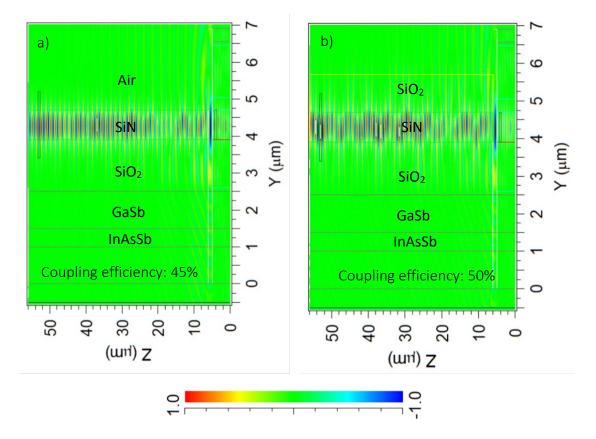

| Figure 101. FDTD simulations of the new configuration. a) with air as the top cladding. b) with 1 $\mu m$ of SiO_2 as the top cladding                                                                                      |

| Figure 102. SEM images of laser morphology. a) after the etching of the facet. b) after the entire laser process                                                                                                            |

| Figure 103. SEM picture of PECVD depositions of SiO <sub>2</sub> and SiN depositions on the facet                                                                                                                           |

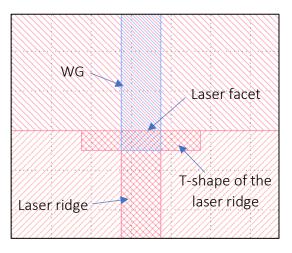

| Figure 105. Mask design of the waveguide and laser ridge definition. The laser ridge mask has a T-<br>shape close to the laser facet to push the corners away                                                               |

| Figure 106. SEM image of the device after the ridge definition                                                                                                                                                              |

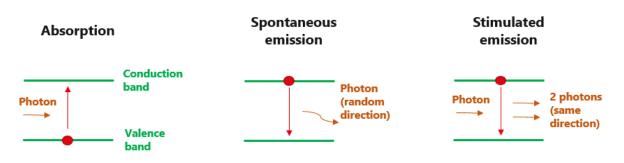

| absorption, spontaneous emission and stimulated emission                                                                                                                                                                    |

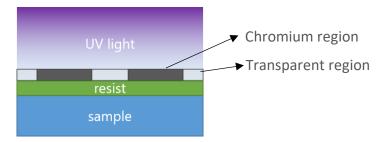

| Figure 111. Sketch of the sample after development. a) In the case of positive resist. b) In the case of negative resist                                                                                                    |

| negative resist                                                                                                                                                                                                             |

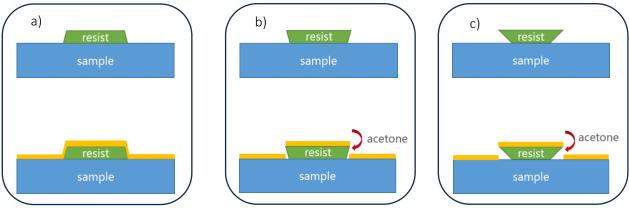

| deposition with a) a positive resist profile, b) a negative resist profile, and c) an accentuated negative resist profile                                                                                                   |

# List of tables

| Table 1. Parameters of the photolithography of the laser ridge definition                         | 23 |

|---------------------------------------------------------------------------------------------------|----|

| Table 2. ICP recipe previously optimized to etch GaSb-based compounds                             | 23 |

| Table 3. Lithography parameters of bottom contact etching                                         | 24 |

| Table 4. Lithography parameters of the metal contact step                                         | 25 |

| Table 5. Recombination coefficient values                                                         | 35 |

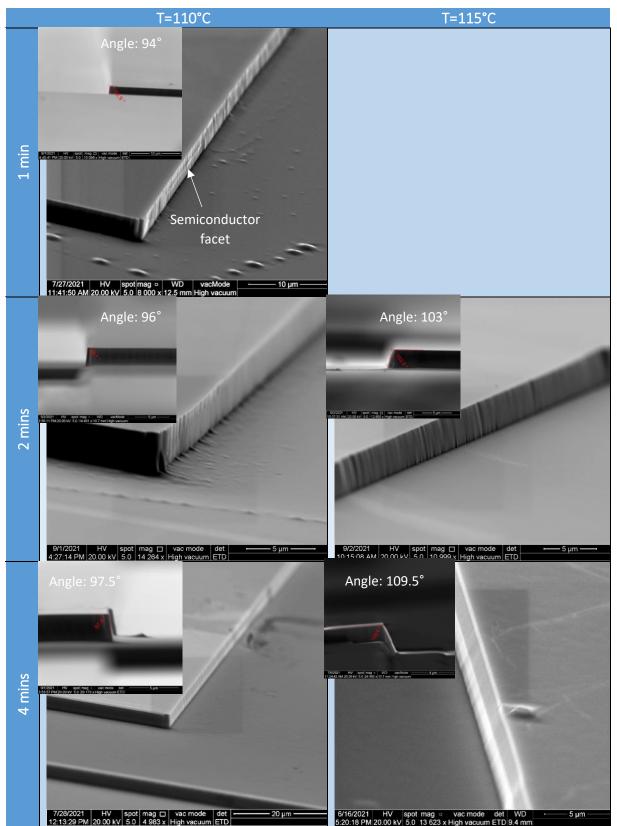

| Table 6. SEM pictures of resist flanks after hard bake for different temperatures and times       | 45 |

| Table 7. SEM pictures of semiconductor flanks after hard bake for different temperatures and time | es |

| and an etching time of 9 minutes                                                                  | 46 |

| Table 8. Hard mask parameters of the facet etching step                                           | 49 |

| Table 9. Photolithography parameters for the laser ridge definition for the etched-facet process  | 52 |

| Table 10. Photolithography parameters of the metallization step for the etched-facet process      | 54 |

| Table 11. Photolithography parameters of the polycrystal removal step                             | 68 |

| Table 12. Lithography parameters for the facet definition on a Si PIC                             | 71 |

| Table 13. Refractive index of different materials under study                                     | 82 |

| Table 14. Refractive indices of different materials.                                              | 87 |

# List of equations

| 28    |

|-------|

| 28    |

| 29    |

| 29    |

| 33    |

| 33    |

| 34    |

| 34    |

| 34    |

| 34    |

| 34    |

| 36    |

| 58    |

| 88    |

| 88    |

| 90    |

| nold. |

| 111   |

|       |

# Introduction

The miniaturization of electronic chips, guided by Moore's Law, has been a cornerstone of the exponential growth of computing and telecommunications, achieving high levels of performance, low power consumption and reduced manufacturing costs. However, the integration density of transistors is arriving to its limits as the power dissipation in chips and the cost per transistor reach an asymptote.[1], [2] Photonic integration, and in particular silicon photonics, has been considered as one of the most promising solutions to overcome these limitations. By harnessing the properties of light rather than electrons, silicon photonics enables optical components to be integrated alongside electronic circuits on the same chip, taking advantage of the very mature silicon industry and CMOS technology. This approach would enable higher bandwidth, low energy consumption and reduced heat generation, providing a cost-effective solution. Significant advances have been made by researchers and industry leaders. However, one of the major remaining challenges is the realization of highly efficient laser sources on these silicon platforms. Much work has been devoted to address this challenge. In particular, the high efficiencies of III-V semiconductors have led to the demonstration of discrete high-performance lasers grown on their native III-V substrates. The next step is to integrate such lasers onto silicon photonic circuits. The heterogeneous integration consists of growing the III-V material on its native substrate and transferring it to the silicon platform, whereas the monolithic integration is based on the direct epitaxial growth of III-Vs on silicon. Although the heterogeneous integration is the most advanced strategy, the monolithic integration is considered the most promising route to low-cost and high-volume production of silicon photonic chips. However, this approach is still in its infancy and further research is needed. Especially, achieving light coupling between the integrated lasers and passive Si-based waveguides would be a major breakthrough towards the realization of fully integrated silicon photonic chips.

Silicon photonics has expanded beyond datacom/telecom into many other application fields. Of interest, the mid-infrared wavelength range is very attractive as many biological and chemical species exhibit their fingerprint absorption lines at these wavelengths. Optical sensing in the mid-infrared is therefore in high demand for societal, environmental and medical applications, among others. However, mid-infrared sensors are bulky and expensive because they still rely on discrete devices. Silicon photonics would offer the opportunity to integrate these mid-infrared devices on silicon platforms to achieve miniaturized, robust and low-cost sensors. To develop these mid-infrared sensors, lasers emitting at these wavelengths are required. Among III-V lasers, GaSb-based lasers are capable of covering the mid-infrared spectral range.

The nanoMIR group specializes in antimonide technology (III-Sbs) and has led major research projects on the integration of antimonides on silicon for mid-infrared sensors. It was within this group that I carried out my work. The aim of my PhD is the integration of GaSb-based lasers on silicon photonic integrated circuits. To achieve this goal, I have carried out different investigations, which are described in 4 different chapters.

In the first chapter, I present the context and motivation of my work in more detail, together with the state of the art. I describe the different approaches to integrating III-V lasers on silicon. I then present the different research efforts in the epitaxial growth of III-V materials on silicon that have overcome significant challenges, followed by the various approaches for coupling the lasers to passive waveguides within a silicon photonic circuit. Finally, I discuss the importance of mid-infrared optical sensing for several vital applications, as well as GaSb-based laser sources capable of covering the mid-infrared wavelength range.

In chapter 2, I investigate the degradation of laser performance caused by threading dislocations, an unavoidable crystalline defect arising from the epitaxial growth of III-Vs on Si. I describe the laser structure and fabrication process, followed by the laser characterizations which are analyzed using a theoretical gain model.

Chapter 3 presents the integration of these GaSb-based lasers on a silicon photonic integrated circuit with the aim of coupling light into passive Si-based waveguides. I begin by describing the associated challenges and then address the development of the laser process on a plain GaSb substrate. Then, I move on to the various fabrication steps, starting with the waveguide fabrication and continuing with the epitaxial growth and processing of the GaSb-based lasers. I then describe the properties of the integrated lasers. Finally, I discuss the light-coupling measurements with the help of simulations.

Chapter 4 is dedicated to the investigation of alternative approaches to increase the light coupling efficiency. I first discuss the possibility of increasing the coupling efficiency by filling the gap between the laser and waveguide. I then studied other approaches to significantly reduce the gap size and thus increase the coupling efficiency.

# 1 Chapter 1. State of the art and motivations

## 1.1 Silicon photonic integrated circuits

#### 1.1.1 Photonic integrated circuit

A photonic integrated circuit (PIC) is a circuit that uses optical signals to perform various functions, similar to how electronic circuits use electrical signals. The idea of a photonic integrated circuit began to take shape in the early years of optical communications in the mid-20<sup>th</sup> century, when researchers and engineers explored the use of light for communication. They were developing optical components such as lasers, modulators or photodetectors, which were discrete and bulky components. As for microelectronics, the goal of a photonic integrated circuit is to integrate all photonic components on a single chip, which would reduce the size, cost and power consumption of the optical components and interconnections. Photonic integration took a significant step forward with the invention of the diode laser in 1962 by Robert N. Hall.[3], [4] Diode lasers provided a compact and highly efficient source of coherent light, which was fundamental to enable the generation of optical signals in integrated circuits. The term "photonics" began to be widely used to describe the use of light to replace applications previously achieved with electronics. In the 1970s, the invention of planar waveguides, structures that can confine and guide light within a thin substrate, was considered a major breakthrough for photonic integrated circuits. Since then, much work has been done to fully integrate photonic functionalities on a single platform, primarily on Indium Phosphide (InP) substrates. The first integration of a laser with another optical component was demonstrated by Suzuki et al. in 1987.[5] Since then, a large range of active and passive photonic components with great performance have been developed in the InP technology, and the fabrication of full photonic integrated circuits with more than 1000 on-chip components was demonstrated.[6]

#### 1.1.2 Silicon photonics

While InP technology was being developed, other research focused on the so-called Silicon (Si) photonics. In fact, InP is a very expensive material and the fabrication of chips relies on 75-mm wafers.[7] The goal of silicon photonics is to integrate photonic and electronic components on a common silicon wafer (Figure 1). This would allow to merge the benefits of PICs with the ones of the very advanced and cheap silicon industry and CMOS technology.[8] It would enable photonics to be scaled up to high levels of integration with improved performance and low cost production based on standard 300-mm wafers used in Si microelectronics.[9], [10], [11], [12], [13], [14]

Figure 1. Representation of a Silicon photonic chip.[15]

Additionally, the optical properties of Si and its related materials allows a large range of applications.[16] Silicon has a wide wavelength transparency window, from 1 to 8 µm, approximately (Figure 2). It can also be combined to a high-quality native oxide (SiO<sub>2</sub>) that serves not only as an insulator and protection but also as a confinement layer thanks to the low refractive index compared with the one of Si (1.4 vs 3.4).[17] Additionally, SiN-based waveguides have recently emerged as a favorable platform thanks to their wider transparency window in the short-wave infrared, lower optical losses and superior high-power handling capability as compared to Si. [18], [19], [20], [21], [22] In addition, SiN has also a higher refractive index than SiO<sub>2</sub> (1.4 vs 2). This makes SiN/SiO<sub>2</sub> waveguides ideal for light propagation. SiN waveguides have been used for example for spectroscopy applications based on surface enhanced Raman spectroscopy.[23] Electro-optic modulators have also been reported using SiN-based platforms. [24], [25] Interestingly, the wavelength transparency window can be increased by introducing Germanium (Ge) which is transparent up to 15  $\mu$ m, approximately (Figure 2). It has a high refractive index (4), which offers the possibility to effectively guide light as well, notably using SiGe material.[26] Other functionalities, like optical modulation, can also be implemented on this platform.[27], [28]

Figure 2. Transmission window of different waveguide materials. The white areas are the wavelength range over which waveguide propagation loss is less than 2 dB/cm. The orange areas are the wavelength range over which loss is high.[8]

Silicon photonics has been considered during the last decade as the most promising platform for the realization of ultra-dense photonic chips. However, one of the biggest challenges in silicon photonics is the realization of high-performance light sources, the component that generates light. It has been the focus of research and has been extensively studied as it is a fundamental step toward the realization of silicon photonic chips. There are several ongoing research efforts that address this problem using different approaches that we will summarize in the next section.[29]

## 1.2 Light sources

#### 1.2.1 Group-IV semiconductor lasers

Since the platform of interest is Si-based, the most appealing way to realize the light source would be with Si-based lasers. There has been much research on Si-based lasers for this reason. Ge-based lasers have also been studied because of their compatibility with the Si foundries. However, Si and Ge are semiconductor materials with an indirect bandgap: the lowest energy of the conduction band and the highest energy of the valence band do not share the same wavevector. Due to the energy and momentum conservation laws, the emission of light by the radiative recombination of an electron-hole pair requires that a third particle (a phonon) be involved in the transition, which is highly improbable. This makes indirect bandgap materials not efficient for light emission. Despite this inconvenient, some progress has been made by exploiting sub-bandgap light-emission processes involving one- and two-phonon assisted transitions.[30] In addition, some recent impressive progress has been made using GeSn alloys which allows to obtain a direct bandgap structure.[31], [32], [33] However, the performances are still too low, making III-V semiconductor lasers the best candidates to date for the integration of lasers on Si platforms.[34], [35], [36]

#### 1.2.2 III-V semiconductor lasers

III-V semiconductors refers to compounds composed of elements from group III and group V of the periodic table. These materials are known for their excellent electronic and optoelectronic properties. They are the most efficient materials for light emission because most of them, like GaSb, InAs or GaAs, among others, exhibit a direct bandgap. In this case, the lowest

energy level of the conduction band and the highest energy level of the valence band are at the same wavevector (Figure 3). This makes electron-hole pair radiative recombination highly efficient.

*Figure 3. Energy band structure of GaAs, an example of direct bandgap.*

III-V lasers also have the flexibility to address a large range of wavelengths, which makes them highly interesting for several applications. For these reasons, they have been extensively studied and they have emerged as the best candidates for the integration of lasers on PICs. Among all the III-V materials, III-Vs crystallizing in the zinc-blende crystal structure are the ones studied for a long time in our group.

In the next section we will describe the different approaches and challenges of integrating these III-V lasers on Si wafers.

#### 1.3 Integration approaches

It exists two integration approaches: the heterogeneous and the monolithic integrations. In this section we are going to address these different integration strategies.

#### 1.3.1 Heterogeneous integration

The heterogeneous integration consists in the transfer of III-V materials or components grown on their native substrate, onto the Si wafer. In this strategy, there are three main techniques: wafer-to-wafer or die-to-wafer bonding, flip-chip integration and micro-transfer printing. The wafer-to-wafer bonding technique involves growing the III-V materials on their native substrate after which the unprocessed III-V wafer is bonded onto the Si wafer, typically after the Si front-end processes are complete, *e.g.* waveguide fabrication. The III-V native

substrate is then removed followed by the device processing (Figure 4a).[37], [38] The advantage of this technique is that the devices are defined using lithography after bonding which enables a high alignment accuracy with the waveguides.[39] Flip-chip integration involves pre-fabricated III-V devices that are aligned and bonded to the Si photonic circuit after the Si front-end and back-end processes are complete (Figure 4b). This technique is quite slow as it involves single-laser transfer (typically 100 units per hour). Finally, micro-transfer printing starts with a finished Si photonic wafer with local back-end openings, where the devices need to be integrated. Multiple coupons of pre-processed devices are simultaneously transferred in a single operation onto the Si wafer by the use of stamps (Figure 4c), typically a soft elastomeric material such as polydimethylsiloxane (PDMS).[39], [40], [41] In one printing cycle, a large number of devices are transferred, resulting in a high throughput integration, similar to the wafer-to-wafer bonding technique. In addition, as with flip-chip integration, this technique allows pre-testing of the devices on their native substrate as they are fabricated prior to their integration on the target Si photonic wafer.

Figure 4. III-V-on-Si heterogeneous integration approaches. a) Wafer-bonding. b) Flip-chip integration. c) Micro-transfer printing.[39]

The heterogeneous integration approach is the most advanced one nowadays.[42], [43], [44], [45] Some commercial products have already entered the market.[46] Despite the maturity of this strategy, it is expected that the monolithic integration will surpass the heterogeneous one in terms of scalability and economic perspectives in the mid- to long-term.[47], [48] In addition, the heterogeneous integration requires etching away the native III-V substrate, a practice that would not be sustainable in the long term.

#### 1.3.2 Monolithic integration

The monolithic integration is based on the direct epitaxy of the III-V material on the Si platform. Although, this is a promising strategy several challenges have to be addressed such as the poor crystal quality of the III-V-on-Si epitaxial material and the complex integration process.

The direct epitaxy of III-Vs on Si generally leads to a large density of crystal defects caused by the lattice, thermal and polarity mismatches between III-Vs and Si. These crystal defects will affect the device performance. When two materials with different thermal expansion coefficient, such as III-Vs and Si, are exposed to high temperatures, the lattice retraction will be different for both materials during cooling down. This, in turn, generates stress in the sample, which can result in the formation of macroscopic cracks for a too-high stress. This can be avoided by using slow temperature ramps during cool down. Another problem is that Si is a non-polar material (crystal made of only one type of atoms) arranged in the diamond crystal structure (Figure 5.a)) whereas III-Vs are polar materials (two types of atoms with different ionicity) arranged in the zinc-blende crystal structure (Figure 5.b)). As the zinc-blende crystal structure doesn't have an inversion symmetry, two different bonds between the III-V and the Si structure will exist. As a result, two different domains will grow from the III-V-Si interface: the so-called V-polar and III-polar domains. At the interface of these two domains, III-III and V-V bonds occurs which form so-called antiphase boundary (APB). [49] These APBs create short-circuits in devices and deteriorate their electrical characteristics. This issue is one of the most important challenges for the integration of III-Vs on Si. Much research has been devoted for a long time to study APBs and to find growth strategies that allow their suppression. Ways to avoid them have been established to demonstrate GaAs-based lasers grown on CMOS-compatible (on-axis) Si substrates. [50], [51], [52] The strategy used consisted in growing templates such as GaAs on Si or GaP on Si by metal-organic vapor phase epitaxy (MOVPE), which allows a Si surface preparation that rapidly avoids APBs. The samples are then transferred to a molecular beam epitaxy (MBE) machine to grow the laser heterostructure. InPbased lasers on Si have also been reported using MOVPE growth, but on patterned Si substrates, which are only marginally compatible with the industry. [53], [54] Later, a strategy based on growing an AlGaAs layer on top of the on-axis Si substrate by MBE allowed to demonstrate InAs-based lasers grown on a single MBE run.[55], [56] In our group, great efforts were done to burry APBs within a GaSb buffer layer. III-Sb lasers fully grown by MBE on Si were reported but they were grown on Si substrates having a large offcut (6°), not compatible with the industry standards. [57], [58] In the following years, a significant breakthrough was achieved by further optimizing the Si substrate preparation to burry APBs. This achievement allowed to demonstrate a variety of mid-infrared lasers epitaxially grown by MBE on on-axis, CMOScompatible, Si substrates. [59], [60], [61], [62], [63], [64]

Figure 5. a) Silicon crystal structure. b) III-V crystal structure. c) Sketch of a V-polar domain and a III-polar domain separated by the antiphase boundary (III-III and V-V bonds).[59]

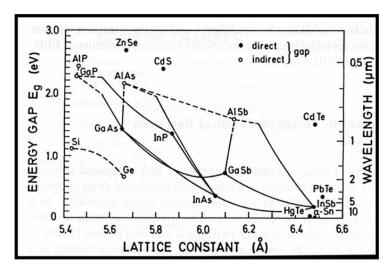

The APBs issue has been resolved in our group. However, another type of defects is created during the III-V-on-Si epitaxial growth: dislocations. Actually, the lattice parameter mismatch between most of the III-V compounds and Si is very high (Figure 6). This leads to stress accumulation during the growth. At a given thickness, the stress is released by generating dislocations.

Figure 6. Energy gap and wavelength vs. lattice constant for some elementary and binary semiconductor materials.

The most common type of dislocation are threading dislocations (TDs) and they are inevitable.[65], [66] They propagate through the entire epitaxial structure, as can be seen in **Figure 7**, reaching the active zone where they will act as non-radiative recombination center and degrade laser performance. Even if they cannot be avoided, their density can be reduced, and this is one of the main challenges regarding the monolithic integration scenario. Much research has been devoted to reducing the threading dislocation density (TDD)[67] and some strategies have proven effective, such as growing filter layers in order to annihilate dislocations. The lowest TDD achieved in our team for a GaSb-on-Si growth is in the low-10<sup>7</sup> cm<sup>-2</sup>, compared

to the  $10^9$  cm<sup>-2</sup> when no growth strategy is applied and to  $10^3$  cm<sup>-2</sup> for growths on native GaSb substrate.

Figure 7. TEM pictures of GaSb layer grown on Si substrate where threading dislocations are visible (Courtesy of Karl Graser, PDI Berlin).

The monolithic integration approach is the most promising one in terms of scalability and cost reduction. High-performance lasers have been reported despite the high defect density arising from the III-V-on-Si growth. However, these lasers have only been demonstrated as discrete devices. The next step toward fully integrated Si photonic chips would be to integrate them on a Si PIC and demonstrate the light coupling from the integrated lasers to passive Si-based waveguides. To address this challenge, different coupling configurations have been studied, either for the heterogeneous or monolithic approach, and I will compare them in the next section.

## 1.4 Coupling configurations

The high defect density arising from the III-V laser growth on Si is not the only challenge of the monolithic integration scenario. The next challenge is the complex fabrication process of lasers on the Si PICs. While the laser cavity mirrors are not difficult to obtain by simple cleavage for discrete III-V-on-Si lasers, for lasers integrated on Si PICs this approach is no more an option since the lasers and the Si PIC are on the same chip. The optical cavity should therefore be processed by other means. The fabrication strategy should also enable the coupling of these active components with the rest of the circuit, *i.e.* the light output from the laser sources should be coupled into passive waveguides which will guide the light to the other optical functions. There are two main coupling configurations that are being studied: evanescent coupling and butt-coupling.

The evanescent coupling is the configuration traditionally used in the heterogeneous integration. It is achieved by bringing the laser and the waveguide into close proximity such

that the electromagnetic field of the laser penetrates into the waveguide via the evanescent field (Figure 8.a)).[68] A tapper is used to progressively reduce the effective refractive index down to the one of the waveguide in order to enable the light coupling. This configuration requires very precise alignment to achieve high coupling efficiency. But, when properly implemented, it can provide very high coupling efficiency, with values reaching up to 90%.[69]

On the other hand, the butt-coupling configuration involves aligning the laser and waveguide face-to-face (Figure 8.b)). The optical field is transmitted by optical mode overlap. This configuration is generally easier to fabricate and align compared to evanescent coupling but the coupling efficiency is lower. The primary reason for this is the high sensitivity of the coupling efficiency to the gap between the laser and the waveguide[70] and also the mismatch between the laser mode and the waveguide mode. A coupling efficiency for this configuration of around 60% have been reported in the heterogeneous approach by Romero-Garcia *et al.*[71]

Figure 8. The two main light coupling configurations. a) Evanescent coupling of a III-V laser into a Si waveguide thanks to a taper section.[69] b) Butt-coupling configuration of a laser into a Si waveguide.[72]

Overall, for applications that demand high coupling efficiency, the evanescent coupling may be the preferred choice even if the fabrication process is less straightforward. Regarding the monolithic integration, the growth of III-V lasers on Si inevitably results in crystal defects detrimental to device performance. Strategies to reduce their density requires growing thick buffer layers (1-5  $\mu$ m) underneath the laser structure. These layers prevent implementing evanescent light coupling from the laser into the waveguide because of the large vertical distance between the laser active zone and the waveguide core, resulting in a drastic increase of the coupling losses. The alternative solution is therefore to implement the butt-coupling configuration. This is the coupling configuration that I developed in my work.

At the beginning of my Ph.D., no III-V lasers had been demonstrated that were monolithically integrated on Si and optically coupled to passive Si-based waveguides. This is the main objective of my thesis as this is considered a key challenge to unlock the realization of Si photonic chips.

## 1.5 Applications of Si PICs

The soaring demand for silicon photonics chips was initiated in the datacom/telecom applications. Actually, in the microelectronics industry, the miniaturization and integration density of transistors, guided by the Moore's Law, is arriving to its limits.[2] It is, therefore, necessary to find an alternative solution to increase communication bandwidths and reduce power consumption, and Si photonics would enable the rapid transmission of data at high bandwidths, providing a cost-effective solution.[73] Silicon photonics has been extended to many other applications besides datacom/telecom, such as optical sensing, optical interconnects, LiDAR (Light Detection and Ranging) systems or quantum technologies, to name but a few.[74], [75], [76], [77], [78] Among these applications, the development of technologies based on optical sensing has been considered a vital need for several applications that we will discuss in the next section.

#### 1.5.1 Optical sensing in the mid-infrared

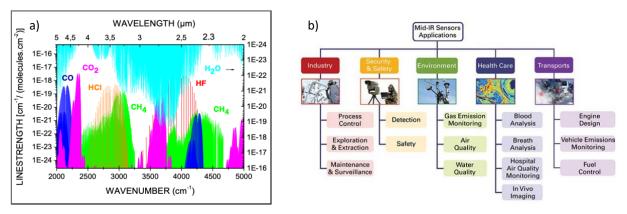

The short-wave portion of the mid-infrared (SWIR) electromagnetic spectrum, ranging from 2 to 5 µm, contains transparency windows of the atmosphere as well as absorption lines of many biological and chemical species (Figure 9a).[79] Developing sensors which work in this wavelength range has been, therefore, considered a vital need for societal, environmental or medical applications, among others (Figure 9b). Their demand has increased significantly in the last decade. In the 2-5-µm spectrum (Figure 9a), gases of interest, such as CO, CO<sub>2</sub>, HF or CH<sub>4</sub>, absorb light. Accurate measurement of the concentration of these molecules is crucial. For instance, detecting CH<sub>4</sub>, a gas with low explosion limit in the air and known for contributing to global warming, [80] is vital for leak detection [81] and gas emission monitoring. Also, the detection of toxic gases like CO or CO<sub>2</sub>[82] is essential for industrial process and air quality controls, for disease diagnosis in the health care sector, to name a few. In addition, some portions of the spectrum are of interest as there are  $H_2O$  windows, which avoids interference of atmospheric water. In this thesis, I mainly worked on lasers emitting near 2.3 µm, a wavelength of interest for trace gas sensing because of the presence of absorption lines of CH<sub>4</sub>, NH<sub>3</sub> and CO, and a H<sub>2</sub>O transparence window (Figure 9a).[83] In addition, this wavelength has recently being used for LIDAR applications.[84]

Figure 9. a) 2-5-μm mid-IR spectrum.[79] b) Mid-IR sensors applications.[85]

The specific characteristics and requirements of these sensors depend on the application. In general terms, they need to be sensitive and selective to detect very low molecule concentrations and target the desired molecule or gas. Much research is focused on sensors based on laser spectroscopy. The TDLAS technique, that stands for Tunable Diode Laser Absorption Spectroscopy, is widely used for gas sensing. The light emitted by the laser source passes through a sample of the gas of interest. If the wavelength of the laser matches the absorption line of the molecule, part of the light is absorbed. The transmitted laser light, after passing through the gas sample, can be measured with photodetectors. The photodetector measures the intensity of the transmitted light at the absorption wavelength and the concentration of the gas can be deduced using Beer-Lambert relation. Other techniques can also be used for gas detection such as QEPAS (quartz-enhanced photoacoustic spectroscopy) or CEPAS (cantilever-enhanced photoacoustic spectroscopy) which are based on the detection of acoustic waves generated by the de-excitation of the target gas molecules.

These mid-IR sensors require laser sources emitting at the wavelengths of interest. In the next section, we will discuss about mid-IR lasers.

#### 1.5.2 Mid-IR lasers

#### 1.5.2.1 The antimonide technology

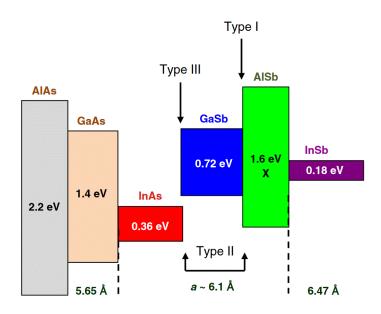

As discussed previously, III-V lasers are the best candidates for Si PICs thanks to their high efficiency. They also have the flexibility to address a wide range of wavelengths in the mid-IR through the choice of adapted materials and the engineering of the band structure (Figure 6). For example, to address wavelengths in the 2-5- $\mu$ m spectral range, antimonides are adapted and these are the ones that have been studied for a long time in our group. Antimonides refers to compounds that have a lattice constant close to 0.61 nm, such as GaSb, InAs and AlSb compounds and their ternary, quaternary and pentanary alloys.[86] They can cover the 2-5- $\mu$ m wavelength range while being closely lattice-matched to GaSb or InAs (Figure 6). Another feature of these compounds is the variety of band alignments.[87] Figure 10 shows the band alignments of III-V binaries in the antimonide material system. We can see different bandgap energies as well as different band alignments (type-I, II and III). The GaSb/AlSb system is type I.

The valence-band maximum of AISb is lower than the conduction-band minimum of InAs, giving a type-II band alignment for the AISb/InAs heterostructure. Finally, the conduction-band minimum of InAs being lower than the valence-band maximum of GaSb, the InAs/GaSb system is type-III. By choosing the right material system and properly designing the composition and layer structure, band engineering allows covering the entire mid-IR spectrum.

Figure 10. Band structure alignments for a selection of unstrained III-V binaries at 300 K.[88]

#### 1.5.2.2 Mid-IR lasers and state of the art on Si substrates

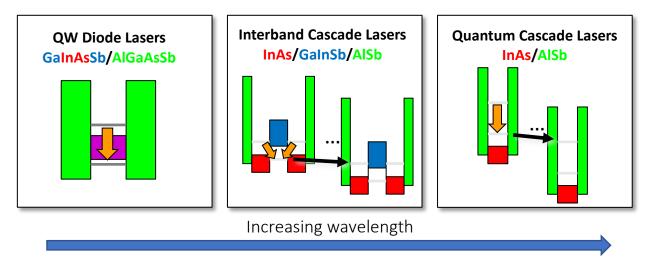

There exist different types of lasers such as diode lasers (DLs), interband cascade lasers (ICLs), quantum cascade lasers (QCLs), among others. They are differentiated by their band structure engineering and carrier confinement schemes leading to distinct emission wavelengths and characteristics.

Figure 11. Band alignments and recombination mechanisms of QW diode lasers, interband cascade lasers and quantum cascade lasers.

ICLs involve interband transitions in a type-II QW where carriers are collected and transferred to the next neighbor type-II QW, leading to a cascade effect. Their design allows

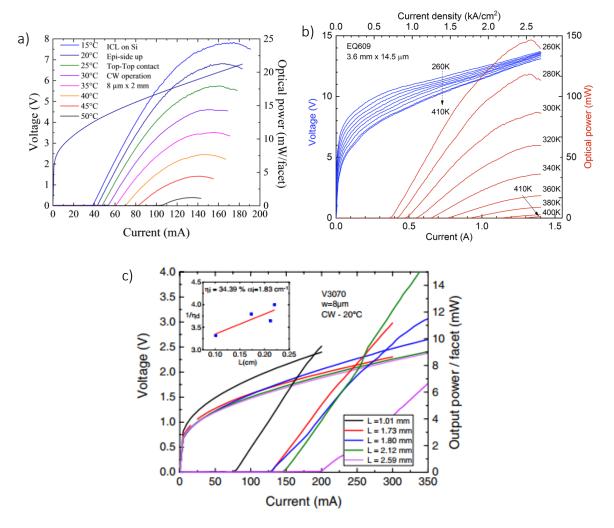

addressing wavelengths from 3 to 7  $\mu$ m. The first ICL was reported in 1997 with an emission wavelength at 3.8  $\mu$ m.[89] The ICLs studied in our team are based on GaInSb/InAs type-II QWs. Their epitaxial growth on on-axis Si substrates has been demonstrated emitting at 3.4  $\mu$ m in the continuous-wave regime and with high performance (Figure 12.a).[64] A quantum cascade laser is based on intersubband transitions within the conduction band in a repeated stack of quantum well structures also creating a cascade effect. QCLs were first demonstrated in 1994 and emitted at 4.2  $\mu$ m in pulsed operation.[90] However, they allow going to longer wavelengths and they are now capable of covering a wide range of wavelengths in the mid-IR, going up to 25  $\mu$ m thanks to the low-energy intersubband transitions (Figure 13).[91] QCLs epitaxially grown on on-axis Si substrates and emitting at 8  $\mu$ m have also been reported in our group (Figure 12.b). They are based on InAs/AlSb structures (Figure 11).[63]

Figure 12. L-I-V curves of different types of lasers grown on on-axis Si substrates. a) ICL. b) QCL. c) DL. [62], [63], [64]

On the other hand, DLs are based on interband transitions in a type-I quantum well structure (Figure 11) and are able to address part of the SWIR wavelength range. The first Sb-based electrically pumped type-I QW diode laser was demonstrated in 1984 using AlGaSb/GaSb QWs emitting at 1.65  $\mu$ m in pulsed operation.[92] In our group, DLs are fabricated with GaInAsSb/AlGaAsSb (QW/barrier) quaternaries and emission wavelengths between 1.55 and

3.3  $\mu$ m have been demonstrated.[93] Diode lasers emitting at 2.3  $\mu$ m have been studied for a long time and they have been used for all the different investigations carried out during my thesis, because they can easily be benchmarked. Although DLs emitting at 2.3  $\mu$ m can be achieved with InP-based lasers, GaSb-based DLs exhibit lower threshold current densities in this spectral range.[69], [94] The state of the art GaSb DLs grown on an on-axis Si substrate before the start of my PhD exhibited a threshold current in continuous-wave operation of around 75 mA for a cavity length of 1 mm and a laser ridge of 8  $\mu$ m (Figure 12.c), high temperature operation and a few tens of mW output power.[62]

Each type of laser has unique characteristics that make them suitable for specific applications in different regions of the mid-IR electromagnetic spectrum. The threshold current density as a function of the operating wavelength for the different types of laser is summarized in **Figure 13**.

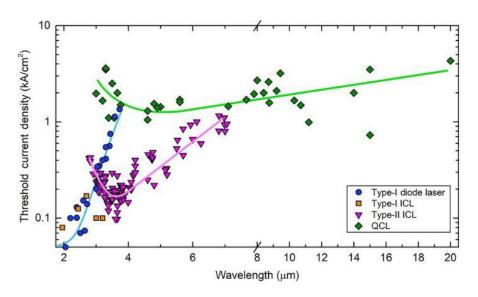

Figure 13. Threshold current densities vs. wavelength of different types of mid-IR lasers.[81]

As discussed in section 1.3.2, threading dislocations arise from the highly-mismatched III-V-on-Si growth and are unavoidable. They create energy levels within the bandgap with which carriers can interact through non-radiative recombination mechanisms (see section 5.1). ICLs are based on transitions between the conduction and valence bands of the neighboring layer, which makes the recombination of the carrier with the defect level in the bandgap unlikely.[64] QCLs are based on intersubband transitions in the conduction band, so carriers do not interact with the defect level in the bandgap. However, while ICLs and QCLs are highly tolerant to threading dislocations,[63], [64], [95] the performance of DLs is dramatically degraded by these defects as the transitions are from the conduction band to the valence band of the QW layer. Great efforts have been made in our team to reduce the TDD. Although significant progress has been made and an improvement in DL performance has been observed, it is not yet comparable to the performance of DLs grown on native GaSb substrate. I have thus

proposed to study the effect of threading dislocations on the GaSb-based DL performance to address this challenge.

## **1.6 Conclusion**

Silicon photonics has emerged as the most promising technology for reducing the cost and increasing the scalability of photonic integrated circuits. The main remaining challenge is the realization of efficient light sources on Si. III-V semiconductor lasers have proven high efficiency and are considered the best candidates for this challenge. The heterogeneous integration of III-V lasers on Si is the most mature approach and devices have already been commercialized. In contrast, the monolithic integration is still in its infancy. However, there is evidence that the monolithic integration will increase the integration density and reduce cost and waste. It is therefore the most promising approach for realizing ultra-dense photonic chips, despite the poor crystal quality of the III-V-on-Si epitaxial growth. Impressive progress has been made in avoiding APBs. Threading dislocations are inevitable, although their density can be decreased to limit laser degradation. Still, all epitaxial III-V lasers on Si reported so far are discrete devices grown on plain Si substrates. The next step is to integrate these lasers on a Si PIC with light coupled into waveguides.

The realization of Si PICs is highly demanded for several applications. Among these applications, optical sensing in the mid-IR have been identified as a vital need for many societal or medical applications, among others. Antimonides have some excellent features that allow them to cover the entire mid-IR wavelength range while being lattice-matched to GaSb. They are therefore the best candidates so far for the integration of laser sources on a Si PIC for sensing applications.

The objective of my thesis is to take a step forward towards the monolithic integration of mid-IR lasers on Si photonic chips. In chapter 2, I will investigate the impact of threading dislocations on the performance of GaSb-based diode lasers. In this chapter, a meticulous study will be carried out to understand the origin of the degradation of the laser structures. In chapter 3, I will address the integration of lasers on a Si PIC with light coupled into passive Si-based waveguides. In this monolithic scenario, several challenges will be faced such as the limitation of using a butt-coupling configuration, which makes an air gap inevitable, the epitaxial growth of the lasers on a Si PIC and the complex laser processing to achieve light coupling. Finally, in chapter 4, I will propose alternative solutions in order to increase the coupling efficiency. The main test vehicle during my thesis was GaSb-based DLs emitting near 2.3 µm because they have been studied for a long time in our team and they can be easily compared with DLs grown on their native GaSb substrate.

# 2 Chapter 2. Discrete GaSb-based diode lasers grown on GaSb and Si substrates

In the previous chapter, we have discussed the importance of GaSb-based materials to address the mid-IR part of the spectrum for sensing applications. In addition, we have also discussed the different integration approaches and we concluded that the monolithic integration of these lasers on Si is the most promising technique in terms of cost, footprint reduction and large-scale production. However, one of the biggest challenges is the poor crystal quality arising from the epitaxial growth. As opposed to APBs,[60]<sup>,</sup>[61]<sup>,</sup>[96] threading dislocations are unavoidable due to the highly mismatched growth. They dramatically affect the laser performance by inducing non-radiative recombinations, which increases the laser threshold at the expense of the device's lifetime. For now, some aspects of the mechanisms responsible for this deterioration remain unclear in the literature where it is often stated that dislocations introduce additional optical losses as well.[58], [97], [98], [99] In order to study the effect of threading dislocations, we will compare in this chapter two series of GaSb diode lasers emitting near 2.3 μm. One series is grown on native GaSb substrates, whereas the other one is grown on Si substrates. First, I will present the growth and fabrication process of the two series of GaSb diode lasers. The experimental results will be analyzed and confronted to a theoretical gain model which will allow extracting the impact of dislocations on the laser performance.

#### 2.1 Diode laser heterostructure

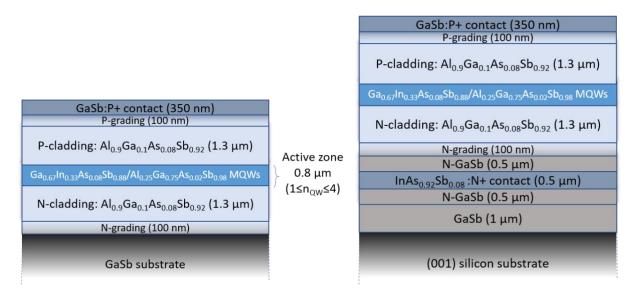

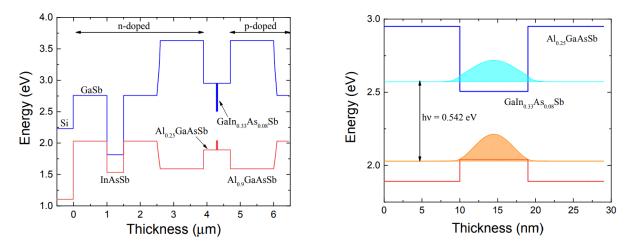

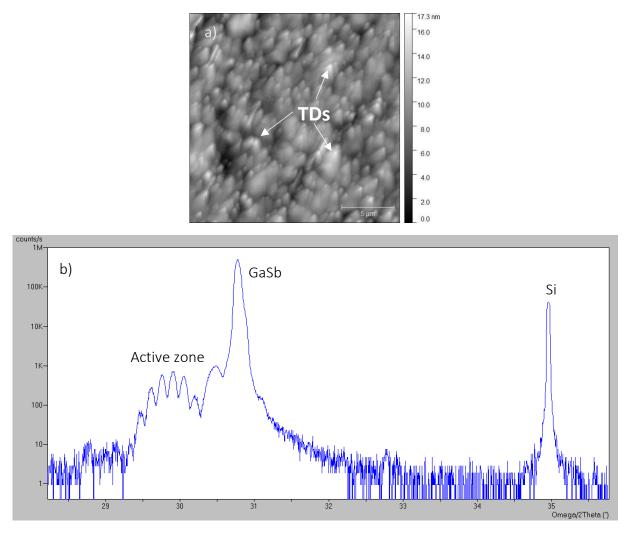

During my Ph.D., I mainly worked on diode lasers designed to emit near 2.3  $\mu$ m (transition energy near 0.542 eV).[87] In this section, I present the design of the laser heterostructure for diode lasers grown on GaSb and on Si substrates.