## (On) The Impact of the Micro-architecture on Countermeasures against Side-Channel Attacks

Lorenzo Casalino

### ▶ To cite this version:

Lorenzo Casalino. (On) The Impact of the Micro-architecture on Countermeasures against Side-Channel Attacks. Computer Science [cs]. Sorbonne Université, 2024. English. NNT: 2024SORUS036. tel-04573949

### HAL Id: tel-04573949 https://theses.hal.science/tel-04573949

Submitted on 13 May 2024

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

Doctoral School of Computer Science, Telecommunication and Electronics (EDITE) of Paris Computer Science Department

# (On) The Impact of the Micro-architecture on Countermeasures against Side-Channel Attacks

By Lorenzo CASALINO

#### A DISSERTATION

Presented and publicly defended on the 30th January 2024 (Grenoble, France) in candidancy for the degree of Doctor in Philosophy

### In presence of the jury:

| Lilian BOSSUET     | University Jean Monnet                          | Jury Chairman |

|--------------------|-------------------------------------------------|---------------|

| Lilian BOSSUET     | University Jean Wonnet                          | Reviewer      |

| Louis GOUBIN       | University of Versailles-St-Quentin-en-Yvelines | Reviewer      |

| Sonia BELAÏD       | CryptoExperts                                   | Examiner      |

| Erven ROHOU        | PACAP, INRIA                                    | Examiner      |

| Arnaud TISSERAND   | Lab-STICC, CNRS                                 | Examiner      |

| Nicolas BELLEVILLE | CEA-List                                        | Supervisor    |

| Damien COUROUSSÉ   | CEA-List                                        | Supervisor    |

| Karine HEYDEMANN   | Thales DIS-LIP6, Sorbonne Université            | Supervisor    |

$Audentes\ Fortuna\ Juvat$

## Acknowledgements

30th January 2024. It is on this very day that I conclude another chapter of my life. A chapter began three years ago, on the 21st January 2021, in the middle of the Covid-19 pandemic. At 06:25 a.m., I boarded the high-speed train departing from Milan, and with destination Paris. On that train, I wondered what I would have lived, who I would have met, how it would have ended. In this few paragraphs, I want to thank the many that, directly or indirectly, aware or unaware, have marked my person along this journey.

My sincere thanks go to my supervisors, Nicolas Belleville, Damien Couroussé and Karine Heydemann. Together, we spent three years of intense and fruitful collaboration. Although the hard times, you have always cared, supported and guided me for the best. For this, I will always be grateful to you. I warmly thank the members of the "Ufficio del Inferno" (original spelling): an unofficial institution of our laboratory, created by the few Ph.D. students trying to survive the constant threat of the infamous *colpo d'aria*. If I have come so far, I also owe it to you.

My experience has not only been marked by the support in the working environment, but also, and foremost, by whom I have met in the everyday life. Thank you, Giulia and Roberto: these three years have been a continuous discovery and evolution of myself, and you played a central role in all of this. A huge thank you to Grenoble Swing and all its members: thanks to you, I have had the possibility to get part, to be part, of something bigger than me, and to improve myself. Right in this association, I have met the one who has become my brother-in-dance, and one of my dearest friends. For having made this period unforgettable, spending awesome evenings in front of a St. Stefanus and dancing; for having been there when the most I needed; for all of this, thank you.

But the support I have gotten goes well beyond that received from those I ran into during this three-year-long chapter. A big shout-out to my "fixed starts": Silvia, Federico, Gianluca, Carolina, Martina, Nipun, Eleonora, Fabrizio and the "Steins; Gate" group. Distant as stars, sometimes in China, Belgium or U.K., you have always been—and I hope you always be— my "reference system", my everlasting support, both in the darkest and brightest moments.

I thank my former M.Sc. supervisors, Alessandro Barenghi and Gerardo Pelosi, for

having introduced me to the marvels of cryptography and side-channel analysis, and for having suggested me to contact Damien for my doctoral studies.

Final thoughts go to my family: my parents, Patrizia and Gianfranco, and my brother, Mattia. What I have achieved throughout all these years, I owe it to your unconditioned love and support.

Grenoble, 29th April 2024.

### Résumé

Les attaques par canaux auxiliaires sont une menace pour la confidentialité des données, en particulier sur les systèmes embarqués. La contre-mesure de masquage constitue une approche de protection sûre et prouvée. Néanmoins, des réalités physiques réduisent les garanties de sécurité prouvées. En particulier, dans le contexte logiciel, le jeu d'instructions (ISA) supporté par un processeur cache au concepteur du schéma de masquage l'une des causes de cette réduction de la sécurité : la micro-architecture. Ainsi, le concepteur ne peut pas déterminer les sources de fuite induites par la microarchitecture et leur impact sur la sécurité d'une implémentation logicielle. Des informations peuvent fuire, par exemple, lors des transitions d'état dans les registres cachés, ou si les signaux dans des éléments combinatoires ont des temps de propagation différents. À cela s'ajoutent les effets de mécanismes spéculatifs potentiels et de la structuration du système mémoire. Plusieurs méthodologies permettent d'atténuer l'impact de la microarchitecture sur les implémentations logicielles masquées, mais ces travaux requièrent une connaissance fine de la micro-architecture, ce qui a plusieurs inconvénients : portabilité limitée des garanties de sécurité entre différentes micro-architectures, connaissance souvent incomplète de la micro-architecture, complexité des micro-architectures. On peut donc se demander s'il existe des approches moins dépendantes de la micro-architecture sous-jacente. Dans cette thèse, nous abordons, selon deux axes, la problématique du développement de logiciels masqués sécurisés en pratique contre les attaques par canal auxiliaire.

Le premier axe vise le développement automatisé de logiciel masqué résistant aux fuites en transitions. Nous proposons une méthodologie qui tire parti des compilateurs optimisants : étant donné une implémentation logicielle, annotée avec des informations relatives aux données sensibles, et une description de la micro-architecture cible, nous montrons comment l'ordonnancement des instructions et l'allocation des registres peut atténuer les fuites basées sur les transitions de manière automatisée.

Le deuxième axe vise une approche indépendante de l'architecture cible. Dans la littérature, les travaux se concentrent en majorité sur l'atténuation de l'impact de la microarchitecture sur les implémentations logicielles protégées par le schéma de masquage Booléen. D'autres types de schémas de masquage ont été montrés plus résistants aux fuites en transition en théorie, et donc potentiellement aux effets de la micro-architecture de la cible. Cependant, leur résistance en pratique n'a pas été étudiée. De plus, l'exploitation potentielle d'informations provenant du parallélisme des données, potentiellement induit par la micro-architecture, n'a pas été étudié pour les implémentations logicielles. Nous étudions ainsi la sécurité en pratique offerte par les schémas de masquage de premier ordre Booléen, arithmétique et produit scalaire contre les fuites induites par la micro-architecture, y compris le parallélisme des données. D'abord, nous montrons que le parallélisme de données se manifeste même sur de simples micro-architectures scalaires. Ensuite, nous étudions l'impact des fuites en transition et du parallélisme de données sur les valeurs masquées avec les schémas de masquage étudiés. Enfin, nous étudions l'impact de ces fuites sur des implémentations masquées du cryptosystème AES-128. Nous montrons qu'aucun des schémas de masquage étudiés n'apporte de protection parfaite face aux fuites micro-architecturales considérées, bien que leur résistance soit très hétérogène.

## Abstract

Side-channel attacks are recognized as a threat for the confidentiality of data, in particular on embedded systems. The masking countermeasure constitutes a provably secure protection approach. Nonetheless, physical non-idealities reduce its proven security guarantees. In particular, in the software implementations, the Instruction Set Architecture (ISA) supported by a processor hides to the masking scheme designer one cause of such physical non-idealities: the micro-architecture. As such, the designer is not aware of the actual micro-architecture-induced side-channel sources and their security impact on a software implementation. Information can leak, for instance, during the state transition of hidden registers, or in the case signals of combinatorial elements exhibit different propagation times. Furthermore, speculative features and the memory subsystems can play a role in such information leakage. Several methodologies allow the mitigation of the impact of the micro-architecture on masked software implementations, but these approaches depend on the detailed knowledge of the micro-architecture, which implies several shortcomings: limited portability of the security guarantees between different micro-architectures, incomplete knowledge of the microarchitecture, complexity of the micro-architecture design. Thus, one might wonder whether there exist approaches less dependent on the underlying micro-architecture. With this thesis, we address, along two axes, the problem of developing practically secure masked software. The first axis targets the automated development of masked software resilient to transition-based leakages. We propose a methodology that takes advantage of optimizing compilers: given in input a software implementation, annotated with sensitive-data-related information, and a description of the target micro-architecture, we show how to exploit the instruction scheduling and register allocation tools to mitigate transition-based leakages in an automated manner. The second axis targets an architecture-independent approach. In literature, most of the works focuses on mitigating the impact of the micro-architecture on software implementations protected with the so-called Boolean masking scheme. Theoretical studies show the better resilience of alternative types masking schemes against transition-based leakages, suggesting their employment against micro-architectural leakage. Yet, their practical resilience has not been explored. Furthermore, the potential

exploitation of the information leaked by data parallelism, potentially induced by the micro-architecture, has not been studied for software implementations. As such, we study the practical security offered by first-order Boolean, arithmetic and Inner-Product masking against micro-architecture-induced leakage, encompassing data parallelism as well. We first show that data parallelism can manifest also on simple scalar micro-architectures. Then, we evaluate the impact of transition-based leakage and data parallelism on values masked with the studied masking schemes. Eventually, we evaluate the impact of such information leakages on different masked implementations of the AES-128 cryptosystem. We show that, although their different leakage resilience, none of the studied masking schemes can perfectly mitigate the considered micro-architectural leakages.

# Contents

| $\mathbf{R}$ | ésum  | é         |                            |  | i                      |

|--------------|-------|-----------|----------------------------|--|------------------------|

| A            | bstra | ct        |                            |  | iii                    |

| $\mathbf{A}$ | crony | ${ m ms}$ |                            |  | ix                     |

| Li           | st of | Figur     | ·es                        |  | xi                     |

| Li           | st of | Table     | es es                      |  | xiii                   |

| Li           | st of | Algor     | m rithms                   |  | $\mathbf{x}\mathbf{v}$ |

| Li           | st of | Micro     | obenchmarks                |  | xvi                    |

| Li           | st of | Defini    | itions and Theorems        |  | xvi                    |

| 1            | Intr  | oducti    | cion                       |  | 1                      |

|              | 1.1   | Conte     | ${ m ext}$                 |  | 2                      |

|              | 1.2   | Motiv     | vation                     |  | 3                      |

|              | 1.3   | Contr     | $\operatorname{ributions}$ |  | 5                      |

|              | 1.4   | Docur     | ment Organization          |  | 6                      |

| 2            | Bac   | kgroui    | nd                         |  | 7                      |

|              | 2.1   | Notat     | tion                       |  | 8                      |

|              | 2.2   | Passiv    | ve Side-Channel Attacks    |  | 8                      |

|              |       | 2.2.1     | Principle                  |  | 8                      |

|              |       | 2.2.2     | Leakage Model              |  | 10                     |

|              |       | 2.2.3     | Statistical Distinguisher  |  | 11                     |

|              |       | 2.2.4     | Further Aspects            |  | 12                     |

|              | 2.3   | The N     | Masking Countermeasure     |  | 13                     |

|              |       | 2.3.1     | Principle                  |  | 14                     |

vi *CONTENTS*

|   |      | 2.3.2                           | Security Models                                                                                                         |

|---|------|---------------------------------|-------------------------------------------------------------------------------------------------------------------------|

|   |      | 2.3.3                           | Leakage Independence and Physical Effects                                                                               |

|   | 2.4  | Securi                          | ty Evaluation of Implementations                                                                                        |

|   |      | 2.4.1                           | Statistical Hypothesis Testing                                                                                          |

|   |      | 2.4.2                           | Information Leakage Quantification                                                                                      |

| 3 | Sta  | te of tl                        | he Art and Research Questions 2                                                                                         |

|   | 3.1  | Prelin                          | ninaries                                                                                                                |

|   |      | 3.1.1                           | ISA and Micro-architecture                                                                                              |

|   |      | 3.1.2                           | Micro-architectural Leakage                                                                                             |

|   |      | 3.1.3                           | On the Variability of the Leakage Behavior                                                                              |

|   | 3.2  | Mitiga                          | ation of Recombination Effects in Software                                                                              |

|   |      | 3.2.1                           | Scope of the Review                                                                                                     |

|   |      | 3.2.2                           | ISA-based Methodology                                                                                                   |

|   |      | 3.2.3                           | ISE-based Methodology                                                                                                   |

|   |      | 3.2.4                           | Non-Completeness-based Methodology                                                                                      |

|   | 3.3  | Discus                          | ssion                                                                                                                   |

|   | 3.4  | Problems and Research Questions |                                                                                                                         |

|   |      | 3.4.1                           | Open Problems                                                                                                           |

|   |      | 3.4.2                           | Research Questions                                                                                                      |

| 4 | An   | Auton                           | nated Methodology to Mitigate Transition-based Leakages                                                                 |

|   | at S | Softwar                         | re Level 39                                                                                                             |

|   | 4.1  | Notat                           | $ion \dots \dots$ |

|   | 4.2  | Transi                          | ition-based Leakage Mitigation                                                                                          |

|   |      | 4.2.1                           | Architectural Register Overwrite                                                                                        |

|   |      | 4.2.2                           | Micro-architectural Register Overwrite—Pipeline Registers 43                                                            |

|   |      | 4.2.3                           | Micro-architectural Register Overwrite—Separated Data paths 4                                                           |

|   |      | 4.2.4                           | Rationale Behind the Mitigation Strategies                                                                              |

|   | 4.3  | Comp                            | ilers and Compilation                                                                                                   |

|   |      | 4.3.1                           | Compiler Organization                                                                                                   |

|   |      | 4.3.2                           | Static Single-Assignment Form                                                                                           |

|   |      | 4.3.3                           | Register Allocation                                                                                                     |

|   |      | 4.3.4                           | Instruction Scheduling                                                                                                  |

|   |      | 4.3.5                           | Code Generation in the LLVM Core Libraries                                                                              |

|   | 4.4  | Enhar                           | acing Code-Generation Modules                                                                                           |

|   |      | 4.4.1                           | General Approach                                                                                                        |

|   |      | 4.4.2                           | Intermediate Value Tagging                                                                                              |

| CONTENTS | vii |

|----------|-----|

|          |     |

|   |     | 4.4.3   | Leakage-aware Machine Scheduler (MS)                                | 63   |

|---|-----|---------|---------------------------------------------------------------------|------|

|   |     | 4.4.4   | Leakage-aware Register Allocator                                    | 66   |

|   | 4.5 | Impler  | mentation Aspects                                                   | 75   |

|   |     | 4.5.1   | Intermediate Value Tagging                                          | 75   |

|   |     | 4.5.2   | Micro-architectural Model                                           | 75   |

|   |     | 4.5.3   | Toolchain Integration                                               | 77   |

|   |     | 4.5.4   | Instruction Scheduling                                              | 78   |

|   | 4.6 | Exper   | imental Evaluations                                                 | 79   |

|   |     | 4.6.1   | Experimental Setup                                                  | 79   |

|   |     | 4.6.2   | Security Evaluation Results and Discussion                          | 81   |

|   |     | 4.6.3   | Overhead Evaluation Results and Discussion                          | 85   |

|   | 4.7 | Relate  | d Work                                                              | 89   |

|   | 4.8 | Conclu  | ısion                                                               | 90   |

| 5 | On  | the Pr  | actical Resilience of Masked Software Implementations               | 93   |

|   | 5.1 | Prelim  | inaries                                                             | 94   |

|   |     | 5.1.1   | A Leakage Model for Parallel Processing of Shares                   | 94   |

|   |     | 5.1.2   | Biasing Leakage Distributions to Attack Masked Parallel Imple-      |      |

|   |     |         | mentations                                                          | 95   |

|   | 5.2 | Paralle | el Processing of Shares in Software                                 | 96   |

|   |     | 5.2.1   | Rationale                                                           | 97   |

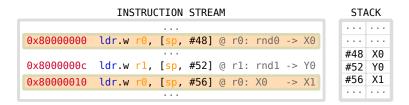

|   |     | 5.2.2   | Microbenchmarks                                                     | 98   |

|   |     | 5.2.3   | Experimental Setup                                                  | 100  |

|   |     | 5.2.4   | Evaluation                                                          | 100  |

|   | 5.3 | Evalua  | ation of the Practical Resilience of Masking Encodings              | 103  |

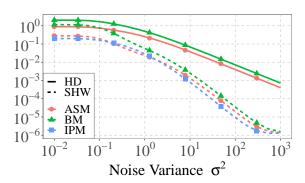

|   |     | 5.3.1   | Theoretical Evaluation                                              | 103  |

|   |     | 5.3.2   | Experimental Evaluation                                             | 105  |

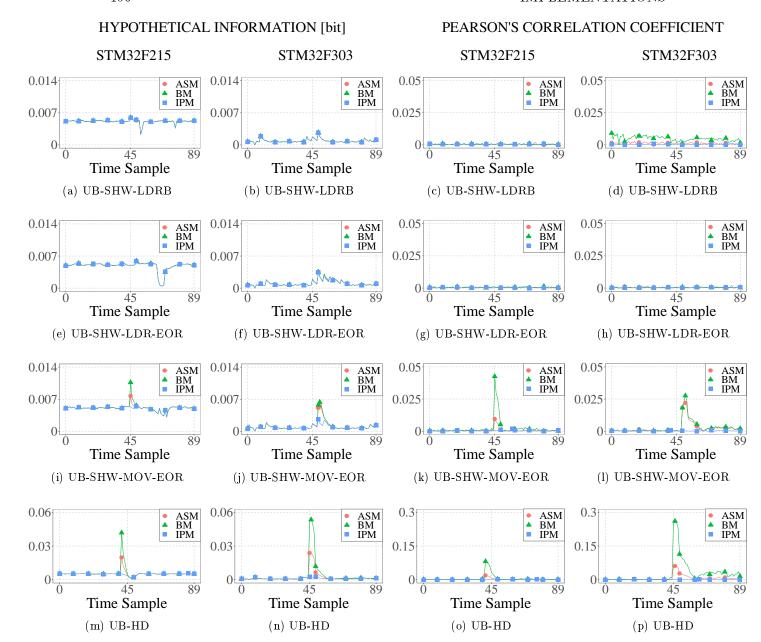

|   | 5.4 | Exploi  | tation of Leakage Model Distribution in Improved Correlation Attack | s108 |

|   |     | 5.4.1   | Rationale                                                           | 108  |

|   |     | 5.4.2   | Evaluation                                                          | 110  |

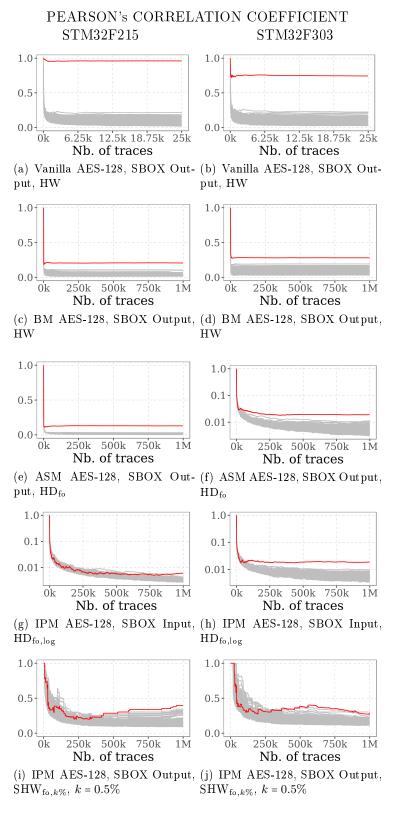

|   | 5.5 | Side-C  | Channel Resilience of Software Masked AES-128                       | 111  |

|   |     | 5.5.1   | Experimental Setup                                                  | 112  |

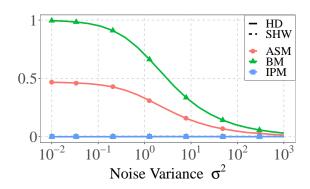

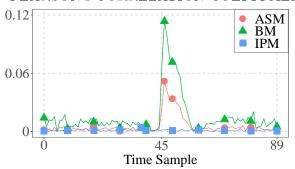

|   |     | 5.5.2   | Information Leakage Evaluation                                      | 115  |

|   |     | 5.5.3   | Information Leakage Exploitation                                    | 117  |

|   | 5.6 | Discus  | $\operatorname{sion}$                                               | 118  |

|   |     | 5.6.1   | On the Resilience of IPM to Transition-based Leakage                | 119  |

|   |     | 5.6.2   | PPS and Parallel-Oriented Architectures                             | 119  |

|   |     | 5.6.3   | Preventing PPS in Software                                          | 120  |

|                                  | 5.7                   | Conclusion   | 121 |  |  |

|----------------------------------|-----------------------|--------------|-----|--|--|

| 6 Conclusion and Perspectives 12 |                       |              |     |  |  |

|                                  | 6.1                   | Conclusion   | 123 |  |  |

|                                  | 6.2                   | Perspectives | 124 |  |  |

| Résumé - Version Étendue         |                       |              |     |  |  |

| Abstract - Extended Version      |                       |              |     |  |  |

| Pe                               | Personal Bibliography |              |     |  |  |

| Bi                               | bliog                 | raphy        | 159 |  |  |

## Acronyms

.td Target Description.

**AGN** Additive Gaussian Noise.

**ASCA** Algebraic Side-Channel Analysis.

BasicRA Basic Register Allocator.

**BLD** Biasing Leakage Distribution.

**DAG** Direct Acyclic Graph.

**DDG** Data-Dependence Graph.

**DOM** Domain-Oriented Masking.

ETag Encoding Tag.

**HD** Hamming Distance.

**HI** Hypothetical Information.

**HW** Hamming Weight.

ILA Independent Leakage Assumption.

${\bf IR}$  Intermediate Representation.

**ISA** Instruction Set Architecture.

**ISE** Instruction Set Extension.

IT Information-Theoretic.

$\mathbf{x}$   $\mathbf{ACRONYMS}$

MI Mutual Information.

MS Machine Scheduler.

**NSA** National Security Agency.

**PCC** Pearson's Correlation Coefficient.

**PI** Perceived Information.

**Post-RA** Post-Register-Allocation.

**PPS** Parallel Processing of Shares.

$\begin{tabular}{ll} \bf Pre-RA & {\bf Pre-Register-Allocation}. \end{tabular}$

SASCA Soft-Analytical Side-Channel Analysis.

**SBox** Substitution Box.

**SCA** Side-Channel Analysis (or Attack).

SSA Static Single-Assignment.

**TI** Threshold Implementation.

# List of Figures

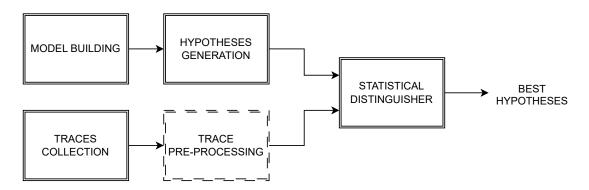

| 2.1  | Overview of a typical SCA process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 8  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

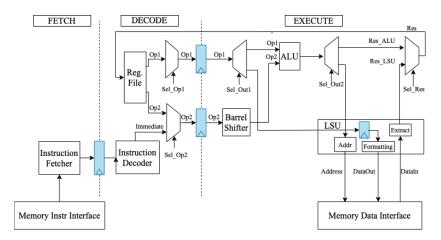

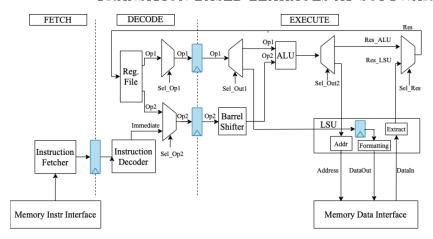

| 3.1  | Simplified model of a three-stage, in-order pipelined micro-architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 22 |

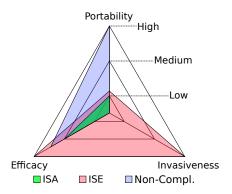

| 3.2  | Qualitative comparison of ISA-based, ISE-based and Non-Completeness-based approaches.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 35 |

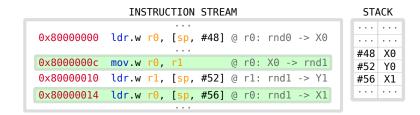

| 4.1  | Architectural register overwrite                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 43 |

| 4.2  | Architectural register overwrite–Register reallocation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 43 |

| 4.3  | Architectural register overwrite–Register flushing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 43 |

| 4.4  | Micro-architectural registers overwrite-Pipeline registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 44 |

| 4.5  | ${\bf Micro-architectural\ registers\ overwrite-Pipeline\ registers:\ instruction\ reschedul-new order and the contraction of th$ |    |

| 4.6  | ing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 44 |

|      | registers flushing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 44 |

| 4.7  | Micro-architectural registers overwrite—Separated data paths                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 45 |

| 4.8  | Micro-architectural registers overwrite—Separated data paths: data path flush-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

|      | ing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 45 |

| 4.9  | Compiler organization and compilation process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 50 |

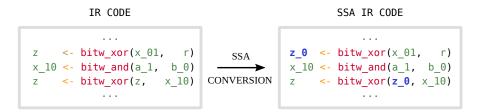

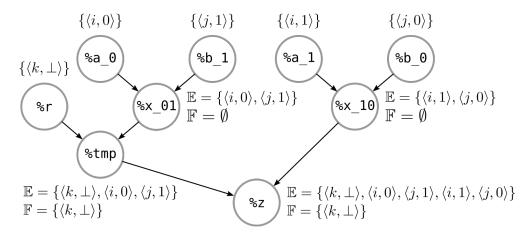

| 4.10 | Conversion to SSA form of an example code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 51 |

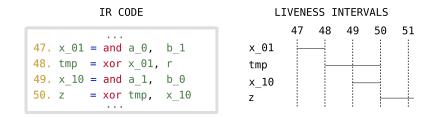

| 4.11 | Liveness intervals of variables in an example code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 51 |

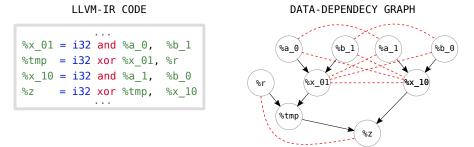

| 4.12 | Data-dependence graph of an example LLVM-IR code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 54 |

| 4.13 | Example of leakage relation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 62 |

| 4.14 | Example of ETags assignment for the SecAnd gadget                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 63 |

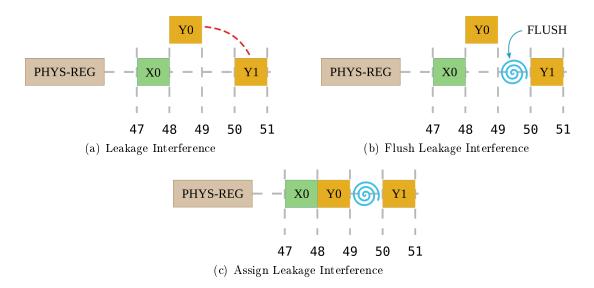

| 4.15 | Occurrences of leakage interferences between live intervals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 67 |

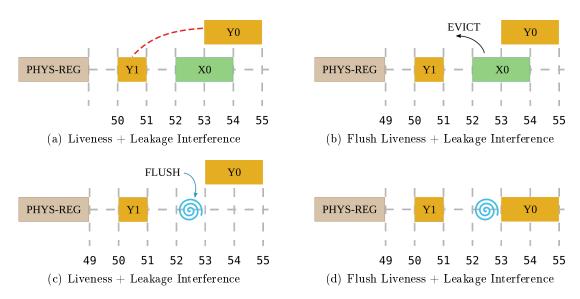

| 4.16 | Occurrences of leakage interferences between live intervals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 68 |

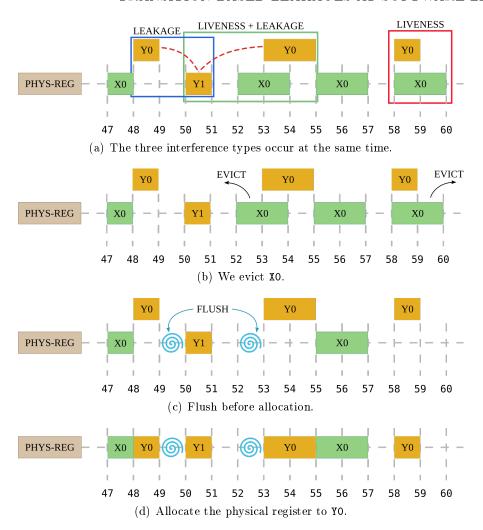

| 4.17 | Handling of liveness interval assignment when the three types of interferences                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

|      | occur at the same time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 70 |

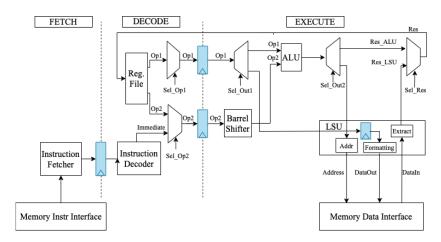

| 4.18 | Leakage-enhanced micro-architectural model for the Cortex-M4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 76 |

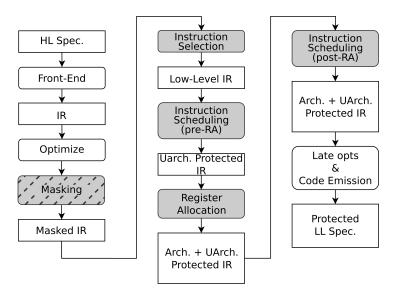

| 4.19 | Toolchain integration.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 77 |

xii LIST OF FIGURES

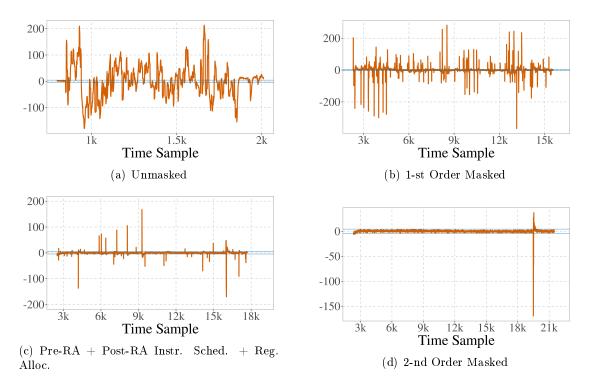

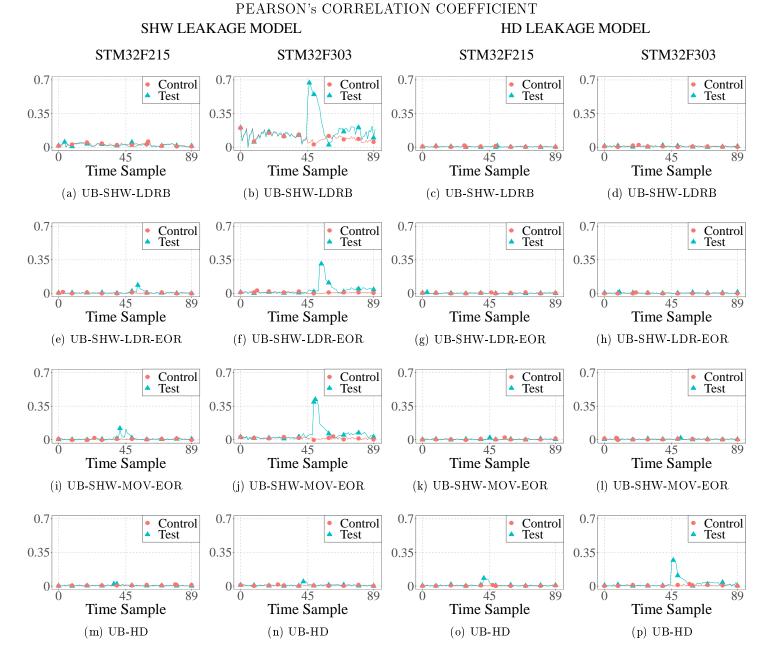

| 4.20 | Non-specific T-test results carried out on the following SIMON128/128 software implementations (10-round-reduced variants) | 82  |

|------|----------------------------------------------------------------------------------------------------------------------------|-----|

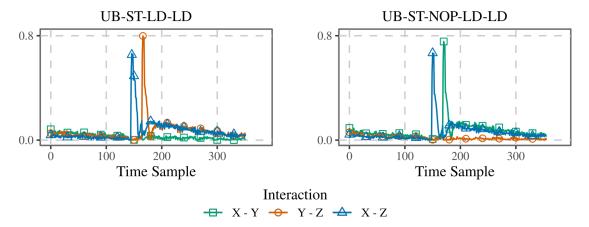

| 4.21 | Correlation plots for the UB-ST-LD-LD and UB-ST-NOP-LD-LD                                                                  | 83  |

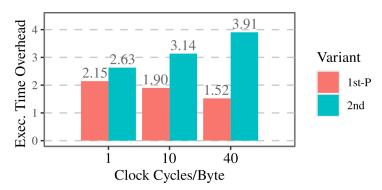

| 4.22 | Execution time overhead induced by on-the-fly randomness generation                                                        | 88  |

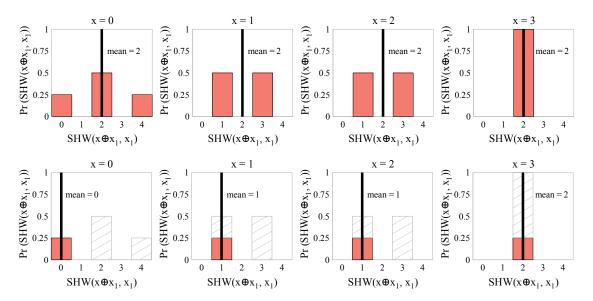

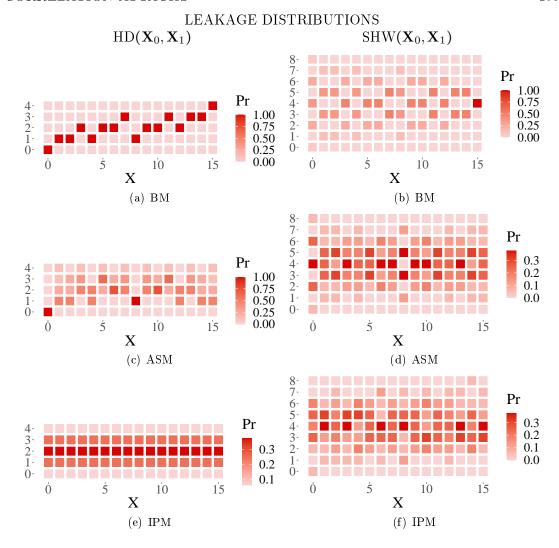

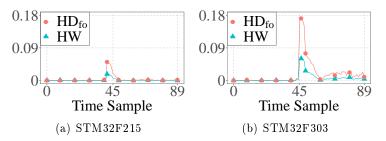

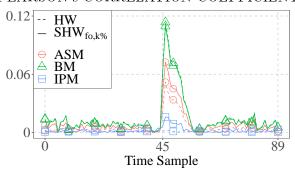

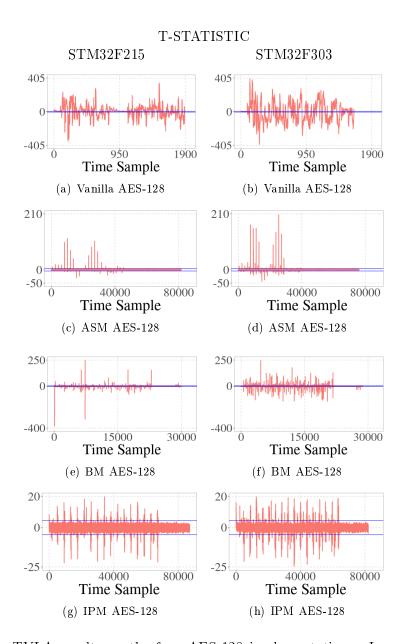

| 5.1  | SHW distributions obtained for various secret values masked with first-order                                               |     |