## Efficient Deployment of Deep Neural Networks on Hardware Devices for Edge AI

Halima Bouzidi

### ▶ To cite this version:

Halima Bouzidi. Efficient Deployment of Deep Neural Networks on Hardware Devices for Edge AI. Artificial Intelligence [cs.AI]. Université Polytechnique Hauts-de-France, 2024. English. NNT: 2024UPHF0006. tel-04574676

### HAL Id: tel-04574676 https://theses.hal.science/tel-04574676v1

Submitted on 14 May 2024

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

École Doctorale PHF nº 635 : Polytechnique Hauts-de-France

Thèse de Doctorat

Déposée pour obtenir le grade de docteur délivré par

## l'Université Polytechnique Hauts-de-France et L'INSA Hauts-de-France

Spécialité "Informatique"

présentée et soutenue publiquement par

### Halima Bouzidi

le 29 Jan 2024 à Valenciennes, France

## Déploiement Efficace des Réseaux de Neurones Profonds sur les Dispositifs Matériels pour l'IA en Edge

Directeur de thèse : **Prof. Smail Niar** Co-encadrant de thèse : **Dr. Hamza Ouarnoughi** Co-encadrant de thèse : **Prof. El-Ghazali Talbi**

Rapporteur

Rapporteuse

Examinatrice

Examinateur

Invité

Jury

Prof. Olivier Sentieys,

Professeur, Université de Rennes, France

Prof. Tulika Mitra,

Professeur, Université de Singapour, Singapour

Prof. Clarisse Dhaenens,

Professeur, Université de Lille, France

Chef de laboratoire, Thales France

Prof. Abdessamad Ait El-Cadi,

Professeur, INSA Hauts-de-France, France

**LAMIH-UPHF**

Déparetement Informatique

UMR CNRS 8201, 59300 Famars, Valenciennes, France

École Doctorale PHF nº 635 : Polytechnique Hauts-de-France

Ph.D. Dissertation

Submitted to obtain a degree of Doctor in Philosophy from

## l'Université Polytechnique Hauts-de-France et L'INSA Hauts-de-France

Discipline "Computer Science and Engineering"

Publicly presented and defended by

### Halima Bouzidi

On the 29 Jan 2024 in Valenciennes, France

## Efficient Deployment of Deep Neural Networks on Hardware Devices for Edge AI

Thesis Director: **Prof. Smail Niar**

Thesis Co-Supervisor : **Dr. Hamza Ouarnoughi** Thesis Co-Supervisor : **Prof. El-Ghazali Talbi**

### Jury

Prof. Olivier Sentieys,Professor, University of Rennes, FranceReviewerProf. Tulika Mitra,Professor, University of Singapore, SingaporeReviewerProf. Clarisse Dhaenens,Professor, University of Lille, FranceExaminerDr. Nicolas Ventroux,Head of Laboratory, Thales, FranceExaminerProf. Abdessamad Ait El-Cadi,Professor, INSA Hauts-de-France, FranceInvitee

#### LAMIH-UPHF

UMR CNRS 8201, 59300 Famars, Valenciennes, France

#### **ABSTRACT**

Neural Networks (NN) have become a leading force in today's digital landscape. Inspired by the human brain, their intricate design allows them to recognize patterns, make informed decisions, and even predict forthcoming scenarios with impressive accuracy. NN are widely deployed in Internet of Things (IoT) systems, further elevating interconnected devices' capabilities by empowering them to learn and auto-adapt in real-time contexts. However, the proliferation of data produced by IoT sensors makes it difficult to send them to a centralized cloud for processing. This is where the allure of edge computing becomes captivating. Processing data closer to where it originates -at the edge- reduces latency, makes real-time decisions with less effort, and efficiently manages network congestion.

Integrating NN on edge devices for IoT enables more efficient and responsive systems, ushering in a new age of self-sustaining  $Edge\ AI$ . However, Deploying NN on resource-constrained edge devices presents a myriad of challenges: (i) The inherent complexity of neural network architectures, which requires significant computational and memory capabilities. (ii) The limited power budget of IoT devices makes the NN inference prone to rapid energy depletion, drastically reducing system utility. (iii) The need of ensuring harmony between NN and HW designs as they evolve at different rates. (iv) The lack of adaptability to the dynamic runtime environment and the intricacies of input data.

Addressing these challenges, this thesis aims to establish innovative methods that extend conventional NN design frameworks, notably Neural Architecture Search (NAS). By integrating HW and runtime contextual features, our methods aspire to enhance NN performances while abstracting the need for the human-inloop. Firstly, we incorporate HW properties into the NAS by tailoring the design of NN to clock frequency variations (DVFS) to minimize energy footprint. Secondly, we leverage dynamicity within NN from a design perspective, culminating in a comprehensive Hardware-aware Dynamic NAS with DVFS features. Thirdly, we explore the potential of Graph Neural Networks (GNN) at the edge by developing a novel HW-aware NAS with distributed computing features on heterogeneous MPSoC. Fourthly, we address the SW/HW co-optimization on heterogeneous MP-SoCs by proposing an innovative scheduling strategy that leverages NN adaptability and parallelism across computing units. Fifthly, we explore the prospect of ML4ML - Machine Learning for Machine Learning by introducing techniques to estimate NN performances on edge devices using neural architectural features and ML-based predictors. Finally, we develop an end-to-end self-adaptive evolutionary HW-aware NAS framework that progressively learns the importance of NN parameters to effectively guide the search toward Pareto optimal solutions.

Our methods can contribute to elaborating an end-to-end design framework for neural networks on edge hardware devices. They enable leveraging multiple optimization opportunities at both the software and hardware levels, thus improving the performance and efficiency of Edge AI systems.

**Keywords:** Hardware-aware Neural Architecture Search, Dynamic Inference, DVFS, Edge AI, Performance Prediction, HW/SW Co-optimization.

### RÉSUMÉ

Les réseaux de neurones (RN) sont devenus une force majeure dans le monde de la technologie. Inspirés par le cerveau humain, leur conception complexe leur permet d'apprendre des motifs, de prendre des décisions et même de prévoir des scénarios futurs avec une précision impressionnante. Les RN sont largement déployés dans les systèmes de l'Internet des Objets (IoT pour Internet of Things), renforçant davantage les capacités des dispositifs interconnectés en leur donnant la capacité d'apprendre et de s'auto-adapter dans un contexte temps réel. Cependant, la prolifération des données produites par les capteurs IoT rend difficile leur envoi vers un centre cloud pour le traitement. Par conséquent, le traitement des données plus près de leur origine, en edge, permet de prendre des décisions en temps réel, réduisant ainsi la congestion du réseau.

L'intégration des RN à l'edge dans les systèmes IoT permet d'obtenir des solutions plus efficaces et réactives, inaugurant ainsi une nouvelle ère de edge AI. Néanmoins, le déploiement des RN sur des plateformes matérielles à ressources présente une multitude de défis. (i) La complexité inhérente des architectures des RN, qui nécessitent d'importantes capacités de calcul et de stockage. (ii) Le budget énergétique limité caractérisant les dispositifs matériels sur edge qui ne permet pas de supporter des RN complexes, réduisant drastiquement la durée de fonctionnement du système. (iii) Le défi d'assurer une harmonie entre la conception des RN et celle des dispositifs matériels de l'edge. (iv) L'absence de l'adaptabilité à l'environnement d'exécution dynamique et aux complexités des données.

Pour pallier ces problèmes, cette thèse vise à établir des méthodes innovantes qui élargissent les cadres traditionnels de conception de RN (NAS pour Neural Architecture Search) en intégrant les caractéristiques contextuelles du matériel et de l'environnement d'exécution. Tout d'abord, nous intégrons les propriétés matérielles au NAS en adaptant les RN aux variations de la fréquence d'horloge. Deuxièmement, nous exploitons l'aspect dynamique au sein des RN d'un point de vue conceptuel, en introduisant un NAS dynamique. Troisièmement, nous explorons le potentiel des RN graphiques (GNN pour Graph Neural Network) en développant un NAS avec calcul distribué sur des multiprocesseurs hétérogènes sur puce (MPSoC pour Multi-Processors Système-on-Chip). Quatrièmement, nous abordons la co-optimisation software et matérielle sur les MPSoCs hétérogènes en proposant une stratégie d'ordonnancement innovante qui exploite l'adaptabilité et le parallélisme des RN. Cinquièmement, nous explorons la perspective de ML4ML en introduisant des techniques d'estimation des performances des RN sur les plateformes matérielles sur edge en utilisant des méthodes basés sur ML. Enfin, nous développons un framework NAS évolutif et auto-adaptatif de bout en bout qui apprend progressivement l'importance des paramètres architecturaux du RN pour guider efficacement le processus de recherche du NAS vers l'optimalité.

Nos méthodes aident à contribuer à la réalisation d'un framework de conception de bout en bout pour les RN sur les dispositifs matériels sur edge. Elles permettent ainsi de tirer avantage de plusieurs pistes d'optimisation au niveau logiciel et matériel, améliorant les performances et l'efficacité de l'Edge AI.

**Keywords :** Hardware-aware Neural Architecture Search, Inference Dynamique, DVFS, Edge AI, Prédiction de Performance, Co-optimization HW/SW.

### ACKNOWLEDGEMENT

Certainly, this journey has been full of ups, downs, and doubts more than anything else. With the help and support from everyone, I was able to cross the finish line. I'm so grateful for the things I've learned and the people I've met.

First and foremost, I offer my immense gratitude to my Ph.D. advisor, Prof. Smail Niar, for guiding me throughout my Ph.D. studies. His encouragement, patience, and support have been crucial in shaping both my research and my personal growth. I also thank my co-advisors, Dr. Hamza Ouarnoughi and Prof. El-Ghazali Talbi, for their invaluable guidance, support, and mentorship. I have gained numerous skills and knowledge from them that will forever shape my career.

I also offer my profound appreciation to my collaborators, Prof. Mohammad Abdullah Al-Faruque and Mohanad Odema, whose consistent support was pivotal in completing my Ph.D. journey. Their unwavering guidance has been instrumental in keeping me open to new ideas and maintaining a growth-oriented mindset.

I would like to thank my thesis committee members, Prof. Olivier Sentieys, Prof. Tulika Mitra, Prof. Clarisse Dhaenens, Dr. Nicolas Ventroux, and Prof. Abdessamad Ait El-Cadi, for their insightful comments and feedback.

I would like to express my sincere gratitude to my lab-mates, Hadjer, Imed, Farouk, Lotfi, Sofiane, Mufida, Affaf, Amine, Fabien, and Nourredine, and to my dearest friends, Yasmine, Katia, and Amal, whose support and friendship have been a source of comfort and motivation throughout my academic journey.

To my Mom, Dad, and Sisters, I've spent considerable time thinking about how to express my gratitude in a way that transcends the usual clichés, yet I find myself at a loss for words. My acknowledgment of you here isn't merely a formality, it's a heartfelt recognition. In the lottery of life, you are my winning ticket. Every good thing and every opportunity that has come my way began with you. From the depths of my heart, thank you a million times over for your endless love, support, and for bearing my absence during moments of happiness and sorrow.

Finally, in such a chaotic world, I often ask myself what can I do to be worthy of all these blessings? I can only hope that the knowledge and skills I've gathered will empower me to contribute towards solving some of our world's issues. May we all work together towards a more fair, happy, and beautiful world.

### LIST OF PUBLICATIONS

The following articles published in either international journals or conferences are directly discussed in the thesis dissertation:

1. [26] **Halima Bouzidi**, Hamza Ouarnoughi, El-Ghazali Talbi, Abdessamad Ait El Cadi, and Smail Niar. "Evolutionary-based Optimization of Hardware Configurations for DNN on Edge GPUs". The International Conference on Metaheuristics and Nature Inspired Computing, (META)" 2021.

**Location in the thesis :** Chapter 2

2. [27] Halima Bouzidi, Hamza Ouarnoughi, El-Ghazali Talbi, Abdessamad Ait El Cadi, and Smail Niar. "Evolutionary-Based Co-optimization of DNN and Hardware Configurations on Edge GPU". The International Conference on Optimization and Learning. (OLA) 2022. Book Chapter, Communications in Computer and Information Science, Springer Nature.

**Location in the thesis :** Chapter 2

3. [25] **Halima Bouzidi**, Hamza Ouarnoughi, Smail Niar, El-Ghazali Talbi, and Abdessamad Ait El Cadi. "Co-Optimization of DNN and Hardware Configurations on Edge GPUs," The Euromicro Conference on Digital System Design (DSD) 2022.

**Location in the thesis :** Chapter 2

- 4. [21] Halima Bouzidi, Mohanad Odema, Hamza Ouarnoughi, Mohammad Al Faruque, Smail Niar. "HADAS: Hardware-Aware Dynamic Neural Architecture Search for Edge Performance Scaling" The Design, Automation and Test in Europe Conference and Exhibition (DATE) 2023. Ranked among Top 30 papers and Nominated for the Best Paper Award. Location in the thesis: Chapter 3

- 5. [165] Mohanad Odema\*, **Halima Bouzidi\***, Hamza Ouarnoughi, Smail Niar, Mohammad Al Faruque. "MaGNAS: A Mapping-Aware Graph Neural Architecture Search Framework for Heterogeneous MPSoC Deployment". ACM Transactions on Embedded Computing Systems 22, 5s, Article 108 (October 2023), Special Issue: CASES Conference at ESWEEK 2023.

**Location in the thesis :** Chapter 4

6. [22] Halima Bouzidi, Mohanad Odema, Hamza Ouarnoughi, Smail Niar, Mohammad Al Faruque. 2023., "Map-and-Conquer: Energy-Efficient Mapping of Dynamic Neural Nets onto Heterogeneous MPSoCs," The ACM/IEEE Design Automation Conference (DAC), 2023. Paper Award from HiPEAC Location in the thesis: Chapter 5

- 7. [23] **Halima Bouzidi**, Hamza Ouarnoughi, Smail Niar, and Abdessamad Ait El Cadi. "Performance prediction for convolutional neural networks on edge GPUs". The ACM International Conference on Computing Frontiers (2021) **Location in the thesis:** Chapter 6

- 8. [24] **Halima Bouzidi**, Hamza Ouarnoughi, Smail Niar, and Abdessamad Ait El Cadi. "Performance Modeling of Computer Vision-based CNN on Edge GPUs". ACM Transactions on Embedded Computing Systems. 21, 5, Article 64 (September 2022)

Location in the thesis: Chapter 6

9. [20] **Halima Bouzidi**, Hamza Ouarnoughi, Abdessamad Ait El Cadi, El-Ghazali Talbi, and Smail Niar. "Sonata: Self-adaptive Evolution for Multi-objective Hardware-aware Neural Architecture Search". Submitted to IEEE Transactions on Evolutionary Computation, 2024.

**Location in the thesis :** Chapter 7

The following articles are not included or discussed in the thesis dissertation:

- 1. [72] Mohamed Ghebriout, **Halima Bouzidi**, Smail Niar, Hamza Ouarnoughi. "Harmonic-NAS: Hardware-Aware Multimodal Neural Architecture Search on Resource constrained Devices". The Asian Conference on Machine Learning (ACML). Proceedings of Machine Learning Research (PMLR), 2024

- 2. [13] Hadjer Benmeziane\*, **Halima Bouzidi\***, Hamza Ouarnoughi, Ozcan Ozturk, Smail Niar. "Treasure What You Have: Exploiting Similarity in Deep Neural Networks for Efficient Video Processing". Submitted to the IEEE Transactions on Computers. 2023"

- 3. [60] Eric Jenn, Floris Thiant, Theo Allouche, **Halima Bouzidi**, Ramon Conejo-Laguna, Omar Hlimi, Cyril Louis-Stanislas, Christophe Marabotto, Smail Niar, Serge Tembo-Mouafo and Philippe Thierion. "An Evaluation Bench for the Exploration of Machine Learning Deployment Solutions on Embedded Platforms". The European Congress on Real Time Embedded Systems (ERTS) 2024.

## Table des matières

| ABST | TRACT (RÉSUMÉ)                                                | j    |

|------|---------------------------------------------------------------|------|

| ACK  | NOWLEDGEMENT                                                  | iii  |

|      | LIST OF PUBLICATIONS                                          | iv   |

| LIST | OF FIGURES                                                    | xiii |

| LIST | OF TABLES                                                     | xvi  |

| LIST | OF TERMS AND ABBREVIATIONS                                    | viii |

| 1    | Introduction                                                  | 1    |

| 1.1  | The Rise of Edge AI                                           | 1    |

| 1.2  | The Emergence of Automated Neural Architecture Design         | 2    |

| 1.3  | Chasing Efficiency in the Era of Edge AI                      | 3    |

| 1.4  | Edge AI Optimization Techniques                               | 4    |

|      | 1.4.1 Software-level Optimizations                            | 4    |

|      | 1.4.2 Hardware-level Optimizations                            | 5    |

| 1.5  | Winning the 'Performance-Efficiency' Lottery Ticket           | 7    |

| 1.6  | Thesis Structure and Contributions                            | 8    |

| 2    | DVFS-NAS : Dynamic Clock Frequency Scaling for Hardware-aware |      |

|      | Neural Architecture Search on Edge GPUs                       | 11   |

| 2.1  | Introduction                                                  | 11   |

| 2.2  | Related Works                                                 | 12   |

| 2.3  | Motivational Example                                          | 15   |

| 2.4  | Problem Statement                                             | 17   |

| 2.5  | Proposed Approach                                             | 18   |

|      | 2.5.1 Joint Search Space                                      | 19   |

|      | 2.5.2 Evolutionary Search Strategy                            | 20   |

|      | 2.5.3 Fitness Evaluation Strategy                             | 21   |

| 2.6 | Evalu  | ation Methodology                                                                                                                                                          | 22        |

|-----|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

|     | 2.6.1  | Experimental Setup                                                                                                                                                         | 22        |

|     | 2.6.2  | Experimental Results                                                                                                                                                       | 23        |

| 2.7 | Discu  | ssion and Key Insights                                                                                                                                                     | 28        |

| 2.8 | Sumn   | nary                                                                                                                                                                       | 29        |

| 3   | HAD    | $\overline{\mathbf{AS}}: \underline{\mathbf{H}}$ ardware- $\underline{\mathbf{A}}$ ware $\underline{\mathbf{D}}$ ynamic Neural $\underline{\mathbf{A}}$ rchitecture Search |           |

|     | for E  | $\operatorname{dge}$ Performance $\operatorname{\underline{S}}$ caling                                                                                                     | <b>30</b> |

| 3.1 | Introd | luction                                                                                                                                                                    | 30        |

| 3.2 | Relate | ed works                                                                                                                                                                   | 31        |

|     | 3.2.1  | Dynamic Early Exit and NAS                                                                                                                                                 | 31        |

|     | 3.2.2  | Dynamic Hardware Reconfiguration                                                                                                                                           | 32        |

| 3.3 | Motiv  | vational Example                                                                                                                                                           | 33        |

| 3.4 | Novel  | Scientific Contributions                                                                                                                                                   | 35        |

| 3.5 | Probl  | em Statement                                                                                                                                                               | 36        |

| 3.6 | Propo  | osed Approach                                                                                                                                                              | 37        |

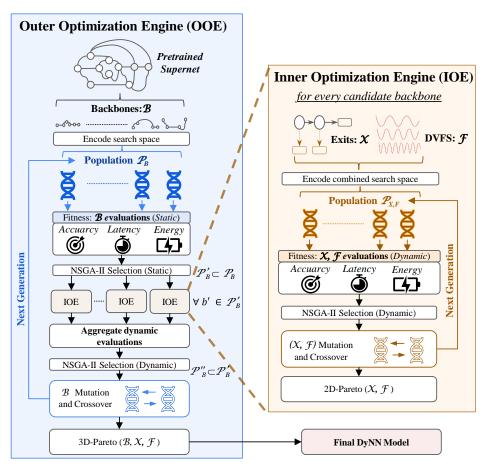

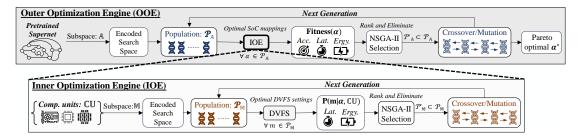

|     | 3.6.1  | Outer Optimization Engine (OOE)                                                                                                                                            | 37        |

|     | 3.6.2  | Inner Optimization Engine (IOE)                                                                                                                                            | 40        |

|     | 3.6.3  | Runtime Controller                                                                                                                                                         | 43        |

| 3.7 | Evalu  | ation Methodology                                                                                                                                                          | 44        |

|     | 3.7.1  | Experimental Setup                                                                                                                                                         | 44        |

|     | 3.7.2  | Co-optimization Results                                                                                                                                                    | 45        |

|     | 3.7.3  | Dissimilarity Ablation Study                                                                                                                                               | 48        |

| 3.8 | Sumn   | nary                                                                                                                                                                       | 48        |

| 4   | MaG    | NAS: A <u>Mapping-aware Graph Neural Architecture Search</u>                                                                                                               |           |

|     | Frame  | ework for Heterogeneous MPSoC Deployment                                                                                                                                   | <b>50</b> |

| 4.1 | Introd | luction                                                                                                                                                                    | 50        |

| 4.2 | Relate | ed Works                                                                                                                                                                   | 52        |

|     | 4.2.1  | GNNs for Computer Vision                                                                                                                                                   | 52        |

|     | 4.2.2  | Hardware Acceleration for GNNs                                                                                                                                             | 52        |

|     | 4.2.3  | Distributed Computing of GNNs                                                                                                                                              | 53        |

|     | 4.2.4  | Graph Neural Architecture Search                                                                                                                                           | 53        |

| 4.3  | Motiv  | ational Example                                              | 54 |

|------|--------|--------------------------------------------------------------|----|

| 4.4  | Novel  | Scientific Contributions                                     | 55 |

| 4.5  | Vision | Graph Neural Network (ViG)                                   | 56 |

| 4.6  | Proble | em Statement                                                 | 57 |

|      | 4.6.1  | System Model for Mapping GNNs onto Heterogeneous MPSoCs      | 57 |

|      | 4.6.2  | Nested Search Formulation                                    | 59 |

| 4.7  | Propo  | sed Approach                                                 | 60 |

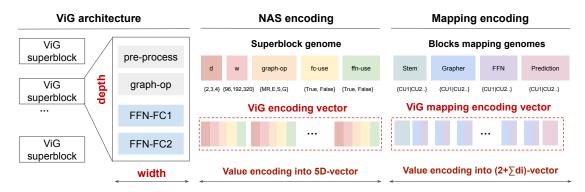

|      | 4.7.1  | Supernet Construction and Training                           | 60 |

|      | 4.7.2  | Nested Evolutionary Search : Outer Optimization Engine (OOE) | 63 |

|      | 4.7.3  | Nested Evolutionary Search : Inner Optimization Engine (IOE) | 64 |

| 4.8  | Exper  | iments and Evaluation                                        | 66 |

|      | 4.8.1  | Experimental Setup                                           | 66 |

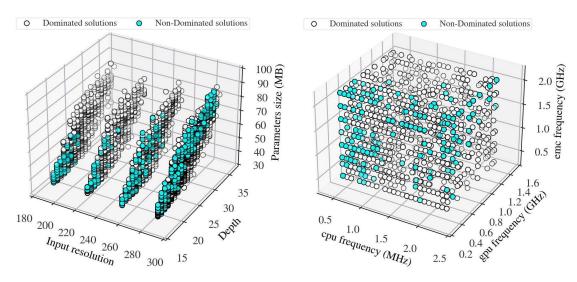

|      | 4.8.2  | OOE Results : GNN Architecture Optimization                  | 69 |

|      | 4.8.3  | IOE Results : Hardware Mapping Optimization                  | 70 |

|      | 4.8.4  | Analysis of Search and Pareto Optimal Models                 | 71 |

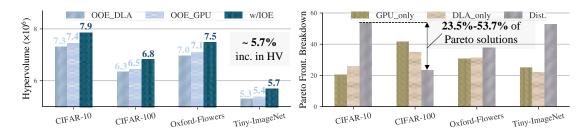

|      | 4.8.5  | Hypervolume and Pareto Composition Analysis                  | 72 |

|      | 4.8.6  | Analysis of GNN Workload Distribution                        | 72 |

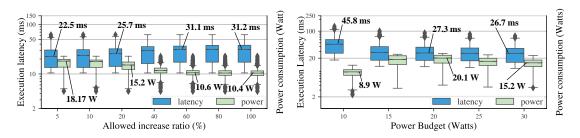

|      | 4.8.7  | Constraint-aware Optimization                                | 73 |

|      | 4.8.8  | Ablation study on the impact of DVFS                         | 75 |

|      | 4.8.9  | Generality and Scalability                                   | 76 |

| 4.9  | Discus | ssion and Key Insights                                       | 78 |

| 4.10 | Summ   | nary                                                         | 79 |

| 5    | Мар-а  | and-Conquer: Energy-Efficient Mapping of Dynamic Neural      |    |

|      | Nets   | onto Heterogeneous MPSoCs                                    | 80 |

| 5.1  | Introd | luction                                                      | 80 |

| 5.2  | Relate | ed Works                                                     | 82 |

|      | 5.2.1  | Dynamic Neural Networks                                      | 82 |

|      | 5.2.2  | Computation Mapping on MPSoCs                                | 82 |

| 5.3  | Motiv  | ational Example                                              | 83 |

| 5.4  | Novel  | Scientific Contributions                                     | 84 |

| 5.5  | Proble | em Statement                                                 | 84 |

|      | 5.5.1  | System Model for Mapping DyNN onto Heterogeneous MPSoCs      | 84 |

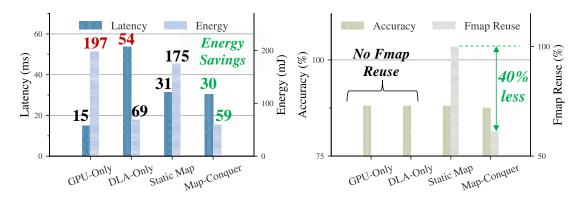

|     | 5.5.2  | Dynamic Transformation of Neural Networks               | 84  |

|-----|--------|---------------------------------------------------------|-----|

|     | 5.5.3  | Distributed Performance Modeling for Dynamic Inference  | 86  |

|     | 5.5.4  | Problem Formulation                                     | 88  |

| 5.6 | Propo  | osed Approach                                           | 89  |

|     | 5.6.1  | Search Space $(X)$                                      | 89  |

|     | 5.6.2  | Performance Objectives $(\mathcal{P})$                  | 90  |

|     | 5.6.3  | Evolutionary Search Algorithm                           | 90  |

|     | 5.6.4  | Channel Partitioning, Reordering, and Arrangement       | 90  |

| 5.7 | Expe   | riments and Evaluation                                  | 91  |

|     | 5.7.1  | Experimental Setup                                      | 91  |

|     | 5.7.2  | Search Efficiency Analysis                              | 91  |

|     | 5.7.3  | Pareto Optimal Models Analysis                          | 92  |

|     | 5.7.4  | Generalization to Other Neural Architectures            | 94  |

| 5.8 | Discu  | ssion and Key Insights                                  | 94  |

| 5.9 | Sumn   | nary                                                    | 95  |

| 6   | Perfo  | rmances Modeling of Computer Vision-based Convolutional |     |

|     | Neura  | al Networks on Edge GPUs                                | 96  |

| 6.1 | Intro  | duction                                                 | 96  |

| 6.2 | Relate | ed Works                                                | 97  |

|     | 6.2.1  | Benchmarking and Performances Analysis                  | 97  |

|     | 6.2.2  | Execution Time Modeling                                 | 97  |

|     | 6.2.3  | Power Consumption Modeling                              | 98  |

|     | 6.2.4  | Memory Usage Modeling                                   | 98  |

| 6.3 | Motiv  | vational Example                                        | 99  |

| 6.4 | Probl  | em Statement                                            | .00 |

| 6.5 | Propo  | osed Approach                                           | .00 |

|     | 6.5.1  | CNN Characterization                                    | .01 |

|     | 6.5.2  | Input Features Selection                                | .05 |

|     | 6.5.3  | Prediction Algorithms                                   | .06 |

| 6.6 | Evalu  | ation Methodology                                       | .06 |

|     | 6.6.1  | CNN Benchmarking                                        | .06 |

|     | 6.6.2  | Data Collection                                         | 06  |

|     | 6.6.3  | Prediction Models Hyperparameters Tuning                                                                               | 108         |

|-----|--------|------------------------------------------------------------------------------------------------------------------------|-------------|

|     | 6.6.4  | Prediction Models Design, Training, and Evaluation                                                                     | 109         |

|     | 6.6.5  | Experimental Setup                                                                                                     | 111         |

|     | 6.6.6  | Experimental Results                                                                                                   | 111         |

| 6.7 | Discu  | ssion and Key Insights                                                                                                 | 117         |

| 6.8 | Sumn   | nary                                                                                                                   | 119         |

| 7   | SON    | $\overline{	ext{ATA}}$ : $\underline{	ext{S}}$ elf-adaptive $\overline{	ext{Evo}}$ lution for Multi-objective Hardware | -           |

|     | aware  | e <u>N</u> eural <u>A</u> rchitec <u>t</u> ure Se <u>a</u> rch                                                         | <b>12</b> 0 |

| 7.1 | Intro  | duction                                                                                                                | 120         |

| 7.2 | Relate | ed Works                                                                                                               | 122         |

|     | 7.2.1  | Evolutionary Neural Architecture Search (ENAS)                                                                         | 122         |

|     | 7.2.2  | Surrogate-assisted Multi-objective ENAS (SaMo-ENAS)                                                                    | 122         |

| 7.3 | Novel  | Scientific Contributions                                                                                               | 123         |

| 7.4 | Desig  | n Parameters Importance Estimation for NAS                                                                             | 123         |

| 7.5 | Probl  | em Statement                                                                                                           | 124         |

|     | 7.5.1  | The Main Problem : HW-aware NAS                                                                                        | 124         |

|     | 7.5.2  | The Sub-Problem : Design Parameter Importance Learning                                                                 | 125         |

| 7.6 | Propo  | osed Approach                                                                                                          | 127         |

|     | 7.6.1  | Search Space Encoding and Initialization                                                                               | 128         |

|     | 7.6.2  | Self-adaptive Mutation and Crossover                                                                                   | 129         |

|     | 7.6.3  | Surrogate-assisted Fitness Evaluation                                                                                  | 130         |

| 7.7 | Expe   | riments and Evaluation                                                                                                 | 131         |

|     | 7.7.1  | Experimental Setup                                                                                                     | 131         |

|     | 7.7.2  | Surrogate Models Analysis                                                                                              | 133         |

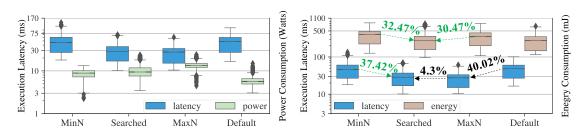

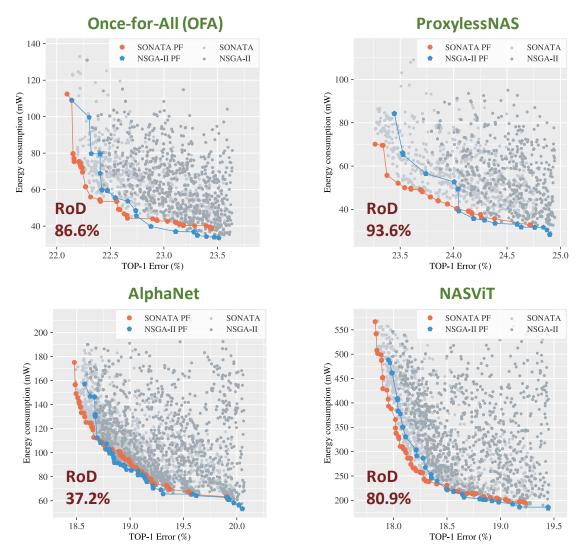

|     | 7.7.3  | SONATA Optimization Efficiency                                                                                         | 135         |

| 7.8 | Sumn   | nary                                                                                                                   | 137         |

| 8   | Conc   | lusions, Outlooks, and Future Directions                                                                               | 139         |

| 8.1 | Sumn   | nary of the Thesis                                                                                                     | 139         |

| 8.2 | Outlo  | ook and Future Directions                                                                                              | 141         |

|     | 8.2.1  | Enrich the Search Space of NAS                                                                                         | 142         |

|     | 8.2.2  | Investigate Novel Hardware Technologies                                                                                | 142         |

| REF   | FERENCES                                        | 143 |

|-------|-------------------------------------------------|-----|

| 8.2.5 | Generalize the HW-aware NAS to Multimodality AI | 143 |

| 8.2.4 | Towards Self-explainable HW-aware NAS           | 143 |

| 8.2.3 | Incorporate Advanced Dynamic Inference Strategy | 142 |

# Table des figures

| 1.1  | Comparison between Cloud and edge computing paradigms                            | 1  |

|------|----------------------------------------------------------------------------------|----|

| 1.2  | The evolution stages of Neural Network design techniques                         | 3  |

| 1.3  | The growth rate of AI workloads in different application domains $$ .            | 4  |

| 1.4  | Artificial Intelligence in the Hardware Market                                   | 5  |

| 1.5  | Thesis structure and dependencies between chapters                               | 8  |

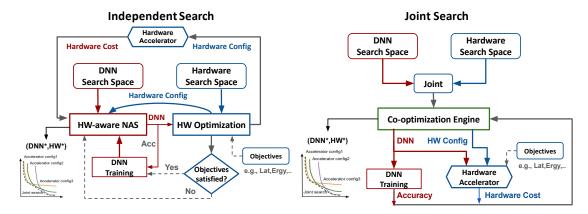

| 2.1  | Independent Vs. Joint Search strategies                                          | 13 |

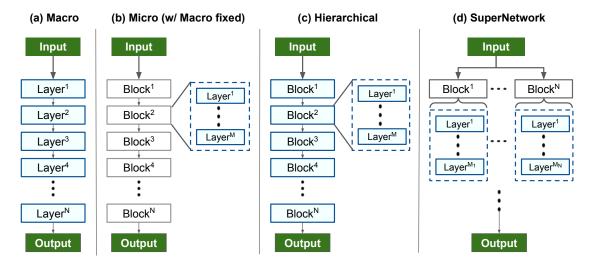

| 2.2  | Variants of Search Spaces in NAS                                                 | 14 |

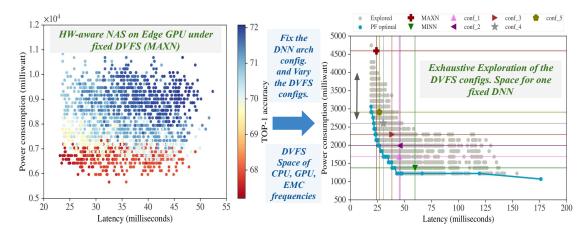

| 2.3  | Typical HW-aware Vs. Co-optimization of DNN and DVFS                             | 15 |

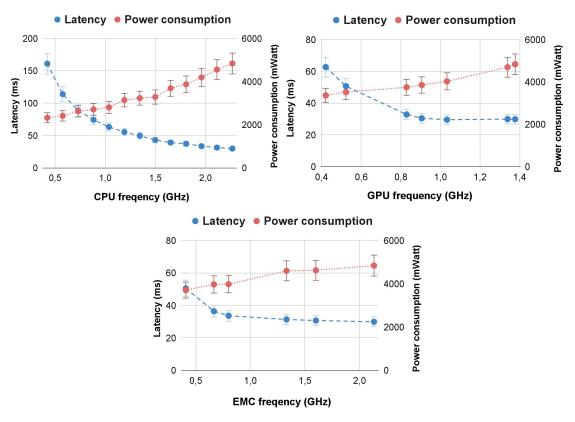

| 2.4  | Impact of clock frequency variations on DNN performances                         | 16 |

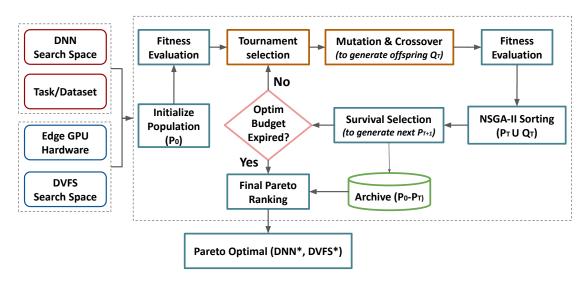

| 2.5  | Overview on our proposed DVFS-NAS co-optimization approach. $$ .                 | 18 |

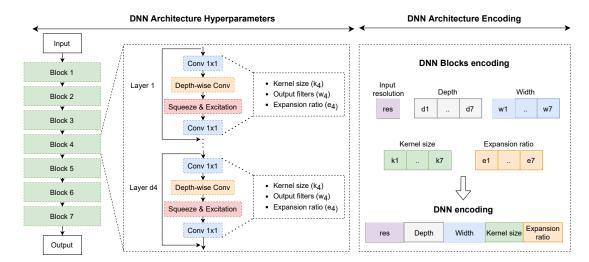

| 2.6  | Details on the DNN search space encoding                                         | 20 |

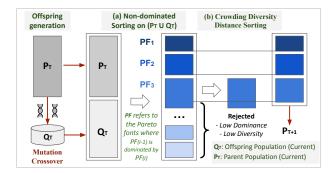

| 2.7  | NSGA-II two-step sorting and parameters                                          | 21 |

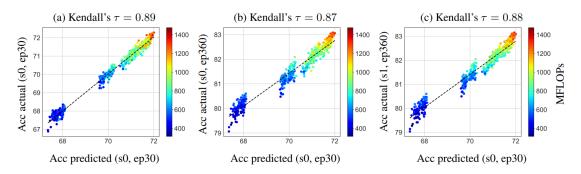

| 2.8  | Rank correlation between estimated and actual accuracy                           | 22 |

| 2.9  | Co-exploration results Vs. Exploration under fixed ${\tt DVFS}$ policy           | 23 |

| 2.10 | An Overview on the explored configurations of DNN and ${\tt DVFS}$ settings      | 24 |

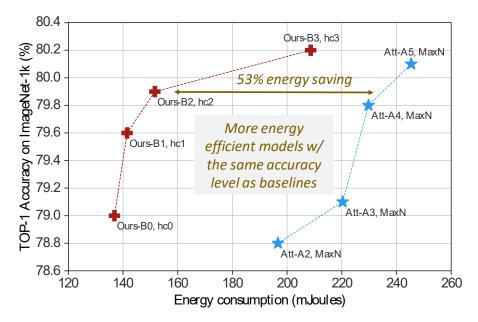

| 2.11 | Our DVFS-NAS Vs. the baseline from AttentiveNAS                                  | 25 |

| 2.12 | Workflow of generating an optimized TensorRT inference engine $$                 | 27 |

| 2.13 | Results of TensorRT optimization under optimal ${\tt DVFS}$ settings             | 27 |

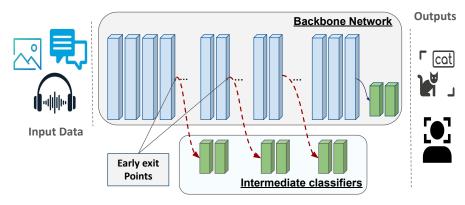

| 3.1  | Dynamic Inference with early-exit                                                | 30 |

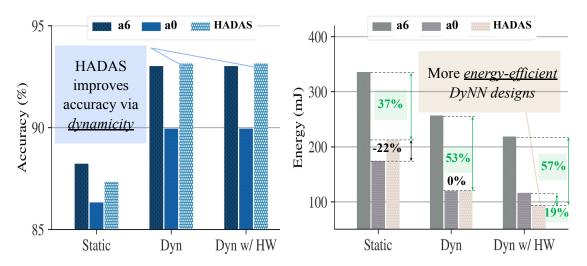

| 3.2  | Comparison between HADAS and baselines from Attentive<br>NAS $\left[ 220\right]$ | 34 |

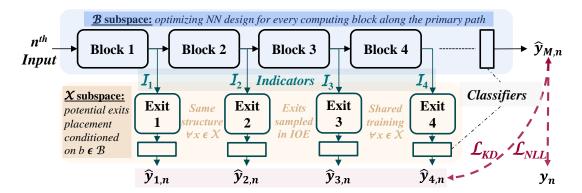

| 3.3  | HADAS co-optimization framework                                                  | 38 |

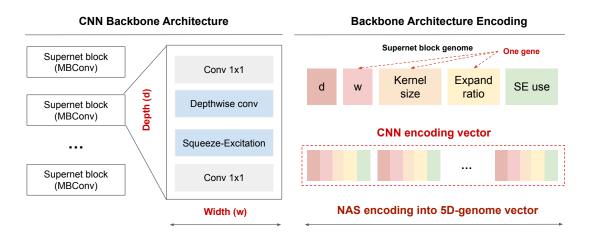

| 3.4  | Backbone Neural Network Encoding                                                 | 39 |

| 3.5  | The combined ${\mathcal B}$ and ${\mathcal X}$ search spaces                     | 41 |

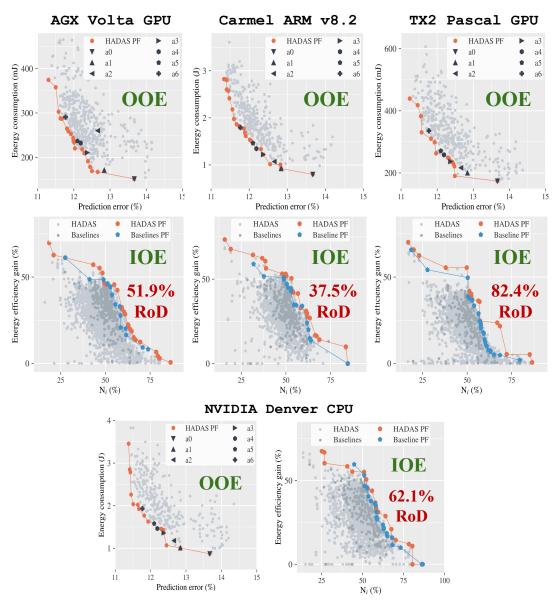

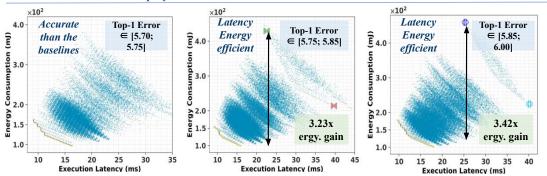

| 3.6  | Results from the OOE and IOE optimization engines of HADAS $$ . $$ .             | 45 |

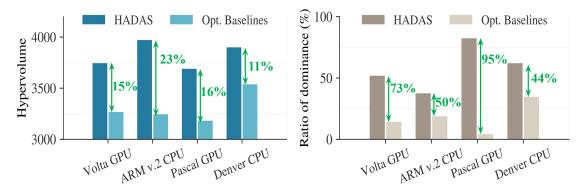

| 3.7  | Comparing search efficacy for HADAS and the optimized baselines .                | 47 |

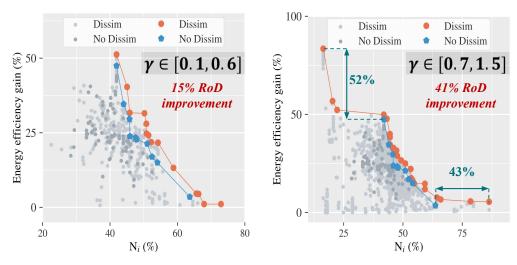

| 3.8  | Ablation study on the dissimilarity regularization of the IOE of                                    |     |

|------|-----------------------------------------------------------------------------------------------------|-----|

|      | HADAS                                                                                               | 48  |

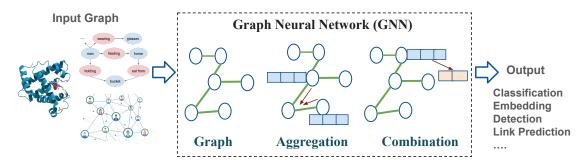

| 4.1  | An Overview on Graph Neural Netwworks (GNN)                                                         | 50  |

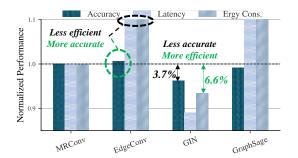

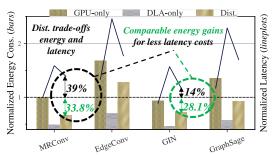

| 4.2  | Comparison between ViG model variants and deployement options .                                     | 55  |

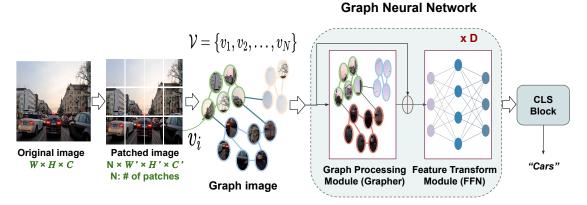

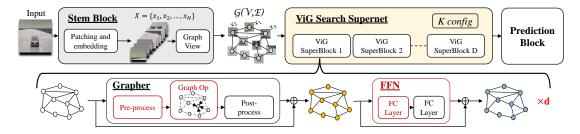

| 4.3  | An overview of the Vision Graph Neural Network                                                      | 56  |

| 4.4  | The ViG supernet implementation for MaGNAS co-search framework                                      | 60  |

| 4.5  | MaGNAS two-tier evolutionary search framework                                                       | 62  |

| 4.6  | Dynamic encoding for GNN architectural-mapping specifications                                       | 67  |

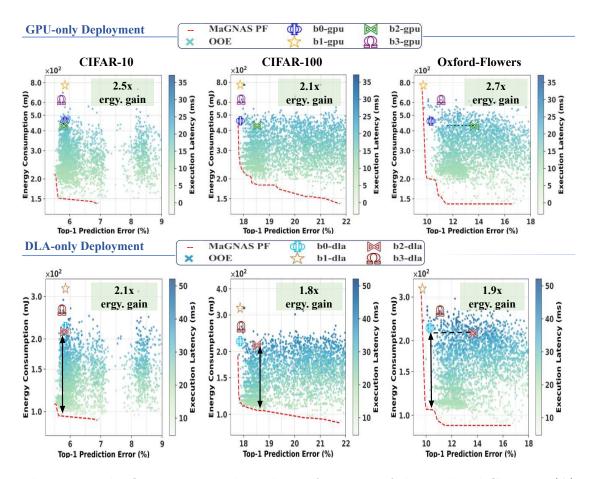

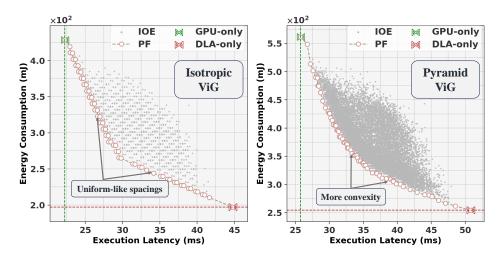

| 4.7  | Results from the OOE and IOE optimization engines of MaGNAS $.$                                     | 69  |

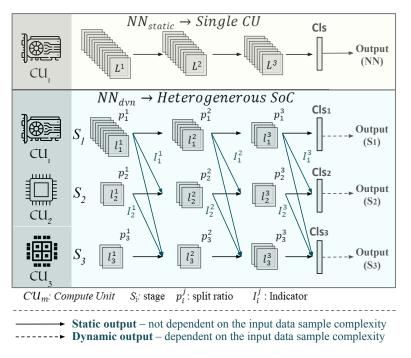

| 4.8  | Results from the OOE and IOE optimization engined of MaGNAS .                                       | 70  |

| 4.9  | Hypervolume results analysis and comparison                                                         | 72  |

| 4.10 | Results of the two constrained optimization                                                         | 73  |

| 4.11 | Ablation on the impact of including ${\tt DVFS}$ within the IOE                                     | 75  |

| 4.12 | Results of the IOE on Isotropic and Pyramid GNN models $\ \ldots \ \ldots$                          | 77  |

| 4.13 | Results of the $\mathit{block\text{-}wise}$ and $\mathit{layer\text{-}wise}$ IOE on MAESTRO [116] . | 78  |

| 5.1  | Comparison of mapping options for $Visformer$ [44] on AGX MPSoC                                     | 83  |

| 5.2  | The transformation of $NN_{static}$ into $NN_{dyn}$ and mapping on MPSoC                            | 85  |

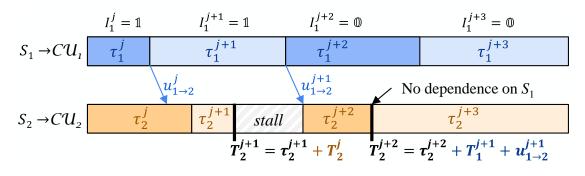

| 5.3  | Concurrent execution of $S_2$ and $S_1$ considering timing dependencies                             | 87  |

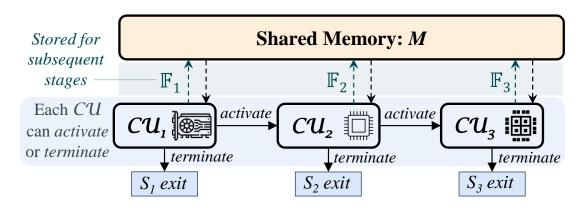

| 5.4  | Illustration of data movement and feature storage on the MPSoC $$ .                                 | 88  |

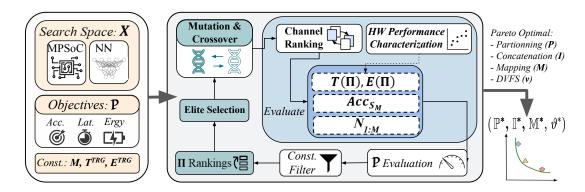

| 5.5  | Overview of the workflow of our proposed optimization framework                                     | 89  |

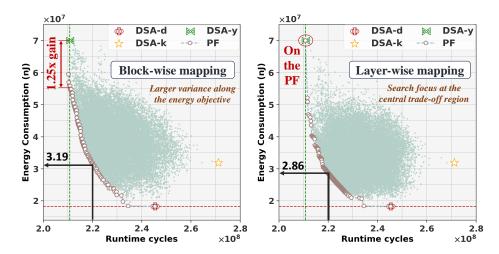

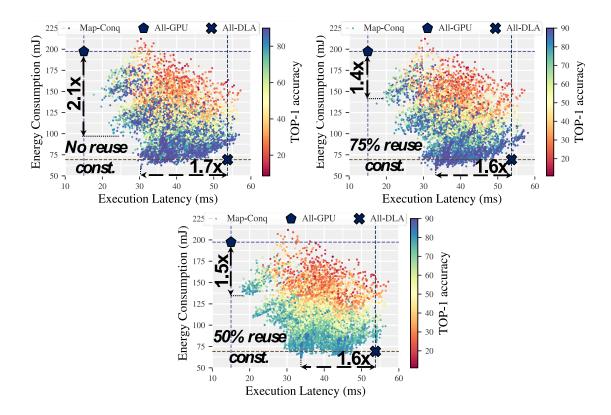

| 5.6  | Results of three search strategies of Map-and-Conquer                                               | 92  |

| 5.7  | Comparison between Pareto optimal $NN_{dyn}$ , mappings, and baselines                              | 93  |

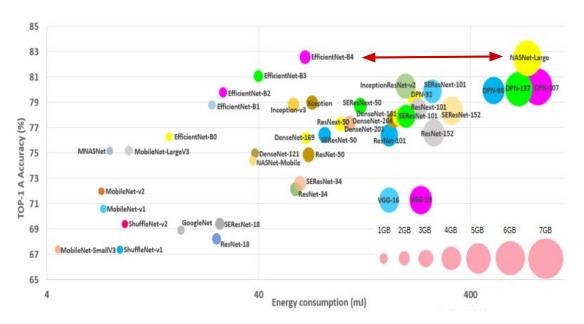

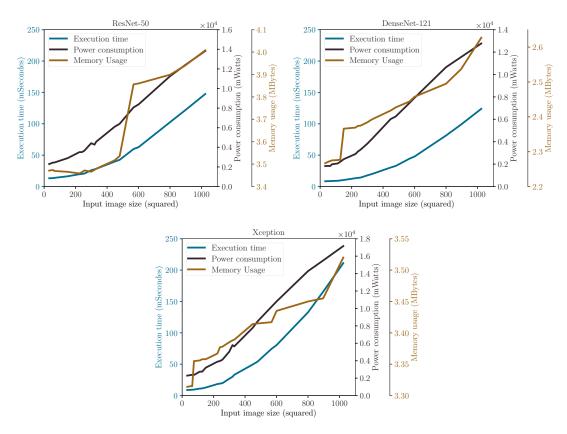

| 6.1  | Interplay between CNN accuracy and hardware efficiency                                              | 99  |

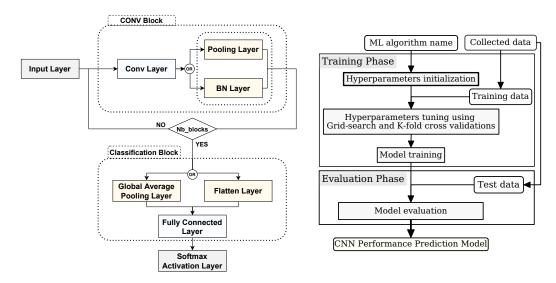

| 6.2  | Modeling methodology for CNNs performances prediction models 1                                      | .00 |

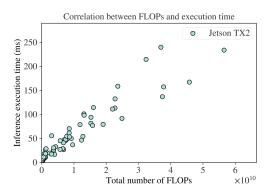

| 6.3  | Correlation between FLOPs and CNN execution time on edge GPUs1                                      | .02 |

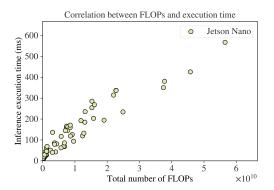

| 6.4  | Impact of FLOPs and CNN model size on the performances $\dots$ 1                                    | .03 |

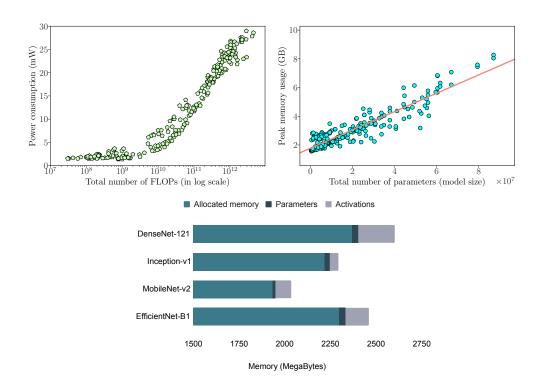

| 6.5  | Impact of varying the input size on the end-to-end performances 1                                   | .04 |

| 6.6  | The forward stepwise selection of CNN features for modeling $1$                                     | .05 |

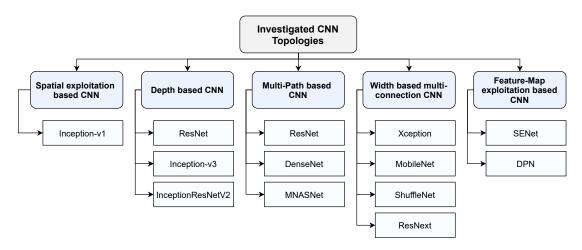

| 6.7  | Taxonomy of the used CNN for the Benchmarking step                                                  | .07 |

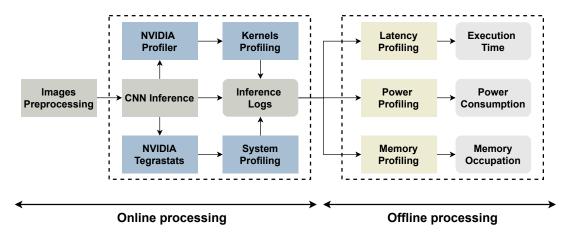

| 6.8  | The workflow of the CNN inference profiling on the edge GPU $1$                                     | .08 |

| 6.9  | CNN baseline for NCA                                                                                | 10  |

| 6.10 | Prediction model design.                                                                            | 10  |

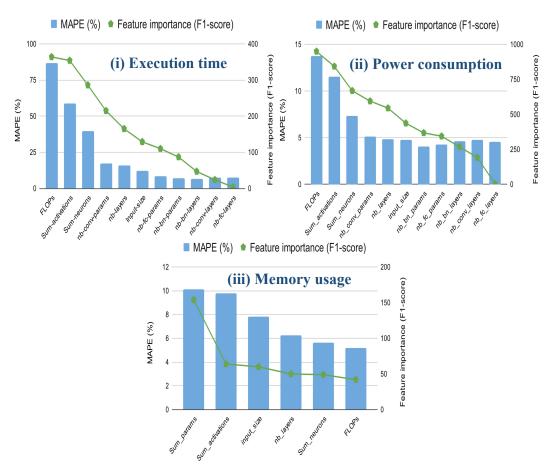

| 6.11 | Mean Absolute Percentage Error (MAPE) for execution time $112$                    |

|------|-----------------------------------------------------------------------------------|

| 6.12 | Mean Absolute Percentage Error (MAPE) for power consumption $$ . $114$            |

| 6.13 | Mean Absolute Percentage Error (MAPE) for memory usage 116 $$                     |

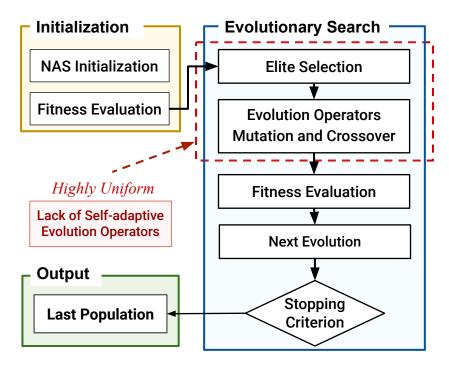

| 7.1  | The flowchart of a typical Evolutionary NAS (ENAS)                                |

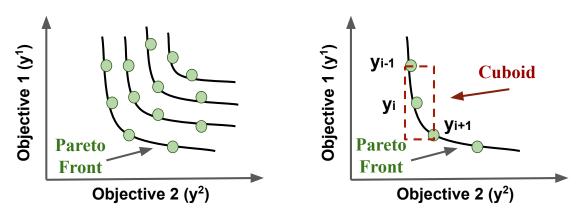

| 7.2  | Calculation of the crowding distance                                              |

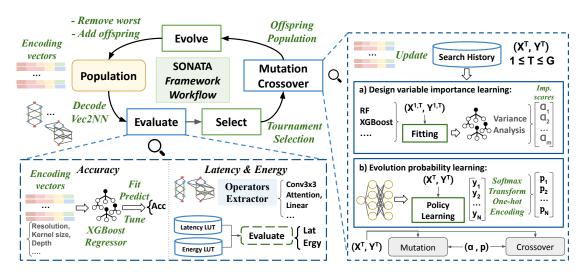

| 7.3  | ${\tt SONATA}$ : self-adaptive and data-driven evolutionary search process. $127$ |

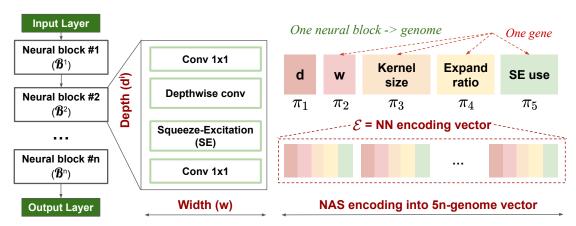

| 7.4  | SONATA Neural network (NN) encoding scheme                                        |

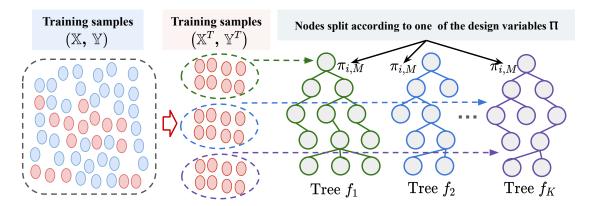

| 7.5  | Nodes split mechanism in tree-based model (XGBoost) 130                           |

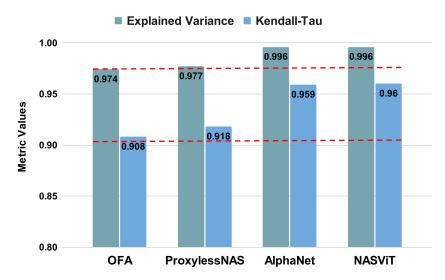

| 7.6  | Performance of the surrogate models for accuracy in ${\tt SONATA}$ 133            |

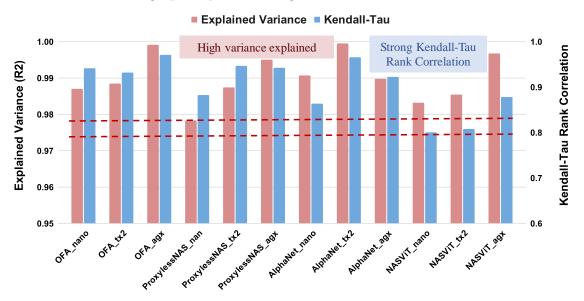

| 7.7  | Performance of the surrogate models used to learn the importance                  |

|      | of NN design parameters                                                           |

| 7.8  | Comparing the optimization results of SONATA Vs. NSGA-II 136                      |

## Liste des tableaux

| 2.1 | Comparison between related works on the DNN-HW co-optimization.          | 13 |

|-----|--------------------------------------------------------------------------|----|

| 2.2 | The joint search space of DNN and hardware parameters                    | 19 |

| 2.3 | Detailed overview on the DNN architecture search space. Each row         |    |

|     | denotes the search space of a fixed block of the DNN macro-architecture. | 20 |

| 2.4 | Detailed performances of our DVFS-NAS Vs. the baseline from At-          |    |

|     | tentiveNAS                                                               | 25 |

| 2.5 | Fine-tuning results to CIFAR-10 and CIFAR-100                            | 26 |

| 3.1 | Comparison between Related-works and ours                                | 33 |

| 3.2 | Details on HADAS joint search spaces in our experiments                  | 44 |

| 3.3 | DyNNs Comparison on the TX2 Pascal GPU                                   | 48 |

| 4.1 | Comparison between related Graph NAS works and ours                      | 53 |

| 4.2 | Joint Search space of GNN architectures, Mapping, and DVFS               | 66 |

| 4.3 | Performances and configurations of Pareto optimal GNNs and map-          |    |

|     | pings                                                                    | 71 |

| 4.4 | Details and comparison of the GNN workload Assignment                    | 73 |

| 4.5 | GNN Workload distribution under different latency constraints            | 74 |

| 4.6 | GNN Workload distribution under different power budgets                  | 75 |

| 5.1 | Comparison between Related-works and ours                                | 82 |

| 5.2 | Comparison between Map-and-Conquer and baselines                         | 93 |

| 6.1 | Summary of notations                                                     | 00 |

| 6.2 | FLOPs breakdown                                                          | 02 |

| 6.3 | Details of the CNN benchmarks used in the experiments                    | 07 |

| 6.4 | Search space of the Hyperparameters per ML method                        | 09 |

| 6.5 | CNN features                                                             | 11 |

|     |                                                                          |    |

| 6.6 | Hardware setup                                                           | 11 |

| 6.8  | Rank correlation coefficients analysis                            |

|------|-------------------------------------------------------------------|

| 6.9  | Power consumption prediction models analysis                      |

| 6.10 | Rank correlation coefficients analysis                            |

| 6.11 | Memory usage prediction models analysis                           |

| 6.12 | Rank correlation coefficients analysis                            |

| 6.13 | SOTA models Vs. our models for execution time prediction 118 $$   |

| 6.14 | SOTA models Vs. our models for power consumption prediction $118$ |

| 6.15 | SOTA models Vs. our models for memory usage prediction 118        |

| 7.1  | Details on OFA [30] and ProxylessNAS [33] search spaces 132       |

| 7.2  | Details on the AlphaNet [219] search space                        |

| 7.3  | Details on the NASViT [75] search space                           |

| 7.4  | Comparison between the optimization efficiency (i.e., convergence |

|      | and diversity) of the baseline static ENAS NSGA-II [52] and our   |

|      | self-adaptive SONATA                                              |

### Chapitre 1

### Introduction

### 1.1 The Rise of Edge AI

Edge AI refers to the fusion of Artificial Intelligence (AI) with Edge computing, heralding a new computing paradigm where AI computations can operate optimally closer to data sources – at the edge of the network system [197]. AI models, notably Neural Networks (NNs), are characterized by their deep layers and interconnected nodes that hold many neurons and parameters. Recently, NNs have demonstrated their aptitude in various domains, from image recognition and language processing to healthcare and chatbot technologies, marking their significant footprint in modern digital landscapes [185]. Given their intricate topology, NNs are computationally and memory demanding, necessitating powerful centralized Cloud servers to handle their processing on the massive amount of data generated by edge sensors. Nevertheless, due to the surge in connected users and inconsistent network bandwidth, Cloud servers struggle to guarantee prompt processing results for end-users within a tight latency delay.

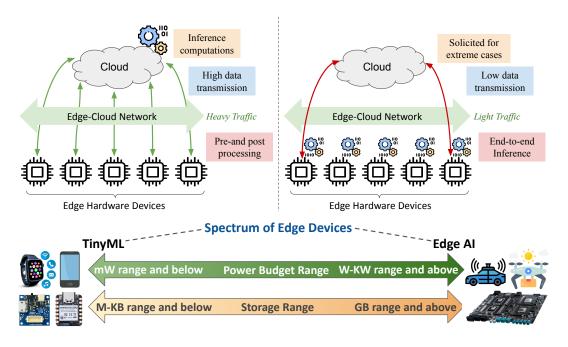

**Figure 1.1 Top**: Comparison between Cloud and edge computing paradigms: By delegating computations to edge devices, low data transmission and network congestion can be achieved. **Bottom**: Spectrum of edge computing devices

The advent of edge computing systems has led to a shift in the *send-to-cloud* archetype, prioritizing processing data near sensors to minimize latency and save network bandwidth. Integrating NNs with edge computing gave rise to Edge AI, in which NN models are further optimized, redesigned, or tuned to enhance their processing on less-powerful edge devices (e.g., smartphones). As shown in Figure 1.1, the benefits of Edge AI compared to Cloud computing are threefold: (i) reduced latency and energy consumption due to local processing. (ii) preserved privacy and minimal security risks by maintaining data locally. (iii) efficient network bandwidth management by saving it for extremely urgent cases [200].

There has been a swift and significant rise in the development of AI-specific chips, dedicated hardware accelerators, and software frameworks specifically tailored to enhance AI-on-device performances [207]. This confluence underscores the burgeoning significance of Edge AI. As we continue to witness the blossoming of applications and the introduction of advanced data processing techniques, like multimodal approaches, the melding of edge computing and neural networks is set to be crucial. Such an integration seeks to unlock the immense potential of data, paving the way for more pervasive real-time and intelligent decision-making that is more ubiquitous than ever.

### 1.2 The Emergence of Automated Neural Architecture Design

In recent years, the evolution of neural network design has witnessed many phases, from handcrafted to automated approaches. The newly emergent concept of Neural Architecture Search (NAS) has been a game changer, lessening the need for human expertise and aiming to fully automate NN's design process [270]. The paradigm of NAS lies in navigating a predefined search space encompassing the possibilities of NN architectures through a vast search process to identify the options that provide the best trade-off between prediction accuracy and computational efficiency [59]. Earlier NAS approaches [86] focused on optimizing the accuracy under efficiency proxy budgets, such as the number of Multiply-Accumulate operations (MAC) as a proxy for computational complexity or the number of learnable parameters as a proxy for model size. However, the focus has shifted with the emergence of Edge AI and the limitations of proxy metrics in capturing hardwarerelated aspects [23]. Instead of solely prioritizing accuracy, researchers have started pursuing a balance between accuracy and hardware efficiency. Subsequently, this gave rise to the extended concept of Hardware-aware NAS (HW-aware NAS) [33] in which neural networks are synergistically designed to optimize hardware-related metrics such as latency, energy consumption, and memory usage.

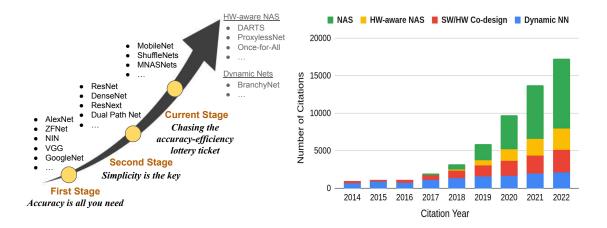

The left of Figure 1.2 illustrates neural network design techniques' evolution stages. Given the broad scope of NNs, we focus our analysis on the specific Convolutional Neural Networks (CNN) case, as they have shown impressive results in many application domains, including computer vision and natural language processing. The First stage marked the emergence of the earliest handcrafted CNNs (e.g., AlexNet [114], VGG [199], and GoogleNet [209]), characterized by large amounts of weights to maximize learning capacity, as accuracy was the only matter. In Second stage, design simplifications have been introduced to make CNN less heavy and mitigate the problem of vanishing gradient [84] due to many learnable weights. This was achieved by including skip and dense connections (e.g., ResNet [84] and Den-

**Figure 1.2 Left**: The evolution stages of NN design landscape: from *static* and *handcrafted* to *dynamic* and *auto-designed*. **Right**: Statistics on the number of publications in NAS, HW-aware NAS, SW/HW Co-design, and Dynamic NN over the last years [1]

.

seNet [94]). The Current stage focuses on chasing the accuracy-efficiency balance that cannot be readily achieved by means of handcrafted methods. Hence, more advanced design techniques have been proposed by incorporating NAS methods that have led to the discovery of NN designs tailored to edge devices, enabling efficient inference without comprising accuracy. Notably, models such as MNAS-Net [213], MobileNet [90], and EfficientNet [29] are the results of advanced NAS methods. Furthermore, the pursuit of NN inference efficiency has opened the door to investigating more design prospects by (i) unleashing the potential of NN dynamicity to operate in an input-adaptive manner [82] and (ii) including HW features in a co-design manner to get the best from both worlds by scaling neural networks and hardware features [43]. The right side of Figure 1.2 reports the latest statistics on the growing popularity of each design approach to emphasize the role each plays in stretching the design landscape of NNss within the era of Edge AI.

### 1.3 Chasing Efficiency in the Era of Edge AI

Chasing computation and energy efficiency for Edge AI has recently been the center of attention due to the surge in demand for real-time AI applications in resource-constrained environments. Thus, many optimization approaches are being thoroughly studied and carefully adjusted to accommodate the need for new emerging applications, neural networks, and hardware paradigms. One prominent optimization strategy is CMOS <sup>2</sup> technology scaling to enable integrating smaller and more energy-efficient transistors onto processing units of compact chips that can serve AI accelerators [35].

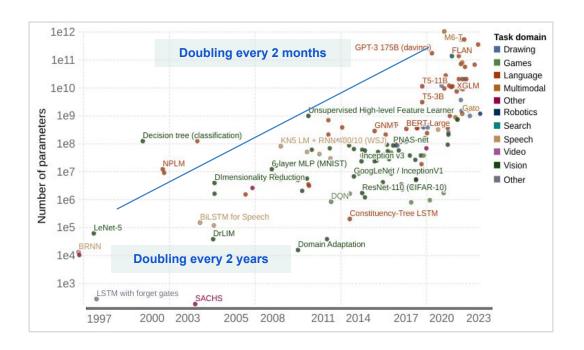

As shown in Figure 1.3, the advancing speed of AI application workloads and their computing complexity, which doubles every two months, limits the potential of technology scaling, particularly regarding power consumption and thermal ma-

<sup>2. &</sup>lt;u>C</u>omplementary <u>M</u>etal-<u>O</u>xide-<u>S</u>emiconductor is a technology for integrated circuits, known for its low power use and high noise resistance, used in most modern digital devices.

**Figure 1.3** The growth rate of AI workloads in different application domains with their respective computing complexity is given in the y-axis as the number of parameters [2].

nagement. Furthermore, as transistors approach atomic limits, sustaining Moore's Law has become increasingly complex, slowing down technological advancements. As a result, optimization strategies are investigated from other perspectives – notably, from application and hardware perspectives. This thesis aims to show how the interplay between both perspectives can be leveraged to enhance efficiency in the era of Edge AI.

### 1.4 Edge AI Optimization Techniques

### 1.4.1 Software-level Optimizations

Software-level optimizations for neural networks on edge computing devices are instrumental in achieving efficient and cost-effective inference. These optimizations mainly focus on tailoring the neural network architecture and operations to minimize computational complexity while maintaining task performance. Given the strong correlation between NN model size and computational complexity, existing optimization strategies focus on providing lightweight models via compression. Model compression has been widely explored in literature. One widely adopted is pruning, which involves retrieving and removing less important weights and neurons from a NN [245, 64, 272]. Pruning is highly applied to CNN by removing specific weights (fine-grain pruning) or entire convolutional filters (coarse-grain pruning). Another technique is quantization, which reduces the precision of input activations and weights from 32-bit floating-point to lower-bit fixed-point representations (16-bit or 8-bit) [221, 243, 178]. Knowledge distillation is another compression method for NN in which a lightweight student model is trained to mimic the behavior and predictions of a large teacher model [247, 76]. Additionally,

Parameter sharing across multiple layers of NN is effective in vision-related tasks through capturing similar patterns or features across different spatial locations [181]. Matrix factorization offers another opportunity for model compression by decomposing a large weight matrix into smaller matrices with lower rank [231].

Compression techniques can be applied directly to a fixed design of neural networks without changing their neural architectures. Nevertheless, re-designing lightweight NN by choosing less compute-demanding operations and/or low values for neural layers depth and width can also be achieved via Neural Architecture Search [229, 252, 173]. NAS approaches have contributed to the realization of compact NN models such as MobileNet-v3 [89] and EfficientNet [215] by adjusting the internal neural architectural configurations to reduce model size while preserving feature representation power. Compression and NAS techniques can collaboratively contribute to facilitating the deployment of NN on edge devices by minimizing computation and memory demands that strongly impact the latency and energy consumption of real-time AI applications.

### 1.4.2 Hardware-level Optimizations

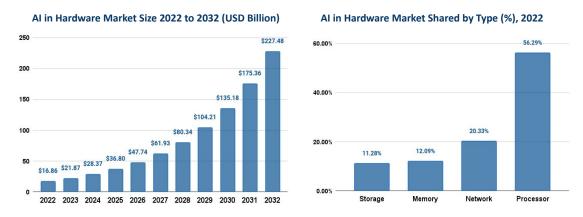

The hardware era has witnessed several computing devices emerging from general-purpose to specialized accelerators. AI applications are often deployed in real-time and critical environments, necessitating fast execution to return inference results within a strict delay. This has made computation acceleration a priority within the hardware community. AI has taken a large amount of the Hardware market, as shown in the left of Figure 1.4 with an estimated 227 billion dollars by 2032. The breakdown in the right of Figure 1.4 emphasizes the importance of processor scaling, depicting up to 56.29% of investment in 2022.

Edge computing devices are battery-powered and operate under a limited power budget. A reasonable use of computing power is needed to prevent dysfunctional or system failure in critical situations (e.g., autonomous cars). Thus, execution latency and power consumption are significant for Edge AI systems.

**Figure 1.4 Left**: The expected growth of the global AI in hardware market size from 2022-2032. **Right**: Breakdown of AI in HW market size per hardware type.

Hardware optimizations are mostly focused maximizing computing capabilities for a *fast inference* and minimizing power consumption for *energy-efficient inference*. Conventional HW accelerators play a pivotal role in achieving this in-

terplay. Graphic Processing Units (GPUs), Field-Programmable Gate Arrays (FP-GAs), and Application-Specific Integrated Circuits (ASICs) have been improved through the recent decades to balance flexibility and efficiency. These accelerators leverage computing parallelism and optimized instruction sets for deep learning operations – matrix-matrix multiply - to maximize resource utilization and speed computations via specialized routines.

Specialized accelerators, such as FPGAs and ASICs, are primarily based on a systolic array, a grid of processing elements (PEs) interconnected in a regular structure for data sharing. These grids can be programmable, allowing for fine-grained computing parallelism and data reuse to optimize matrix-matrix multiplication, the core operation in neural networks.

General-purpose accelerators (GP), such as CPU and GPU, are built upon fixed hardware micro-architectures that, unlike FPGAs, don't allow for hardware reconfigurability. Instead, they encompass a grid of cores with parallel processing units that share cache memory for data communication and synchronization. Commodity edge GPUs often integrate specialized tensor cores optimized for matrix-matrix multiply. Although general-purpose accelerators are more flexible regarding programmability and can perform well for different operations, they're rigid and closed HW architecture for further design tuning (e.g., computation parallelism).

Unlike monolithic accelerators, heterogeneous MPSoCs (Multi-Processor Systems on Chips) are designed to embed different accelerators within the same die to accommodate the computing requirements of hybrid types of NN operations. Each computing unit (CU) of the MPSoC is optimized for distinct computational tasks [111]. For instance, commercial MPSoCs, such as the Nvidia Jetson series: AGX Xavier [162], TX2 [160], and Nano [163], as well as from other HW vendors such as Tesla FSD [211], and Intel Movidius Myriad 2 [161] have successfully integrated a variety of proven hardware computing units (e.g., CPU, GPU, and NPU) and industrial IPs on a single chip to achieve said purpose. This heterogeneity ensures that each phase of the inference pipeline – from data preprocessing to the final output – can be mapped to the most suitable CU, thereby maximizing efficiency and effectively using the MPSoC resources [22]. Furthermore, this approach accelerates inference speedup and maximizes energy efficiency by mapping computations to less energy-demanding CUs. As neural networks grow in complexity and ubiquity, heterogeneous MPSoCs play a crucial role in the speedup-energy balance.

Another way to reduce the energy consumption in edge computing systems is by leveraging Dynamic Voltage and Frequency Scaling. DVFS is a power management technique that adjusts the supply voltage and the operating clock frequency. It serves as a control knob to balance execution time and power consumption by adjusting the speed of computations and data transmission. The rationale behind DVFS for AI-based applications is the fluctuating computational demands observed in NN workloads. The NN inference pipeline encompasses hybrid operations with distinct computational and memory demands. Compute-bound operations typically require high clock frequencies on the computing unit, while memory-bound operations can benefit from optimizing the clock frequency of the DRAM. Power consumption is proportional to clock frequency and square of voltage. The quadratic correlation between power and voltage is crucial as it yields significant power gains. However, since frequency is typically proportional to voltage, dynamic voltage scaling is closely related to frequency scaling. For instance, higher frequency

cies necessitate higher voltages and vice versa. Consequently, many accelerators offer mechanisms to employ DVFS by adjusting the clock frequencies of computing units and memory controllers. As NNs become more intricate and expansive, utilizing DVFS is essential to ensure efficient inference without compromising the device's battery life or thermal limits.

Finally, as we're approaching the end of Moore's law, physical and thermal limitations of existing CMOS technologies have pushed the hardware community to investigate unconventional computing paradigms beyond the typical Von Neumann architecture. Specifically, alternatives to conventional and monolithic accelerators are expected to be served by emerging neuromorphic, photonics, and quantum computing paradigms. Inspired by the human brain system, neuromorphic computing aims to emulate neural structures and operations, providing energy-efficient processing capabilities tailored for AI tasks like pattern recognition [110]. Quantum computing, which leverages the principles of quantum mechanics, is expected to accelerate intricate AI algorithms that are infeasible for classical computing systems [74]. Meanwhile, photonic computing employs light-based signals instead of electronic ones, offering rapid data transmission, reduced energy consumption, and eco-friendly systems – pivotal for real-time AI applications on edge systems [227]. While these innovative computing paradigms are in their early stages, they foreshadow a groundbreaking shift in Edge AI, paving the way for enhanced computational capabilities that align seamlessly with the needs of future AI applications (e.g., Multimodal Large Language Models).

### 1.5 Winning the 'Performance-Efficiency' Lottery Ticket

As the fields of neural networks and hardware systems progress rapidly at different rates, there's a predominant focus on optimizing each domain independently. This singular approach often ignores the critical significance of integrating, unifying, and harmonizing advancements from both fields. Existing works must bridge the gap between NN and HW innovations to unlock further potential breakthroughs from joining efforts. More precisely, the architectural design of neural networks plays a critical role in the tug-of-war between performance tasks and inference efficiency. If not carefully tuned, even the most advanced optimizations at the software or hardware levels might not yield the desired outcomes when applied to ill-designed neural networks. Regardless of the software or hardware innovations, if the foundational neural network design is flawed, these enhancements could fail to achieve their potential benefits. Conversely, while delegating more emphasis on tuning and refining the design of neural networks via handcrafted or automated approaches (e.g., NAS or HW-aware NAS) is laudable, It's neither efficient nor effective when applied solely. When Auto-design approaches are employed in isolation, without incorporating the other optimization levels mentioned previously, their results are often sub-optimal. Thus, a holistic, hierarchical, and cross-level approach that leverages various optimization strategies at different levels is expected to yield more robust and optimal results.

On the other hand, incorporating many factors into the design space exploration for NN and HW optimization often yields an exponential search space explosion. Exploring such a joint large search space employing traditional approaches of *train-and-deploy* is inefficient, time-consuming, and resource-intensive. A strategy

to accelerate the evaluation and search process to explore as many design options as possible is essential. One way to achieve this is using Machine Learning (ML) based performance estimators. By employing prediction models, we can significantly accelerate the exploration process, making it possible to quickly identify promising design candidates without exhaustive training, testing, and deploying each one. This approach falls under the umbrella of ML for ML or ML4ML to speed up the NN design, making the pursuit of the most efficient and accurate NN designs economically viable and technically feasible.

### 1.6 Thesis Structure and Contributions

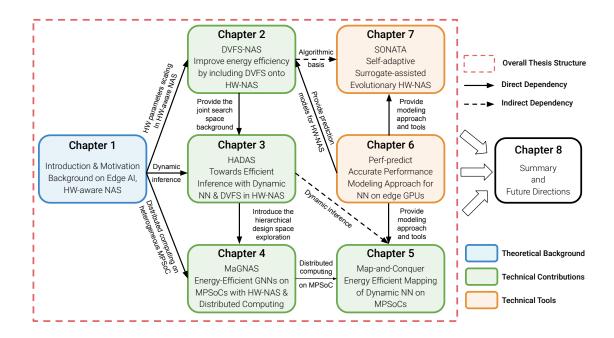

**Figure 1.5** Thesis structure and dependencies between chapters

This thesis aims to mitigate the disparity observed in literature by delving into the interdisciplinary fields of multi-objective optimization, surrogate modeling, HW-aware NAS, and software and hardware optimizations. We focus on expanding the typical HW-aware NAS frameworks by leveraging various optimizations to support the ultimate objective of Edge AI – identifying the optimal Nash equilibrium between accuracy, execution speed, and energy efficiency to promote more sustainable computing. As depicted in Figure 1.5, this thesis contains the following contributions and novelties in the realm of Edge AI optimization:

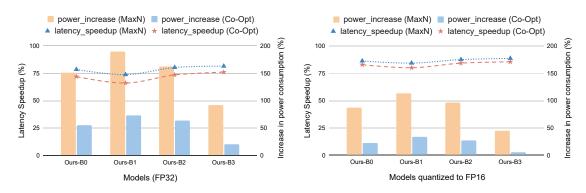

— Chapter 2: Dynamic Clock Frequency Scaling (DVFS) in HW-aware NAS In [26, 27, 25], we extend the typical HW-aware NAS framework by including Dynamic Clock Frequency Scaling (DVFS) features as re-configurable hardware parameters on edge GPU MPSoCs. We showcase the importance of tailoring the design of NN to different DVFS policies and vice-versa. Consequently, we construct a joint search space of neural networks built upon the supernet structure of AttentiveNAS [220] and DVFS parameters by varying the clock frequencies. We propose a co-optimization framework to explore the predefined joint search space. Our proposed approach has been validated on

three datasets for Image classification, namely CIFAR-10, CIFAR-100, and ImageNet-1k, using the Jetson AGX Xavier edge GPU from NVIDIA. Compared to the default DVFS configuration (MAXN), evaluation results have shown up to  $\sim 53\%$  energy gains on the native Pytorch framework and a latency speedup of  $\sim 81\%$  and power saving of  $\sim 61\%$  with TensorRT.

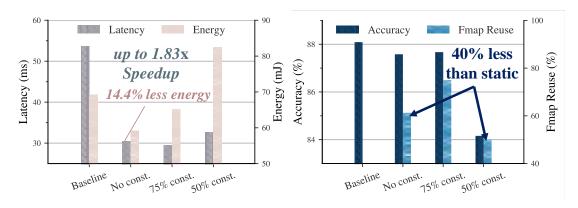

- Chapter 3: Hardware-aware Dynamic Neural Architecture Search In [21], we explore the prospect of dynamic neural networks (DyNN) through our framework, HADAS, a versatile and comprehensive HW-aware NAS framework that jointly optimizes static and dynamic components in NNs to balance the performance-efficiency tradeoff. We leverage the early exit dynamic inference technique to terminate computation earlier when the output can be correctly predicted. We make the design of the DyNN fully searchable by expanding the existing infrastructure of HW-aware NAS and supernets and constructing a novel joint search space for: (i) static backbone NN design, (ii) dynamic early-exit branches, and (iii) DVFS configurations. Then, we contribute an innovative co-optimization framework by hierarchizing the design exploration process of static and dynamic components using two dedicated optimization engines. We validate our approach using the CIFAR-100 dataset on various hardware configurations: ARM, Denver CPUs, Volta, and Pascal GPUs from the NVIDIA Jetson AGX Xavier and TX2. Evaluation results have seen the superiority of HADAS by providing up to  $\sim 57\%$  while sustaining an acceptable level of accuracy.

- Chapter 4: Hardware-aware NAS for GNN on Heterogeneous MPSoC In [165], we delve into the world of Graph Neural Networks (GNN) on commodity edge heterogeneous MPSoCs. Specifically, we target the case of vision GNNs that have shown impressive results in recognizing visual patterns by transforming images into graphs of pixels and learning contextual information from neighboring graph nodes. We propose an end-to-end framework, MaGNAS from GNN design optimization to workloads mapping on MPSoC. We first construct and design novel supernet structures for GNNs by varying graph operations such as aggregation and combination. We provide a detailed and comprehensive system model for GNN workload characterization and mapping on heterogeneous MPSoC in a distributed, pipelined fashion. Then, we implement a hierarchical design space exploration to optimize the design of GNNs jointly with their workload mappings on the heterogeneous computing units of the MPSoC. We validate our proposed framework on various datasets for image recognition, namely CIFAR-10, CIFAR-100, Tiny-ImageNet, and Oxford-Flowers. As hardware settings, we employ (i) the NVIDIA Jetson AGX Xavier as a real MPSoC and (ii) MAESTRO, a cost model to simulate the case of an MPSoC by varying dataflows. Evaluation results have demonstrated the effectiveness of our approach by providing  $\sim 1.57 \times$  latency speedup,  $\sim 3.38 \times$  energy efficiency for several vision datasets while sustaining less than 0.11% accuracy reduction from SOTA models.

- Chapter 5: Mapping of Dynamic Neural Nets on Heterogeneous MPSoC In [22], we research the potential of distributed and parallel computing for dyNN on heterogeneous MPSoCs. One way to enable the dynamic and collaborative usage of the computing units within an MPSoC is through dyNN. Specifically, by employing an early exit scheme, computing units will be acti-

vated according to the complexity of the input data. Within this context, we introduce Map-and-Conquer, an innovative framework designed to efficiently map the computing stages of DyNNs on heterogeneous MPSoCs in a parallel pipeline manner. Our methodology first determines the best partitioning strategy for the DyNN across its 'width' dimension, allowing for concurrent and parallel deployment of DyNN inference blocks on various computational units. We validate our approach on Transformers and CNN models on the CIFAR-100 dataset. We employ a real MPSoC from NVIDIA, Jetson AGX Xavier, equipped with a CPU, GPU, and Deep Learning Accelerator (DLA) as a hardware setting. Our evaluation results have shown that our dynamic configurations are 2.1x more energy-conserving than GPU-only setups and experience 1.7x reduced latency than DLA-only configurations.

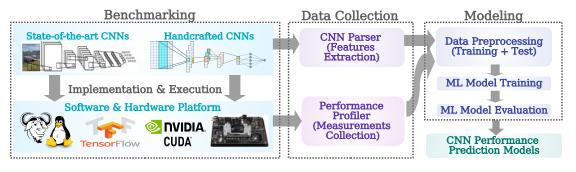

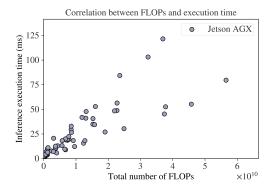

- Chapter 6: Performances Modeling of Neural Networks on Edge GPUs In [23, 24], we contribute to the concept of ML4ML by demonstrating how ML-based methods can be used to reduce the complexity of HW-aware NAS. One critical challenge of HW-aware NAS is performance evaluation. This process is time-consuming, necessitating the execution of an entire pipeline from model design to deployment and many rounds of performance measurements. To accelerate this step, performance prediction models can be used instead to provide quick estimations within microseconds. Within this scope, we propose a comprehensive performance analysis and characterization of CNN inference workloads on edge GPUs. We study the correlation between diverse CNN features and several performance metrics (i.e., latency, power consumption, and memory usage). We elaborate an end-to-end modeling methodology using ML-based methods to fit performance prediction models. We validate our approach on SOTA and synthetic CNN architectures on three edge GPUs from the NVIDIA Jetson series: AGX Xavier, TX2, and Nano. Our prediction models have shown an average error of  $\sim 11\%$ ,  $\sim 6\%$ , and  $\sim 8\%$  for latency, power, and memory usage estimations, respectively.

- Chapter 7: Surrogate-assisted Self-adaptive Evolution for HW-aware NAS In [?], we extend the concept of ML4ML to enhance the efficiency of evolutionary search algorithms in HW-aware NAS. Most existing HW-aware NAS methods, such as evolutionary algorithms, are built upon multi-objective optimization approaches. However, these algorithms heavily rely on randomness without established reasoning on the importance of NN design parameters on the optimization objectives. A priori knowledge of the importance of design parameters helps focus on the most rewarding ones during the search and thus wisely use the optimization budget. Furthermore, the massive amount of data generated during the search can be exploited to derive such knowledge. Given these observations, we propose SONATA, a self-adaptive evolution for multi-objective HW-aware NAS frameworks. We design self-adaptive evolution operators guided by the importance of NN design parameters. We leverage ML-based methods to progressively learn the importance of design parameters from the data generated during the search. An extensive evaluation of multiple NAS search spaces and edge devices has shown that our approach improves upon the baseline with an accuracy improvement up to  $\sim 0.25\%$  and latency/energy gains up to  $\sim 2.42x$ .

### Chapitre 2

### DVFS-NAS: Dynamic Clock Frequency Scaling for Hardware-aware Neural Architecture Search on Edge GPUs

### 2.1 Introduction

Deep Neural Networks (DNN) and hardware accelerators are leading forces for the recent observed progress in Edge AI. On the one hand, a new neural architectural paradigm is proposed each month, striving for more accuracy and efficiency. On the other hand, the hardware market has shifted towards designing devices that ensure flexibility and generality for less energy demands while satisfying the user experience with less latency. Thus, reconfigurability has been standardized across general-purpose hardware platforms such as GP-GPUs through cores and clock frequency scaling to emulate different performance and energy efficiency levels using the same device. However, recently, DNN architectures are becoming increasingly complex and hardware resource-demanding. As shown in Figure 1.3, the growth rate of DNN model complexity (i.e., "every two months") exceeds the hardware scaling capabilities of Moore's law (i.e., "every two years"). Thus, exploring new optimization dimensions in existing hardware devices is mandatory to meet the computation demands of DNN models.

Particularly, when DNN models are implemented on resource-constrained systems (e.g., edge computing), it becomes inevitable to meticulously optimize them to strike the optimal balance between accuracy and execution latency, as well as energy efficiency. In order to address this particular difficulty, researchers have introduced Hardware-aware Neural Architecture Search (HW-aware NAS) as a new AutoML paradigm, targeting edge systems [14]. HW-aware NAS incorporates hardware efficiency as an additional optimization objective during the neural architecture design space exploration.

Nevertheless, hardware efficiency is contingent upon the interplay between the architectural design of the neural network and the settings of the hardware itself [157, 244]. Most existing works on Hardware-aware NAS primarily focus on optimizing neural networks without considering the hardware accelerator's reconfigurability. As elucidated in the study conducted by [100], the aforementioned technique exhibits sub-optimality due to the limited exploration potential of the HW-aware NAS when confined to a predetermined hardware design. Therefore, including the hardware design space has made it viable to identify customized DNNs for any configuration and vice versa. We refer to this joint exploration of both search spaces as the co-optimization.

In this chapter, we propose to include Dynamic Clock Frequency Scaling (DVFS) features in the HW-aware NAS process on commodity edge GPUs. We aim to