## Walk-In: flexible virtualization APIs for performance and security in the modern datacenter

Tu Dinh Ngoc

### ▶ To cite this version:

Tu Dinh Ngoc. Walk-In : flexible virtualization APIs for performance and security in the modern datacenter. Library and information sciences. Université de Toulouse, 2024. English. NNT : 2024TLSES002 . tel-04579334

## HAL Id: tel-04579334 https://theses.hal.science/tel-04579334v1

Submitted on 17 May 2024  $\,$

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# **Doctorat de l'Université de Toulouse**

## préparé à l'Université Toulouse III - Paul Sabatier

Walk-In : interfaces de virtualisation flexibles pour la performance et la sécurité dans les datacenters modernes

# Thèse présentée et soutenue, le 5 février 2024 par Ngoc Tu DINH

### École doctorale

EDMITT - Ecole Doctorale Mathématiques, Informatique et Télécommunications de Toulouse

### **Spécialité**

Informatique et Télécommunications

### Unité de recherche

IRIT : Institut de Recherche en Informatique de Toulouse

### Thèse dirigée par

Georges DA COSTA et Daniel HAGIMONT

### **Composition du jury**

Mme Julia LAWALL, Rapporteure, INRIA Paris

- M. David BROMBERG, Rapporteur, Université de Rennes

- M. Renaud LACHAIZE, Examinateur, Université Grenoble Alpes

- M. Georges DA COSTA, Directeur de thèse, Université Toulouse III Paul Sabatier

- M. Daniel HAGIMONT, Co-directeur de thèse, Toulouse INP

- M. Noel DE PALMA, Président, Université Grenoble Alpes

Membres invités

M. Boris TEABE, Toulouse INP

### Doctorate from the University of Toulouse

prepared at the Université Toulouse III - Paul Sabatier

## Walk-In: Flexible Virtualization APIs for Performance and Security in the Modern Datacenter

Thesis presented and defended on 05 Feb 2024 by:

## Tu Dinh Ngoc

**Doctoral school:**

EDMITT - Ecole Doctorale Mathématiques, Informatique, Télécommunications de Toulouse

**Specialty:** Computing and Telecommunications

**Research unit:** IRIT : Institut de Recherche en Informatique de Toulouse

> **Thesis directed by:** Georges Da Costa and Daniel Hagimont

#### Jury composition:

Ms. Julia Lawall, Reviewer, INRIA Paris Mr. David Bromberg, Reviewer, Université de Rennes Mr. Renaud Lachaize, Examiner, Université Grenoble Alpes Mr. Georges Da Costa, Thesis director, Université Toulouse III - Paul Sabatier Mr. Daniel Hagimont, Thesis director, Toulouse INP Mr. Noel De Palma, Jury president, Université Grenoble Alpes

Guest members:

Mr. Boris Teabe, Toulouse INP

#### Abstract

Virtualization is a powerful tool that brings numerous benefits for the security, efficiency and management of computer systems. Modern infrastructure therefore makes heavy use of virtualization in almost every software component. However, the extra hardware and software layers present various challenges to the system operator.

In this work, we analyze and identify the challenges relevant to virtualization. Firstly, we observe a complexification of maintenance from the numerous software layers that must be constantly updated. Secondly, we notice a lack of transparency on details of the underlying infrastructure from virtualization. Thirdly, virtualization has a damaging effect on system performance, stemming from how the layers of virtualization have to be navigated during operation.

We explore three approaches of solving the challenges of virtualization through adding flexibility into the virtualization stack.

- Our first contribution tackles the issue of maintainability and security of virtual machine platforms caused by the need to keep these platforms up-todate. We introduce HyperTP, a framework based on the hypervisor transplant concept for updating hypervisors and mitigating vulnerabilities.

- Our second contribution focuses on performance loss resulting from the lack of visibility of non-uniform memory access (NUMA) topologies on virtual machines. We thoroughly evaluate I/O workloads on virtual machines running on NUMA architectures, and implement a unified hypervisor-VM resource allocation strategy for optimizing virtual I/O on said architectures.

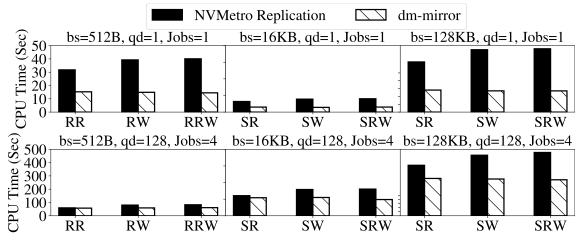

- For our third work, we focus our attention on high-performance storage subsystems for virtualization purposes. We present NVMetro, a flexible yet easy to use virtual storage platform that supports the implementation of fast yet efficient storage functions.

Together, our solutions demonstrate the tradeoffs present in the configuration spaces of virtual machine deployments, as well as how to reduce virtualization overhead through dynamic adjustment of these configurations.

#### Résumé en français

La virtualisation est un outil puissant conférant de nombreuses avantages pour la sécurité, l'efficacité et la gestion des systèmes informatiques. Par conséquent, la virtualisation est largement utilisée dans les infrastructures informatiques modernes. Cependant, les couches materielles et logicielles supplémentaires posent de nouveaux défis aux administrateurs systèmes.

Dans cette thèse, nous présentons notre analyse des défis liés à la virtualisation. Nous constatons que les nombreux composants de virtualisation doivent être tenus à jour, ce qui complique fortement la maintenance logicielle. Deuxièmement, nous remarquons que la virtualisation masque les spécificités du matériel. Enfin, elle réduit les performances des systèmes du fait de la coordination entre les logiciels impliqués par la virtualisation.

Nous étudions trois approches pour relever les défis présentés ci-dessus en augmentant la flexibilité de la pile de logiciels de virtualisation.

- Notre première contribution concerne la maintenabilité et la sécurité des plateformes de machines virtuelles en tenant compte du besoin de les maintenir à jour. Nous présentons notre cadre « HyperTP » pour la mise à jour des hyperviseurs et l'attenuation des vulnérabilités pendant le délai entre leur découverte et leur correction.

- Notre deuxième contribution concerne la perte de performance résultant du manque de visibilité des topologies NUMA dans les machines virtuelles. Nous étudions la performance des charges de travail d'E/S virtuelles afin de déterminer une politique d'allocation des ressources pour l'optimisation des E/S.

- Notre troisième contribution concerne la virtualisation des systèmes de stockage à haute performance. Nous présentons la plateforme de stockage NVMetro, qui permet la réalisation de fonctions de stockage performantes grâce à sa flexibilité et à sa facilité d'utilisation.

En résumé, nos contributions montrent les compromis présents dans les configurations des machines virtuelles, ainsi que la réduction des coûts de virtualisation par la manipulation dynamique de ces configurations.

# Acknowledgements

Firstly, I would like to acknowledge my PhD jury members for the time and effort you have spent on my thesis. I would like to thank Ms. Julia Lawall and Mr. David Bromberg for agreeing to review my thesis and giving me helpful comments and feedback; and Mr. Noel De Palma and Mr. Renaud Lachaize for examining my work and joining my thesis defense. I greatly enjoyed our discussion as well as your deep insights.

I am very grateful to Mr. Daniel Hagimont and Mr. Georges Da Costa for guiding me through my PhD. You gave me the incredible opportunity to do research at IRIT, and your advices and wisdom were truly valuable to my project.

A special thank goes to Mr. Boris Teabe, who has assisted me throughout my years in France. You went above and beyond in accompanying me both at and outside of work. I am very glad to have you as a mentor and excellent collaborator.

I would like to also thank the laboratory secretaries Ms. Sylvie Armengaud and Ms. Vanessa Adjeroud for your hospitality and support during my PhD. You were an invaluable help to all of us at IRIT.

Thanks to all of my good friends in France: Armel, Jean-Baptiste, Boris Wembe, Djob, Firmin, Kevin, Hiep, Hoang, and so many others, who were a great fun to talk with every day, and made the office a truly enjoyable place to be at.

Lastly, I cannot forget to thank my father, mother and sister, who cared about and encouraged me when I was far away from home.

# **Publications**

Following is a list of works that have been accomplished as part of my research project. Works **2**, **3** and **4** constitute parts of this thesis.

#### First-author works:

- Tu Dinh Ngoc, Boris Teabe, Alain Tchana, Gilles Muller, and Daniel Hagimont. Mitigating vulnerability windows with hypervisor transplant. In *Proceedings* of the Sixteenth European Conference on Computer Systems, EuroSys '21, page 162–177, New York, NY, USA, 2021. Association for Computing Machinery. ISBN 9781450383349. doi:10.1145/3447786.3456235

- 2. Tu Dinh Ngoc, Boris Teabe, Daniel Hagimont, and Georges Da Costa. Optimized resource allocation on virtualized non-uniform I/O architectures. In 2022 22nd IEEE International Symposium on Cluster, Cloud and Internet Computing (CCGrid), pages 432–441. IEEE, 2022. doi:10.1109/CCGrid54584.2022.00053

- Tu Dinh Ngoc, Boris Teabe, Alain Tchana, Gilles Muller, and Daniel Hagimont. HyperTP: A unified approach for live hypervisor replacement in datacenters. *Journal of Parallel and Distributed Computing*, page 104733, 2023. doi:10.1016/j.jpdc.2023.104733

- 4. Tu Dinh Ngoc, Boris Teabe, Georges Da Costa, and Daniel Hagimont. Flexible NVMe request routing for virtual machines. In *2024 IEEE International Parallel and Distributed Processing Symposium (IPDPS)*, 2024 **[To appear]**

#### Other works:

- 5. Brice Ekane, Tu Dinh Ngoc, Boris Teabe, Daniel Hagimont, and Noel De Palma. FlexVF: Adaptive network device services in a virtualized environment. *Future Generation Computer Systems*, 127:14–22, 2022. doi:10.1016/j.future.2021.08.011

- Jean-Baptiste Decourcelle, Tu Dinh Ngoc, Boris Teabe, and Daniel Hagimont. Fast VM replication on heterogeneous hypervisors for robust fault tolerance. In *Proceedings of the 24th International Middleware Conference*, Middleware '23, pages 15–28, New York, NY, USA, 2023. Association for Computing Machinery. ISBN 9798400701771. doi:10.1145/3590140.3592849

# Contents

| 1 | Introduction |                                                                         |    |  |  |  |

|---|--------------|-------------------------------------------------------------------------|----|--|--|--|

|   | 1.1          | Overview                                                                | 1  |  |  |  |

|   | 1.2          | The challenges of virtualization                                        | 2  |  |  |  |

|   | 1.3          | Our contributions                                                       | 2  |  |  |  |

|   | 1.4          | Structure of this thesis                                                | 4  |  |  |  |

| 2 | Con          | text                                                                    | 5  |  |  |  |

|   | 2.1          | The various facets of virtualization                                    | 5  |  |  |  |

|   | 2.2          | Inside platform virtualization                                          | 6  |  |  |  |

|   | 2.3          | NUMA and I/O virtualization                                             | 12 |  |  |  |

|   | 2.4          | The NVM Express specification                                           | 13 |  |  |  |

|   | 2.5          | Linux's eBPF engine                                                     | 14 |  |  |  |

| 3 | Нур          | erTP: A unified approach for live hypervisor replacement                | 15 |  |  |  |

|   | 3.1          | Overview                                                                | 16 |  |  |  |

|   | 3.2          | Design of HyperTP                                                       | 18 |  |  |  |

|   | 3.3          | Prototype                                                               | 23 |  |  |  |

|   | 3.4          | Evaluation                                                              | 29 |  |  |  |

|   | 3.5          | Discussion                                                              | 40 |  |  |  |

|   | 3.6          | Related works                                                           | 41 |  |  |  |

|   | 3.7          | Summary                                                                 | 43 |  |  |  |

| 4 | Opti         | imized resource allocation on virtualized non-uniform I/O architectures | 45 |  |  |  |

|   | 4.1          | Overview                                                                | 46 |  |  |  |

|   | 4.2          | Impact of NUIOA on VM performance                                       | 47 |  |  |  |

|   | 4.3          | NUIOA-aware VM resource allocation strategy                             | 53 |  |  |  |

|   | 4.4          | Evaluation                                                              | 55 |  |  |  |

|   | 4.5          | Related works                                                           | 61 |  |  |  |

|   | 4.6          | Summary                                                                 | 62 |  |  |  |

| 5 | NVN          | Metro: Enhancing mediated NVMe virtualization with eBPF                 | 65 |  |  |  |

|   | 5.1          | Overview                                                                | 66 |  |  |  |

|   | 5.2          | Design of NVMetro                                                       | 67 |  |  |  |

|   | 5.3          | Use cases                                                               | 72 |  |  |  |

|   | 5.4          | Evaluation                                                              | 77 |  |  |  |

| 6 | Con | clusion and perspectives | 89 |

|---|-----|--------------------------|----|

|   | 5.6 | Summary                  | 88 |

|   | 5.5 | Related works            | 86 |

## Chapter 1

## Introduction

#### Contents

| 1.1 Overview                         | 1 |

|--------------------------------------|---|

| 1.2 The challenges of virtualization | 2 |

| 1.3 Our contributions                | 2 |

| 1.4 Structure of this thesis         | 4 |

### 1.1 Overview

Among other advances, virtualization has been the main driver of changes in how organizations develop and deploy software. Numerous hardware and software tools have been developed for the purposes of virtualization: specialized CPU instructions, hardware protocols, software stacks (e.g. VMware vSphere, Kubernetes), among others.

At its core, virtualization entails providing an abstract representation of computing resources on top of real ones. Almost any resource can be virtualized: memory, storage/ networking, operating system environments, etc. Virtualization brings various benefits to the operation of computer systems: firstly, virtualization helps increases hosting density by sharing the same physical hardware across multiple execution environments. Secondly, virtualization provides a layer of isolation for security, reliability and resource control reasons. Lastly, it lets the system operator freely manipulate virtual resources: granting and taking them away, saving and loading their states, or even migrating them across machines.

The modern deployment model therefore contains multiple instances of virtualization. Consider an example of a function-as-a-service (FaaS) deployment, where virtualization-adjacent components are shown in bold: a serverless function runs in a **container** hosted in a **virtual machine** (VM) managed by a **hypervisor**. The function communicates with the outside world through a **container network interface** provided by an **overlay network** backed by the virtual machine's **virtual network interface**.

## **1.2** The challenges of virtualization

As we can see, modern software deployments make extensive use of virtualization in various points of their infrastructure. However, such an extensive virtualization stack brings significant challenges to the system operator. We list below a few examples of challenges we tackle in this thesis.

**Manageability.** Each of these virtualization layers include their own software stack which needs to be maintained, updated and secured. Particularly, updating a virtualized infrastructure is critical to maintaining its security, yet there exists numerous difficulties in discovering, testing and deploying patches [7, 8]. Zhang et al. reports needing a total of 15 days just to upgrade a virtual machine monitor to a newer version [9]. Together, these tasks take up a considerable amount of time and resources, without eliminating the *vulnerability window* between the moment a vulnerability becomes known, and when the infrastructure is fully secured (also known as a *patch gap*).

**Transparency.** Virtualization hides details of the underlying infrastructure from the application. While this is often intentionally done for security and portability purposes, it also takes away the opportunity to optimize workloads for the systems they are running from. In particular, modern servers are *distributed systems* consisting of islands of compute, memory and I/O linked together with interconnects. While solutions exist to reflect this architecture to VMs, the information they provide is often not complete, and the reconfiguration inefficient [10, 11].

**Performance.** The enormous software stack of modern deployments comes with a significant performance cost, as more work is needed to mediate an application's operations. Li et al. demonstrates an overhead of over 3× for device emulation in Xen, a common part of virtual machines running on said platform [12]. Zhong et al. shows that software has become the bottleneck of high-performance storage, with the file system driver, kernel crossing and block layer operations accounting for over 40% of average I/O latency [13].

## 1.3 Our contributions

In this thesis nicknamed "Walk-In", we propose to mitigate the above challenges through adding *flexibility* in the virtualization software stack. The core idea of our work is to explore the configuration space of virtualized deployments, and choose an appropriate configuration that targets a given challenge. By presenting multiple choices of virtualization methods while deeply understanding the pros and cons of each method, our work aims to solve the inefficiencies of virtualized deployments by choosing a virtualization method that best fits each use case. We apply our idea of flexibility in each of the challenges presented above:

- 1. We tackle the problems of hypervisor updating and vulnerability mitigation by dynamically switching from a current hypervisor to another. By introducing two levels of flexibility in hypervisor implementation and switching method, we can effectively *avoid* an active vulnerability in minimal time and with minimal overhead.

- By analyzing the various tradeoffs involved in I/O performance, as well as VM and application configurations, we create an I/O-aware resource allocation strategy that optimizes the performance of virtual I/O on non-uniform memory access (NUMA) architectures.

- 3. We present a virtual storage platform that combines an intelligent request classifier and router mechanism with multiple I/O paths for implementing sophisticated storage functions while maintaining high performance and security.

For our first contribution, we build *HyperTP*, a generic hypervisor replacement framework which flexibly combines two approaches: in-place server micro-rebootbased hypervisor transplant (noted *InPlaceTP*) and live VM migration-based hypervisor transplant (noted *MigrationTP*). HyperTP hinges on a *VM state hierarchy* for organizing different types of hypervisor memory states in terms of their relation to VM execution, and an *Unified Intermediate State Representation* (UISR) that abstracts VM-relevant memory states between multiple different hypervisors. We describe our implementations of both approaches, including technical details of our UISR design and the transplant process. Our evaluation results show that HyperTP delivers satisfactory performance: (1) InPlaceTP imposes minimal VM downtime, even under increasing number of VMs and memory sizes; (2) MigrationTP changes a VM's underlying hypervisor while taking the same time and impacting virtual machines with the same performance degradation as normal live migration. Finally, we discuss how the combination of InPlaceTP and MigrationTP can be used to address the challenges of upgrading a hypervisor cluster, and to mitigate known unpatched hypervisor vulnerabilities.

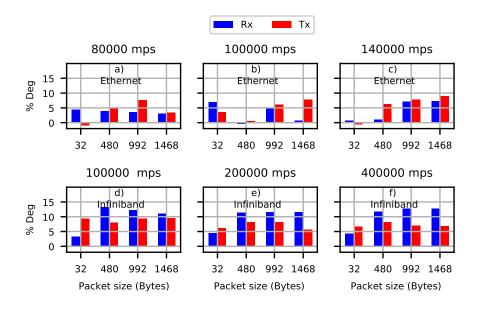

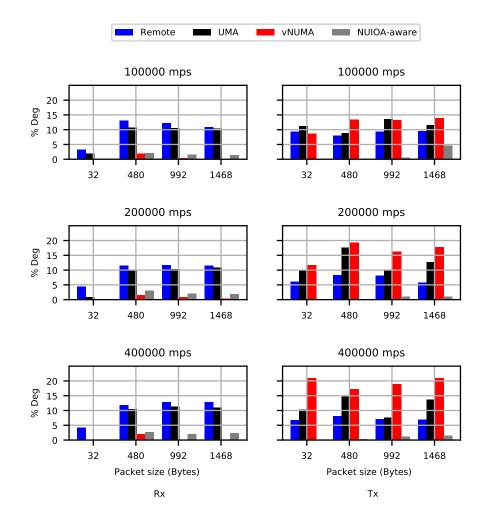

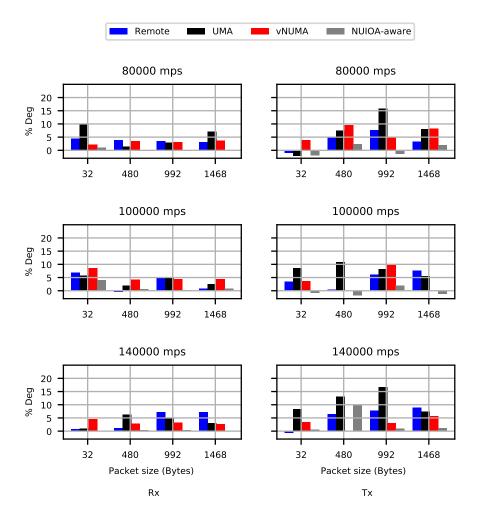

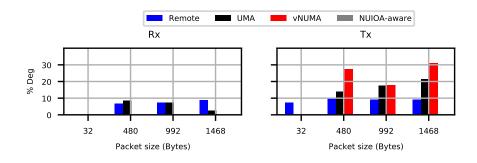

Secondly, we investigate the impact of virtualized I/O on NUMA architectures. As I/O devices are typically connected to one particular NUMA node, this leads to a situation where device access on one node is faster than another. This phenomenon is called *non-uniform I/O access* (NUIOA). This non-uniformity impacts the performance of I/O applications that are not executed on the correct NUMA node. Our contribution in this chapter is twofold: (1) we thoroughly study the impact of NUIOA on application performance in VMs; and (2) we propose a VM resource allocation strategy that reduces the impact of NUIOA by splitting home node resources across all VMs. We implement our allocation strategy on the Xen hypervisor and carry out evaluations with well-known benchmarks to validate our strategy. The obtained results show that with our NUIOA allocation scheme, we can improve the performance of application in VMs by up to 20% compared to common allocation strategies.

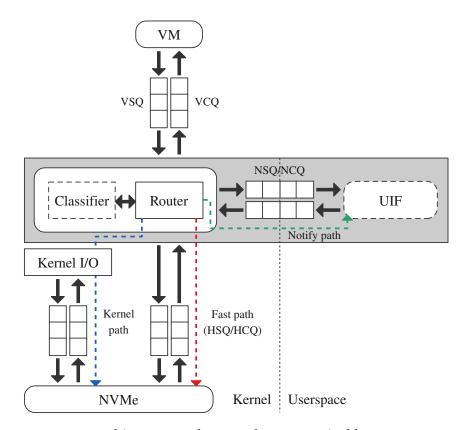

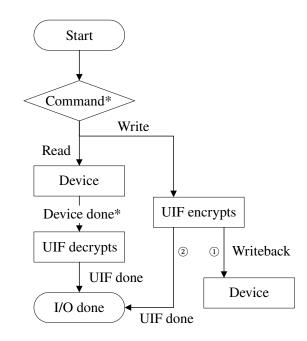

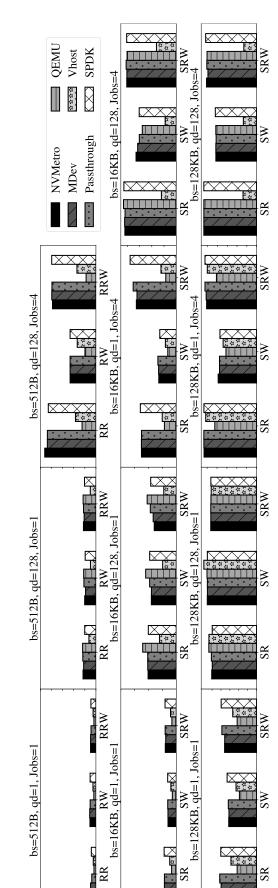

With our third idea, we first observe that existing storage virtualization tools either depend on a heavy and inefficient I/O stack that is not optimized for parallelism, or require a separate API that is difficult to manage and monitor. We introduce *NVMetro*, a

solution based on the NVMe protocol that proposes a flexible choice between multiple I/O paths to ease the development of adaptive and performant virtual storage. NVMetro provides two components: (1) an intelligent I/O classification and routing framework powered by Linux's *Extended Berkeley Packet Filter* (eBPF); and (2) an easy-to-use and performant API to assist the creation of *userspace I/O functions* (UIFs) within our framework. We demonstrate the benefits of NVMetro by implementing two virtual storage functions, and we evaluate them using various benchmarks. The obtained results show that NVMetro achieves a performance and scalability comparable to bleeding-edge, kernel-bypass technologies while retaining the flexibility of traditional OS-based storage APIs.

## 1.4 Structure of this thesis

In Chapter 2, we introduce the various aspects of platform virtualization, including the components of a virtual machine, their implementation in modern hypervisors, and the various tradeoffs of different VM platforms. We also investigate the NVM Express specification and Linux's eBPF engine, important components of high-performance I/O stacks. In Chapter 3, we present HyperTP through the lens of our hypervisor transplant concept, with detailed descriptions of its design and implementation, as well as relevant discussions of its security and performance properties. Chapter 4 evaluates I/O workloads under multiple scenarios to provide our observations on the effects of NUIOA on VM performance and to offer a strategy for improving performance in these scenarios. In Chapter 5, we present NVMetro from its design criteria, describe and evaluate several relevant use cases, and compare our solution to competing ones. Finally, Chapter 6 summarizes Walk-In's common theme of *flexibility*, while giving perspectives about future works.

## **Chapter 2**

## Context

#### Contents

| 2.1 | The various facets of virtualization |                                                |    |  |  |  |

|-----|--------------------------------------|------------------------------------------------|----|--|--|--|

| 2.2 | Inside                               | platform virtualization                        | 6  |  |  |  |

|     | 2.2.1                                | Mechanisms of machine component virtualization | 7  |  |  |  |

|     | 2.2.2                                | Virtualization of the x86 architecture         | 8  |  |  |  |

|     | 2.2.3                                | Memory virtualization                          | 8  |  |  |  |

|     | 2.2.4                                | Virtualization of I/O devices                  | 9  |  |  |  |

|     | 2.2.5                                | Virtualizing signal delivery                   | 10 |  |  |  |

|     | 2.2.6                                | Managing virtual machine states                | 11 |  |  |  |

| 2.3 | NUMA                                 | and I/O virtualization                         | 12 |  |  |  |

| 2.4 | The N                                | VM Express specification                       | 13 |  |  |  |

| 2.5 | Linux'                               | 's eBPF engine                                 | 14 |  |  |  |

## 2.1 The various facets of virtualization

As stated in Chapter 1, virtualization aims to partition a *physical resource* into one or more instances of a corresponding *virtual resource*. To further clarify this concept, we provide below a list of virtual resources commonly available in modern software architectures:

Virtual memory serves as the main backing principle of OS processes. With virtual

memory, each process gains a separate view of its own memory, isolated from

other processes on the same system. Virtual memory functionalities are backed

by memory management units available on modern CPUs, which translate virtual

addresses belonging to different virtual address spaces into physical addresses for

accessing main memory and I/O devices.

- *Virtual machines* (VMs) supply an operating system environment that acts like a physical computer, complete with virtual CPUs, memory, I/O, and so on. Managed by a *virtual machine monitor* (VMM) or *hypervisor*, VMs provide a robust isolation of workloads and administrative duties. Thanks to a familiar and diverse choice of guest operating systems, VMs form one of cloud computing's core offerings, *infrastructure-as-a-service* (IaaS).

- *Containers* are a partitioning of OS resources (processes, filesystems, network devices) into separate domains. Containers are managed by a *container runtime*, and may be backed by a single OS (e.g. Linux, using its various namespaces and control group features) or by separate VMs. Developers create containers from self-contained bundles of applications and their dependencies called *container images*. Container platforms such as Docker and Kata Containers have attracted significant interest in recent years due to their low overhead and high deployment consistency.

## 2.2 Inside platform virtualization

*Platform virtualization* refers to the process where *hypervisors* partition a *host* machine to provide an isolated *virtual machine* environment for *guest operating systems*. According to Popek and Goldberg, such an environment invokes the following properties: efficiency, where unprivileged instructions are executed without interception; resource control, where the hypervisor retains complete control over any resources granted to the VM; and equivalence, where the guest software can access resources in the same way as software running on unvirtualized hardware [14].

This thesis focuses specifically on virtual machines and their implementations in common hypervisors (KVM, Xen) on the x86 architecture. To this end, we first break down a virtual machine environment into its components:

- *Virtual CPUs* (vCPUs), which present the guest OS and applications with an execution context. Each vCPU possesses its own states, such as registers, interrupts, execution modes, and so on.

- *VM memory*, in the form of a separate guest physical address space. Like in a physical machine, VM physical addresses can be mapped to main memory or a so-called *memory-mapped I/O device*.

- Various *virtual devices* that provide I/O services to the VM. We consider two classes of virtual devices: critical *platform devices* necessary for a VM's operation, and *bulk I/O devices* that supply the VM with storage, networking, etc. Under our definition, vCPUs are naturally considered a type of virtual device.

The next sections present individual elements of platform virtualization for each of the aforementioned components.

#### 2.2.1 Mechanisms of machine component virtualization

VM components are commonly virtualized in one of three ways: **trap-and-emulate**, where sensitive operations within the guest are intercepted by hardware, then the hypervisor alters the VM's state accordingly; **binary translation**, where the guest software is broken down into its component executable instructions, and any sensitive instructions within the guest program are replaced with innocuous ones that replicate their effects within the VM's context; and **hardware-assisted virtualization**, where a commonly-used resource (vCPU, VM memory) is exposed directly by hardware in an efficient fashion.

Each virtualization method listed above has its own advantages and disadvantages. For example, hardware-assisted virtualization brings the best performance but obviously requires support from the underlying hardware. In contrast, binary translation and trapand-emulate often come with a significant overhead, especially for high-performance bulk I/O devices such as storage and networking. To mitigate this shortcoming, modern hypervisors optimize virtual I/O by providing a VM-specific I/O interface via special instructions and protocols in a process called *paravirtualization* [15, 16].

Common VM platforms such as KVM and Xen consist of two components: a *hypervisor kernel* that runs at the highest privilege level and provides virtualization primitives; as well as a *deprivileged VMM* (e.g. QEMU, kvmtool, Firecracker) that uses the hypervisor kernel's API to manage VMs and grant them access to resources.<sup>1</sup> This kernel/user split implies a tradeoff between security and performance. To elaborate, such a separation minimizes a VM platform's attack surface by running most of its code in an unprivileged, sandboxable mode subject to the operating system's controls. At the same time, signaling code paths between the VM and virtual device provider become much slower. Events coming from the VM (e.g. control register writes, I/O accesses) must pass through the hypervisor kernel before being relayed to the VMM. Conversely, in order to signal the VM with an interrupt, the VMM must request the hypervisor kernel via a system call [12]. For this reason, hypervisors often directly virtualize performance-critical devices (e.g. interrupt controllers). The component split is also configurable depending on security requirements, where in-kernel virtual devices can be disabled and replaced with VMM-based ones in sensitive environments [17].

Goldberg categorized hypervisors into two types: *type-1 hypervisors* and *type-2 hypervisors* [18]. Type-1 hypervisors (e.g. Xen, Hyper-V) run directly on a physical machine and take full control of its hardware. Type-2 hypervisors (e.g. KVM, VirtualBox) instead work as a component of the host OS. The two types of hypervisors differ in implementation. Under a type-1 hypervisor, system resources (memory, scheduling, device access) are controlled by the hypervisor, and the host OS runs in virtualized mode. In contrast, with a type-2 hypervisor, the host OS runs in unvirtualized mode and retains control over resource allocation, while providing these services to the hypervisor.

<sup>&</sup>lt;sup>1</sup>In this thesis, we use the term *[userspace] VMM* to refer to the deprivileged component of a virtual machine platform. Conversely, the privileged component is called the *hypervisor [kernel]*.

#### 2.2.2 Virtualization of the x86 architecture

The x86 architecture was not designed for virtualization at the outset and presented significant challenges to virtualization, as it presented several virtualization-sensitive instructions that were also unprivileged, and thus not intercepted by hardware [19]. Initial attempts at x86 virtualization found in VMware and QEMU used a binary translation approach to emulate sensitive instructions in software [19, 20, 21]. However, such an approach remain slow, with the VMM having to handle numerous potential issues [22].

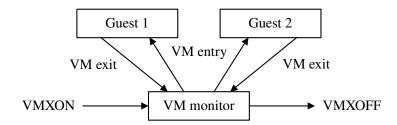

Intel patched the virtualization gap of x86 in introducing their VT-x virtualization technology [22], which introduces separate host (*VMX root*) and guest (*VMX non-root*) execution modes. Each vCPU in VMX non-root mode is associated with a VM control structure (VMCS) containing its state, and which the host can manipulate using VMREAD and VMWRITE instructions. From VMX root mode, the host executes a guest vCPU through a *VM entry* operation, which puts the corresponding physical CPU in non-root mode. Subsequently, any sensitive instruction executed by the guest either directly manipulates the guest state without affecting the host, or causes a *VM exit* that notifies the host of such an event. Figure 2.1 illustrates the various execution modes provided by VT-x [23].

Figure 2.1: Interaction of a VMM and guests [23].

#### 2.2.3 Memory virtualization

Prior to specific memory virtualization capabilities in hardware, x86 memory virtualization is performed through the *shadow paging* technique. In summary, for each process in the guest VM associated with a guest page table (GPT), the hypervisor creates a *shadow page table* (SPT) which translates virtual addresses of said process to host physical addresses. The hypervisor retains exclusive control over address translation by intercepting all memory management operations (CR3 register, TLB flushes). It also intercepts writes to guest page tables and updates the corresponding SPTs in parallel. Upon an attempted task switch from the guest, the hypervisor substitutes the correct SPT. These interceptions cause an execution overhead during these operations, especially with e.g. task creations which heavily involve page table manipulations. Xen improved upon shadow paging by introducing a paravirtualized interface that batches page table updates [16]; however, this paravirtualization does not totally eliminate the overhead of shadow paging. Bhargava et al. [24] introduced *nested paging* as part of AMD's AMD-V virtualization technology to reduce the overhead of memory virtualization. With this technology, hypervisors create *nested page tables* (NPT) associated to a VM control block (AMD-V's equivalent of VT-x's VMCS). These NPTs transparently translate from guest physical addresses to host physical addresses during guest execution, while letting guests manage their own GPTs without hypervisor interception. However, nested paging causes an overhead in memory accesses due to needing two levels of address translation. This particular overhead of nested paging has been explored in previous works [25, 26]. To compensate, huge pages can be used to reduce the overhead of nested paging by reducing the total number of translation levels, as well as the TLB space needed for caching translations.

Table 2.1 summarizes the behaviors of guest operations for each memory virtualization method.

| G: guest        | VA: virtual address                              | Green :  | optima  | l performance    |

|-----------------|--------------------------------------------------|----------|---------|------------------|

| H: host         | PA: physical address                             | Yellow : | scope f | or improvement   |

| S : shadow      | PT: page table                                   | Red :    | poor pe | erformance       |

| N: nested       |                                                  |          |         |                  |

| Method          | Memory accesses                                  | GPT      | Г edits | Context switches |

| Shadow paging   | $\text{GVA} \xrightarrow{\text{SPT}} \text{HPA}$ | Tra      | р       | Trap             |

| Paravirtualized | $\text{GVA} \xrightarrow{\text{SPT}} \text{HPA}$ | Bate     | ched    | PV SPT switch    |

|                 |                                                  |          |         |                  |

Table 2.1: Summary of memory virtualization behaviors per guest operation.

#### 2.2.4 Virtualization of I/O devices

Virtual I/O devices are commonly exposed to the VM using one of the following methods:

- *Emulation*, where the VMM mimics the behavior of a real I/O device, e.g. *Intel* 82574L GbE Controller, Realtek RTL8139 (networking); LSI MegaRAID SAS 1078, SiI3112A PCI to Serial ATA Controller (storage).<sup>2</sup> Emulated devices often have low performance, since each I/O operation requires several MMIO accesses, each of which must be intercepted by the hypervisor and sent to the VMM.

- *In-VMM paravirtualization*, where the I/O device protocol exposed by the VMM is VM-specific (e.g. by following the *Virtio* specification [27]). The guest OS must contain the appropriate drivers for these protocols.

- *In-hypervisor paravirtualization*, where the hypervisor kernel itself emulates the virtual device instead of the deprivileged VMM. For example, Linux provides *Vhost* modules that implement Virtio network and storage devices directly inside the kernel for better I/O performance.

<sup>&</sup>lt;sup>2</sup>Virtual device examples provided by QEMU 6.2.

• *Device passthrough*, where an entire physical device is assigned to a VM. As physical devices have access to the system's memory via DMA, their access is often guarded with a *I/O memory management unit* (IOMMU), which constrains their memory access via a virtual input/output address space. Linux provides device passthrough facilities through its *Virtual Function I/O* (VFIO) framework.

As an example, Table 2.2 presents Gregg's [28] breakdown of virtualization methods found in the Xen hypervisor, categorized by the virtual device type.

Table 2.2: Spectrum of virtualization modes in the Xen hypervisor [28].

| <ul><li>P : paravirtualized</li><li>VS : virtualized in software</li><li>VH: virtualized in hardware</li></ul> |      |             | Tellow             | : optim<br>: scope<br>: poor j         | for ir                | nprove                    | ment |

|----------------------------------------------------------------------------------------------------------------|------|-------------|--------------------|----------------------------------------|-----------------------|---------------------------|------|

| Туре                                                                                                           | Mode | With        | Dick and motionals | Disk and network<br>Interrupts, timers | Emul. MB, legacy boot | Priv. instr., page tables |      |

| Fully virtualized                                                                                              | HVM  |             | V                  | S VS                                   | VS                    | VH                        |      |

| Hybrid, Xen 3.0                                                                                                | HVM  | PV drivers  | F                  | <b>v</b> VS                            | VS                    | VH                        |      |

| Hybrid, Xen 4.0.1                                                                                              | HVM  | PVHVM drive | ers <b>F</b>       | P P                                    | VS                    | VH                        |      |

| Hybrid, Xen 4.4                                                                                                | PV   | HVM ("PVH"  | ') I               | P P                                    | Р                     | VH                        |      |

| Fully paravirtualized                                                                                          | PV   |             | F                  | P P                                    | Р                     | Р                         |      |

A common pattern of I/O protocols is shared memory-based communication. This pattern is used in e.g. Xen PV, Virtio and the NVMe protocol, and consists of two parts: a shared memory buffer, often in the form of a producer/consumer ring; and two-way signal delivery mechanisms between the VMM and guest. I/O requests from one side (e.g. the guest sending a packet) are accomplished by first populating a ring entry with data pointers, then sending a signal to inform the other party of the update in ring status.

### 2.2.5 Virtualizing signal delivery

As mentioned above, for virtualized I/O protocols to function, the VMM must provide VMs with signal delivery in the form of interrupts: timer, device, interprocessor (IPI), etc. Similar to any other devices, interrupt controllers are exposed to the VM in several ways:

• *Emulation:* where a well-known hardware interrupt controller is mimicked in software (e.g. the Intel 8259 PIC);

- *Paravirtualization:* Since efficient interrupt virtualization is crucial to virtual I/O performance, VMMs often provide a paravirtualized interrupt interface with a lower overhead. Namely, Xen and Hyper-V both propose their own paravirtual interrupt mechanism configured via hypercalls. Newer hardware interrupt controller specifications (e.g. x2APIC) are designed to be simpler and more efficient to emulate, and its implementations can perform as well as paravirtualized interrupt controllers.

- *Hardware-assisted:* Newer CPUs from Intel and AMD provide explicit support for virtualizing interrupt controllers as part of their hardware virtualization technologies. These include automatic emulation of several virtual interrupt types (timers, IPIs); emulation of interrupt controller registers; *posted interrupts* for direct delivery of interrupts to vCPUs without VM exits; and the related *interrupt remapping* for delivery of interrupts originating from hardware.

#### 2.2.6 Managing virtual machine states

As part of virtual machine management tasks, VMMs provide various methods for controlling their execution states. Besides the basic start/stop and pause/resume, the following operations are commonly provided:

- *VM state dumping and loading*. With this operation, the VM's running states (CPU registers, memory contents, device states) are dumped to stable storage as a save file with a well-defined format. This save file can later be used to reconstruct the running VM.

- *VM live migration*. This operation moves a running VM from one host to a second host with minimal downtime. Based on the same principles as VM state dumping, live migration is often implemented in one of two ways:

- *Pre-copy migration:* VM memory is copied to the second host in the background without pausing the VM. Once enough of the memory contents have been copied, the VM is paused and the remaining states are transferred over so that the VM could be resumed in the second host. Since the VM keeps running in the original host during migration, any pages modified by the VM must be copied again, a lengthy process on busy VMs.

- Post-copy migration, where the VM is first transferred over to the second host, but at first without its memory. Any memory accesses will trap to the hypervisor, where it will force the memory pages in question to be copied over; the rest will be copied in background. Post-copy has the disadvantage of severely slowing down the VM during these page faults, as they involve network activity and multiple transfers of control between the VM, VMM and hypervisor.

- *VM snapshotting*. Using this operation, a VM's disk contents (and often its running states) are checkpointed into a stable on-disk snapshot. Any further changes

toward these states are redirected into a differential image. At any time, the VM's states can be rolled back to that of the snapshot.

### 2.3 NUMA and I/O virtualization

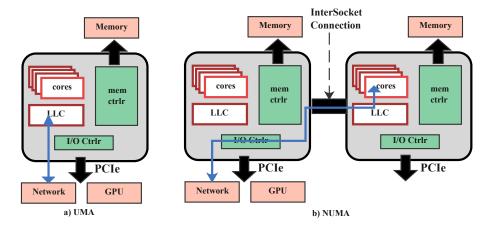

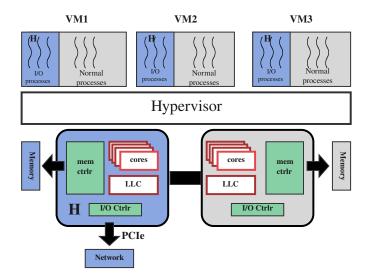

Figure 2.2: I/O in a server based on a (a) UMA (i.e. non-NUMA) architecture; (b) NUMA architecture.

As the demand for computing power increases, manufacturers aim to integrate more and ever faster CPU cores, memory, storage, networking etc. into their server products. Yet with CPUs increasing in speed and parallelism, it becomes more difficult to feed them with data. Signal path length becomes a significant concern, as data latencies are constrained by physical limitations of the hardware itself; hardware designers therefore need to limit the distances between CPUs, memory and peripheral devices.

On architectures where the processor is connected to devices using a single bus link (which is often the case for single-socket systems with uniform memory access, UMA), all CPU cores share the same I/O path to a certain device (blue arrow on Figure 2.2a). However, with ever-increasing demands for processing power and hosting density, current servers can come with multiple processors, each with its own CPU cores, memory hierarchy and I/O link organized as an independent node (see Figure 2.2b). These nodes are then linked with a fast *interconnect*, which can be PCIe itself or a proprietary interconnect (e.g. Intel UPI).

This independent node architecture is often called *non-uniform memory access* (NUMA), but its implications extend beyond memory access, as we will demonstrate below. I/O devices such as network cards and storage drives are most of the time furnished with a single PCIe link, and as a result each device is affiliated with a single NUMA node, which we call the *home node* of that device. It follows that any communications (e.g. register writes, interrupts, DMA operations) between a device and a node that is not its home node (or *remote node* for short) would suffer extra overhead, due to them needing to cross the NUMA interconnect between nodes. This situation is called *non-uniform I/O access* (NUIOA) [29]. NUIOA not only affects I/O latency due to the longer signal path, but may also affect the maximum available I/O

bandwidth when the workload is constrained by interconnect bandwidth. Therefore, for I/O intensive workloads to achieve optimal performance under NUIOA architectures, the tasks performing I/O (in both kernel-mode and user-mode) need to be located on the corresponding device's home node (see Figure 2.2b).

**Locality of devices and virtualization.** With ever-increasing performance of I/O devices and system buses such as PCI Express, servers are often equipped with only a single device of each I/O type. In other words, each server would have one network adapter, one NVMe storage device, and so on. Thus, I/O application performance both inside and outside VMs depend on the locality of the application in regards to the device it interacts with. By default, hypervisors do not relocate applications depending on their NUIOA affinity, leading to wasted performance in case of applications that perform direct device I/O (e.g. userspace drivers, RDMA applications, etc.) Moreover, some current hypervisors like Xen do not expose device locality to guest OSes, therefore causing VMs to be unaware of this association and unable to make the appropriate scheduling decisions.

**NUMA in virtualization.** Hypervisors often use one of two approaches for handling VM resources on NUMA architectures: memory interleaving or vNUMA. Memory interleaving is the default allocation strategy on hypervisor such as Xen [10]. It consists of allocating the VM memory by regions of 1 GB with a round-robin algorithm on each NUMA node, then presenting a Uniform Memory Architecture (UMA) to the VM. vNUMA involves presenting to the VM a virtual NUMA topology which maps its resources to virtual NUMA nodes. It is supported by modern hypervisors such as Xen, VMware and Hyper-V. vNUMA can take advantage of existing operating systems' NUMA awareness to improve VM guests' CPU and memory allocation locality.

### 2.4 The NVM Express specification

The Non-Volatile Memory Express (NVMe) specification [30] has been widely adopted as a way to remedy I/O inefficiencies between the storage device and operating system. At the core of NVMe is the concept of I/O queues, where multiple independent storage operations can be performed simultaneously without the cost of synchronization. This highly-optimized design has massively benefited storage device and application scalability. Indeed, NVMe devices have managed to reach impressive performance figures; for example, the Intel Optane P5800X series claims a performance of up to 5 million I/O per second and a 99th percentile latency of less than 6  $\mu$ s [31].

To summarize, the NVMe specification defines a communication protocol between software (the "host") and storage devices (the "controllers"). It specifies an *admin command set* for the host to interrogate and manipulate the controller, and various other command sets for each individual use case: the *NVM command set* for traditional block devices; and the *NVMe-KV command set* for devices having a key-value interface instead of the traditional block device interface.

NVMe provides a generalized *command queue* abstraction regardless of command set. The host sends I/O commands to a controller via *submission queues* (SQs); the controller processes each command and puts its result into a corresponding *completion queue* (CQ). Aside from a dedicated SQ/CQ pair for admin commands, each NVMe controller can communicate with the host using up to 65535 queues, and each queue is further capable of containing up to 65535 commands being processed in parallel. Each queue is a lockless producer-consumer ring buffer; as such, each CPU can communicate with the controller using a dedicated queue, removing the need for synchronization between CPUs when submitting requests. In addition, NVMe allows a N-to-1 correlation between SQs and CQs; in other words, multiple SQs can be associated to the same CQ. The host can wait for completion notifications from a controller in two ways: it can either receive interrupts from the controller, or continuously poll its CQs for any new entries (called *busy polling*, a.k.a. *active polling*).

The NVMe specification allows the use of various transports over which I/O data can flow, such as a *memory transport* for devices attached to a system bus like PCIe, *message transport* over TCP or Fibre Channel, or a *RDMA-based transport* for high-speed remote storage over Infiniband or converged Ethernet. NVMe's support for multiple transports lets operating systems and applications use the same driver and software stack regardless of the underlying connection.

In summary, NVMe's scalable protocol and feature set enables countless new use cases: remote storage, intelligent tiering, key-value databases, etc. NVMe enjoys widespread support from numerous hardware and software vendors, and is poised to become a prominent all-purpose storage protocol.

### 2.5 Linux's eBPF engine

Berkeley Packet Filters (BPF) [32] was introduced in the BSD operating system for packet inspection, filtering and capturing. BPF makes use of *BPF filters* written in a virtual machine-based language that lets one filter program process multiple protocols at different network layers. Linux originally adopted BPF for the same purpose in its socket filter [33].

The BPF instruction set was extended in Linux into *Extended BPF* (eBPF) with extra instructions and registers. Before running each eBPF program, the Linux kernel verifies its safety through a large range of properties, including constraints on memory accesses, loops and program size. eBPF programs can call a list of authorized kernel helper functions; however, this approach requires recompiling and reinitializing the eBPF verifier every time a new helper function is needed. Linux eBPF is currently employed in various use cases, such as system call filtering (via the Seccomp-BPF API), kernel tracing, LSM security controls, or infrared signal decoding. Notably, its Express Data Path (XDP) feature executes eBPF programs at the earliest points of network packet reception, such as in the network driver or directly inside SmartNIC hardware for the purposes of packet classification and routing [34].

## **Chapter 3**

# HyperTP: A unified approach for live hypervisor replacement

#### Contents

| 3.1 | Overv         | iew                                                 | 16 |  |  |  |

|-----|---------------|-----------------------------------------------------|----|--|--|--|

| 3.2 | Desig         | n of HyperTP                                        | 18 |  |  |  |

|     | 3.2.1         | Principles                                          | 18 |  |  |  |

|     | 3.2.2         | In-place hypervisor transplant                      | 20 |  |  |  |

|     | 3.2.3         | Migration-based hypervisor transplant               | 21 |  |  |  |

|     | 3.2.4         | Using hypervisor transplant in a datacenter         | 21 |  |  |  |

| 3.3 | Proto         | type                                                | 23 |  |  |  |

|     | 3.3.1         | UISR and device management                          | 24 |  |  |  |

|     | 3.3.2         | Implementing InPlaceTP                              | 25 |  |  |  |

|     | 3.3.3         | Implementing MigrationTP Xen-to-KVM transplantation | 28 |  |  |  |

| 3.4 | Evalua        | ation                                               | 29 |  |  |  |

|     | 3.4.1         | Experimental setup                                  | 29 |  |  |  |

|     | 3.4.2         | Time breakdown                                      | 30 |  |  |  |

|     | 3.4.3         | Impact on applications                              | 34 |  |  |  |

|     | 3.4.4         | Hypervisor update                                   | 38 |  |  |  |

|     | 3.4.5         | Hypervisor security                                 | 39 |  |  |  |

|     | 3.4.6         | Memory overhead                                     | 39 |  |  |  |

| 3.5 | Discus        | ssion                                               | 40 |  |  |  |

| 3.6 | Related works |                                                     |    |  |  |  |

|     | 3.6.1         | Hypervisor update                                   | 41 |  |  |  |

|     | 3.6.2         | Hypervisor security                                 | 42 |  |  |  |

| 3.7 | Summ          | nary                                                | 43 |  |  |  |

### 3.1 Overview

Chapter 1 showed that the increasing usage of virtualization in modern datacenters is accompanied with a simultaneous increase in the need for regular preventative maintenance and updating of hypervisors and related software. Hypervisor updates are often done for one of two reasons: either for introducing new features, or to mitigate a certain vulnerability. These updates involve one of several methods: (1) a full reboot of the host and all running guests; (2) live migration of running VMs from a host running old versions of the hypervisor to another host running updated software; and (3) live patching of the running hypervisor. Each method has its own set of limitations: full reboots are highly disruptive to the infrastructure's operations; live migration consumes large amounts of time and network bandwidth, and prevents the usage of certain virtualization features; live patching is limited to small fixes, mostly of security issues, and requires extra development effort to create a customized livepatch for each fix, as automated patch generation does not guarantee that a patch is safe to apply [35, 36]. Therefore, there remains a need for a timely and efficient hypervisor maintenance system capable of delivering both feature and security updates without causing service disruption or restricting desirable features.

To address this need, we introduce the concept of *hypervisor transplant*. Our goal is to quickly replace one running hypervisor  $H_{\text{current}}$  with another  $H_{\text{target}}$  without rebooting running VMs for the purpose of speeding up preventative maintenance of virtualization infrastructure. Note that  $H_{\text{target}}$  can be anything from an updated version of  $H_{\text{current}}$  to a completely different hypervisor, allowing more flexibility in choosing an appropriate hypervisor for the required workload.

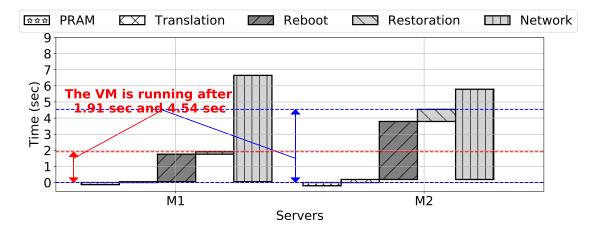

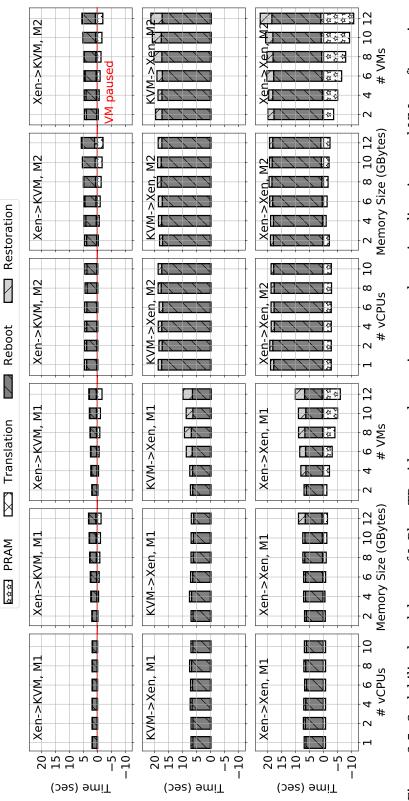

We materialized our concept of hypervisor transplant in a platform called *HyperTP*, which combines in a unified way two complementary approaches: *in-place micro-reboot-based transplant* (noted InPlaceTP) which replaces a running hypervisor with little downtime and no extra resources, and *live VM migration-based transplant* (noted MigrationTP) which causes almost no VM downtime. The combination of these two approaches answers the constraints put on both applications running in VMs and on datacenter infrastructures.

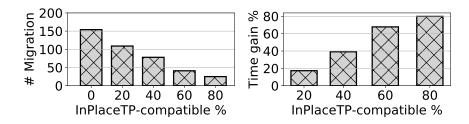

Indeed, InPlaceTP and MigrationTP present a tradeoff between maintenance deadline, downtime tolerance and upgrade resource availability. For instance, InPlaceTP's micro-reboot-based transplant requires several seconds of downtime. However, such downtime figures are not without precedent. Namely, Microsoft Azure presents downtimes of up to 30 seconds for maintenance operations [37]. Orthus [9] reports figures of up to 9.8 seconds for VMM upgrades. Similarly, Hy-FiX [38] requires 8.1 to 12.3 seconds of downtime for the same task. In exchange for an extended downtime, In-PlaceTP, by its in-place nature, does not require large amounts of extra resources and significantly shortens the maintenance timeframe. In comparison, MigrationTP causes minimal downtime to running VMs but with the additional cost of spare machines and network bandwidth, like other live-migration-based maintenance operations [9]. In the current state of HyperTP, it is up to the datacenter operator to decide which transplant approach is the most appropriate for their maintenance operation, since equivalent policies are already provided for dealing with periodic platform updates.

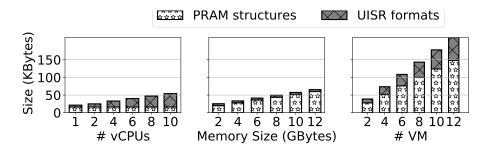

While live migration and micro-reboot are known approaches, the main novelty in designing HyperTP is to ease the support of *multiple different hypervisors*. Naturally, this raises the question of managing the heterogeneity of their VM state representations. To resolve this, we build both approaches of HyperTP around two common principles, a *VM state hierarchy* which identifies and defines the various types of memory states in relation to their functionalities relative to a VM's operation, and an *Unified Intermediate State Representation* (UISR) to facilitate the creation of HyperTP-compatible hypervisors.

We demonstrated our platform by re-engineering Xen and KVM, the two most popular open source hypervisors, into HyperTP-compliant hypervisors. They represent the two types of hypervisors: type-1 (Xen) and type-2 (KVM), thus demonstrating the scope and flexibility of our solution. We evaluated our prototype at a machine scale to validate its ability to transplant both idle VMs as well as active VMs running various types of benchmarks. We also presented the downtime incurred by HyperTP while running various workloads such as SPEC CPU 2017, MySQL and Redis.

We investigated the usage of HyperTP at a cluster scale in a datacenter. We highlighted two direct usages of the platform: for *hypervisor updating*, where HyperTP shortens the time and reduces the resources needed to apply a new hypervisor version; and for *hypervisor security*, where HyperTP helps reduce the time window where a virtualized infrastructure is exposed to known vulnerabilities.

To summarize, in this chapter, we present the following contributions:

- We present HyperTP, a two-pronged solution including MigrationTP and In-PlaceTP to help simplify hypervisor updates and maintain hypervisor security.

- We implement HyperTP in multiple directions: Xen→KVM, KVM→Xen, and Xen→Xen, thus demonstrating HyperTP's scope and flexibility.

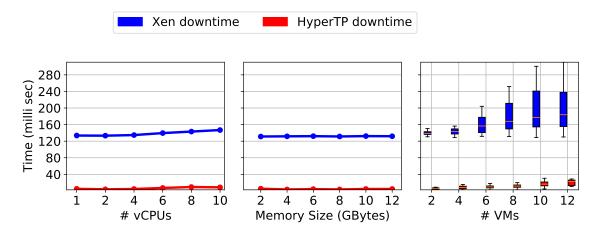

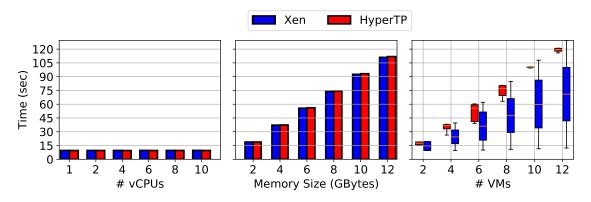

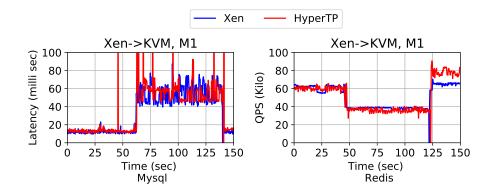

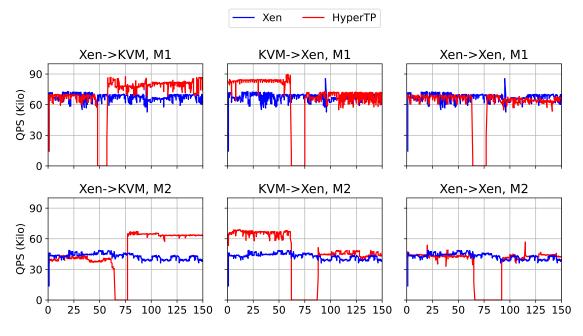

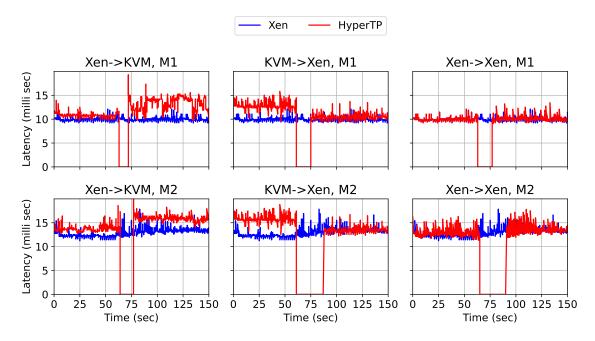

- InPlaceTP Xen→KVM causes minimal downtime to running VMs (1.91 seconds for a VM with 1 vCPU and 1 GB of RAM), with negligible memory and I/O overhead and without requiring VM reboots. With KVM→Xen and Xen→Xen, the downtime is about 7.8 seconds for the same VM configuration. MigrationTP offers similar performance to traditional homogeneous VM live migration.

- We show the benefits of InPlaceTP over migration-based solutions for upgrading an existing virtualization cluster. Namely, we demonstrate that upgrading 10 servers each running 10 VMs using InPlaceTP for 80% of the VMs takes 3 minutes and 54 seconds while using MigrationTP alone would take up to 19 minutes.

- We conduct a study of vulnerabilities in Xen and KVM over the last 7 years. We observe that most vulnerabilities are specific to a single hypervisor and caused by faulty implementations, and show how HyperTP can be used to reduce vulnerability windows of virtualized infrastructures.

The rest of the chapter is organized as follows. Section 3.2 present the general overview of HyperTP. Section 3.3 presents the implementation of HyperTP. Section 3.4

presents the evaluation results, followed by Section 3.5 which discusses the limitations of our approach. Section 3.6 discusses the related works. Finally, Section 3.7 concludes this chapter.

## 3.2 Design of HyperTP

In this section, we first present the two main principles of the design of HyperTP, *VM* state hierarchy and *Unified Intermediate State Representation*. We then show how these principles are applied to InPlaceTP and MigrationTP, and demonstrate their application in our aforementioned use cases.

### 3.2.1 Principles

To reiterate, the main goal of HyperTP is to rehost a VM running on one hypervisor to another hypervisor without causing a VM reboot. Let us note  $H_{\text{current}}$  and  $H_{\text{target}}$  as the current and target hypervisors of the transplant process respectively. A hypervisor transplant is conducted by performing the following five generic work items:

- 1. Suspend running VMs;

- 2. Translate VM states into the UISR neutral format;

- 3. Transfer VM states to the new target hypervisor;

- 4. Restore VM states from UISR to  $H_{target}$  format;

- 5. Resume VMs and finish the transplant operation.

Note that the aforementioned workflow is not meant to be taken in strict sequence; we optimize the contents and ordering of this workflow depending on the scenario being executed (InPlaceTP or MigrationTP). These optimizations are described in the next sections of this chapter.

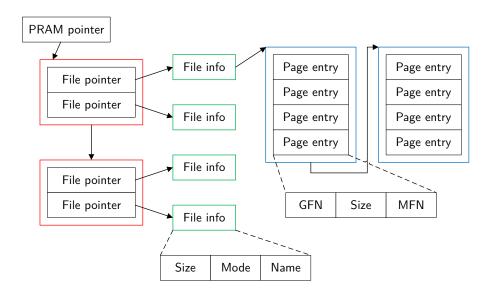

**VM state hierarchy.** Generally, we consider that the VMs' states include all the data structures in the hypervisor for the management of virtual resources (CPUs, memory, devices). Following Section 2.2, we observe that a VM's in-memory representation consists of multiple types of data, where each data type needs to be translated in a different way. For example, a guest memory page needs to be treated differently from a scheduling object associated to a vCPU. Nevertheless, different hypervisors running on the same platform typically aim to provide a common-ground virtual hardware that accomodates most guest OSes; not to mention, these hypervisors necessarily share some common behaviors by virtue of running on the same architecture. This implies *there exists a commonality between how different hypervisors manage their internal states*.

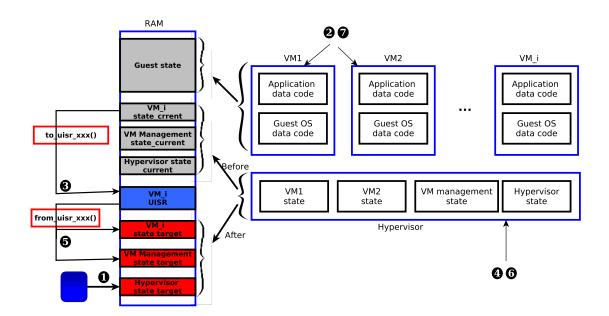

In HyperTP, we propose a hierarchy of memory resources in a VM, which serves to inform us of which kinds of data need to be kept as-is, transformed or discarded. Our resource hierarchy is divided into four main categories:

- *Guest State*, like its name, represents the memory states that are specific and visible to the VM, like memory pages. During transplantation, guest states require the least transformation, i.e. they can stay mostly untouched throughout the whole process.

- *VM<sub>i</sub> State* corresponds to data structures that are specific to the execution of one VM, but are not necessarily visible to the VM in their raw form. An example of *VM<sub>i</sub> State* are 2D page tables (2DPT) or vCPU register states. In fact, while the structure and content of the 2DPT is usually specific to the hardware virtualization technology being used (e.g. Intel's EPT, AMD's NPT), each hypervisor has its own policies for managing the 2DPT, and therefore the contents of each VM's 2DPT are not directly translatable between hypervisors. Similarly, while vCPU register states are closely linked to the vCPU's execution, each hypervisor saves a vCPU's states in its own different data structure, and therefore these states must be translated if a VM were to be transplanted between different hypervisors.

- *VM Management States* are in-memory states that serve to manage the VM, but do not necessarily contain the VM's state itself. For example, a hypervisor's scheduler queue might refer to a VM's vCPUs, but does not contain any vCPU states. In general, these states can be easily reconstructed if necessary from the previously-mentioned types of state.

- *HV State* finally represents the set of hypervisor states that are not specific to any VM, such as the memory assigned to hardware drivers. HyperTP does not save or transform these states; they are considered to be disposable (in the case of InPlaceTP, where they are reinitialized using micro-reboot) and/or reconstructable (in the case of MigrationTP, where the migration does not take them into account).

**Unified Intermediate State Representation.** From the hierarchy of VM states presented above, we observe that many types of VM states are at least partially specific to each hypervisor that is managing the VM. Yet, it is unreasonable to demand that all hypervisors use the same data structures for its functionalities in order to support hypervisor transplant, since such standardization not only limits the range of functionalities each hypervisor can potentially support, but also might introduce accidental common vulnerabilities.

To realize the concept of hypervisor transplant, we transform each VM's states into a UISR. UISR represents the hypervisor-dependent state of each VM with a hypervisorindependent intermediate representation that facilitates the transfer of VM states across different hypervisors. In this sense, UISR shares the same objectives as the networklevel neutral data representation XDR [39]. Relying on a neutral format simplifies the re-engineering of a hypervisors into a HyperTP-compliant one, since the hypervisor developer only has to understand the UISR format instead of the representation formats of all existing hypervisors. The goal of UISR is to sufficiently represent a VM for its reconstruction in a HyperTPcapable, compatible hypervisor. Following the VM state hierarchy presented above, we posit that *knowledge of* Guest State *and*  $VM_i$  State *is sufficient for the reconstruction of a* VM. These states are therefore the targets of our UISR. In general, the following VM states are collected by HyperTP and distilled into UISR: VM memory pages; CPU registers and control registers; interrupt controller and timer states; and virtual hardware states (including *hidden states* required to reconstitute the virtual device). However, we acknowledge that the above list is not an exhaustive list of all VM states; the restorability of VMs under HyperTP depends on the compatibility of their configuration and the UISR format.<sup>3</sup>

To transform a VM's states between its hypervisor-specific representation and UISR, each hypervisor needs to implement a pair of translation functions for each class of VM state. These functions can be as simple as the identity function for hypervisors that directly use UISR as their internal VM states, or an explicit translation from a hypervisor's internal state to the corresponding UISR. Nevertheless, knowing that hypervisors often share certain commonalities (as argued in the above section), we expect most hypervisors to be able to support UISR without needing extensive modifications.

#### 3.2.2 In-place hypervisor transplant

Figure 3.1: Basic workflow of InPlaceTP.

Figure 3.1 summarizes the working principles of InPlaceTP. In short, InPlaceTP performs a hypervisor transplant through the means of replacing the running hypervisor. To accomplish this, step **①** first loads the target hypervisor into memory. After pausing any running guest VMs to be transplanted **②**, we invoke the corresponding UISR

<sup>&</sup>lt;sup>3</sup>Note that this limitation is present in same-hypervisor live VM migration as well; current hypervisors prevent VMs using certain hardware features from being migrated.

translation functions to convert the corresponding  $Guest/VM_i$  States to the UISR format O. We perform a micro-reboot to hand over control of the hardware to  $H_{target}$  O, while passing to it any relevant UISR  $Guest/VM_i$  States.  $H_{target}$  then converts the received  $Guest/VM_i$  States into its own native format O, and uses these states to reconstruct the VMs O. Finally, the VMs to be transplanted are resumed O and the transplantation process is completed.

For the purpose of HyperTP, *Guest States* refer specifically to memory pages owned by the VM and used as its memory. These pages naturally do not require any specific transformation or rewriting to be converted into UISR. As long as these pages remain intact, they can be easily reincorporated into the new VM. That is why during the entire process, InPlaceTP ensures that these *Guest States* are protected from accidental deletion and corruption. The steps ③ and ⑤ in fact simply involve recording their location in the host's physical memory, and giving them back to the VM afterwards. This represents a large time saving for InPlaceTP as costly memory copies and disk writes are minimized.

#### 3.2.3 Migration-based hypervisor transplant

Under MigrationTP, the target of transplantation is no longer the current server, but rather a remote server, in the same way as normal VM live migration. As such, MigrationTP follows the same procedure as VM live migration, which largely matches up with HyperTP's own steps. The differences come during the sending of VM state to the destination server; during this step, MigrationTP makes use of *state proxies* to translate the VM's  $VM_i$  *States* into UISR. Note that these proxies are based on the same state transformations as used by InPlaceTP. On the destination server, another proxy then translates the UISR back into  $H_{target}$ 's VM state format. While *Guest States* need to be copied over network to the destination server unlike InPlaceTP, this copying step does not need to involve the state proxy.

#### 3.2.4 Using hypervisor transplant in a datacenter

In summary, HyperTP is a combination of two related approaches InPlaceTP and MigrationTP, based on a common UISR for the representation of VM states. In this section, we elaborate on the application of HyperTP to two exemplary use cases: firstly, for installing updates on virtualized infrastructure; and secondly, for the mitigation of hypervisor vulnerabilities.

**Hypervisor update.** As stated in Section 3.1, hypervisor updates are used not only to fix system bugs but also to deploy new software features. A public cloud provider might wish to quickly upgrade their hypervisor fleet to add new services and to increase feature velocity of their cloud solution; a private cloud customer might instead want to install a new hypervisor version to maintain software support, or to fix performance and reliability issues, etc. However, existing hypervisor update methods are either disruptive or limited in scope, causing risk-averse operators to hesitate applying updates.

In comparison, HyperTP offers datacenter operators rapid deployment of new software with InPlaceTP in complement with other upgrade choices (MigrationTP, normal migration or live patching). Additionally, InPlaceTP is not only capable of upgrading the current hypervisor core, but can even completely replace it with a different hypervisor altogether. This is especially useful e.g. in cases where the operator wishes to switch their hypervisor vendor, where the two different hypervisors can be managed using the same tooling (like OpenStack). In conclusion, HyperTP helps facilitate the deployment of desirable updates while minimizing their impact on the infrastructure.

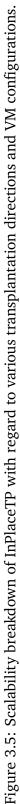

Figure 3.2: (a) Traditional vulnerability mitigation in data centers and (b) our hypervisor transplantation-based solution.

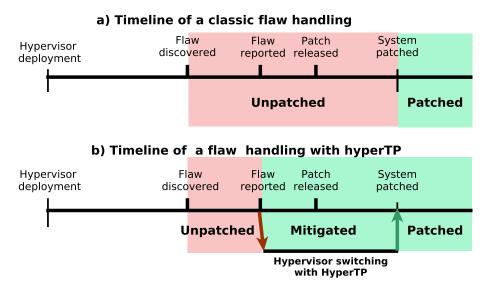

**Hypervisor security.** Hypervisors are continuously subject to multiple security vulnerabilities. Similar to previous works [40], we define the *hypervisor vulnerability window* regarding a given security flaw as the time between the identification of said flaw (whether by a good or bad actor) and the integration of a patch in the running hypervisor (see the red zone in Figure 3.2a). In fact, the vulnerability window is the sum of two durations: (1) the time required to propose a patch once the vulnerability is discovered; and (2) the time to apply this patch in the system. The time to release of a patch is highly dependent on the corresponding vulnerability's severity, and can vary from one week with vulnerabilities such as the MD5 collision attack [41], to 7 months with vulnerabilities such as Spectre and Meltdown [42, 43].<sup>4</sup> Meanwhile, the time to apply a patch mainly depends on the datacenter operators' patching policies. Together, this timeframe leaves plenty of time to launch an attack against a vulnerable installation.

To alleviate this issue, HyperTP can be used to preemptively and temporarily replace the actual datacenter hypervisor (e.g. Xen) with a different hypervisor (e.g. KVM) which is immune to the given vulnerability (see Figure 3.2b). This approach mitigates

<sup>&</sup>lt;sup>4</sup>Note that Spectre and Meltdown are CPU-specific vulnerabilities with CVEs declared on Intel products. Hypervisors and operating systems were not directly concerned by the CVE declaration.

the impact of a vulnerability given one of the following conditions is met: (1) there is already a known-safe hypervisor when the vulnerability is discovered, and (2) a patch solving the vulnerability can be developed in a shorter amount of time for an alternate hypervisor than the one used in the datacenter.

| Year  | Xen | KVM | Common |

|-------|-----|-----|--------|

| 2013  | 3   | 3   | 0      |

| 2014  | 4   | 1   | 0      |

| 2015  | 11  | 1   | 1      |

| 2016  | 6   | 3   | 0      |

| 2017  | 17  | 1   | 0      |

| 2018  | 7   | 2   | 0      |

| 2019  | 7   | 2   | 0      |

| Total | 55  | 13  | 1      |

|       |     |     |        |

Table 3.1: Number of Xen and KVM critical and medium vulnerabilities per year.

To investigate the viability of hypervisor transplant in this context, we collected a list of critical vulnerabilities over the last 7 years for Xen and KVM (see Table 3.1). A vulnerability is considered as critical when its Common Vulnerability Scoring System 2.0 score is higher than 7 [44]. Over that period, we found only one common critical vulnerability (CVE-2015-3456) originating from QEMU, a common component used by both Xen and KVM. This low number supports our starting assumption that a safe alternate hypervisor exists. Overall, the number of critical vulnerabilities per year remains low, which means that even if hypervisor transplant cannot be done too frequently, it would still bring an improvement in security.

# 3.3 Prototype

We implemented HyperTP on top of two commonly-used open-source hypervisors, Xen and Linux KVM. We used Xen 4.12.1 with fully-virtualized HVM domains; Xen PV was not used due to its tight coupling with the Xen API, which makes moving PV-based VMs away from Xen more difficult than moving HVM-based VMs. On the KVM side, we used Linux 5.3.1 along with the standalone kvmtool. We implemented InPlaceTP in three transplantation directions: Xen $\rightarrow$ KVM and KVM $\rightarrow$ Xen as examples of our heterogeneous hypervisor transplant; and finally Xen $\rightarrow$ Xen as an example for enabling live upgrade of Xen hypervisor instances. KVM $\rightarrow$ KVM InPlaceTP can be implemented with the same principles; however, we did not implement this scenario as it is already covered by existing works [9, 38]. MigrationTP was additionally implemented for the Xen $\rightarrow$ KVM direction. We configured our VMs to use remote storage to concentrate I/O activity onto virtual networking.

Our HyperTP prototype represents a total of approximately 8.5 KLOC, of which 2.2 KLOC belong to the hypervisors, 5.2 KLOC in userspace management tools (*libxl*, kvmtool and Kexec), and 1.1 KLOC for HyperTP orchestration purposes. We based our prototype mostly in userspace; in fact, only 10% of our implementation involves

Xen/Linux kernel code. Such a prototype takes advantage of existing tools and libraries for controlling VMs (*libxenctrl*, kvmtool), therefore being highly compatible with different versions of Xen and Linux/KVM. Our implementation of HyperTP also runs the bulk of its code with minimal privilege and only during the transplant process, thus minimizing HyperTP's security footprint.

In the following sections, we describe the common implementations of VM state management with UISR, as well as our implementations of InPlaceTP and MigrationTP in detail.

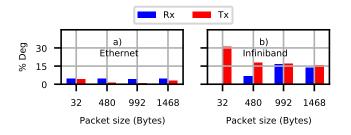

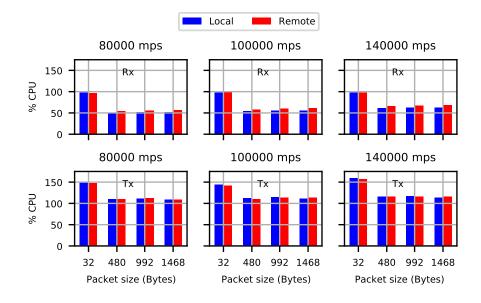

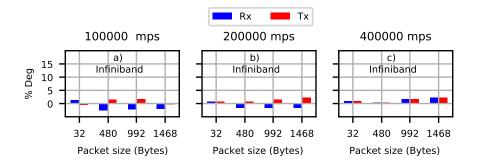

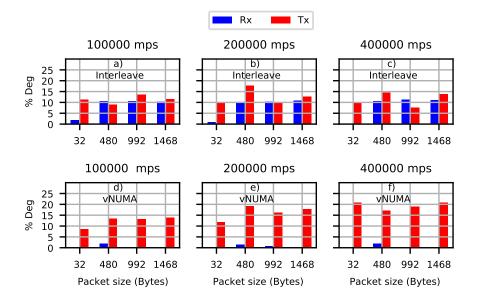

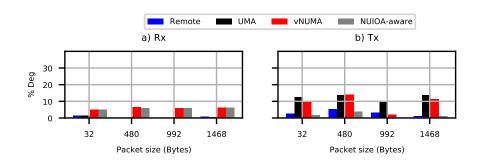

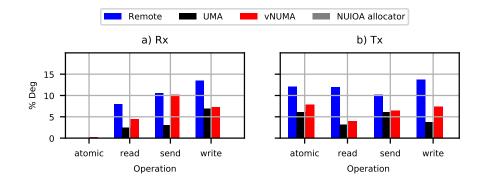

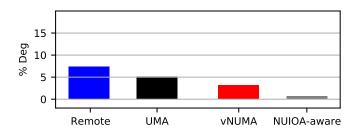

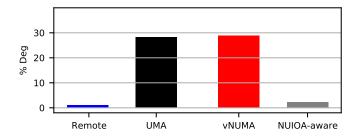

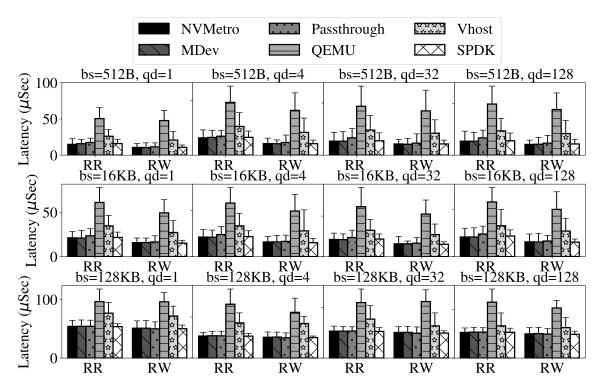

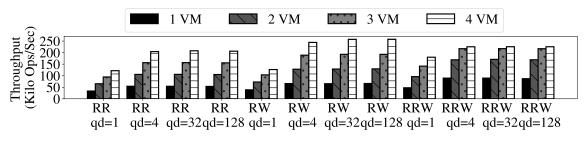

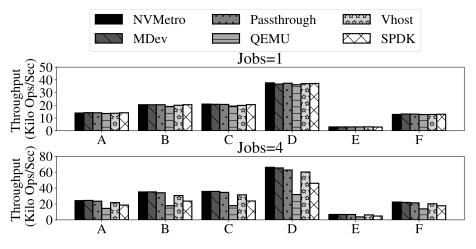

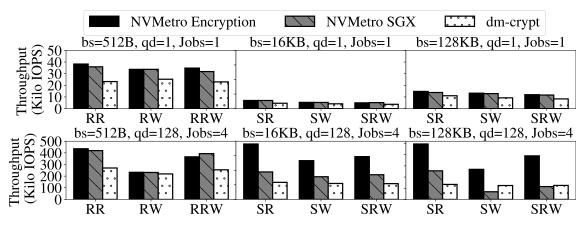

#### 3.3.1 UISR and device management