# Digital oscillatory neural network implementation on FPGA for edge artificial intelligence applications and learning

Madeleine Abernot

#### ▶ To cite this version:

Madeleine Abernot. Digital oscillatory neural network implementation on FPGA for edge artificial intelligence applications and learning. Artificial Intelligence [cs.AI]. Université de Montpellier, 2023. English. NNT: 2023UMONS074. tel-04587733

### HAL Id: tel-04587733 https://theses.hal.science/tel-04587733

Submitted on 24 May 2024

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### THÈSE POUR OBTENIR LE GRADE DE DOCTEUR DE L'UNIVERSITE DE MONTPELLIER

En Systèmes Automatiques et Microélectroniques

École doctorale : Information, Structures, Systèmes

Unité de recherche UMR5506

# Digital oscillatory neural network implementation on FPGA for edge applications and learning

### Présentée par Madeleine Abernot Le 18 Décembre 2023

# Sous la direction de Aida Todri-Sanial et Nadine Azemard-Crestani

#### Devant le jury composé de

Haralampos Stratigopoulos, Directeur de recherche, LIP6, CNRS

Lorena Anghel, Professeur, Grenoble INP

Maria José Avedillo, Professeur, Institut de microélectronique de Séville

Gyorgy Csaba, Professeur, Université catholique Pazmany Peter

Nadine Azemard-Crestani, Chargé de recherche, LIRMM, CNRS

Sylvain Saighi, Professeur, IMS, Université de Bordeaux

Catherine D. Schuman, Maître de conférence, Université de Tennessee

Aida Todri-Sanial, Professeur, Université technologique de Eindhoven

Théophile Gonos, Président, A.I.Mergence

Président du jury

Examinateur

Examinateur

Examinateur

Co-directrice de thèse

Rapporteur

Rapporteur

Directrice de thèse

Invité

# Digital oscillatory neural network implementation on FPGA for edge applications and learning

### Madeleine Abernot

Supervized by:

### Aida Todri-Sanial Nadine Azemard-Crestani

A thesis submitted in fulfillment of the requirements for the degree of Doctor of Philosophy in the

SYAM - I2S

### **ACKNOWLEDGEMENTS**

This thesis would never have been completed without the contribution of many entities.

I would like to first thank my advisors, Aida Todri-Sanial and Nadine Azémard-Crestani for your support and encouragement along the journey. A particular thanks to Aida, who followed me patiently from the beginning and always motivated me to become a better researcher, teaching me scientific, management, and communication skills.

I would like to express my gratitude to my thesis committee, Pr. Sylvain Saïghi, Dr. Catherine D. Schuman, Pr. Lorena Anghel, Pr. María José Avedillo, Dr. Haralampos Stratigopoulos, Pr. Gyorgy Csaba, and Dr. Théophile Gonos for your engagement, time, and insightful comments.

A special thanks to my colleagues from the NeurONN project, in particular Manuel Jimenez, Dr. Juan Nuñez, Pr. María José Avedillo, Sylvain Gauthier, Dr. Théophile Gonos, and Dr. Siegfried Karg. It has been a pleasure to learn and collaborate with you.

I am sincerely grateful to my excellent colleagues from the LIRMM. A major thanks to Thierry Gil who motivated me from the beginning of my Ph.D. journey, helped me build real demonstrators, and taught me rigor and method.

I thank my colleagues and friends in and around the corridor who have brightened my days for three years. Thank you Corentin Delacour for sharing this 3-year experience with me. I enjoyed working with you and I learned a lot from you, you helped me get started on many neuromorphic aspects. More than that, you have been a great emotional support. Thank you Stefania Carapezzi, you have been a really supportive office-mate, sharing all your knowledge and bringing incredible food support. Thank you Gabriele Boschetto for sharing your research experience and your gastronomic passion. Thank you Eirini Karachristou for your help in managing and organizing the NeurONN project, and for your willingness to create a cohesive and friendly team. Thank you Camille Couralet for your everyday support and for your unfailing energy for laughing, running, dancing, etc. Thank you Cécile Romane for sharing your tips on thesis and post-thesis management. Thank you Adrien Suau for your kind welcoming and advice during this thesis. Thank you Siyuan Niu for transmitting your Ph.D. experience and for being a great Tuesday's partner for the African food truck. Thank you Mr. Lee for taking care of all my Tuesday lunches.

I also would like to thank Ana Tacuri for her help in understanding the laboratory and organizing missions around the world. Thank you Virginie Feche for your positivity, and for your nutritional support in organizing breakfasts. Thank you Elena Demchenko, Paul Leloup, and Jérémie Salles for bringing me back to running, so I could take the lead of the breakfasts. Thank you as well to the entire team RA, Thomas, Julien, Loic, Pierre, Sarah, Quentin, Ismael, and others, who helped me get through the thesis writing. A major thanks to Geneviève Carrière for taking care of me and my health every day during those three years.

Now, I would like to show my gratitude to my family, starting with my parents Yves and Florence Abernot. Thank you for always helping and supporting me in achieving my ambitions. Thank you as well for your moral support every time I needed it and for your sportive motivation with windsurfing and yoga courses. I also thank my brother, my sister, and their partners, Jeanne, Samuel, Damien, and Appoline for the example you set by doing plainly what you like. Thank you Sam for keeping me up to date on musical trends, and thank you Jeanne for your traditional dance training. I also thank Réglisse. After 20 years, you are still sharp and alive to comfort the family. I finally express my gratitude to my grandparents for sharing their life experiences and for all the happy moments we had and will have.

I also would like to thank my friends, who accompanied me during the thesis. First, I would like to thank my childhood friends from Saint-Brieuc. Thank you Séléna and Julie. Meeting you for a meal, a drink, a swim, or whatever when I come back to Brittany brightens my days. Thank you, Louisa and Lucas, it is always a pleasure to share a *fondue* with a glass of wine with you in Montpellier or in Lyon. Thank you, Clotilde, Théo, François, Chloé, and Alice, it is always a pleasure to catch up. Thank you, Marie, I am really grateful that we managed to stay in contact despite the distance.

Then, I would like to thank the friends I met during my studies in Rennes and Bordeaux. Thank you, Lenny and Gautier, I am really happy to see that after Rennes we took different paths which are in the end similar and converging. Thank you, Matthieu, Sylvain, Christian, Baptiste, Clément, and Emmanuelle. We had a great time in Bordeaux, and I am really sad that we can not stay in touch more often. Thank you, Thomas, Clotilde, Etienne, Amandine, Matthieu, Lucie, and Antoine. Thank you for kindly welcoming me into your friendly group. It is always a pleasure to share moments with you everywhere in France and Europe. Thank you Félix and Axelle. I enjoy climbing, hiking, or simply conversing with you.

Now, I would like to thank all the people I met lately in Montpellier. Thank you Nizar, Marian, and Antonin for the nice dinners and board-game parties. Thank you Alexia and Benoit for teaching me (or trying to teach me) the science of bread, beer, knitting, windsurfing, and more. Thank you Aurélien, Camille, Mara, Yentl, Hyppolite, Hervé, Ioannis, Juliette, and Thomas for the nice climbing days and party nights. Thank you Alizée. We met first in Saint-Brieuc but re-discovering you in Montpellier has strengthened our friendship. I thank you for always being here to listen when I need to share my frustrations, to go hiking or biking when I need some fresh air, and to go out drinking and dancing when I need to let off steam. Also, I am sincerely thankful to the (extended) family of Thibaud. Thank you, Gilles and Caroline, for your warm welcomes and hospitality during weekends and holidays. Thank you, Julien, Clara, Cécile, and Bastien, for the nice and funny moments we had and still have. Thank you, Catherine, Jean, and Raymonde for sharing your life experiences and I wish you bien des choses.

Finally, a special thanks to Thibaud. You have supported my joys, my frustrations, and my clumsiness every day for more than six years. I would like to especially thank you for your help in maintaining a healthy lifestyle, taking care of most cleaning, cooking, gardening, and washing machine household tasks, and encouraging me to keep up with social, cultural, and sporting activities. I would have never achieved this 3-year experience without your sense of humor, your talents for sewing and decorating, and of course your emotional support.

This thesis work has been supported by the European Union's Horizon 2020 research and innovation program, EUH2020 NEURONN (www.neuronn.eu) project under Grant No. 871501.

# RÉSUMÉ

Au cours des dernières décennies, la multiplication des objets embarqués dans de nombreux domaines a considérablement augmenté la quantité de données à traiter et la complexité des tâches à résoudre, motivant l'émergence d'algorithmes probabilistes d'apprentissage tels que l'intelligence artificielle (IA) et les réseaux de neurones artificiels (ANN). Cependant, les systèmes matériels pour le calcul embarqué basés sur l'architecture von Neuman ne sont pas efficace pour traiter cette quantité de données. C'est pourquoi des paradigmes neuromorphiques dotés d'une mémoire distribuée sont étudiés, s'inspirant de la structure et de la représentation de l'information des réseaux de neurones biologiques. Dernièrement, la plupart de la recherche autour des paradigmes neuromorphiques ont exploré les réseaux de neurones à impulsion ou spiking neural networks (SNNs), qui s'inspirent des impulsions utilisées pour transmettre l'information dans les réseaux biologiques. Les SNNs encodent l'information temporellement à l'aide d'impulsions pour assurer un calcul de données continues naturel et à faible énergie. Récemment, les réseaux de neurones oscillatoires (ONN) sont apparu comme un paradigme neuromorphique alternatif pour du calcul temporel, rapide et efficace, à basse consommation. Les ONNs sont des réseaux d'oscillateurs couplés qui émulent les propriétés de calcul collectif des zones du cerveau par le biais d'oscillations. Les récentes implémentations d'ONN combinées à l'émergence de composants compacts à faible consommation d'énergie encouragent le développemment des ONNs pour le calcul embarqué. L'état de l'ONN le configure comme un réseau de Hopfield oscillatoire (OHN) avec une architecture d'oscillateurs entièrement couplés pour effectuer de la reconnaissance de formes avec une précision limitée. Cependant, le grand nombre de synapses de l'architecture limite l'implémentation de larges ONNs et le champs des applications de l'ONN. Cette thèse se concentre pour étudier si et comment l'ONN peut résoudre des applications significatives d'IA embarquée à l'aide d'une preuve de concept de l'ONN implémenté en digital sur FPGA. Tout d'abord, ce travail explore de nouveaux algorithmes d'apprentissages pour OHN, non supervisé et supervisé, pour améliorer la précision et pour intégrer de l'apprentissage continu sur puce. Ensuite, cette thèse étudie de nouvelles architectures pour l'ONN en s'inspirant des architectures en couches des ANNs pour créer dans un premier temps des couches d'OHN en cascade puis des réseaux ONN multi-couche. Les nouveaux algorithmes d'apprentissage et les nouvelles architectures sont démontrées avec l'ONN digital pour des applications d'IA embarquée, telles que pour la robotique avec de l'évitement d'obstacles et pour le traitement d'images avec de la reconnaissance de formes, de la détection de contour, de l'extraction d'amers, ou de la classification.

### **ABSTRACT**

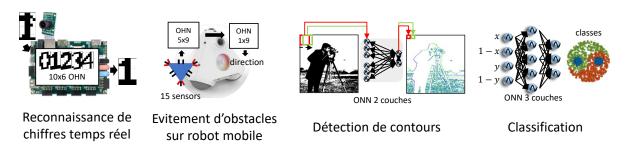

In the last decades, the multiplication of edge devices in many industry domains drastically increased the amount of data to treat and the complexity of tasks to solve, motivating the emergence of probabilistic machine learning algorithms with artificial intelligence (AI) and artificial neural networks (ANNs). However, classical edge hardware systems based on von Neuman architecture cannot efficiently handle this large amount of data. Thus, novel neuromorphic computing paradigms with distributed memory are explored, mimicking the structure and data representation of biological neural networks. Lately, most of the neuromorphic paradigm research has focused on spiking neural networks (SNNs), taking inspiration from signal transmission through spikes in biological networks. In SNNs, information is transmitted through spikes using the time domain to provide a natural and low-energy continuous data computation. Recently, oscillatory neural networks (ONNs) appeared as an alternative neuromorphic paradigm for low-power, fast, and efficient time-domain computation. ONNs are networks of coupled oscillators emulating the collective computational properties of brain areas through oscillations. The recent ONN implementations combined with the emergence of low-power compact devices for ONN encourage novel attention over ONN for edge computing. State-of-the-art ONN is configured as an oscillatory Hopfield network (OHN) with fully coupled recurrent connections to perform pattern recognition with limited accuracy. However, the large number of OHN synapses limits the scalability of ONN implementation and the ONN application scope. The focus of this thesis is to study if and how ONN can solve meaningful AI edge applications using a proof-of-concept of the ONN paradigm with a digital implementation on FPGA. First, it explores novel learning algorithms for OHN, unsupervised and supervised, to improve accuracy performances and to provide continual on-chip learning. Then, it studies novel ONN architectures, taking inspiration from state-of-the-art layered ANN models, to create cascaded OHNs and multi-layer ONNs. Novel learning algorithms and architectures are demonstrated with the digital design performing edge AI applications, from image processing with pattern recognition, image edge detection, feature extraction, or image classification, to robotics applications with obstacle avoidance.

# **C**ONTENTS

| 1 | Intr | oduction                                                                      | 1              |

|---|------|-------------------------------------------------------------------------------|----------------|

|   | 1.1  | Artificial Intelligence and Artificial Neural Networks                        | 1              |

|   | 1.2  | Hardware architectures for edge computing                                     | 4              |

|   | 1.3  | Neuromorphic computing paradigms                                              | 7              |

|   | 1.4  | Oscillatory Neural Networks (ONNs)                                            | 8              |

|   | 1.5  | Challenges and motivations                                                    | 10             |

|   | 1.6  | Outline                                                                       | 11             |

| 2 | Dig  | ital Oscillatory Hopfield Network (OHN)                                       | 15             |

| _ | 2.1  | Introduction                                                                  | 15             |

|   | 2.2  |                                                                               | 16             |

|   | 2.3  | Oscillatory Hopfield network (OHN)                                            | 17             |

|   | 2.4  | Digital OHN implementation                                                    | 18             |

|   |      | 2.4.1 Digital oscillators                                                     | 19             |

|   |      | 2.4.2 Hard-coded 5-bit register synapses                                      | 21             |

|   |      | 2.4.3 Additional control block                                                | 22             |

|   | 2.5  | Validation and characterization of the digital OHN                            | 22             |

|   |      | 2.5.1 Simulation evaluation of the digital OHN                                | 22             |

|   |      |                                                                               | 23             |

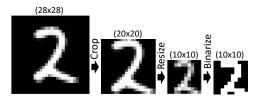

|   | 2.6  | Digits recognition from a camera stream                                       | 27             |

|   | 2.7  | Discussion and conclusion                                                     | 29             |

| 3 | ОП   | N learning for outo association                                               | 31             |

| 3 | 3.1  | N learning for auto-association Introduction                                  | 31             |

|   | 3.2  | Unsupervised learning for binary OHN                                          | 32             |

|   | 5.2  | •                                                                             | 33             |

|   |      | 3.2.2 HNN unsupervised learning rules adapted for OHN                         | 34             |

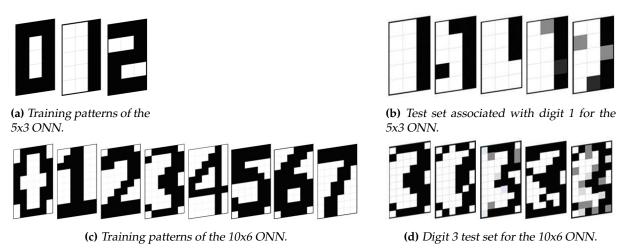

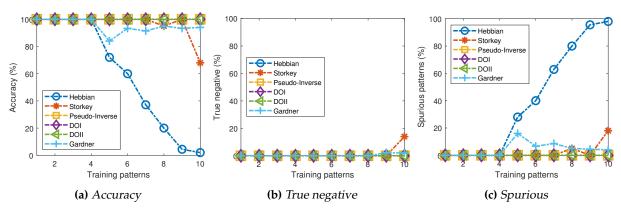

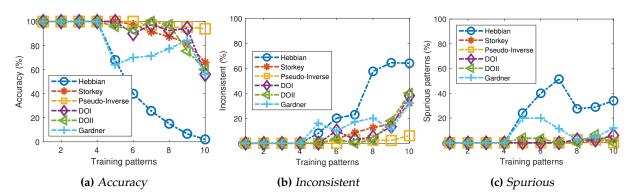

|   |      | 3.2.3 Comparison of unsupervised learning rules for digits recognition appli- | J <del>1</del> |

|   |      | cation                                                                        | 35             |

|   | 3.3  | Implementing on-chip learning for binary OHN                                  | 36             |

|   |      |                                                                               | 37             |

|   |      |                                                                               | 37             |

|   |      |                                                                               | 38             |

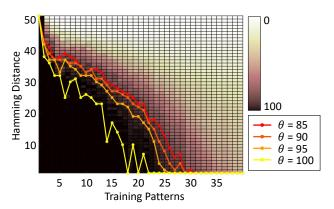

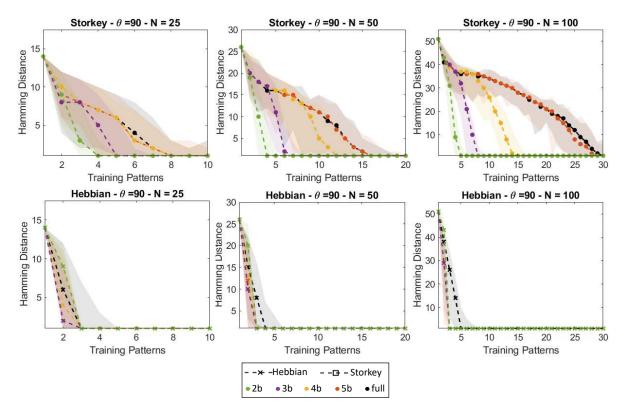

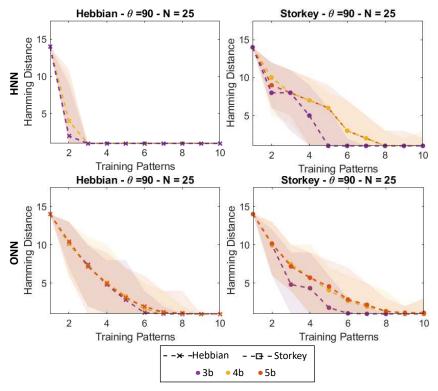

|   |      | 3.3.4 Scalability of the OHN on-chip learning architecture                    | 39             |

|   |      | 3.3.5 Discussion of the OHN on-chip learning                                  | 44             |

|   | 3.4  | Supervised learning for binary-OHN MNIST classification                       | 45             |

|   |      | 3.4.1 MNIST classification with OHN                                           | 45             |

|   |      | 3.4.2 Unsupervised learning for MNIST Classification                          | 48             |

|   |      | 3.4.3 Supervised AAM-EP learning for MNIST Classification                     | 49             |

|   |      | 3.4.4 Benchmarking and discussion                                             | 52             |

|   | 3.5  | Discussion and conclusion                                                     | 54             |

| 4   | Caso   | caded OHNs for multi-level auto-association 5                    | 7 |

|-----|--------|------------------------------------------------------------------|---|

|     | 4.1    | Introduction                                                     | 7 |

|     | 4.2    | Cascaded digital OHN inference and learning                      | 8 |

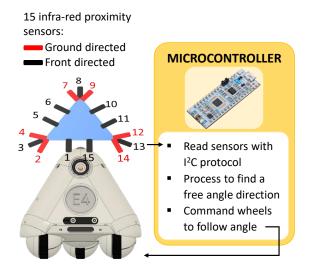

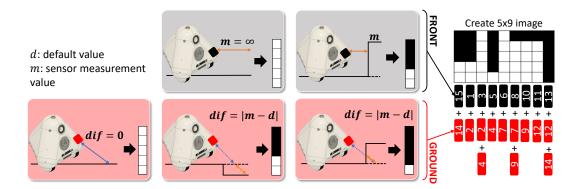

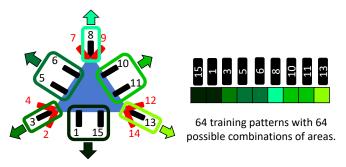

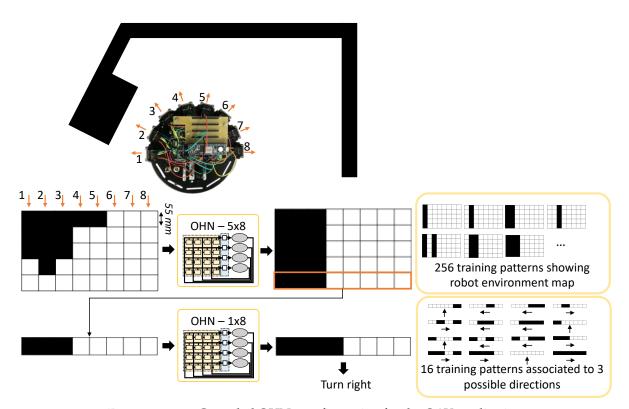

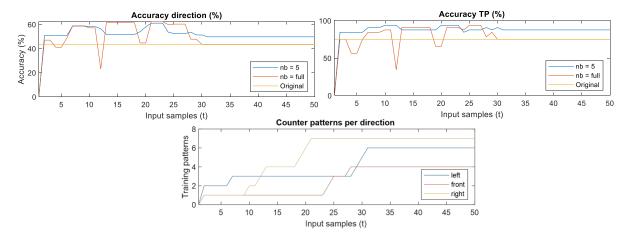

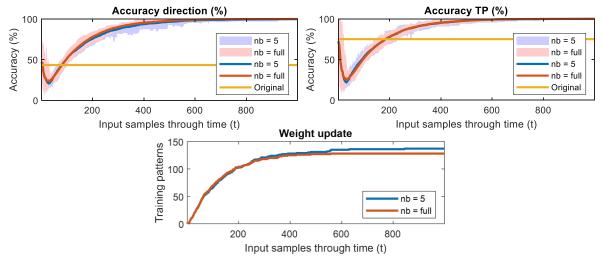

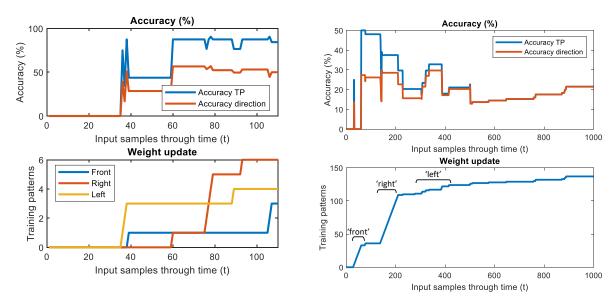

|     | 4.3    | Cascaded OHNs for obstacle avoidance (OAV)                       | 9 |

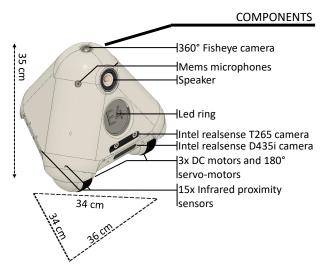

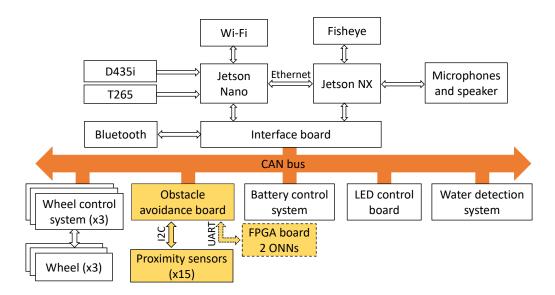

|     |        | 4.3.1 E4 robot                                                   | 0 |

|     |        | 4.3.2 Default OAV process on E4                                  | 1 |

|     |        | 4.3.3 Cascaded OHN for OAV on E4                                 | 2 |

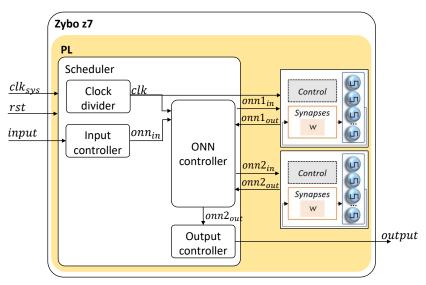

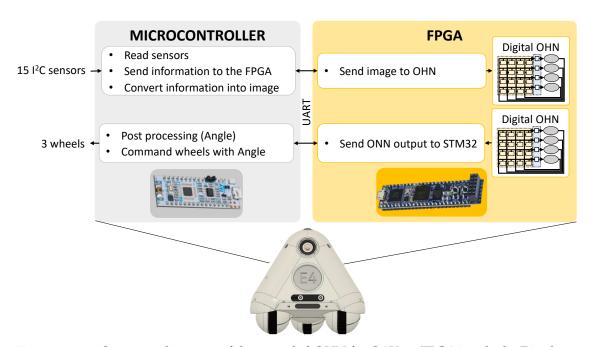

|     |        | 4.3.4 Cascaded digital OHN implementation on E4 6                | 4 |

|     |        | 4.3.5 OAV on E4 system performances 6                            | 5 |

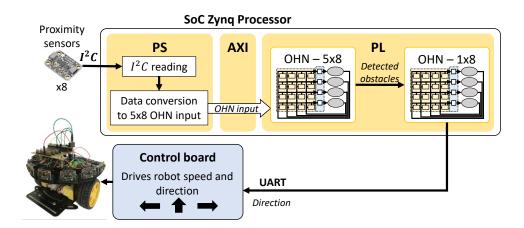

|     | 4.4    | All-in-one SoC architecture for OAV on Arduino robot 6           | 6 |

|     |        |                                                                  | 7 |

|     |        | 4.4.2 OAV on mobile robot                                        | 8 |

|     |        | 4.4.3 OAV on SoC performances                                    | 9 |

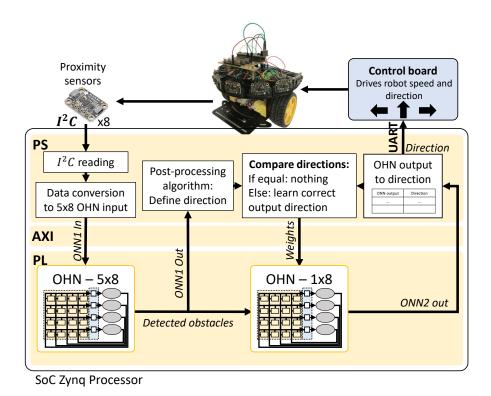

|     | 4.5    | •                                                                | 0 |

|     |        | 4.5.1 On-chip SoC architecture                                   | 0 |

|     |        | 4.5.2 Training OHN on-chip for OAV                               |   |

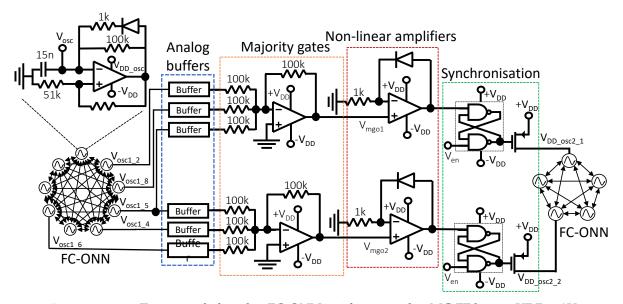

|     | 4.6    | Analog cascaded OHNs for image edge detection                    |   |

|     |        | 0 0                                                              | 7 |

|     |        | 4.6.2 Application to image edge detection                        |   |

|     |        |                                                                  | 9 |

|     | 4.7    | Discussion and conclusion                                        |   |

|     | 1.,    | 2.Deablion and conclusion 1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1. | • |

| 5   | Mul    | ti-layer ONN for hetero-association and classification 8         | 3 |

|     | 5.1    | Introduction                                                     | 3 |

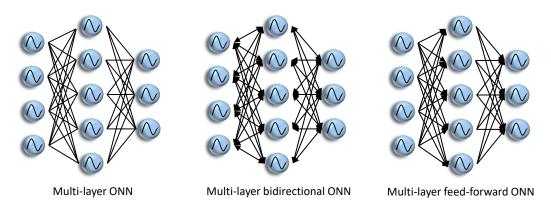

|     | 5.2    | Multi-layer architectures                                        | 4 |

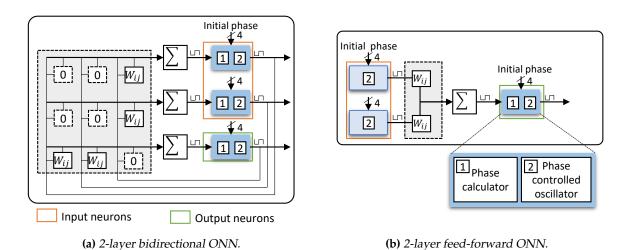

|     |        | 5.2.1 Multi-layer bidirectional ONN                              | 5 |

|     |        | 5.2.2 Multi-layer feed-forward ONN                               | 6 |

|     |        | 5.2.3 Implementation                                             |   |

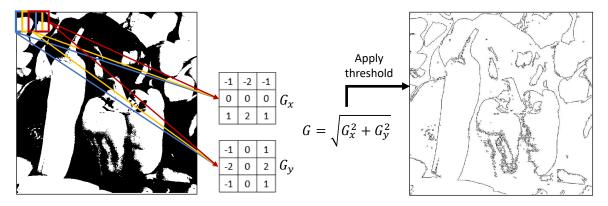

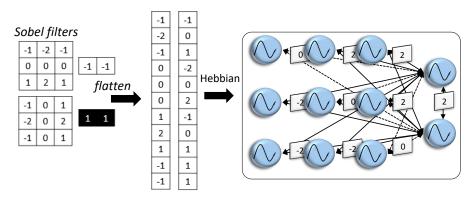

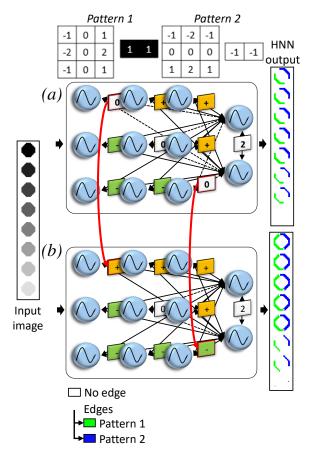

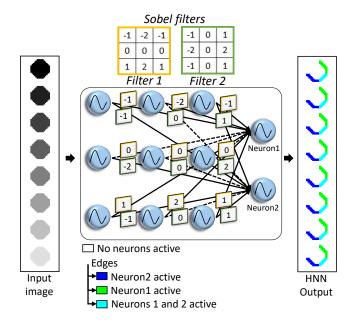

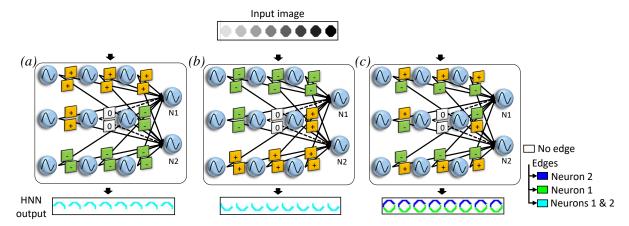

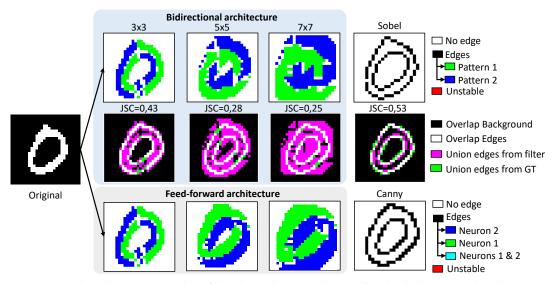

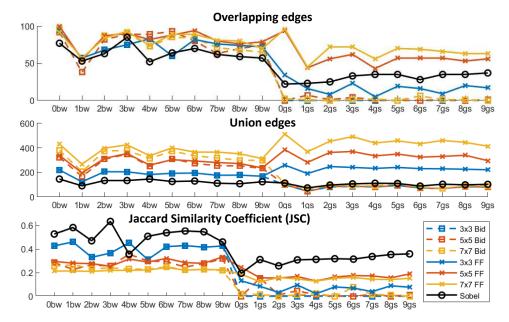

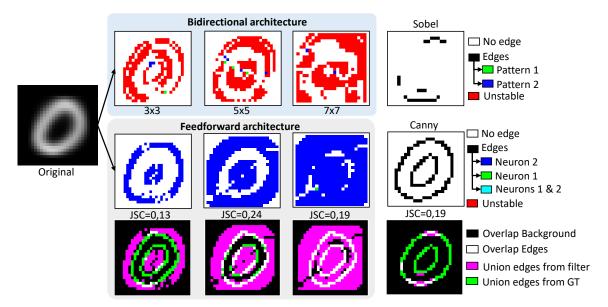

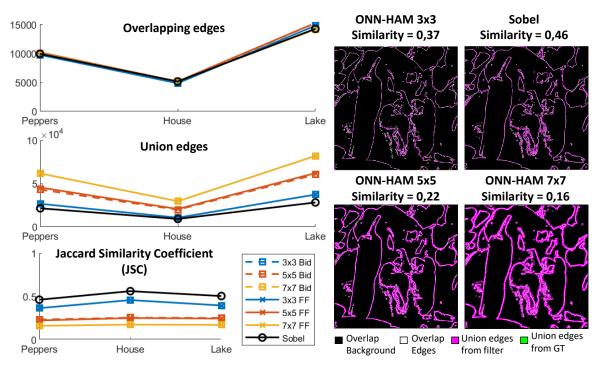

|     | 5.3    | 2-layer ONN for image edge detection                             | 8 |

|     |        | 5.3.1 Evaluation of the image edge detection application 8       |   |

|     |        | 5.3.2 2-layer bidirectional ONN                                  |   |

|     |        | 5.3.3 2-layer feed-forward ONN                                   |   |

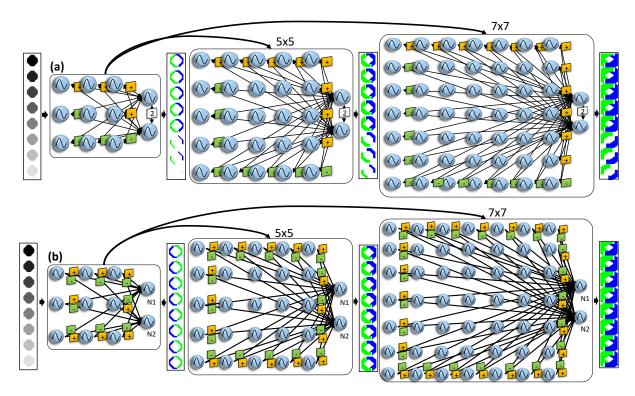

|     |        | 5.3.4 Extension to 5x5 and 7x7 input kernels                     | 2 |

|     |        | 5.3.5 Results and benchmarking                                   |   |

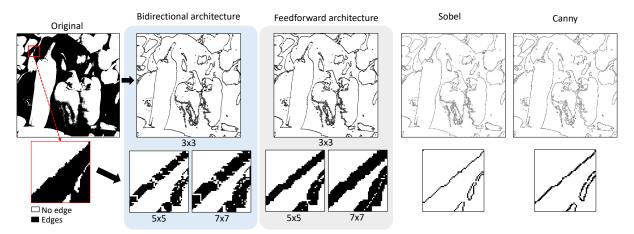

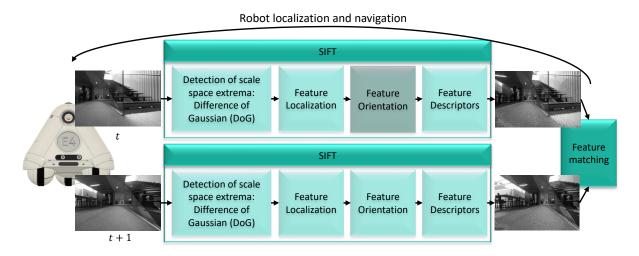

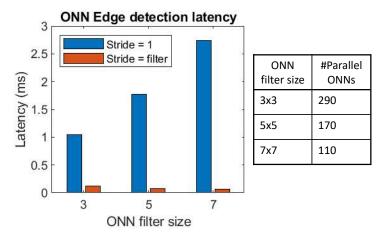

|     | 5.4    | ONN image edge detection for feature extraction                  |   |

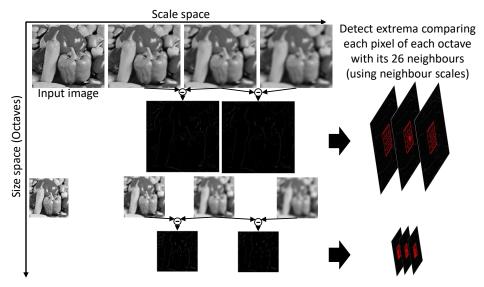

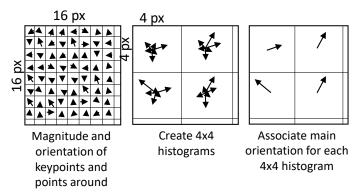

|     |        | 5.4.1 Feature detection and description with SIFT                |   |

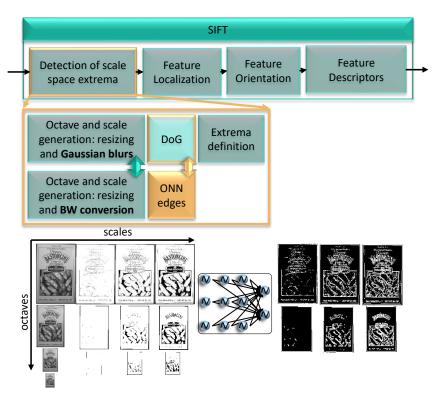

|     |        | 5.4.2 SIFT-ONN adaptation                                        |   |

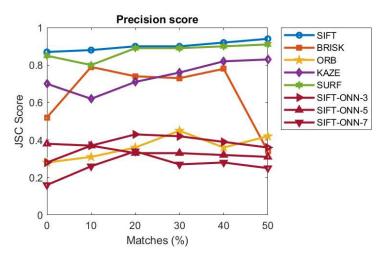

|     |        | 5.4.3 Validation and evaluation methods                          |   |

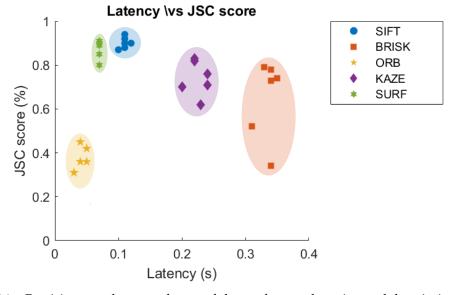

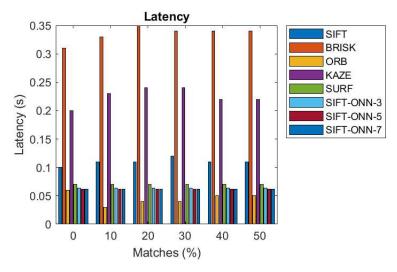

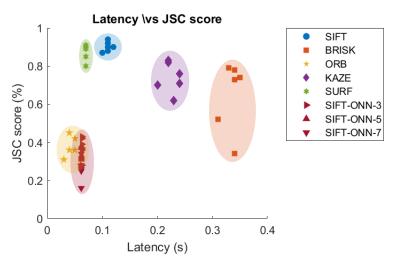

|     |        | 5.4.4 Results and benchmarking                                   |   |

|     | 5.5    | 3-layer feed-forward ONN for classification                      |   |

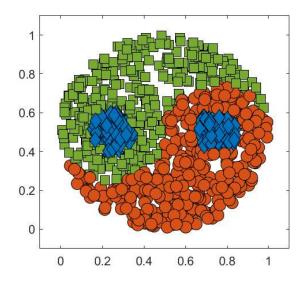

|     |        | 5.5.1 Yin-Yang classification dataset                            |   |

|     |        | 5.5.2 Training ONN for Yin-Yang classification                   |   |

|     |        | 5.5.3 Results and benchmarking                                   |   |

|     | 5.6    | Discussion and conclusion                                        |   |

|     | 0.0    | Discussion and conclusion                                        | _ |

| 6   | Disc   | cussion and conclusion 11                                        | 3 |

|     | 6.1    | Contributions                                                    |   |

|     | 6.2    | Future work                                                      |   |

|     |        |                                                                  |   |

| Bil | bliog  | raphy 11                                                         | 7 |

| Cu  | ırricu | ılum Vitae 13                                                    | 5 |

| Résumé | de la thèse                                                        | 139 |

|--------|--------------------------------------------------------------------|-----|

| .1     | Intelligence artificielle et réseaux de neurones artificiels       | 139 |

| .2     | Calcul neuromorphique et réseaux de neurones oscillatoires         | 141 |

| .3     | Motivations de la thèse                                            | 142 |

| .4     | Implémentation digitale d'un réseau de neurones oscillatoire       | 143 |

| .5     | Amélioration de l'apprentissage d'un OHN                           | 143 |

| .6     | Amélioration de l'architecture de réseaux de neurones oscillatoire | 144 |

| .7     | Applications de l'ONN pour l'IA embarquée                          | 145 |

| .8     | Conclusion et perspectives                                         | 146 |

# LIST OF FIGURES

| 1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>1.6<br>1.7                                       | ANN architectures.  Hardware computing architectures.  Leaky integrate and fire (LIF) spiking neuron model.  Phase-based ONN computing.  ANN vs. SNN vs. ONN computing.  Timeline of ONN historical development.  Main contributions of the Ph.D.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2<br>5<br>7<br>8<br>9<br>10<br>12                                                            |

|-------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

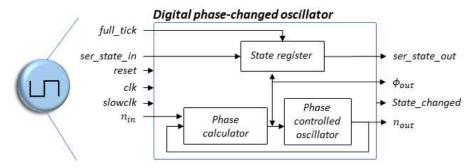

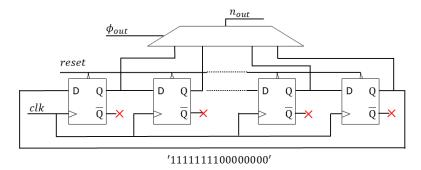

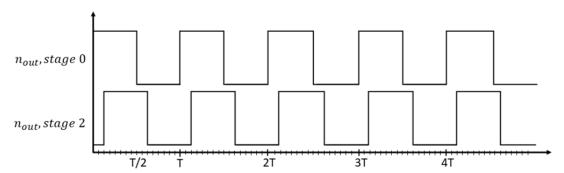

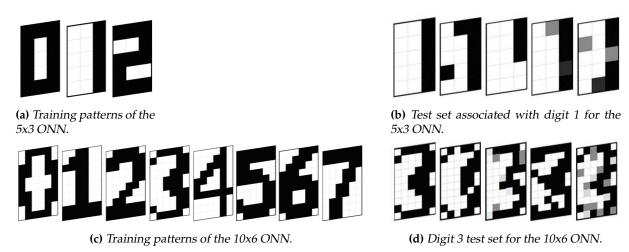

| 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.8<br>2.9<br>2.10<br>2.11<br>2.12 | HNN building blocks.  OHN for pattern recognition, with energy landscape.  Digital 2-neuron OHN.  Digital 4-neuron OHN.  Digital OHN building blocks.  Digital oscillator neuron.  Logic diagram of the implemented phase-controlled oscillator.  Output of internal neuron shift-register.  Training and test patterns for digit recognition task.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 17<br>18<br>19<br>20<br>20<br>21<br>21<br>23<br>24<br>26<br>28<br>28                         |

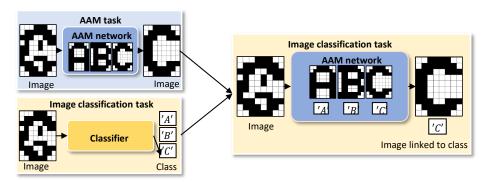

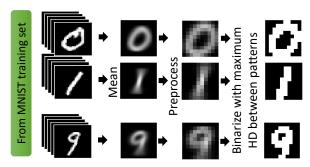

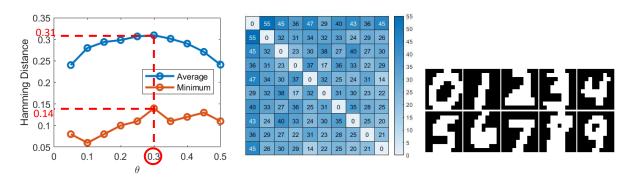

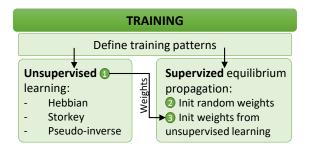

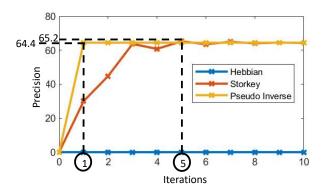

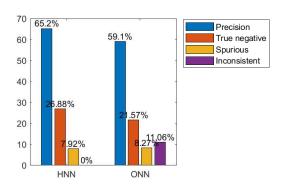

| 3.12<br>3.13<br>3.14<br>3.15<br>3.16<br>3.17                                        | ONN energy landscape representation.  Training and test patterns for the digit recognition task.  HNN results of the 10x6 digits recognition application.  Digital OHN results on the 10x6 digits recognition application.  on-chip learning OHN architecture.  100-neuron HNN capacity.  Multiple-size HNN capacity.  OHN on-chip learning resource utilization.  Capacity of 25-neuron HNN and OHN trained with Hebbian or Storkey.  MNIST pre-processing method.  Parallel between AAM and image classification tasks.  Process of definition of MNIST training patterns.  Definition of MNIST training patterns.  Training options for MNIST classification.  MNIST classification results using unsupervised learning.  MNIST classification results with AAM-EP supervised learning.  MNIST classification results with unsupervised and supervised EP learning.  OHN and HNN results with unsupervised Storkey and supervised EP learning. | 32<br>35<br>36<br>36<br>37<br>40<br>41<br>42<br>46<br>47<br>47<br>48<br>49<br>51<br>52<br>52 |

| 4.1                                                                                 | OHN computing with 2 cascaded OHNs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 58                                                                                           |

| 6               |

|-----------------|

| 6               |

| 6               |

| 6               |

| 6               |

| 6               |

| 6               |

| 6               |

| 66              |

| 7               |

| ge              |

| edge            |

| 75              |

| 78 ond layer    |

| ond layer       |

|                 |

|                 |

| 80              |

| 84              |

|                 |

|                 |

| 0               |

| 88              |

| 89              |

| 90              |

| e detection. 90 |

| 9:              |

| 92              |

| 93              |

| 94              |

| between         |

| 94              |

| 9!              |

| images 90       |

| between         |

| anny GT         |

| 90              |

| tion, and       |

| 10              |

| 10              |

| 102             |

| 100             |

| 103             |

| 512x512         |

| 104             |

| lution 10       |

| 100             |

| ith state-      |

|                 |

| 10'             |

| 102             |

|                 |

### List of figures

| 1 | Différents types de réseaux de neurones |

|---|-----------------------------------------|

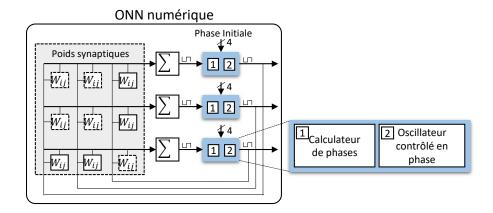

| 2 | ONN numérique                           |

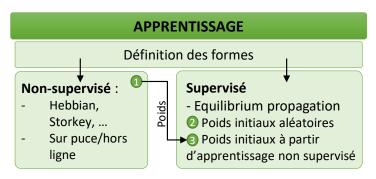

| 3 | Apprentissage de l'OHN                  |

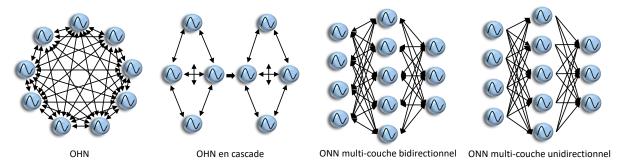

| 4 | Architectures de l'ONN                  |

| 5 | Applications de l'ONN                   |

# LIST OF TABLES

| 1.1 | Main contributions of the Ph.D                                                      | 13   |

|-----|-------------------------------------------------------------------------------------|------|

| 2.1 | Frequency limits and resource utilization of the digital ONN design                 | 23   |

| 2.2 | Training patterns combinations for digits recognition                               | 24   |

| 2.3 | Error rate of ONN on FPGA for digits recognition                                    | 25   |

| 2.4 | Digital OHN timing performances                                                     | 27   |

| 2.5 | Digital OHN resource utilization                                                    | 27   |

| 2.6 | Digital OHN power and energy consumption                                            | 27   |

| 2.7 | Comparison of the digital OHN with other fully-connected ONN implementations.       | . 30 |

| 3.1 | HNN learning rules features                                                         | 34   |

| 3.2 | On-chip learning performances                                                       | 39   |

| 3.3 | On-chip OHN learning and inference latency                                          | 43   |

| 3.4 | Comparison of the digital ONN with re-programmable synapses                         | 44   |

| 3.5 | OHN and HNN MNIST classification best results                                       | 52   |

| 3.6 | MNIST classification training computational efforts                                 | 53   |

| 3.7 | Comparison of network models trained with EP on MNIST classification                | 54   |

| 4.1 | Performances of the OAV function on the E4 robot                                    | 65   |

| 4.2 | OAV computation time comparison between software and cascaded OHNs                  | 65   |

| 4.3 | Performances of the OAV-SoC system                                                  | 69   |

| 4.4 | On-chip OAV learning system performances on Zybo-Z7 board                           | 76   |

| 4.5 | Precision of cascaded analog OHNs on image edge detection                           | 80   |

| 4.6 | Latency performances of our solution                                                | 80   |

| 5.1 | ONN edge detection latency performances and resource utilization                    | 97   |

| 5.2 | Estimation of full image edge detection using ONN                                   | 97   |

| 5.3 | Performances of FPGA implementation of edge detection algorithms from the           |      |

|     | literature                                                                          | 98   |

| 5.4 | Estimation of resource utilization, latency, and precision for various parallel and |      |

|     | overlapping parameters for the two ONN architectures                                | 99   |

| 5.5 |                                                                                     | 105  |

| 5.6 | Accuracy of the 3-layer feed-forward ANNs for Yin-Yang classification               | 111  |

| 57  | 3-layer feed-forward ONN characteristics                                            | 111  |

### LIST OF ACRONYMS

AAM auto-associative memory. AI artificial intelligence. ANN artificial neural network.

BAM bidirectional associative memory.

BNN binary neural network.

BPTT back-propagation through time.

CHR contrastive Hebbian rule.

CNN convolutional neural network.

COP combinatorial optimization problem.

CPU central processing unit.

DLP deep learning processor.

DNN deep neural network.

DoG difference of Gaussian.

DOI Diederich-Opper rule I.

DOII Diederich-Opper rule II.

EP equilibrium propagation.

FF feed-forward.

FPGA field-programmable gate array.

FPS frames per second. FSM finite state machine. GPU graphics processing unit.

GT ground truth.

HAM heterogeneous associative memory.

HD Hamming distance.

HNN Hopfield neural network.

I<sup>2</sup>C inter-integrated circuit.

JSC Jaccard similarity coefficient.

LEGION locally excitatory globally inhibitory oscillator network.

LIF leaky integrate and fire.

LUT look-up table.

MAC multiply and accumulate.

MG majority gate.

ML machine learning.

MLP multi-layer perceptron.

NMAC<sub>OP</sub> number of multiply and accumulate operations.

NPU neural processing unit. OAV obstacle avoidance.

OHN oscillatory Hopfield network.

OIM oscillatory Ising machine.

ONN oscillatory neural network.

ORB oriented FAST and rotated BRIEF.

PL programmable logic.

PLL phase-locked loop.

PP post-processing.

PS processing system.

ReLU rectified linear unit.

RNN recurrent neural network.

SIFT scale-invariant feature transform.

SLAM simultaneous localization and mapping.

SNN spiking neural network.

SoC system on chip.

STDP spike timing dependent plasticity.

STO spin-torque oscillator. SURF speeded up robust features.

ToF time of flight.

TPU tensor processing unit.

UART universal asynchronous receiver transmitter.

# **INTRODUCTION**

#### **Contents**

| 1.1 | Artificial Intelligence and Artificial Neural Networks | 1  |

|-----|--------------------------------------------------------|----|

| 1.2 | Hardware architectures for edge computing              | 4  |

| 1.3 | Neuromorphic computing paradigms                       | 7  |

| 1.4 | Oscillatory Neural Networks (ONNs)                     | 8  |

| 1.5 | Challenges and motivations                             | 10 |

| 1.6 | Outline                                                | 11 |

|     |                                                        |    |

In the last decades, data growth has led to the emergence of increasingly powerful artificial intelligence (AI) algorithms. However, the state-of-the-art edge computing systems based on von Neuman architecture can not efficiently handle this large amount of data and calculations. Thus, novel brain-inspired neuromorphic computing paradigms emerged to propose low-power fast computing systems for edge AI. In particular, the oscillatory neural network (ONN) neuromorphic paradigm takes inspiration from brain waves to compute using the natural synchronization of coupled oscillators. ONNs have mainly been used to perform pattern-recognition tasks which is limiting for edge AI. In this thesis, we study how to perform meaningful AI edge applications with the ONN computing paradigm. In particular, we use a proof-of-concept of the ONN computing paradigm with a digital design implemented on field-programmable gate array (FPGA) to explore various learning algorithms, architectures, and edge applications compatible with ONN. This chapter first provides a description of state-of-the-art AI algorithms and hardware computing platforms before presenting neuromorphic computing paradigms, especially ONN to state the main motivation of this Ph.D. thesis. Finally, this chapter details the main contributions and outline of this Ph.D. thesis.

### 1.1 Artificial Intelligence and Artificial Neural Networks

The development of large-scale micro-electronic processors, following Moore's law prediction [1], has led to the development of novel computing algorithms to bring human capabilities to machines. We define AI as the ensemble of algorithms and models solved by machines that try to either overcome human capabilities to solve a specific task or to replace humans on more general-purpose tasks. With the increasing complexity of AI tasks to solve, deterministic computing algorithms were discontinued for the emergence of probabilistic machine learning (ML) models. ML models are a subset of AI algorithms that are capable of learning tasks from data using an objective function, and a learning algorithm capable of optimizing the objective

function [2]. ML models include broad types of algorithms, however, they are more and more associated with the subset of artificial neural network (ANN) models.

ANNs are computing models taking inspiration from neuroscience and brain neural network structure to learn and compute [3]. The human brain is known to compute hard tasks while consuming a low amount of power [4], making it attractive for efficient computing. It is composed of a biological neural network that treats and transmits information efficiently. Concisely, a biological neural network is made of neurons interconnected with synapses by axons and dendrites. The human neural network is made of around 86 billion neurons interconnected by even more synapses, around 10000 billion in 1 cm<sup>3</sup>. The efficiency of the human brain mainly comes from its scalability and its plasticity, making it highly reconfigurable to adapt its knowledge through time.

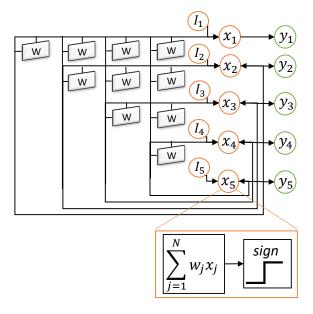

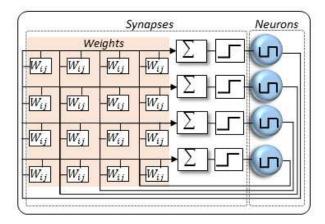

ANNs take inspiration from biological neural networks by considering two main elements, artificial neurons interconnected by artificial synapses. The first mathematical model of a biological neuron was proposed by McCulloch and Pitts in 1943 [5] before being used for computation, as a perceptron, by Rosenblatt in 1960 [6]. It is defined by two functions:

- 1. an **integration function** that integrates the synaptic information. The first integration function proposed by Rosenblatt [6] computes a weighted sum of the pre-synaptic neuron states and synaptic weight factors and is still widely used nowadays, see Figure 1.1a,

- 2. an **activation function** that computes the integrated information to activate or not the neuron output. The first proposition of an activation function was a *sign* function, see Figure 1.1a.

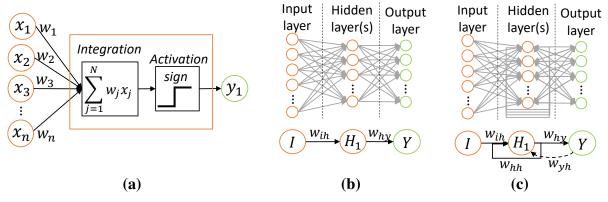

FIGURE 1.1 – (a) Perceptron neuron. (b) Feed-forward DNN architecture. (c) Recurrent DNN architecture.

A single perceptron neuron with a *sign* activation function does not allow non-linear transformation between input and output data, limiting its application to linear tasks [7]. Thus, since the introduction of the perceptron, novel ANN models have been proposed, modifying neuron functions and proposing novel architectures. First, novel non-linear activation functions offering a wider possibility of output states were developed to improve ANN performances. Particularly, the sigmoid function and the rectified linear unit (ReLU) function are nowadays typical activations [8]. Then, novel ANN topologies or architectures were introduced creating layers of neurons in which there is no synaptic connection within layers, but there are synaptic connections between layers. Synapses can be unidirectional, transmitting information from input to output layers, and producing feed-forward models, see Figure 1.1b. Otherwise, synapses can be multi-directional creating recurrences between layers or between neurons from the same

layer, producing recurrent models, see Figure 1.1c. If a network architecture is made of more than one layer (feed-forward or recurrent), it is called a deep neural network (DNN). A feed-forward DNN of perceptron neurons is called a multi-layer perceptron (MLP) and produces a non-linear relation between input and output, enlarging the complexity of tasks to solve with ANNs.

Image classification is a typical non-linear AI task used in a wide variety of domains, such as for smart city security, healthcare, or autonomous driving. However, even if MLPs offer distinctive performances on small-scale image classification [9], they can not easily handle large-scale images. In image classification, the input data is represented by the intensity of each pixel in the image. For example, for a 28x28 gray-scale image, the network requires an input layer of 784 neurons, which is multiplied by three for RGB images. The large input layer increases computation and memory requirements making it challenging to perform large-scale image classification with MLPs. Convolutional Neural Networks (CNNs) [10] were introduced to solve the scaling issue of MLP models on image classification, taking inspiration from the visual nervous system of the vertebrate by creating a hierarchical model [11, 12]. The first solution to reproduce the visual nervous system was the Neocognitron proposed by Fukushima in 1980 [13] before the emergence of CNNs developed by LeCun in the 1990s [9, 10]. A CNN is made of two main components, convolutional layers which are sparse layers extracting features from the original image, and a final fully connected MLP layer performing classification from the extracted features, thus limiting input layer size. Additional operations, like Maxpooling and Normalization, can also be used to analyze and select important features in order to reduce the input dimension of the MLP classifier. The architecture of the CNN, the number of convolutional layers, Maxpooling, and Normalization can vary depending on the task to solve, and finding the best architecture is still an open question [14]. In 2009, the ImageNet dataset was proposed to benchmark ANN models on image classification [15] and various CNN-based models achieved high precision [16, 17, 18]. However, CNN models are efficient for static input data like images, but not optimized for dynamical data.

Recurrent Neural Networks (RNNs) [19] are networks that include some recurrences in their topology by connecting neurons among the same layer or allowing connections from neurons of upper layers to neurons of previous layers, such that the information is propagating in different directions, see Figure 1.1c. Recurrences allow remembering previous information of sequential data, creating dependencies. Thus, RNNs are often used for dynamical data processing, but also for clustering tasks. For example, the first RNN model was the Hopfield neural network (HNN) [20] proposed by Hopfield in 1982 with a single-layer architecture to perform auto-associative memory (AAM). However, classical RNNs are slow to train and suffer from vanishing gradient problems, forgetting old dependencies for long input sequences [21]. Recently RNNs gained interest in natural language processing [22] with the introduction of Long Short Term Memories (LSTMs) [23] and the emergence of the attention mechanism [24], reducing the vanishing gradient problem. For example, the attention mechanism is behind the powerful Generative Pre-trained Transformer (GPT) models capable of generating human-like text or images [25, 26].

Novel ANN architectures are still being investigated in order to improve performances and adapt to various data types. In parallel, ANN learning algorithms are also explored to correctly configure the ANN models by adapting the synaptic parameters, mainly the weight factors, to the assigned tasks. To do so, ANN learning algorithms use a dataset, an objective function, and an optimization algorithm capable of optimizing the objective function. Learning algorithms are divided into two main categories:

1. Supervised learning considers datasets containing data samples with correct associated

outputs to perform classification or regression tasks, associating a prediction or a label to input data.

Unsupervised learning considers datasets containing input samples without the associated prediction and needs to find correlations and structure to organize data without additional feedback indicating if the organization is correct or not. It is often used for clustering.

The state-of-the-art supervised learning is the gradient back-propagation algorithm introduced in the 1980s for feed-forward ANNs [27, 9]. It calculates the error between the ANN prediction and the label to propagate the gradient to the previous layers and update the synaptic parameters. The introduction of back-propagation with the parallel developments of ANN architectures revolutionized the use of DNNs and CNNs, introducing deep learning. However, deep learning usually compels a large learning dataset, resulting in an important number of computations. For example, image classification of handwritten digits with MNIST achieves more than 99% of precision but requires training over 60000 samples [9]. Back-propagation has also been adapted to RNN with the back-propagation through time (BPTT), computing gradient back-propagation for multiple time steps, but it is even more computation-demanding than the usual back-propagation algorithm. The first unsupervised learning algorithm is the Hebbian learning introduced by Hebb in 1949 [28]. It uses learning data to reinforce synaptic parameters locally between two neurons if they have equal activation values, following "neurons that fire together, wire together". Unsupervised learning algorithms usually require fewer learning samples and fewer computations while it also achieves lower precision than supervised algorithms. Recently, unsupervised learning algorithms gained interest with the emergence of self-supervised learning [29, 30] used for limited or corrupted datasets to label additional or missing data using unsupervised learning before configuring the ANN model with supervised learning.

Supervised and unsupervised learning algorithms are commonly computed only once with the entire learning dataset before using the configured model for an infinite inference loop. However, in the case of evolving environments or data, it is necessary to learn redundantly or continuously through time to keep the ANN configuration optimized. Continual learning is another area of research which integrates supervised and unsupervised algorithms [31, 32, 33] to learn novel data while avoiding catastrophic forgetting of previously learned data [34, 35].

Using ANNs, specifically CNNs and DNNs, has successfully been used to teach smart systems to recognize or detect objects [36], [16], [37], [38], [39], read texts [9], and analyze speeches [40, 41]. However, with the growing complexity of applications to solve and the ever-increasing amount of data to treat, ANNs are often implemented on expensive hardware, and the impact of AI on global warming is becoming non-negligible [42, 43]. Thus, while the need for more powerful AI algorithms is not decreasing, it is necessary to propose novel hardware computing solutions to reduce the impact of AI.

### 1.2 Hardware architectures for edge computing

The development and generalization of computing hardware started with the introduction of the von-Neuman architecture, together with Moore's law prediction. A classical central processing unit (CPU), based on von-Neuman architecture, disconnects the memory unit from the computing unit, inducing memory reading and writing processes during computation, see Figure 1.2. CPUs are nowadays spread everywhere thanks to their efficiency in treating general-purpose sequential tasks. However, for large-scale memory-intensive computations, the com-

munication bus between memory and computing units is saturated, generating computing latency, and high energy consumption, this is called the von Neuman bottleneck [44]. Graphics processing units (GPU) were developed to enable parallel processing, combining multiple CPU cores, to speed up data-intensive processing, such as graphical processing. In ANNs, the core inference operation is the multiply and accumulate (MAC) operation that is computed thousands or millions of times, distributed sequentially or in parallel depending on the architecture. Moreover, ANN learning is in general more computation-intensive than inference, as it uses large datasets to correctly represent all possible input data and maximize the accuracy during inference.

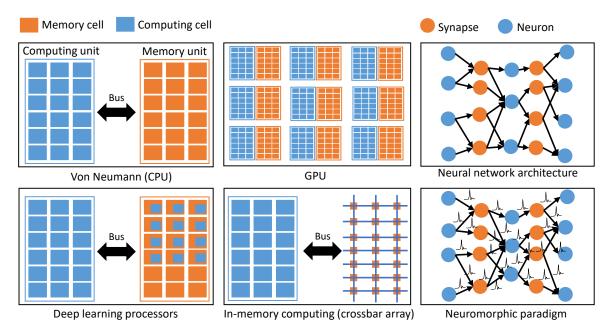

**FIGURE 1.2 –** *Hardware computing architectures, from von Neuman to in-memory computing, up to neuromorphic computing.*

State-of-the-art ANN computes inference and learning in the cloud using large-scale CPUs and GPUs. With the increasing complexity of ANN models and learning datasets, the important data transfer between processing and memory units slows down ANN computation and consumes more energy [45]. For example, training a CNN model sometimes needs to use multiple GPUs for hours or days to obtain satisfactory precision [46]. Various strategies are explored to improve the performances of cloud data center hardware resources [47]. In particular, researchers study ANN-based hardware accelerators to optimize data and computation distribution to reduce resource utilization, data transfer, latency, and energy consumption of ANN inference and learning in the cloud [48, 49, 50]. Most ANN-based accelerators investigate algorithm-aware hardware processing unit architectures that are made of operation-specific cells with distributed memory for ANN models [51]. For example, deep learning processor (DLP) such as neural processing unit (NPU) and tensor processing unit (TPU) are made of multiple small-scale cells containing both memory units and processing units capable of simple or vectored MAC operations to improve parallelization and accelerate the ANN inferences. Recently, analog computing also gained interest in taking advantage of the physical computing properties of analog circuits for low-cost computation. Analog computing also provides natural continuous values encoding while digital processing still relies on discrete binary values, even though multi-valued logic is also explored [52]. Similarly to analog computing, inmemory computing uses physical attributes of memory devices to compute MAC operations. It allows fast computation with low energy consumption compared to classical von-Neuman architectures [53]. One interesting solution creates crossbar arrays of memory devices to perform vectored MAC operations [54, 55], see Figure 1.2. Nowadays, there are digital, analog, or hybrid DLP accelerators. However, even if DLP drastically reduces the energy and latency of DNN inference and learning, it can be challenging to implement it in highly constrained edge devices [51].

Especially, in recent years, we have witnessed a proliferation of smart edge devices adopted by all industry sectors. From healthcare to security, robotics, and even home automation, there are edge computations in every domain [56, 57]. Currently, many edge devices still use cloud computing, sending data over the cloud for computation. However, data transfer requires large bandwidth meanwhile generating important computation latency, energy consumption, and privacy concerns. Thus, there is a need to develop fast and low-power hardware architectures to compute ANN inference and learning at the edge.

Learning at the edge is really challenging due to the large datasets and intensive learning algorithms necessary to achieve high inference accuracy. Yet, one solution comes with continual learning, performing learning iterations through time depending on the environment. Continual learning can hardly be implemented in the cloud due to the recurrent transmission of information between cloud and edge devices. However, implementing learning at the edge is also challenging as it requires additional resources for learning and re-programmable synaptic elements. Thus, at the same time, some study novel low-cost continual learning algorithms [58] and others explore compact and low-power devices and circuits for reconfigurable synapses [59].

For edge inference, a straightforward solution is to consider existing tiny micro-controllers with tiny ANN models [60], applying additional constraints to their architectures. For example, limiting the synaptic parameter precision, scaling down the network size, increasing the sparsity of synaptic connections, or reducing the possible states of the activation functions can optimize ANN models to reduce resource utilization and energy consumption while saving correct precision [61]. Recently, binary neural network (BNN) were investigated as low-cost solutions for image classification tasks at the edge [62, 63, 64, 65]. Alternatively, in the same spirit as DLP for cloud computing, brain-inspired neural network architectures were introduced, distributing memory to reduce latency and energy consumption induced by on-chip data transfer. Neural network architectures use analog or digital circuits to mimic ANN neuron and synapse functionalities, see Figure 1.2. Neurons and synapses are often implemented with multiple analog or digital circuits depending on the type of ANN and the task to solve. For example, in-memory computing with crossbar arrays can also be configured in neural network architectures if combined with additional neural activation circuits [66, 67]. Implementing tiny ANN models in neural network architectures can importantly reduce ANN inference latency and energy consumption. However, using tiny ANN models, with either micro-controllers or neural network architectures, can also impact the accuracy performances of the model.

In the human brain, data is encoded in the time domain through spikes. Using the time domain can encode continuous data in a more natural manner than in the amplitude domain. Also, edge devices often process dynamic data from sensors, and using the time to encode data creates natural dependencies between the following data, helping for dynamic data processing. Temporal encoding, together with the biological plausibility motivated the recent development of brain-inspired neuromorphic computing paradigms [68, 69, 70], mimicking not only the biological neural network architecture but also the representation of information.

### 1.3 Neuromorphic computing paradigms

The definition of a neuromorphic computing paradigm is still debated today [69] but in this thesis, we define a neuromorphic computing paradigm as an electronic system mimicking the brain with its neural network architecture and representation of information. Taking inspiration from biological representations of information, various neuromorphic paradigms were proposed to achieve low-power computation. On one side, researchers explore novel materials, devices, and circuits to build low-power neuromorphic systems capable of learning and inference [71, 72, 69]. In parallel, novel algorithms and applications are explored to demonstrate the effectiveness and added value of neuromorphic paradigms for edge computing [53, 73].

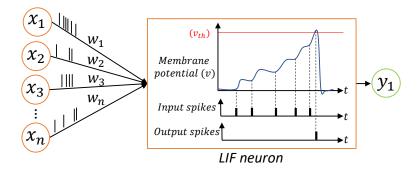

FIGURE 1.3 – Leaky integrate and fire (LIF) spiking neuron model.

The state-of-the-art neuromorphic paradigm is called spiking neural network (SNN) [74]. SNNs were introduced in the 1990s taking inspiration from the human brain where information is transmitted between neurons through spikes [75, 74, 76]. The interest of SNN is its data representation with spikes in the time domain, providing natural and low-energy continuous data encoding [77]. Many different spiking neuron models were developed over time, being more biologically plausible or providing better accuracy [75, 76, 78]. Nowadays, the leaky integrate and fire (LIF) neuron model [79] is widely used for its simplicity and efficiency while being less biologically plausible than others. The LIF neuron integrates the post-synaptic spikes by increasing the membrane potential of the neuron until it reaches a threshold that triggers an output spike, see Figure 1.3. Using numerical data, SNN necessitates data encoding through time, using mainly rate or temporal encoding, to be used straightforwardly on event-based data and sensors [80]. For example, SNN has been efficiently used to classify images from dynamic vision sensors (DVS) or event-based cameras [81, 82, 83]. To do so, various supervised and unsupervised learning strategies have been proposed [73, 84]. The supervised back-propagation algorithm can not directly be employed to train SNN because of the non-differentiable activation function [85]. A simple solution is to employ back-propagation on an ANN with an approximated differentiable activation function before transferring the weights to a real SNN. However, back-propagation is not biologically plausible, and the precision obtained is not always competitive with equivalent ANNs [86]. Thus, alternative spike-based supervised learning algorithms are also investigated to obtain better precision and to be more biologically plausible [87, 88, 89, 90, 91]. In parallel, always with the aim of being closer to the brain, spiking synaptic plasticity was introduced with the spike timing dependent plasticity (STDP) [92, 93], close to the Hebbian rule [28]. STDP has efficiently been used with many SNN architectures, feed-forward or recurrent, to perform image classification, clustering, or dynamic data treatment [94, 95]. Furthermore, beyond-ML applications have been explored, solving for example combinatorial optimization problem (COP) [96] or random walks [97]. Even if SNN showcased good accuracy for edge applications, it still falls behind ANN performances. Current research interests concentrate first on novel beyond-ML algorithms and applications for which SNN

overcomes ANN accuracy. Meanwhile the exploration of SNN learning algorithms and applications, other efforts are given to create efficient SNN testing methods [98, 99] and to build reliable SNN-based chips [100]. Multiple neuromorphic chips were developed providing large-scale SNNs for efficient edge inference, for example SpiNNaker [101], Truenorth [102], Loihi [103], Brainscale [104], among others. However, those neuromorphic chips do not provide learning at the edge, and continual online or on-chip learning solutions for SNNs are still being explored. Complementary to these large-scale CMOS-based neuromorphic chips, important efforts are being made to create novel materials, devices, and circuits for low-power compact SNN hardware [105, 69].

SNN has been widely explored in the last decades. However, novel promising neuromorphic computing paradigms emerged recently to substitute SNN for edge computing, i.e. hyperdimensional computing takes inspiration from the hyperdimensionality, the holographic representation, and the randomness of the biological neural network to compute [106, 107]. Alternatively, another neuromorphic paradigm emerged recently, taking inspiration from the collective computational properties of the brain oscillations with oscillatory neural network (ONN) [108].

### 1.4 Oscillatory Neural Networks (ONNs)

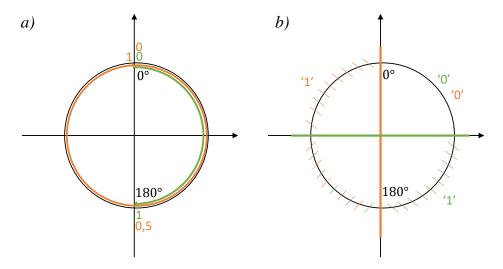

ONN is a promising alternative neuromorphic computing paradigm taking inspiration from the collective computational properties of brain areas through oscillations [109]. ONN computes using the physical synchronization of coupled oscillators [110, 111, 112]. To make the parallel with ANNs and SNNs, each neuron is an oscillator and each synapse is the coupling element, or the connectivity, between oscillators. In particular, ONN can be considered a specific case of SNN where neurons have constant frequency [113]. Synchronization of coupled oscillators was first observed by Huygens with Pendulum [114], before being employed for solving boolean functions in the 1950s [115, 116]. However, the development of transistor-based logic became more competitive than coupled oscillators. In the 1980s, Hopfield [20, 117] combined the neural network principle with physics and the Ising principle [118] to create energy-based spin-glass models. Later, Hoppenstead [119] and Aoyagi [120] highlighted the intrinsic Isingenergy minimization of ONN, which brought ONN back into the spotlight combined with its remarkable dynamic from Kuramoto [121]. It motivated on one side, the research for compact, fast, and low-power ONN implementations, and on the other side novel ONN architectures, learning algorithms, and edge applications.

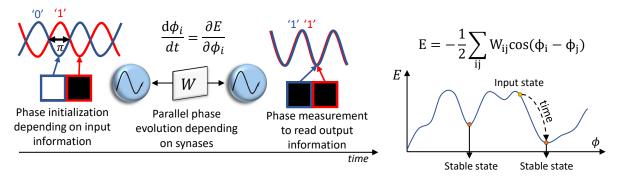

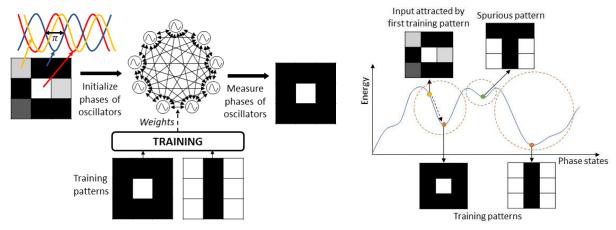

FIGURE 1.4 – Phase-based ONN computing principle.

The non-linear dynamics of coupled oscillators can be harnessed in many different ways to perform intelligent tasks. However, most ONN developments fall into two classes depen-

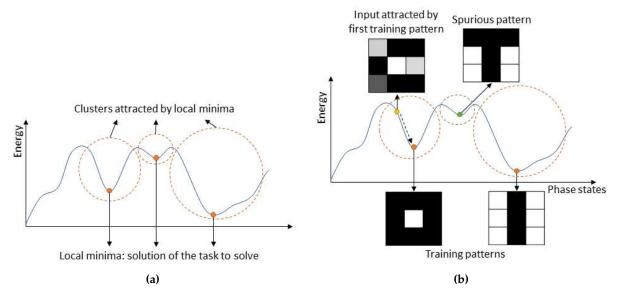

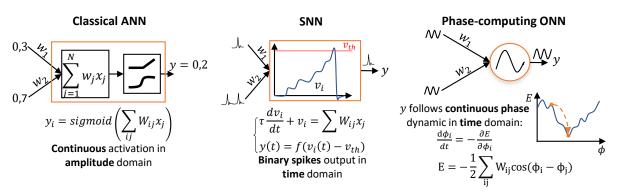

ding on the type of input/output encoding, **frequency-based ONN** where inputs are oscillator frequencies and outputs are the synchronization levels between oscillators, and **phase-based ONN** where oscillators have equal frequency and input/output is encoded in phase relationship among oscillators. Additionally, in phase-computing ONN, the phase evolution during computation can be associated with the minimization of an energy function, like in HNNs or attractor networks [122], see Figure 1.4. In comparison with classical ANNs, ONNs like SNNs do not use a deterministic activation function but compute depending on physical parameters with phase and/or frequency dynamic models, such as the Kuramoto model [121]. Also, SNNs represent information in binary spikes while ONNs represent information in continuous phase or frequency. Figure 1.5 presents the main differences of ANN, SNN, and ONN computing.

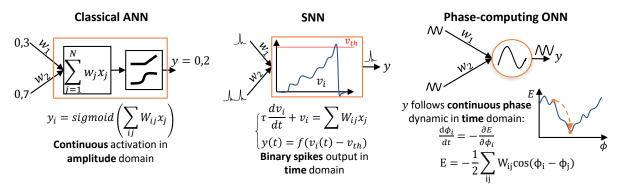

FIGURE 1.5 – ANN vs. SNN vs. ONN computing.

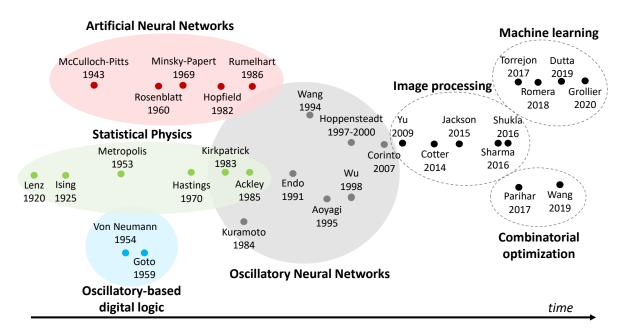

From the theory of computing with coupled oscillators, researchers investigated how to build ONN demonstrators for meaningful applications, see Figure 1.6. Starting with Wang and Terman in 1994, who introduced the locally excitatory globally inhibitory oscillator network (LEGION) ONN array for image segmentation [123], just before Hoppensteadt and Izhikevich linked the theory of coupled oscillators to energy-based HNNs [20] for associative memory applications [124, 119]. LEGION was introduced in 1994 as a solution to perform image segmentation using an array topology of locally excitatory oscillators computing in phase [123, 125, 126, 127] with an additional global inhibitory neuron, all trained with unsupervised Hebbian learning. The first analog implementation was proposed in 1999 [128] and further improved with a neuromorphic analog image segmentation system in 2006 [129]. Meanwhile, other works focused on adapted LEGION architectures with digital implementations [130, 131, 132]. Lately, LEGION motivated the development of phase-based and frequency-based ONNs for clustering and vision tasks [133, 134, 135, 136] using oscillators' array topology. In parallel, Hopfield's work [20, 117] propelled novel energy-based models of neural networks using analog phase dynamics such as phasor neural networks [137] and oscillatory Hopfield network (OHN) [108, 124]. The fully connected architecture allows recurrent signal propagation with oscillating neurons capable of performing auto-associative memory (AAM) tasks or pattern recognition using unsupervised Hebbian learning. Although Hoppensteadt presented the first hardware solution to implement OHN using phase-locked loop (PLL) in 2000 [119], many challenges were still limiting the large-scale implementation of such networks. In 2011, it was reported the first implemented OHN with 8 analog van der Pol oscillators performing phase-based pattern recognition [138]. Later, building OHNs with spin-torque oscillator (STO) was suggested to solve pattern recognition with frequency-based computing [139]. However, OHN raised more interest when Jackson[140, 141] and Shi [142] proposed larger-scale OHN, going up to 100 oscillators. Similarly, the development of novel compact and low-power devices for neuromorphic computing offered novel solutions for efficient phase-computing ONN [143, 144, 145].

**FIGURE 1.6** – Timeline of ONN historical development.

In the last decades, researchers also proposed alternative architectures to LEGION and OHN. For example, the star coupling topology was introduced to perform phase-based static or dynamic pattern recognition [146, 147]. The star coupling was then derived in frequency-based computing to also perform image processing, like pattern recognition [148], image segmentation [149] and convolution operations [150]. Alternatively, convolution operations can also be solved using layered networks of frequency-computing oscillatory neurons [151]. The layered topology, often used in neural networks, was also applied for classification tasks using oscillatory neurons, however being different from ONN computing [152, 153, 154, 72]. Additionally, for classification, the random and sparse topology of reservoir computing combined with the high non-linearity of coupled oscillators highlighted low-power and low-density properties [155, 156, 157]. Finally, another promising area recently proposed to build oscillatory Ising machine (OIM) to solve COPs creating graph-type architectures [158, 159, 160].

In terms of learning, Hebbian plasticity is the state-of-the-art for many applications and architectures, for example performing image segmentation [123, 125, 149], or pattern recognition [138, 141, 147]. Alternatively, we found in the literature a few works using simulated annealing to define circuit parameters [151], as well as gradient back-propagation on ANNs with weight transfer [152]. Finally, others perform custom learning, reproducing convolution filters [150, 143], or adapting a computational graph representation with coupled oscillators for COP. Up to our knowledge, all existing ONN demonstrators perform learning offline and synaptic weights are configured before inference.

### 1.5 Challenges and motivations

The theory around coupled oscillators encourages research on ONN-based systems for low-power edge AI accelerators. In particular, in this thesis, we focus on phase-computing ONN accelerators, motivated by:

Introduction 1.6. Outline

1. the **physical dynamic** that can facilitate the ONN design with a wide variety of oscillators, including low-power compact analog or digital devices,

- 2. the parallel synchronization of coupled oscillators providing fast inference,

- 3. the **data representation** in the time domain with oscillators' phases limiting voltage amplitude and power consumption.

In the literature, different architectures, implementations, learning algorithms, and applications were introduced for ONN, however, there appear to be a few isolated works. More generally, the state-of-the-art for ONN is to build a network of fully-coupled oscillators, configured with unsupervised Hebbian learning to solve AAM tasks, creating an OHN.

The fully-coupled architecture limits the scalability of ONN implementation. Considering a network of N neurons, there are N(N-1) synapses, making it difficult to implement at a large scale. For example, the largest OHN implemented in hardware integrates 100 neurons and is designed mainly with digital technologies [141]. Meanwhile, for analog design, a recent work built the largest 30-neuron fully connected ONN [161]. In comparison, [162] proposed an ONN-based digital hardware integrating 1968 oscillators interconnected in an array topology to perform COP. Even if a large part of the ONN community explores novel low-power compact materials, devices, and circuits [163, 164, 72, 159], we believe there is a need to investigate alternative ONN architectures to go beyond OHN.

Furthermore, OHN, such as HNN, trained with unsupervised Hebbian learning is not competitive with alternative models executing AAM tasks [165]. Thus, it is also necessary to study innovative learning solutions, first to try increasing OHN performances on AAM tasks, then to provide on-chip or online learning ability to OHN designs, and finally to enlarge the ONN scope of architectures and applications. The ONN can not be shortened to OHN to answer edge AI requirements, and we believe there are alternative applications where ONN can be competitive against other ANN and neuromorphic models.

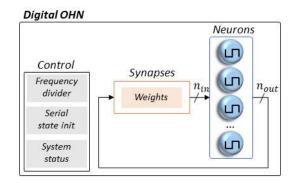

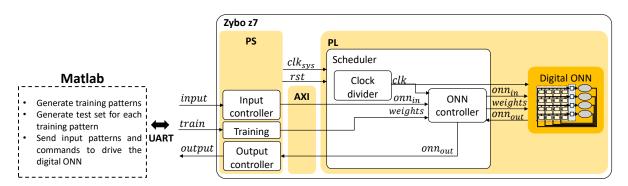

Finally, to study and demonstrate diverse ONN architectures, learning algorithms, and applications, we need an easily reconfigurable ONN implementation. Current state-of-the-art ONN implementations are hardly reconfigurable, for example, synaptic weights can be modified but the core structure of the network can not be changed. Here, we focus on a digital ONN implemented into a field-programmable gate array (FPGA) to be able to reconfigure the ONN synaptic weights and structure and to allow deploying demonstrators easily inside edge systems. Thus, in this Ph.D. thesis, I explore novel architectures, learning algorithms, and edge applications to go beyond OHN based on the digital ONN on FPGA.

#### 1.6 Outline

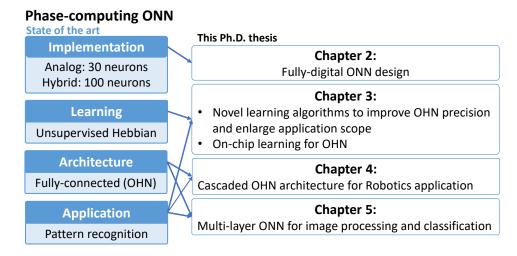

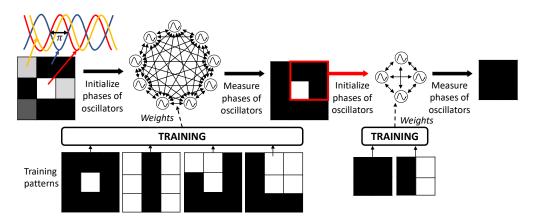

My Ph.D. thesis is organized into four chapters. **Chapter 2** details the phase-based ONN computing paradigm, presents the digital ONN implementation, and characterizes the design compared with previous ONN implementations, considering the state-of-the-art fully connected recurrent OHN configured for pattern recognition.

Chapter 3 studies various learning algorithms to improve OHN performances for pattern recognition. In particular, it first studies the adaptation of unsupervised learning algorithms introduced for HNN to the digital OHN with binary patterns, considering offline and on-chip

Introduction 1.6. Outline

learning. Then, it introduces a supervised learning algorithm and showcases the performance improvement to solve a digit recognition application.

**Chapter 4** introduces a novel ONN architecture with cascaded OHNs implemented in digital which allows applying ONN to a robotic obstacle avoidance application. Furthermore, it proposes a solution to implement the cascaded OHN architecture in analog to perform an image edge detection application.

**Chapter 5** presents another innovative ONN architecture with multi-layer ONNs for heteroassociation or classification. It studies inference and learning with multi-layer ONNs implemented digitally considering bidirectional or feed-forward connections. Also, it showcases the application of two-layer ONNs to image edge detection and feature extraction.

Finally, Chapter 6 provides a discussion along with a general conclusion to resume the main contributions of this Ph.D. thesis and open novel perspectives for the ONN computing paradigm. Table 1.1 and Figure 1.7 summarize the main contributions of each chapter.

FIGURE 1.7 – Main contributions of the Ph.D. thesis. OHN means oscillatory Hopfield network.

*Introduction* 1.6. Outline

**TABLE 1.1** – Main contributions of the Ph.D. thesis. OHN means Oscillatory Hopfield Network and EP means equilibrium propagation.

| Ch. | Problem        | Topic         | Contributions                                      |

|-----|----------------|---------------|----------------------------------------------------|

| 1   | Can we build a | Digital OHN   | (1) I detail the ONN computation and the digital   |

|     | large-scale    | for pattern   | OHN on FPGA. (2) I validate the OHN with           |

|     | reconfigurable | recognition.  | unsupervised learning solving digit recognition.   |

|     | ONN?           |               | (3) I demonstrate its real-time performances       |

|     |                |               | at the edge using a camera stream.                 |

| 2   | Can we improve | OHN           | (1) I study and compare unsupervised learning      |

|     | OHN precision  | learning.     | algorithms for OHN. (2) I build an on-chip         |

|     | results?       |               | learning platform for OHN. (3) I apply supervised  |

|     |                |               | EP learning to OHN solving MNIST.                  |

| 3   | Can we go      | Cascaded      | (1) I introduce a cascaded OHN architecture and    |

|     | beyond-OHN     | OHN           | implement it in FPGA. (2) I apply it               |

|     | with novel     | architecture. | on robotic obstacle avoidance using off-           |

|     | architectures? |               | and on-chip learning. (3) I apply an analog        |

|     |                |               | cascaded OHNs to image edge detection.             |

| 4   | Can we go      | Layered       | (1) I introduce layered ONN architectures and      |

|     | beyond-OHN     | ONN           | implement it in digital. (2) I apply a 2-layer ONN |

|     | with novel     | architecture. | to image edge detection. (3) I apply a 3-layer     |

|     | architectures? |               | ONN to classification.                             |

# DIGITAL OSCILLATORY HOPFIELD NETWORK (OHN)

#### **Contents**

| 2.1 | Introduction                                       | 15 |

|-----|----------------------------------------------------|----|

| 2.2 | ONN computing paradigm                             | 16 |

| 2.3 | Oscillatory Hopfield network (OHN)                 | 17 |

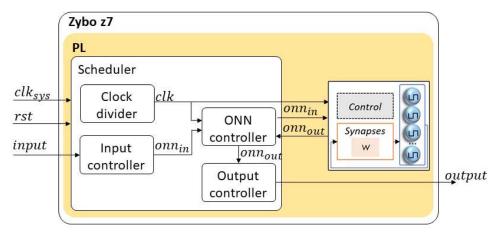

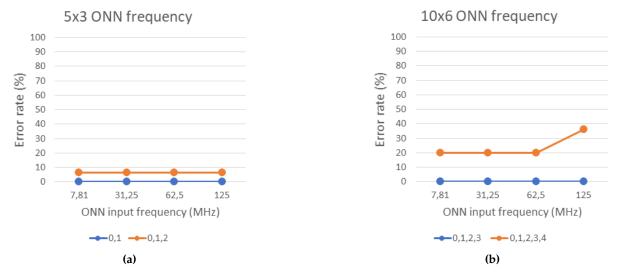

| 2.4 | Digital OHN implementation                         | 18 |

| 2.5 | Validation and characterization of the digital OHN | 22 |

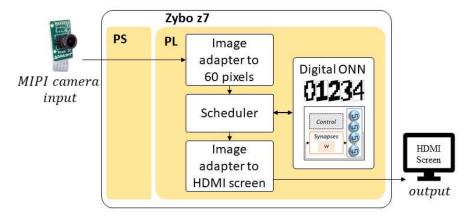

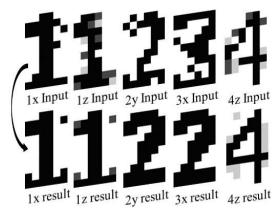

| 2.6 | Digits recognition from a camera stream            | 27 |

| 2.7 | Discussion and conclusion                          | 29 |

## 2.1 Introduction

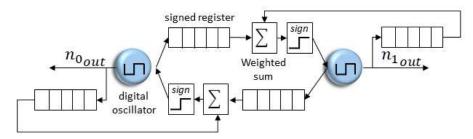

An oscillatory neural network (ONN) is a physical and hardware-based, neuromorphic computing approach [166, 167] which aims to provide low-power AI edge systems. Phase-computing ONNs, that are considered in this work, use coupled oscillators mimicking at the circuit level the basic structure of the brain architecture, and at the system level the collective computational synchronization of brain areas. In phase-based ONN, information is represented in the phase relationship between oscillators, and coupling between them induces phase synchronization or de-synchronization in time. For example, considering mechanical oscillators with metronomes, the random start of five homogeneous metronomes in a propagating environment will make them oscillate in parallel [168]. After several cycles, they get synchronized in frequency while their phase relations can give us meaningful information. Using phase-based computing, ONN achieves fast parallel computation with a limited oscillating voltage amplitude to perform low-power computation.

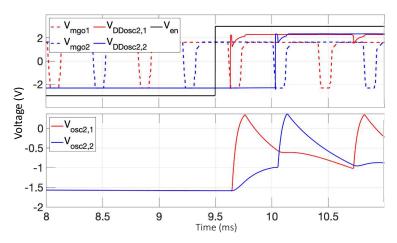

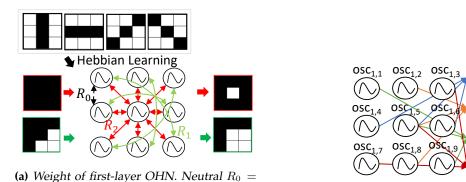

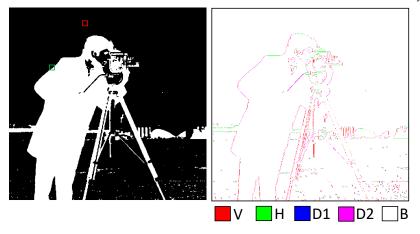

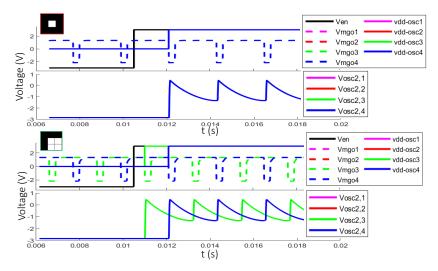

In state-of-the-art, ONN is used as an oscillatory Hopfield network (OHN) structured with a fully connected architecture, configured with unsupervised Hebbian learning for pattern recognition [119], such as in HNN. However, current implementations of OHN are limited in size due to the exponential increase of synaptic elements when increasing the number of oscillating neurons. To our best knowledge, the largest OHN fully analog design reaches 30 oscillators [161], and the largest hybrid OHN reaches 100 neurons [141]. Compared to other ANNs, built with thousands of neurons, HNN and OHN are also limited in terms of precision. The recent development of modern Hopfield networks with multi-layer architectures and continuous output states trained with gradient-based learning achieved competitive results com-