## Développement et caractérisation d'un circuit intégré de lecture de détecteurs LGAD destinés à la mesure 'pico-seconde' du temps de vol pour l'expérience ATLAS

Maxime Morenas

#### ▶ To cite this version:

Maxime Morenas. Développement et caractérisation d'un circuit intégré de lecture de détecteurs LGAD destinés à la mesure 'pico-seconde' du temps de vol pour l'expérience ATLAS. Electronique. Institut Polytechnique de Paris, 2023. Français. NNT: 2023IPPAX110. tel-04607890

### HAL Id: tel-04607890 https://theses.hal.science/tel-04607890v1

Submitted on 11 Jun 2024

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Développement et caractérisation d'un circuit intégré de lecture de détecteurs LGAD destinés à la mesure 'pico-seconde' du temps de vol pour l'expérience ATLAS

Thèse de doctorat de l'Institut Polytechnique de Paris préparée à l'École polytechnique

École doctorale n°626 École doctorale de l'Institut Polytechnique de Paris (EDIPP) Spécialité de doctorat : Électronique et Optoélectronique

Thèse présentée et soutenue à Palaiseau, le 30 novembre 2023, par

#### MORENAS MAXIME

#### Composition du Jury :

Laurent SERIN

Directeur de recherche, CNRS/IN2P3 (IJCLab) Président

Marlon BARBERO

Professeur des universités, Université Aix-Marseille Rapporteur

Angelo RIVETTI

Professeur, Université de Turin/INFN Rapporteur

Sophie BARON

Ingénieure de recherche, CERN Examinatrice

Etiennette AUFFRAY-HILLEMANNS

Directrice de recherche, CERN Examinatrice

Christophe DE LA TAILLE

Professeur, École polytechnique (OMEGA) Directeur de thèse

## Table des matières

| Ta | ıble d                | les matières                                            | i    |

|----|-----------------------|---------------------------------------------------------|------|

| Li | ste d                 | es figures                                              | v    |

| Li | ste d                 | es tableaux                                             | xiii |

| 1  | Introduction générale |                                                         |      |

| 2  | Con                   | ntexte                                                  | 3    |

|    | 2.1                   | La mesure de temps au HL-LHC                            | 4    |

|    |                       | 2.1.1 Du Large Hadron Collider au HL-LHC                | 4    |

|    |                       | 2.1.2 ATLAS                                             | 5    |

|    |                       | 2.1.3 HGTD                                              | 7    |

|    |                       | 2.1.4 Généralités sur la mesure de temps                | 8    |

|    |                       | 2.1.4.1 Jitter dû au time-walk                          | 9    |

|    |                       | 2.1.4.2 Jitter électronique                             | 10   |

|    | 2.2                   | Formation du signal dans un détecteur à semiconducteurs | 10   |

|    |                       | 2.2.1 Principe général                                  | 10   |

|    |                       | 2.2.2 Low Gain Avalanche Diode                          | 12   |

|    |                       | 2.2.3 Jitter d'un détecteur à semiconducteurs           | 14   |

|    |                       | 2.2.3.1 Bruit de Landau                                 | 14   |

|    |                       | 2.2.3.2 Distorsion du signal                            | 15   |

|    | 2.3                   | Choix d'une technologie d'ASIC                          | 15   |

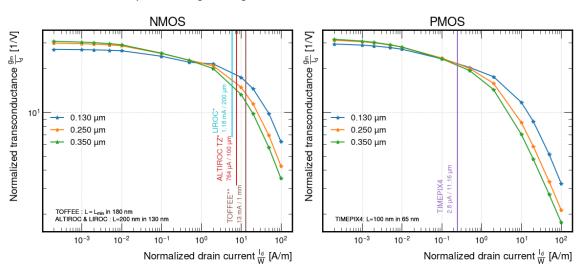

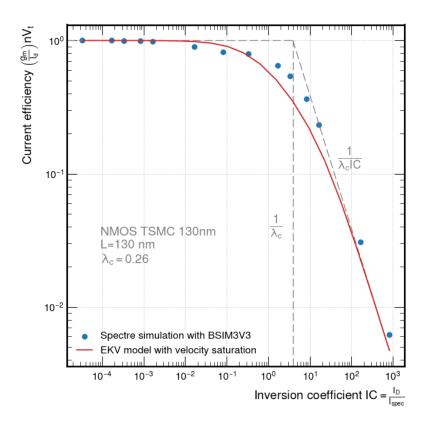

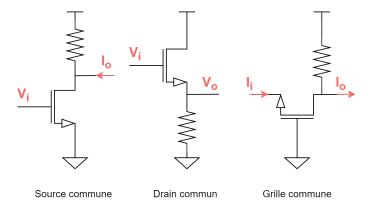

|    |                       | 2.3.1 Gain intrinsèque d'un MOSFET                      | 15   |

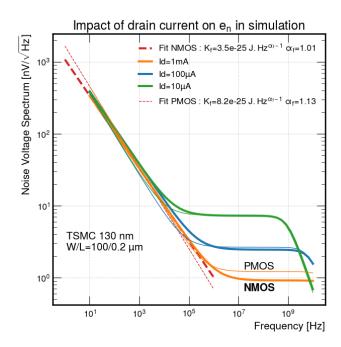

|    |                       | 2.3.2 Sources de bruit d'un MOSFET                      | 18   |

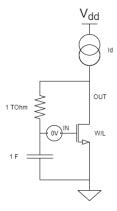

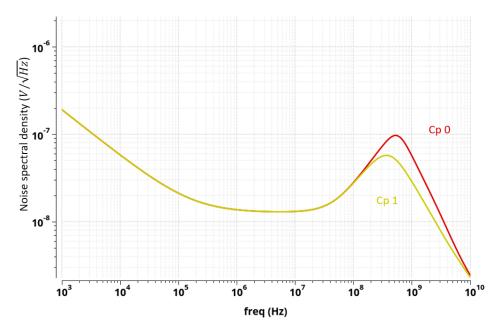

|    |                       | 2.3.2.1 Simulation                                      | 19   |

|    | 2.4                   | Instrumenter un détecteur                               | 20   |

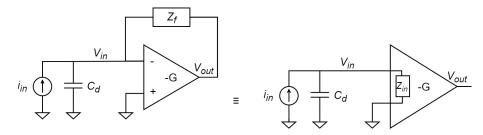

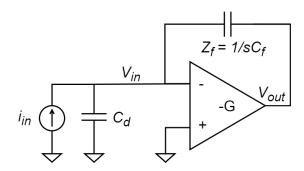

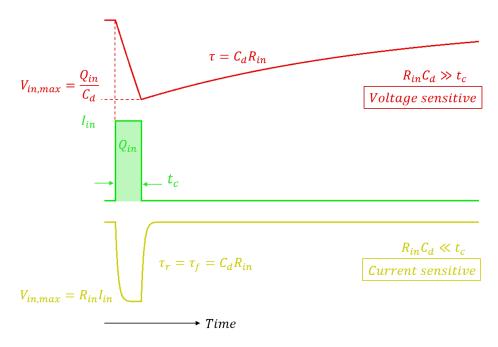

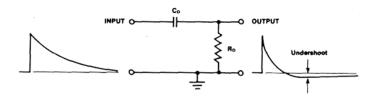

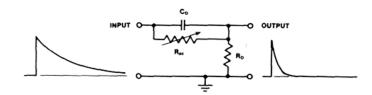

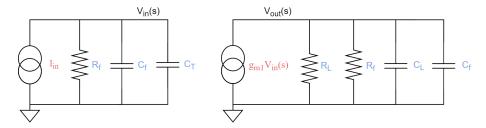

|    |                       | 2.4.1 Préamplificateur à contre-réaction capacitive     | 22   |

|    |                       | 2.4.1.1 Impédance d'entrée                              | 22   |

|    |                       | 2.4.1.2 Étude du signal                                 | 23   |

|    |                       | 2.4.2 Préamplificateur à contre-réaction résistive      | 24   |

|    | 2.5                   | Conclusion                                              | 25   |

|    | 2.6                   | Bibliographie                                           | 25   |

| 3  | Des                   | scription d'ALTIROC                                     | 27   |

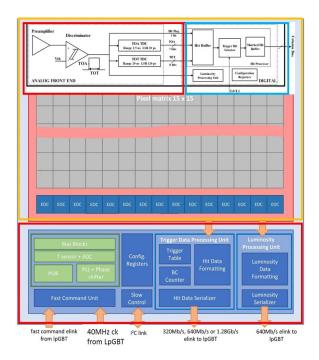

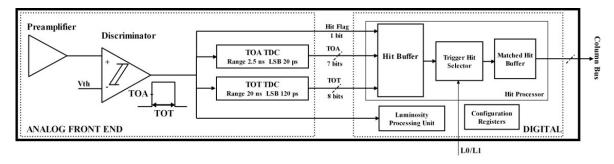

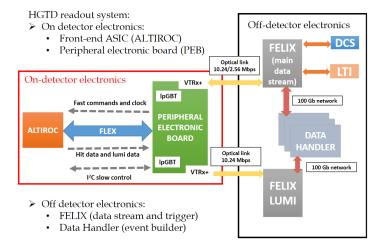

|    | 3.1                   | Architecture globale                                    | 28   |

|    | 3.2                   | Spécifications                                          | 29   |

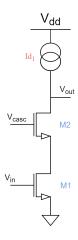

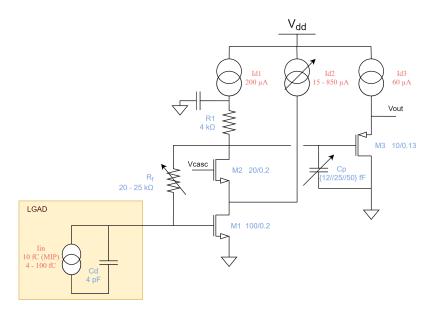

|    | 3.3                   | Préamplificateur d'ALTIROC                              | 29   |

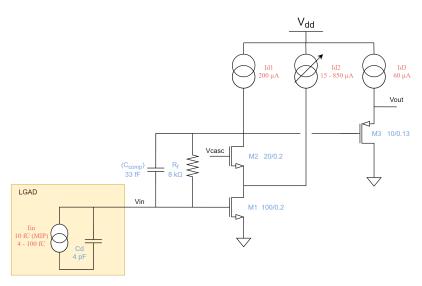

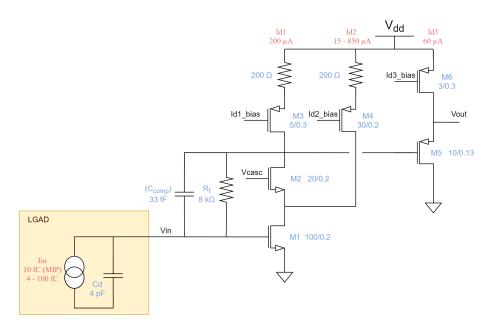

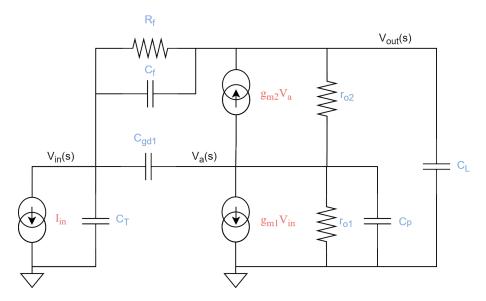

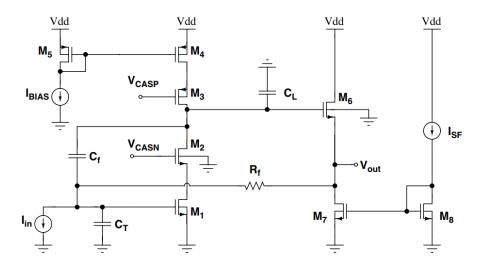

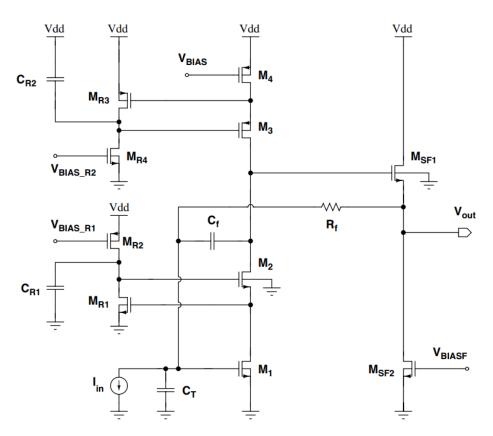

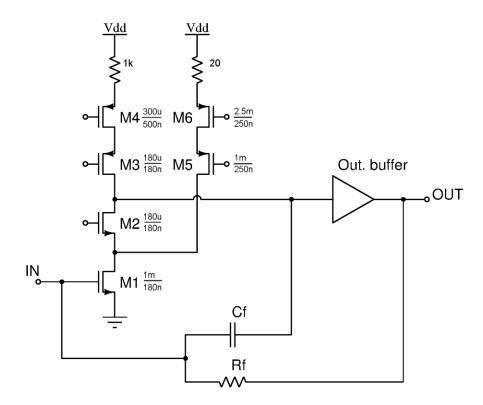

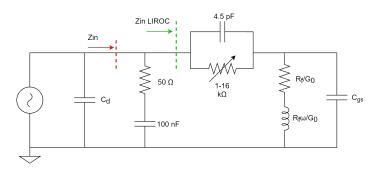

|    |                       | 3.3.1 Schéma                                            | 30   |

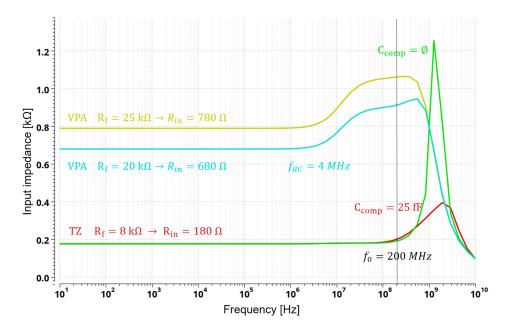

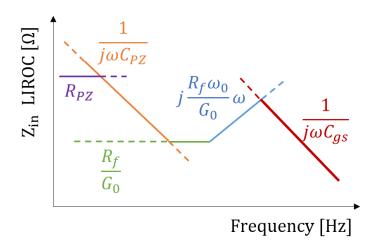

|    |                       | 3.3.2 Impédance d'entrée                                | 30   |

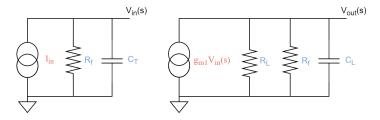

|    |                       | 3.3.3 Étude du signal                                   | 34   |

|    |                       | 3.3.3.1 Boucle ouverte                                  | 34   |

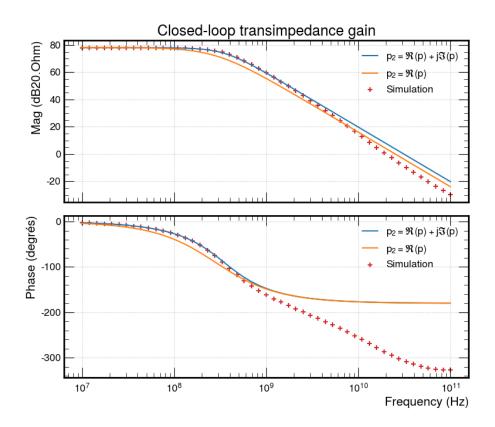

|    |                       | 3 3 3 2 Boucle fermée                                   | 36   |

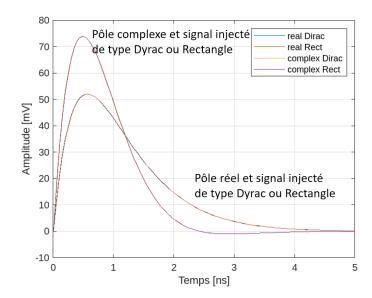

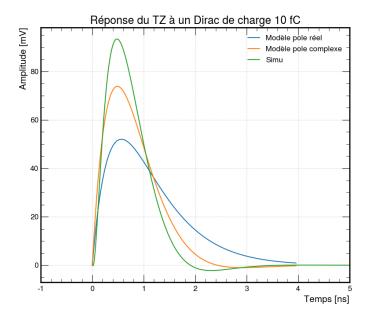

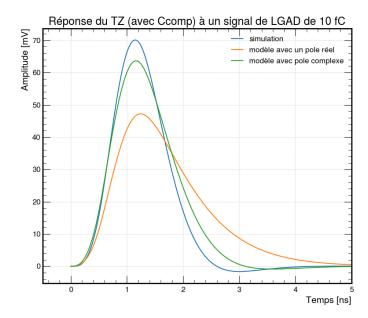

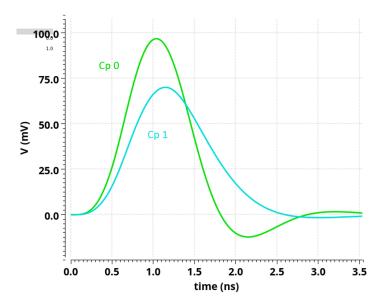

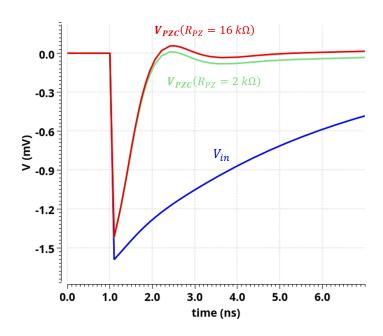

|   |     |          | 3.3.3.3 Réponse temporelle du préamplificateur                          | 39 |

|---|-----|----------|-------------------------------------------------------------------------|----|

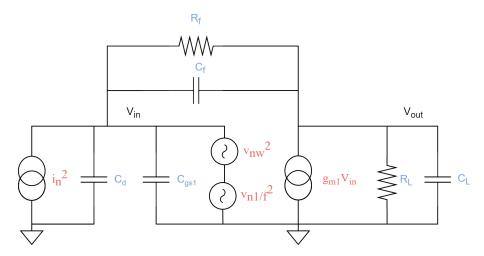

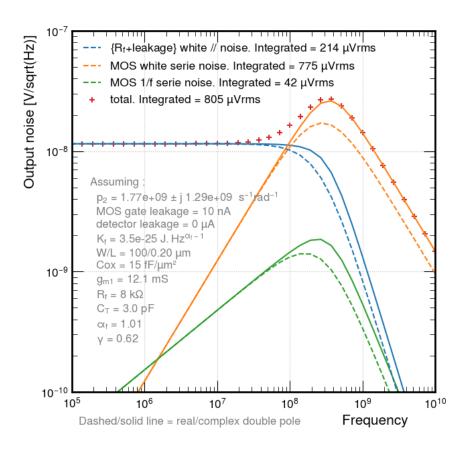

|   |     | 3.3.4    | Etude du bruit                                                          | 41 |

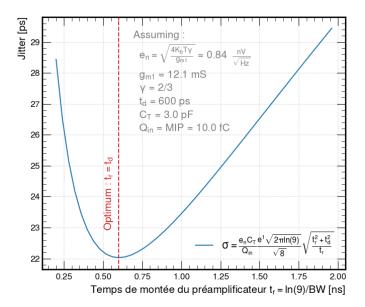

|   |     | 3.3.5    | Etude du jitter                                                         | 45 |

|   |     | 3.3.6    |                                                                         | 47 |

|   | 3.4 | Discri   |                                                                         | 49 |

|   | 3.5 |          |                                                                         | 50 |

|   | 3.6 |          |                                                                         | 51 |

|   | 3.7 |          |                                                                         | 52 |

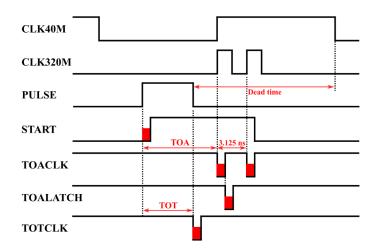

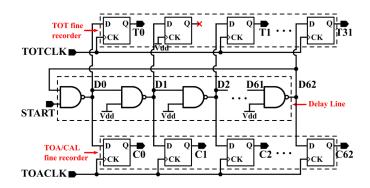

|   |     | 3.7.1    | •                                                                       | 52 |

|   |     |          |                                                                         | 53 |

|   |     | 311.12   |                                                                         | 53 |

|   |     |          | •                                                                       | 54 |

|   |     |          |                                                                         | 56 |

|   | 3.8 | Concl    | •                                                                       | 57 |

|   | 3.9 |          |                                                                         | 57 |

|   | 0.0 | Dibilo   | Stupine                                                                 | ٠. |

| 4 | Que | elles pe | erformances ALTIROC atteint-il?                                         | 59 |

|   | 4.1 | Introd   | luction                                                                 | 60 |

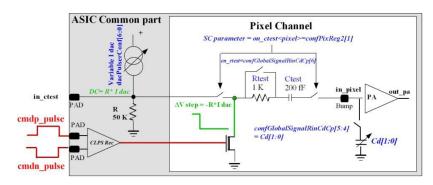

|   | 4.2 | Carac    | térisation sur banc de test                                             | 60 |

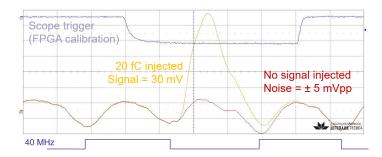

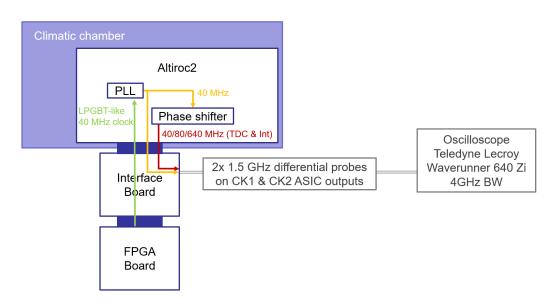

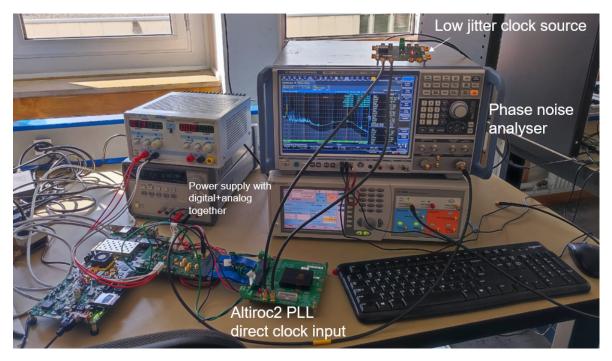

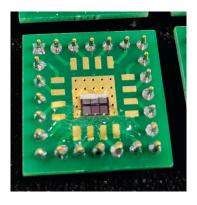

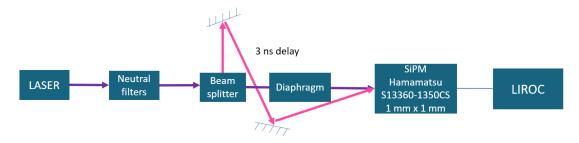

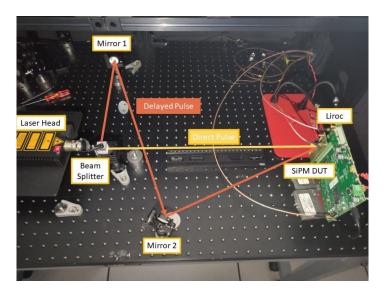

|   |     | 4.2.1    | Système de test                                                         | 60 |

|   |     | 4.2.2    | Seuil minimal de détection du front-end                                 | 61 |

|   |     |          | 4.2.2.1 Méthodologie                                                    | 61 |

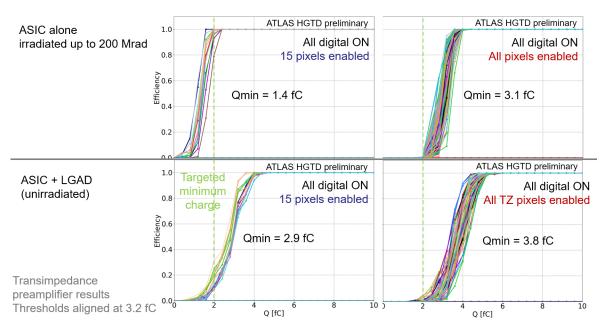

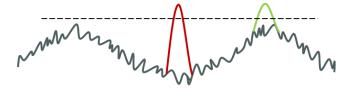

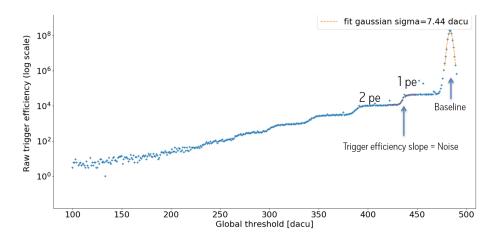

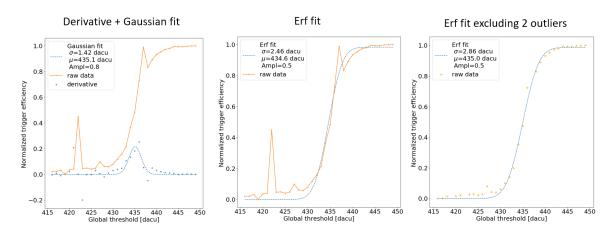

|   |     |          | 4.2.2.2 Résultats                                                       | 62 |

|   |     |          | 4.2.2.3 Impact de l'activité digitale sur le seuil minimal de détection | 65 |

|   |     | 4.2.3    | Calibration pour la mesure de temps                                     | 66 |

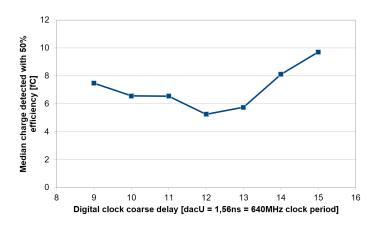

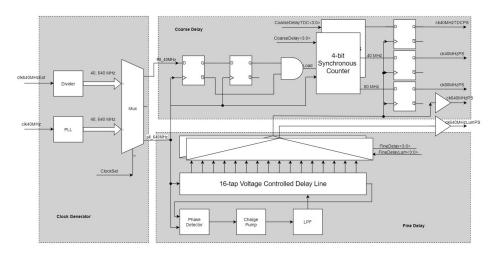

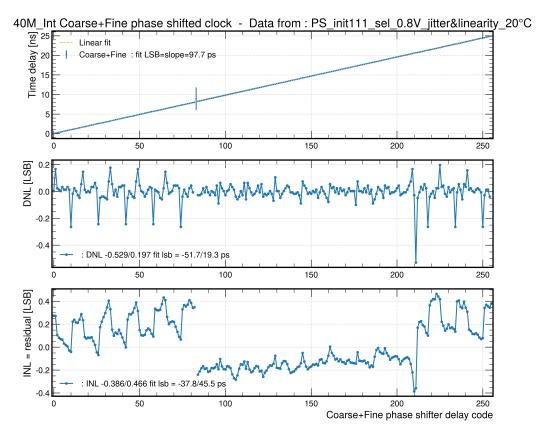

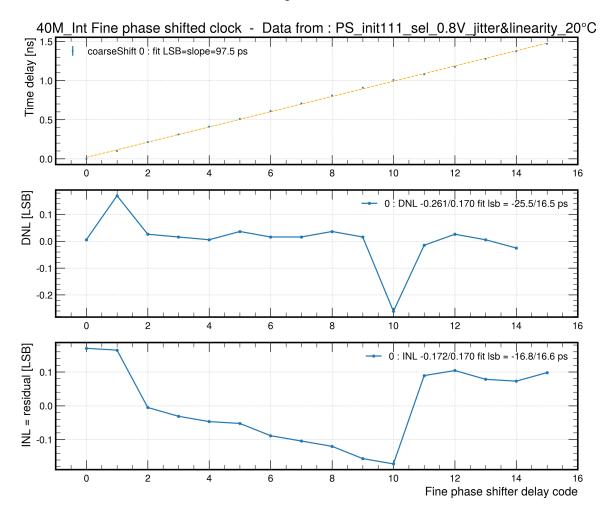

|   |     |          | 4.2.3.1 Calibration du phase shifter                                    | 67 |

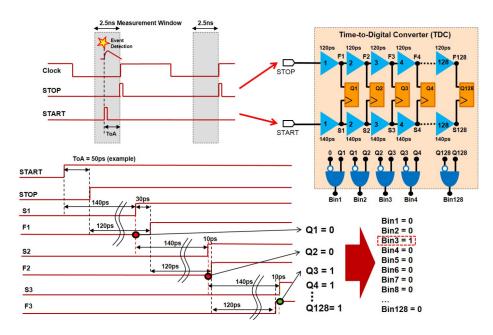

|   |     |          | 4.2.3.2 Calibration des TDC                                             | 69 |

|   |     | 4.2.4    | Correction du time-walk                                                 | 70 |

|   |     |          | 4.2.4.1 Description du phénomène                                        | 70 |

|   |     |          | 4.2.4.2 Résultats                                                       | 71 |

|   |     |          | 4.2.4.3 Conséquences sur la topologie du préamplificateur               | 71 |

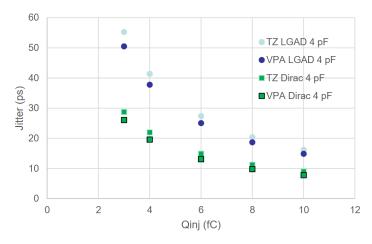

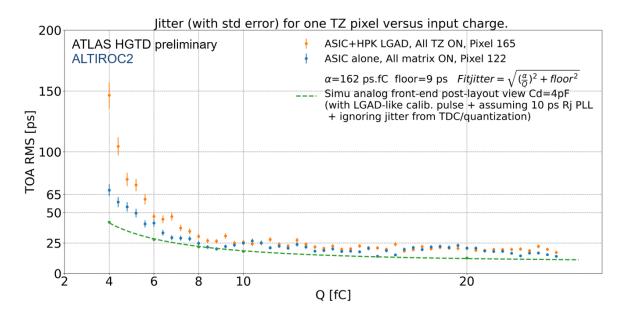

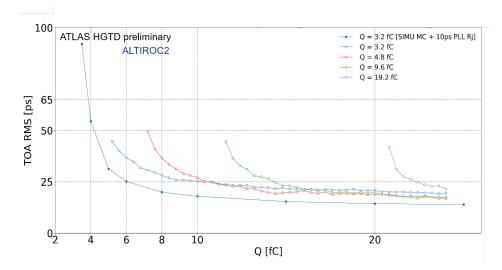

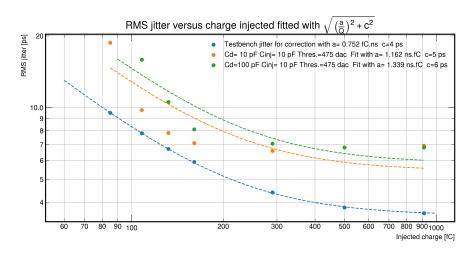

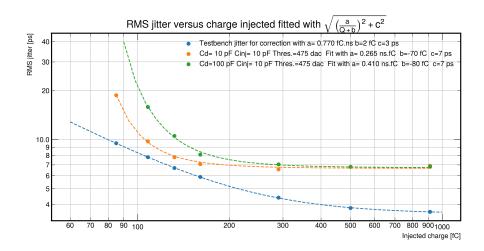

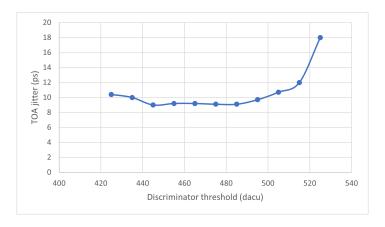

|   |     | 4.2.5    | Caractérisation du jitter                                               | 72 |

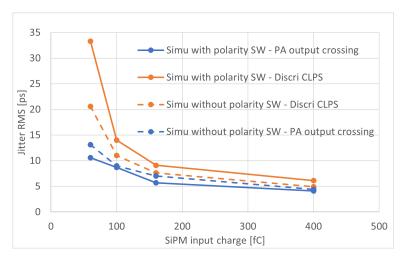

|   |     |          | 4.2.5.1 Modélisation du jitter                                          | 72 |

|   |     |          | 4.2.5.2 Résultats                                                       | 73 |

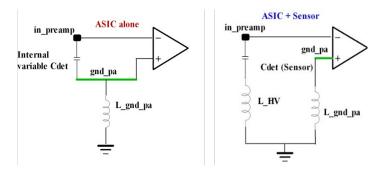

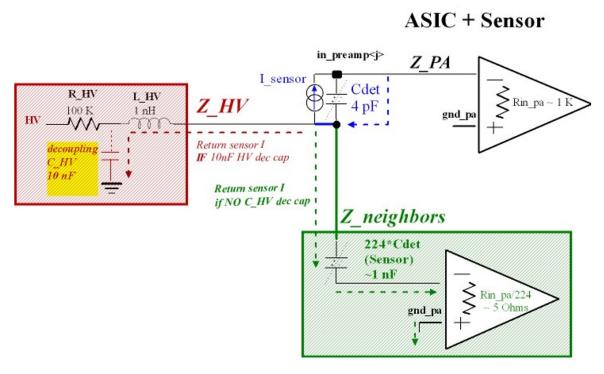

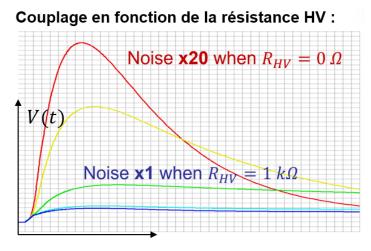

|   |     |          | 4.2.5.3 Une modélisation erronée de la capacité détecteur?              | 74 |

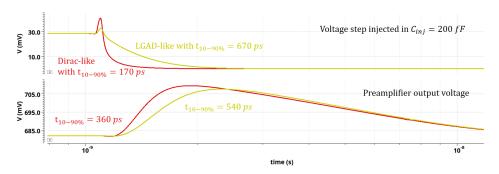

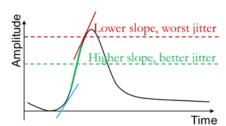

|   |     |          | 4.2.5.4 Impact de la forme du pulse sur le jitter                       | 74 |

|   |     |          | 4.2.5.5 Comparaison avec le jitter attendu                              | 75 |

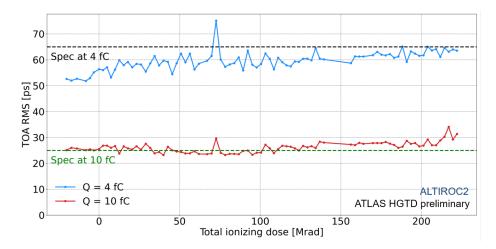

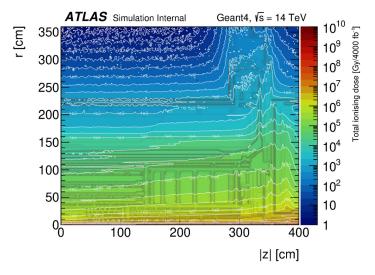

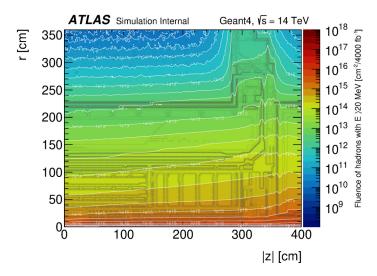

|   |     |          | 4.2.5.6 Évolution du jitter avec la dose ionisante totale absorbée      | 76 |

|   |     | 4.2.6    | Importance du floorplan                                                 | 77 |

|   | 4.3 | Carac    | térisation avec LGAD en faisceau-test                                   | 78 |

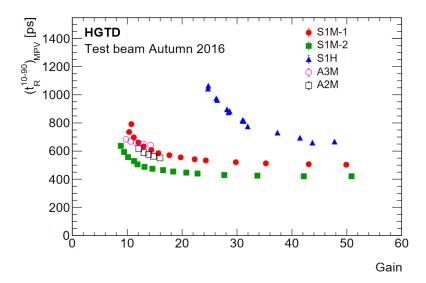

|   |     | 4.3.1    | Résultats d'ALTIROC1                                                    | 78 |

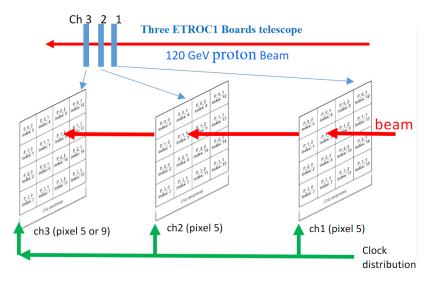

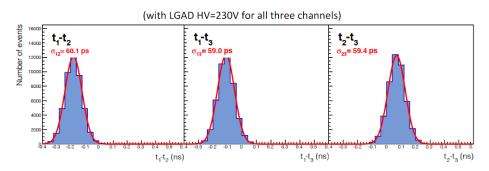

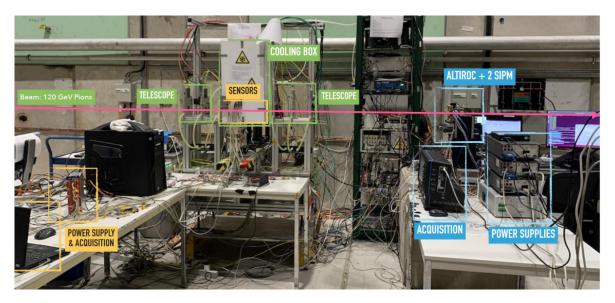

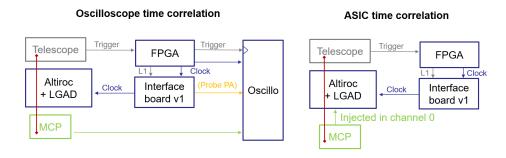

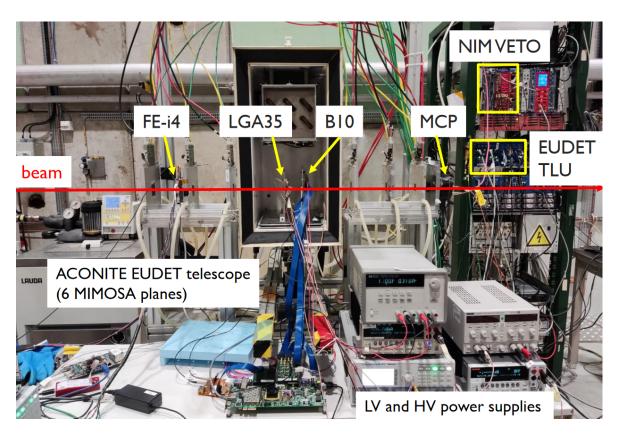

|   |     |          | 4.3.1.1 Description du banc de test                                     | 78 |

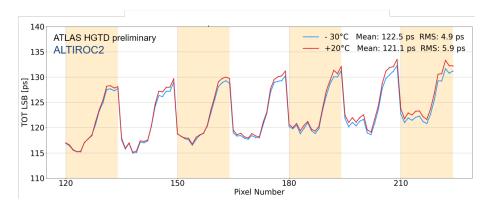

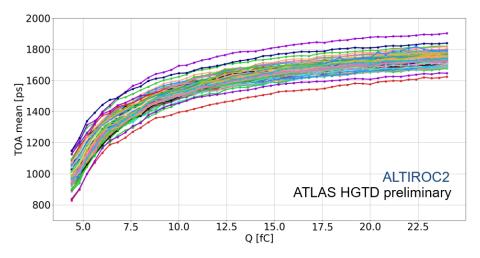

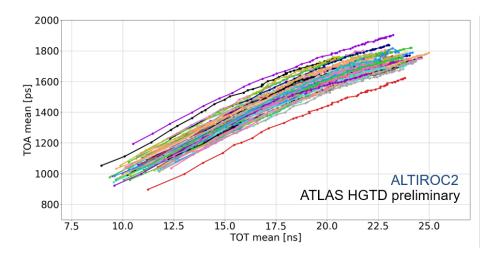

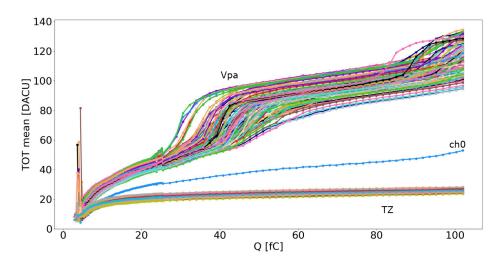

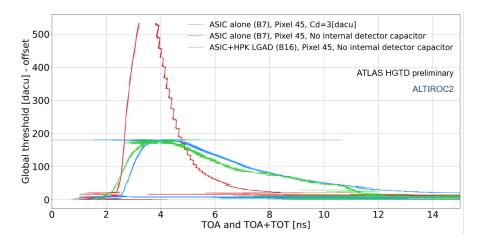

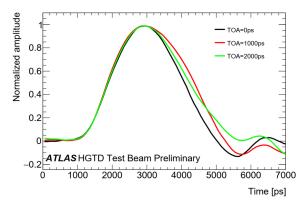

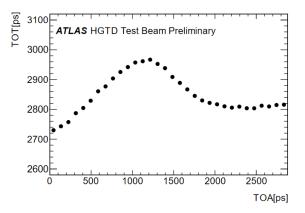

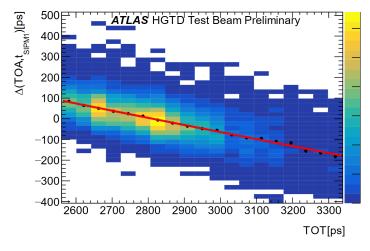

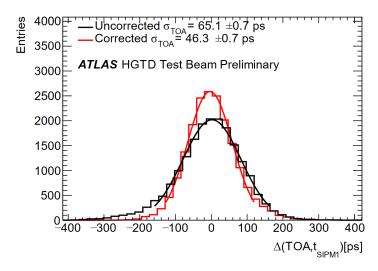

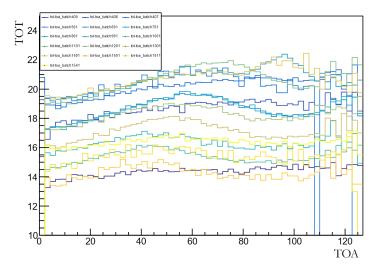

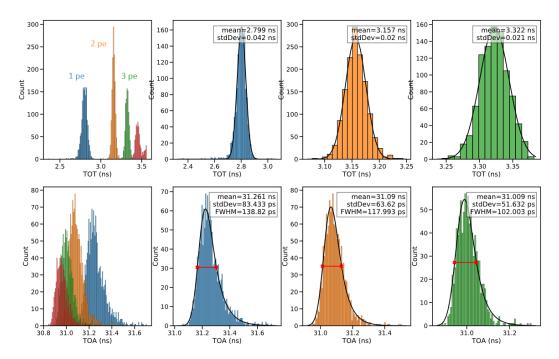

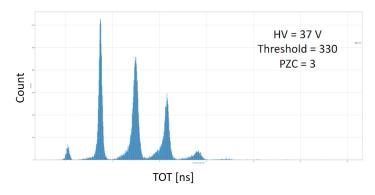

|   |     |          | 4.3.1.2 Dépendance du TOT au TOA                                        | 79 |

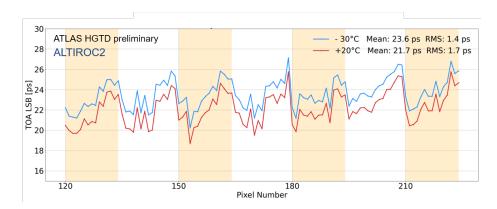

|   |     | 4.3.2    | Résultats d'ALTIROC2                                                    | 82 |

|   |     |          | 4.3.2.1 Description du banc de test                                     | 82 |

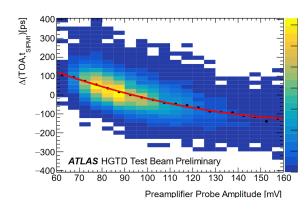

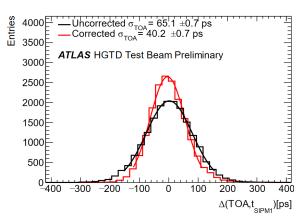

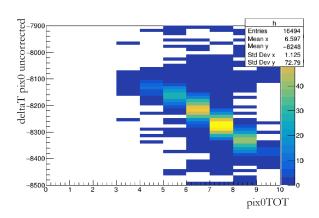

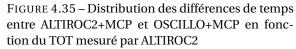

|   |     |          | 4.3.2.2 Dépendance du TOT au TOA                                        | 83 |

|   |     | 4.3.3    | Conclusion                                                              | 84 |

|   | 4 4 | Riblio   | ographie                                                                | 86 |

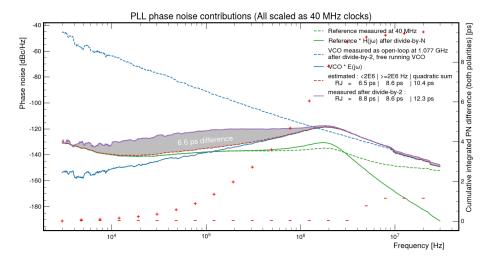

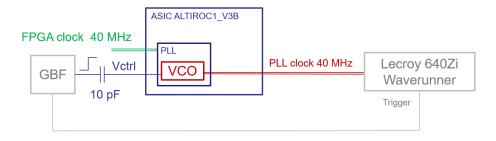

| 5 | Car        | actáric        | ation d'une boucle à verrouillage de phase                                                                     | 87           |

|---|------------|----------------|----------------------------------------------------------------------------------------------------------------|--------------|

| J | 5.1        |                |                                                                                                                | 88           |

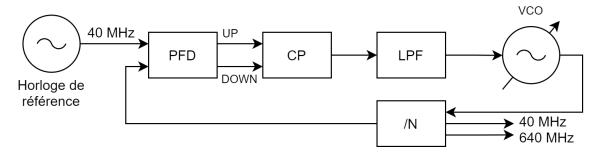

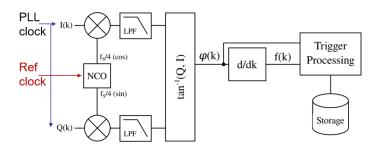

|   | 3.1        |                |                                                                                                                | 88           |

|   |            | 5.1.2          | <u> </u>                                                                                                       | 89           |

|   |            | 5.1.3          |                                                                                                                | 90           |

|   |            | 5.1.4          | taran da antara da a | 92           |

|   |            | 5.1.5          |                                                                                                                | 93           |

|   |            | 3.1.3          |                                                                                                                | 93           |

|   |            |                | 0                                                                                                              | 94           |

|   |            |                | 1                                                                                                              | 94           |

|   |            |                |                                                                                                                | 94           |

|   |            |                | 1 0                                                                                                            | 94           |

|   |            |                |                                                                                                                | 95           |

|   |            |                |                                                                                                                | 95<br>95     |

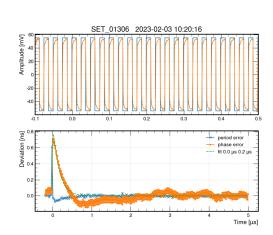

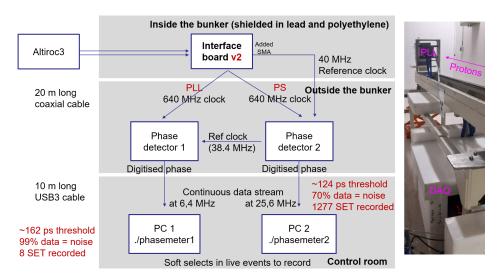

|   | 5.2        | Carac          |                                                                                                                | 95           |

|   | 3.2        | 5.2.1          |                                                                                                                | 95           |

|   |            |                |                                                                                                                | 95<br>96     |

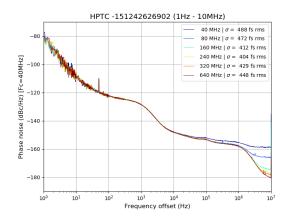

|   |            | 3.2.2          | 1                                                                                                              | 96           |

|   |            |                | •                                                                                                              | 97           |

|   |            |                | 1 1                                                                                                            | 97           |

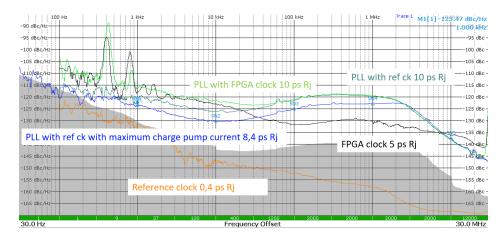

|   |            | 5.2.3          |                                                                                                                | 97<br>100    |

|   |            | 5.2.5          | •                                                                                                              | 100          |

|   |            |                | •                                                                                                              | 100<br>100   |

|   |            |                |                                                                                                                | 100<br>101   |

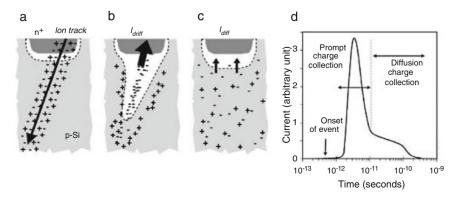

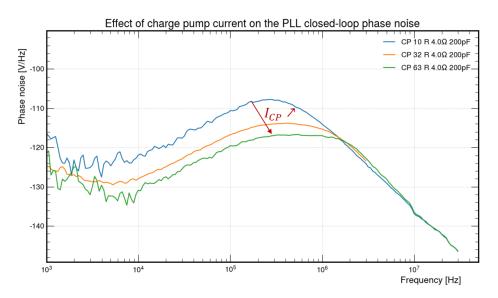

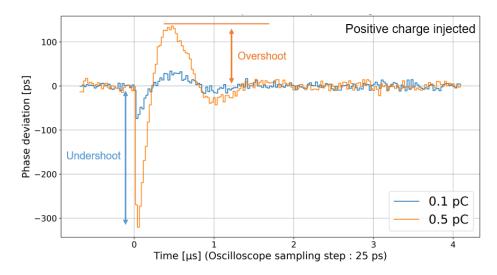

|   | 5.3        | Carac          |                                                                                                                | 101<br>104   |

|   | 3.3        | 5.3.1          |                                                                                                                | 104<br>104   |

|   |            |                |                                                                                                                | 104<br>105   |

|   | E 4        | 5.3.2          | 1                                                                                                              | 103<br>108   |

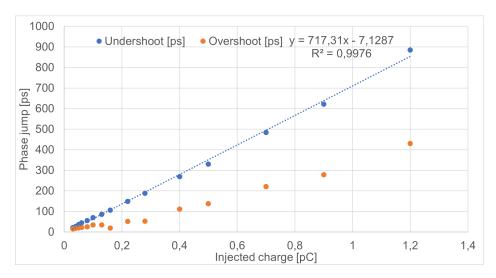

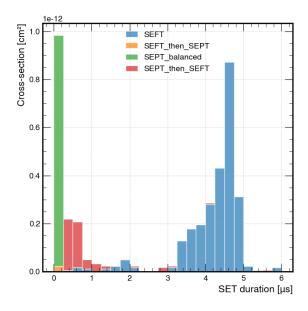

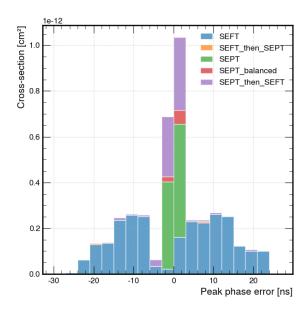

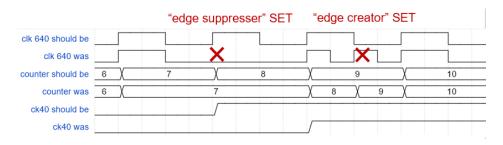

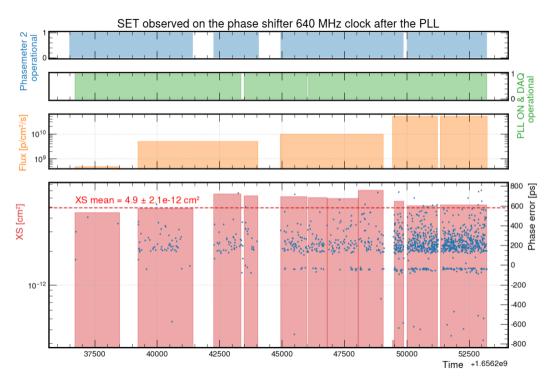

|   | 5.4        | 5.4.1          | 1 0                                                                                                            | 108<br>108   |

|   |            |                | •                                                                                                              |              |

|   |            | 5.4.2          |                                                                                                                | 111          |

|   |            | 5.4.3          | Discussion                                                                                                     |              |

|   |            |                |                                                                                                                |              |

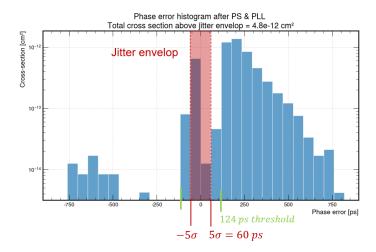

|   | 5.5        |                | ième campagne de SET                                                                                           |              |

|   |            | 5.5.1          | 1 0                                                                                                            | 118          |

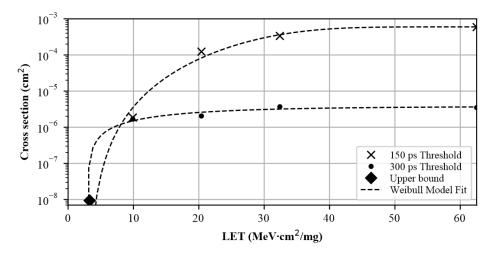

|   |            | 5.5.2<br>5.5.3 | •                                                                                                              | l 18<br>l 19 |

|   | E C        | 0.0.0          |                                                                                                                |              |

|   | 5.6<br>5.7 | _              |                                                                                                                | 123<br>124   |

|   |            |                |                                                                                                                | ı 24<br>l 24 |

|   | 5.8        | DIDIIO         | grapine                                                                                                        | 124          |

| 6 | Mes        | ure de         | temps en photon unique avec des SiPM                                                                           | 27           |

|   |            |                |                                                                                                                | 128          |

|   |            | 6.1.1          |                                                                                                                | 128          |

|   |            | 6.1.2          |                                                                                                                | 128          |

|   |            | 6.1.3          | •                                                                                                              | 129          |

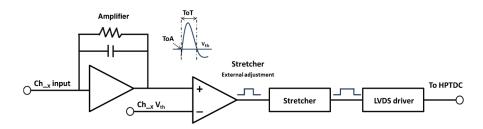

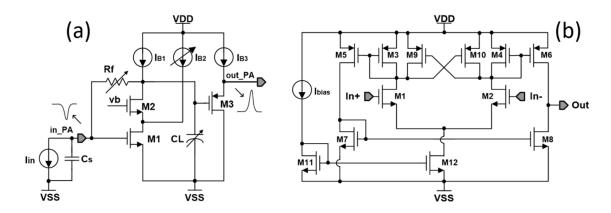

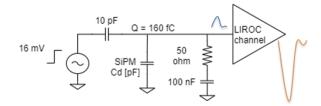

|   | 6.2        | Descr          |                                                                                                                | 130          |

|   |            |                |                                                                                                                | 130          |

|   |            | 6.2.2          |                                                                                                                | 130          |

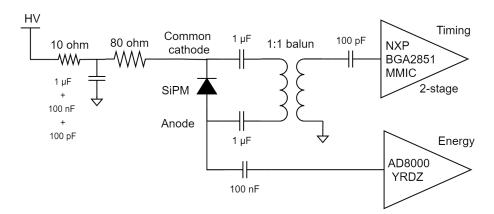

|   |            |                | •                                                                                                              | 130          |

|   |            |                |                                                                                                                | 131          |

|   | 6.3        | Perfo          |                                                                                                                | 134          |

|   | -          | 6.3.1          |                                                                                                                | 134          |

|   |            | 6.3.2          | Mesures avec un SiPM couplé à un cristal                                                                       |              |

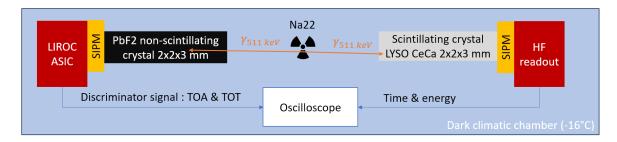

|   |     |        | 6.3.2.1    | Description de la référence de temps                           | 137 |

|---|-----|--------|------------|----------------------------------------------------------------|-----|

|   |     |        | 6.3.2.2    | Performances de la référence de temps                          | 137 |

|   |     |        | 6.3.2.3    | Description de la détection de gamma côté LIROC                | 138 |

|   |     |        | 6.3.2.4    | Sélection en énergie des évènements coïncidents                |     |

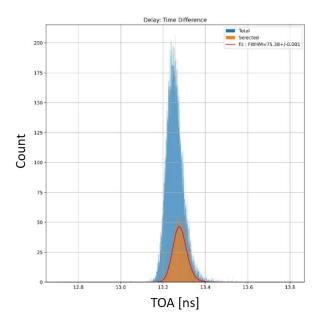

|   |     |        | 6.3.2.5    | Méthodologie d'analyse                                         | 140 |

|   |     |        | 6.3.2.6    | Performances de LIROC + SiPM FBK UHD-DA                        |     |

|   |     |        | 6.3.2.7    | Performances de LIROC + SiPM FBK M3                            | 142 |

|   |     | 6.3.3  | Complé     | Ement d'analyse                                                | 143 |

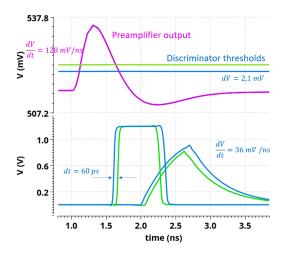

|   |     |        | 6.3.3.1    | Estimation du bruit et de la pente du signal                   | 143 |

|   |     |        | 6.3.3.2    | Comparaison avec le jitter attendu mesuré au pulser            | 145 |

|   |     |        | 6.3.3.3    | Caractérisation des SiPM FBK                                   | 145 |

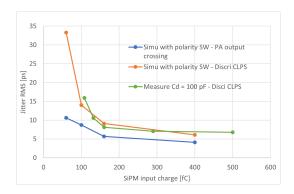

|   |     |        | 6.3.3.4    | Simulation de LIROC couplé à un SiPM FBK de SPAD 40 $\mu m$    | 145 |

|   |     | 6.3.4  | Mesure     | avec un LASER                                                  | 147 |

|   |     |        | 6.3.4.1    | Résolution temporelle en photon unique                         | 147 |

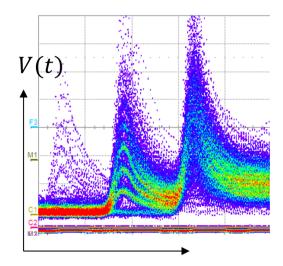

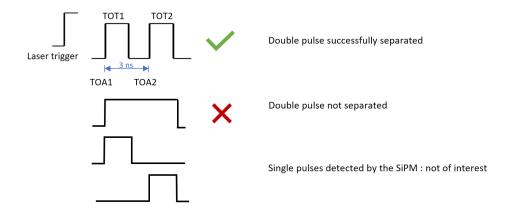

|   |     |        | 6.3.4.2    | Séparation de pulses doubles                                   | 148 |

|   | 6.4 | Concl  | usion      |                                                                | 152 |

|   | 6.5 | Biblio | graphie    |                                                                | 152 |

| 7 | Con | clusio | n généra   | le et perspectives                                             | 153 |

| 8 | Ann | exes   |            |                                                                | 157 |

|   | 8.1 | Variar | nte de l'a | nalyse en boucle ouverte du préamplificateur en transimpédance | 157 |

|   | 8.2 | Biblio | graphie    |                                                                | 158 |

# Liste des figures

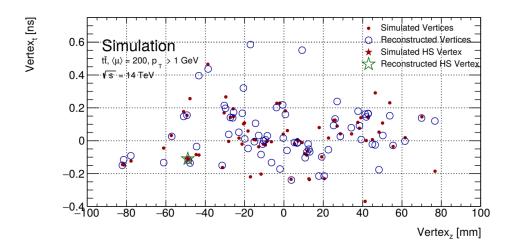

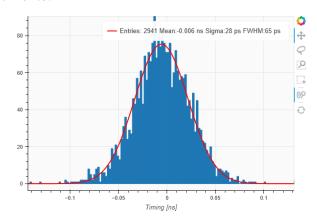

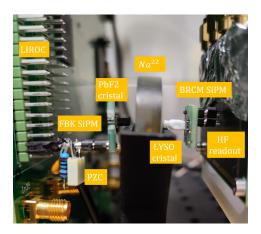

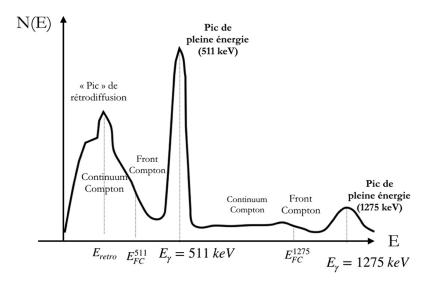

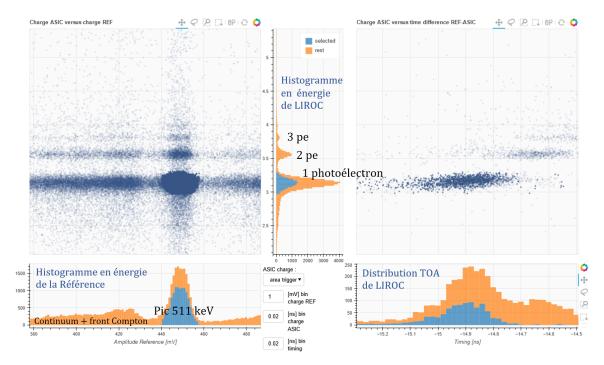

| 1.1  | Visualisation des vertex primaires dans le plan z-t, simulant un événement dit Hard Scatter (HS) superposé à des interactions de pile-up pour un nombre moyen de collisions de 200. Les vertex reconstruits sont marqués par des cercles bleus alors que le vertex de l'évènement d'intérêt (HS) est représenté par une étoile verte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1   |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

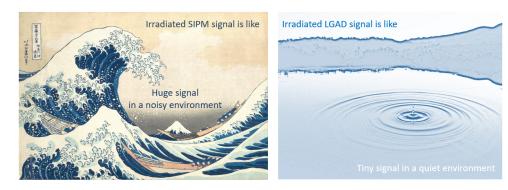

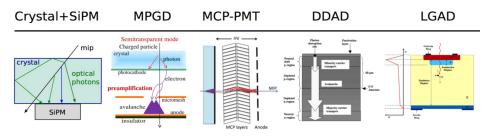

| 2.1  | Bien choisir son détecteur : SiPM versus LGAD, d'après Ted Liu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3   |

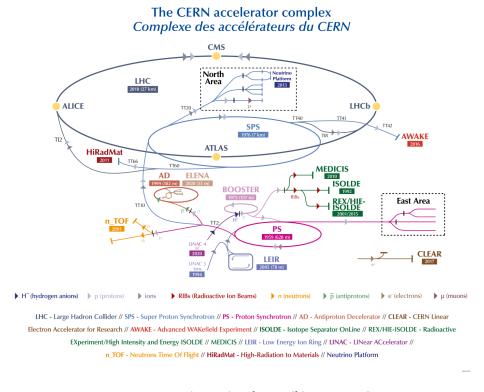

| 2.2  | Représentation des accélérateurs au CERN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4   |

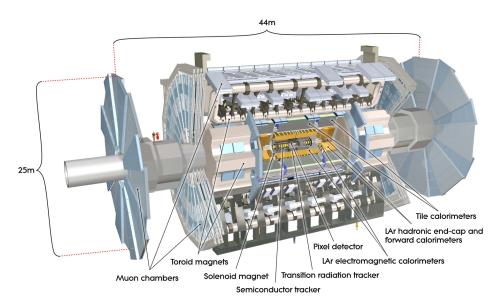

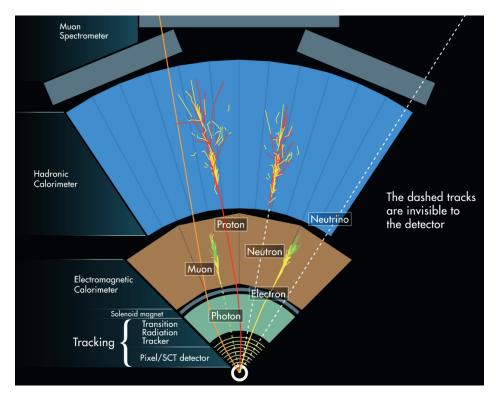

| 2.3  | Vue schématique du détecteur ATLAS (avant upgrade Phase-II HL-LHC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5   |

| 2.4  | Vue transversale du détecteur ATLAS avec de multiples interactions types                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 6   |

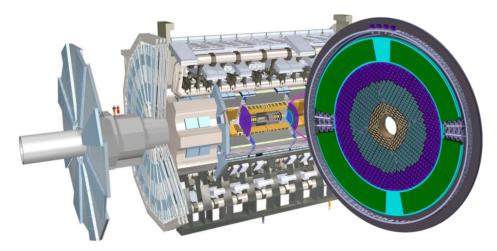

| 2.5  | Le détecteur HGTD au sein d'ATLAS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7   |

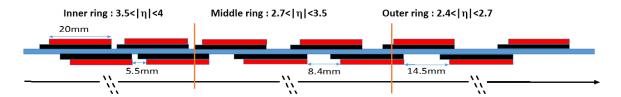

| 2.6  | Vue en coupe du détecteur HGTD illustrant le chevauchement des zones de détec-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

|      | tion (en rouge). L'électronique est en noir, la plaque de refroidissement en bleu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 8   |

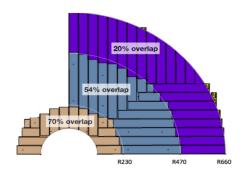

| 2.7  | Vue de face (quart) d'HGTD montrant la variation du chevauchement en fonction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

|      | du rayon                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 8   |

| 2.8  | Panel de détecteurs pour la mesure de temps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 9   |

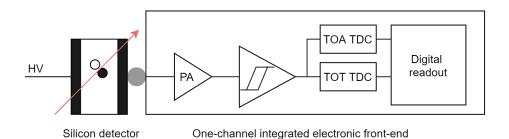

| 2.9  | Architecture électronique de lecture d'un détecteur silicium                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 9   |

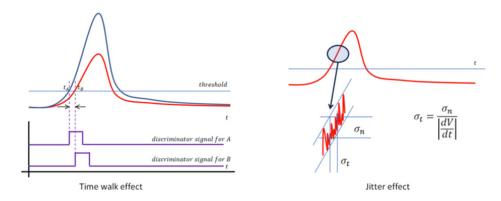

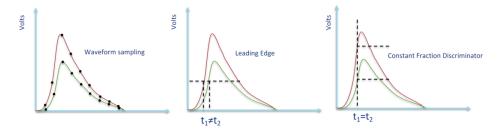

| 2.10 | Effet du timewalk (gauche) et du jitter électronique (droite) [2]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 9   |

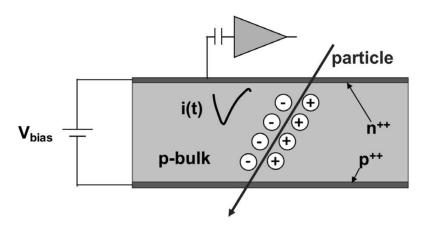

| 2.11 | Schéma en coupe d'un jonction PN traversée par une particule ionisante [5]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 10  |

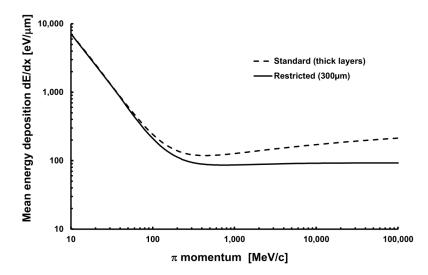

| 2.12 | Energie moyenne déposée dans le silicium en fonction de la quantité de mouvement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

|      | du pion (formule de Bethe et Bloch) [5]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 11  |

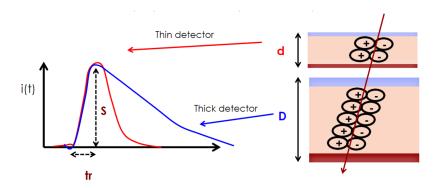

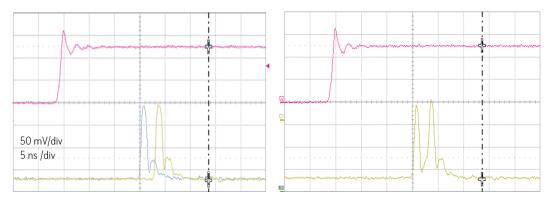

| 2.13 | Profils temporel du courant issus de détecteur silicium fin et épais, d'après Nicolò                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

|      | Cartiglia                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 12  |

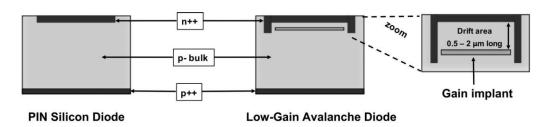

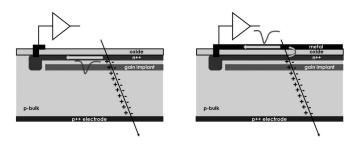

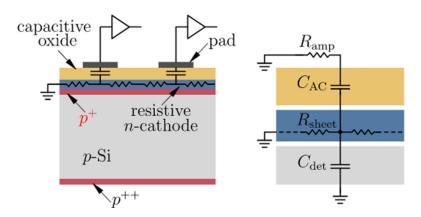

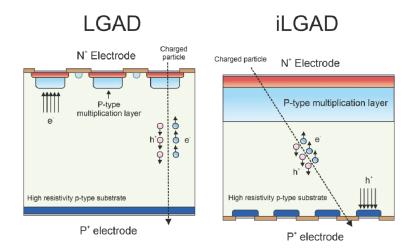

| 2.14 | Schéma en coupe d'une diode PIN et d'un LGAD montrant une profondeur de la                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

|      | couche $p^+$ comprise entre 0.5 et 2 $\mu$ m, d'après [5]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 12  |

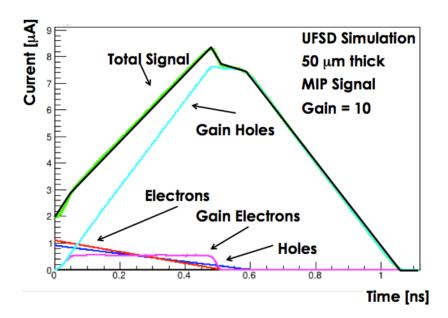

| 2.15 | Simulation WF2 du courant total induit sur la cathode par un MIP traversant un                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

|      | UFSD (Ultra-Fast Silicon Detector, nouvelle génération de LGAD), d'après Nicolò                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| 0.10 | Cartiglia                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 13  |

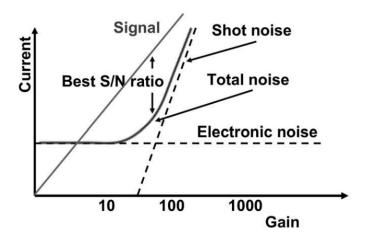

|      | Évolution du signal et du bruit en fonction du gain interne d'un LGAD [5]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 14  |

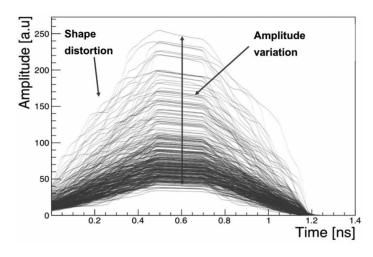

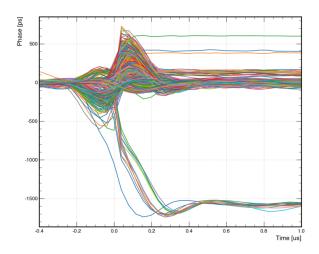

| 2.17 | Simulation WF2 des effets combinés de Landau et des non-uniformités du champ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

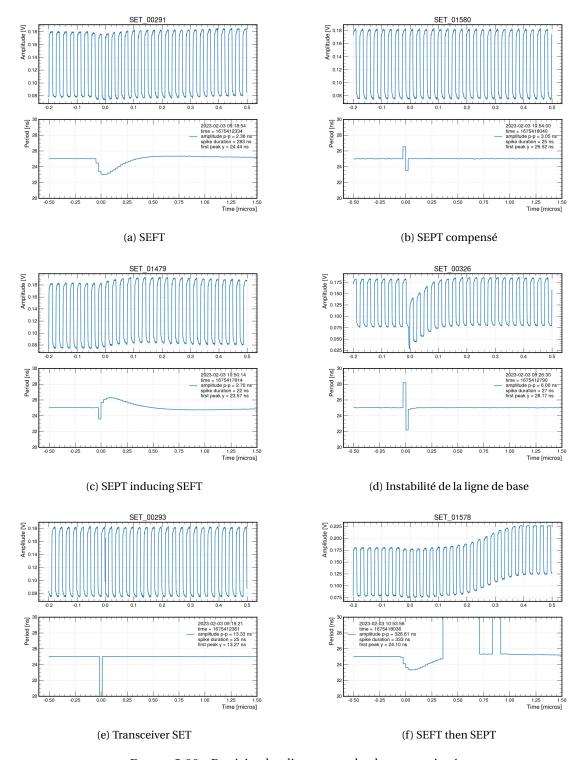

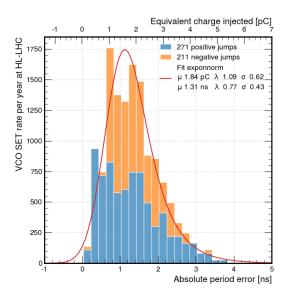

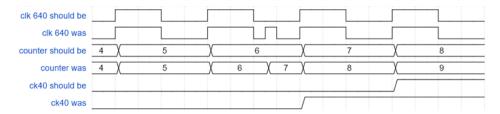

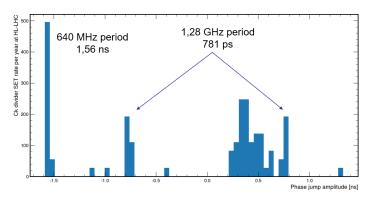

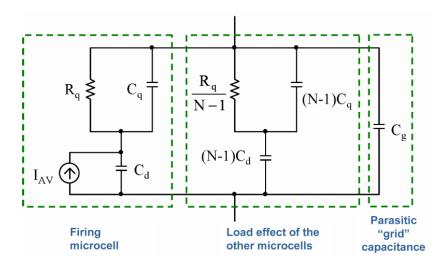

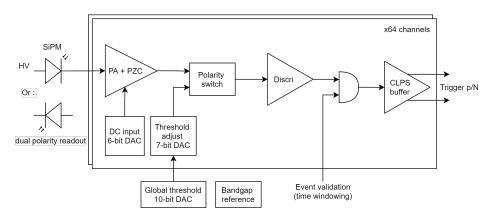

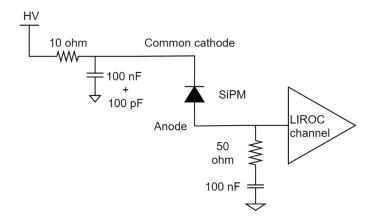

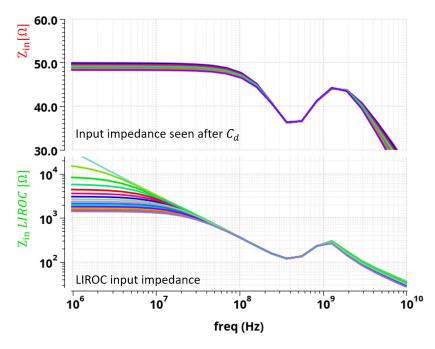

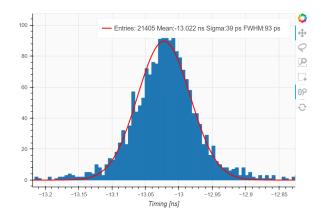

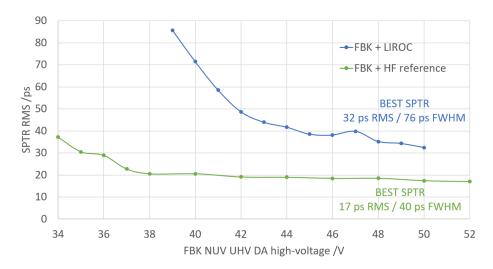

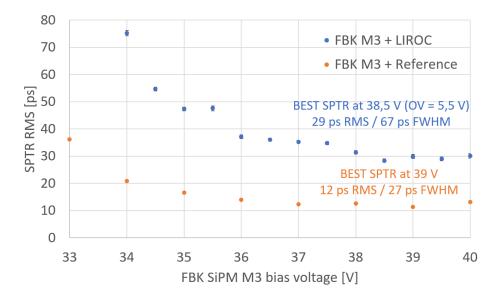

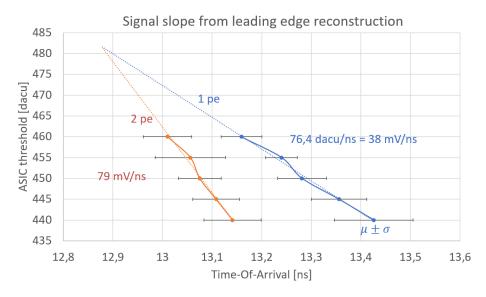

|      | électrique sur le signal induit dans un UFSD de 50 μm d'épaisseur par un MIP avec                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1.4 |