### Development of a self-sustained wireless sensor node. Sébastien Guigue

#### ▶ To cite this version:

Sébastien Guigue. Development of a self-sustained wireless sensor node.. Electronics. Université de Bordeaux, 2024. English. NNT: 2024BORD0082 . tel-04635678

### HAL Id: tel-04635678 https://theses.hal.science/tel-04635678v1

Submitted on 4 Jul2024

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THÈSE PRÉSENTÉE POUR OBTENIR LE GRADE DE DOCTEUR DE L'UNIVERSITÉ DE BORDEAUX

ÉCOLE DOCTORALE DES SCIENCES PHYSIQUES ET DE L'INGÉNIEUR

SPÉCIALITÉ ELECTRONIQUE

### Par Sébastien Guigue

# Développement, intégration et prototypage d'un noeud-capteur autonome à récupération d'énergie pour réseaux de capteurs sans fils

Sous la direction de : Thierry Taris Jean-Baptiste Begueret

Soutenue le 02 Mai2024

Membres du jury :

| М. | Shahriar MIRABBASI     | Professeur d'Université | Univ. of British Columbia | Rapporteur            |

|----|------------------------|-------------------------|---------------------------|-----------------------|

| М. | Hervé BARTHELEMY       | Professeur d'Université | Université de Toulon      | Rapporteur            |

| М. | David DUBUC            | Professeur d'Université | Université Paul Sabatier  | Président             |

| М. | Pierre COUROUVE        | Ingénieur               | CEA Leti                  | Examinateur           |

| М. | Thierry TARIS          | Professeur d'Université | Bordeaux INP              | Directeur de thèse    |

| М. | Jean-Baptiste BEGUERET | Professeur d'Université | Université de Bordeaux    | Co-Directeur de thèse |

|    |                        |                         |                           |                       |

| М. | Camille LEROUX         | Maitre de Conférence    | Bordeaux INP              | Invité/Co-encadrant   |

## ACKNOWLEDGMENTS

The completion of this thesis would not have been possible without the contribution of many individuals who played an important role in this work. Hence, this manuscript could not begin without some acknowledgments.

First of all, I express all my gratitude to Thierry Taris, Jean-Baptiste Begueret and Camille Leroux, my thesis advisors without whom this thesis would not have been possible. Thank you for your time, your patience, all the knowledge you brought me, and most of all, for your constant good mood. It has been a pleasure working with you during these three years.

I would like to thank all the member of the IMS Laboratory with whom I exchanged during these thesis. Working in the company of really kind people helped to make this journey more pleasant. Thus, I would like to thank Corentin, Anais, Maxime, Salime, Rémi, Martin, JC, Timothée, Sujeevan, Samir, Clement, Paul, Guillaume, Virgile, Henrique, Jonathan. I had a great time with all of you.

I would like to thank Leo, for your kindness, your sense of humour and all the climbing sessions we had together.

Thank you Nicolas for all the fun I had with you, great climbing moments and some discussions with had during hard moments. Spending time with you is always a pleasure.

Thank you Pierre for sharing my extreme humour since now 5 years, I have good memories of some great meals we had together and I promise, I will not forget our pact...

Thank you Maxandre for the fun we had together, the climbing sessions, for playing with me in the best band(IMHO), hope we will do some stuff together in the future.

Thank you Antoine(Saaaaaam) for sharing the early mornings in the lab with me. I have a special appreciation for your delightful taste in music but excepting this point, I am really happy for meeting you and sharing three years with of you.

Finally I want to thank my parents, my brother and my sister for encouraging me in my studies, for giving me the taste of well-done job, and for giving me values that contributed to who I am now.

Tired of lying in the sunshine, staying home to watch the rain You are young and life is long, and there is time to kill today And then one day you find ten years have got behind you No one told you when to run, you missed the starting gun

**Roger Waters**

# Contents

| Co       | onter | nts                                                                                                      |  |   | ii           |

|----------|-------|----------------------------------------------------------------------------------------------------------|--|---|--------------|

| Li       | st of | Figures                                                                                                  |  |   | $\mathbf{v}$ |

| Li       | st of | Tables                                                                                                   |  |   | vii          |

| G        | lossa | ry                                                                                                       |  |   | viii         |

| 1        | Intr  | roduction to Wireless Sensor Networks                                                                    |  |   | 3            |

|          | 1.1   | What is a Wireless Sensor Network?                                                                       |  |   | 3            |

|          |       | 1.1.1 Introduction                                                                                       |  |   | 3            |

|          |       | 1.1.2 Wireless Sensor Network Architecture                                                               |  |   | 4            |

|          |       | 1.1.3 Wireless Sensor Node                                                                               |  |   | 5            |

|          |       | 1.1.4 Wireless Sensor Network History                                                                    |  | • | 6            |

|          | 1.2   | Applications of Wireless Sensor Networks                                                                 |  |   | 9            |

|          |       | 1.2.1 Health Applications                                                                                |  |   | 9            |

|          |       | 1.2.2 Environmental Applications                                                                         |  | • | 10           |

|          |       | 1.2.3 Industrial Applications                                                                            |  |   | 11           |

|          |       | 1.2.4 Urban Applications                                                                                 |  |   | 12           |

|          |       | 1.2.5 Conclusion                                                                                         |  |   | 13           |

|          | 1.3   | Power Management                                                                                         |  |   | 14           |

|          |       | 1.3.1 Introduction                                                                                       |  |   | 14           |

|          |       | 1.3.2 Power sources                                                                                      |  |   | 14           |

|          | 1.4   | Challenges for Wireless Sensor Networks                                                                  |  |   | 15           |

|          |       | 1.4.1 Security $\ldots$ |  |   | 16           |

|          |       | 1.4.2 Robustness                                                                                         |  |   | 16           |

|          |       | 1.4.3 Management                                                                                         |  |   | 16           |

|          |       | 1.4.4 Power Consumption                                                                                  |  |   | 17           |

|          | 1.5   | System Overview                                                                                          |  |   | 18           |

|          |       | 1.5.1 Rectification                                                                                      |  |   | 18           |

|          |       | 1.5.2 Power Management                                                                                   |  |   | 19           |

|          |       | 1.5.3 Wake Up Generation                                                                                 |  |   | 20           |

|          |       | 1.5.4 Data Processing and Data Sending                                                                   |  |   | 20           |

|          |       | 1.5.5 Full System                                                                                        |  |   | 21           |

|          | 1.6   | Conclusion                                                                                               |  |   | 21           |

| <b>2</b> | Min   | nimalist Low Power Microcontroller Design                                                                |  |   | <b>22</b>    |

|          | 2.1   | Introduction                                                                                             |  |   | 22           |

|          | 2.2   | Technology Choice                                                                                        |  |   | 25           |

|          | 2.3   | Microcontroller Architecture                                                                             |  |   | 26           |

|   |              | 2.3.1          | Microcontroller Specifications                                                                                                         |

|---|--------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------|

|   |              | 2.3.2          | Initial Architecture                                                                                                                   |

|   |              | 2.3.3          | Global Architecture                                                                                                                    |

|   |              | 2.3.4          | The Control Unit                                                                                                                       |

|   |              | 2.3.5          | Processing Unit                                                                                                                        |

|   |              | 2.3.6          | The Boot Loader                                                                                                                        |

|   |              | 2.3.7          | Data size                                                                                                                              |

|   |              | 2.3.8          | Instruction Set                                                                                                                        |

|   |              | 2.3.9          | Memory                                                                                                                                 |

|   | 2.4          | Periph         |                                                                                                                                        |

|   |              | 2.4.1          | Communication Protocols                                                                                                                |

|   |              | 2.4.2          | Peripherals Interfacing                                                                                                                |

|   | 2.5          |                | Duty Cycling     37                                                                                                                    |

|   | 2.6          |                | $sis \dots sis$                                                                                                                        |

|   | $2.0 \\ 2.7$ | -              | $sion \dots \dots$               |

|   | 2.1          | Concit         | $51011 \dots \dots$                    |

| 3 | Wał          | e-Up           | Radios 44                                                                                                                              |

| - | 3.1          | -              | $action \dots \dots$             |

|   | 3.2          |                | pe Detector                                                                                                                            |

|   | 0.2          | 3.2.1          | Overview                                                                                                                               |

|   |              | 3.2.1          | Envelope Detector topology                                                                                                             |

|   |              | 3.2.2          | Design and implementation                                                                                                              |

|   |              | 3.2.3<br>3.2.4 | Matching Network                                                                                                                       |

|   | 3.3          |                | rator $\ldots$                                        |

|   | ა.ა          | 3.3.1          |                                                                                                                                        |

|   |              |                |                                                                                                                                        |

|   |              | 3.3.2          | Comparator topology                                                                                                                    |

|   | 2.4          | 3.3.3          | Design and implementation                                                                                                              |

|   | 3.4          |                | 1tor                                                                                                                                   |

|   |              | 3.4.1          | Overview                                                                                                                               |

|   |              | 3.4.2          | Correlator topology                                                                                                                    |

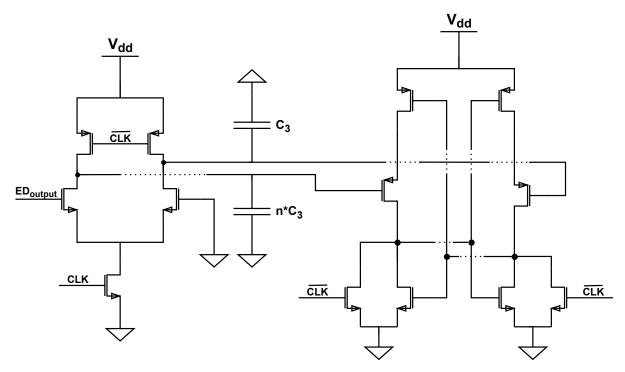

|   |              | 3.4.3          | Design and implementation 57                                                                                                           |

|   | 3.5          | Oscilla        |                                                                                                                                        |

|   |              | 3.5.1          | Overview                                                                                                                               |

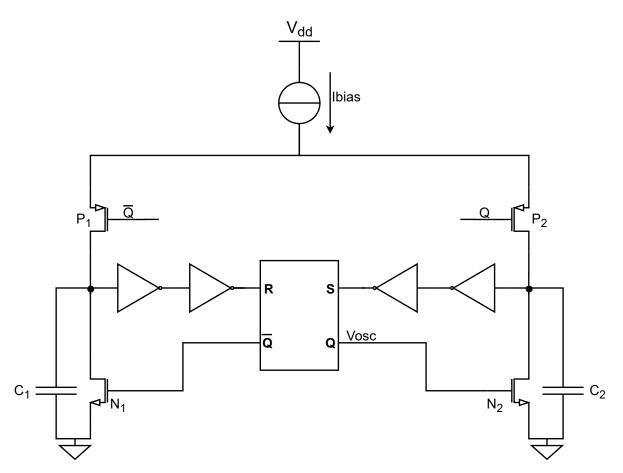

|   |              | 3.5.2          | Oscillator topology                                                                                                                    |

|   |              | 3.5.3          | Design and implementation                                                                                                              |

|   | 3.6          | Curren         | t Source $\ldots \ldots 62$   |

|   |              | 3.6.1          | Overview                                                                                                                               |

|   |              | 3.6.2          | Current source topology                                                                                                                |

|   |              | 3.6.3          | Design and implementation                                                                                                              |

|   | 3.7          | Democ          | ulation                                                                                                                                |

|   | 3.8          | Conclu         | $sion \ldots .$ |

|   |              |                |                                                                                                                                        |

| 4 | Full         | v              | n Study 75                                                                                                                             |

|   | 4.1          | Introd         | $action \dots \dots$             |

|   | 4.2          | Radio          | Transceiver and Sensor                                                                                                                 |

|   | 4.3          | Energy         | Harvester $\ldots$ $\ldots$ $75$                                                                                                       |

|   | 4.4          | Full Sy        | stem Autonomy Estimation                                                                                                               |

|   |              | 4.4.1          | RX/TX Mode                                                                                                                             |

|   |              | 4.4.2          | RX Only Mode                                                                                                                           |

|          | 4.5  | 4.4.3Burst Mode854.4.4Energy Harvesting Contribution87Conclusion88         | 7 |

|----------|------|----------------------------------------------------------------------------|---|

| <b>5</b> | Con  | clusion 91                                                                 | L |

|          | 5.1  | Introduction                                                               | 1 |

|          | 5.2  | Comparison to Other Works                                                  | 1 |

|          | 5.3  | Future Perspectives                                                        | 3 |

|          | 5.4  | Conclusion                                                                 | 5 |

|          | Refe | rences $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $96$ | 3 |

# List of Figures

| 1.1  | Applications covered by $IoT[1]$ .                                              | 4  |

|------|---------------------------------------------------------------------------------|----|

| 1.2  | Wireless Sensor Networks Topologies [2].                                        | 5  |

| 1.3  | Typical architecture of a Wireless Sensor Node.                                 | 6  |

| 1.4  | Principle of Sound Surveillance System                                          | 7  |

| 1.5  | Pictures of the System Developed by the MIT[8].                                 | 8  |

| 1.6  | Application Field of WSNs.                                                      | 9  |

| 1.7  | WSNs in Healthcare Overview.                                                    | 9  |

| 1.8  | Example of Wearable Device with Multiple Sensors[12]                            | 10 |

| 1.9  | WSNs in Environment Applications Overview.                                      | 10 |

| 1.10 | Acoustic Sensor for Environmental Monitoring[15].                               | 11 |

| 1.11 | WSNs in Industry Applications Overview.                                         | 11 |

|      | Example of WSNs Use in Logistics[16]                                            | 12 |

|      | WSNs in Urban Applications Overview.                                            | 12 |

|      | WSNs in Smart City[20]                                                          | 13 |

| 1.15 | Connected Devices Forecast[21]                                                  | 14 |

|      | Different Sources for Energy Harvesting[23].                                    | 15 |

|      | Wireless Sensor Node Duty Cycling[46]                                           | 17 |

|      | Wireless Sensor Node with Wake-Up Radio.                                        | 17 |

| 1.19 | (a) COTS Wireless Sensor Node, (b) Schematic View of the Node[47]               | 18 |

| 1.20 | Measurement Results of the Rectifier [47]                                       | 19 |

|      | Measurement Results of the Energy Harvester [47]                                | 19 |

|      | Generation of the Wake-Up Signal [47].                                          | 20 |

| 1.23 | Autonomy of the Node[47]                                                        | 21 |

| 0.1  |                                                                                 | 00 |

| 2.1  | Position of the MCU in a Node.                                                  | 22 |

| 2.2  | Example of an IoT Oriented MCU[55].                                             | 23 |

| 2.3  | Data-Path of the 8-bit CPU[63]                                                  | 26 |

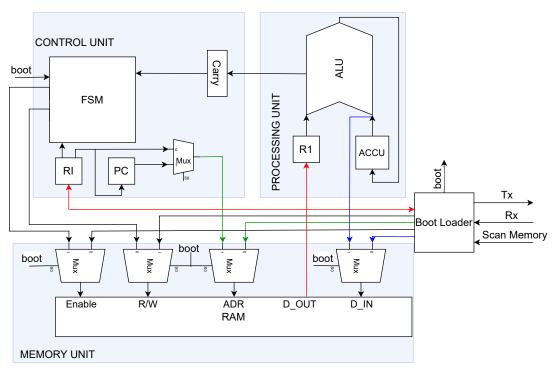

| 2.4  | Architecture of the MCU.                                                        | 28 |

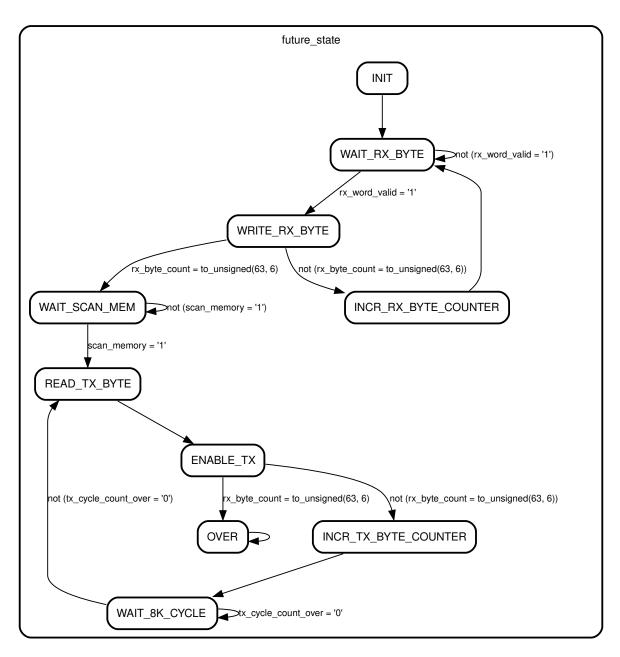

| 2.5  | Finite State Machine of the Boot Loader.                                        | 30 |

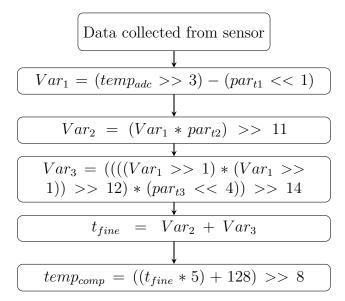

| 2.6  | Compensation Calculation for Temperature Measurement [64]. $\ldots$             | 31 |

| 2.7  | Size of Assembly Code in (a)16 and (b) 32 bits.                                 | 32 |

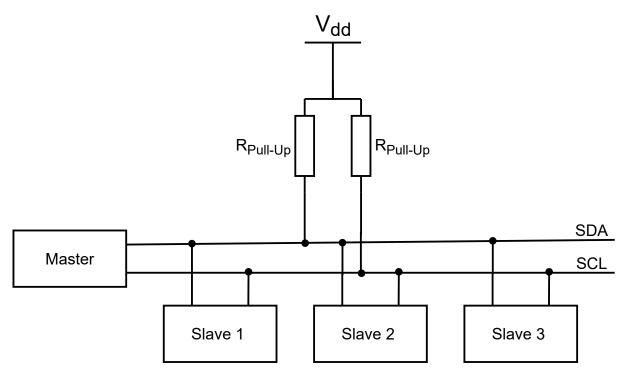

| 2.8  | Schematic of an I2C Communication.                                              | 34 |

| 2.9  | Schematic of an SPI Communication.                                              | 35 |

| 2.10 | Integration of the SPI into the MCU.                                            | 36 |

|      | Differentiation Between SPI and RAM.                                            | 36 |

|      | MCU Routine.                                                                    | 37 |

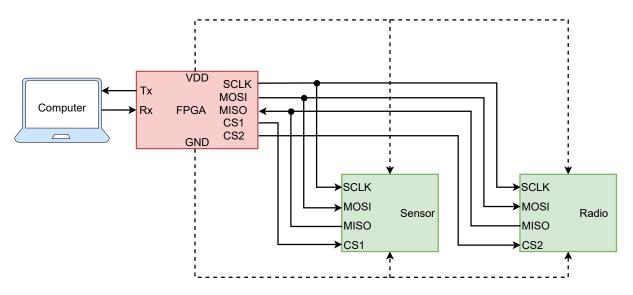

|      | Schematic of the Demonstrator.                                                  | 40 |

|      | Demonstrator (on the left) with Sensor (on the right) and Transceiver (on top). | 40 |

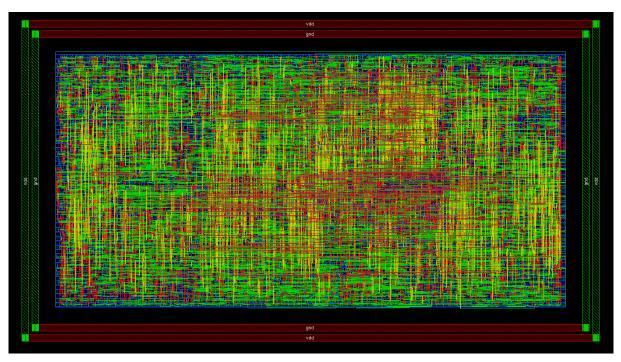

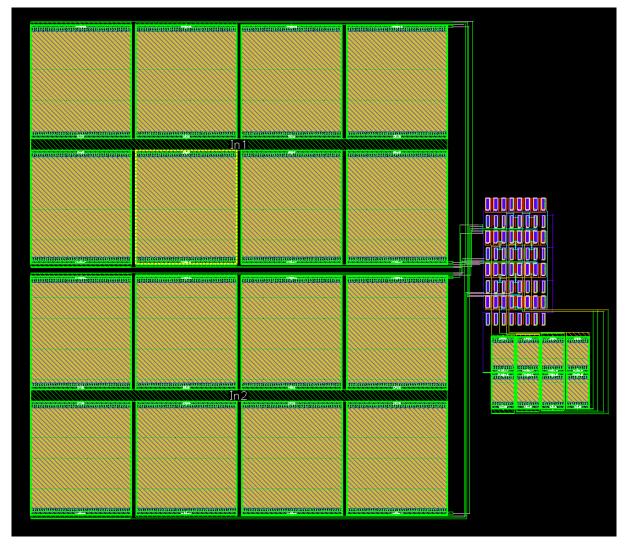

| 2.15 | Layout of the MCU Core.                                                         | 42 |

| 3.1   | Position of the WuRx in a Node.                                           | . 44 |

|-------|---------------------------------------------------------------------------|------|

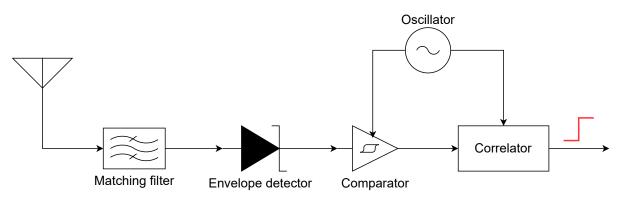

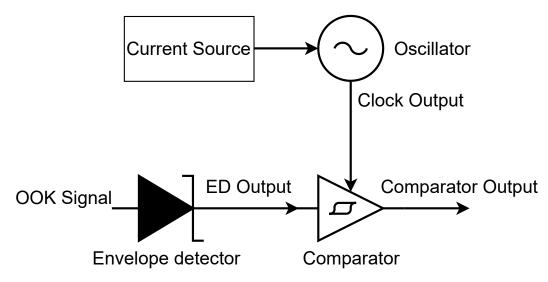

| 3.2   | Schematic of a WuRx.                                                      | . 45 |

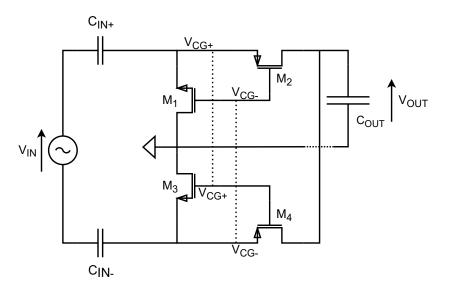

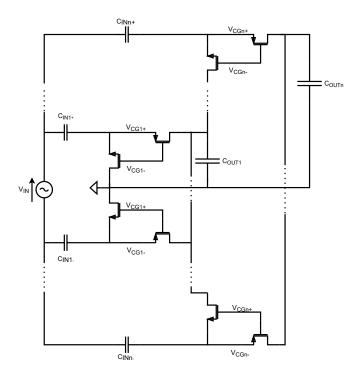

| 3.3   | Schematic of a Single Stage Cross-Coupled Envelope Detector               | . 46 |

| 3.4   | n-Stage Cross-Coupled Envelope Detector.                                  |      |

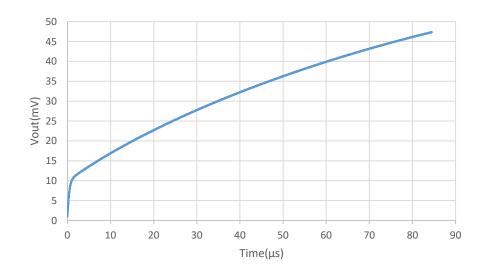

| 3.5   | Layout of the Envelope Detector.                                          |      |

| 3.6   | Output Voltage of the Envelope Detector.                                  |      |

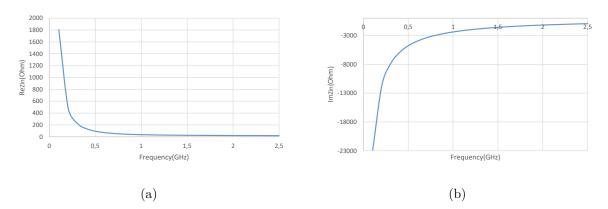

| 3.7   | Impedance of the Rectifier (a) Real Part (b) Imaginary Part               |      |

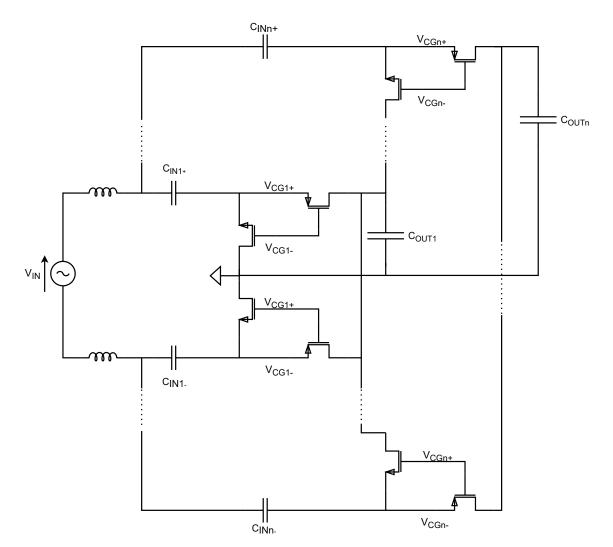

| 3.8   | Envelope Detector with Matching.                                          |      |

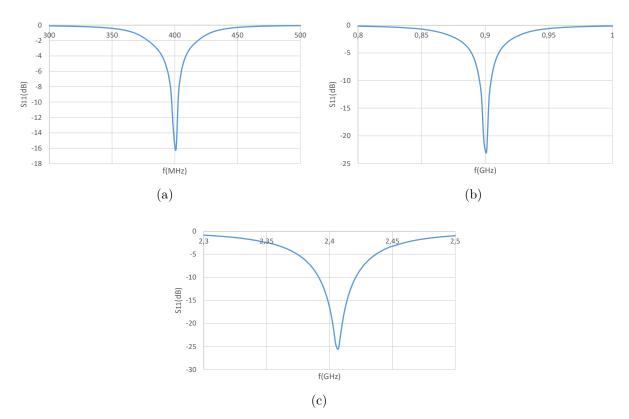

| 3.9   | Envelope Detector $S_{11}$ Parameter at (a) 400MHz (b) 900MHz (c) 2.4GHz. |      |

| 3.10  |                                                                           |      |

| 3.11  | Layout of the Comparator.                                                 |      |

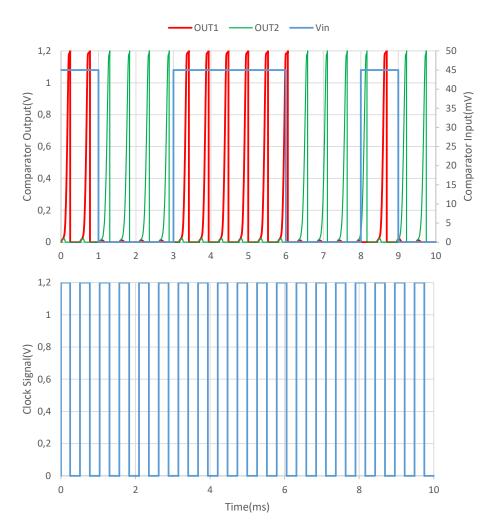

|       | Comparator Response.                                                      |      |

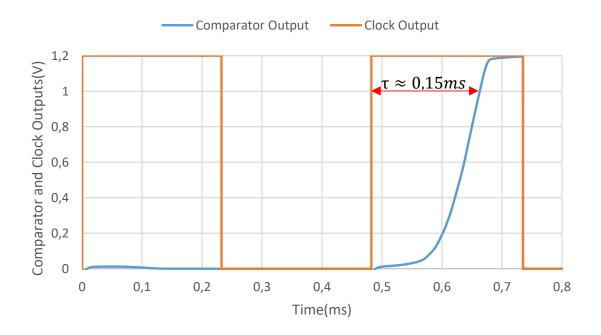

|       | Comparator Delay.                                                         |      |

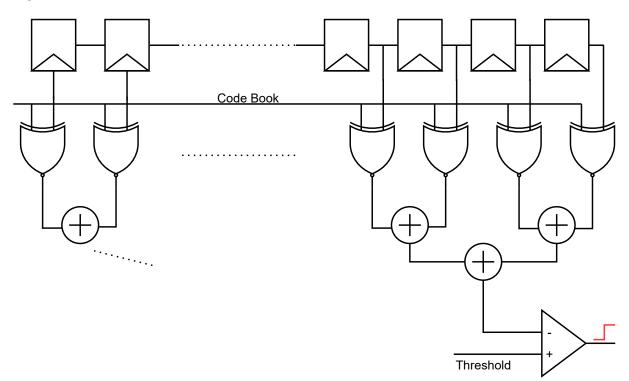

|       | Correlator Schematic.                                                     |      |

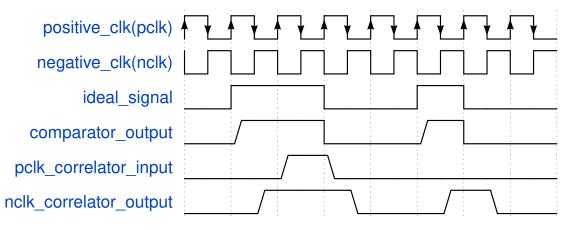

|       | Choice of the Correlator Clock.                                           |      |

|       | Layout of the Correlator                                                  |      |

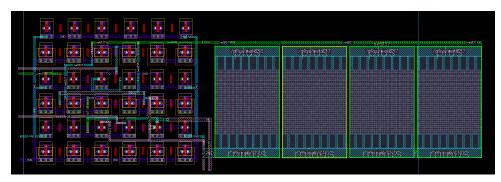

|       | RS Oscillator Schematic.                                                  |      |

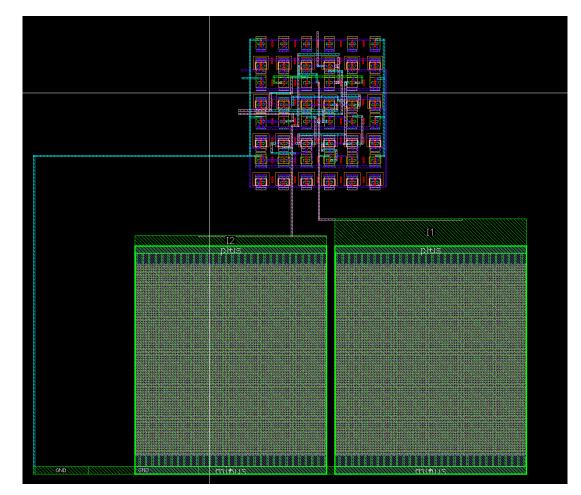

|       | Layout of the Oscillator.                                                 |      |

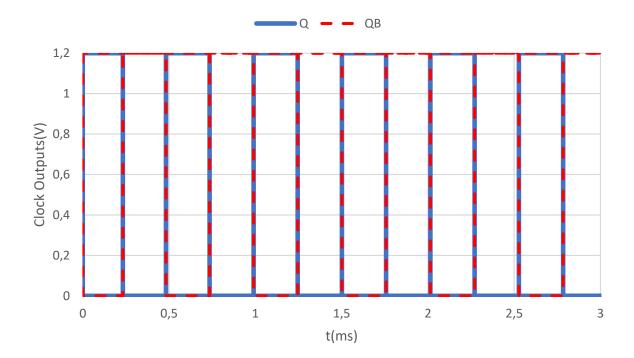

|       | Clock Signals of the Oscillator.                                          |      |

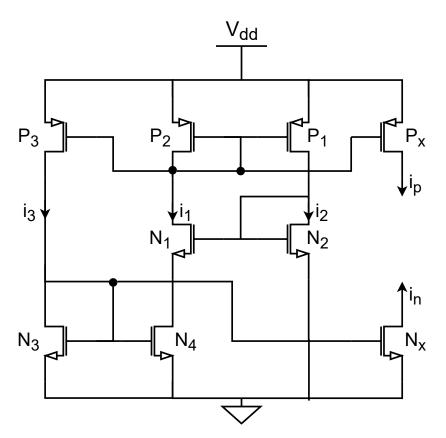

|       | Schematic of the Current Source.                                          |      |

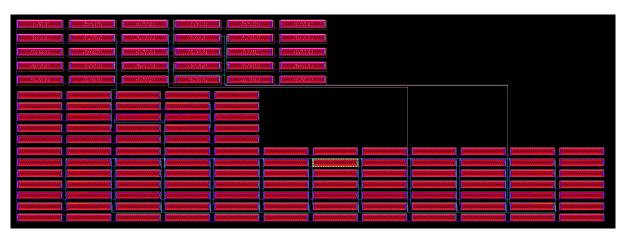

|       | Layout of the Current Source.                                             |      |

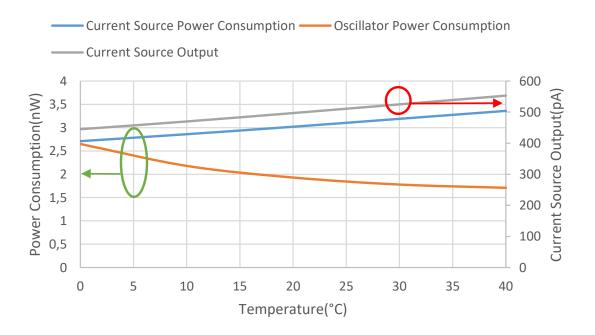

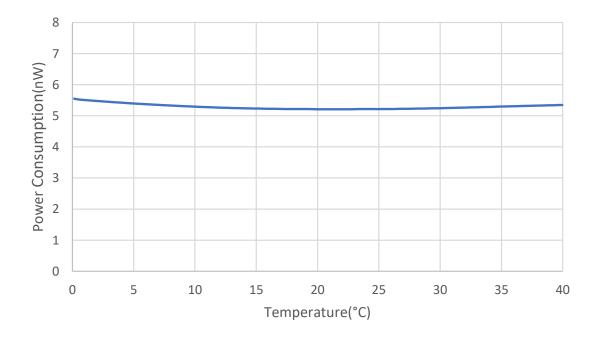

|       | Power Consumption of the Current Source with Temperature Variations       |      |

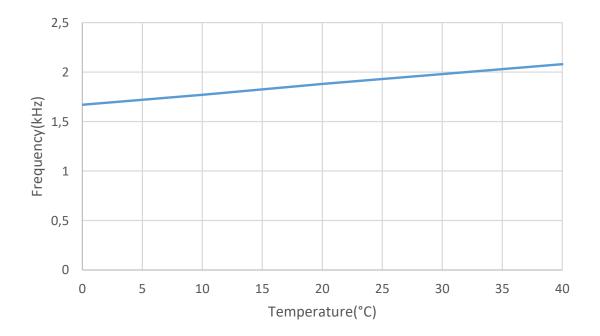

|       | Frequency Clock with Temperature Variations.                              |      |

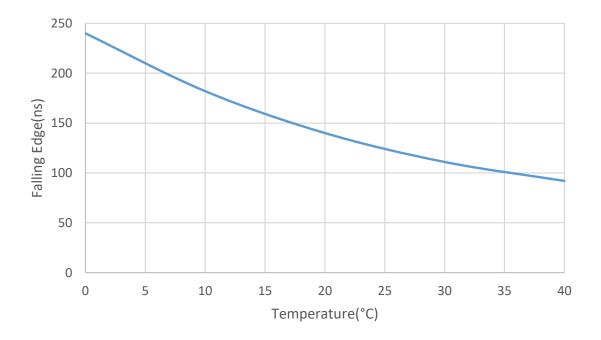

|       | Falling Edge of the Oscillator with Temperature Variations.               |      |

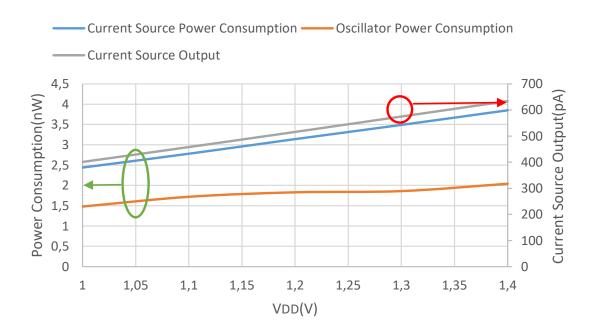

|       | Power Consumption of the Current Source with Voltage Supply Variations.   |      |

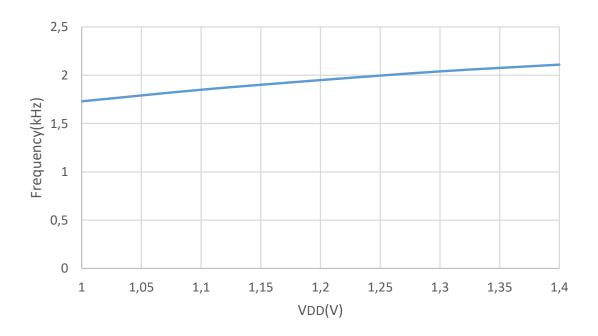

|       | Oscillator Frequency with Voltage Supply Variations.                      |      |

|       | Schematic of the Simulated Circuit in PLS.                                |      |

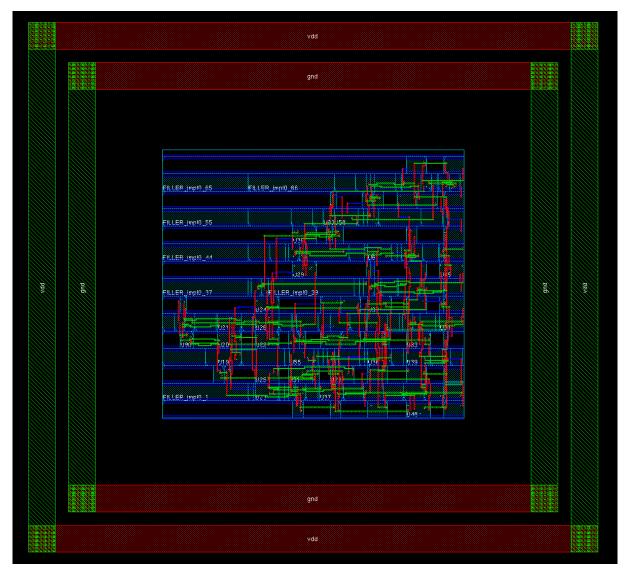

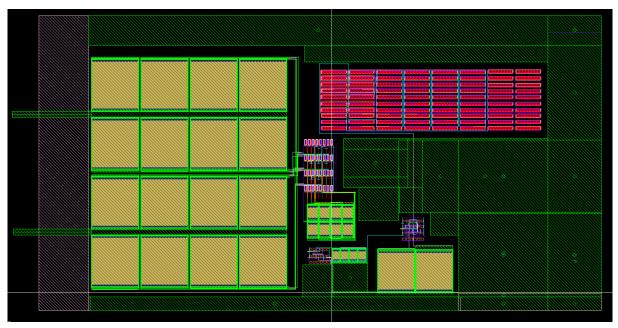

|       | Layout of the Demodulation Block.                                         |      |

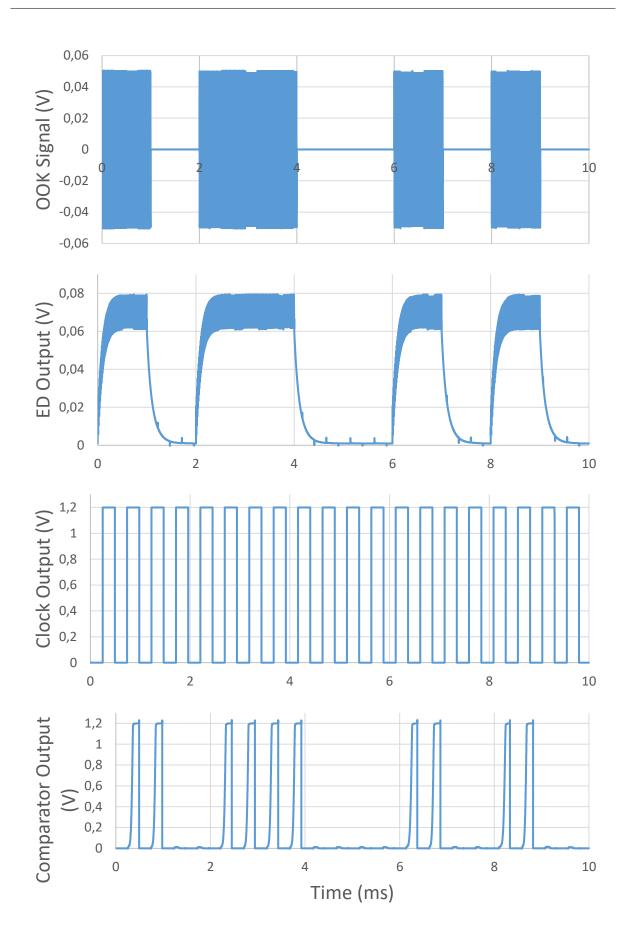

|       | Simulation of the Demodulation.                                           |      |

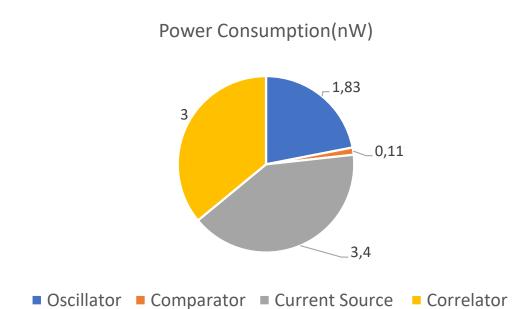

|       | Power Consumption of the Circuit.                                         |      |

|       | Power Consumption Variations of the Demodulation Block.                   |      |

| 0.01  |                                                                           | . 10 |

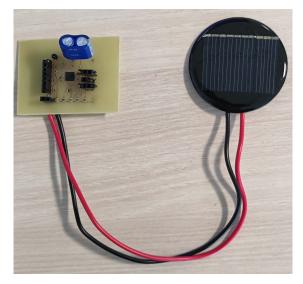

| 4.1   | PCB of the Solar Harvester.                                               | . 76 |

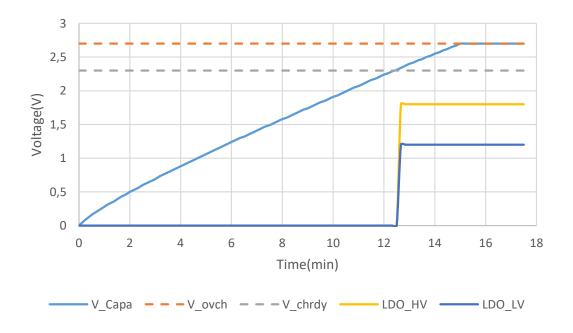

| 4.2   | Charge of the Supercapacitor at 10000 Lux                                 | . 77 |

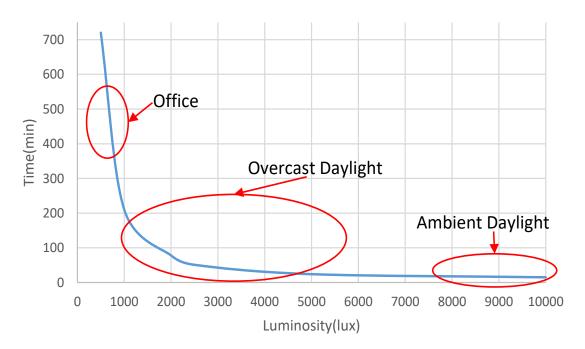

| 4.3   | Charge Time Depending on the Luminosity.                                  | . 77 |

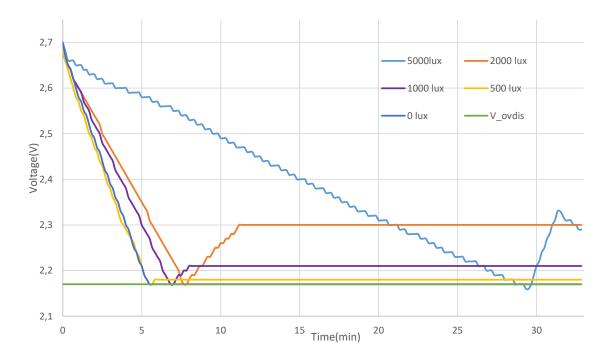

| 4.4   | Capacity Discharge at 1mA Output Current                                  | . 78 |

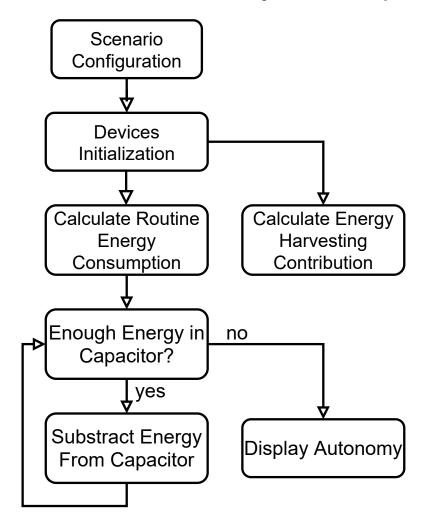

| 4.5   | Flow of the Simulator.                                                    | . 79 |

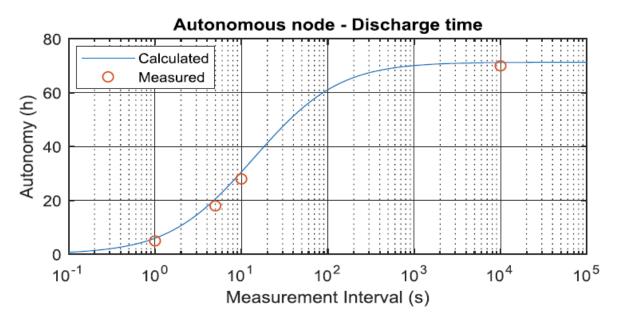

| 4.6   | Comparison of the Simulator with Measurements[83]                         | . 80 |

| 4.7   | RX/TX Mode Illustration                                                   | . 81 |

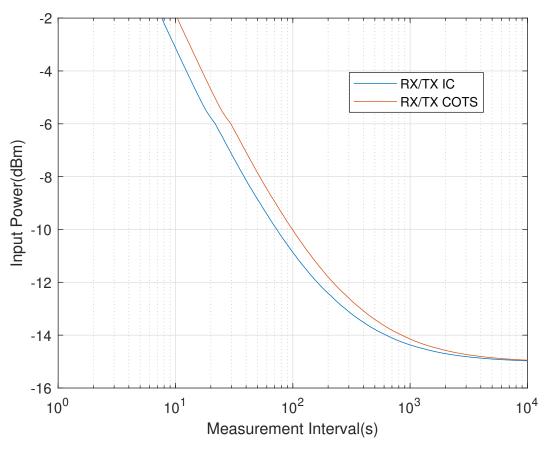

| 4.8   | Input Power Requirements in RX/TX Mode                                    | . 82 |

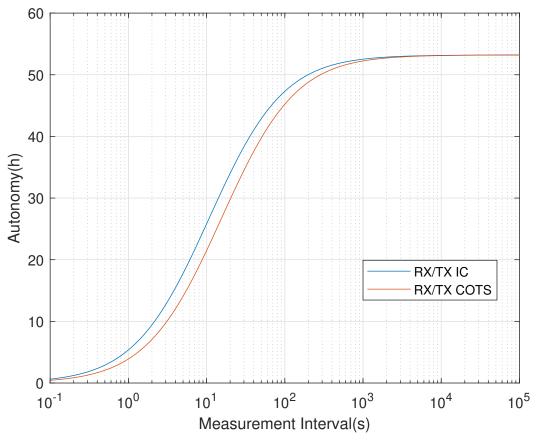

| 4.9   | Autonomy of the Node in RX/TX Mode                                        | . 83 |

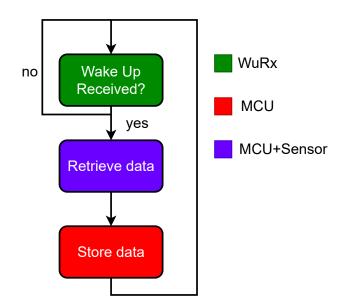

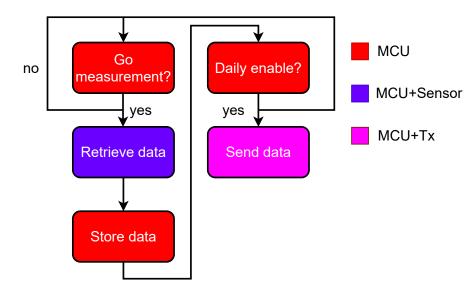

| 4.10  | Rx Only Mode Illustration.                                                | . 83 |

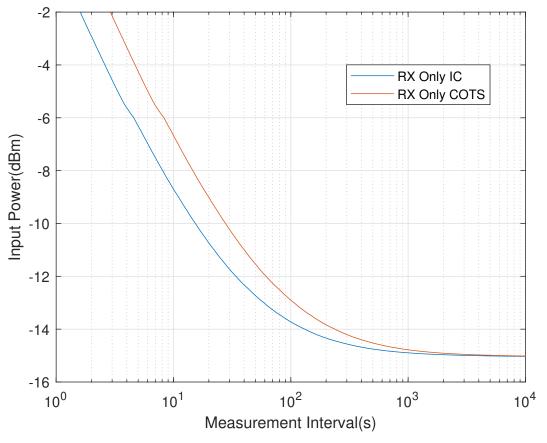

| 4.11  | Input Power Requirements in RX Only Mode                                  | . 84 |

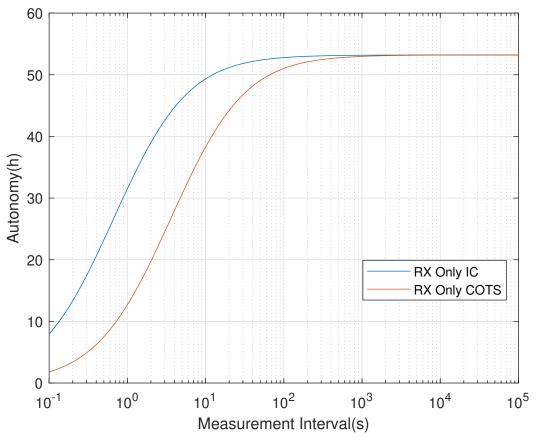

| 4.12  | Autonomy of the Node in RX Only Mode.                                     | . 85 |

| 4.13  | Burst Mode Illustration.                                                  | . 85 |

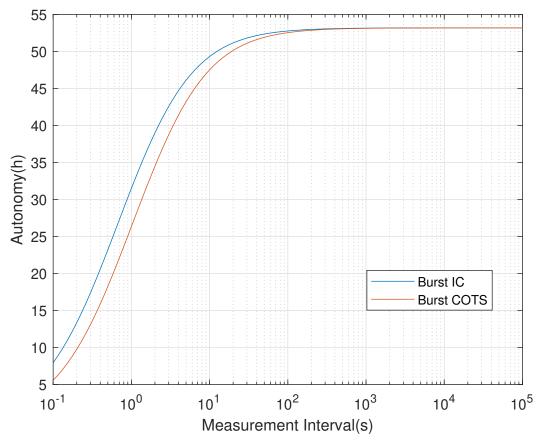

| 4.14  | Autonomy of the Node in Burst Mode                                        | . 86 |

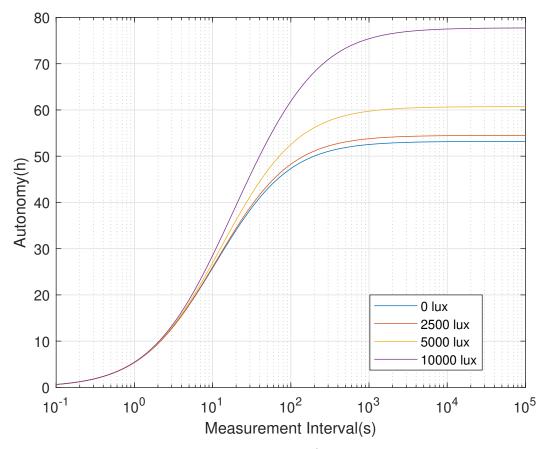

| 4.15  | Autonomy of the Node in RX/TX Mode with Light Variations                  | . 87 |

| 4.16  | Autonomy of the Node in RX Only Mode with Light Variations                | . 88 |

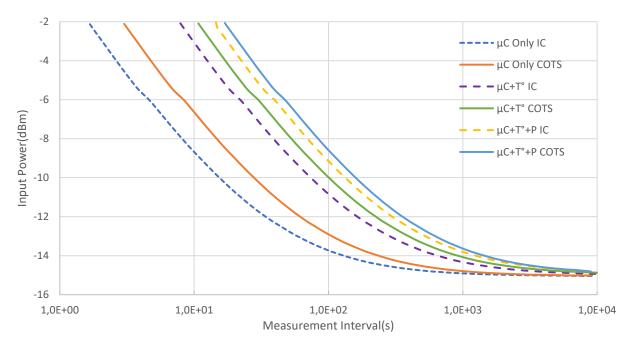

| 4 1 8 | Input Power Requirement for the Nodes with Several Sensors                | . 89 |

# List of Tables

| 1.1 | Typical Characteristics from Different Sources.         | 15 |

|-----|---------------------------------------------------------|----|

| 1.2 | Power Consumption Summary of the Node[47].              | 20 |

| 2.1 | Features of IoT Oriented MCUs.                          | 23 |

| 2.2 | State Machine of the 8-Bit CPU.                         | 27 |

| 2.3 | Instruction Set of the MCU.                             | 32 |

| 2.4 | Power Consumption Estimation.                           | 39 |

| 2.5 | Area Estimation.                                        |    |

| 2.6 | Power Consumption Comparison.                           | 41 |

| 3.1 | Envelope Detector Sensitivity at Different Frequencies. | 49 |

| 3.2 | Truth Table of a XNOR Gate.                             | 56 |

| 3.3 | Truth Table of a RS latch.                              | 58 |

| 3.4 | Comparison with State-of-the-Art.                       | 73 |

| 4.1 | Comparison of the Radio Transceivers                    | 75 |

| 4.2 | Light Range Example.                                    | 76 |

| 4.3 | Performance Comparison for Energy Harvesters.           | 76 |

| 4.4 | Comparison Between WSN#1 and WSN#2                      | 89 |

| 5.1 | Node Comparison with State-Of-the-Art                   | 91 |

# GLOSSARY

AC: Alternative Current ACCU: Accumulator ALU: Arithmetic Logic Unit BL: Boot Loader COTS: Components Off The Shelf CU: Control Unit DARPA: Defense Advanced Research Projects Agency DSN: Distributed Sensor Networks DC: Direct Current ED: Envelope Detector FPGA: Field Programmable Gate Area FRAM: Ferroelectric Random Access Memory FSM: Finite State Machine I2C: Inter-Integrated Circuit IC: Integrated Circuit IoT: Internet of Things **IPTO:** Information Processing Techniques Office MEMS: Microelectromechanical System MCU: Microcontroller Unit PCB: Printed Circuit Board PLS: Post Layout Simulation PU: Processing Unit QoS: Quality of Service **RAM:** Random Access Memory **RF:** Radio-Frequency SOSUS: Sound Surveillance System SPI: Serial Peripheral Interface UART: Universal Asynchronous Receiver Transmitter WuRx: Wake-Up Radio WSN: Wireless Sensor Network

ix

# GENERAL INTRODUCTION

There has been an upsurge in the number of connected devices in the IoT(Internet of Things) context. The multiplication of Wireless Sensor Networks (WSNs) lead to an increase of the number of batteries and of waste generated. In a context of green electronics, the development of self-sustained circuits supplied with energy harvesting has to be managed.

Chapter I will give an overview of wireless sensor networks, including a brief history these systems, the different fields of application, the challenges and some possible solutions to overcome these issues.

Chapter II will present the design of a custom Microcontroller Unit (MCU) which runs the WSN with a minimum power consumption. The architecture of the microcontroller, the instruction set, the interfacing and all the design choices will be presented.

Chapter III describes the design of a Wake-Up Radio (WuRx), an always-on circuit which switches on the WSN when a request is sent. The choice for the architecture of each block Will be explained, while detailing the different aspects of each block. The blocks are as follows:

- An envelope detector for data reception,

- A comparator for data demodulation,

- An oscillator to provide a clock for the system,

- A correlator to compare the received message with a reference,

- A current source to provide temperature robustness.

Chapter IV provides an analysis of the entire wireless sensor node. An estimation of the node autonomy is presented and a comparison with a node designed with market components is presented. Perspectives of improvement for future works will also be presented.

# INTRODUCTION GÉNÉRALE

Il y a eu une recrudescence du nombre de dispositifs connectés dans le contexte de l'Internet des objets. La multiplication des réseaux de capteurs sans fil a conduit à une augmentation du nombre de batteries et de déchets générés. Dans un contexte d'électronique verte, le développement de circuits autonomes alimentés par la récupération d'énergie doit être géré.

Le premier chapitre donnera un aperçu des réseaux de capteurs sans fil, y compris une brève histoire de ces systèmes, les différents domaines d'application, les défis et quelques solutions possibles pour surmonter ces problèmes.

Le second chapitre présentera la conception d'un microcontrolleur sur mesure pour l'application qui controle le noeud capteur avec une consommation minimale d'énergie. L'architecture du microcontrôleur, le jeu d'instructions, l'interfaçage et tous les choix de conception seront présentés.

Le troisième chapitre décrit la conception d'une radio de réveil, un circuit toujours actif qui active le noeud capteur lorsqu'une requête est envoyée. Le choix de l'architecture de chaque bloc sera expliqué, en détaillant les différents aspects de chaque bloc. Les blocs sont les suivants :

- Un détecteur d'enveloppe pour la réception des données,

- Un comparateur pour la démodulation des données,

- Un oscillateur pour fournir une horloge pour le système,

- Un corrélateur pour comparer le message reçu avec une référence,

- Une source de courant pour assurer la robustesse thermique.

Le dernier chapitre fournit une analyse de l'ensemble du nœud de capteur sans fil. Une estimation de l'autonomie du nœud est présentée et une comparaison avec un nœud conçu avec des composants du marché est également présentée. Des perspectives d'amélioration pour les travaux futurs seront également exposées.

# CHAPTER 1

# INTRODUCTION TO WIRELESS SENSOR NETWORKS

#### 1.1 What is a Wireless Sensor Network?

Wireless Sensor Networks (WSNs) have become a prevalent technology in the context of the Internet of Things (IoT). This section provides a brief historical overview of WSNs, their design principles, and delves into the issue of power management. It also includes a description of their application fields and concludes by highlighting the challenges and future prospects of this technology.

#### 1.1.1 Introduction

The increasing pursuit of having connected devices leads to a need of smaller low power systems, with cheaper costs to be massively manufactured, and a minimal low human intervention for maintenance. However, this continuous increase faces the actual environmental problematic, which brings designers to create sustainable systems, particularly concerning products lifetime, recycling and green power management.

WSNs are the ones of the most impacted systems by these issues, because of the important amount of devices that are and will be deployed in the upcoming years. This makes it very challenging to combine the endless connectivity expansion with the energy sobriety obligation.

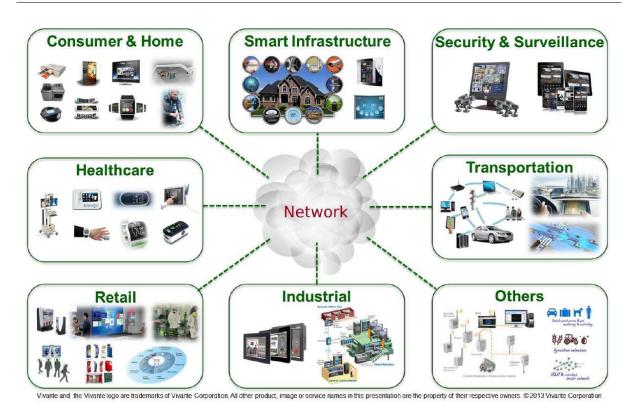

The Internet of Things (IoT) refers to the interconnected network of physical devices, vehicles, buildings, and other objects that are embedded with sensors, software, and network connectivity, enabling them to collect and exchange data. This network of interconnected devices can communicate with each other and with other systems, allowing for greater automation, control, and efficiency. Domains covered by IoT are described in Fig.1.1.

Figure 1.1: Applications covered by IoT[1].

Current research in IoT has generated a significant interest in deploying systems that are ultra low power and low maintenance. However, this state of affairs is inadequate in light of the present environmental context, and it is crucial to have systems that consume such low power that they can be batteryless and self-sustained solely through ambient energy harvesting.

#### 1.1.2 Wireless Sensor Network Architecture

WSNs are a type of network that consists of small devices called wireless sensor nodes, which are equipped with sensors to collect data from their environment, process that data, and communicate the information to other nodes in the network or to a central server called gateway.

Wireless sensor nodes can be deployed in a variety of environments, including indoor and outdoor settings, and are used in many different applications, such as environmental monitoring, industrial control, healthcare, and security systems. They can measure a wide range of physical parameters, such as temperature, humidity, light, sound, motion, and pressure.

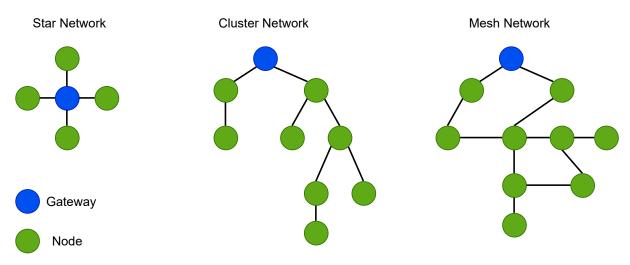

The nodes in a WSN can communicate with each other through different wireless communication protocols, such as Wi-Fi, Bluetooth, Zigbee, or LoRaWAN to name a few. The nodes can also be configured to form a mesh network, where they can relay information to other nodes in the network, extending the network's coverage and increasing its reliability and Quality of Service(QoS).

Overall, wireless sensor nodes are an important technology for collecting and transmitting data from various environments and can help automate processes, increase efficiency, and provide valuable insights for decision-making in many different fields. Fig. 1.2 shows different topologies of WSNs.

Figure 1.2: Wireless Sensor Networks Topologies[2].

In a wireless sensor network, a gateway is a device that serves as a bridge between the wireless sensor nodes and a central server or the internet. The gateway typically has a more powerful processor and communication capabilities than the individual sensor node, enabling collecting and processing data from multiple nodes. The gateway transmits these data to a central server or the cloud.

One of the main functions of a gateway in a wireless sensor network is to manage the network and its nodes. It can perform tasks such as node registration, network configuration, and software updates. It can also monitor the health and status of the nodes, such as battery level and connection status.

The gateway can also provide additional features and functionalities, such as data encryption and security, data aggregation and analysis, and integration with other systems and applications.

Overall, the gateway is an essential component of a wireless sensor network that enables the efficient collection, processing, and transmission of data from the sensor nodes to a central server or the internet.

#### 1.1.3 Wireless Sensor Node

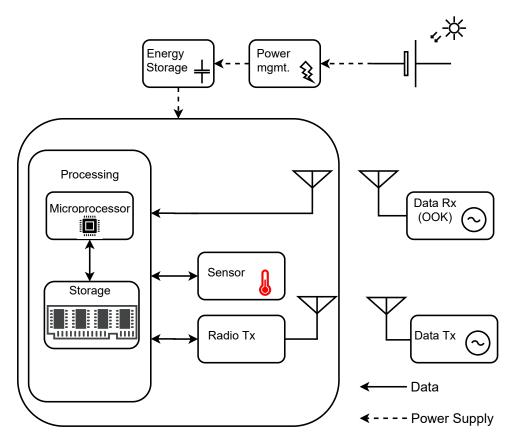

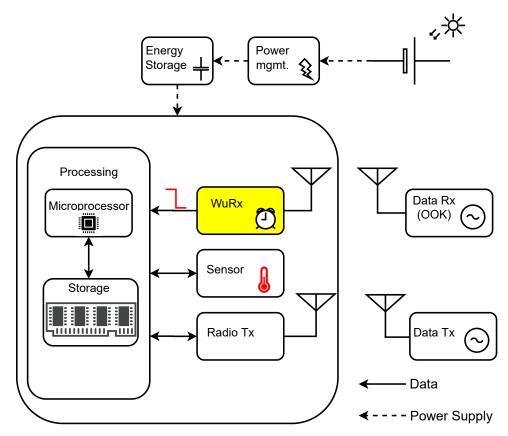

A wireless sensor node is a compact device designed to collect and transmit data wirelessly from the environment it is deployed in. It typically consists of four main components as illustrated in Fig. 1.3:

• A sensor which is the primary component of the node, responsible for measuring the physical or environmental parameter of interest, such as temperature, humidity, or light intensity to name a few.

- A microcontroller which acts as the brain of the node, responsible for processing the data received from the sensor and controlling the wireless communication module.

- The wireless communication module is responsible for transmitting the data collected by the sensor to a central hub or gateway, typically over a radio frequency band.

- A power source to supply the entire system, the power source can be either a battery or an energy harvesting system, depending on the application and the expected lifetime of the node.

Figure 1.3: Typical architecture of a Wireless Sensor Node.

The compact size and wireless communication capability of sensor nodes are critical for deployment in various environments, including indoor and outdoor settings. They can be used for a wide range of applications, including environmental monitoring, smart buildings, healthcare, agriculture, and industrial automation. The flexibility and scalability of these devices make them a crucial component of the IoT ecosystem.

#### 1.1.4 Wireless Sensor Network History

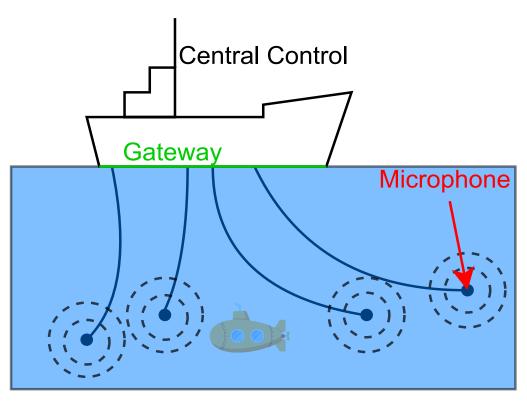

Since most of new technology inventions emerge from military research, it is difficult to exactly determine the exact introduction of an innovation. However, the predecessor of WSNs can be found back in the 1950s. Sound Surveillance System (SOSUS) was a classified US Navy program that operated during the Cold War for the detection of Soviet submarines. The system consisted of a network of underwater microphones or hydrophones that were deployed at various locations in the world's oceans to detect the sound signatures of submarines[3], [4]. Fig. 1.4 presents the principle of SOSUS system.

Figure 1.4: Principle of Sound Surveillance System.

While SOSUS was not a wireless sensor network in the modern sense, it could be considered as a precursor to modern underwater acoustic sensor networks, which are wireless sensor networks designed for underwater applications.

The study of sensor networks originated in 1980 when the Defense Advanced Research Projects Agency (DARPA) launched the Distributed Sensor Networks (DSN) program[5]. At that time, the Arpanet, a forerunner of the Internet, had been functioning for several years and was being used by approximately 200 hosts located in universities and research institutions. R. Kahn, one of the co-inventors of the TCP/IP protocols and a major figure in the development of the Internet, was the director of the Information Processing Techniques Office (IPTO) at DARPA. He sought to investigate whether the Arpanet approach to communication could be applied to sensor networks. The sensor network was envisioned as having numerous low-cost sensing nodes spread across different locations, which would work collaboratively but independently, with information being routed to the most suitable node.

Considering the technological limitations of the time, the DSN program was a highly ambitious initiative. This was an era before personal computers and workstations were widely available, and most processing was done using minicomputers. Modems were operating at speeds ranging from 300 to 9600 Bd, and Ethernet was only just starting to gain popularity.

At Carnegie Mellon University, researchers aimed to create a network operating system that would provide flexible and transparent access to distributed resources required for a fault-tolerant DSN. To achieve this, they developed a communication-oriented operating system called Accent[6], which has primitives that facilitate transparent networking, system reconfiguration, and rebinding. The Accent operating system later evolved into the Mach operating system[7], which enjoyed significant commercial success. In addition, these researchers also worked on developing protocols for network inter process communication to support dynamic rebinding of active communicating computations, an interface specification language for building distributed system software, and a system for dynamic load balancing and fault reconfiguration of DSN software. They demonstrated all of these concepts in an indoor test bed with signal sources, acoustic sensors, and VAX computers connected via Ethernet.

MIT researchers in Cambridge conducted a study on tracking helicopters using a distributed array of acoustic microphones by applying knowledge-based signal processing techniques. They utilized signal abstractions and matching techniques and developed SPLICE and Pitch Director's Assistant for DSN data analysis and algorithm development. Tracking multiple targets in a distributed environment is much more challenging than centralized tracking since the association of measurements to tracks and the estimation of target states must be distributed over the sensor nodes. Advanced Decision Systems developed a multiple-hypothesis tracking algorithm for dealing with challenging scenarios involving high target density, missing detections, and false alarms, and decomposed the algorithm for distributed implementation. MIT Lincoln Laboratory developed a real-time test bed for acoustic tracking of low-flying aircraft for demonstration. The sensors used were acoustic arrays arranged in three concentric triangles, and the test bed was successfully demonstrated with low-flying aircraft tracked using acoustic sensors and TV cameras. This was the state-of-the-art technology in the early 1980s.

Acoustic Array Mobile Node Equipment Rack Figure 1.5: Pictures of the System Developed by the MIT[8].

Until the 2000's, researches were mainly focused on communication protocols, recent advances in computing and communication have caused a significant shift in sensor network research and brought it closer to achieving the original vision. Small and inexpensive sensors based upon microelectromechanical system (MEMS) technology, wireless networking, and inexpensive low-power processors allow the deployment of a wide number of sensors and extended the field of applications.

### 1.2 Applications of Wireless Sensor Networks

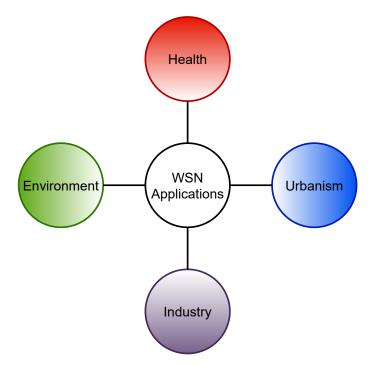

The expansion of WSNs opens a wide range of applications, from military applications to domestic applications with innovative systems. This section will present WSNs application in the following fields: healthcare, environment, industry and urban applications.

Figure 1.6: Application Field of WSNs.

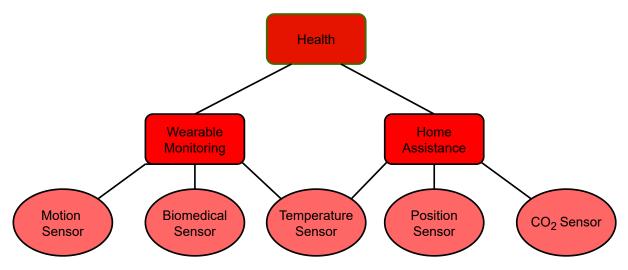

#### 1.2.1 Health Applications

WSNs in healthcare context already exist with the massive development of smart watches that can give information such as heart rate or average body activity. Currently with the miniaturization of devices, it becomes easier to develop wearable devices and the field of application becomes wider. An overview is given in Fig. 1.7.

Figure 1.7: WSNs in Healthcare Overview.

Several applications already exist about healthcare[9]. Some of them focus on elder's safety such as fall detectors[10], posture detectors and location tracking. Some use biological sensors to monitor patient's health. Some applications are dedicated to continuous sensing for patients suffering from cognitive disorders such as Parkinson or Alzheimer. There is also significant research effort in developing small sensor devices which can be implanted in human body. Other researches are more related to smart homes[11] which will be presented in a next part.

Figure 1.8: Example of Wearable Device with Multiple Sensors[12].

The main challenge of WSNs in healthcare, in addition of low power consumption and small footprint is data security. Because personal data can be handled, more security must be added to preserve people's privacy thus requiring more computing capabilities.

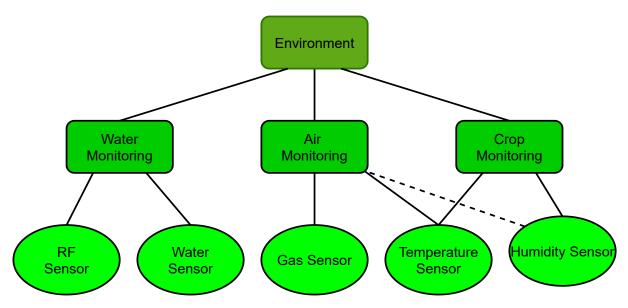

#### **1.2.2** Environmental Applications

WSNs are used in environmental sensing to monitor parameters such as air or water quality, or even in agriculture applications. Fig. 1.9 gives an overview of the possible use of WSNs in the environment context.

Figure 1.9: WSNs in Environment Applications Overview.

In this context, WSNs can harvest data from their environment for several applications such as pollution control, natural disasters prevention (earthquakes for example)[13] or to serve for smart agriculture[14]. Fig. 1.10 gives an example of an acoustic sensor called audiomoth which can have several uses such as the monitoring of species, soundscape analysis or environmental surveillance.

Figure 1.10: Acoustic Sensor for Environmental Monitoring[15].

The main challenge in this application context is the distance from infrastructures which reinforce the need of energy autonomy and the use of green energy for more sustainability.

#### 1.2.3 Industrial Applications

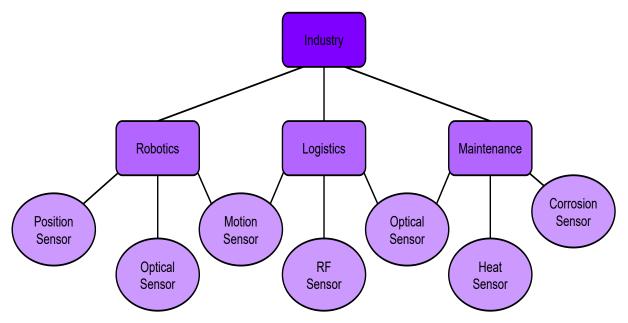

WSNs are widely used in the industry particularly with the automatising of some tasks and so the increasing use of robots by industrialists. Several use of WSNs can be imagined as depicted in Fig. 1.11.

Figure 1.11: WSNs in Industry Applications Overview.

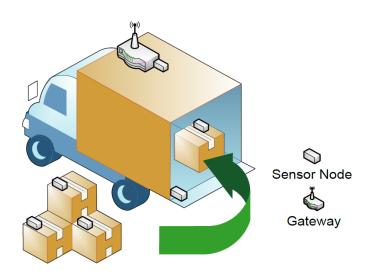

Sensors are already widely exploited on line work machines to increase the production rate. If these sensors can be made autonomous in energy, the gains would be significant. WSNs can also be used in logistics, if each package is associated with a tag that is checked automatically with a WSN, time can be saved.

Figure 1.12: Example of WSNs Use in Logistics[16].

The main constrains in the development of WSN dedicated to industrial application are the reliability and the cost of the solutions.

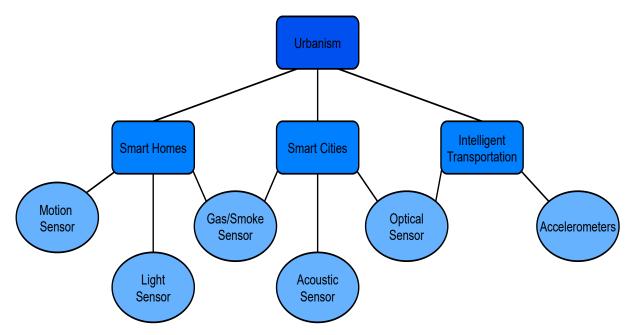

#### **1.2.4** Urban Applications

With the upcoming development of smart cities, smart homes and autonomous cars, the number of uses of WSNs continuously increases. Several possible applications are presented by Fig. 1.13.

Figure 1.13: WSNs in Urban Applications Overview.

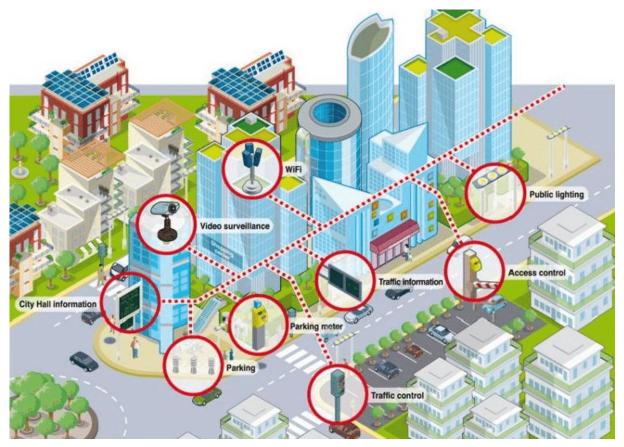

The development of WSNs has increased for smart homes use[17], [18]. The objective with the concept of smart cities in the upcoming years is to have a full connectivity that can be compliant with autonomous vehicles that will also use WSNs[19]. Indeed, autonomous cars will need to communicate with the external environment to function correctly, the development of this technology is therefore dependent on the development of infrastructures for smart cities. Fig. 1.14 gives an example of the connected objects that will be foundable in smart cities.

Figure 1.14: WSNs in Smart City[20].

#### 1.2.5 Conclusion

The extension possibilities for WSNs are continuously increasing with more upcoming applications. The use of WSNs can go from basic temperature sensors to industrial or healthcare applications, each field having its specific constraints. The common point is that the multiplication of the number of devices will lead to ecological concerns particularly with power consumption and batteries manufacturing. The subject of power management is critical for any application.

#### **1.3** Power Management

#### 1.3.1 Introduction

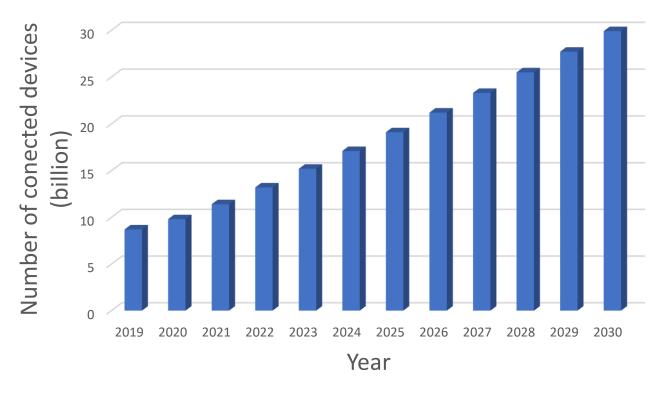

The expansion of IoT leads to a continuous increase in the number of connected devices. The forecasts tend to 30 billions of devices by the end of the decade[21] as presented by Fig. 1.15 and all these devices need to be supplied.

Figure 1.15: Connected Devices Forecast[21].

Depending on the application, several typed of batteries can be deployed, considering an ideal case where all the devices are powered by a 3V coin battery which is the smaller format. 30 billions battery would weight more than 80 million kilograms which represents the weight of an aircraft carrier. Moreover, considering the cost of these batteries around  $1 \in$ , it would represent the price for 5 warships. Finally, 30 billions of coin batteries would circle the Earth more than 40 times[22].

To conclude, the costs, natural resources and human resources for batteries replacement cannot support this amount of batteries and the ecological impact would be too important to be sustainable. This is the reason why a solution to maximize batteries lifetime or even remove batteries from connected devices needs to be found.

#### 1.3.2 Power sources

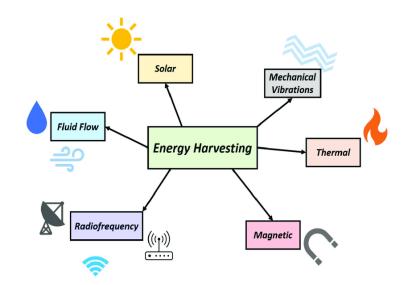

To replace batteries, some alternative sources of energy have to be found. This part presents different sources that are available, their advantages and drawbacks, and if there are usable or not in a WSN context. Depending on the amount of energy required by a system, and the cost involved in implementing powering such devices, different power sources may be adapted for different implementations, scenarios or schemes. Analyzing different sources will also permit to check which method is the most suitable to the application. Fig. 1.16 presents a variety of different energy sources for IoT devices:

Figure 1.16: Different Sources for Energy Harvesting[23].

Table 1.1 presents typical energy range for each methods, the advantages and the drawbacks for each method.

Table 1.1: Typical Characteristics from Different Sources.

| Energy     | Available Power                           | Advantages                         | Drawbacks                                   | Sources                      |

|------------|-------------------------------------------|------------------------------------|---------------------------------------------|------------------------------|

| Mechanical | 100µW-mW                                  | Continuous energy in some context  | Expensive, need to have device in movement  | [24], [25], [26], [27]       |

| Thermal    | mW                                        | Can harvest large amount of power  | Always need temperature variations          | [23], [28], [29], [30], [31] |

| Magnetic   | -                                         | -                                  | Need magnetic source                        | [23],[32],[33]               |

| Fluid      | mw - 100mW                                | Large amount of energy             | Expensive, dependent on the environment     | [34],[35],[36],[37]          |

| RF         | $\sim 100 \mu W$                          | RF waves everywhere                | Not a lot of power, dependent on the source | [25],[38],[39]               |

| Solar      | ${\sim}100\mu\mathrm{W}{-}100\mathrm{mW}$ | Good efficiency, mature technology | Dependent on the light                      | [27], [40], [41], [42]       |

Among the various sources of harvestable energy, wind and solar energies typically exhibit the highest power output per unit area. Additionally, thermoelectric, electromagnetic, and vibrational energy sources offer intriguing energy densities. However, it is important to acknowledge that implementing these energy harvesting technologies can often be costly due to overhead expenses, infrastructure requirements, and maintenance. Furthermore, it is worth mentioning that certain harvesting methods can be combined synergistically.

For this thesis RF and solar harvesting are chosen because of their ease of installation, low cost and their dependency on external parameters is less restrictive than the other methods.

#### 1.4 Challenges for Wireless Sensor Networks

The future perspective of a fully connected society becomes more and more realistic but in this context, several challenges appear and have to be tackled to keep on increasing the use of WSNs. The issue of power consumption has been discussed in the previous section, but other challenges must be considered.

#### 1.4.1 Security

As previously mentioned, data security is one of the main issues for WSNs. If personal or sensitive data are handled, a higher level of encryption must be used to ensure that these data cannot be recovered. Another security issue is denial-to-service attack which consists in making the device nonoperational[43]. A higher level of data coding needs to be used to overcome these issues, however, this leads to more complex and more power hungry systems which will have a lower lifetime. A trade-off needs to be found when considering this issue.

#### 1.4.2 Robustness

The robustness is the ability of a system to function with an invariant behaviour when external disturbances occur. WSNs are highly subject to robustness issues[44] because of its low cost, low power and so low complexity design. In this context, the sensor nodes must have as low false wake up as possible and need to miss requests as few as possible. Besides, if the nodes are placed in harsh environment, the system needs to be robust enough so that it is not degraded with time by its environment and its functioning still be accurate.

#### 1.4.3 Management

Up to now, WSNs designs were based on small size networks applied to only one application and so WSNs were designed with no really consideration for management. Because future WSNs are supposed to have hundreds or even thousands of nodes, it is important to manage the good operation of the whole group[45].

Sensor management can be described as a dynamic system that aims to manage and coordinate sensor nodes in order to improve performance while minimizing energy consumption. There is a wide range of applications for sensor networks, each with different requirements. These applications can be classified as follows:

- Scavenging parameters of the physical environment such as the temperature in a room for example.

- Detecting events and assessing their impact: is there a sudden evolution of a parameter and what is the impact?

- Being able to make the different between objects that are analysed

- Tracking moving objects.

These four application types have different performance metrics, such as detection probability, identification accuracy, and probability of loss-of-track. Additionally, certain performance metrics, such as lifetime and latency, should also be considered. Energy efficiency is crucial in WSNs, and all network operations should be performed with minimal energy consumption. In some applications, the collected data is only valuable if it reaches the observer in a timely manner. Hence, the main objective of sensor network management is to balance these performance metrics in order to maximize overall performance.

#### 1.4.4 Power Consumption

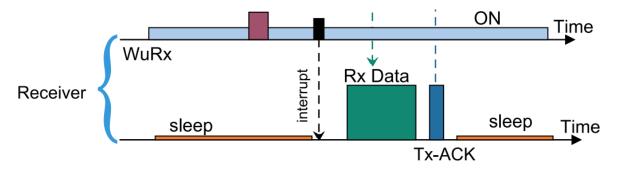

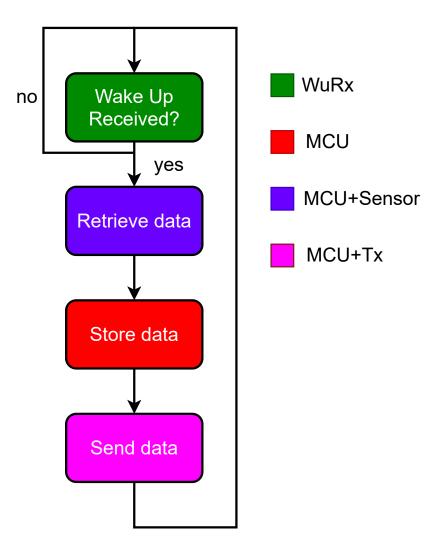

Because the node is functioning only when a request occurs, it spends a major part of the time in idle state waiting for an event. This leads to a power consumption used for no activity. To avoid this waste of energy, actual nodes integrate an other block called Wake-Up Radio (WuRx). The purpose of this block is to be always on when the rest of the node is shutdown, and when an action is intended, it sends a signal to switch on the node to perform the measurement, and then go back in shutdown mode as illustrated in Fig. 1.17.

Figure 1.17: Wireless Sensor Node Duty Cycling[46].

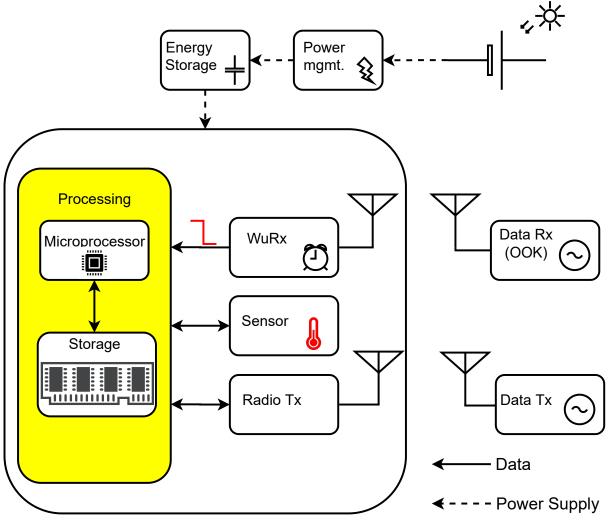

This solution allows to have only one low power circuit active during higher amount of time and so save an important quantity of energy. Fig. 1.18 shows the architecture of a wireless sensor node including the WuRx module.

Figure 1.18: Wireless Sensor Node with Wake-Up Radio.

Concerning the MCU, an issue is that actual circuits are designed to cover as many applications as possible. This leads to extra features that are useless for this application and so extra power consumption. A sober design must be done to save as much energy as possible.

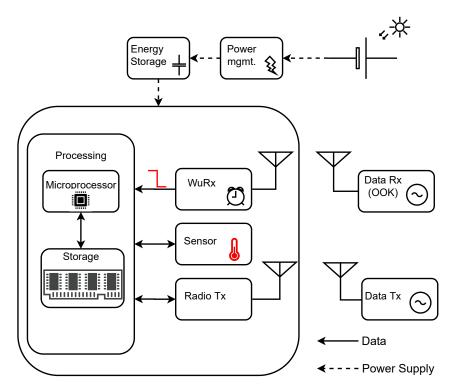

#### 1.5 System Overview

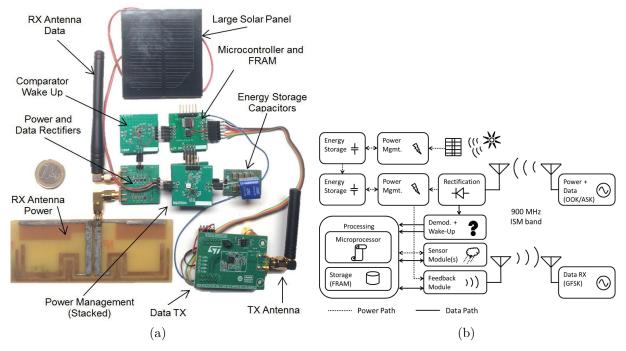

This thesis is meant to be the continuity of [47] starting from the final results. The conclusion of this work is that designing a wireless sensor node powered by energy harvesting is doable, and a full system designed with Component Off The Shelf(COTS) and market component was developed. Fig. 1.19 shows the manufactured wireless sensor node with the components soldered on Printed Circuit Boards(PCB) and the schematic view of this node.

Figure 1.19: (a) COTS Wireless Sensor Node, (b) Schematic View of the Node[47].

The more challenging blocks of this system will be briefly presented with their role, their performances and limitations. Finally the axes of improvement will be presented and will determine the research directions for this thesis.

#### 1.5.1 Rectification

The incoming RF energy and data go through two rectifiers in parallel that are used to demodulate incoming data on a one hand, and to harvest RF energy on the other hand. The circuit was designed using HSMS-285C diodes[48].

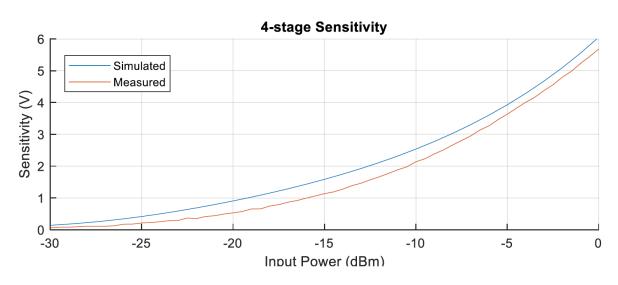

Fig. 1.20 presents the output of the rectifier depending on the input power. A slight amount of energy can be harvested at the maximum sensitivity of -30dBm while integrated rectifiers in WuRx can easily go under -60dBm. The sensitivity of the circuit is limited by COTS diodes which exhibit a high threshold voltage(typically 200mV). To overcome this limitation, the solution will be to develop an integrated circuit using diode-connected transistors featuring circuit technics to compensate for intrinsic device threshold voltage and to reach better sensitivities.

Figure 1.20: Measurement Results of the Rectifier [47].

#### 1.5.2**Power Management**

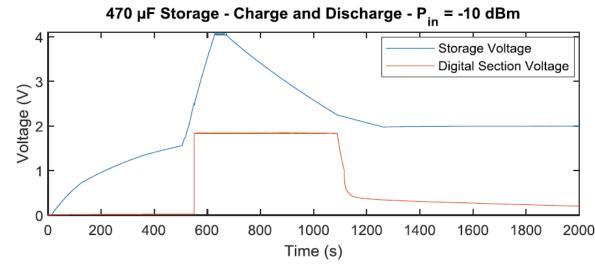

The energy harvested from RF or solar sources is then handled by power management modules Texas Instrument bq25504[49] and bq25570[50] respectively. Fig. 1.21 shows the measurement of RF energy harvesting with this circuit.

Figure 1.21: Measurement Results of the Energy Harvester [47].

It appears that the circuit is able to charge a  $470\mu F$  capacitor and deliver the current drawn by the node during its operating phase. However, the remark can be done that the circuit operates with an input power of -10dBm which is not the range of value that is met in energy harvesting.

This principle limitation for these circuits is their cold stat voltage i.e the minimum voltage needed to engage the power management. In this thesis, the choice was made to test products from the company E-Peas which presents lower cold start voltage and so should afford better performances.

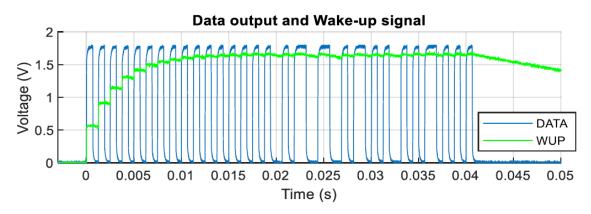

#### 1.5.3 Wake Up Generation

To use the node only when needed, a wake up radio was also designed. It is composed of a band-pass filter, a comparator and a rectifier. Fig. 1.22 shows the generation of the wake up signal after a request. The power consumption for the demodulation is around 800nW which is quite significant. Comparatively, most of state-of-the-art circuit have a power consumption ranging from 10nW to 100nW for these applications. This limitation is here again due to the use of COTS components. To overcome this issue, this thesis focuses on implementing a full custom wake up Radio in CMOS technology. This WuRx module is further detailed in Chapter 3.

Figure 1.22: Generation of the Wake-Up Signal[47].

#### 1.5.4 Data Processing and Data Sending

The data are gathered from the sensor(BME280 from Bosch[51]) and processed with a PIC16LF1559 microcontroller[52] to be further stored in a Ferroelectric Random Access Memory(FRAM)[53]. The data are then sent back with the STMicroelectronics Spirit1 transmitter[54]. Table. 1.2 summarizes the power consumption of the node for each operation. It can be noticed that both devices are not optimized for low power applications. Concerning the radio transmitter, the choice is made to use a new market component dedicated for low power applications. The same direction will be taken for the sensor, a market component will be used because they already fit well low power applications. On the other hand, the MCU has much more features than the ones needed for the required task and the same drawback can be found with most of market components. This is why in this thesis the choice was made to design a dedicated MCU with the minimum functionalities to save the maximum amount of energy.

| Command             | Duration(ms) | $Power(\mu W)$ | $Energy(\mu J)$ |

|---------------------|--------------|----------------|-----------------|

| Sleep Mode          | -            | 0.92           | -               |

| False Wakeups       | 16.8         | 416            | 7               |

| Temperature         | 40.6         | 422            | 17.1            |

| Measurement         | 40.0         | 422            | 11.1            |

| FRAM Data Storage   | 42.1         | 420            | 17.7            |

| FRAM Data Retrieval | 42.2         | 417            | 17.6            |

| Data Transmission   | 55.9         | 1750           | 97.8            |

Table 1.2: Power Consumption Summary of the Node[47].

#### 1.5.5 Full System

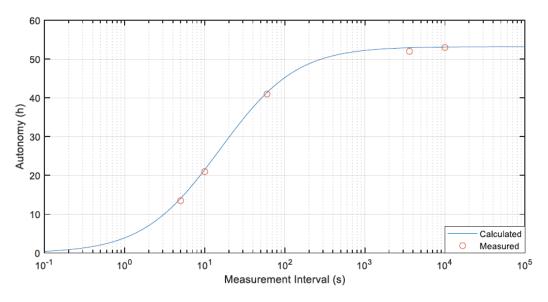

The designed system managed to work with energy harvesting and could achieve an autonomy up to 50 hours depending on the time interval between measurements. Fig. 1.23 presents the autonomy of the system in function of the measurement intervals.

Figure 1.23: Autonomy of the Node[47].

The conclusions of this thesis pointed out some limitations. Firstly the use of COTS for the design of the WuRx significantly reduces its performances in term of sensitivity and power consumption due to the components limitations. An integrated design would allow to gain sensitivity and lower the global consumption. Moreover, the microcontroller used in this work is a generic market components which has a quite high power consumption to perform the required operations and the idea of having an application specific circuit was proposed. Working on these two aspects would enhance the performances of the node and increase its lifetime.

#### 1.6 Conclusion

This chapter presents an overview of WSNs, how it works, the different fields of application and the upcoming challenges. It brings out the fact that power consumption will be the limiting factor in most applications and this performance is for now the main point for improvements.

To demonstrate the feasibility of an autonomous IoT node, a first development based on COTS devices had been realized by Dr J. Nicot during his PhD at the IMS lab. This first demonstrator was fully autonomous and included the main features of an IoT node. Pointing out the limitations of a COTS implementation, it served as a starting point of this PhD work.

This work will focus on the design of a low power WuRx and MCU that will be integrated into a WSN with the objective of having an autonomous system. The circuit will be designed to be connected with market components concerning the sensor, the radio module and the power management unit.

# CHAPTER 2

## MINIMALIST LOW POWER MICROCONTROLLER DESIGN

## 2.1 Introduction

The previous chapter presented the interest of having a purpose-designed microcontroller to limit extra power consumption. Fig. 2.1 shows the position of the MCU in the node.

Figure 2.1: Position of the MCU in a Node.

The MCU acts as the brain of the WSN, its function is to communicate with the peripherals, handle the data and perform some calculation if necessary. The necessary features in the MCU are those which allow to perform the mentioned functionalities.

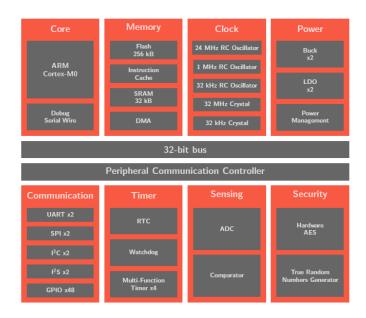

The actual trend with market components is to have multi-purpose circuit that are able to cover a wide range of applications. This implies having many peripherals, multiple communication protocols, different types of memories and many other features. To illustrate this, Fig. 2.2 shows an example of an IoT-oriented microcontroller. The counterpart is that the MCU becomes larger, its static power consumption increases and the high number of pads also increases the leakage current. The objective in this thesis is to present an MCU design which limits the number of features to function and so save the maximum power.

Figure 2.2: Example of an IoT Oriented MCU[55].

Table. 2.1 presents the main features of some IoT oriented MCUs. This allows to have an overview of the design trends in this field. It can be seen that all the circuits share the same voltage supply range which is a standard range for microcontrollers. All the circuit are in 32-bit topology, which is actually the most widespread configuration for microcontrollers.

|                           | [56]                           | [57]                                                                                                      | [58]                               | [59]                              | [55]                 |

|---------------------------|--------------------------------|-----------------------------------------------------------------------------------------------------------|------------------------------------|-----------------------------------|----------------------|

| Data Size                 | 32 bits                        | 32 bits                                                                                                   | 32 bits                            | 32 bits                           | 32 bits              |

| Voltage Supply(V)         | 3.8                            | 1.7-3.6                                                                                                   | 1.6-3.6                            | 1.65-3.6                          | 1.8-3.3              |

| Core                      | Arm Cortex M0+                 | Arm Cortex M4                                                                                             | Arm Cortex M23                     | Arm Cortex M0+                    | Arm Cortex M0        |

| Memories                  | 512kB flash/128kB RAM/32kB ROM | 1-MB application flash/<br>32-KB auxiliary flash/32-KB supervisory flash/<br>16kB flash cache/288-KB SRAM | 512kB flash/64kB SRAM<br>/32kB ROM | 64kB flash/8kB RAM/<br>2kB EEPROM | 256kB flash/<br>SRAM |

| Clock Sources             | 4                              | 3                                                                                                         | 4                                  | 5                                 | 4                    |

| Communication Peripherals | 3 SPI/3 I2C/3 UART/ 2USB       | 9 SPI/I2C/UART                                                                                            | 6 SPI/I2C/UART USB                 | 1 USB/3 UARTs/4 SPI/ 2I2C         | UART / 2 SPI / 2 I2C |

Table 2.1: Features of IoT Oriented MCUs.

It is important to note the wide variety of memories, clocks and peripherals. This choice allows the circuits to cover many applications, communicate with several peripherals and operate at various frequencies. The counterpart is that it generates non negligible power consumption that can be considered wasted if the MCU does not operate at full potential. Besides, in a low requirement application such as sensor networks, the amount of memory in the MCUs can be questioned. The presented circuits have two or three types of different memories, the entirety representing dozens of kilobytes of data. This high amount of memory allows the microcontrollers to be versatile and cover a wide area of applications. Indeed, from the industrial point of view, developing only one circuit doing different tasks instead of having multiple circuits is more lucrative.

On the other hand, this amount of memories appears to be oversized in WSNs applications considering the fact that the node just has to send few instructions and stores a small amount of data. Limiting the memory size of the circuit would decrease the power consumption and leakage to benefit for an increased autonomy of the circuit. Besides, less memory means a lower footprint for the circuit which will reduce the cost for manufacturing.

This chapter presents the design of a custom 32-bit MCU. It goes through the architecture of the system and the choices that are made to design this architecture. Finally a logical synthesis of the MCU is introduced in which the performance and power consumption of the MCU is presented.

## 2.2 Technology Choice

The choice of the technology has to suit for both the design of the WuRx and the MCU. The global power consumption of the MCU in the IoT is usually in the milliwatt range[60] while WuRx are in the nanowatt or microwatt range. The choice of the technology is focused on limiting the MCU power consumption.

In digital design, the power consumption comes from switching transistors. Eq. 2.1 presents the dynamic power consumption for transistors when switching[61].

$$P_{dynamic} = C_L \times V_{DD}^2 \times f \times \alpha \tag{2.1}$$

Where  $C_L$  is the load capacitance,  $V_{DD}$  is the voltage supply, f is the frequency and  $\alpha$  is the switching activity.

This equations shows that with smaller transistors, the capacitance  $C_L$  is reduces and so, if all the others parameters are unchanged, the power consumption will be reduces. This is one of the reasons why small technological nodes are preferred for digital designs. Although smaller technological nodes are preferred because of their lower dynamic power consumption, leakage current tends to increase while the node size decreases[62] which can be a limitation for low energy requirements. A the technology with the best trade off between these two parameters must be found.

Typically in low power applications, the most critical part of a MCU is the memory, mainly because it occupies a wider area, and also because it may need to be always powered on to keep data, which will lead to continuous leakage current.

The choice of the technology is done after a study on the available memories. The studied technologies are 28nm FDSOI, 65nm Bulk and 130nm from STMicroelectronics.

The main parameters of a memory are the size, the density i.e. the number of bits per area unit, the access time, the dynamic and static power consumption. Here the parameter to be optimized is energy consumption. The memory is selected depending on this parameter. More specifically, because the MCU will be off most of the time, the memory with the lowest static power consumption is aimed.

The studied shows that for similar memory size, memories with leakage around few hundreds of nanowatts can be used with the 65nm technology while the other technologies presents memories with current leakage in the microwatt range. For this reason, the chosen technology is the 65nm Bulk technology from ST Microelectronics, this technology presents the lowest current leakage and so the impact of the memory is minimised during the off phases of the MCU.

## 2.3 Microcontroller Architecture

## 2.3.1 Microcontroller Specifications

Before digging into the core of the MCU, the specifications of the circuit must be listed. The target is the design of a low power MCU for a wireless sensor node. The main optimization scope for the entire design is to present a power consumption as low as possible. The MCU is hard coded to reduce its complexity and the code is executed when an enable is sent by the WuRx. Concerning the function of the microcontroller, the circuit must be able to communicate with two peripherals, a radio and a sensor, and perform basic computations. The voltage supply comes from the energy harvesting block.

## 2.3.2 Initial Architecture

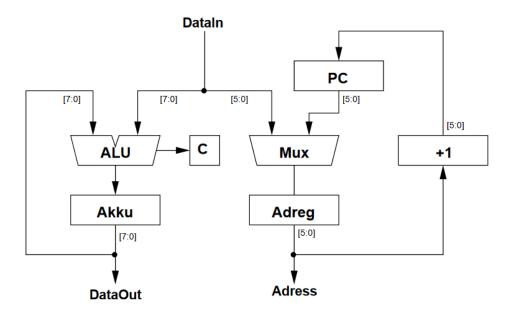

The design of the MCU is inspired by the design presented in [63] which is a minimal 8-bit microcontroller design with a function centered on only on register(ACCU). This reference circuit is given with only four instructions(NOR, ADD, STORE, JUMP) and a 64 byte memory.

The design goal is to minimize the utilization of macrocells exclusively for combinational logic, with the objective of maximizing the availability of usable registers. To achieve this, structures such as multiplexers between registers and the address/data output must be avoided at all costs. As a result, the data path is divided into one path for the address and another for the data.

Unlike other small CPUs, the address generation is not performed by the main ALU. Instead, a separate incrementer is necessary for the PC. Fortunately, the PC incrementer can still fit into the macrocells(i.e. a functional block or unit within the microcontroller that typically performs a specific task or set of tasks) that house the PC register, enabling the entire address-data path to fit within 12 macrocells.

The data-path represents 14 macrocells: eight for the accumulator, one for the carry flag and five combinational cells for the carry propagation.

Figure 2.3: Data-Path of the 8-bit CPU[63].

The data-path operates under the influence of a straightforward state machine featuring 5 states. The encoding of these states is thoughtfully selected to minimize the necessary macrocells for storage and decoding. In total, 5 macrocells are utilized for control.

Table. 2.2 outlines the state encoding for the state machine. The majority of instructions are executed within a concise two-clock cycle time frame.

| State | Function                          |

|-------|-----------------------------------|

| S0    | Fetch Instruction/Operand address |

| S1    | Write ACCU into memory            |

| S2    | Read operand, ADD                 |

| S3    | Read operand, NOR                 |

| S4    | Clear carry, Read PC              |

Table 2.2: State Machine of the 8-Bit CPU.

Because the purpose in this design is to save as much energy as possible, the idea is to start with this minimalist circuit, and then add features only if necessary, and so limit the energy consumption increase.

The next section presents the design of the MCU, decisions that were made and the justifications of these choices.

## 2.3.3 Global Architecture

The architecture of the designed MCU is presented in Fig. 2.4. It can be divided in four parts:

- The Control Unit (CU) fetches the instructions from the memory and then decodes them. The relevant control signals are then generated for the Processing Unit and the MU.

- The Processing Unit (PU) loads the operands from the memory, executes the instruction through the Arithmetic and Logic Unit(ALU) and finally stores the result in the ACCU register.

- The Memory Unit (MU) stores instructions and data following a Von Neumann architecture. This allows an easier implementation and less connections in comparison with an Harvard architecture.

- The Boot Loader (BL) first loads the program stored in the memory and then launches the execution. In Fig. 2.4, it can be noticed that the BL has additional pins  $T_x$ ,  $R_x$  and  $Scan\_Memory$ . These pins allows to send the program from a computer and give back the content of the MCU memory. This method is used for testing the circuit on board and debugging.

Figure 2.4: Architecture of the MCU.

The CPU functioning can be described as follows: the CU fetches the instruction in the memory and stores it in the RI register. The instruction is decoded to tell which task is loaded in the register. After that the operands are fetched and sent to the Processing Unit. The execution is performed by the Arithmetic Logic Unit and finally the result of the operation is stored in the memory by the Control Unit.

## 2.3.4 The Control Unit

The Control Unit fetches the instructions and controls the Processing Unit. This block can be separated in different parts:

- A register that takes the instructions from the RAM and sends them to the Finite State Machine (FSM) and the Program Counter (PC).

- A program counter that increments at each instruction and sends the address of the next instruction to be executed.

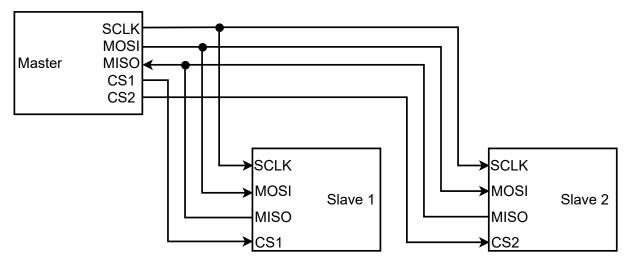

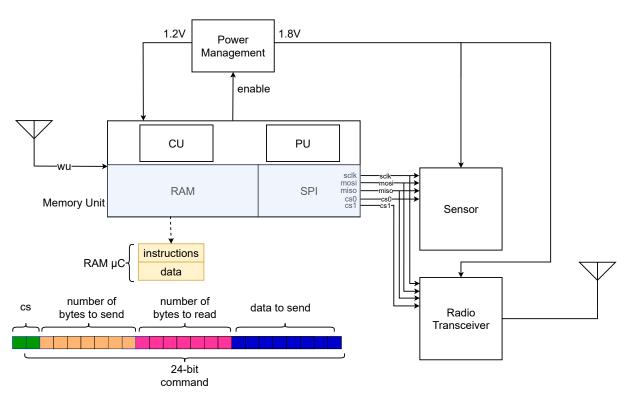

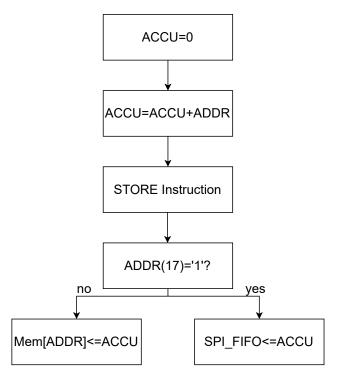

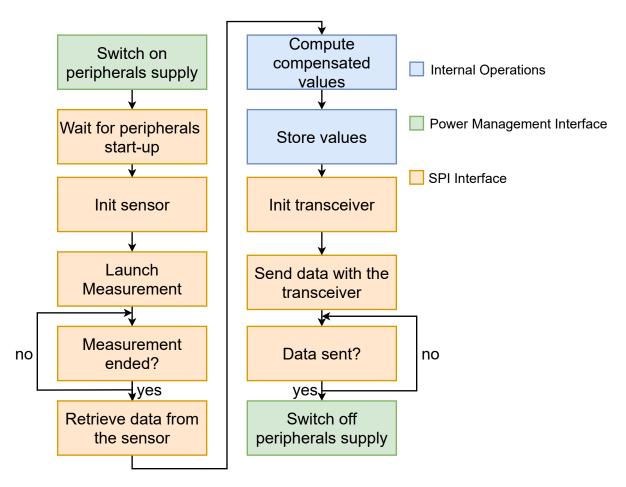

- A Finite State Machine that takes the instructions from the RAM, decode them, fetches the operands related to the instruction and drives the Processing Unit depending on the instruction to execute. This FSM contains ten different states.