# Methods for fast exploration of manycore architectures based network-on-chip with emerging technologies

Ibrahim Krayem

### ▶ To cite this version:

Ibrahim Krayem. Methods for fast exploration of manycore architectures based network-on-chip with emerging technologies. Performance [cs.PF]. Université de Rennes, 2024. English. NNT: 2024URENS008. tel-04689936

# HAL Id: tel-04689936 https://theses.hal.science/tel-04689936v1

Submitted on 6 Sep 2024

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THÈSE DE DOCTORAT DE

## L'UNIVERSITÉ DE RENNES

ÉCOLE DOCTORALE Nº 601 Mathématiques, Télécommunications, Informatique, Signal, Systèmes, Électronique Spécialité : Informatique

# Par Ibrahim KRAYEM

Methods for fast exploration of manycore architectures based Network-on-Chip with Emerging Technologies

Thèse présentée et soutenue à Lannion, le 29/02/2024 Unité de recherche : IRISA - Équipe Taran

#### Rapporteurs avant soutenance :

GOGNIAT GuyProfesseur des Universités, Université Bretagne SudVERDIER FrançoisProfesseur des Universités, Université Côte d'Azur

#### **Composition du Jury :**

| Président :                           | Gilles SASSATELLI                | Directeur de recherche, LIRMM, CNRS/Université Montpellier                                             |

|---------------------------------------|----------------------------------|--------------------------------------------------------------------------------------------------------|

| Examinatrice :                        | Lilia ZAOURAR                    | Ingénieure de Recherche-PhD, CEA List                                                                  |

| Dir. de thèse :<br>Co-dir. de thèse : | Cédric KILLIAN<br>Daniel CHILLET | Professeur des Universités, Université Jean-Monnet<br>Professeur des Universités, Université de Rennes |

"Tout récipient se restreint par son contenu, sauf le récipient de la connaissance, car il s'élargit avec lui."

La Voie de l'Éloquence

# Acknowledgement

Tout d'abord, je voudrais remercier mes superviseurs, Daniel Chillet et Cedric Killian, pour leurs conseils, leurs discussions perspicaces et leur précieux mentorat tout au long de mon parcours de doctorat. Vous m'avez montré comment faire de la bonne recherche. Vous m'avez encouragé dans les moments difficiles et je vous en suis très reconnaissant.

Je tiens à exprimer ma profonde gratitude à tous les membres du comité de soutenance pour avoir accepté d'évaluer mon travail de thèse. M. VERDIER François et M. GOG-NIAT Guy pour avoir été membre de mon jury de thèse et avoir montré de l'intérêt pour le projet. Mme. Lilia ZAOURAR et M. Gilles SASSATELLI qui ont accepté d'être les examinateurs de mon projet de thèse et ont consacré leur temps à l'évaluation approfondie de mon travail. Votre volonté d'évaluer ce manuscrit ne valide pas seulement des années de travail acharné, mais constitue le dernier pont crucial entre l'étudiant et l'universitaire. Votre expertise et vos critiques perspicaces ont été un atout inestimable, façonnant non seulement ce manuscrit mais aussi mes aspirations futures en tant que chercheur.

En outre, je remercie sincèrement les membres de l'équipes TARAN et Granit : le chef de notre laboratoire Prof. Olivier Sentieys, tous les membres permanents de notre laboratoire qui n'ont jamais hésité à nous fournir l'aide dont nous avions besoin, et qui ont offert beaucoup de conseils et de discussions lors de nos réunions de groupe. Un grand merci à tous les doctorants et chercheurs postdoctoraux de notre équipe. Mais je n'oublie pas non plus de remercier le Dr. Joel Ortiz Sosa pour sa collaboration et l'aide apportée au début de mon projet.

La base sur laquelle ma vie est construite est sans aucun doute ma famille. Mon père Ali et ma mère Jamila, vos sacrifices, votre amour et votre foi inébranlable en moi ont été le vent sous mes ailes. Vous m'avez inculqué les valeurs de travail, d'intégrité et de compassion qui m'ont guidé à chaque étape de ce voyage. Votre foi en moi a souvent dépassé la mienne et je vous en serai éternellement reconnaissante. Je n'oublierais pas non plus mes frères Hussein, Abbass et Mohammed et mes sœurs Fatima et Marwa qui ont toujours cru en moi et m'ont soutenu à chaque étape de ma vie. Votre amour, votre patience et votre foi en mes capacités ont été une source constante de motivation dont je vous suis éternellement reconnaissante. Je tiens à exprimer ma plus profonde gratitude envers la communauté libanaise, qui s'est révélée être bien plus qu'une communauté : une véritable deuxième famille. Votre soutien gravé dans mon cœur.

À ma fiancée Nour, les mots me manquent pour exprimer toute ma gratitude pour ton amour inconditionnel, ton soutien et ta patience. Ton soutien continu a été une source constante de force, rendant les défis moins ardus et les joies bien plus douces. Pour votre amour, votre soutien, votre patience et pour les innombrables petites choses que vous faites et qui font une grande différence, merci.

Enfin, et ce n'est certainement pas le moins important, je tiens à exprimer ma profonde gratitude envers le Dieu et l'Imam Al Mahdi tout-puissant pour toutes leurs grâces et leur soutien tout au long de ce projet. Je leur offre ce travail en signe de remerciement, et je suis reconnaissant pour tout ce qu'ils ont fait.

# Contents

| $\mathbf{R}$ | Résumé étendu |         | 17                                                                                                              |    |

|--------------|---------------|---------|-----------------------------------------------------------------------------------------------------------------|----|

| In           | Introduction  |         | 23                                                                                                              |    |

| 1            | Sta           | te of t | he art                                                                                                          | 29 |

|              | 1.1           | Introd  | luction                                                                                                         | 29 |

|              | 1.2           | Histor  | rical Evolution and Background of Network on Chip Architectures                                                 | 30 |

|              |               | 1.2.1   | Evolution of microprocessors                                                                                    | 30 |

|              |               | 1.2.2   | Topologies                                                                                                      | 32 |

|              |               |         | 1.2.2.1 2D Topologies                                                                                           | 32 |

|              |               |         | 1.2.2.2 3D Topology                                                                                             | 35 |

|              |               | 1.2.3   | Data transfer format                                                                                            | 36 |

|              |               | 1.2.4   | Components                                                                                                      | 37 |

|              |               | 1.2.5   | Routing algorithm                                                                                               | 38 |

|              |               | 1.2.6   | Flow control methods and arbitration                                                                            | 39 |

|              |               | 1.2.7   | Pros and Cons of classical Electrical NoCs                                                                      | 41 |

|              | 1.3           | Emerg   | ging Technologies                                                                                               | 42 |

|              |               | 1.3.1   | Optical Networks on Chip                                                                                        | 43 |

|              |               | 1.3.2   | RF-Interconnect NoC                                                                                             | 44 |

|              |               | 1.3.3   | Surface Wave Interconnect                                                                                       | 45 |

|              |               | 1.3.4   | Wireless Networks on Chip                                                                                       | 46 |

|              |               |         | 1.3.4.1 Key components                                                                                          | 46 |

|              |               |         | 1.3.4.2 Architectures $\ldots$ | 46 |

|              |               |         | 1.3.4.3 Channel access methods and protocols                                                                    | 49 |

|              |               | 1.3.5   | Overall comparison                                                                                              | 52 |

|              | 1.4           | NoC 7   | Traffic patterns                                                                                                | 53 |

|              |               | 1.4.1   | Synthetic Traffic                                                                                               | 53 |

|              |               | 1.4.2   | Benchmark applications                                                                                          | 54 |

|              |               |         | 1.4.2.1 Benchmark suites                                                                                        | 54 |

### CONTENTS

|          |                     |                   | 1.4.2.2 Characterization $\ldots$                         | 57        |

|----------|---------------------|-------------------|-----------------------------------------------------------|-----------|

|          | 1.5                 | Conclu            | usion                                                     | 58        |

| <b>2</b> | AM                  | IHNO              | C : Analytical Model for Hybrid NoC                       | 61        |

|          | 2.1                 |                   | uction                                                    | 61        |

|          | 2.2                 |                   | mance Evaluation                                          | 62        |

|          |                     | 2.2.1             | Evaluation metrics                                        | 63        |

|          |                     | 2.2.2             | Evaluation tools                                          | 65        |

|          |                     |                   | 2.2.2.1 Simulators                                        | 65        |

|          |                     |                   | 2.2.2.2 Analytical model                                  | 69        |

|          | 2.3                 | Hybrid            | d interconnection models                                  | 72        |

|          |                     | 2.3.1             | Overview of the analysis flow                             | 72        |

|          |                     | 2.3.2             | Analytical Model                                          | 73        |

|          |                     |                   | 2.3.2.1 A simple one-input one-output routing element     | 73        |

|          |                     |                   | 2.3.2.2 General case                                      | 76        |

|          | 2.4                 | Exper             | imental Evaluations                                       | 78        |

|          |                     | 2.4.1             | Experimental Setup                                        | 78        |

|          |                     | 2.4.2             | Parameters exploration with synthetic traffics            | 79        |

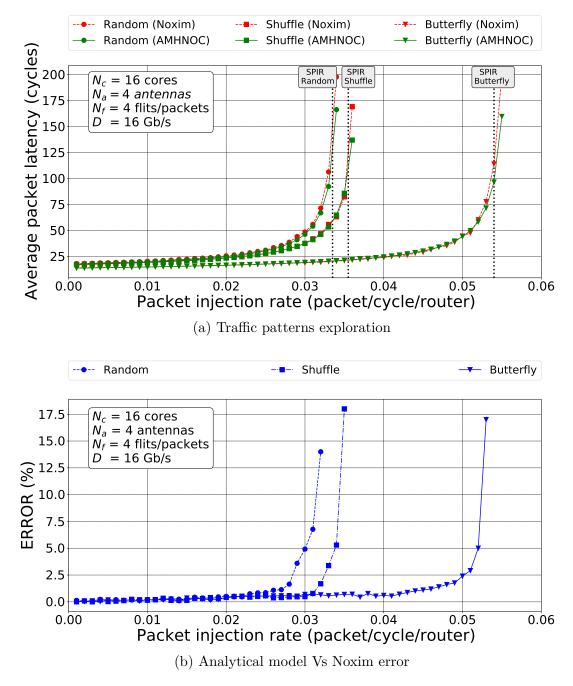

|          |                     |                   | 2.4.2.1 Traffic patterns exploration                      | 80        |

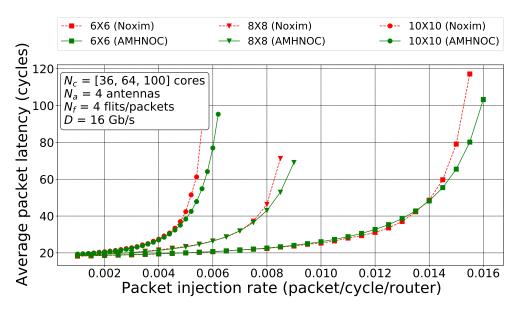

|          |                     |                   | 2.4.2.2 Architecture size exploration                     | 82        |

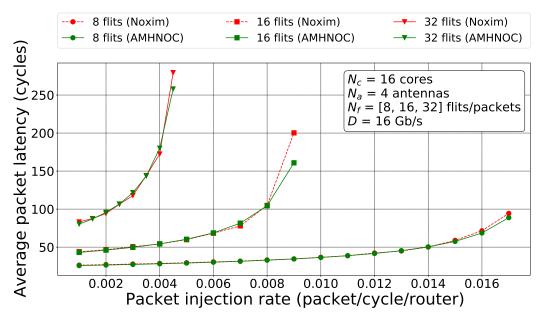

|          |                     |                   | 2.4.2.3 Packet size exploration                           | 83        |

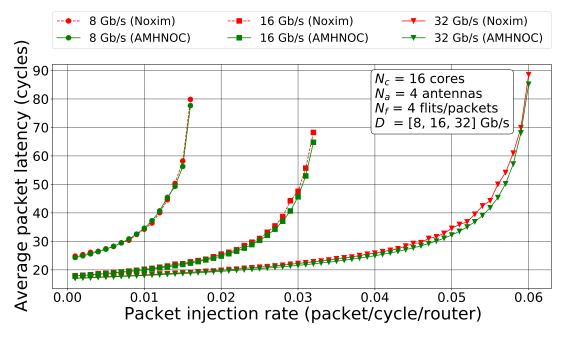

|          |                     |                   | 2.4.2.4 Wireless datarate exploration                     | 84        |

|          |                     |                   | 2.4.2.5 Exploration of number of antennas                 | 85        |

|          |                     | 2.4.3             | Network throughput                                        | 86        |

|          |                     | 2.4.4             | Execution time                                            | 86        |

|          |                     | 2.4.5             | Benchmark applications                                    | 88        |

|          |                     | 2.4.6             | Relative Error                                            | 90        |

|          | 2.5                 | Conclu            | usion                                                     | 91        |

| 3        | <b>11</b> 7;,       | dowin             | g of application traces for fast NoC performance analysis | 93        |

| ა        | <b>vv</b> II<br>3.1 |                   | uction                                                    | <b>93</b> |

|          | 3.1<br>3.2          |                   |                                                           |           |

|          | 0.2                 | 3.2.1 Noxim-Cycle |                                                           | 95<br>96  |

|          |                     | 3.2.1<br>3.2.2    | Results Comparison                                        | 90<br>96  |

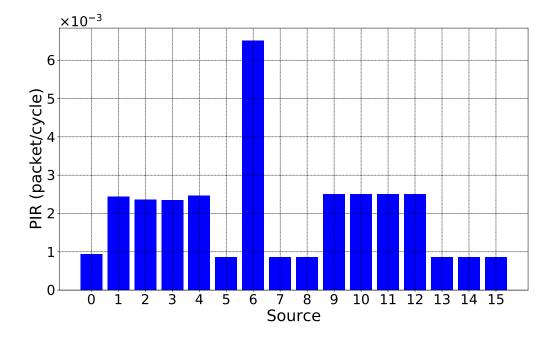

|          | 3.3                 |                   | mark Application Traffic Injection Distribution           | 90<br>97  |

|          | 0.0                 | Donon             | mark application frame injection Distribution             | 51        |

### CONTENTS

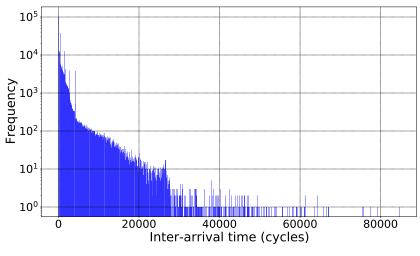

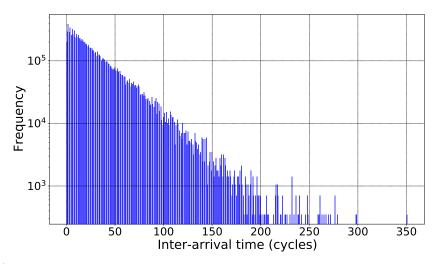

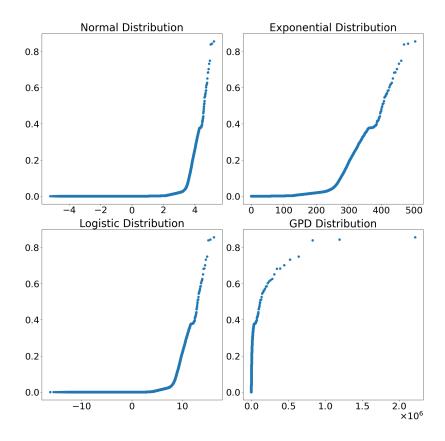

|                        | 3.3.1        | Inter-arrival times                                                                                 | 97  |

|------------------------|--------------|-----------------------------------------------------------------------------------------------------|-----|

|                        | 3.3.2        | Squared Coefficient of Variation and Q-Q Plot                                                       | 100 |

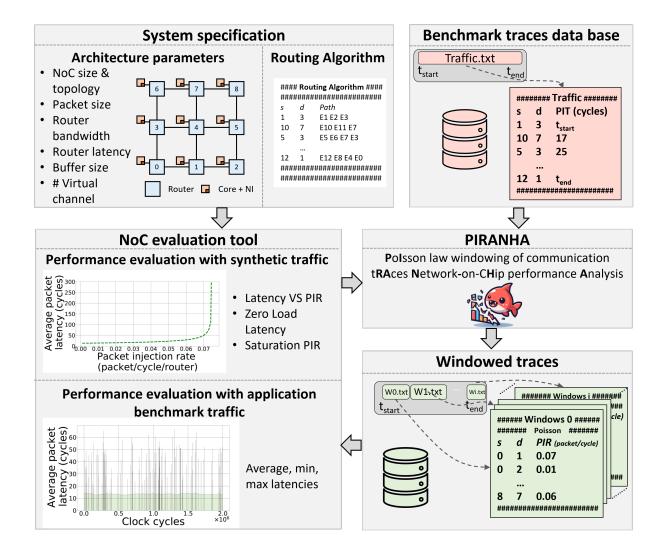

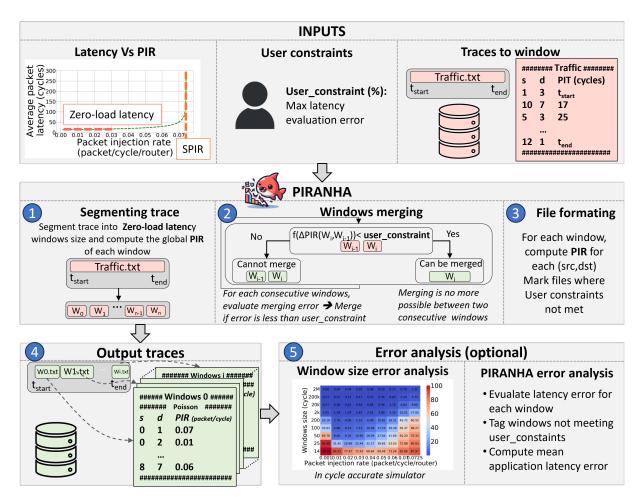

| 3.4 Proposed Framework |              | sed Framework                                                                                       | 102 |

|                        | 3.4.1        | Overview                                                                                            | 102 |

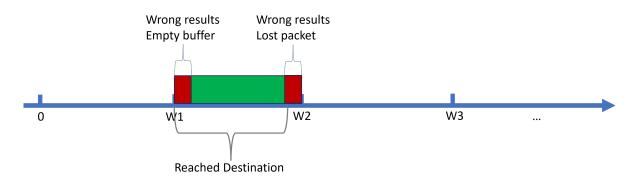

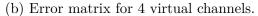

|                        | 3.4.2        | Impact of windows on errors $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 104 |

|                        | 3.4.3        | PIRANHA methodology                                                                                 | 104 |

| 3.5                    | Exper        | imental Results                                                                                     | 107 |

|                        | 3.5.1        | Experimental Setup                                                                                  | 107 |

|                        | 3.5.2        | Random Traffic Analysis                                                                             | 108 |

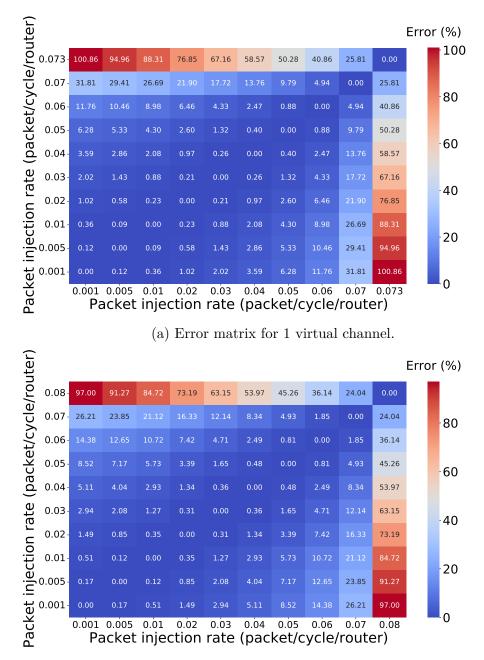

|                        | 3.5.3        | Error Matrices                                                                                      | 109 |

|                        | 3.5.4        | PIRANHA Validation                                                                                  | 112 |

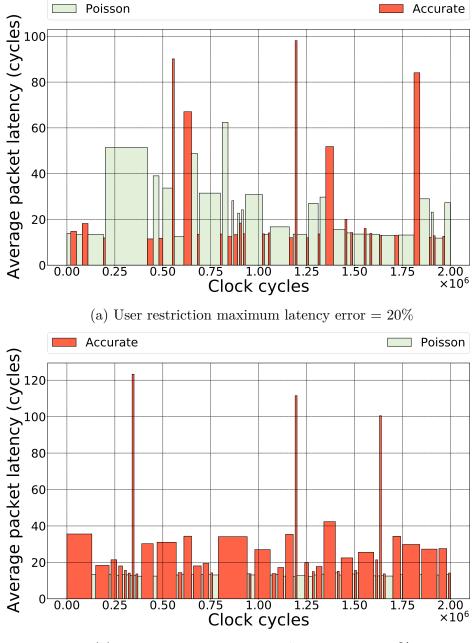

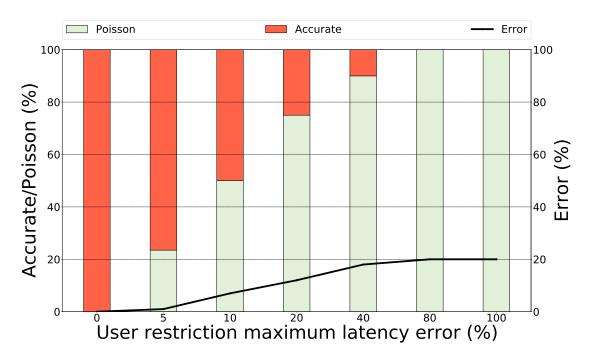

|                        | 3.5.5        | PIRANHA Extension : Windowing <i>Poisson</i> and <i>Accurate</i>                                    | 113 |

|                        | 3.5.6        | Discussion                                                                                          | 116 |

|                        |              | 3.5.6.1 <i>Poisson</i> and <i>Accurate</i> utilization                                              | 116 |

|                        |              | 3.5.6.2 Input file size $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$     | 117 |

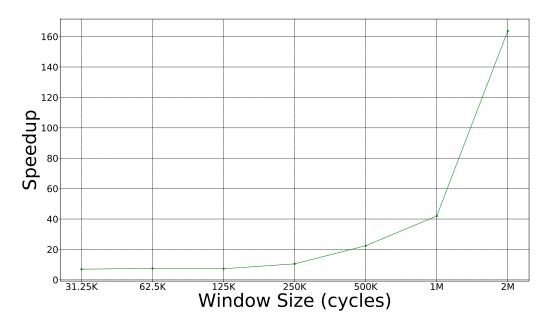

|                        |              | 3.5.6.3 Execution time $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$      | 117 |

|                        |              | 3.5.6.4 Number of windows                                                                           | 118 |

| 3.6                    | Concl        | usion                                                                                               | 119 |

| 4 Co                   | nclusio      | n and perspectives                                                                                  | 121 |

| 4.1                    | Concl        | usion                                                                                               | 121 |

| 4.2                    | Persp        | ectives                                                                                             | 122 |

| Scient                 | ific Co      | ntributions                                                                                         | 125 |

| Acron                  | Acronyms     |                                                                                                     | 127 |

| Biblio                 | Bibliography |                                                                                                     | 129 |

# **List of Figures**

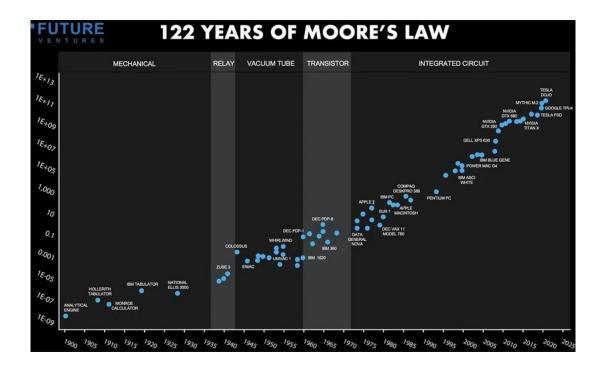

| 1    | 122 years of Moore's law [AI]                                               | 24 |

|------|-----------------------------------------------------------------------------|----|

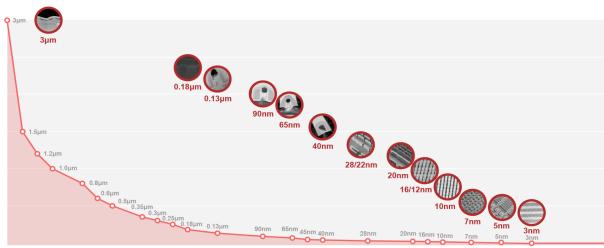

| 2    | The evolution of the node sizes of semiconductor technology over several    |    |

|      | decades [TSM].                                                              | 25 |

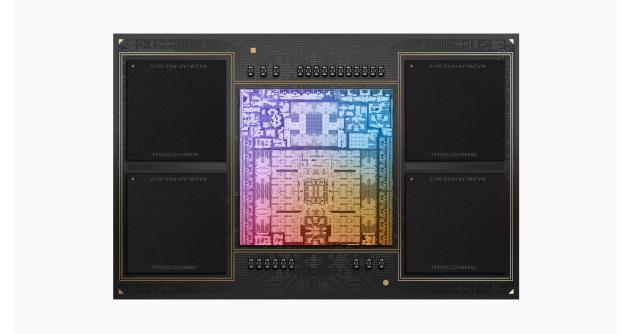

| 3    | M2 Pro features 40 billion transistors, 200GB/s of unified memory band-     |    |

|      | width, and up to 32GB of fast, low-latency unified memory.                  | 26 |

| 4    | General Architecture for an MPSoC using a shared-memory bus-based sys-      |    |

|      | tem                                                                         | 26 |

| 1.1  | 50 years of Microprocessor Trend Data [Rup22]                               | 31 |

| 1.2  | Different Network-on-Chip (NoC) direct topologies.                          | 32 |

| 1.3  | Unicast, multicast and broadcast communication.                             | 34 |

| 1.4  | 3D OASIS-NoC $2 \times 2 \times 4$ mesh topology [AAK10]                    | 35 |

| 1.5  | Data transmission hierarchical: Bits, Flits, Packets and Messages           | 36 |

| 1.6  | An example of a NoC-based many-core on-chip system                          | 37 |

| 1.7  | Example of routing algorithms: (a) XY and (b) West-first routing algorithm. | 38 |

| 1.8  | Technology based classification NoC [BBB17]                                 | 42 |

| 1.9  | Nanophotonic interconnect NoC Optical (ONoC) [Lee22].                       | 43 |

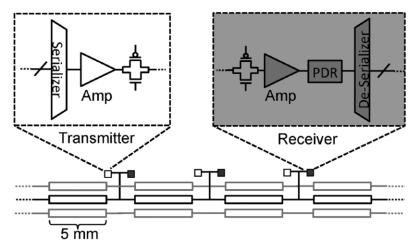

| 1.10 | General schematic representation for the transmission line link intercon-   |    |

|      | nect. On the left, we have the Transmitter block, containing a Serializer   |    |

|      | followed by an amplifier (Amp). On the right, the Receiver block also con-  |    |

|      | tains an amplifier, followed by a Phase and data recovery (PDR) and a       |    |

|      | Deserializer. The two blocks are connected by a series of lines that repre- |    |

|      | sent the transmission line itself, with a measurement 5 mm. [Car+12]        | 44 |

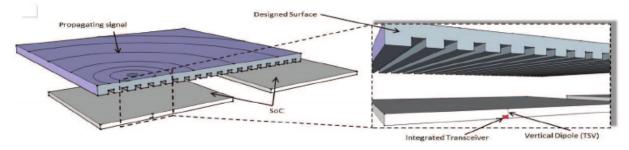

| 1.11 | Surface wave implementation [Kar+12]                                        | 45 |

|      | Sketch of a Wireless NoC architecture [Tim+18]                              | 47 |

| 1.13 | A pure multi-channel wireless-based NoC with a mesh topology [Zha+11]       | 47 |

| 1.14 | Example of Hybrid NoC architecture                                          | 48 |

| 1.15 | Token                                                                       | 50 |

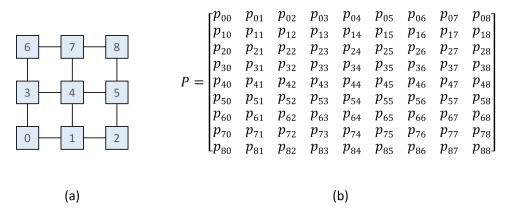

| 1.16 | Example of $N_c = 9$ cores based on (a) network mesh topology with its      |    |

|      | respective (b) frequency matrix of communication between cores              | 54 |

### LIST OF FIGURES

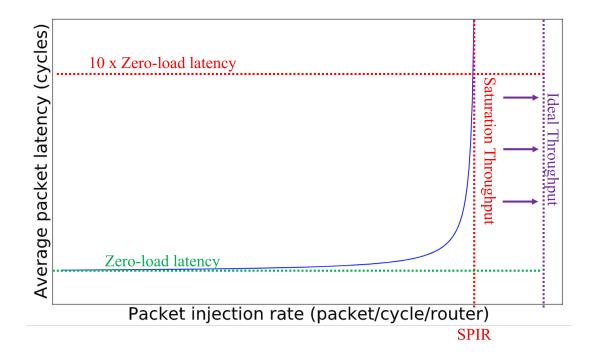

| 2.1  | Average latency relation to packet injection rate                                              | 64  |

|------|------------------------------------------------------------------------------------------------|-----|

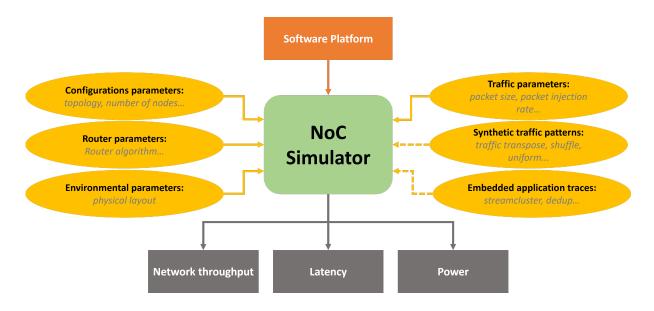

| 2.2  | Overview of NoC simulator.                                                                     | 66  |

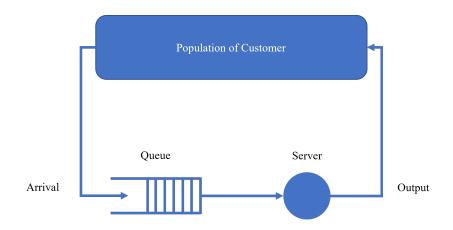

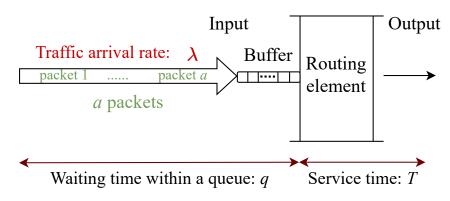

| 2.3  | Queueing theory.                                                                               | 70  |

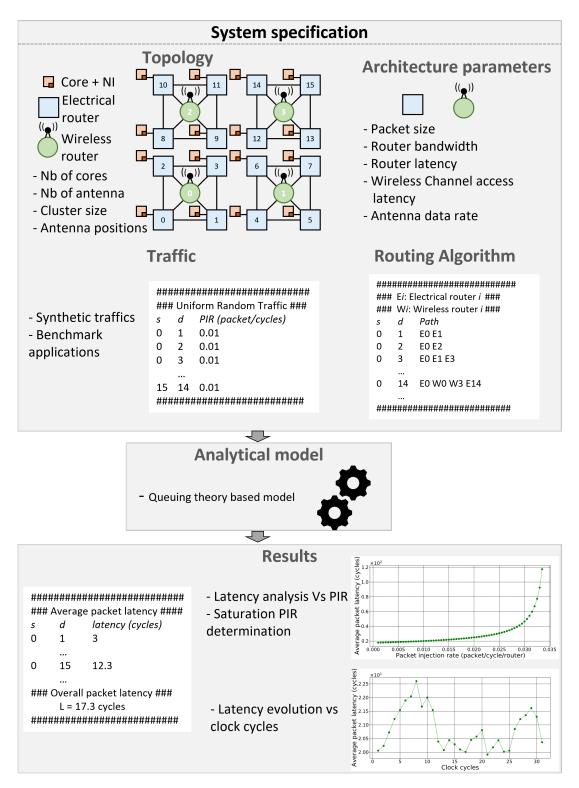

| 2.4  | Overview of the analysis flow based on AMHNOC.                                                 | 71  |

| 2.5  | Example of a single queue routing element                                                      | 75  |

| 2.6  | General case of service managing $m$ inputs and $n$ outputs                                    | 76  |

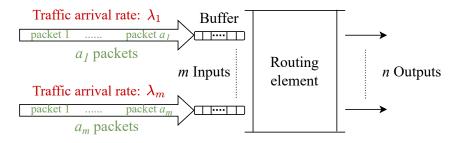

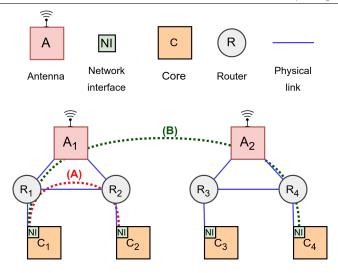

| 2.7  | Overview of a cluster-based hybrid NoC. Intra-cluster communication are                        |     |

|      | done through ENoC (A), while inter-cluster communications are handled                          |     |

|      | with wireless communications (B)                                                               | 79  |

| 2.8  | Traffic patterns exploration (a) and analytical model Vs Noxim error (b).                      | 81  |

| 2.9  | Architecture size exploration.                                                                 | 82  |

| 2.10 | Packet size exploration                                                                        | 83  |

| 2.11 | Wireless datarate exploration.                                                                 | 84  |

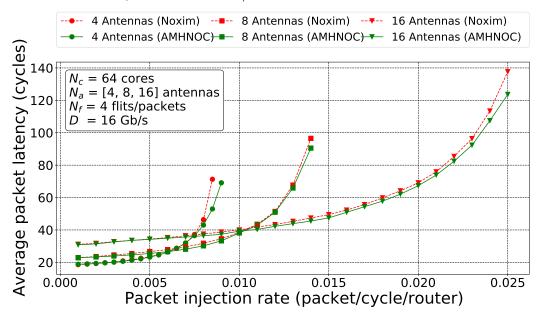

| 2.12 | Exploration of number of antennas                                                              | 85  |

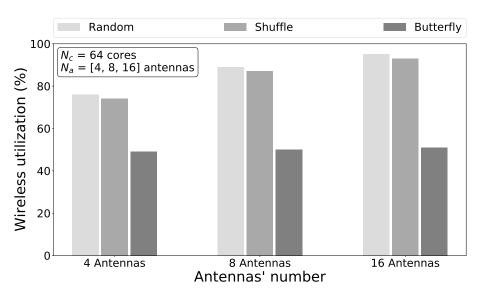

| 2.13 | Wireless utilization rate.                                                                     | 86  |

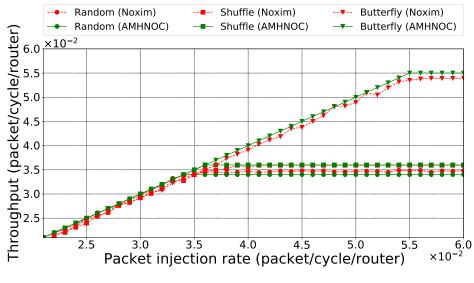

| 2.14 | Throughput Vs. PIR                                                                             | 87  |

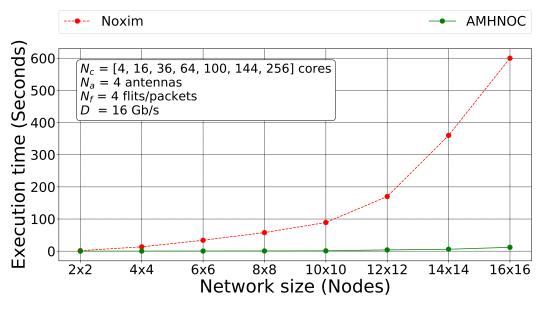

| 2.15 | Execution time evaluation.                                                                     | 88  |

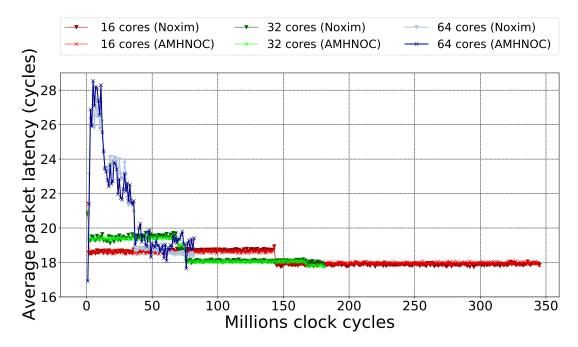

| 2.16 | Validation of the analytical model using the dedup benchmark application                       | 89  |

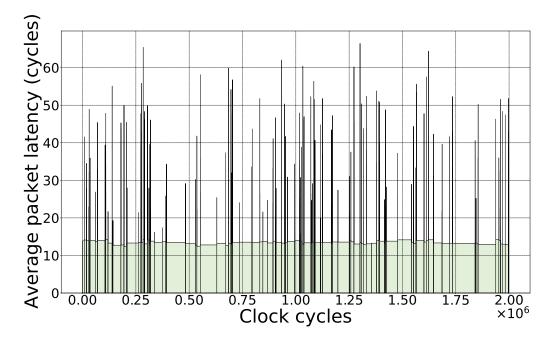

| 3.1  | Packet injection rate per source for dedup application.                                        | 98  |

| 3.2  | Distribution of inter-arrival times for dedup application. $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 99  |

| 3.3  | Q-Q plots of inter-arrival times of dedup benchmark against well known                         |     |

|      | distributions                                                                                  | 101 |

| 3.4  | Overview of the NoC performance evaluation flow integrating the proposed                       |     |

|      | PIRANHA method                                                                                 | 102 |

| 3.5  | Lost/reach packets.                                                                            | 104 |

| 3.6  | PIRANHA method                                                                                 | 105 |

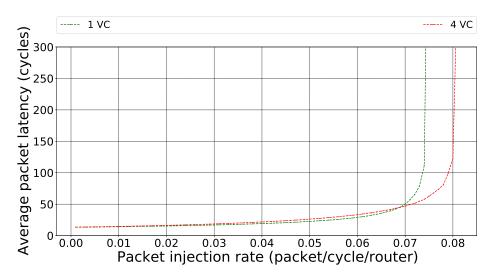

| 3.7  | Average packet latency Vs. Packet injection rate (PIR) for 1 and 4 virtual $$                  |     |

|      | channel                                                                                        | 108 |

| 3.8  | Error matrix obtained when merging the two windows.                                            | 110 |

| 3.9  | Error matrices obtained versus size window                                                     | 111 |

| 3.10 | Validation of PIRANHA using the dedup benchmark application with $Pois$ -                      |     |

|      | son method for traces windowing                                                                | 112 |

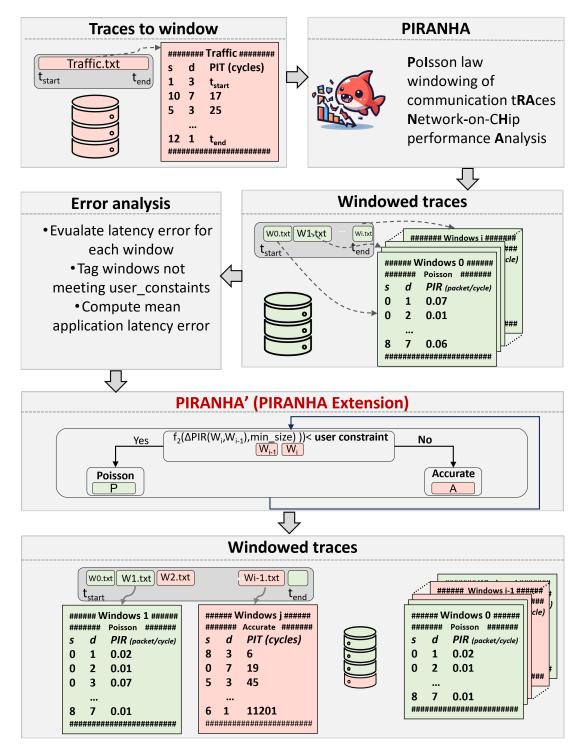

| 3.11 | PIRANHA Extension method                                                                       | 114 |

| 3.12 | Validation of PIRANHA using the dedup benchmark application with Pois-    |

|------|---------------------------------------------------------------------------|

|      | son & Accurate method for traces windowing                                |

| 3.13 | Validation of PIRANHA using the dedup benchmark application with $Pois$ - |

|      | son & Accurate                                                            |

| 3.14 | Speedup evaluation                                                        |

# **List of Tables**

| 1.1 | Advantages of Different Flow Control Techniques [MMH21].                                                | 40  |

|-----|---------------------------------------------------------------------------------------------------------|-----|

| 1.2 | Summary comparison of the key features for current and emerging on-chip                                 |     |

|     | interconnects [Kar+16]                                                                                  | 51  |

| 1.3 | Comparisons among the WiNoC, 3D-NoC and photonic NoC [WJ14]                                             | 53  |

| 1.4 | Overview of PARSEC workloads [DM14]                                                                     | 55  |

| 2.1 | Comparison of NoC simulators [Kha+18]                                                                   | 67  |

| 2.2 | Summary comparison of different analytical models                                                       | 72  |

| 2.3 | List of the parameters used in our model $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 74  |

| 2.4 | Average latency error between the analytical model compared to Noxim for                                |     |

|     | different benchmark applications                                                                        | 90  |

| 3.1 | Example of table-based input of Noxim: a) using PIR and b) using PIT                                    | 96  |

| 3.2 | Parameters for latency evaluation                                                                       | 96  |

| 3.3 | Mean, standard deviation and Square Coefficient of Variation (SCV) of the                               |     |

|     | Packet Inter-Arrival Times for PARSEC Benchmarks                                                        | 100 |

| 3.4 | Parameters for experimental setup.                                                                      | 108 |

| 3.5 | Input size for Accurate and Poisson for different benchmark applications 1                              | 117 |

# Réseaux sur Puce - Network-on-Chip

Le paysage technologique en constante évolution stimule la demande de systèmes embarqués multicœurs à grande échelle et hautement efficaces. Depuis son introduction au début des années 2000, le concept de Réseaux sur Puce (Network-on-Chip - NoC) a subi une transformation notable, s'établissant fermement dans l'architecture de ces systèmes. Actuellement, les NoCs sont incorporés dans des composants avancés tels que le CPU Intel Core i9 [Int], le Système sur puce Snapdragon® 8 Gen 2 de Qualcomm [Yua+23] et le FPGA Stratix d'Altera [Sam+23], témoignant de leur importance et de leur pertinence dans l'industrie des semi-conducteurs.

L'étude des NoCs implique une analyse minutieuse de leurs divers composants, notamment les algorithmes de routage et les critères d'évaluation pertinents. Face à l'évolution rapide de la technologie des semi-conducteurs et aux besoins accrus en traitement de données, les NoCs classiques rencontrent continuellement de nouveaux défis [PJD22]. La recherche et le développement incessants ont conduit à l'apparition de stratégies innovantes pour surmonter ces obstacles, assurant ainsi l'adaptabilité et l'efficacité des NoCs dans le contexte technologique actuel [MSP23].

# Évaluation des performances

L'évolution vers des architectures multicœurs, caractérisée par un parallélisme massif sur une seule puce, a marqué un tournant ces dernières années. Ces architectures, intégrant des dizaines, voir des centaines de cœurs hétérogènes, favorisent des capacités de calcul parallèle considérables, pertinentes notamment pour le calcul à haute performance (High-Performance Computing HPC) [Viv21]. Cette augmentation du parallélisme entraîne une augmentation conséquente des échanges de données, mettant en lumière l'importance cruciale du système de communication pour la performance globale.

Les avancées dans l'intégration du silicium ouvrent la voie à des interconnexions innovantes telles que les réseau sans fil sur puce (WiNoCs) [Ort+19]. Les WiNoCs exploitent la large bande de fréquences du processus CMOS, permettant des communications rapides sur de longues distances sans augmentation significative de la latence, contrairement aux NoCs électriques qui sont limités par les traversées de routeurs. Bien que les WiNoCs puissent fonctionner seuls, la combinaison de WiNoCs et de NoCs électriques dans un système hybride offre une flexibilité, en utilisant des communications sans fil pour les distances longues et des routeurs électriques pour les distances courtes, pour surmonter les limitations de bande passante des WiNoCs.

L'exploration des architectures de systèmes multicœurs représente un défi en raison de la complexité et du temps requis pour l'évaluation des performances, laquelle repose souvent sur des simulations lentes, particulièrement dans le cas de système à large échelle. En alternative, la modélisation mathématique se présente comme un compromis intéressant entre rapidité de calcul et précision. Les modèles analytiques appliqués aux interconnexions sur puce, basés sur la théorie des files d'attente, offrent des indicateurs de performance comme l'utilisation moyenne de la mémoire tampon et la latence des paquets. Toutefois, un défi majeur réside dans le fait que les modèles actuels sont principalement conçus pour des interconnexions homogènes et ne s'adaptent pas bien aux systèmes d'interconnexion hybrides.

## Traces de trafic d'application

L'évaluation des performances d'un NoC lors des premières phases de conception architecturale, souvent désignée comme l'exploration de l'espace de conception, est cruciale pour les concepteurs de système sur puce. La simulation de systèmes complets, englobant l'architecture dans son ensemble – coeurs de calcul, mémoires, interconnexions, et l'exécution des applications –, représente la méthode la plus fiable pour évaluer les performances des interconnexions et leur influence sur l'exécution des applications. De plus, cette approche est essentielle pour mesurer précisément la vitesse d'exécution d'une application.

Malgré son importance, la simulation de systèmes complets pour l'évaluation des performances des NoCs s'avère extrêmement chronophage. La complexité de personnaliser des simulateurs tels que le fameux Gem5 représente un premier obstacle majeur pour les concepteurs souhaitant tester des interconnexions sur puce émergentes. De plus, la durée nécessaire à ces simulations limite drastiquement l'exploration efficace de l'espace de conception. Un exemple concret de cette limitation est la simulation de l'exécution d'une architecture à 64 cœurs traitant une vidéo de 13 secondes avec l'application x264 dans le cadre de la suite PARSEC. Avec un processeur Dual Intel Xeon 4214 et 64 Go de mémoire, une telle simulation requiert environ cinq jours, ce qui restreint considérablement la possibilité d'évaluer divers paramètres en un temps raisonnable.

Les modèles analytiques et les simulateurs NoC représentent des solutions pour l'évaluation des performances des NoCs. Cependant, ils présentent des limites, notamment l'incapacité à évaluer l'accélération des applications, car ils se concentrent sur les traces de communication sans exécuter les applications simultanément avec le NoC. Malgré cela, leur utilisation reste privilégiée dans la conception des NoCs. Historiquement, les concepteurs ont recours à des modèles de trafic génériques, comme les modèles aléatoires ou transposés, pour évaluer le comportement des NoCs. Récemment, l'adoption de modèles de trafic plus réalistes, reflétant le comportement des applications réelles, a gagné en intérêt. Cette approche implique d'abord l'exécution d'une application sur un simulateur de système complet pour enregistrer les traces de communication, qui sont ensuite injectées dans un outil d'analyse de performance NoC. L'injection de ces traces peut se faire de deux manières : i) l'injection paquet par paquet à des moments précis, ou ii) l'utilisation d'un trafic basé sur le taux d'injection de paquets (PIR). La première méthode peut être très chronophage en raison du volume de données à traiter, tandis que la seconde, bien que plus rapide, peut affecter la fidélité des résultats en raison des variations dans le calcul du PIR.

L'utilisation des traces de trafic d'application pour l'analyse de performance des NoCs est un sujet largement abordé dans la littérature. Ces traces sont couramment employées soit pour valider les propositions de recherche, comme dans notre étude, soit pour comparer et caractériser des applications de référence. Des approches variées sont adoptées pour cette analyse. Par exemple, certaines études, comme celles référencées dans [Adusumilli 2023, Chen 2020], utilisent un taux d'injection de paquets (PIR) constant pour chaque cœur durant toute l'application, ce qui peut atténuer les variations et manquer de précision dans l'évaluation des performances de l'interconnexion. D'autre part, d'autres chercheurs [Mandal 2019, Mandal 2021a] ont divisé les traces en fenêtres de temps de taille fixe pour mieux appréhender l'évolution de la latence en fonction des cycles d'horloge. Cependant, la sélection arbitraire de la taille de ces fenêtres soulève des questions quant à l'impact de ce choix sur la précision de l'évaluation des performances.

Les travaux que nous avons réalisés et qui sont présentés dans ce document abordent ces différentes problématiques. Nous proposons d'étendre les modèles analytiques pour prendre en compte l'hétérogénéité d'un NoC. De plus, nous proposons un modèle exhaustif pour l'analyse des traces d'application et l'automatisation de leur utilisation dans l'évaluation des performances des NoCs, que ce soit via des simulations ou des modèles analytiques.

## Le reste du manuscrit est organisé de la façon suivante

#### Chapitre 1

Ce chapitre dédié aux NoCs traite de leur évolution historique et des principes fondamentaux qui les régissent. Nous entamerons par une analyse approfondie des topologies, des composants et des formats de transfert de données des NoCs, suivie d'un examen des algorithmes de routage et des techniques de contrôle de flux. Par la suite, nous définirons et discuterons les critères d'évaluation qui déterminent les performances des NoCs. Il est également crucial de reconnaître les limites des NoCs électriques traditionnels, tout en examinant les technologies émergentes, en particulier les réseau sans fil sur puce. Finalement, le chapitre conclura avec une explication détaillée des différents modèles de trafic utilisés dans les NoCs, en se concentrant sur les applications synthétiques et les benchmarks.

#### Chapitre 2

Dans ce chapitre, nous proposons d'étendre les modèles analytiques pour prendre en compte l'hétérogénéité d'un NoC. Nous introduisons un modèle analytique innovant pour les NoCs hybrides, basé sur le modèle de file d'attente M/G/1. Ce modèle est conçu pour évaluer la latence moyenne des paquets et le débit du réseau dans unNoC hybride, où les paquets peuvent emprunter des chemins électriques, sans fil, ou mixtes. Le modèle repose sur une distribution de Poisson pour le trafic de communication, avec des routeurs utilisant l'arbitrage round-robin et un accès au canal sans fil via un système de passage de jetons. Il permet une configuration distincte des temps de service et des capacités des canaux électriques et sans fil, reflétant les conceptions matérielles réelles. Ce modèle offre une hétérogénéité qui facilite l'exploration des paradigmes de conception futures, tels que les architectures basées sur les chiplets ou les accélérateurs. Il aborde des caractéristiques clés non couvertes par les modèles conventionnels, telles que i) un mécanisme d'accès au canal sans fil distinct, ii) des largeurs de bande de communication hétérogènes entre les médias électriques et sans fil, et iii) des différences dans les temps de latence entre les routeurs électriques et sans fil. À notre connaissance, ce modèle est le premier de son genre pour une interconnexion hybride sur puce.

### Chapitre 3

Ce chapitre se consacre à l'élaboration d'un modèle exhaustif pour l'analyse des traces d'application et l'automatisation de leur usage dans l'évaluation des performances des NoCs, que ce soit via des simulations ou des modèles analytiques. L'intégration des fenêtres d'analyse est mise en avant, soulignant leur rôle crucial dans la capture de la dynamique temporelle de la latence. Le cadre développé ne se limite pas à recommander l'utilisation de fenêtres d'analyse ; il fournit également des indications sur la taille optimale de ces fenêtres et expose les bénéfices de leur utilisation. En offrant une perspective détaillée sur l'évaluation des applications réelles et en explorant l'impact des fenêtres d'analyse sur les résultats, ce modèle permet d'améliorer la robustesse des études de recherche et de réaliser des comparaisons plus précises entre différentes architectures. Ainsi, ce chapitre enrichit la compréhension de l'évaluation des performances des NoCs et promeut une approche plus approfondie et complète de l'analyse des applications de référence dans le domaine des architectures informatiques.

## **Context and Motivations**

In the early days of the electronics industry, devices were mainly based on electron tubes. These tubes control the flow of electrons between two metal electrodes in a vacuum or gas-sealed container [Oka94]. In 1925, Lilienfeld [Edg30] introduced the concept of current control by a perpendicular electric field, later known as Metal-Semiconductor Field-Effect Transistor (MESFET). Despite the difficulties encountered in the initial manufacture of the MESFET, progress was made with Schottky's theory of rectification behavior in metal-semiconductor contacts and the creation of the first bipolar junction transistor in 1947 by Bardeen, Brattain and Shockley [Ort09]. More progress was then made in the 1960s with the development of the Metal-Oxide-Semiconductor Field-Effect Transistor (MOSFET) and the establishment of silicon as the reference semiconductor, thus culminating in the successful manufacture of the MESFET [Mea66], marking the transition to the era of nanoscale electronics.

Moore's Law, a key concept in semiconductor technology, has its origins in an observation made in 1965 by Gordon Moore, co-founder of Intel. Figure 1 illustrates the 122 years of Moore's law, which postulates that the number of transistors on a microelectronic chip will double approximately every two years, increasing computing power. The graph shows the evolution of different computing technologies, from mechanical systems to integrated circuits. It starts with mechanical devices used in the early 20th century, followed by relays, vacuum tubes, transistors, and finally integrated circuits dominating today. An exponential increase in the computing power can be observed over time, particularly from the 1960s onward with the advent of transistors. This trend highlights the rapid and impressive progress of semiconductor technology, leading to major advances in computing and digital technologies.

Figure 2 additionally illustrates the evolution of the node sizes of semiconductor technology over several decades, from  $3\mu m$  to 3nm. A constant and significant reduction in node size is recognized, reflecting the technological advances in miniaturization. The graph further shows that, as early as the 1970s, the nodes were relatively large, measur-

Figure 1: 122 years of Moore's law [AI].

ing micrometers. However, as technology progressed, they gradually decreased, reaching sub-micrometer sizes such as 90nm, 65nm, and down to recent nanometer sizes such as 7nm and 5nm. The images inserted in the graph show the density of transistors or structures at each stage, highlighting the massive increase in density as technology advances. This continuous reduction in node size is a testament to the ingenuity of microelectronics engineering, enabling increased performance and greater chip energy efficiency.

For instance, in the beginning of 2023, apple announced [App] the M2, M2 pro and M2 Max (Figure 3) next generation System-on-Chip (SoC): the M2 Max builds upon the capabilities of the M2 Pro, featuring up to a 12-core CPU and a remarkable 19-core GPU. In addition, the M2 Max boasts a GPU with up to 38 cores. This cutting-edge chip is manufactured using second-generation 5 nm process technology. When it comes to the transistor count, the M2 Pro is packed with 40 billion transistors, while the M2 Max contains an astounding 67 billion.

Today, other giants such as Huawei are not to be outdone, regularly announcing significant technological advances in this field. The Kirin 9000S processor is used in the latest Mate 60 Pro phone [HUA]. The Kirin 9000 is an advanced 5nm chipset, featuring a CPU with 1x Cortex-A77 at 3.13 GHz, 3x Cortex-A77 at 2.54 GHz, and 4x Cortex-A55

Figure 2: The evolution of the node sizes of semiconductor technology over several decades [TSM].

at 2.05 GHz. It features a 24-core Mali-G78 GPU with Kirin Gaming+ 3.0, Huawei Da Vinci 2.0 AI architecture with 2x Ascend Lite + 1x Ascend Tiny, supports 5G SA&NSA, Sub-6G&mmWave, has a four-channel Kirin 6.0 ISP, 8 MB system cache and supports LPDDR5/4X memory.

These innovations are not simply technological triumphs. They also embody a global struggle for supremacy in the semiconductor sector. It is not just a competition between companies but also between nations. Chips and Integrated Circuit (IC) are at the heart of most modern technologies, from smartphones and autonomous cars [GGM23] to communications infrastructures and supercomputers. Whoever leads in this field holds considerable influence, both economically and strategically.

The frenetic pace of this "chip war" illustrates just how crucial these innovations are to the future of technology and, by extension, to our way of life.

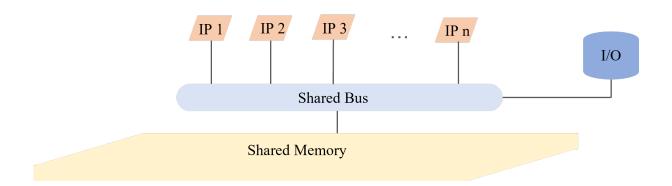

The work presented in this manuscript takes place in the technological domain, particularly concentrating on interconnects, which are crucial components in the architecture of modern computing systems. Our focus is on interconnection and chip performance. Initially, the most common approach to interconnecting the Intellectual Property (IP) such as Central Processing Unit (CPU) cores, memory, and Input/Output (I/O) devices was a shared bus [Ack+00]. This means that all IP had to communicate with each other over the same pathway (bus). Figure 4 illustrates an example of the general architecture of a

Figure 3: M2 Pro features 40 billion transistors, 200GB/s of unified memory bandwidth, and up to 32GB of fast, low-latency unified memory.

Figure 4: General Architecture for an MPSoC using a shared-memory bus-based system.

Multiprocessor System-on-Chip (MPSoC) using a shared memory bus system. Although this approach was simple, it quickly became a bottleneck as the number of cores increased. The shared bus had limited bandwidth, and when multiple cores tried to communicate simultaneously, they had to wait their turn, reducing the overall system performance.

To get around this problem, the importance of on-chip networks came into picture. Initially electrically based, then followed by the emerging of new technologies such as photonics and wireless communication as well as the hybrid communication that combines both electrical with either wireless or photonic communications. These emerging technologies were first considered because of limitations in terms of latency and energy consumption. This thus implies the major issue of performance analysis, which forms a crucial step in the early stages of system-on-chip design.

This evaluation, which involves several metrics such as latency, throughput and energy consumption, can be carried out using different approaches:

- Full system simulator; such as sniper and Gem5, that cover interconnections, cores and memories.

- NoC simulator: like noxim and booksim, are cycle-accurate interconnection network simulator.

- Analytical model: based on queuing theory with which several metrics can be considered such as latency, throughput and saturation.

It is worth noting that simulators are very slow, which is considered as a limitation for designers. On the other hand, analytical models are much faster while still maintaining good precision. Moreover, in terms of complexity, simulators are much more complicated than analytical models.

# Contributions and Organization of the Thesis

This doctoral research makes a significant contribution to the understanding and improvement of NoCs through two major advances, each detailed in its own chapter.

The first contribution, outlined in Chapter 2, "AMHNOC: Analytical Model for Hybrid NoC", presents a novel analytical model for evaluating the performance of hybrid NoCs. We have introduced new evaluation metrics and tools, including simulators and analytical models, to finely analyze hybrid interconnects. In-depth parameter exploration with synthetic traffic was carried out to understand the impacts of traffic patterns, architecture size, packet size, wireless data rate, and number of antennas on network throughput and execution time. This exhaustive analysis has enabled us to identify optimal configurations for different types of reference applications, minimizing relative error and maximizing overall performance.

The second contribution, detailed in Chapter 3, "Application trace windowing for fast NoC performance analysis", proposes a methodological framework for accelerating NoC performance analysis by exploiting application trace windowing. We have developed a window splitting and merging technique to improve the accuracy of performance evaluation while reducing computational complexity. Experimental results validated the effectiveness of this method with random traffic and a combination of precise and Poisson traffic, confirming the significant reduction in errors and improvement in execution time.

Together, these contributions broaden the horizon of possibilities in NoC design and optimization, providing system designers with analytical and practical tools to meet the challenges of today's and tomorrow's high-performance computing systems.

# State of the art

### **1.1** Introduction

As the technological landscape evolves, the demand for efficient, multicore embedded systems on a large scale becomes increasingly critical.

As the technological landscape continues to develop, the need for efficient, multicore embedded systems on a large scale systems becomes increasingly important. Initially introduced in the early 2000s, the concept of NoC has undergone a remarkable evolution and has become strongly based on the architecture of these systems. Today, it is integrated into processors and SoC designs such as the Intel Core i9 CPU [Int], Qualcomm's Snapdragon® 8 Gen 2 SoC [Yua+23], and Altera's Stratix FPGA [Sam+23].

An in-depth study of NoCs requires an extensive exploration of its multiple components, including the routing algorithms used and the relevant evaluation metrics. In parallel with the constant evolution of semiconductor technologies and the increasing demands of data processing, traditional NoCs are regularly subjected to new challenges [PJD22]. Ongoing research and development has enabled the emergence of novel approaches to address these issues, ensuring the adaptability and efficiency of NoCs [MSP23].

In this chapter, the historical evolution of NoCs, highlighting their essential principles will be illustrated (Section 1.2). Starting first with a detailed analysis of topologies, components, and data transfer formats followed by a study of routing algorithms and flow control methods. The evaluation criteria defining the performance of NoCs will be then detailed. Furthermore, despite that traditional electrical NoCs offer many advantages, it is essential to highlight their limitations.

Additionally, the present emerging technologies, in particular Wireless Network-on-Chip (WiNoC) will be presented in Section 1.3. After in Section 1.4, a detailed explanation of the traffic patterns used considering its two types i.e., synthetic and benchmark applications, will be provided.

# 1.2 Historical Evolution and Background of Network on Chip Architectures

Communications saturation in bus-based architectures results from the integration of numerous logic blocks, known as IP, communicating with each other on a single chip as transistors become miniaturized. This led to the recognition of NoC as a remedy for the limitations of MPSoC [BD02]. To overcome the limitations posed by shared bus-based architectures, NoCs offer a scalable and robust solution for interconnecting numerous cores and other components within a single chip, making it an essential feature of the modern SoC landscape.

#### **1.2.1** Evolution of microprocessors

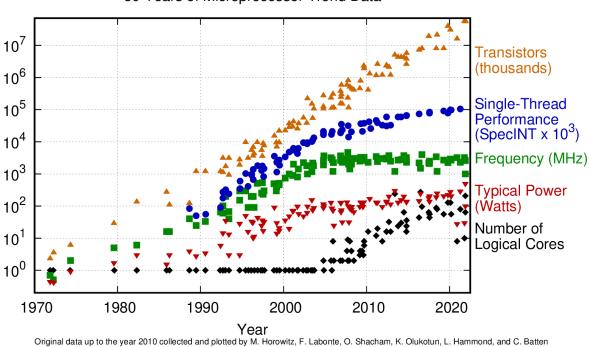

The evolution of microprocessors has been characterized by a continuous increase in computing power, miniaturization of components and improved energy efficiency. Over the last 50 years, the evolution of microprocessors has significantly changed the landscape of digital technology. The constant focus on miniaturization and increased functionality has led to the development of increasingly complex systems. Figure 1.1 [Rup22] shows several key trends in microprocessor development over the past five decades. Since the 1970s, there has been an exponential growth in the number of transistors, in accordance to Moore's law, which predicts a doubling in the number of transistors every two years. This is due to the reduction of the transistor size to just a few nanometers [Tau23]. At the same time, the performance of single thread increased sharply from the 1970s and up until the 2000s before stabilizing. This indicates that the performance gains per thread were reaching their limits. Additionally, the rapid increase in the microprocessor's frequency, until the early 2000s, before slowing down, is probably due to the thermal and power consumption constraints. We also note that microprocessor power consumption rose until the early 2000s before stagnating, reflecting a growing interest in energy efficiency in chip design. Following this stagnation, the industry moved towards a significant increase in the number of logic cores, marking a shift towards multi-core architectures to counter the stabilization of single-threaded performance. In this context, NoC have been crucial to guarantee optimal communication between the various components and cores, reflecting the need to adapt to the growing complexity of SoC.

The progression of SoC and NoC reflects the constant pursuit for higher performance

50 Years of Microprocessor Trend Data

Figure 1.1: 50 years of Microprocessor Trend Data [Rup22].

New plot and data collected for 2010-2021 by K. Rupp

in the microprocessor field. While early generations of microprocessors concentrated on increasing the number of transistors and clock frequency, physical constrains and heat dissipation problems led to the adoption of the multi-core approach. NoCs emerged as an elegant solution to the growing complexity of intra-chip communication, offering superior scalability and energy efficiency compared to traditional bus and point-to-point architectures. This transformation has been accompanied by innovations like Surface Wave Interconnect (SWI), which hold the potential to further revolutionize interconnects by using surface waves for ultra-fast, low-power wireless communication, thus enabling even denser, more integrated systems. These technologies are reshaping the SoC design paradigms, opening the door for a new era of compact, potent electronic devices capable of satisfying the ever-growing processing and connectivity demands of the digital age.

#### 1.2.2 Topologies

#### 1.2.2.1 2D Topologies

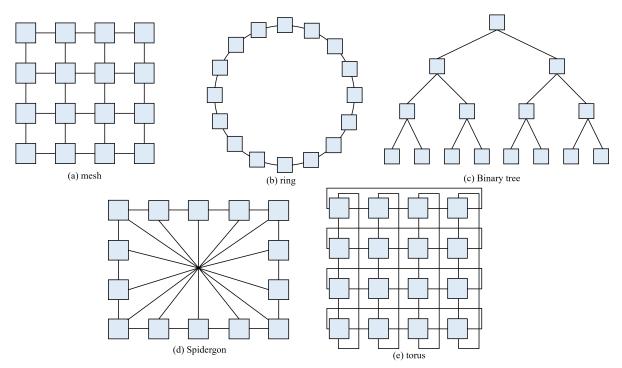

The study of network topologies within NoCs is an essential aspect, as it affects communication efficiency and the optimization of the overall SoC performance. Careful topology selection has a direct influence on the scalability, latency, and power consumption, which is necessary to meet the needs of today's sophisticated applications. Generally, the topology of NoC determines how to manage the physical layout and the network connections. Two categories of topologies have been defined, direct and indirect topologies [CML12]. In indirect topology, not all routers are associated with an IP, in which some of them are only responsible for forwarding packets within the network. By specializing routers in an indirect topology, more advanced NoCs can be constructed, allowing for precise control over traffic management to reduce bottlenecks and enhance overall system performance. In contrast, in direct topology (such as mesh, ring, binary tree, etc.), every router is connected to an IP. Such a pair (IP, router) is called a node. Figure 1.2 illustrates some examples of direct topologies:

Figure 1.2: Different NoC direct topologies.

• Mesh [Kum+02]: The mesh topology is defined by the dimensions n and m  $(n \times n)$

m), which determine the number of nodes in each row and column, respectively. Figure 1.2-a shows an example of a  $4 \times 4$  mesh with n = 4 and m = 4 and 16 cores in total. Furthermore, all IP are connected to a router, which in turn is connected to 2, 3, or 4 adjacent routers. Each router is equipped with a maximum of five ports (for Electrical Network-on-Chips (ENoCs)), one connected to an IP and the rest linked to up to four neighboring routers if they exist. The communication pathways used to establish a connection between two neighboring routers, or between a single router and an IP, comprise two unidirectional links that run in opposite directions. The mesh topology offers a simple, regular and scalable structure with redundant communication paths. However, it suffers from potentially higher communication latency between remote nodes and increased routing complexity with network size.

- **Ring** [CGL11]: As represented in Figure 1.2-b, all nodes are connected in a ring with each node maintaining connections with two neighboring nodes, regardless of the size of the ring. The greatest distance between any pair of adjacent nodes increases proportionally to the number of nodes. Although ring topology offers predictable latency with a simple structure, it remains sensitive to failures with a limited ability to handle heavy traffic loads.

- Binary tree [DYN03]: It comprises a specific arrangement of routers or nodes that are connected to one another in a structure similar to that of a tree, with the exception of the root node. Each node is connected to one parent and zero, one, or two child nodes. We refer to a tree as balanced when each leaf node is equally spaced from the root, indicating that all tree branches are of equal lengths. As shown in Figure 1.2-c, each parent node is connected to two child nodes, with a total of 15 nodes in the architecture. The binary tree topology provides a structured hierarchy and modular expansion. Nevertheless, it suffers from an increased potential latency for inter-tree communications and susceptibility to failures in high-level nodes.

- Spidergon [Cop+04]: In a Spidergon, the nodes are connected in a ring with each node being connected to the node on the opposite side of the ring, as illustrated in Figure 1.2-d. Spidergon topology affords a better latency and power consumption than other topologies for medium-sized networks, however, the increasing complexity and potentially higher interconnection costs for very large networks are still considered as disadvantages for such topology.

• Torus [Pan+05]: As presented in Figure 1.2-e, a  $n \times m$  torus configuration is derived from a mesh topology  $n \times m$  by incorporating a wraparound channel on every row and column. The inclusion of these wraparound channels helps to decrease both the diameter and the average distance across the router. As a result, each router is equipped with 5 ports, linked to 5 routers. The advantage of such topology includes their flexibility and redundancy with multiple paths between nodes, facilitating fault tolerance and better performance. On the other hand, their drawbacks include the higher interconnection complexity and potentially increased routing cost.

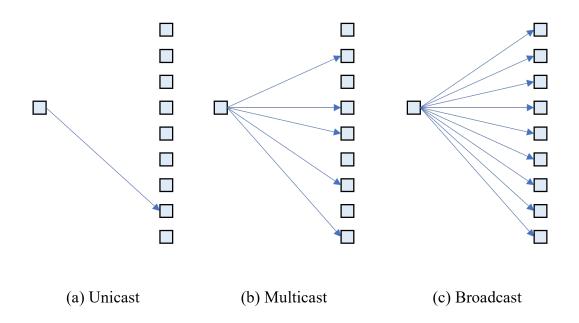

Figure 1.3: Unicast, multicast and broadcast communication.

One of the most commonly used topologies for NoCs is the mesh topology that is adopted in this thesis (Figure 1.2-a). Whatever the topology used, it is necessary to improve the performance of NoC by proposing interconnection architectures that facilitate collective communications. For example, **unicast** communication enables the packet transmission from a one source to one destination. Additionally, the **multicast** communication, enables transmission from one source to M destinations and is ideal for applications such as cache synchronization or instruction distribution. **Broadcast** communication, on the other hand, enables transmission from one source to all destinations, and is crucial for operations such as service announcements or global configuration updates.

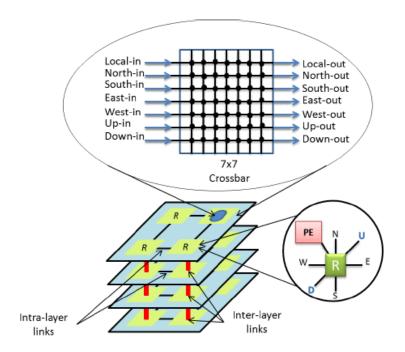

#### 1.2.2.2 3D Topology

Having explored two-dimensional NoC topologies, it is important to note that another dimension can be added, for even greater efficiency, resulting in the revolutionary emergence of what are known as 3D NoCs [PF07]. As shown in Figure 1.4, the 3D topology enables connections not only horizontally and vertically (intra-layer links) on a single plane but also across different layers of a stacked chip (inter-layer links). By stacking the integrated circuits within multiple layers, 3D NoCs exploit vertically to increase the connection density and decrease the distance that should be traversed by the signal, thus, reducing the latency and potentially increasing the bandwidth, thereby, the overall system performance is improved [AAK10; BG20]. Therefore, 3D NoCs mark a substantial advancement in the field of electronic systems design. Additionally, this 3D architecture also offers a better thermal management and reduced power consumption, paving the way for more compact designs, which is particularly beneficial for mobile devices for instance as well as for applications that require a high computing power in a small space.

Figure 1.4: 3D OASIS-NoC  $2 \times 2 \times 4$  mesh topology [AAK10].

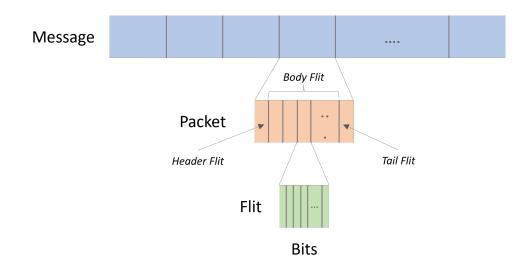

## **1.2.3** Data transfer format

In NoCs, a message, which is a complete unit of information, is transmitted from one point to another. It includes complex data types such as files, images or texts and often divided into several smaller packets to facilitate transmission [ZWG13]. Each packet contains a part of the message, as well as some additional information, such as the source and destination addresses and error-checking information. A packet is further divided into smaller units called flits (Flow Control Digit). The flit is the basic transfer unit in a NoC and corresponds to the width of the interconnection between the routers. A packet typically consists of a head flit, which often contains routing information, as well as information about the number of flits included in the packet, and a body flit carrying the actual packet data. Including a tail flit adds an additional flit to the packet to terminate it. It should be noted that the number of flits can vary within a packet, including in rare cases flits of uniform size.

Figure 1.5: Data transmission hierarchical: Bits, Flits, Packets and Messages.

This process of dividing messages into packets and flits enables more efficient use of the network. It also allows better control of traffic, as packets can be routed individually, and transmission can be controlled at flit level [Lee+13].

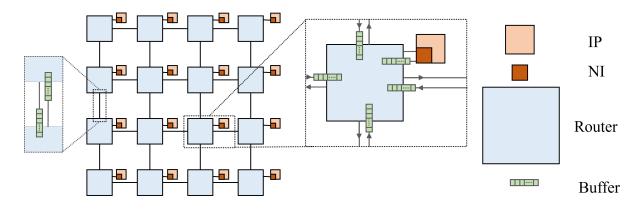

## **1.2.4** Components

After discussing how messages are structured and organized efficiently, it is important to identify the individual components of a NoC to better understand how these messages are processed and routed. The components of a NoC are the fundamental elements that define its efficiency and reliability. In order to ensure optimal communication between the cores of a SoC and that the network can effectively handle the high processing demands of contemporary IT systems, careful design of these components is imperative.

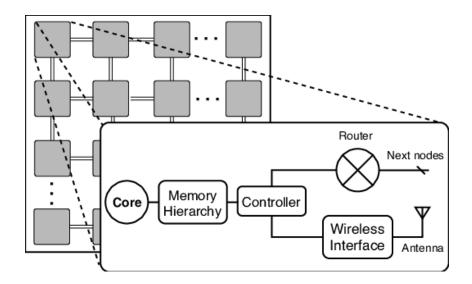

Figure 1.6: An example of a NoC-based many-core on-chip system.

Figure 1.6 shows a general example of a NoC-based many-core on-chip system. Generally, routers, links and Network Interface (NI) are the three essential components that form NoCs [DYN03], especially in a basic electrical NoC. The **Router** is an important component of a NoC that is responsible of routing data packets. Typically, it comprises input and output ports, **buffers** for holding incoming packets, and a switching unit. The role of the switching unit is to transmit packets according to the implemented routing algorithms (discussed in Section 1.2.5).

Initially, there is only one channel per port with virtual channels which are defined to share physical router resources and increase throughput, allowing logical separation of data streams to reduce congestion and improve overall performance [BV15]. The **NI** on the other hand, establish logical connections between the network and the IP that is interconnected with the router through electrical links. The actual set of routing paths is decided by the routing algorithm and will be detailed in the following section.

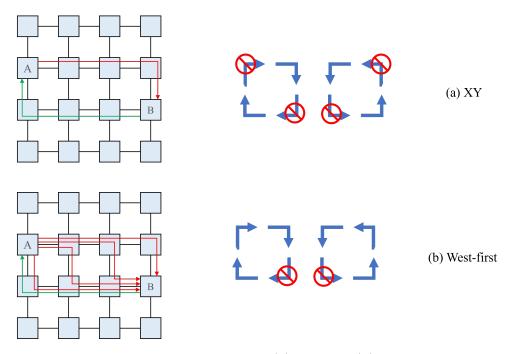

## 1.2.5 Routing algorithm

The path a packet takes to reach its destination is determined by the routing algorithm which indicates the next channel to be used at each intermediate node. The channel though can be chosen from several options. Nonetheless, the packet will be blocked and will not progress if all candidate channels are full.

Moreover, the routing algorithm can also impact the connectivity, which indicates the ability to route packets from any source node to any destination node. Similarly, adaptivity, which is the ability to select a different path for routing packets when there is contention or faulty components, is also a key feature determined by the routing algorithm used [Mer+22].

Furthermore, the routing algorithm has a vital role in ensuring deadlock and livelock freedom, i.e., guaranteeing that packets will not end up in an indefinite blockage or constantly drift within the network without reaching their destination.

Figure 1.7: Example of routing algorithms: (a) XY and (b) West-first routing algorithm.

Depending on their level of adaptability, routing algorithms can be classified into different categories. For example, deterministic routing, such as XY routing [CGP12], as shown in Figure 1.7 (a), always follows a predefined path and is totally deterministic when the number of turns is restricted to four, but for one communication, just one turn, offering a single possible path for a packet from source A to destination B and vice versa. Other methods, such as "West first" routing (Figure 1.7 (b)), allows all possible shortest paths when a packet travels east (from source A to destination B), but only allows one path when it travels west (from source B to destination A), requiring the west direction to be taken first if necessary. Other variants of this approach include the "North first", "South first", and "East first" methods [TSJ].

For adaptive routing methods, designed to avoid congested network paths, additional knowledge of the network is required. These routing algorithms naturally require more work to develop and therefore cost more in terms of space, cost, and power. Consequently, it is necessary to consider the appropriate Quality of Service Quality-of-Service (QoS) parameter before resorting to these techniques [AS09].

## **1.2.6** Flow control methods and arbitration

The routing of packets is allowed and stopped by the flow control mechanism. When a packet is blocked, buffer space is needed to store it. Additionally, packet transmission is halted by the flow control mechanism when there is no more buffer space available. It resumes when the packet is routed and there is space in the buffer. Furthermore, the packet may be dropped or rerouted through another channel if there is no flow control and no additional buffer space available.

Furthermore, flow control regulates the sequence of data from its source to its destination in the path. Its primary function is resource (like channels, bandwidth, and buffers) allocation and conflicts resolution for these resources. By minimizing waiting times for shared resources, effective flow control increases network packet speed and decreases problems such as deadlocks. Wormhole flow control is the most widely used, as it provides better buffer utilization and lower latency. In terms of virtual channels, using the same physical channel allows the use of idle bandwidth (the available transmission capacity on the network that is not actively carrying packets or data transfers) [MMH21].

In the literature, different flow control methods have been proposed and are summarized in Table 1.1 along with their advantages. These methods include Clumsy FC, Prediction Based FC, Distributed Buffer FC, Improved FC, Injection Level FC, Pile Level FC, QHT FC, and Fault Tolerant FC. Several criteria are examined, such as area reduction, cost reduction, design complexity, increased packet injection rate, latency reduction, throughput increase, power consumption reduction, congestion control, fault tolerance and buffer utilization. For each criterion, some techniques show benefits, indicated by a " $\checkmark$ ", while others do not, as shown by a "-". Therefore, the table provides a valuable

|                                   | Clumsy FC    | Prediction<br>Based FC | Distributed<br>Flit Buffer<br>FC | -            | Injection<br>Level<br>FC | Flit<br>Level<br>FC | QLT FC       | Fault Tol-<br>erant FC |

|-----------------------------------|--------------|------------------------|----------------------------------|--------------|--------------------------|---------------------|--------------|------------------------|

| Reduced<br>Area                   | -            | -                      | $\checkmark$                     | -            | -                        | -                   | $\checkmark$ | $\checkmark$           |

| Reduced<br>Cost                   | -            | -                      | -                                | -            | $\checkmark$             | -                   | $\checkmark$ | -                      |

| Reduced<br>Design Com-<br>plexity | -            | -                      |                                  | -            | -                        | -                   | -            | -                      |

| Reduced La-<br>tency              | -            | $\checkmark$           | $\checkmark$                     | -            | $\checkmark$             | $\checkmark$        | -            | -                      |

| Increased<br>Throughput           | $\checkmark$ | -                      | -                                | -            | -                        | $\checkmark$        | -            | -                      |

| Reduced<br>Power                  | -            | -                      | -                                | -            | $\checkmark$             | -                   | $\checkmark$ | $\checkmark$           |

| Congestion<br>Control             | -            | $\checkmark$           | -                                | -            | $\checkmark$             | -                   | -            | -                      |

| Fault Toler-<br>ance              | -            | -                      | $\checkmark$                     | $\checkmark$ | -                        | -                   | $\checkmark$ | $\checkmark$           |

| Better<br>Buffer Uti-<br>lization | -            | ~                      | -                                | -            | -                        | ~                   |              | -                      |

Table 1.1: Advantages of Different Flow Control Techniques [MMH21].

overview of the relative strengths of each technique with respect to the various criteria evaluated.

Arbitration, on the other hand, determines the access priority when multiple cores attempt to simultaneously access a shared resource router in the NoC. There exist many different arbitration processes [AS09]. For example, Round Robin arbitration offers a high level of fairness between cores by equally treating each port of entry. This ensures a fair distribution of the schedules. In this way, each input port is offered the same opportunity to access the output port, thus solving the starvation problem [LJL13]. First Come, First Serve (FCFS) is another arbitration in which the first packet that arrives is the first to be processed. This is the simplest of the scheduling algorithms. Additionally, the **Fixed Priority** arbitration assigns priorities to each packet. Packets with higher priority are processed before those of lower priority [Jai+15]. This arbitration technique is simple to use, but the critical path delay increases with the number of inputs. It also unfairly favors a single input port, leading to problems of low utilization for the other ports [Bec+12]. Other arbitration techniques that include, for instance, the **Dynamic** Adaptive Arbiter, where the buffer status can dynamically change the priority of the input port, and the **Ring Arbiters**, where the signal is generated by a token, are discussed and detailed in [Jia+13].

## 1.2.7 Pros and Cons of classical Electrical NoCs

The integration of thousands of heterogeneous cores and huge parallel computation capabilities suitable for High Performance Computing (HPC) [Viv21] are allowed. These parallelism capabilities obviously generate an enormous amount of data exchanges, making the communication medium a key element in overall system performance.

The evolution from dedicated wires and buses to NoC architectures in multi-core systems has been mainly driven by the need for efficient and scalable communication schemes. One of the key advantages of conventional electrical NoCs is their predictability. They can be designed to guarantee certain levels of performance, particularly when using deterministic routing algorithms. In addition, they offer a modular design, enabling designers to reproduce tiles (consisting of a processing element and a router) on the chip, thus simplifying design scalability. This modularity also facilitates the streamlining of the design and verification processes. Moreover, electrical NoCs effectively manage the complexity of on-chip communications, enabling power, latency, and bandwidth to be optimized according to the performance requirements of the applications and systems. Furthermore, the adaptability of its design allows different topologies to be implemented according to the particular requirements of SoC. In addition, their cost-effectiveness and capacity to accommodate intricate communication protocols render them a dependable and reasonably priced option for the vast majority of modern IT applications.

On the other hand, although transistors have become smaller, links remain the same size, resulting in dis-proportionality between the cost of communications and that of computations. In addition, in an extended many-core system, long-distance communications require the passage through many nodes. This leads to a significant increase in the dynamic power consumption. Moreover, as interconnections get closer together in increasingly dense architectures, electromagnetic interference and cross-talk become significant problems. Due to these constraints, different alternatives have been explored by researchers, which has led to the development of emerging technologies which hold the potential to get around some of these issues and open the door for a new era of intra-chip communications. Theses technologies include for example optical or millimeter-wavebased NoCs and will be further detailed in the following section.

# 1.3 Emerging Technologies

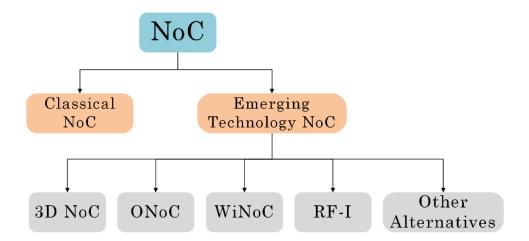

As the electronics industry continues to push the boundaries of miniaturization and efficiency, the design and innovation of on-chip interconnects becomes essential. In addition to the 3D technology discussed in Section 1.2, work has been done to implement emerging technologies in NoCs such as Optical Network-on-Chip (ONoC), WiNoC, RF-Interconnect and other alternatives (Figure 1.8). Table 1.3 summarizes a comparison among the WiNoC, 3D-NoC and photonic NoC [WJ14]. These innovations have led to the implementation of hybrid NoC technologies that use wireless and waveguide technologies with traditional ENoC. In our work, we have focused primarily on these emerging technologies and hybrid NoCs. These technological advances promise to bring significant improvements in speed, efficiency and flexibility for future systems.

Figure 1.8: Technology based classification NoC [BBB17].

Since many years ago, traditional NoCs have served as the basis of intra-chip communications, allowing for effective integration and communication between the many components on a chip. Like any system, they are not without limitations. It is important to evaluate the advantages and disadvantages of traditional electrical NoCs given the emergence of new technologies and the increasing expectations for performance and efficiency. Likewise, it is crucial to look at emerging technologies aiming to overcome the challenges posed by traditional solutions.

## **1.3.1** Optical Networks on Chip

Integration of optical links into circuits based on Silicon Photonics (SiP) is considered as a major solution to address the bandwidth and energy limitations of electrical interconnections, giving rise to Optical Networks on Chip (ONoCs) [WNL17]. However, the development of SiP devices and the management of on-chip optical data transmission present many challenges and requiring a thorough understanding of the traffic requirements and constraints associated with integrating both electronic and photonic devices. In this regard, our Lab has carried out research pioneering the Architectural exploration of network interface for energy efficient 3D optical network-on-chip [Pha18; Luo18].

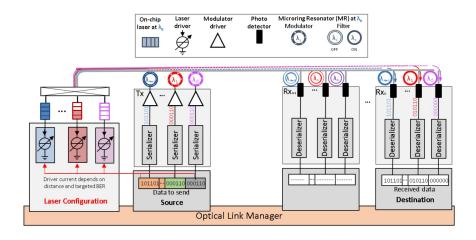

Figure 1.9: Nanophotonic interconnect NoC Optical (ONoC) [Lee22].

Figure 1.9 details an ONoC architecture, displaying photonic devices such as waveguides, multi-wavelength lasers, and microring resonators (MRRs) used as modulators and photo detectors. Light signals generated by the laser sources are modulated using wavelength-specific microring modulators with on-off keying (OOK) modulation, thus, converting parallel bit electrical signals into serialized sequences. These signals, possibly modulated into multiple wavelengths to accelerate transfer, traverse a shared waveguide with wavelength-division-multiplexing (WDM), facilitating parallel signal transmission. At the destination, the signals are filtered by microring filters, directing specific wavelengths to photo-detectors. These photo-detectors can convert them back into electrical signals for the respective chip nodes. Each ONoC node communicates with many others via the Signal Writer and Multiple Reader (SWMR) model, using WDM-enabled waveguides.

## 1.3.2 **RF-Interconnect NoC**

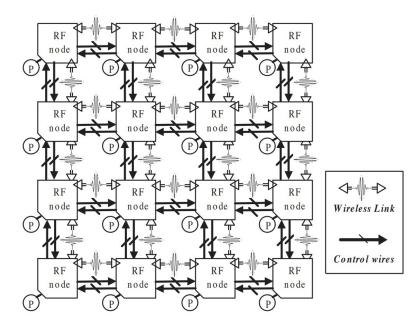

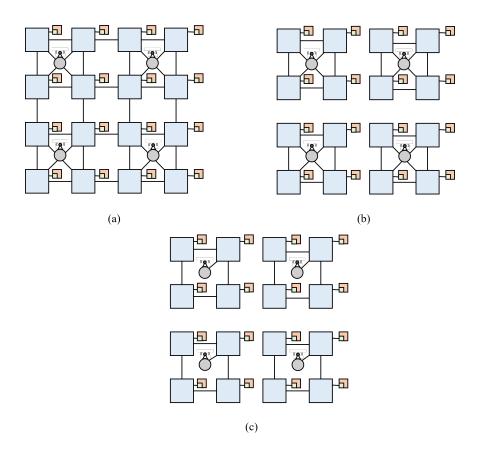

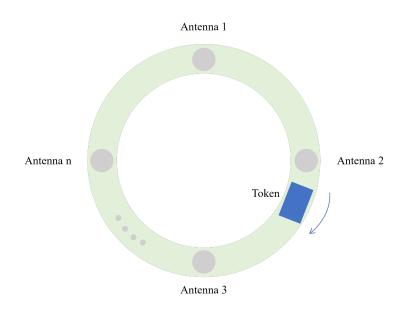

Transmission delays, power-hungry routers, and the less importance of scalability, all make switched networks-on-chip less attractive. An alternative is to use high-quality transmission lines. For medium-scale multi-core processors (CMPs), the interconnection infrastructure can eliminate the need for packet switching and offer energy and performance advantages over conventional mesh interconnections. A possible NoC strategy is represented by RF-Interconnects, which use radio frequency signals to connect SoC cores. With greater bandwidth and less power consumption than electrical NoCs, this new technology seeks to overcome their drawbacks without the physical limitations of wired interconnects.