## Hardware security for just-in-time compilation in language virtual machines

Quentin Ducasse

### ▶ To cite this version:

Quentin Ducasse. Hardware security for just-in-time compilation in language virtual machines. Computer science. ENSTA Bretagne - École nationale supérieure de techniques avancées Bretagne, 2024. English. NNT: 2024ENTA0003. tel-04690882

### HAL Id: tel-04690882 https://theses.hal.science/tel-04690882v1

Submitted on 6 Sep 2024

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

| COLLEGES | SCIENCES         |

|----------|------------------|

| BRETAGNE | POUR L'INGENIEUR |

| LOIRE    | ET LE NUMERIQUE  |

# THÈSE DE DOCTORAT DE

### L'ÉCOLE NATIONALE SUPÉRIEURE DE TECHNIQUES AVANCÉES BRETAGNE

ÉCOLE DOCTORALE Nº 648 Sciences pour l'Ingénieur et le Numérique Spécialité : STIC - Informatique

## Par Quentin DUCASSE

Sécurisation matérielle de la compilation à la volée des machines virtuelles langage

Thèse présentée et soutenue à Brest, le vendredi 29 mars 2024 Unité de recherche : Lab-STICC, équipe ARCAD

#### Rapporteurs avant soutenance :

Sébastien PILLEMENTProfesseur - Université de NantesLaure GONNORDProfesseure - Grenoble INP / Esisar

#### Composition du Jury :

| Président :             | Ludovic MÉ    | Professeur - INRIA                    |

|-------------------------|---------------|---------------------------------------|

| Examinateurs :          | Gaël THOMAS   | Télécom SudParis                      |

|                         | Zoé DREY      | Ingénieure                            |

| Dir. de thèse :         | Loïc LAGADEC  | Professeur - ENSTA Bretagne           |

| Co-encadrant de thèse : | Pascal COTRET | Enseignant-chercheur - ENSTA Bretagne |

#### Invité :

Guillermo POLITO Chargé de recherche - INRIA Lille

## REMERCIEMENTS

Je tiens tout d'abord à remercier mon encadrant, Pascal Cotret, pour le soutien qu'il a pu m'apporter ainsi que les connaissances qu'il m'a transmises durant la réalisation de ces travaux. Je tiens également à remercier mon directeur de thèse, Loïc Lagadec, pour les conseils avisés qu'il m'a prodigués tant dans la direction des travaux de recherche que dans la qualité de ses remarques. Je leur suis extrêmement reconnaissant de la confiance qu'ils m'ont accordée, laquelle m'a permis de m'épanouir scientifiquement à leurs côtés.

J'adresse toute ma reconnaissance à Sébastien Pillement et Laure Gonnord qui m'ont fait l'honneur d'accepter d'évaluer mes travaux en tant que rapporteurs. Je remercie également Ludovic Mé, Gaël Thomas et Zoé Drey d'avoir accepté de faire partie du jury d'évaluation. Je souhaite ensuite remercier Erven Rohou et Lilian Bossuet d'avoir participé à mon comité de suivi de thèse et pour leurs conseils.

Je remercie également Guillermo Polito et Pablo Tesone pour m'avoir accueilli et épaulé pendant mon échange au sein de l'équipe RMoD. Je les remercie pour le soutien qu'ils m'ont apporté ainsi que la qualité de nos échanges techniques et scientifiques.

Je suis également reconnaissant d'avoir pu travailler au sein de l'ENSTA Bretagne où j'ai eu la chance de côtoyer et travailler avec des collègues et amis qui m'ont soutenu et accompagné dans mes activités d'enseignement et de recherche.

Enfin, je remercie chaleureusement mes proches, mes amis et ma famille pour leur soutien permanent et leur confiance au long de ces années où j'ai pu être moins disponible pour eux. Je remercie particulièrement mes parents pour leur enthousiasme communicatif ainsi qu'Armelle Gillot pour son soutien constant et sa bienveillance.

# STRUCTURE

### Note sur la structure de la thèse

Cette thèse est écrite en anglais pour ses chapitres principaux d'état de l'art, des contributions, ainsi que l'introduction et la conclusion. Un résumé en français reprenant les points principaux de chacun des chapitres est présenté en français après la table des matières. Un résumé plus court en français et en anglais se trouve en quatrième de couverture.

### Note on the thesis structure

This thesis is written in English for its main chapters of state-of-the-art, contributions, as well as the introduction and conclusion. A summary in French of the main points of each chapter is presented after the table of contents. A shorter summary in French and English can be found on the back cover.

| R        | ésum           | ié de la | a thèse                                           | 15 |

|----------|----------------|----------|---------------------------------------------------|----|

|          | Intr           | oductio  | n                                                 | 15 |

|          | État           | t de l'A | ${ m rt}$                                         | 17 |

|          | Gig            | ue : Un  | Générateur de Code JIT Instrumentable             | 19 |

|          |                |          | a : Sécurisation du Code JIT par les Instructions | 20 |

|          | Exte           | ension o | d'un Compilateur JIT sur RISC-V                   | 22 |

|          | Con            | clusion  | · · · · · · · · · · · · · · · · · · ·             | 23 |

| 1        | Intr           | roduct   |                                                   | 25 |

|          | 1.1            | Motiv    | ation $\ldots$                                    | 25 |

|          | 1.2            | Formu    | ulation of the Research Question                  | 27 |

|          | 1.3            |          | ibution                                           |    |

|          | 1.4            | Organ    | nization                                          | 30 |

|          |                |          |                                                   |    |

| Ι        | Ba             | ackgro   | ound & Related Works                              | 32 |

| <b>2</b> | $\mathbf{Rel}$ | ated V   | Vork: Language Virtual Machines Security          | 33 |

|          | 2.1            | Backg    | round: Language Virtual Machines                  | 33 |

|          |                | 2.1.1    | Interpretation                                    | 35 |

|          |                | 2.1.2    | Just-in-Time Compilation                          | 36 |

|          |                | 2.1.3    | Additional components                             | 37 |

|          | 2.2            | Virtua   | al Machine Attacks                                | 38 |

|          |                | 2.2.1    | Context and Threat Model                          | 38 |

|          |                | 2.2.2    | JIT Code Injection Attacks                        | 39 |

|          |                | 2.2.3    | Code Reuse Attacks                                | 42 |

|          |                | 2.2.4    | Data-Only Attacks                                 | 45 |

|          | 2.3            | VMs (    | Countermeasures                                   | 48 |

|          |                | 2.3.1    | Diversification                                   | 48 |

|   |     | 2.3.2  | Memory Protection                     | 49        |

|---|-----|--------|---------------------------------------|-----------|

|   |     | 2.3.3  | Capability Containment                | 52        |

|   |     | 2.3.4  | Hardware-Enforced Isolation           | 56        |

|   | 2.4 | Summ   | ary                                   | 60        |

| 3 | Ope | en Har | dware-Accelerated Security Features   | <b>65</b> |

|   | 3.1 | Motiv  | $\operatorname{ation}$                | 65        |

|   | 3.2 | A Prin | mer on the RISC-V ISA                 | 67        |

|   |     | 3.2.1  | Modularity                            | 67        |

|   |     | 3.2.2  | Extensibility                         | 67        |

|   |     | 3.2.3  | Memory System                         | 68        |

|   |     | 3.2.4  | Open-source Processor Implementations | 70        |

|   | 3.3 | Portal | pility of known attacks to RISC-V     | 71        |

|   | 3.4 | Hardw  | vare Run-time Protections             | 72        |

|   |     | 3.4.1  | Hardware Control-Flow Integrity       | 73        |

|   |     | 3.4.2  | Memory Tagging and Pointer Extension  | 75        |

|   |     | 3.4.3  | Domain Isolation                      | . 77      |

|   | 3.5 | Summ   | ary                                   | . 79      |

|   |     |        |                                       |           |

## II Contributions

| 4 | $\operatorname{Gig}$ | ue: JI | $\Gamma$ Code Snapshot Generation for Hardware Testing                                              | 83 |

|---|----------------------|--------|-----------------------------------------------------------------------------------------------------|----|

|   | 4.1                  | Motiva | ation                                                                                               | 83 |

|   |                      | 4.1.1  | Technology Stack                                                                                    | 83 |

|   |                      | 4.1.2  | Existing Development Tools                                                                          | 84 |

|   |                      | 4.1.3  | Custom Instruction Examples $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 85 |

|   | 4.2                  | Gigue: | Design                                                                                              | 86 |

|   |                      | 4.2.1  | Binary Structure and Execution                                                                      | 87 |

|   |                      | 4.2.2  | Parametrization                                                                                     | 89 |

|   |                      | 4.2.3  | Code Generation                                                                                     | 90 |

|   |                      | 4.2.4  | Modularity and Extensions                                                                           | 92 |

|   |                      | 4.2.5  | Test framework                                                                                      | 93 |

|   | 4.3                  | Workle | Dad Qualification                                                                                   | 94 |

|   |                      | 4.3.1  | VM Qualification                                                                                    | 94 |

81

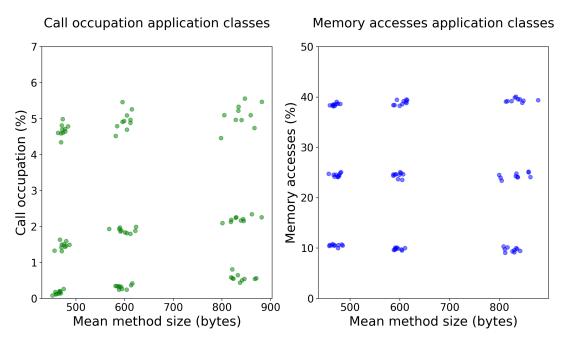

|          |     | 4.3.2  | Application Class Qualification                     | . 95  |

|----------|-----|--------|-----------------------------------------------------|-------|

|          |     | 4.3.3  | Summary                                             | . 97  |

|          | 4.4 | Use Ca | ase                                                 | . 98  |

|          |     | 4.4.1  | Workload Generation                                 | . 98  |

|          |     | 4.4.2  | Experimental Setup                                  | . 99  |

|          | 4.5 | Summ   | ary                                                 | . 101 |

| <b>5</b> | JIT | Domai  | in: Instruction-level security for the JIT compiler | 103   |

|          | 5.1 | Threat | t Model $\ldots$                                    | . 103 |

|          | 5.2 | Softwa | are Execution Model                                 | . 104 |

|          |     | 5.2.1  | Instruction-Level Domain Isolation                  | . 104 |

|          |     | 5.2.2  | Memory Model                                        | . 105 |

|          |     | 5.2.3  | Call Stack Separation                               | . 105 |

|          |     | 5.2.4  | Data Access Control                                 | . 107 |

|          |     | 5.2.5  | System Call Filtering                               | . 108 |

|          | 5.3 | Hardw  | vare Extension Design                               | . 108 |

|          |     | 5.3.1  | Instruction Tagging                                 | . 109 |

|          |     | 5.3.2  | Control and Status Registers                        | . 111 |

|          |     | 5.3.3  | Domain Check: Code Domain                           | . 112 |

|          |     | 5.3.4  | Domain Check: Data Domain                           | . 113 |

|          |     | 5.3.5  | Domain Check: Fetch Domain                          | . 114 |

|          | 5.4 | Evalua | ation                                               | . 116 |

|          |     | 5.4.1  | Functional Verification                             | . 116 |

|          |     | 5.4.2  | Experimental Setup                                  | . 117 |

|          |     | 5.4.3  | Experimental Results                                | . 118 |

|          | 5.5 | Summ   | ary                                                 | . 121 |

| 6        | JIT | Comp   | oiler Extension to RISC-V                           | 123   |

|          | 6.1 | The P  | haro Virtual Machine                                | . 123 |

|          |     | 6.1.1  | VM Compilation                                      | . 124 |

|          |     | 6.1.2  | VM Runtime                                          | . 125 |

|          |     | 6.1.3  | VM development process                              | . 127 |

|          | 6.2 | Cogit  | RISC-V Backend Port                                 | . 128 |

|          |     | 6.2.1  | RISC-V Design Choices                               | . 128 |

|          |     | 6.2.2  | CogRTL and RISC-V                                   | . 130 |

|    | 6.3   | Tooling  | Extension                                                                                                                                                      | . 133 |

|----|-------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

|    |       | 6.3.1 (  | $Choice of the simulator \ldots \ldots$ | . 133 |

|    |       | 6.3.2    | Test harness extension                                                                                                                                         | . 134 |

|    |       | 6.3.3 I  | Machine code debugger                                                                                                                                          | . 134 |

|    |       | 6.3.4    | Custom Instructions                                                                                                                                            | . 135 |

|    | 6.4   | Validati | on & Evaluation                                                                                                                                                | . 137 |

|    | 6.5   | Summar   | ry                                                                                                                                                             | . 138 |

|    | 6.6   | Next St  | eps                                                                                                                                                            | . 139 |

| 7  | Con   | clusion  | and Future Works                                                                                                                                               | 141   |

|    | 7.1   | Summar   | ry of Contributions                                                                                                                                            | . 141 |

|    | 7.2   | Limitati | $\operatorname{ions}$                                                                                                                                          | . 143 |

|    | 7.3   | Future V | Works                                                                                                                                                          | . 144 |

|    |       | 7.3.1 (  | Gigue and Hardware Development                                                                                                                                 | . 145 |

|    |       | 7.3.2    | JIT-Specific Custom Instructions                                                                                                                               | . 147 |

|    | 7.4   | Final R  | emarks                                                                                                                                                         |       |

|    |       |          |                                                                                                                                                                |       |

| Α  | Add   | ress (R  | e)Randomization                                                                                                                                                | 150   |

| В  | San   | dboxing  |                                                                                                                                                                | 153   |

| Bi | bliog | raphy    |                                                                                                                                                                | 155   |

# LIST OF TABLES

| 2.1 | Summary of VM Attacks and Defenses                                    | 62  |

|-----|-----------------------------------------------------------------------|-----|

| 4.1 | Gigue Characterization Parameters                                     | 89  |

| 4.2 | Pharo VM Inline Caches Usage                                          | 95  |

| 4.3 | Pharo VM JIT Code Region                                              | 96  |

| 4.4 | Instruction Range and Distribution among Benchmark Execution Traces . | 96  |

| 5.1 | Intruction Domain Tagging                                             | .10 |

| 5.2 | JITDomain Validation Tests                                            | .16 |

| 5.3 | JITDomain Performance Overhead (Call Applications)                    | .19 |

| 5.4 | JITDomain Performance Overhead (Memory Applications)                  | .19 |

| 5.5 | JITDomain Resource Utilization                                        | .20 |

| 6.1 | Cogit Micro-benchmarks and Speedup                                    | .37 |

| 6.2 | Cogit JIT Code Comparison                                             | .38 |

# LIST OF FIGURES

| 1    | Modèle mémoire de la séparation des domaines                        |

|------|---------------------------------------------------------------------|

| 2.1  | Virtual Machines Taxonomy                                           |

| 2.2  | Virtual Machine Overview                                            |

| 2.3  | JIT Spraying Example                                                |

| 2.4  | Code Injection Attacks Against VMs 42                               |

| 2.5  | Code Reuse (ROP) Attacks against VMs                                |

| 2.6  | Shellcode Examples for Executable Memory Allocation                 |

| 2.7  | Data-only Attacks against VMs                                       |

| 2.8  | Control-Flow Integrity for VMs                                      |

| 2.9  | JITGuard and SGX Isolation for VMs                                  |

| 2.10 | MPK Isolation for VMs                                               |

| 3.1  | Control Status Registers of the Physical Memory Protection Unit 69  |

| 3.2  | Physical Memory Protection Matching Logic                           |

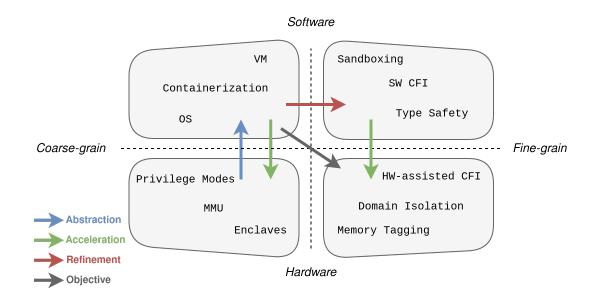

| 3.3  | Run-time Protections and their Coarseness                           |

| 3.4  | Hardware-enforced Control-Flow Integrity                            |

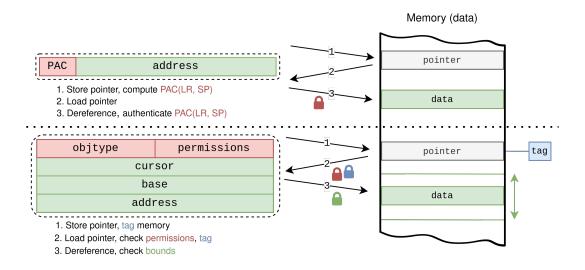

| 3.5  | Memory Tagging and Pointer Extensions                               |

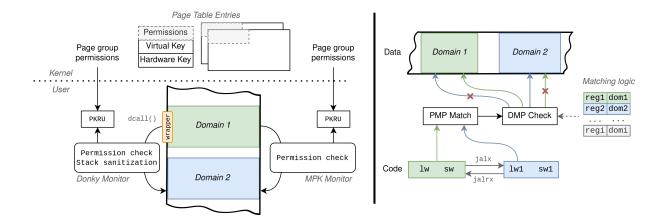

| 3.6  | Hardware Domain Isolation                                           |

| 3.7  | Links between Requirements, Research Questions and Contributions 80 |

| 4.1  | Technical Stack and Custom Instructions                             |

| 4.2  | Gigue Binary Structure and Execution                                |

| 4.3  | Gigue Test Framework Handler for a Shadow Stack Solution 93         |

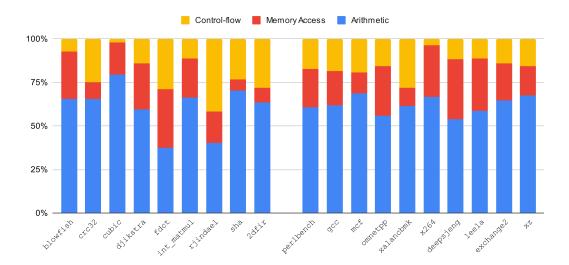

| 4.4  | Instruction Distribution of BEEBS and SPEC CPU-2017                 |

| 4.5  | Application classes generation                                      |

| 4.6  | Gigue Environment Setup                                             |

| 4.7  | Gigue Workload Execution on CVA6 and Rocket                         |

| 5.1  | JITDomain Memory Model                                              |

| 5.2  | Code Example for Call Stack Separation                              |

| 5.3  | Code Example for Data Access Control and Domain Changes 107                                                                                                          |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.4  | CVA6 Pipeline Overview                                                                                                                                               |

| 5.5  | Instructions and their domain $\ldots \ldots \ldots$ |

| 5.6  | Domain Configuration through CSRs                                                                                                                                    |

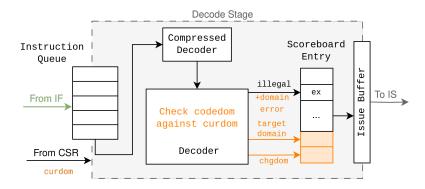

| 5.7  | JITDomain Code Domain Check                                                                                                                                          |

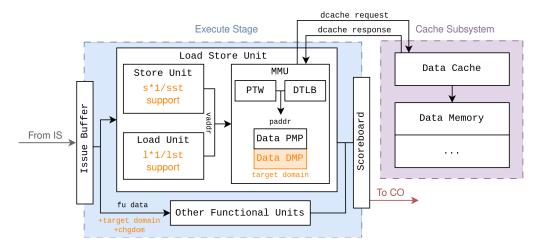

| 5.8  | JITDomain Data Access Domain Check                                                                                                                                   |

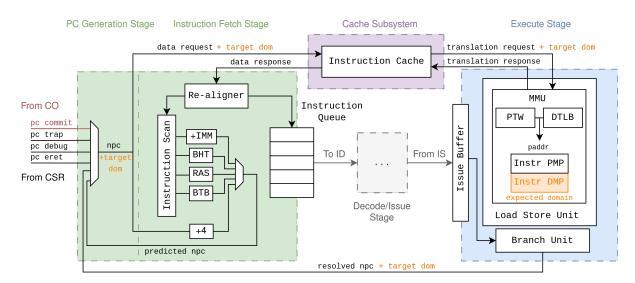

| 5.9  | JITDomain Instruction Fetch Domain Check                                                                                                                             |

| 5.10 | JITDomain Cycle and CPI Overhead (Call Applications)                                                                                                                 |

| 5.11 | JITDomain Cycle and CPI Overhead (Memory Applications) 120                                                                                                           |

| 6.1  | Compilation Process of the Pharo VM                                                                                                                                  |

| 6.2  | Pharo Source Code Compilation Steps                                                                                                                                  |

| 6.3  | Memory Layout of the Pharo VM Simulation Environment                                                                                                                 |

| 6.4  | RISC-V Instruction Types Encoding                                                                                                                                    |

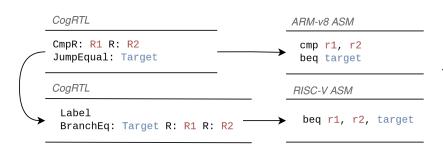

| 6.5  | CogRTL Conditional Jump for RISC-V                                                                                                                                   |

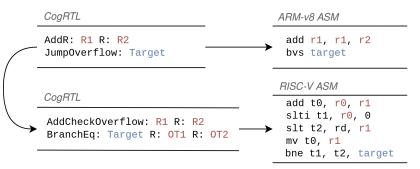

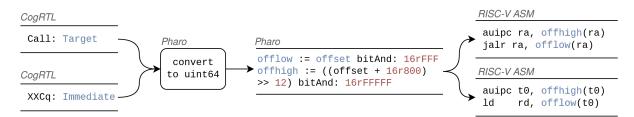

| 6.6  | CogRTL Overflow Check for RISC-V                                                                                                                                     |

| 6.7  | RISC-V Immediate Value Handling                                                                                                                                      |

| 6.8  | Pharo JIT Machine Code Debugger                                                                                                                                      |

| 7.1  | Axes of the Future Works                                                                                                                                             |

| B.1  | Sandboxing VMs                                                                                                                                                       |

### Introduction

Ces dernières décennies ont vu la sécurité d'un nombre croissant de systèmes d'information compromise, faisant fuiter les données personnelles et confidentielles de millions d'utilisateurs. En 2014, la vulnérabilité "Heartbleed" [1] affecte entre 24 et 55% des sites HTTPS les plus utilisés. Ce bug de la librairie de cryptographie OpenSSL [2], très largement distribuée, utilisait les données envoyées par un utilisateur sans vérification préalable, lui permettant d'exfiltrer des informations confidentielles stockées par le serveur. Pour garantir l'intégrité et la sécurité des données d'un utilisateur d'un système d'information, plusieurs solutions sont mises en place au niveau de l'architecture matérielle directement, du système d'exploitation (OS), ou à travers des environnements d'exécution dédiés.

Parmi ces environnements d'exécution, les machines virtuelles langage (VMs) supportent l'exécution d'un langage de programmation en faisant abstraction du processus de compilation et d'allocation mémoire pour l'utilisateur. Elles permettent la portabilité directe du code applicatif sur les architectures supportées par la VM. Java ou Python utilisent chacun une VM pour leur exécution. Ce sont des logiciels complexes qui gèrent à la fois la compilation du langage source, son optimisation, et l'utilisation de la mémoire par l'application. Les caractéristiques de portabilité et de garanties d'exécution font des VMs et des langages qu'elles supportent des outils de développement intéressants. Des VMs sont déployées sur la majorité des systèmes d'information, à travers par exemple un navigateur web et sa VM JavaScript chargée d'exécuter sur l'ordinateur de l'utilisateur le code JavaScript fourni par un serveur dans une page web. Un autre exemple, l'Android Run Time (ART) permet l'exécution d'applications Android et est déployée sur tous les smartphones utilisant cet OS. Le déploiement et l'adoption globale de VMs sur une variété de systèmes d'information à usage du grand public, couplé à leur capacité à exécuter des tâches à criticité importante telles que la manipulation de la mémoire et la génération de code machine en font des cibles intéressantes pour un attaquant. En particulier, le composant chargé de la compilation à la volée ("just-in-time" ou JIT en anglais), est critique à la performance et manipule du code exécutable.

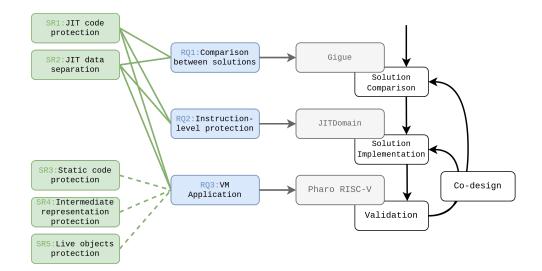

Nous nous intéressons dans le contexte de cette thèse à la mise en place de défenses autour des VMs, et en particulier à la sécurisation du code recompilé à la volée. Nous motivons aussi la pertinence de l'accélération matérielle de ces défenses dans un objectif de co-design applicatif/matériel. Nous présentons trois contributions principales :

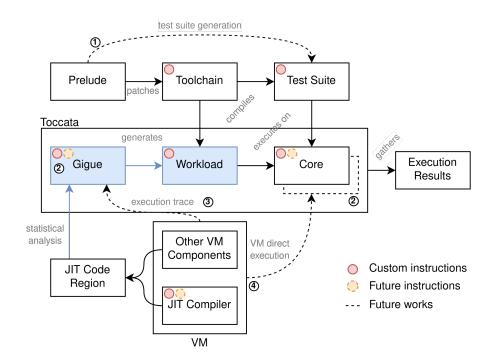

Un générateur de binaires instrumentés, Gigue. Il génère des exécutables ressemblant à des régions de code machine recompilé par la VM, selon des paramètres de caractérisation. Les binaires sont complétés par des instructions aléatoires selon la caractérisation, et instrumentables avec des instructions dédiées. Ils sont directement exécutables sur un processeur synthétisable ou son simulateur associé. Gigue permet la génération de binaires variés et d'un socle de comparaison de solutions de sécurité.

Une solution d'isolation par les instructions, JITDomain. Cette solution d'isolation définit des domaines à travers des instructions dédiées. La solution est appliquée au code machine recompilé par une VM. Elle permet la garantie d'aspects importants de sécurité à l'exécution comme la séparation de l'accès aux données, l'isolation de la pile d'appel et le filtrage des appels systèmes. La solution est déployée sur le processeur RISC-V open-source CVA6 [3] avec un coût minimal en ressources matérielles et performance du binaire instrumenté.

Le port d'un compilateur JIT sur RISC-V, Cogit le compilateur à la volée de la VM Pharo. Nous présentons le port des outils de développement et de tests utilisés par la VM Pharo sur l'architecture RISC-V. Le compilateur JIT utilise une représentation intermédiaire qui n'est pas directement interfaçable avec le jeu d'instruction RISC-V. Le port valide l'intégralité des tests unitaires mis en place par la VM Pharo et l'utilisation du compilateur JIT permet une accélération du nombre de bytecode et d'appels de fonction exécutés. Nous étendons les outils de simulation de la VM pour permettre l'exécution d'instructions personnalisées.

Nous présentons dans la suite de ce résumé une partie de l'état de l'art sur les attaques et défenses de VMs ainsi que la présentation de solutions de sécurité matérielle liées à l'isolation fine. Nous présentons ensuite un résumé de chacune des trois contributions, puis les perspectives qui résultent de ces travaux.

### État de l'Art

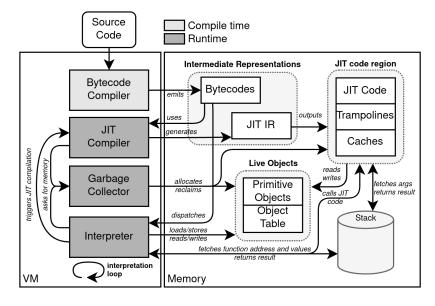

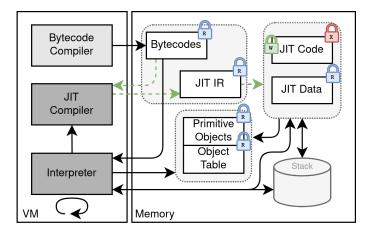

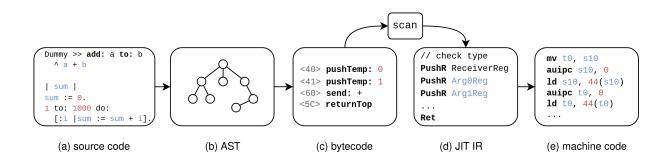

Les machines virtuelles langage (VMs) sont des environnements d'exécution complexes qui contiennent différents niveaux de compilation et d'exécution. Le code source est d'abord traduit sous forme d'un arbre de syntaxe abstraite (abstract syntax tree ou AST). Cet arbre est ensuite transformé en une autre représentation intermédiaire, propre à l'interprétation : le bytecode. L'interpréteur exécute la succession de bytecode directement, un à un via un "switch" sur toutes les instructions existantes. Ce processus amène à une exécution ralentie du code applicatif par rapport à du code directement compilé. Lorsqu'une suite de bytecode est souvent utilisée, la VM fait appel à un ou plusieurs compilateur(s) à la volée (ou "just-in-time" (JIT) en anglais) qui recompilent cette succession de bytecode en code machine directement. La granularité et la méthode de recompilation dépendent de la VM et de son implémentation. Une trace d'exécution ou une fonction fréquemment appelée peuvent être sélectionnés et recompilés. Enfin, ces composants qui contrôlent le flot d'exécution travaillent avec le ramasse-miettes (ou "garbage collector" (GC) en anglais) pour attribuer et récupérer de la mémoire. Plusieurs algorithmes et méthodes d'attribution et récupération de mémoire sont utilisés pour minimiser la latence et le temps passé à récupérer la mémoire inutilisée. Ces composants sont responsables de l'exécution et la gestion du code applicatif du langage qu'ils supportent.

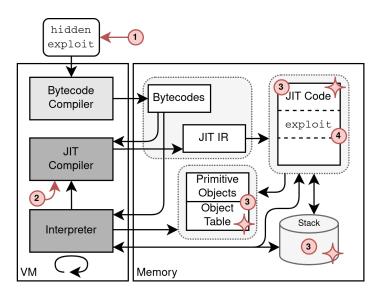

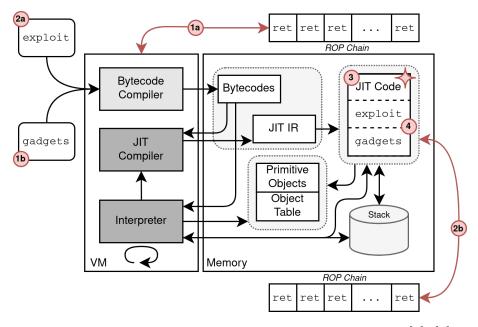

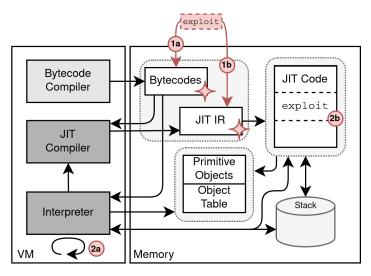

Dans l'ensemble, les attaques contre les VM se sont d'abord concentrées sur le compilateur JIT et la région de code JIT. Celle-ci nécessite un accès en écriture pour y placer le code machine ainsi qu'un accès en exécution pour rediriger le flot de contrôle vers la nouvelle version du code. Ces caractéristiques en ont fait un composant sensible à l'injection de code [4]. La zone de code JIT peut être utilisée pour mettre en défaut des mesures comme la distribution aléatoire de l'espace d'adressage (ou *ASLR* en anglais) en utilisant la prédictibilité de la génération du code. D'autres attaques se servent du compilateur JIT pour renforcer des attaques existantes de réutilisation de code [5], voire l'injection de code lui-même propice à la réutilisation de code [6]-[8]. La réutilisation de code se base sur la détection de "gadgets", des petites successions de code machines dédiées à une tâche particulière et dont l'enchaînement permet d'exécuter un code arbitraire. Enfin, les représentations intermédiaires que la VM utilise sont aussi des cibles potentielles d'injections malicieuses. C'est le cas pour le bytecode [9], instructions que l'interpréteur consomme, ou la représentation intermédiaire du compilateur JIT pour la recompilation [10]. Ces trois attaques se caractérisent en "code injection", "code reuse" et "data-only".

Au fur et à mesure de l'évolution de la sécurité des logiciels, les défenses autour des machines virtuelles se sont d'abord concentrées sur la perturbation du déterminisme introduit par le compilateur JIT. Des propriétés telles que la diversité et la randomisation jouent un rôle essentiel dans le renforcement de la sécurité du processus de compilation JIT, en particulier contre les simples attaques par injection [11]-[13]. Toutefois, ces mesures peuvent s'avérer inadéquates face à des menaces plus sophistiquées ou pour assurer des garanties plus fortes. Le contrôle des permissions de mémoire est une méthode simple pour se prémunir contre l'injection de code, en empêchant les attaquants d'écrire dans la mémoire exécutable [14], [15]. Étant donné que le compilateur JIT a explicitement besoin de mémoire exécutable, la double allocation d'une région mémoire avec des permissions différentes permet une séparation des accès [16], [17]. La réutilisation du code reste un problème, le code JIT exposant les gadgets disponibles aux attaquants. Deux mesures de protection consistent à supprimer la lisibilité du code JIT exécutable et à mettre en œuvre un mécanisme robuste d'intégrité du flot de contrôle [18], [19]. Une isolation restrictive à grain fin entre les composants offre la plus grande fiabilité à la VM, mais a un impact net sur les performances, impact amorti à travers une accélération matérielle [9], [10].

Les solutions d'isolation fine à l'exécution sont coûteuses lors de leur exécution complète du côté logiciel. Une proposition de primitives de sécurité supportées matériellement amortit ce coût en performance. Pour pouvoir expérimenter avec le design et l'implémentation de telles solutions, RISC-V [20] est un jeu d'instruction open-source, modulaire et qui permet l'ajout de nouvelles instructions dédiées. Les solutions d'isolation fines se séparent en trois catégories importantes. Tout d'abord, l'accélération de solutions d'intégrité de flot de contrôle. Intel supporte une pile d'appels dupliquée et séparée dans l'espace d'adressage avec CET [21, Vol.1 Ch.17]. Des solutions comparables sont disponibles sur RISC-V [22], [23] et proposent une vérification du flot de contrôle accélérée. Ensuite, le marquage et la séparation de la mémoire à travers l'extension des pointeurs, qu'ARM définit avec MTE [24] et PAC [25, Ch.B6]. RISC-V propose un équivalent sur les adresses de la pile d'appel [26] ou l'ajout de tags en mémoire [27]. Ces pointeurs peuvent être étendus avec de nombreuses métadonnées utilisées à l'exécution [28]-[30]. Enfin, l'isolation de domaines via un moniteur dédié et l'extension des pages de mémoire [31], [32] étend le principe des clés mémoire mis en place par Intel MPK [21, Vol.3 Sec.4.6]. Cette isolation peut aussi se mettre en place directement par l'attribution d'un domaine à une instruction spécifique [33], [34]. Ces solutions sont légères à la mise en place et accélérées matériellement pour garantir une isolation fine

### Gigue : Un Générateur de Code JIT Instrumentable

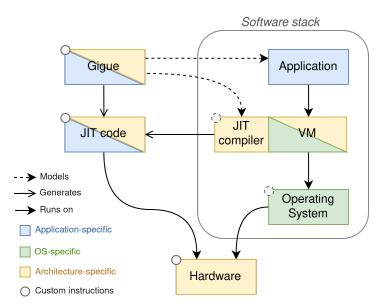

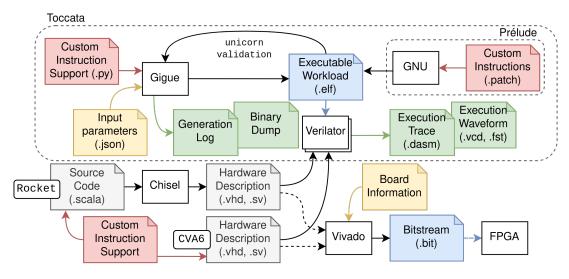

La comparaison de solutions d'isolation dédiées au code JIT nécessite un changement à trois niveaux applicatifs : l'intégration dans un processeur, une interface du système d'exploitation ainsi qu'une extension de la VM. Cette pile technologique ralentit considérablement l'expérimentation, en particulier pour le développeur matériel qui a un cycle de retour d'expérience de son implémentation allongé. Pour permettre une possibilité de co-design logiciel/matériel, nous proposons Gigue, un générateur de binaires similaire à la région de code JIT qui propose une interface pour instrumenter les binaires à différents niveaux. Notre objectif est de pouvoir exécuter ces binaires directement sur les simulateurs "cycle-accurate" de processeurs RISC-V open-source.

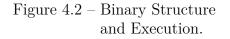

Gigue est construit autour de trois objectifs principaux : la paramétrisation et détermination de caractéristiques des binaires générés, la modularité de sa génération permettant l'instrumentation des binaires à différents niveaux, ainsi que la vérification de l'exécution des binaires avant leur distribution. Les binaires que Gigue génère sont compilé statiquement et donc auto-contenus dans un exécutable ELF. Leur structure est inspirée de la région de code JIT de la VM Pharo. Ils sont composés d'une région qui contient différentes méthodes JIT remplies aléatoirement d'instructions, ainsi que d'autres éléments tels que des caches polymorphiques [35], ou des "trampolines" qui contrôlent le flot d'exécution venant et sortant. Une autre région appelle successivement toutes les méthodes présentes dans la première dans un ordre aléatoire. Pour générer le binaire correspondant, toutes les méthodes sont instanciées, remplies d'instructions, puis Gigue en déduit un graphe de flot de contrôle et ajoute des appels inter-fonctions dans le corps des méthodes. Il compacte les différentes parties dans un binaire directement exécutable.

De nombreux paramètres permettent de contrôler la génération de binaires de Gigue. Tout d'abord, la caractérisation de la zone contenant les méthodes JIT à travers sa taille et la fréquence d'apparition de ses différents éléments. Ensuite, le type d'application généré est contrôlée par la caractérisation des méthodes elles-même (taille et variation de taille), la distribution des types d'instruction qui les compose (arithmétique, accès mémoire, changement de flot de contrôle) ou la fréquence d'utilisation des appels ainsi que leur profondeur. Ces paramètres permettent de générer et amplifier des classes d'applications données pour tester différents paramètres. Dans un cas d'usage, nous utilisons des informations d'exécution de différents benchmarks [36], [37] ainsi que des informations sur la région de code JIT Pharo [38]. Nous dérivons 9 classes d'applications avec des tailles de méthodes et densité d'appels différentes. De manière similaire, nous générons 9 classes d'applications différentes en variant la taille des méthodes et la quantité d'appels mémoire qui compose les méthodes. Nous démontrons l'interfaçage direct de Gigue avec deux processeurs applicatifs open-source : CVA6 [3] et Rocket [39].

Pour permettre l'ajout d'instructions "*custom*" au sein des binaires générés par Gigue, nous définissons plusieurs points d'accroche dans le processus de génération. Trois exemples sont intégrés dans Gigue, un premier ajoute des instructions de rotation qui ne sont pas ajoutées au jeu d'instruction par défaut; un second ajoute une "*shadow stack*", une pile d'appel dupliquée qui stocke les adresses de retour mises en place lors d'un appel de fonction; enfin, une authentification de pointeur est mise en place, authentifiant les adresses de retour des fonctions lors de l'appel et les vérifiant lors du retour du flot de contrôle. Ces trois solutions sont ajoutées dans les binaires soit dans le corps des méthodes (permier cas) ou dans le prologue et l'épilogue des fonctions. Pour vérifier leur implémentation dans le binaire, nous proposons une interface de test simplifié qui utilise le simulateur de processeur Unicorn [40]. Les nouvelles instructions sont détectées, et lors de la levée d'une exception les concernant, la routine correspondante est exécutée sur l'état du processeur avant de continuer l'exécution. Ce support permet de garantir l'exécution des binaires avant leur distribution, ainsi que de vérifier l'intégration des instructions dans le binaire.

## JITDomain : Sécurisation du Code JIT par les Instructions

Extraits de l'état de l'art et des solutions de sécurité déjà déployées autour des VMs et leurs éléments, nous définissons plusieurs garanties nécessaires à la sécurisation du code JIT. Tout d'abord, la séparation de la pile d'appel et la vérification des adresses de retour permettent de garantir l'intégrité du flot de contrôle à gros grain. Ensuite, l'accès des données contenues dans la région du code JIT doit être strictement limitée aux accès provenant du code JIT lui-même. Enfin, le filtrage des appels système restreint les capacités d'un attaquant qui contrôlerait la région du code JIT. Pour permettre leur adoption, la mise en place de ces garanties doit se faire avec un impact minimum sur les ressources matérielles du processeur ainsi qu'un impact minimum sur la performance et la taille du code JIT instrumenté.

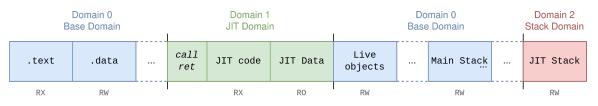

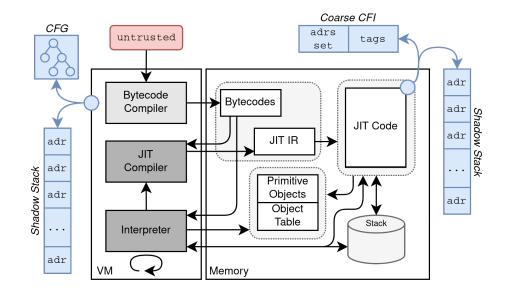

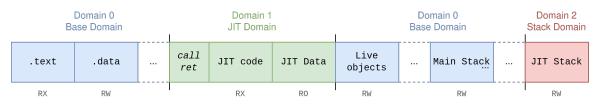

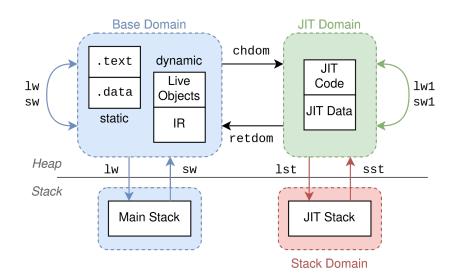

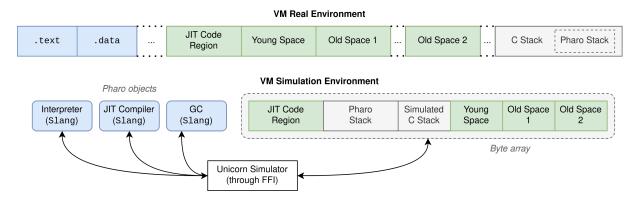

Afin de séparer la région du code JIT du reste de l'application, nous étendons le principe d'isolation de domaines par les instructions. Ce principe est présenté par les auteurs de RIMI [33] et consiste à dupliquer les instructions d'accès mémoire pour chaque domaine qui doit être isolé. De cette manière, les données contenues dans le code JIT ne peuvent être utilisées que par le code JIT lui-même et la "shadow stack" n'est accessible qu'en utilisant les instructions load/store qui lui sont attribuées. L'espace mémoire est séparé en plusieurs domaines qui sont présentés sur la Figure 1 avec leurs permissions associées. Le domaine de base (bleu) contient le code statique de la VM et de ses composants et utilise la pile pour ses appels et une zone dédiée du tas pour y stocker les objets utilisés par l'application. La zone JIT (vert) contient le code JIT, les données associées ainsi que les "trampolines", des routines directement émises en code machine qui sont utilisés par le code JIT. Les données de cette région sont placées séparément et dans une région qui est "read-only". Enfin, une autre pile d'appel est placée dans une zone à part et contient les adresses de retour des appels de fonctions.

FIGURE 1 – Modèle mémoire de la séparation des domaines.

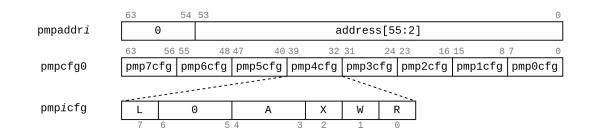

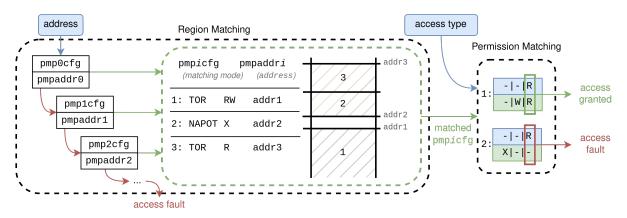

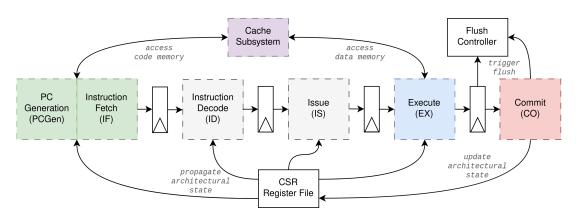

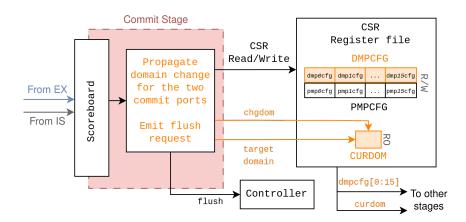

Pour supporter la séparation de ces domaines, plusieurs modifications sont implémentées sur le processeur CVA6 [3]. Tout d'abord, l'étage de décodage est étendu avec les nouvelles instructions d'accès mémoire depuis le code JIT (1\*1/s\*1 pour les différentesvariantes de taille des loads/stores), les instructions d'accès à la pile d'appel (1st/sst)ainsi que les instructions de changement de domaine (chdom/retdom). Chaque instruction se voit associer un domaine d'exécution et un domaine d'accès. L'attribution des domaines se fait par extension du module "*Physical Memory Protection (PMP)*" déjà présent dans le processeur et qui associe à différentes plages d'adresses leurs permissions associées. Ce module est étendu pour intégrer des informations de domaines, vérifiées une fois les permissions validées. L'accès aux données est validé dans ce module, intégré dans l'unité qui contrôle les accès mémoire. De même, les instructions de changement de domaine vérifient à la fois que leur domaine d'exécution correspond au domaine courant et le "fetch" d'instructions en résultant correspond bien au nouveau domaine. Enfin, les instructions de base du jeu d'instruction RISC-V se voient attribuer des accès au domaine de base ainsi qu'une vérification d'absence de changement de domaine.

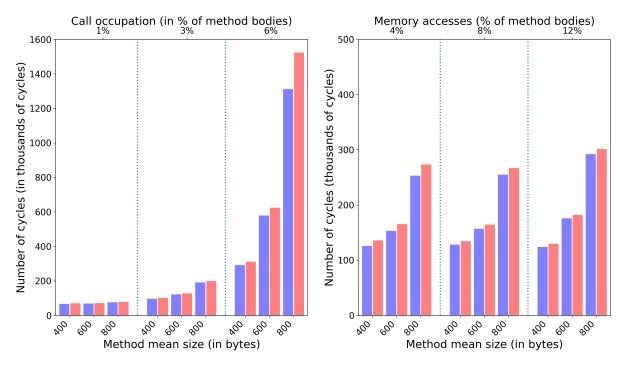

Les modifications apportées au processeur sont minimales et correspondent à une

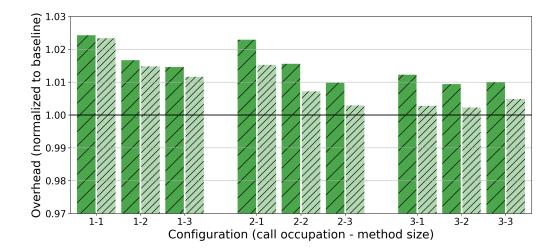

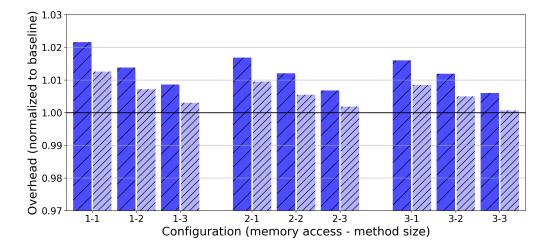

augmentation des ressources utilisées de moins de 0.5%. Nous instrumentons les binaires générés par Gigue avec cette solution pour déterminer l'impact sur la performance. Nous validons l'exécution des binaires dans le harnais de tests de Gigue en vérifiant le domaine courant et accédé de chacune des nouvelles instructions. Après instrumentation, et pour les mêmes classes d'application que celles définies dans le test d'interfaçage de Gigue, nous exécutons les binaires sur le processeur modifié. L'impact sur la performance est minimal sur l'intégralité des classes d'application, et s'inscrit à 1.5% en moyenne pour le nombre de cycles, et 0.95% pour le nombre de cycles par instruction.

### Extension d'un Compilateur JIT sur RISC-V

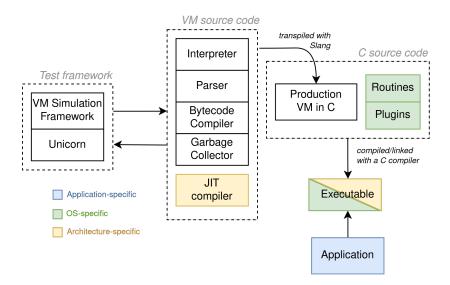

Pour pouvoir proposer un cas d'usage réel sur la mise en place de solutions d'isolation légère, nous étendons le compilateur JIT de la VM Pharo sur le jeu d'instruction RISC-V. Ce port est motivé par l'absence d'un compilateur JIT complet sur ce jeu d'instruction et la validation de résultats préliminaires obtenus à travers les binaires générés par Gigue. La VM Pharo utilise un harnais de tests complet et un environnement de simulation qui permettent de faciliter le port de son compilateur JIT surde nouvelles architectures. Le langage Pharo, successeur de Smalltalk-80 utilise des "*images*" comme support d'exécution de ses applications, contenant à la fois le code source des principaux éléments du langage, des outils dédiés ainsi que les objets instanciés par la VM.

Le compilateur JIT de la VM Pharo, Cogit, est un compilateur non-optimisant qui recompile les successions de bytecode à la granularité d'une méthode. Il utilise une représentation intermédiaire à deux adresses, calquée sur le jeu d'instruction x86/x64 pour permettre sa traduction directe. Ce choix de la représentation intermédiaire a nécessité plusieurs adaptations dans le port du compilateur sur RISC-V. Le jeu d'instruction RISC-V fait plusieurs choix de simplification qui permettent de faciliter son implémentation dans un processeur. Parmi eux, l'existence d'un unique mode d'adressage de la mémoire, l'absence de codes de conditions (*"flag registers"*) et de leurs instructions de comparaison associées, ou l'unique utilisation de valeurs immédiates. Pour faire coïncider le processus de compilation avec RISC-V, nous rajoutons une étape dans la compilation pour gérer l'utilisation des codes de conditions et traduire une suite de comparaison/branchement correctement. Nous rajoutons également des vérifications sur le traitement des valeurs immédiates utilisées et de leur correcte extension de signe.

Pour pouvoir valider le port de Cogit sur RISC-V, nous étendons l'environnement de

simulation propre à la VM Pharo [41], [42] en utilisant une nouvelle version du simulateur de processeur utilisé dans le harnais de tests, Unicorn [40]. Ce simulateur est utilisé en boîte noire pour valider les différents comportements du JIT. Plusieurs bugs ont été corrigés dans ce simulateur et rapportés dans ses dernières versions. Le harnais de tests a aussi été étendu avec des vérifications propres au port sur RISC-V et pour valider les changements dans la représentation intermédiaire ainsi que contrôler l'expansion du code généré pour combler les instructions manquantes sur RISC-V. Enfin, le débogueur de code machine implémenté dans l'infrastructure de tests est également étendu pour afficher plus clairement la traduction entre la représentation intermédiaire et le code machine généré. Nous étendons le simulateur pour supporter des instructions "custom" spécifiées par le développeur et validons leur exécution dans l'environnement de simulation.

La VM et son compilateur JIT sont finalement déployés sur une image QEMU [43] pour mesurer le gain en performance. Nous remarquons à l'aide de "*micro-benchmarks*" que le compilateur JIT permet une exécution de bytecode 40x plus rapide (en bytecode par seconde), ainsi que 63x plus d'appels de fonctions par seconde. Cependant, pour constater l'impact des patches nécessaires à la concordance entre la représentation intermédiaire et le code machine généré, nous constatons également une augmentation de 48% de la taille des méthodes JIT compilées par rapport à leur version x86/x64. Le port du compilateur JIT ouvre la porte à une expérimentation sur la pertinence d'instructions dédiées au compilateur dans un contexte de sécurité mais également d'accélération matérielle plus général.

### Conclusion

À travers ces travaux, nous proposons, mettons en œuvre et évaluons un cadre de sécurité soutenu par le matériel pour protéger le code JIT. Il applique des politiques de sécurité à la région du code JIT, comme le prévoient les défenses de l'état de l'art autour des machines virtuelles, à un coût matériel et logiciel minimal. Pour évaluer l'impact de la solution et la comparer à d'autres, nous proposons également Gigue, un générateur de binaires instrumentables. Enfin, nous avons étendu le compilateur JIT du Pharo VM pour qu'il prenne en charge l'ISA RISC-V et définit les premières étapes d'un cadre de sécurité associé. Nous pensons que ces trois contributions, disponibles en open-source, fournissent un environnement réaliste pour de futures évaluations et extensions dans les domaines de la sécurité matérielle et de son application aux machines virtuelles langage.

## INTRODUCTION

### 1.1 Motivation

Over the last decade, the security of an increasing number of computing systems has been compromised. One of the most well-known and severe vulnerabilities was disclosed in 2014 as the "Heartbleed" bug [1]. It affects the widely-used OpenSSL cryptographic software library [2] through its implementation of the Transport Layer Security (TLS) protocol "heartbeat" extension (RFC6520 [44]). The use of unmonitored user input led the server to leak its secret keys and sensitive user information. Due to its usage in widespread open-source web servers like Apache and nginx, the bug was estimated to affect between 24 and 55% of popular HTTPS sites [45]. Using a different attack vector on the same target [46], Meltdown [47] and Spectre [48] exploited critical architectural vulnerabilities in Intel, AMD and ARM processors, therefore affecting billions of devices. These attacks managed to leak sensitive information (such as passwords or personal details) from the speculative execution of the processor, either in out-of-order execution or branch prediction. The security of computing systems is guaranteed by the implementation of software patches set up once the vulnerability is revealed and identified. To this end, OpenSSL was patched to mitigate the Heartbleed bug<sup>1</sup>, and directives to protect against Meltdown attacks at kernel and OS levels since completely changing the hardware might not be an option. This leaves an open window for attackers where the bug is disclosed and users are vulnerable. In addition, even with updates patching the vulnerabilities, several platforms are not updated and live with the vulnerability.

To provide end users with guarantees on their application code security, several layers of primitives are set up at the hardware level, Operating System (OS) level, virtualization level, or through dedicated run-time environments<sup>2</sup>. Language Virtual Machines

<sup>1.</sup> https://git.openssl.org/gitweb/?p=openssl.git;h=96db9

<sup>2.</sup> We use the word "run-time" as an adjective to qualify the dynamic nature of an object (e.g. "runtime solution"), "runtime" as a noun to define the execution environment of a language (e.g. "the C #runtime"), and "run time" to qualify the moment of the execution (e.g. "at run time").

(VMs) are the execution environment of high-level managed programming languages. They abstract the compilation process and memory management to the developer and offer portability of application code. Smalltalk, Java, Python, or JavaScript all use a VM to execute and manage their code. They are complex engines composed (at least) of a source code compiler, an interpreter, a memory manager, and an optional set of increasingly optimizing run-time compilers that recompile frequently used code at run time. Their volatility and portability make them easy to deploy on several devices while guaranteeing the execution of application code. For example, JavaScript VMs are deployed in all web browsers and execute the embedded JavaScript code sent by the server on the client computer. To this end, most web browsers embed either the Google V8 engine, Apple JavaScriptCore, or Mozilla Firefox SpiderMonkey. Therefore, billions of devices deploy a JavaScript VM to display the latest ECMAScript standard [49], the reference to guarantee the inter-operability of the modern web. Other widely deployed examples include Android applications that are Java applications compiled down to the intermediate representation of the Java Virtual Machine (JVM), Java bytecode. This bytecode is then translated into an executable to run on the Dalvik Virtual Machine (DVM) or its successor, Android RunTime (ART). The executable is distributed to billions of end users and their devices.

The wide deployment and adoption of VMs coupled with their ability to handle memory and output machine code at run time makes them interesting targets for attackers that aim at end users. Traditional code injection attacks install attacker-supplied input in executable memory before redirecting the flow of control<sup>3</sup> to it. They are amplified in the context of VMs as the Just-In-Time (JIT) compiler(s) use a memory zone to deploy optimized and executable machine code. This zone is modified by an attacker through the injection of a malicious payload [4], or the reuse of genuine code that contains predictable elements that are then composed to define a payload [5], [6]. Other attack vectors through other components such as the interpreter [9] or garbage collector [50] can be exploited to leak sensitive information, corrupt the state of the VM, or, in the worst case, lead to arbitrary code execution on the victim's computer. Through the widespread distribution of VMs presented earlier, an attacker could launch their attack by targeting an end user with a malicious webpage or Android application to remotely execute arbitrary code. A recent example of a major vulnerability involving a VM is *Log4Shell* [51], which affected

<sup>3.</sup> We use the appellation "control flow" or "flow of control" to name the order in which program elements are executed (statements, functions, or instructions). We use the adjective "control-flow" accordingly (*e.g.* "control-flow integrity").

the popular  $Log_4J$  Java logging framework. The unmonitored user input was used to inject Java objects from an arbitrary URL to target malicious endpoints, therefore enabling arbitrary Java code execution on the server.

### 1.2 Formulation of the Research Question

The traditional answer to disclosed vulnerabilities is to patch the issue in the affected component and provide updates for the end users. Admitting the possible weaknesses of parts of the system and building defense solutions with it in mind mitigate the overall impact of a later attack. Preemptive actions and primitives that enforce security properties are highly desirable in a context that handles untrusted user input. Software-only proposals such as Control-Flow Integrity (CFI) [52], Information Flow Control (IFC) [53], or Data Flow Integrity (DFI) [54] offer strong security guarantees to the user. However, along with the guarantees come a heavy cost in performance and code size, preventing the actual usage of such solutions in performance-critical systems. While those solutions apply to the static part of the VM, dynamically generated code and data are too expensive to instrument [18] and result in degraded versions of the solution [19]. Common security measures such as guaranteeing that memory is never executable and writable at the same time are not trivial to enforce on dynamically generated JIT code [10], [19] and often result in a deterring cost in performance.

The integration of hardware-accelerated security features into vendor processors offers a tangible performance advantage over their software counterparts. This makes them attractive for performance-critical components and ensures robust isolation when deployed around and in VMs [9], [10]. However, challenges arise when dealing with closed-source vendor solutions such as Intel SGX [21, Vol.3 Ch.34-39], or ARM TrustZone [55]. Responding to a disclosed vulnerability targeting the mechanism becomes difficult due to the patch cycle aligning with the next generation of processors from the vendor. Many of these extensions were deprecated by the manufacturer itself (*i.e.* Intel MPX, Intel SGX, *etc.*). The necessity for open and flexible solutions becomes evident, especially in light of vulnerabilities identified in their counterparts. Dedicated instructions offer an alternative approach to existing solutions [22], [32], or provide new fine-grain isolation techniques [31], [33]. We raise questions about their application or design, particularly concerning dynamically generated JIT code.

We present the thesis statement as the following:

"Dedicating custom instructions supported by the underlying hardware processor to the machine code generated by the JIT compiler of a VM can enforce strong isolation primitives around this performancecritical component."

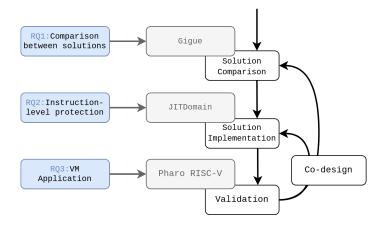

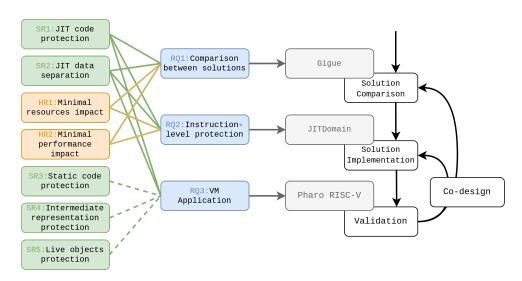

Derived from this statement, we define three research questions that tackle the different research axes of this thesis:

**RQ1:** What metrics define hardware solutions in the context of JIT code, and how can we compare solutions without complete access to a VM?

**RQ2:** What defines an interesting custom instruction for the JIT code, and how can the JIT code be isolated through the instructions it generates?

**RQ3**: What challenges arise when adding custom instruction to the JIT compiler, and how can it be tested without complete access to the hardware implementing the solution?

### **1.3** Contribution

In this thesis, we propose a security approach that shifts away from relying solely on software-defined security primitives. Instead, we advocate for a strategy based on leveraging dedicated hardware-assisted security features. Furthermore, rather than utilizing off-the-shelf components found in commercial processors, our proposal involves extending open-source processors through a defined methodology to create and implement a comprehensive solution framework. Our method taps into the extensive instruction set extension space of the RISC-V Instruction Set Architecture (ISA) [20], [56], enabling versatile prototyping within existing processors. The proposed multi-level approach emphasizes early validation of prototyped solutions at different stages of the technology stack, ranging from processor support to practical usage in VMs. To assist in decision-making, we provide tools for estimating the potential impact of a solution on the JIT compiler performance before deploying the solution in a production VM. To this end, we reconcile low-level hardware extensions to the high-level JIT compiler through the instrumented generated machine code. The main contributions of this thesis are the following. A synthetic JIT code workload generator. We introduce Gigue, a synthetic random workload generator designed to produce executables resembling JIT code regions. The generated binaries are self-contained and can be deployed bare-metal on the processor, either directly or through their cycle-accurate simulator. We present how Gigue can be utilized to generate a set of binaries and augment them by shifting their input parameters. We run the resulting binaries on two fully-featured RISC-V cores, CVA6 [3] and Rocket [39]. In addition, we present how we integrate custom instructions in the Gigue binaries through hooks available at different instruction generation levels. This extension is also present in the testing environment Gigue provides to validate to test the correct execution of binaries, even when containing custom instructions. We also provide utilities to run, collect, and display results, as well as patch the compilation toolchain or generate minimal binary examples.

An instruction-level domain isolation implementation. We present JITDomain, an instruction-level domain isolation framework derived from embedded systems [33] and applied in the context of JIT compilation. It takes advantage of the locality of the JIT code region and its need for strict and performant security guarantees. To this end, we add duplicated memory access instructions, routines to change domain, and shadow stack instructions. The JIT code is allocated within a hardware-defined domain, enforcing several aspects: *data separation* as only JIT code is permitted to access JIT data present in the JIT code region; call stack separation as the JIT call stack is placed into a domain accessible exclusively through the prologues and epilogues of JIT-compiled methods; system-call filtering from the JIT code, where the execution is stopped as soon as a system call instruction is decoded from the domain, either from the expected or hidden (after a disruption) control flow. We propose an implementation of the design in the CVA6 RISC-V core [3] and present an evaluation of the solution on Gigue binaries that implement the solution. The resulting overhead in terms of FPGA resource utilization boils down to a 0.5% area overhead, and the performance overhead is measured at less than 2%.

A JIT compiler port to the RISC-V ISA. We highlight the challenges of porting a JIT compiler to the RISC-V ISA by presenting the port of Pharo VM's JIT compiler Cogit to the RISC-V ISA. We present the main differences between the RISC-V ISA and more traditional x86/64 or ARMv7/v8 instruction sets. The impact of these differences is presented through the lens of the Pharo VM JIT compiler Intermediate Representation (IR) and on the testing and tooling ecosystem. We extended the Pharo VM development tools to accommodate the available RISC-V environment. Among them, is Unicorn [40], the CPU emulator used to test JIT code from within the Pharo environment, and the machine code debugger. We developed a version compliant with the Pharo VM's test harness and managed to run a minimal image on a QEMU RISC-V Fedora image getting 40x speedup over the base interpreter in the number of executed bytecodes and 63x calls per second. To add JIT code custom instructions, we connect emulator hooks to handle custom instructions, allowing for prototyping and validation of custom instructions and their usage from within the VM development environment.

The contributions are linked to the research question they aim to answer in the above figure. Their goal and articulation range from the creation of a platform for meaningful comparison of solutions, to the implementation of a solution in hardware, along with a port of the Pharo VM and a first implementation in its simulation environment. The wider goal of this thesis is to provide tools to co-design hardware isolation for VMs.

### 1.4 Organization

The remainder of this thesis is outlined as follows. In Chapter 2, we conduct a comprehensive examination of the background and state-of-the-art attacks targeting language VMs, along with the defensive measures implemented in response. We then identify a set of practical components and their associated requirements for VMs to consider adopting. Chapter 3 delves into the RISC-V instruction set and the corresponding extensions, viewed through the lens of the identified VM requirements. The chapter sheds light on the solutions derived from this exploration. Next, in Chapter 4, we introduce Gigue, our workload generator. Gigue serves as a foundational tool for comparing security solutions in the context of just-in-time-compiled code. Chapter 5 details our efforts in designing and implementing JITDomain, an instruction-level domain isolation framework that exploits just-in-time-compiled code locality for isolation. Moving forward, Chapter 6 addresses the challenges associated with extending the Pharo VM JIT compiler to the RISC-V ISA and how it opens up further experimentation for VM security prototyping. Finally, in Chapter 7, we discuss the future directions of this work and conclude the thesis.

Part I

# **Background & Related Works**

# RELATED WORK: LANGUAGE VIRTUAL MACHINES SECURITY

In recent years, security has become a crucial issue, and the technical complexity associated with it continues to grow. Thus, security attacks and defenses follow the usual cat and mouse game of finding a new attack and designing a security mechanism to protect against it. This has led to complex, heterogeneous attacks, i.e. those operating at several levels, to which fine-grained defense mechanisms respond.

This concern also applies to language Virtual Machines (referred to as VMs, for which an overview is provided in Section 2.1). Attackers attempt to compromise VMs and, through it, access the victim host computer. Section 2.2 covers various attack schemes. Defense solutions, as presented in Section 2.3, must strike a balance between security guarantees and the performance overhead they incur. As the global summary presented in Section 2.4, fine-grain isolation of known critical VM components is crucial for its protection. Performance-critical components benefit from hardware-enforced guarantees due to their lower impact on performance and the higher level of security they provide.

### 2.1 Background: Language Virtual Machines

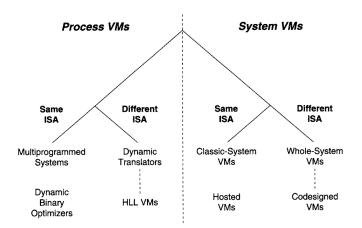

**Glossary:** In the book "Virtual Machines: Versatile Platforms for Systems and Processes" [57], Jim Smith and Ravi Nair introduce a taxonomy of the term Virtual Machine and its different meanings. They split the VM characterization into two main categories, as presented in Figure 2.1: process VMs and system VMs. Process VMs support an Application Binary Interface (ABI), user instructions, and system calls. Process VMs using the same guest/host Instruction Set Architecture (ISA) come as multiprogrammed systems (as included in most of today's systems) or dynamic binary optimizers that optimize guest instructions. Process VMs with different guest/host ISA come as dynamic translators that convert guest instructions to the host ISA, or High-Level Languages (HLL)

VMs that perform an abstraction of the guest at a higher-level process interface. System VMs support a complete ISA, with both user and system instructions. Their main goal is to provide replicated and isolated system environments of a guest ISA on top of another (or the same) host ISA.

This chapter addresses HLL VMs, which will be called Language VMs, VMs, or execution engines transparently, with a specific focus on security, from both attacks and countermeasures points of view.

Figure 2.1 – A Taxonomy of Virtual Machines, as presented by J. Smith and R. Nair [57].

Language virtual machines have been a major milestone in language implementation through the two main contenders Smalltalk [58] and Java [59]. They simplified the process of ensuring the portability of applications for developers by providing a portable execution environment. As Java advertised in 1995, "write once, run anywhere" (as long as the Java VM is available for the corresponding OS and architecture). Smalltalk and Self [60] have brought to life many of the concepts that are still used today in the virtual machines of recent languages. Among them, careful language optimizations [35], [61], [62] and adaptation to new architectures [63], [64]. Today, virtual machines are widely deployed. In cloud environments, as the run-time environment for supported languages; as embedded support in web browsers to execute the JavaScript client-side part of web pages. However, their propagation, widespread usage, and implementation complexity make them a target of choice for attackers.

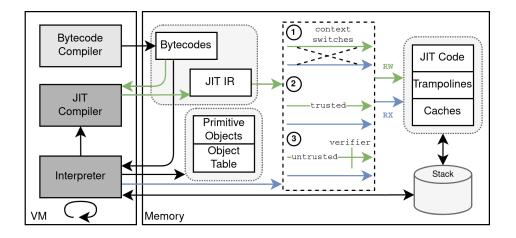

Before analyzing these attack scenarios, a deep understanding of the insights of virtual machines is mandatory. These components, an overview of which is depicted in Figure 2.2, will be further detailed in this section, along with corresponding annotations in the

figure.

Figure 2.2 – Virtual machine overview (derived from [9]).

### 2.1.1 Interpretation

To start the execution of a managed language, the source language is *interpreted*. This step starts with a *parser* that constructs the Abstract Syntax Tree (AST) representation of the input source language. The AST is then compiled by a *bytecode compiler* into a VM-specific intermediate representation (IR) referred to as bytecode. The bytecode is consumed by an interpreter, in a cycle of fetching the bytecode, analyzing it, executing the corresponding action, then fetching the next bytecode. As most of the interpreter activity decode/dispatch is spent in the dispatch loop, the base process tied in both the direct and indirect branch predicts that impact performance [65]. "Threaded interpretation" [66] promotes a goto implementation rather than the base switch implementation [67]. This allows the dispatch step to occur by jumping directly to the next correct execution unit at the end of the previous execution unit, reducing the time spent in the loop. However, with more recent processors and more precise branch predictors, the indirect branching prediction now presents less of an impact on performance [68] and any optimization on the interpretation process usually fall short in the presence of a Just-in-time (JIT) compiler.

# 2.1.2 Just-in-Time Compilation

JIT compilation refers to the recompilation at run time of a succession of bytecode detected as of interest as being frequently called. Hence, in *mixed mode Just-in-time (JIT) compiler architecture*, the interpreter, baseline of the execution is followed by a sequence of successively higher optimizing JIT compilers. The qualifications of "succession of bytecode" and "frequently" from the previous sentence are fine-tuned and VM-dependent. The granularity depends on the VM: either it is an execution trace [69], [70], a method [59], [71], or a basic-block [72]. Once a "hot path" is detected, the selected JIT compiler (which is selected based on its degree of optimization) recompiles the succession of bytecode into a compiler-specific Intermediate Representation (IR). The need to introduce this new IR comes from its different goals. Whereas the bytecode is designed to be executed by the interpreter, the JIT IR is designed to support optimization down to machine code.

The two main challenges faced by JIT compilation are: (1) ensuring calls/returns between the interpreter and the JIT code region transparently, and (2), in the case of dynamically typed languages, type-inferring efficiently to avoid a costly method lookup.

**Control-flow dispatch:** The call stack of the JIT code region needs to interact with the native stack of the VM as well as the rest of the host architecture. To help redirect control flow, switch between the native and JIT call stack along the defined calling convention, as well as perform other often-used routines, the JIT compiler installs machine code stubs called *trampolines* in the JIT code region. Direct call to these trampolines avoids the use of duplicated routines throughout elements of the JIT code region.

**Type inference:** Dynamically-typed object-oriented languages are prone to slowdown at *method-lookup* time. Identifying the correct class from which to extract a named method for application to the final instance is a costly process. It is usually sped up through a collection of optimizations. *Inline caches* specialize the type by generating machine code for the most used receiver type and verifying it with a type guard. This type specialization can be propagated aggressively through the whole trace [73] of a tracing compiler. It can also be extended to *Polymorphic Inline Caches (PICs)* [35], a machine code jump table that redirects to the correct polymorphic method in the JIT code region based on the receiver type. From the study of the usage of PICs, often used receiver types are inferred to better direct caching on further executions in an optimization called *type feedback* [74]. *Hidden classes* (as named in Google Chrome JavaScript V8 engine) or maps [61] are introduced in Self, a dialect of Smalltalk, and help to efficiently manipulate dynamic objects by creating a shared iterative underlying structure that stores the layout of live objects. Splitting the layout from the live objects and having them reference it makes any optimization of the layout beneficial to all live objects referencing it and reifies the JIT compilation of shared structures.

## 2.1.3 Additional components

In addition to the components responsible for the compilation and execution of the source language (that is the main focus of this thesis), VMs need two parts to fully operate: (1) a component that transparently manages memory for the applications it executes and (2) a way to operate with the lower-level components of the execution stack: the Operating System (OS) and shared libraries. VMs automatically grant and retrieve memory to objects in the heap. The component responsible for memory allocation and retrieval is called a *garbage collector* [75]. This component is a research area by itself, both in the algorithms it uses, the performance it provides, and the treatment of garbage collector-related bugs (which are often very complex). To fully integrate into modern computer architecture, VMs also need to interact with external elements handled by the OS through shared libraries or other routines. *Foreign function interfaces (FFI)* connect the VM to its surroundings and allow it to perform OS and architecture-dependent tasks such as **syscall** accesses, graphic libraries, or user-defined bridges to routines in other languages.

# 2.2 Virtual Machine Attacks

Attacks against VMs are based on known attacks against statically compiled code, extended in the dynamic context of VMs, and taking advantage of the low-level operations the JIT compiler has to perform. Attacks are divided into three main categories: **code-injection attacks**, **code-reuse attacks**, and **data-only attacks**. These categories are mostly presented in chronological order and highlight the vulnerability of many parts of the VM. In the rest of this chapter, the following terminology is used to qualify attacks and the elements surrounding them:

- Vulnerability: A weakness in an information system, system security procedures, internal controls, or implementation that could be exploited or triggered by a threat source. Common memory vulnerabilities are: buffer overflow, from lack of array bound checking, allowing an attacker to spill values on the stack; use-after-free, from dangling pointers, referencing uncontrolled memory; or type confusion, from object metadata confusion, giving access to memory referenced for object attributes.

- Exploit: A program, piece of code or even some data written by a hacker or malware writer that is designed to take advantage of a bug or vulnerability in an application or operating system.

- Payload: Objective of what a virus, worm or trojan is designed to do on a victim's computer, either delivered via a stager or directly placed on the victim's computer (called stageless, or stage-0).

- *Stager:* An executable used in multistage cyberattacks to establish a connection to the command-and-control (C&C) server, deliver and then run larger malicious modules.

- Shellcode: A type of payload that spawns a shell for the attacker, by running "/bin/sh", often hardcoded in assembly.

# 2.2.1 Context and Threat Model

**Context:** In their work, Zhang et al. [19] illustrate the process that the Firefox Gecko engine follows to execute and display internet resources. HTML, CSS, and multimedia inputs are first consolidated into a *Document Object Model (DOM)*, which is utilized by the *layout engine* and *rendering engine* to present web pages to users. The DOM interface also serves as a communication channel for the JavaScript VM (SpiderMonkey in Firefox) to interact with page elements. Scripts undergo an initial interpretation and are then recompiled by the JIT compiler to generate platform-specific native instructions. These instructions are placed in the JIT code region, where they may be optimized as described earlier. The garbage collector manages memory allocation and reclamation for necessary objects. Major web browsers, such as Firefox, Chrome, and Safari, embed production JavaScript VMs (like SpiderMonkey and V8). These VMs continuously evolve to meet the latest standards and user demands for high performance. However, each year, new memory vulnerabilities are discovered in production VMs, often related to memory errors or data validation, which can potentially lead to arbitrary code execution on the host computer.

**Threat Model:** In line with the scenario and expectations surrounding modern VMs, the fundamental threat model for VM attacks assumes that the attacker can supply arbitrary input data (source code) to the VM. This input is expected to be compiled, executed, and possibly recompiled by the VM without raising any suspicion. The system incorporates static code defenses, including strong  $W \oplus X$  policies, Data Execution Prevention (DEP), and Address Space Layout Randomization (ASLR). These defenses have been designed to counter overflow attacks, either they target the stack or the heap. In these attacks, an adversary typically injects malicious code into executable memory and then manipulates the control flow to execute it. In the remainder of this document, the threat model is refined to better represent the capability of the new attacks. As new vulnerabilities are found each year in VMs, it is expected that an attacker knows the existence of a memory vulnerability.

**Orthogonal works:** Side-channel attacks exploit information from hidden auxiliary channels, which can be either physical through time or energy leaks [47], [48], or software-induced using memory locality properties [76]. JIT compilers, susceptible to introduce timing side-channel vulnerabilities [77] in the generated machine code, have been addressed in the literature [78], [79]. Garbage collectors, responsible for handling sensitive objects, are also vulnerable to side-channel attacks [50], [80], potentially revealing information on disposed objects. We argue that these side-channel attacks, though orthogonal to our work, should be considered in the design of a VM protection solution.

# 2.2.2 JIT Code Injection Attacks