## Évaluation de topologies d'amplificateurs faible bruit et robustes en filière GaN pour applications radar ou télécom en bande X

Bastien Pinault

## ▶ To cite this version:

Bastien Pinault. Évaluation de topologies d'amplificateurs faible bruit et robustes en filière GaN pour applications radar ou télécom en bande X. Electromagnétisme. Université de Toulouse, 2024. Français. NNT: 2024TLSES070. tel-04692765

## HAL Id: tel-04692765 https://theses.hal.science/tel-04692765v1

Submitted on 10 Sep 2024

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Doctorat de l'Université de Toulouse

préparé à l'Université Toulouse III - Paul Sabatier

Évaluation de topologies d'amplificateurs faible bruit et robustes en filière GaN pour applications radar ou télécom en bande X.

Thèse présentée et soutenue, le 27 juin 2024 par

## **Bastien PINAULT**

## École doctorale

GEETS - Génie Electrique Electronique, Télécommunications et Santé : du système au nanosystème

## **Spécialité**

Electromagnétisme et Systèmes Haute Fréquence

## Unité de recherche

LAAS - Laboratoire d'Analyse et d'Architecture des Systèmes

## Thèse dirigée par

Jean-Guy TARTARIN

## **Composition du jury**

M. Thierry TARIS, Rapporteur, Bordeaux INP

M. François DANNEVILLE, Rapporteur, Université de Lille

Mme Carole ROSSI, Examinatrice, CNRS Occitanie Ouest

M. Jean-Guy TARTARIN, Directeur de thèse, Université Toulouse III - Paul Sabatier

#### Membres invités

M. Damien SAUGNON, CNRS Occitanie Ouest

M. Vincent ARMENGAUD, CNES

« Tout le monde est un génie. Mais si vous jugez un poisson sur ses capacités à grimper à un arbre , il passera toute sa vie à croire qu'il est stupide »

Albert EINSTEIN

## Remerciements

Aucun accomplissement n'est le fruit d'un seul individu. Je tiens à exprimer ma profonde gratitude envers toutes les personnes qui m'ont soutenu tout au long de ce parcours. Leurs encouragements, conseils et soutiens ont été essentiels pour atteindre cet objectif. Leur contribution a été inestimable et je suis reconnaissant pour leur présence à mes côtés.

J'exprime une profonde gratitude à Jean-Guy TARTARIN, grâce à qui j'ai énormément appris que ce soit sur le plan scientifique, mais également humain. Merci de m'avoir fait confiance dès le Master et de m'avoir offert cette opportunité. J'ai beaucoup aimé nos discussions, pas toujours scientifique qui m'auront permis de progresser, de surmonter des doutes et de changer de perspectives quand cela était nécessaire. Merci de m'avoir fait confiance pour les enseignements, un domaine auquel j'aurais vraiment pris goût.

Merci à Damien SAUGNON, pour son aide précieuse dans les salles G31 et G32. Toutes ces mesures n'auraient pas pu voir le jour sans toi, j'espère emmener avec moi une partie de la rigueur de travail que tu tentes de communiquer. Au-delà de l'aspect professionnel, j'ai énormément apprécié les moments de discussion que nous avons pu avoir, que ce soit autour d'un VNA ou d'une bière (à consommer sur une chaise plus stable que celle au Pays-Bas...). Je remercie également le service I2C, Nicolas MAURAN, Alexandre RUMEAU et Lucas MOREAU pour leur aide et les formations prodiguées sur les différents instruments que comporte le LAAS.

Je remercie également les différents membres des équipes MOST et ISGE, tous les citer me ferait prendre le risque d'en oublier donc cela restera non nominatif.

Merci aux ITA, doctorants et stagiaires avec qui j'ai pu partager de bons moments que ce soit le midi au LAAS ou ailleurs. Un merci particulier à Alexandre FLETE, Alexis BOUGAUD, Arnaud COLLET, Germain BOURSIER, Paul KERN et Romain BOYER d'avoir supporté toutes les conneries que je pouvais sortir les midis.

Je voudrais partager ma plus profonde gratitude envers les membres du bureau G19. Audrey CAYRON, mon premier mentore et parrain dans l'aventure de thèse, qui à défaut de me transmettre la passion de la rédaction aura réussi me donner tous les petits tuyaux, sans lesquelles j'aurais eu beaucoup de mal. Nasri SAID, « le mec trop fort », « j'ai beaucoup aimé » toutes les discussions scientifiques, philosophiques et géopolitiques que nous avons pu avoir. Au-delà de mon amitié, j'ai un profond respect pour l'homme sage que tu es. Sans transition, Lucas KEMYSTETTER « El Perturbator », je ne peux malheureusement pas mettre le surnom complet... Merci pour tous ces bons moments et pour les discussions beaucoup moins philosophiques, mais très intéressantes quand même. Merci à Loïc POUZENC de m'avoir aidé à traiter des données quand une certaine deadline était beaucoup trop proche. Même si nous n'étions pas souvent d'accord j'ai apprécié nos débats parfois très « polarisés ».

« Je sais que nous nous reverrons un jour ou l'autre. Salut, les potes! »

L'enseignement est une partie que j'ai réellement appréciée, ce n'est pas juste la transmission d'un savoir, il permet de relativiser et de se remettre en question, bref de voir les choses sous un nouvel angle. Au-delà des étudiants à qui je dois beaucoup, j'ai apprécié pouvoir rencontrer des enseignants que j'avais eus en licence ou master. Merci, tout particulier à Marc TERNISIEN pour les conseils pas toujours éclairés en termes d'enseignements. Dans la même veine, je salue Mathieu MASQUERE, Gerald LEDRU qu'il m'a fait plaisir de revoir après mon stage de L3 au LAPLACE et avec qui j'ai partagé de bons moments dans les enseignements d'électronique.

Je remercie tous mes partenaires de padel, mais aussi du volley que ce soit à l'Université Paul SABATIER ou à Ramonville (« SIU »). Ces activités m'ont permis de trouver un second souffle notamment dans des moments de doutes.

À tous mes amis que ce soit de l'Union, de la fac, de la Play, merci de m'avoir accompagné pendant toutes ces années. Merci aux « Golden Flame » et aux « Gens bons ».

Merci à Fadwa de m'avoir supporté pendant toutes ces années, ta gentillesse et ta bonté m'apportent énormément, tu as tout mon amour.

Merci à ma famille d'avoir été un socle sur lequel j'ai toujours pu m'appuyer. Ces moments avec vous, trop rare me sont vraiment précieux.

À mon père, à ma mère, je vous dois absolument tout. Vous êtes mes modèles, mes amis et un livre plus long que cette thèse serait nécessaire pour exprimer toute ma gratitude. Merci.

## Table des matières

| REMERCIEI  | MENTS                                                        | 3                    |

|------------|--------------------------------------------------------------|----------------------|

| TABLE DES  | MATIERES                                                     | 5                    |

| INTRODUC   | CTION GENERALE                                               | 9                    |

| BIBLIOGRA  | taphie                                                       | 13                   |

| CHAPITRE   | 1: LE ROLE DE L'AMPLIFICATEUR FAIBLE BRUIT DANS UNE ARCHITEC | TURE DE RECEPTION 15 |

| 1.1 In     | ITRODUCTION                                                  | 15                   |

| 1.2 RA     | APPORT SIGNAL A BRUIT ET FACTEUR DE BRUIT                    |                      |

| 1.3 Ac     | GRESSIONS ELECTROMAGNETIQUES                                 |                      |

| 1.3.1      | Sensibilité des architectures de réception                   |                      |

| 1.3.2      | 2 La guerre électronique                                     | 20                   |

| 1.3.3      | B Les contres contre-mesures                                 | 25                   |

| 1.3.4      | Applications pour LNAs robustes                              | 25                   |

| 1.4 TE     | ECHNOLOGIE NITRURE DE GALLIUM                                | 27                   |

| 1.4.1      | Champs applicatifs                                           | 27                   |

| 1.4.2      | ? Technologie faible bruit                                   | 28                   |

| 1.4.3      | B Technologie utilisée : OMMIC-D01GH                         | 31                   |

| 1.4.4      | Quel substrat pour le GaN ?                                  | 33                   |

| 1.5 CA     | ARACTERISTIQUES NON LINEAIRES                                | 34                   |

| 1.5.1      | Linéarité et Densité de puissance                            |                      |

| 1.5.2      | Pacteurs de mérites non linéaires                            | 35                   |

| 1.6 Cc     | ONTEXTE DE LA THESE                                          | 37                   |

| 1.6.1      | Architecture de réception robuste                            | 37                   |

| 1.7 Co     | OMPARATIF TECHNOLOGIQUE                                      | 39                   |

| 1.7.1      |                                                              |                      |

| 1.8 M      | 1ethodes conventionnelles de robustification d'un LNA        | 40                   |

| 1.8.1      | l Composant robuste                                          | 40                   |

| 1.8.2      | ? Résistance de grille                                       | 42                   |

| 1.8.3      | B Limiteur à diode                                           | 43                   |

| 1.8.4      | 1 Limiteur actif                                             | 43                   |

| 1.8.5      | · · · · · · · · · · · · · · · · · · ·                        |                      |

| 1.8.6      | 6 Changement de polarisation                                 | 46                   |

| 1.8.7      |                                                              |                      |

| 1.8.8      | 3 Mise en parallèle                                          | 46                   |

| 1.9 O      | BJECTIF DE LA THESE                                          |                      |

| 1.9.1      |                                                              |                      |

| 1.9.2      | ? Fiabilité : robustesse et survivabilité                    | 50                   |

| 1.10       | VERS UNE PLUS GRANDE INTEGRATION                             |                      |

| 1.11       | CONCLUSION                                                   |                      |

| 1.12       | Bibliographie                                                | 53                   |

| CHAPITRE : | 2: CONCEPTION LNA MONOETAGE ET MULTIETAGES ROBUSTES REC      | ONFIGURABLES EN      |

| TENSION.   | 57                                                           |                      |

|            | ITRODUCTION                                                  |                      |

|            | ESIGN KIT                                                    |                      |

| 2.3 CR     | ritere de validation des Designs                             | 57                   |

| 2.4 Dı     | IMENSIONNEMENT DU COMPOSANT ACTIF                            | 58                   |

| 2.4.1      | Considérations statiques                                     | 58                   |

| 2.4     | 4.2 Fo   | acteurs de mérite hyperfréquences                            | 60         |

|---------|----------|--------------------------------------------------------------|------------|

| 2.4     | 4.3 R    | outine de conception                                         | 61         |

| 2.4     | 1.4 Ét   | tude fréquentielle                                           | 62         |

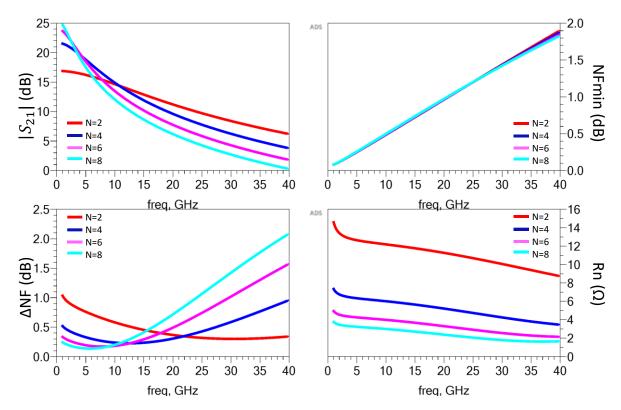

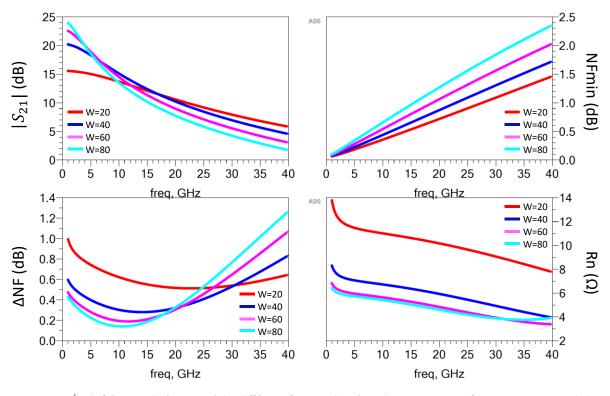

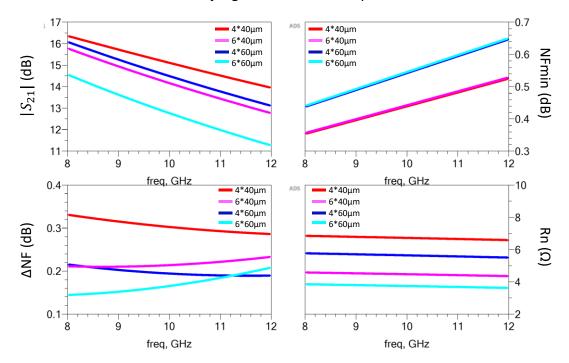

| 2.4     | 4.5 Ét   | tude paramétrique                                            | 64         |

| 2.4     | 1.6 Li   | mite de la conception conventionnelle                        | 65         |

| 2.5     | CONCEPT  | ION BIMODALE                                                 | 66         |

| 2.6     | Метнор   | OLOGIE COMPOSANT LNA ROBUSTE RECONFIGURABLE                  | 67         |

| 2.6     | 5.1 C    | artographie de la technologie                                | 67         |

| 2.6     | 5.2 Co   | onsidération du gain                                         | 68         |

| 2.6     | 5.3 D    | imension physique du HEMT : limitations                      | 70         |

| 2.6     | 5.4 D    | imensions physiques du HEMT : Applications                   | 71         |

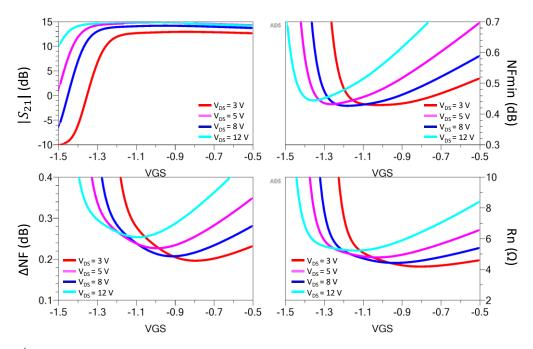

| 2.6     | 6.5 A    | gilité en tension                                            | <i>7</i> 3 |

| 2.6     | 6.6 In   | fluence de la contre-réaction inductive                      | <i>7</i> 5 |

| 2.6     | 6.7 A    | gilité en tension : limites                                  | 76         |

| 2.6     | 5.8 A    | gilité en tension : conclusion                               | 80         |

| 2.7     | ÉLEMENT  | S PASSIFS                                                    | 81         |

| 2.7     | 7.1 In   | ductances                                                    | 83         |

| 2.8     | MISE EN  | PLACE DES LNAS MONOETAGES                                    | 87         |

| 2.8     | 3.1 R    | appels                                                       | 87         |

| 2.8     | 3.2 A    | daptation entrée/sortiedaptation entrée/sortie               | 87         |

| 2.8     | 3.3 D    | émarche de conception                                        | 89         |

| 2.9     |          | LE LNA RECONFIGURABLE                                        |            |

| 2.9     | 9.1 Pi   | réambule                                                     | 89         |

| 2.9     |          | éseaux passifs : Electrique vs EM                            |            |

| 2.9     |          | abilité haute et moyenne fréquence                           |            |

| 2.9     |          | osimulation : Stabilité                                      |            |

| 2.9     |          | osimulation : Paramètres S et facteur de bruit               |            |

| 2.9     |          | hangement du point de repos : petit signal                   |            |

| 2.9     |          | hangement du point de repos : Non linéaires                  |            |

| 2.9     |          | nalyse Monte-Carlo                                           |            |

| 2.10    |          | B : LE LNA ROBUSTE                                           |            |

| 2.1     | 10.1     | Réseaux passifs : Contre-réactions                           |            |

| 2.1     | 10.2     | Réseaux passifs : Stabilité                                  |            |

| 2.1     | 10.3     | : Résultats LNA#B : Simulation électrique vs Cosimulation EM |            |

| 2.1     | 10.4     | Résultats LNA#B : Simulation Non Linéaire                    |            |

|         | 10.5     | Résultats LNA#B : Simulations Monte-Carlo                    |            |

| 2.11    |          | A VS LNA#B                                                   |            |

|         | <br>11.1 | Comparatif bruit et point de compression                     |            |

|         | 11.2     | Solutions non implémentées                                   |            |

| 2.12    |          | A DEUX ETAGES                                                |            |

|         | 12.1     | Préambule                                                    |            |

|         | 12.2     | LNA deux étages reconfigurable en tension                    |            |

|         | 12.3     | Architecture parallèle                                       |            |

|         | 12.4     | Architecture Cascade : topologie à deux étages               |            |

|         | 12.5     | Coupleur interétage                                          |            |

| 2.13    | -        | CUSION                                                       |            |

| 2.13    |          | DGRAPHIE                                                     |            |

|         |          |                                                              |            |

| CHAPITE | RE 3:    | CARACTERISATIONS ELECTRIQUES ET EN BRUIT DES LNAS EN BANDE X | 121        |

| 3.1     | Introdu  | CTION                                                        | 121        |

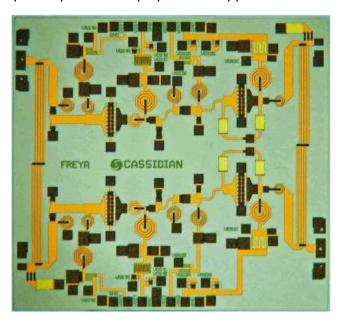

| 3.2     | PRESENT  | ATION DE LA PLICE MMIC                                       | 121        |

| 1.      | Instabilites basses frequences                                                   | 122 |

|---------|----------------------------------------------------------------------------------|-----|

| 3       | 2.1 HEMT seul                                                                    | 122 |

| 3       | 2.2 Instabilité LNA                                                              | 123 |

| 3.3     | Mesure Statique                                                                  | 125 |

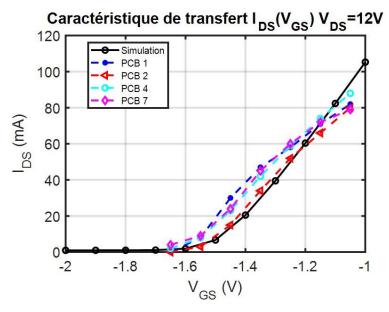

| 3       | 3.1 Dispersion                                                                   | 125 |

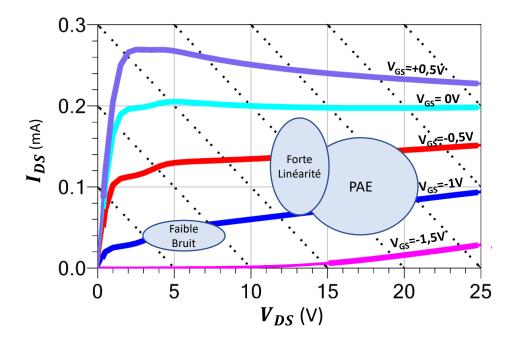

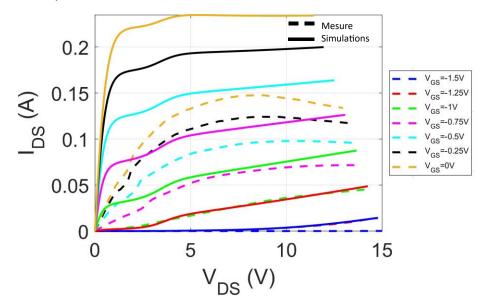

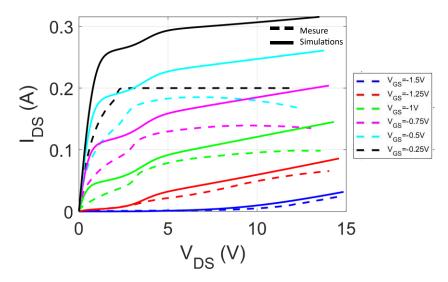

| 3       | 3.2 Caractéristiques de sortie                                                   | 127 |

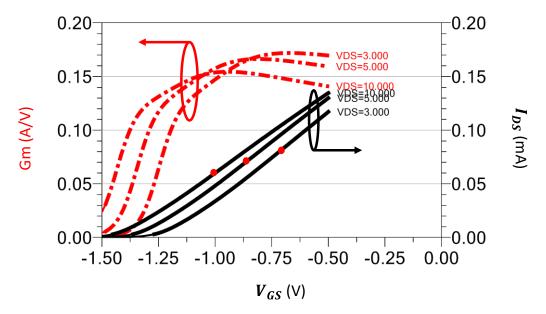

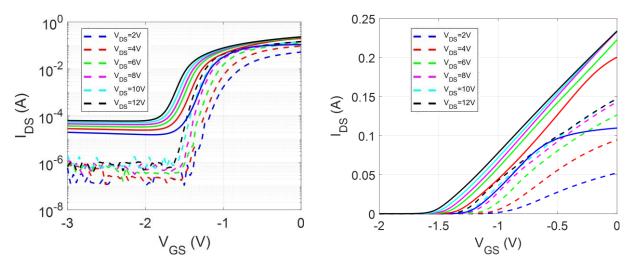

| 3       | 3.3 Caractéristiques de transfert et transconductance                            | 128 |

| 3.4     | DISPERSIONS                                                                      | 129 |

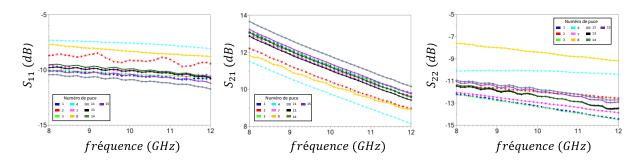

| 3.5     | LNA#A: MESURE VS SIMULATION - PARAMETRES S ET BRUIT                              | 131 |

| 3       | 5.1 Mode faible bruit                                                            |     |

| 3       | 5.2 Mode agression EM                                                            | 132 |

| 3.6     | LNA#A: MESURE VS SIMULATION - PERFORMANCES NON-LINEAIRES RF                      | 133 |

| 3.      | 6.1 Mode Faible Bruit                                                            | 134 |

| 3.      | 6.2 Mode Agression EM                                                            |     |

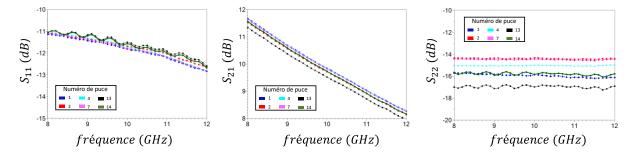

| 3.7     | LNA#B: MESURE VS SIMULATION - PARAMETRES S ET BRUIT                              |     |

| 3.8     | LNA#B: MESURE VS SIMULATION - PERFORMANCES NON-LINEAIRES RF                      |     |

| 3.9     | COMPARATIF DES PERFORMANCES                                                      | 137 |

| 3.10    | Stress RF: Monoetages                                                            | 140 |

| 3       | 10.1 Procédure de test                                                           |     |

|         | 10.2 Mesure durant le stress RF                                                  |     |

|         | 10.3 Mesure de reprises : Paramètres d'adaptation                                |     |

| _       | 10.4 Mesure de reprises : Gain petit signal                                      |     |

| _       | 10.5 Mesure de reprises : Facteur de bruit                                       |     |

| _       | 10.6 Mesure de reprises : SOA                                                    |     |

| _       | 10.7 Limites de la procédure de test                                             |     |

| 3.11    | LNA DEUX ETAGES: PCB                                                             |     |

| 3.12    | LNA DEUX ETAGES: PARAMETRES S ET BRUIT                                           |     |

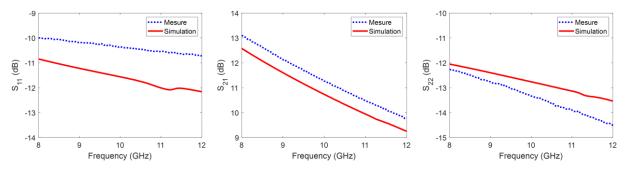

|         | 12.1 Mesures vs Simulations : Mode Faible Bruit                                  |     |

|         | 12.2 Mesures vs Simulations : Mode Haute Linéarité                               |     |

| 3.13    | LNA DEUX ETAGES: PERFORMANCES NON-LINEAIRES                                      |     |

|         | 13.1 Mesures vs Simulations : Mode Faible Bruit                                  |     |

| _       | 13.2 Mesures vs Simulations : Mode Haute Linéarité                               |     |

| 3.14    | LNA DEUX ETAGES: ETAT DE L'ART                                                   |     |

| 3.15    | VITESSE DE COMMUTATION.                                                          |     |

| _       | 15.1 Conclusion                                                                  |     |

| 3.16    | Bibliographie                                                                    | 162 |

| CHAPITI | RE 4 : VERS UN CIRCUIT RECONFIGURABLE TOTALEMENT INTEGRE MMIC, ET PERSPECTIVES D | ES  |

| TRAVAL  | JX 165                                                                           |     |

| 4.1     | Introduction                                                                     | 165 |

| 4.2     | Systeme de conversion RF/ DC                                                     |     |

|         | 2.1 Principe de fonctionnement                                                   |     |

|         | 2.2 Dimension du HEMT                                                            |     |

|         | 2.3 Impédance de sortie et connexion à la partie DC                              |     |

|         | 2.4 Connexion au LNA                                                             |     |

| 4.3     | ATTENUATEUR COMMANDABLE                                                          |     |

| 4.4     | LNA DEUX ETAGES                                                                  |     |

| 4.5     | FONCTIONNEMENT GLOBAL DE LA PUCE                                                 |     |

|         | 5.1 Éléments de test non présentés                                               |     |

|         | 5.2 Limiteur + LNA                                                               |     |

|         | 5.3 Jonction avec le détecteur de puissance (convertisseur RF/DC)                |     |

|         | Conclusion at perspectives                                                       |     |

| 4.7      | Bibliographie                  | 184 |

|----------|--------------------------------|-----|

| CONCLU   | JSION GENERALE                 | 185 |

| LISTE DE | ES PUBLICATIONS ET CONFERENCES | 187 |

## Introduction Générale

Le domaine des télécommunications, s'il s'est largement popularisé, s'est essentiellement développé sur des nécessités militaires. Télécommunications et Défense sont ainsi intimement liées, d'aussi loin que l'on remonte ; l'internet et la téléphonie mobile basée sur un multiplexage de code en sont deux exemples parmi tant d'autres, mais ils sont désormais largement déployés dans le domaine grand public. Information, désinformation, blocage des moyens d'information ; ces notions ne sont pas nouvelles, mais l'avènement de technologies toujours plus avancées oblige à développer de nouveaux systèmes (hardware et software), d'anticiper les moyens de les perturber ou de les détruire, et d'y trouver des parades. Maintenir ses moyens de communication relève d'un problème de souveraineté nationale. La naissance des semi-conducteurs puis leurs fortes démocratisations dans les années 70 peuvent ainsi s'expliquer par la convergence de ces intérêts.

Par l'attractivité, due à leurs propriétés physique et électrique l'utilisation de semiconducteurs a ouvert la porte aux des systèmes intégrés, à la montée en fréquence et en débit : au fil des décennies, la réduction d'échelle a permis d'intégrer un nombre croissant de composants sur une surface donnée [1]. L' augmentation des densités de puissance qui viennent en corollaire de cette réduction d'échelle reste un élément limitant en performance et en fiabilité des dispositifs d'amplification de type « transistors » : même si le niveau de maturité d'une technologie permet de maximiser les caractéristiques intrinsèques, le matériau utilisé reste limitant. Ainsi l'utilisation du Silicium (Si), de l'Arséniure de Gallium et/ou Silicium-Germanium (SiGe) sont devenus limitants pour certaines applications en puissance et/ou hautes fréquences.

Dans ce contexte, le nouveau millénaire a vu apparaître l'émergence des technologies grand gap au niveau des chaînes de production industrielle (fonderies). Les caractéristiques intrinsèques du nitrure de gallium (GaN) le placent naturellement dans la catégorie des matériaux adaptés aux applications de puissance à haute fréquence ; ce dernier bénéficiant d'une mobilité, d'une tension de seuil et d'une densité électronique élevée. La conductivité thermique du GaN favorise une dissipation efficace de la chaleur générée au sein du transistor actif. La vitesse de saturation élevée des électrons dans ce matériau permet aux dispositifs de fonctionner à des fréquences très élevées, renforçant ainsi leur utilité dans les applications à large bande passante et à haute fréquence. Ce matériau peut ainsi répondre à un vaste spectre applicatif.

Ce matériau GaN s'est avéré rapidement mature et exploitable dans le domaine de l'optique, puis de l'optoélectronique [2], avec la commercialisation de diodes électroluminescentes (DEL) proposant une forte efficacité lumineuse, une large gamme colorimétrique ainsi qu'une faible consommation.

Outre les domaines de l'optique, l'électronique s'est emparée de ce matériau dès la fin des années 80 (du siècle précédent). Pour des raisons de complexité des systèmes, les applications électroniques, en commutation ou en analogique RF, ont été plus tardives à percer vis-à-vis

des domaines optiques. Les premiers transistors ont été développés et commercialisés par des fonderies au début des années 2000, d'abord pour des applications analogiques HF, puis pour les dispositifs de puissance pour les applications de la conversion d'énergie.

Le nitrure de gallium joue désormais un rôle essentiel dans la transition écologique vers une mobilité électrique plus efficace et durable, en offrant des avantages significatifs en termes d'efficacité énergétique, de performances et de réduction des émissions. Il intervient notamment dans le secteur automobile que ce soit sur les véhicules électriques et hybrides par le biais de l'électronique de puissance. La maîtrise de substrat permettant une meilleure efficacité thermique [3] ainsi que la réduction des coûts de production pourrait également démocratiser son utilisation.

Concernant les applications de l'électronique hautes fréquences, de nombreux domaines se sont rapidement intéressés aux atouts que présente le GaN :

- Dans le domaine des télécommunications, les stations de bases tendent à multiplier les gammes de fréquences afin de permettre aux utilisateurs de profiter de services de plus en plus complets. Dans l'optique d'augmenter les débits, les nouvelles fréquences d'utilisation augmentent afin de favoriser la bande passante. La nécessité de sobriété énergétique étant plutôt opposée à la montée en fréquence, le rendement des systèmes opérants dans ces stations doit donc être maximisé, et le GaN apparaît comme un candidat idéal : ce choix a été renforcé par l'apparition d'un rendement en puissance ajoutée qui est optimisée proche des limites en puissance pour les transistors GaN réalisés, contrairement au constat que l'on peut faire sur les technologies traditionnelles à faible bande interdite. Le déploiement des réseaux 5G a donc accru la demande de composants RF haute performance, et le GaN est devenu essentiel pour les amplificateurs de puissance utilisés dans ces stations de base.

- Dans le domaine spatial, les voies d'émission souffrent des mêmes considérations avec des contraintes sur le rendement encore plus critique. Les amplificateurs de puissances (PA) GaN sont donc rapidement apparus comme le candidat idéal pour l'implémentation des chaînes d'émission. L'Europe a été pionnière dans cette aventure en envoyant les premiers amplificateurs de puissance GaN dans l'espace en 2013, avec le programme majeur du satellite PROBA-V dédié à l'observation de la biomasse (satellite en orbite basse). L'utilisation d'amplificateurs de puissance est désormais préférée aux technologies de type TWTA et solutions dérivées pour réaliser des constellations de satellites pour les communications haut débit (internet, constellations en orbite basse LEO)

- Dans le militaire, les architectures à base de nitrure de Gallium ont très rapidement été utilisées dans le cadre de la guerre électronique. Leur capacité à fournir des signaux de forte puissance servant aux technologies de brouillage, mais aussi aux systèmes radars devant opérer dans des conditions difficiles. L'aspect robuste offert par la large bande interdite étant un atout considérable dans un milieu hostile.

Si le GaN a donc vite trouvé sa place dans les chaînes d'émissions hautes fréquences embarquées, sa légitimité à être employé dans la chaîne de réception en tant qu'amplificateur faible bruit (LNA) a été plus longtemps controversée. Le LAAS et l'IEMN ont été parmi les

premiers à identifier ce potentiel orienté « récepteur » sur les technologies de Thales III-V Lab, au cours d'un projet Européen finalisé en 2003. Cependant, des performances en bruit moins bonnes que celles de ses concurrents directs, et notamment l'arséniure de gallium (GaAs), l'ont longtemps rendu inéligible. Deux atouts majeurs ont inversé cette tendance :

- En premier lieu, la montée en niveau TRL a permis de mieux préciser les performances des transistors pour les applications de puissance, mais également pour les applications faible bruit. La diminution des niveaux détectables en technologie GaN avec des filières commercialisées a changé l'image de cette technologie résolument considérée pour ses seules aptitudes en puissance. La maîtrise technologique a donc permis de faire converger les facteurs de bruit des technologies GaN au plus proche de ceux de ses rivaux, qui disposaient alors d'un niveau de maturité bien supérieur.

- La robustesse naturelle du matériau GaN permet de minimiser, voire de s'affranchir totalement des dispositifs de protection disposés en début de la chaîne de réception. Il est ainsi possible de revoir la topologie de principe des récepteurs sans affecter la détectivité globale du système ni la robustesse de ce dernier.

L'utilisation de technologie GaN en vue d'implémenter un LNA robuste est donc à présent chose commune. C'est dans ce contexte que s'inscrit cette thèse.

Le LAAS n'ayant jamais abandonné l'idée d'exploiter ces technologies pour de nouvelles générations de récepteurs robustes totalement intégrés MMIC, de nombreux projets ont continué à être développés en ce sens.

Le travail de thèse exposé dans ce manuscrit s'inscrit dans ce cheminement. Il propose pour la première fois une étude exhaustive des solutions topologiques à base de technologie GaN MMIC, jusqu'aux tests de robustesse pour valider les approches développées dans ce travail.

Le premier chapitre s'attache à contextualiser l'emploi de LNA robuste, et à dresser la liste des solutions implémentées dans les différents domaines afin de robustifier les architectures de réception.

Le deuxième chapitre expose la méthodologie déployée en vue d'implémenter un nouveau type de LNA robuste. Ce chapitre est fortement orienté sur la conception de circuit. Il propose une autre conception de LNA plus conventionnelle dans l'optique de présenter une étude comparative entre deux solutions concurrentes.

Le troisième chapitre s'attache à la caractérisation des différents LNAs implémentés sur la puce. Des mesures de performances statiques, en paramètres S bas-niveau, en facteur de bruit, et en régime fort niveau (non linéaire). Des stress par palier sont effectués dans le but de fournir une étude comparative la plus complète possible sur l'objectif de réaliser des LNAs robustes aux agressions électromagnétiques.

Le quatrième chapitre présente une nouvelle topologie de puce, en s'appuyant sur les résultats obtenus par le premier run. Il vise à développer une solution totalement intégrable, et propose également un mécanisme de protection supplémentaire lui-même intégré.

Une conclusion générale vient recenser les résultats majeurs de ce travail, et les perspectives générales en sus de celles développées en chapitre quatre.

## Bibliographie

- [1] G. E. Moore, « Cramming More Components Onto Integrated Circuits », *Proceedings of the IEEE*, vol. 86, n° 1, p. 82-85, janv. 1998, doi: 10.1109/JPROC.1998.658762.

- [2] I. Akasaki, H. Amano, et S. Nakamura, « The nobel prize in physics 2014 », 2014.

- [3] J. Achard *et al.*, « Thick boron doped diamond single crystals for high power electronics », *Diam Relat Mater*, vol. 20, n° 2, p. 145-152, févr. 2011, doi: 10.1016/j.diamond.2010.11.014.

## Chapitre 1 : Le rôle de l'amplificateur faible bruit dans une architecture de réception

## 1.1 Introduction

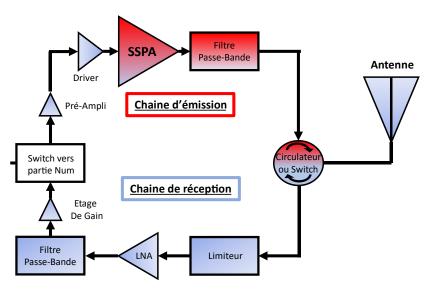

Un système de télécommunications ou de détection est communément constitué de deux voies (cf. Figure 1).

La première est dédiée à l'émission ; elle est constituée d'éléments permettant de fournir des niveaux importants de puissance radiofréquences (RF). Nous retrouvons ainsi les amplificateurs de puissance intégrés (SSPA, « Solid State Power Amplifier »), ils peuvent aussi être déclinés sous les terminaisons de PA (« Power Amplifier ») ou encore HPA (« High Power amplifier »). Ces amplificateurs présentent l'avantage de fournir de bon niveau de compacité ainsi qu'une masse relativement faible. Ils vont être capables de fournir des puissances de l'ordre de la centaine de Watts en fonction de la bande de fréquence visée. Si le cahier des charges nécessite des puissances d'émissions encore supérieures, l'utilisation de tubes à ondes progressives (TWT, « Traveling-Wave Tube ») peut alors s'avérer nécessaire. Ces derniers permettent de fournir des puissances de l'ordre de la dizaine de kilowatts pour des contraintes fréquentielles moins importantes. En revanche ces avantages se payent au niveau de la masse des dispositifs, points souvent limitants dans les applications de types systèmes embarqués. Au vu des niveaux de puissances mis en jeu, il est fréquent de retrouver sur la voie d'émission des dispositifs de filtrage afin de ne propager la puissance uniquement sur la bande de fréquence souhaitée. L'addition de dispositif sélectif en fréquence permet donc de ne pas venir perturber les systèmes annexes travaillant à des fréquences proches ou pouvant interférer avec les harmoniques générées par les fortes puissances mises en jeu.

La seconde branche d'un système télécom ou radar est dédiée à la réception; elle est constituée d'un l'amplificateur faible bruit plus communément appelé LNA (« Low Noise Amplifier »). Cet amplificateur constitue le premier étage actif de cette architecture de réception. Il est nominalement conçu pour recevoir des signaux RF de faibles amplitudes. L'objectif de ce dernier sera alors de rehausser le niveau du signal RF de sorte à le rendre interprétable (amplificateur) pour le reste de la chaîne de réception, tout en minimisant sa contribution au bruit total (faible bruit). Si l'aspect performance, lié à la formule de Friis des bilans de liaison d'une communication hertzienne permettrait de limiter le récepteur au seul LNA (et au filtre de fréquences placé en amont afin de respecter les critères d'allocations fréquentielles), les considérations opérationnelles telles que la protection face aux signaux potentiellement agressifs (intentionnels ou pas) doivent également être prise en considération. Ces systèmes de protection RF ayant pour but de protéger le LNA seront discutés plus tard dans le manuscrit. Comme pour la voie d'émission, un filtre peut également se trouver en amont du LNA comme évoqué précédemment : ce dernier permet de s'affranchir de signaux potentiellement nocifs en dehors de la bande de fréquence de travail.

Ces deux voies d'émission-réception sont reliées à une antenne via un circulateur ou un système de commutation (« RF switch »). Idéalement l'émission et la réception sont entièrement décorrélées de sorte qu'une voie ne puisse pas perturber l'autre : c'est potentiellement le cas de la voie d'émission vis-à-vis de la chaîne de réception. Il est également possible de trouver des systèmes à doubles antennes qui distinguent de fait les deux voies : l'émission et la réception se font alors via des canaux montant et descendant fréquentiellement distincts.

Figure 1 : Schéma bloc d'une architecture émission/réception

## 1.2 Rapport signal à bruit et facteur de bruit

L'élément principal permettant de différencier le LNA des autres amplificateurs, c'est sa nécessité de dégrader le moins possible le rapport signal à bruit (RSB) :

$$RSB = \frac{Signal\ utile}{\Sigma\ Bruit}$$

(1)

Ce rapport traduit la quantité de signal interprétable vis-à-vis du plancher de bruit. Il quantifie donc une information utile par rapport à son pendant « non utile » et irréductible : le bruit. Dès lors qu'un signal est émis, le rapport signal à bruit ne peut que se dégrader (à l'exception des systèmes utilisant des protocoles de redondance qui opèrent au détriment du débit d'une communication, comme le propose la société Sigfox). En effet chaque dispositif, qu'il soit passif ou actif, va venir ajouter sa contribution en bruit et ainsi détériorer le rapport signal à bruit global de l'architecture de réception.

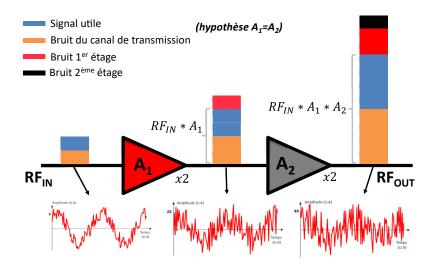

Figure 2 : Schéma de principe de la dégradation du rapport signal à bruit induit par deux étages amplificateurs identiques

La Figure 2 schématise l'influence de deux étages actifs identiques sur la dégradation du rapport signal à bruit global. Nous pouvons voir en sortie du premier étage que le signal utile a été amplifié, à l'instar du bruit présent sur le canal de transmission : en plus de cela le bruit généré par l'amplificateur vient dégrader le RSB disponible en sortie. Il est ainsi aisé d'observer en sortie du deuxième étage, la contribution majeure du bruit du premier étage sur le RSB global. Ce phénomène se réitère d'un étage sur le suivant, mais avec une contribution du bruit propre des étages suivants amoindrie par l'amplification de l'étage précédent : c'est ce que traduit une autre formule de Friis sur le bruit d'une chaîne d'amplificateurs. La prédominance sur le RSB des étages situés proche de l'antenne vient justifier la nécessité de concevoir des amplificateurs dont le facteur de mérite à l'ordre 1 est le bruit. [1], au même titre que l'amplification – justifiant de fait l'appellation spécifique de cet « amplificateur faible bruit ». Nous passons ainsi d'un signal interprétable en entrée à un signal « noyé » dans le bruit en sortie. L'influence des dispositifs actifs n'est donc prise en compte qu'après que le signal ne les ai traversé. De plus, il est dépendant de leur emplacement dans la chaîne de réception, il est donc nécessaire de mettre en place une métrique qui traduit la dégradation du RSB uniquement induite par l'amplificateur en question. Le facteur de bruit, noté F permet ainsi de juger de l'impact d'un dispositif actif (ou non) et ceux de manière décorrélée du gain et du niveau de signal d'entrée :

$$F = \frac{RSB_{in}}{RSB_{out}} \tag{2}$$

De manière plus commune, le facteur de bruit est employé sur une échelle logarithmique, il est ainsi écrit NF lorsqu'il est en dB et F quand il est en valeur naturelle. Il est intéressant de remarquer que, contrairement aux autres facteurs de mérite tels que les gain-atténuation des autres dispositifs électroniques, le facteur de bruit traduit un rapport signal à bruit en entrée, relativement à celui de sortie (bruit ramené en entrée). Ceci est dû à l'utilisation pratique de ce paramètre. Il est pertinent d'analyser le bruit critique acceptable en entrée de l'amplificateur, afin de le confronter à celui incident sur cet amplificateur, afin de définir les

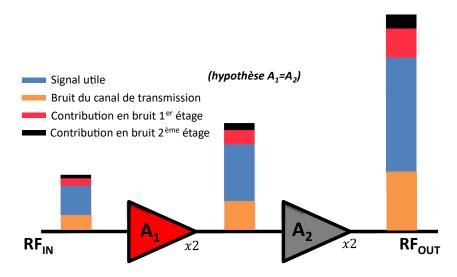

marges des signaux RF et les types de modulations qui peuvent être utilisées. De plus, les bilans de liaisons s'opèrent entre l'antenne et la partie électronique afin d'également prendre en compte le bruit propre de l'antenne sous une forme de température de bruit que l'on peut transposer en facteur de bruit. C'est à cette interface que la qualité d'une liaison, c'est-à-dire sa capacité à répondre à sa mission de transmission des données, se détermine. Ce niveau de bruit, irréductible, permet de fixer le niveau de puissance devant être émis pour satisfaire le bilan de liaison HF, ou encore la portée de cette liaison. Cette représentation, telle qu'illustrée en Figure 3, est conforme à la manière d'appréhender le bruit dans les systèmes de réception électronique, avec les contributions en bruit de chaque étage ramené en entrée du LNA : sur cette figure, le bruit incident sur l'amplificateur (antenne et bruit externe) est également représenté pour quantifier visuellement le rapport signal à bruit.

Figure 3 : Représentation du facteur de bruit dans une architecture de réception composée par deux étages amplificateurs identiques

La formule de FRIIS permet ainsi de pointer l'influence accrue des étages situés en amont de la chaîne de réception, le facteur de pondération d'un étage par rapport à l'autre étant son gain (G) :

$$F = F_1 + \frac{F_2 - 1}{G_1} + \frac{F_3 - 1}{G_1 G_2} + \dots + \frac{F_n - 1}{G_1 G_2 \dots G_{n-1}}$$

(3)

Dans cette formule, l'indice est relatif à l'étage d'amplification : chaque étage étant adapté en entrée et en sortie sous la même impédance caractéristique. Les facteurs de bruit F<sub>i</sub> et les gains G<sub>i</sub> sont évidemment exprimés en valeurs naturelles. Cette formule s'applique à l'échelle du système, mais également au niveau de chaque étage ainsi qu'au niveau du composant, il sera ainsi plus important de minimiser le facteur de bruit avant la zone d'amplification. C'est également pour cela que l'adaptation en bruit d'un transistor est plus critique en entrée du composant. On retrouvera ainsi des éléments passifs bruités dont il faudra minimiser l'impact, surtout en tête d'architecture de réception (câble de connexion antenne-récepteur, pertes du filtre RF, pertes du limiteur de puissance si présent) ; pour les éléments passifs, le facteur de

bruit est obtenu de façon plus directe, puisqu'il correspond aux pertes de l'élément à la température ambiante.

## 1.3 Agressions électromagnétiques

## 1.3.1 Sensibilité des architectures de réception

Comme évoqué en introduction, un LNA est nominalement conçu pour recevoir des signaux de faibles puissances après atténuation lors de leur propagation en espace libre. Cependant, comme exposé sur la Figure 4, cet amplificateur peut être confronté à des puissances plus importantes de manière inopinée.

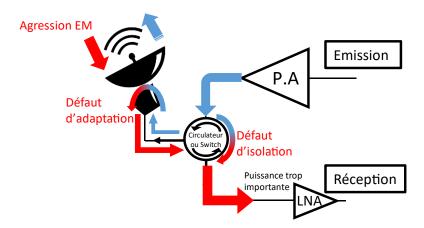

Figure 4 : Schéma d'architecture émission/réception contenant les diverses sources pouvant générer un une forte puissance RF sur le LNA

Plusieurs phénomènes peuvent ainsi exposer le LNA à des amplitudes RF importantes :

Défaut d'isolation du circulateur. L'utilisation d'un circulateur venant faire la jonction entre émission, réception et antenne peut s'avérer opportune dans certaines situations. En effet, ce dernier est purement passif et ne nécessite pas de système de commande permettant de faire passer le signal sur une voie ou sur une autre. Il permet également de minimiser les pertes d'insertion et dans un cas nominal fournit une très bonne isolation. Cependant un choc mécanique, un champ magnétique, une puissance ou une température trop élevée peuvent entraîner une désaimantation du circulateur. Les voies n'étant pas spatialement décorrélées, le chemin dédié à l'émission se retrouve lié au LNA. De manière nominale, l'isolation peut s'avérer insuffisante pour éviter un couplage significatif de la voie d'émission sur celle de réception. Indépendamment du signal, le bruit large bande de l'amplificateur de puissance, généralement élevé, peut dégrader sensiblement la détectivité en entrée du LNA. L'utilisation d'un switch peut alors s'avérer être une meilleure option, néanmoins cela induit une complexification du système, car la mise en place d'une commande est nécessaire pour synchroniser les signaux d'émission et de réception. Cette commande est aussi susceptible de se dégrader et de rendre le système inopérant. Le switch induit aussi des temps de commutation qui peuvent favoriser l'utilisation d'autres systèmes.

L'étude système permet d'appréhender l'ensemble de ces contraintes et de définir l'élément le plus à même pour réaliser la redirection des signaux d'émission et de réception.

- Défaut d'adaptation de l'antenne. L'amplificateur transmet à l'antenne une forte puissance afin que cette dernière soit émise; idéalement l'antenne devrait être parfaitement adaptée au reste du système et n'induirait donc pas de réflexion. De par leur conception, les antennes proposent un taux d'onde stationnaire non unitaire qui provoque ainsi un retour de puissance vers le module d'émission-réception, et donc, dans certains cas, vers le LNA. Les contraintes mécanique et thermique peuvent également causer une dégradation de cette adaptation.

- Agression électromagnétique (EM). Qu'elle soit volontaire ou non, une agression électromagnétique fait parvenir à l'antenne, et par extension au LNA, un signal dont l'amplitude est supérieure à celle prévue nominalement. Cela peut brouiller le signal utile et de fait le rendre inexploitable, mais pour des niveaux de puissance anormalement élevés, cela peut détruire le récepteur.

#### 1.3.2 La guerre électronique

Ils existent plusieurs types d'agression EM potentielle, tout d'abord celles provoquées par des phénomènes naturels, tels que les tempêtes solaires et les décharges électrostatiques causées par la foudre. Ces dernières tendent à impacter les appareils dans une gamme de fréquences très large et dans des proportions variables en fonction de leur niveau d'action ; cela dépend fortement de la distance entre le système et l'événement.

Il y a également d'autres agressions EM involontaires, mais dont l'origine est humaine. Elles sont des à la « pollution » du spectre électromagnétique par l'activité humaine. Peuvent alors intervenir des phénomènes comme des interférences dues à la réception de signaux non destinés à la cible. Néanmoins ce genre d'évènement se veut assez rare à grande échelle si la réglementation stricte de chaque pays, région et continent est respectée. Des instances internationales comme l'UIT (« Union Internationale des Télécommunications ») ou les normes IEEE mises en place dans l'objectif de garantir une compatibilité EM entre les appareils permettent d'établir les gabarits des systèmes selon leurs gammes de fréquences respectives, et de dimensionner les Émetteurs-Récepteurs en conséquence.

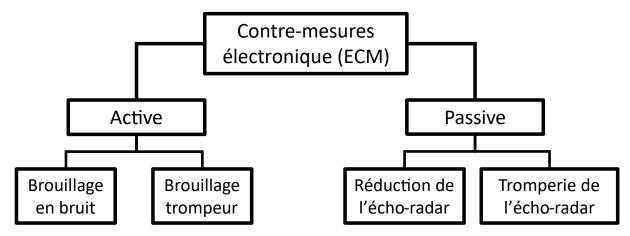

Enfin le dernier type d'agression EM possible est volontaire : il s'agit de techniques employées dans le cadre de la guerre électronique (EW – « Electronic Warfare »). La catégorie des attaques électronique (EA – « Electronic Attack ») se scinde en trois parties :

- Les contre-mesures électroniques (ECM « Electronic CounterMeasures »): elles comprennent différents types de brouillages dont l'objectif est de mettre en erreur totale ou partielle le système de détection.

- Les armes à énergies dirigées (**DEW** « Directed-Energy Weapons ») : elles visent à détruire le système de détection à l'aide de faisceau EM puissant. En l'absence de redondance de système, le récepteur est mis hors d'usage.

Les missiles anti-rayonnement (ARM – « AntiRadiation Missiles ») : ils sont destinés à réaliser une attaque physique à l'aide de missiles sur les sites comportant les systèmes de détection. L'ensemble du système est totalement détruit, ce qui pose de nombreux problèmes en situation spatiale pour tous les opérateurs de satellites, dans la gestion des déchets et de leur action potentielle et non contrôlable sur les satellites en opération. Des effets en cascade peuvent être la conséquence collatérale de l'utilisation d'un tel système et ces options sont à haut risque pour toutes les nations en capacité de l'utiliser.

#### Les contre-mesures électroniques (ECM)

Il existe différents types de contre-mesures, les principales grandes catégories sont reportées sur la Figure 5. Ces dernières peuvent être opérées de manière active ou passive.

Figure 5 : Catégorisation des contre-mesures électroniques

Dans le cadre d'un brouillage actif, il est possible d'induire le système de détection en erreur de deux manières différentes. Le brouillage en bruit (ou « Noise Jamming ») consiste à émettre un signal bruité (non-déterministe pour le détecteur), visant à noyer l'information utile reçue par un système de détection. L'approche logicielle est ici minimisée, et connaître la position exacte de l'appareil n'est pas une nécessité absolue.

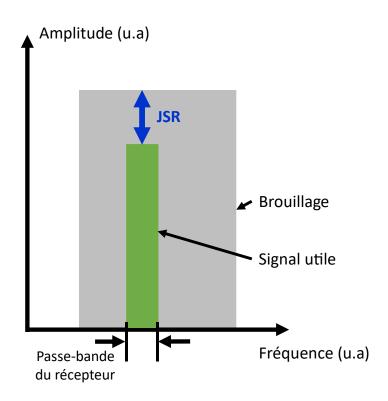

Le but du brouilleur est alors de relever le plancher de bruit de l'appareil de sorte que le rapport du signal utile vis-à-vis du brouillage soit défavorable pour le détecteur (nous parlons dans ce cas de JSR pour « Jamming to Signal Ratio » [cf. Figure 6]).

Figure 6 : Illustration du JSR (« jamming to signal ratio ») qui est le rapport des deux puissances reçues (signal utile et brouillage) dans la bande de fréquence du récepteur. Adapté de [2]

De façon effective, ce brouillage s'effectue via une série de pulses aléatoires où chaque train d'impulsion possède une amplitude et une phase différentes du précédent de sorte à balayer les canaux utilisables par la cible. Le brouillage est considéré comme effectif si le JSR est au moins supérieur à 0 dB relativement au signal utile à perturber ; le récepteur capte alors un niveau de bruit élevé et n'arrive pas extraire l'information utile de ce dernier. Un niveau entre 0 dB et 40 dB est en général requis en fonction du type de modulation et du type de brouillage. L'un des avantages de cette méthode est qu'il est possible d'effectuer un brouillage de zone et donc d'aveugler plusieurs récepteurs simultanément. Dans le même temps, la fréquence à laquelle opère le radar n'est pas connue, un compromis va donc être recherché entre la bande de fréquence sur laquelle est opéré le brouillage et le niveau de brouillage visé. En effet, au plus la diffusion d'un signal bruité se fera sur bande étroite, au plus l'énergie sera concentrée dans ce domaine fréquentiel. Malgré cela, il est toujours possible pour l'opérateur radar de décaler la fréquence de fonctionnement. De fait, la stratégie consistant à viser une bande de fréquence trop étroite devient risquée. Une solution intermédiaire consiste à effectuer un balayage en fréquence. Cela permet d'être sûr d'avoir un JSR élevé, au moins de manière sporadique. Ce genre de mode opératoire permet d'éviter les ciblages automatiques (en dehors de toute intervention de type intelligence artificielle) et nécessite donc la mobilisation d'un opérateur radar. [2], [3]

Plusieurs paramètres vont également venir pondérer les niveaux de signal utile et de bruit au niveau de l'antenne. Nous retrouvons parmi eux :

#### Côté brouilleur:

- La puissance du brouilleur

- Le gain de l'antenne du brouilleur (dépendant de sa directivité et de son dépointage)

- La distance entre le brouilleur et le récepteur (qu'il soit embarqué ou non, le signal émis par le brouilleur ne parcourt qu'une seule fois la distance séparant les deux éléments Radar-Cible)

#### - Côté Radar

- La puissance du radar

- Le gain de son antenne (a priori maximisé par le fait qu'elle pointe dans la direction de la cible)

- La distance entre le radar et la cible (le signal doit parcourir deux fois cette distance)

- La section radar de la cible (définissant la puissance de l'écho radar renvoyé en chemin retour)

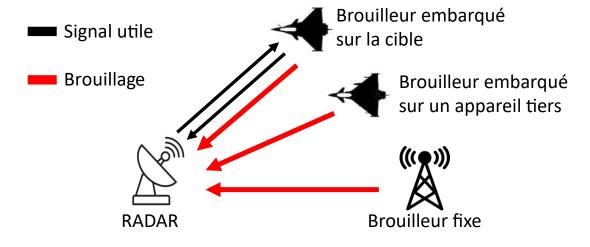

Ces paramètres permettent d'introduire le concept de zone de détection (« Burn-Through ») dans laquelle le signal utile au radar sera plus important que le signal du brouilleur. La zone de détectivité est située au plus proche du radar et son diamètre d'action dépend des paramètres cités ci-dessus. Il est également situationnel, puisque, comme l'illustre la Figure 7, le brouillage peut être effectué à partir d'un point fixe, un appareil mobile ou depuis la cible elle-même. La puissance du signal perturbateur sera alors variable ou non, dépendant également de la directivité de l'antenne de réception et de celle du brouilleur. Le facteur de bruit du récepteur rentre aussi en compte, car il permettra, ou non de détecter un signal qui s'extrait à peine du plancher de bruit.

Figure 7 : Différents supports à partir desquels un brouillage RADAR peut s'opérer

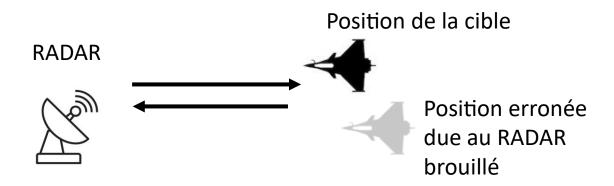

L'autre type de brouillage actif qu'un récepteur peut subir est un brouillage trompeur (« Deceptive jamming »), son rôle est d'interférer avec le signal utile capté par le radar dans le but d'induire de fausses informations, qu'elle soit relative à la position ou à la vitesse de la cible. Les techniques employées dans le cadre de la Figure 8 peuvent être nombreuses, mais

nécessitent une approche software aussi bien dans mise en œuvre que dans la façon de déjouer ces contre-mesures.

Figure 8 : Brouillage trompeur

Les contre-mesures peuvent également être passives, elles peuvent alors viser à réduire l'écho radar à l'aide de solutions chimiques qui dégradent fortement le bilan de liaison (pertes additives provoquées par nuage de fumée ou aérosol). Elles peuvent également servir à renvoyer une multitude d'échos, le récepteur ne pouvant plus différencier les uns des autres. Cette technique du « chaff » fut l'une des premières employées ; elle consiste à disposer à intervalles réguliers des bandes de matières EM réfléchissantes. L'espacement entre ces dernières est optimisé de sorte à créer de multiples renvois pour une gamme de fréquences donnée. Enfin les derniers types de contre-mesures passives sont les leurres, ils consistent à imiter la signature infrarouge et/ou visuelle de l'appareil. [4]

#### Les armes à énergies dirigées (DEW)

Les armes à énergies dirigées incluent les lasers à forte énergie ainsi que les armes microondes à forte puissance. Côté hyperfréquence, l'objectif de tels dispositifs est de saturer voire même de détruire les appareils électroniques embarqués par les cibles, le premier à en subir les conséquences étant le LNA. Ces armes permettent d'atteindre leurs cibles de manière quasi certaine, car la puissance EM destructive est envoyée à la vitesse de la lumière dans un faisceau assez large. Le cadre de cette thèse aborde essentiellement ce type d'agression, en plus des agressions non intentionnelles dont les effets peuvent être identiques, quoique dans des proportions moins sévères.

#### Les missiles anti-rayonnement (ARM)

Missiles ayant pour objectif de détruire les systèmes radars sols. Les sites de détection émettant par définition des ondes EM, les missiles se focalisent sur ces rayonnements. Ils représentent un aspect important de la guerre électronique, mais sont quelque peu hors sujet ici. [5]

#### 1.3.3 Les contres contre-mesures

Comme nous avons pu le voir dans la partie précédente, les techniques de brouillage sont nombreuses et diversifiées. Il n'existe pas de dispositif de protection adapté à tous les types d'attaques. Nous distinguons ainsi deux types d'attaques, la première ayant pour but d'aveugler, voire même d'endommager le récepteur en envoyant un signal de trop forte intensité (« jamming »), la seconde visant à tromper la cible en lui envoyant de fausses informations (« spoofing »). Deux contre-mesures vont respectivement pouvoir s'appliquer à ces différents scénarios.

- « Hardware » : Vise à rendre le système robuste aux agressions EM, permettant ainsi au récepteur de ne pas être détruit ou endommagé par des signaux de fortes puissances. Dans l'idéal, le récepteur continue à avoir un fonctionnement en régime nominal (mode linéaire) de sorte que le système reste opérant pendant l'attaque. Nos travaux rentrent dans ce cadre de contre-mesures, ou systèmes de protection « hardware ».

- « Software » : Consiste à développer des algorithmes permettant la détection de signaux erronés ainsi que leurs filtrages ; l'objectif étant de continuer à traiter les informations renvoyées par le signal utile ou a minima d'informer l'utilisateur du système que les données affichées sont peut-être corrompues. L'approche logicielle est une part non négligeable des travaux visant à rendre les systèmes de détection robustes. Si elle est essentielle et fortement complémentaire à nos travaux, elle ne sera pas abordée dans ce manuscrit.

Ce manuscrit sera donc axé autour des solutions matérielles pouvant être mises en place pour protéger un LNA, et par extension l'intégralité de l'architecture de réception contre des amplitudes de signaux pouvant nuire à l'intégrité du système.

#### 1.3.4 Applications pour LNAs robustes

La conception de LNA robuste semble ainsi apparaître comme une nécessité dans de nombreux domaines. En raison des agressions volontaires qu'elles sont susceptibles de subir dans un spectre fréquentiel et applicatif très large, les applications militaires sont concernées par ce besoin (cf. Figure 9). Cela concerne aussi bien les équipements embarqués (véhicules sol, air, mer, fantassins), fixes sols ou satellites.

Dans les autres applications concernées, nous retrouvons également les satellites de télécommunication. À mi-chemin entre militaire et civil, ces derniers représentent un enjeu économique incontournable de l'époque contemporaine, et peuvent faire l'objet d'agression volontaire comme involontaire (parmi lesquelles nous pourrions citer les erreurs de dépointage par exemple). En addition de cela, tout système embarqué et plus particulièrement dans le domaine spatial se voit dans l'obligation d'intégrer des systèmes fiables en raison de l'impossibilité de réparation et du coût inhérent au remplacement d'un tel système. En effet, même si des systèmes de redondance sont prévus, le satellite sera inopérant une fois ces systèmes de secours épuisés. Là encore, la notion de protection vient

renforcer le caractère opérationnel des satellites afin d'éviter une sur sollicitation des modules de redondance qui ont été dimensionnés et intégrés sur une base de défaillance sur le long terme (FIT, failure in time, traduite en durée de vie MTTF mean time to failure).

Les satellites peuvent être dédiés à d'autres utilisations, par exemple l'observation terrestre. Nous retrouvons dans cette catégorie les radars à ouverture synthétique (SAR – « Synthetic Aperture Radar »). Ces derniers permettent une ouverture d'antenne plus grande que ce qu'autorise la conception par une prise en compte de la variation de phase liée au mouvement du satellite et par un traitement de données approprié. Ils favorisent des observations à différents niveaux de précision en fonction de la bande de fréquence dans laquelle ils opèrent. De la bande L à C (1- GHz), le SAR sera dédié à la typographie du sol ainsi qu'à l'observation de zones larges comme l'observation des forêts (zones de déforestation). En bande X-Ku, il est possible d'observer les mouvements de terrain et glaciers, et les phénomènes météorologiques. À partir de la bande Ka, l'observation de petites cibles devient possible (bâtiments, véhicules, cours d'eau, etc...).

Un graphique des applications principales est reporté, avec les bandes de fréquences allouées, en Figure 8.

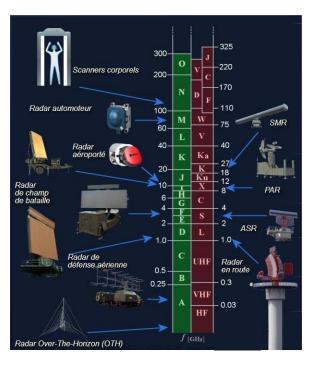

Figure 9 : Applications militaires des systèmes radars dans les différentes bandes de fréquences [6]

Les AESA (« Active Electronic Scanned Array »), sont un type d'antenne active. Elles sont basées sur des modules émetteurs-récepteurs individuels (propre à chaque élément rayonnant). Les éléments rayonnants fonctionnent en réseau d'antennes. Les AESA sont employées dans les radars d'avion de combat et sont donc particulièrement sujettes à tous types d'agression. Elles sont fortement mises à profit dans le cadre de la guerre électronique, car elles permettent un balayage rapide couplé à une bonne directivité ; en revanche, dans l'optique de rester opérantes, elles se doivent donc d'être robustes. [7]

## 1.4 Technologie Nitrure de Gallium

## 1.4.1 Champs applicatifs

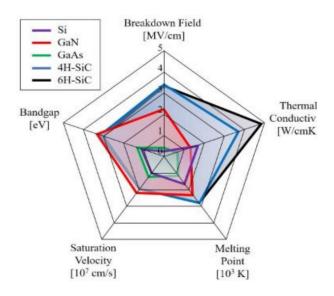

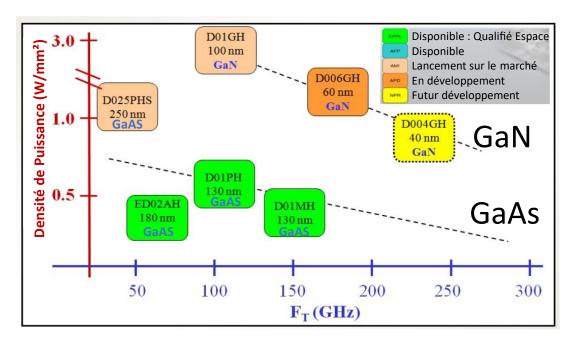

Comme nous l'avons vu, le champ applicatif pour les LNAs robustes est assez large. Cependant, dans l'optique de concevoir de tels amplificateurs, il est important de choisir une technologie capable de fournir des performances cohérentes avec ce que requiert le cahier des charges. Pour ce faire la technologie Nitrure de Gallium (GaN) semble cocher toutes les cases (cf. Figure 10). En effet, sa large bande interdite ainsi que sa forte tension de claquage permet de fonctionner à des niveaux de puissance supérieurs à ceux des concurrents directs basés sur les technologies Silicium-Germanium (SiGe) et Arséniure de Gallium (GaAs). Il possède également une haute mobilité électronique qui couplé à un gaz d'électron bidimensionnel (dispositif à hétérojonction - HEMT) lui permettent des fonctionnements à plus haute fréquence que les semiconducteurs dédiés à la puissance tels que le Carbure de Silicium (4H-SiC ou 6H-SiC).

Figure 10 : Comparatif Si, GaN, GaAs et SiC

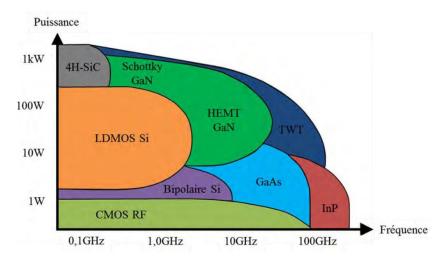

Comme il est possible de le voir sur la Figure 10, le GaN possède donc tous les prérequis pour des applications forte puissance à haute fréquence [8]. La Figure 11 montre qu'il apparaît ainsi comme un candidat idéal pour les applications de LNA robuste dans une gamme fréquentielle assez large allant de quelques centaines de Mégahertz à la cinquantaine de Gigahertz. Pour de telles applications, ses concurrents historiques directs sont le SiGe et le GaAs. Encore aujourd'hui ce sont ces deux technologies qui sont majoritairement utilisées dans le domaine spatial, avec une spécialisation selon les fonctions HF. Cela est attribué à un niveau de maturité supérieur, garantissant des composants moins dispersifs et dont les mécanismes de dégradation sont identifiés et quantifiés de manière plus précise. Ainsi le maintien de ces technologies est probablement dû à une certaine forme d'héritage, mais pas seulement. En effet, les performances en bruit de l'Arséniure de Gallium sont, encore aujourd'hui, intrinsèquement meilleures en bruit HF et rien ne garantit que les verrous technologiques

franchis pour ce matériau le soient également pour le GaN. De plus, la mobilité électronique du GaAs étant supérieure à celle du GaN, les applications comprises entre 50 GHz et 100 GHz les laissent en position d'avantage . Pour des fréquences de fonctionnement encore supérieures, le Phosphure d'Indium (InP) sera la technologie la plus adaptée pour tendre vers des applications Térahertz.

Coté puissance, ce sont les dispositifs SiC qui seront préférés pour les modules de commutation forte puissance même si les technologies GaN tendent à améliorer de manière significative leurs performances, et rentrent également dans la compétition.

Il apparaît alors que le GaN est un candidat idéal pour des applications à fort niveau RF tel que les PAs. Mais quid des applications faible bruit ?

Figure 11: Performances en puissance des différentes technologies de semi-conducteur en fonction de la fréquence [9]

## 1.4.2 Technologie faible bruit

La mobilité électronique quantifie la vitesse à laquelle les électrons peuvent traverser le matériau sous un champ électrique ; elle décide en partie de l'éligibilité d'un matériau pour des applications RF [10]. Concernant les dispositifs faible bruit, cette condition, nécessaire au niveau matériau, n'est pas suffisante au niveau dispositif actif : à l'échelle du transistor, d'autres facteurs vont intervenir dans la décision. Parmi eux, la corrélation entre pic de transconductance ( $G_m$ ) et le courant dans le canal ( $I_{DS}$ ) qui lui est associé permettent de mettre en évidence un avantage pour les transistors HEMT GaN par rapport aux transistors HEMT GaAs qui représentent actuellement la solution privilégiée pour les applications les plus performantes. Le pic de transconductance dans un régime statique équivaut à la zone où le gain RF sera le plus favorable. Bien sûr cette considération statique est à pondérer relativement à la fonction dynamique, et peut varier en fonction des circuits d'adaptation qui seront placés autour du transistor (en entrée et en sortie). Il est tout de même possible d'observer que ce maximum de transconductance intervient dans une zone où le courant de drain est relativement faible vis-à-vis du courant de saturation du composant pour le GaN ( $I_{DS}=I_{DSS}/5$ ) [11]. Le bruit généré par le courant statique reste raisonnable (environ 2 à 3 fois

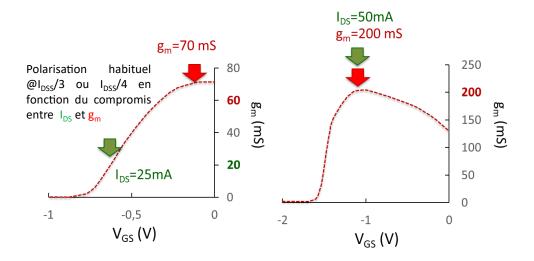

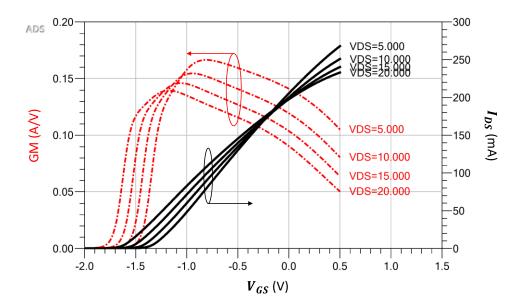

plus élevé que pour les solutions GaAs pour un transistor de dimension équivalente, polarisé à son optimum en bruit HF), tandis que l'effet d'une transconductance plus élevée (4 à 10 fois supérieure à celle du GaAs) vient contrebalancer ce constat. Ceci est lié au fait que les technologies GaAs voient leur pic de transconductance décalé par rapport à la zone de faible courant I<sub>DS</sub>, ce qui contraint le concepteur à un compromis plus important quant aux choix de la polarisation statique pour un équilibre entre maximisation du gain (g<sub>m</sub>) et minimisation du bruit de canal (I<sub>DS</sub>). Ce phénomène est illustré sur la figure 11 pour deux technologies de chez OMMIC; les technologies ED02AH (HEMT GaAs) et D01GH (HEMT GaN sur Si) sont comparées pour une même dimension de composant.

Figure 12 : évolution de la transconductance statique  $G_M$  et du courant de drain statique  $I_{DS}$  en fonction de la tension de grille ( $V_{GS}$ ) pour un transistor HEMT de 6 doigts de grille de largeur individuelle 40 $\mu$ m polarisé à  $V_{DS}$ =5V, selon les technologies OMMIC GaAs ED02AH en figure de gauche (longueur de grille 200 nm) et OMMIC GaN D01GH en figure de droite (longueur de grille 100 nm) [12]

Les profils de gain de transconductance montrent que pour la polarisation optimale en bruit en filière ED02AH, le gain de transconductance n'est que de 20mS, avec un courant de drain  $I_{DS}$  de 25mA. Malgré une dégradation du bruit liée à une multiplication par deux du courant de drain pour la technologie D01GH, le gain de transconductance est multiplié par dix ! les équations de bruit ci-après démontrent l'impact de chacun de ces deux paramètres statiques sur les facteurs de mérite des transistors.

Malgré cela, dues à un niveau de maturité supérieur, les technologies GaAs permettent encore aujourd'hui d'obtenir des facteurs de bruits inférieurs aux dispositifs GaN dans une bande de fréquence équivalente. Le choix de la technologie est donc encore soumis à débat pour des fréquences allant jusqu'à 50 GHz.

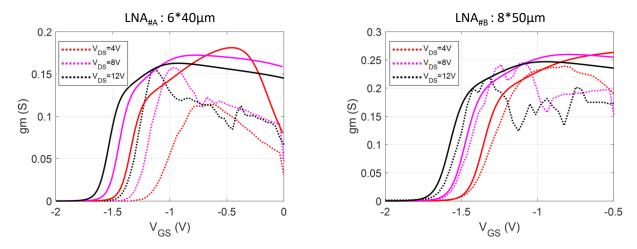

Figure 13 : Corrélation entre  $G_M$  et  $I_{DS}$  en fonction de la tension de grille ( $V_{GS}$ ) pour différentes tensions de drain ( $V_{DS}$ ) pour un transistor HEMT GaN en technologie D01GH (4\*50 $\mu$ m)

Selon certains modèles, et comme démontré dans [13], seul de la transconductance influe sur le facteur de bruit minimal  $(F_{min})$  comme en atteste l'équation (4).

$$F_{min} = 1 + 2\sqrt{P} * \frac{f}{f_c} * \sqrt{g_m * (R_s + R_g)}$$

(4)

Où Rs et Rg sont respectivement les résistances de source et de drain. Le facteur P étant un paramètre de bruit définit par l'équation (5), où  $\delta id^2$  est le carré du bruit du courant de drain sur une bande de fréquence  $\Delta f$ .

$$\overline{\delta\iota d^2} = 4KT_0 * g_m * P * \Delta f \tag{5}$$

Dans [14], l'auteur démontre la relation entre P et le courant statique I<sub>DS</sub> via l'équation (6):

$$P = \frac{I_{DS}}{E_c * L_g * g_m} \tag{6}$$

Dans cette expression,  $E_C$  correspond au champ électrique critique et  $L_g$  à la longueur de grille. Il est ainsi possible de relier l'impact du courant de drain au facteur de bruit minimum ( $F_{min}$ ) via (7).

$$F_{min} = 1 + 2 * \sqrt{\frac{I_{DS}}{E_c * L_g} * \frac{f}{f_c} * \sqrt{(R_s + R_g)}}$$

(7)

Ainsi, en faisant d'une pierre deux coups, le GaN permet de façon simultanée de choisir une polarisation nominalement faible bruit en octroyant la possibilité d'avoir un bon  $g_m$  avec un courant de canal relativement faible.

Ces équations restent très utiles pour apprécier l'impact des différents éléments électriques et des polarisations, elles permettent ainsi la sélection optimale du composant. Bien entendu, lors de la phase de conception sur la technologie retenue, les modèles électriques et en bruit sont déjà intégrés dans le kit de conception.

## 1.4.3 Technologie utilisée : OMMIC-D01GH

La technologie utilisée durant ces travaux de thèse est la D01GH de OMMIC (devenu MACOM-France depuis janvier 2023). Il s'agit d'un process GaN sur Silicium avec des longueurs de grille de 100 nm. Il est à noter que la technologie offre la possibilité d'incorporer des transistors avec des longueurs de grille plus petites (60 nm) sur le même wafer. Afin de sécuriser notre preuve de concept topologique, nous avons décidé d'orienter notre étude sur une longueur de grille de 100 nm, même si des LNAs ont également été simulés avec la longueur de grille de 60 nm.

Les performances principales annoncées par le fondeur sont reportées sont évolutives, en 2020-2021, soit au moment de la conception et de l'envoi du run, la technologie D0XGH avait les performances suivantes [15]:

Fréquence de transition : 110 GHz.

- Tension de claquage : 36V.

- Densité de puissance : 4W/mm² pour le procédé 100nm.

Transconductance extrinsèque : >800mS/mm

Densité de courant : >1.2A/mm

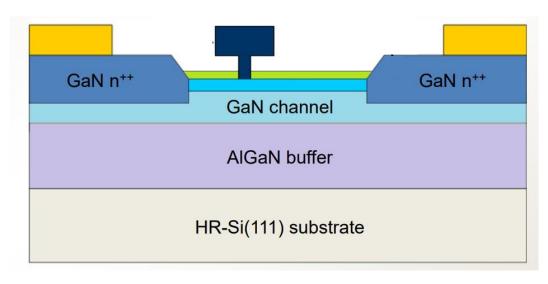

L'épitaxie générale des transistors de la technologie D01GH aboutit à un composant dont la figure de coupe est proposée sur la Figure 14. Nous y retrouvons plusieurs points importants :

Figure 14 : Structure épitaxiale de la technologie D01GH [16].

- Une couche de passivation in situ (vert). Elle permet de réduire l'impact des défauts de surface sur les porteurs de charges en les séparant physiquement. Ces défauts

génèrent des niveaux d'énergie supplémentaire ce qui entraîne le piégeage et la libération de pair électrons/trous. Ainsi la passivation permet de prévenir contre les effets de piège et l'effet mémoire généralement relevés sur les mesures de retard à la commande (gate/drain lag). La technologie devient plus reproductible avec des performances stables dans le temps. En plus de cela, la couche de passivation permet d'éviter les phénomènes d'oxydation.

- Une barrière AIN (bleu). Elle permet de réduire les effets de canal court en confinant les porteurs de charges dans le canal et empêchant le déplacement vertical de ces derniers. Elle permet également de réduire les courants de fuites vers la grille en isolant cette dernière du canal 2DEG.

- Une faible longueur de grille (100 nm) permettant la montée en fréquence de la technologie.

- Un faible espacement grille-source (250 nm). Permet également de travailler à plus hautes fréquences en réduisant certaines capacités parasites. L'augmentation de la distance grille-drain permet aussi de supporter des champs électriques plus importants, et ainsi d'augmenter la tension de claquage du transistor.

- La reprise des contacts ohmiques, à l'aide de GaN dopé n+.

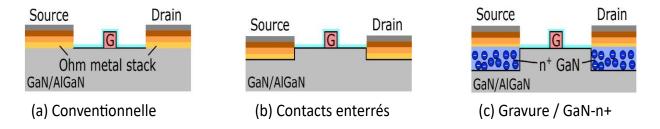

De manière traditionnelle, les contacts se font via un empilement de couches métalliques Ti/Al/Ni/Au depuis le substrat GaN (cf. Figure 15.a). Cependant en plus des différentes interfaces métalliques, les porteurs doivent franchir la barrière AlN. La seconde option, présente sur la Figure 15.b, consiste à diminuer l'épaisseur de la barrière (voir à la retirer totalement) à l'endroit où sont positionnés les contacts de sorte à favoriser la conduction des porteurs. La technologie D01GH vient relier directement les contacts ohmiques au gaz bi dimensionnel (2-DEG) à l'aide d'une gravure et d'un GaN dopé n (cf. Figure 15.c) [17]. Cette procédure a pour objectif de minimiser les résistances parasites d'accès [18], [19]. Les contacts sont quant à eux en or, les résistances de contacts sont ainsi diminuées: la résistance de contact R<sub>C</sub> et la résistance de canal R<sub>ON</sub> sont données inférieures à 0.1 Ω.mm [16]

- La couche AlGaN « back barrier » (violet). Elle permet également d'éviter certains phénomènes de pièges ainsi que des courants de fuite dans le substrat, en confinant les électrons dans le canal. Cependant le rôle principal de cette « back barrier » est de servir d'étage tampon entre le GaN est le substrat silicium. En effet, il existe un désaccord de maille de 17% entre le GaN et le silicium (dans sa configuration cristalline « 111 »). Ces deux matériaux n'ayant pas une bonne compatibilité naturelle, la mise en place d'un étage tampon en AlGaN permet d'atténuer le désaccord de maille en augmentant progressivement le taux d'aluminium de la « back barrier ».

Figure 15 : Différentes solutions pour faire des contacts ohmiques pour transistor HEMT GaN [20]

## 1.4.4 Quel substrat pour le GaN?

Dans la technologie D01GH, le choix du substrat s'est porté sur le Silicium. Si ce dernier présente le désavantage d'un désaccord de maille important avec le GaN, il octroie cependant de nombreux avantages, dont celui du coût fortement réduit par rapport à ses concurrents directs que sont le carbure de silicium et le diamant. Cela permet des productions à plus grande échelle, sur des wafers de diamètres supérieurs. En plus de cela, les technologies Si sont les technologies à base de matériau semiconducteur les plus matures. Cela entraîne un meilleur contrôle des procédés de fabrication, et ainsi des performances et une reproductibilité accrue. Enfin, le substrat Silicium permet d'envisager des technologies hybrides composées de GaN pour les dispositifs sujet des niveaux de puissance RF importants et de CMOS pour le contrôle de certaines fonctions. Des développements technologiques sont poussés pour permettre l'exploitation d'un substrat silicium compatible CMOS, (100) par exemple, alors que le substrat d'épitaxie Si pour technologie GaN est essentiellement (111).

Comme le montre le Tableau 1, le SiC offre une véritable alternative au substrat silicium, avec un désaccord de maille de seulement 3,4%, il est ainsi possible de réduire l'épaisseur de l'étage tampon et ainsi favoriser la montée en fréquence de la technologie. Viens s'ajouter à cela une très bonne conductivité thermique ce qui en fait un candidat séduisant pour des applications RF de puissances.

Les applications GaN sur diamant sont plus rares même si, sur le papier, le diamant est « le » candidat idéal pour faire office de substrat pour le GaN. En effet, sa conductivité thermique, son coefficient d'expansion thermique ainsi que l'isolation électrique qu'il fournit défie toute concurrence, mais les reports sur diamant s'heurtent encore à de nombreuses contraintes. En effet, les problèmes de qualité de surface du diamant introduisent des défauts cristallins lors de la croissance épitaxiale qui tendent à se répercuter sur les performances électriques et sur la fiabilité des composants [21]. De plus, les substrats diamant sont généralement de petite taille et onéreux, ce qui limite de facto leurs développements à grande échelle.

Envisagée pendant un temps, la technologie GaN sur GaN permet de s'affranchir des problèmes inhérents aux désaccords de maille [22]. Cependant, le matériau étant cher et ses disponibilités limitées son utilisation semble compromise à terme. De plus, le GaN possédant un important coefficient d'expansion thermique, une élévation des températures des composants peut induire des défauts cristallins voir des dislocations du matériau [23].

| Matériau                       | Constante de maille<br>a<br>(en Å) | Désaccord de maille<br>avec le GaN<br>(en %) | Conductivité<br>thermique κ<br>(en W.cm <sup>-1</sup> .K <sup>-1</sup> ) | Coefficient d'expansion thermique $\Delta a/a$ (en $10^{-6}$ . $K^{-1}$ ) | Isolation électrique<br>(en Ω.cm)   |

|--------------------------------|------------------------------------|----------------------------------------------|--------------------------------------------------------------------------|---------------------------------------------------------------------------|-------------------------------------|

| GaN                            | 3,12                               | 0                                            | 1,3                                                                      | 5,6                                                                       | > 10 <sup>9</sup>                   |

| 6H-SiC                         | 3,08                               | 3,4                                          | 4,9                                                                      | 4,2                                                                       | > 10 <sup>11</sup>                  |

| Al <sub>2</sub> O <sub>3</sub> | 2,75                               | 16                                           | 0,4                                                                      | 7,5                                                                       | > 10 <sup>12</sup>                  |

| Si(111)                        | 3,84                               | 17                                           | 1,5                                                                      | 3,6                                                                       | $4 \times 10^3 - 10^4$              |

| Diamant                        | 3,56                               | 14                                           | 25                                                                       | 0,8                                                                       | 10 <sup>12</sup> - 10 <sup>15</sup> |

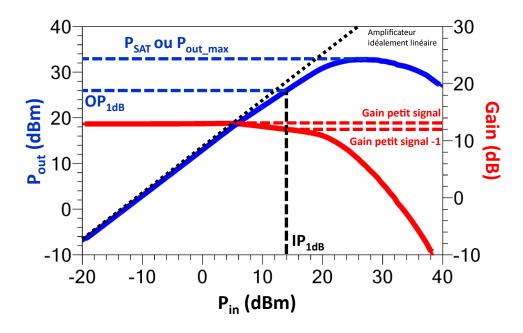

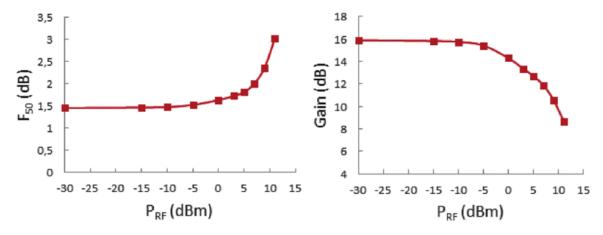

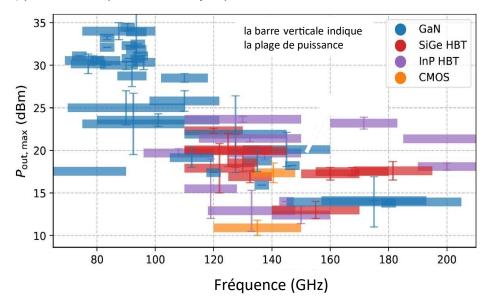

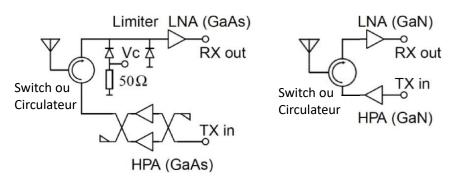

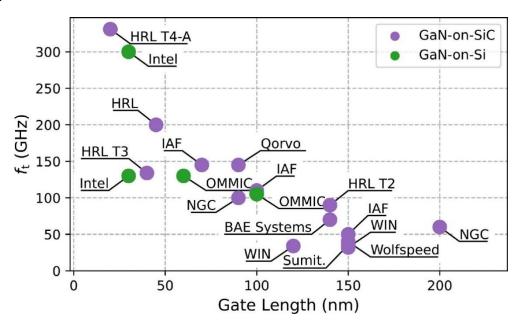

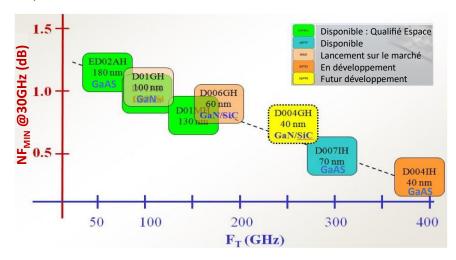

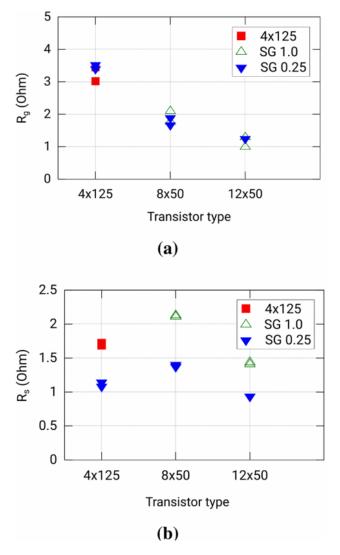

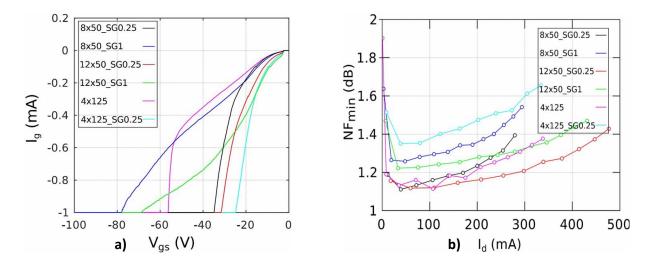

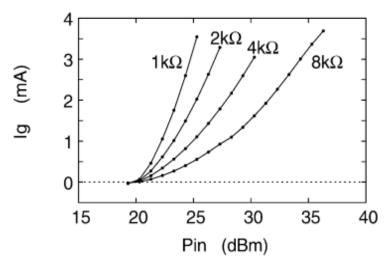

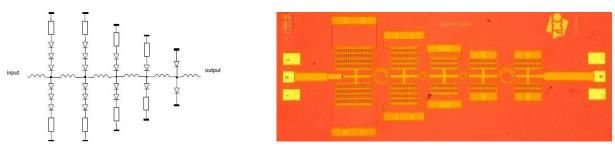

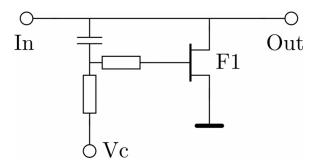

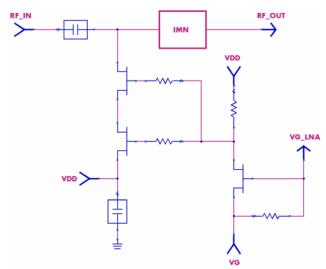

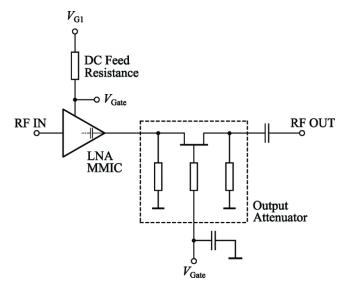

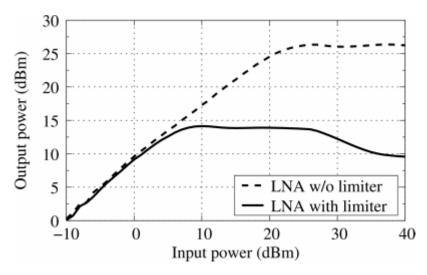

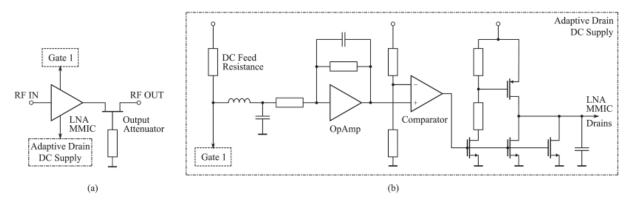

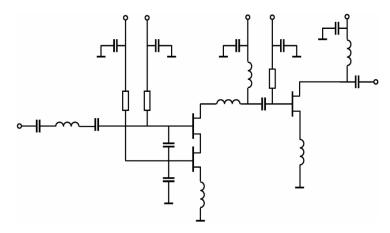

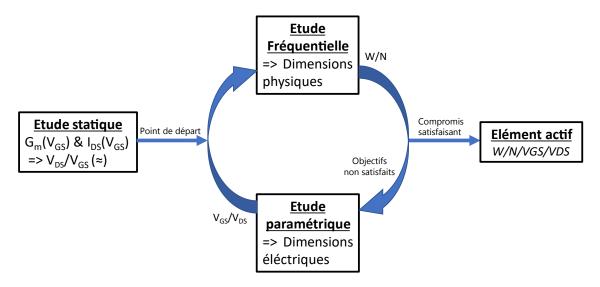

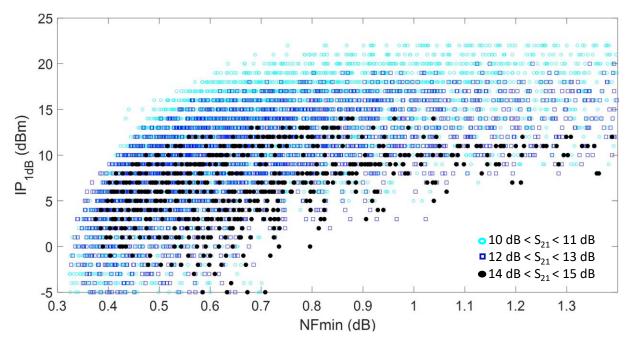

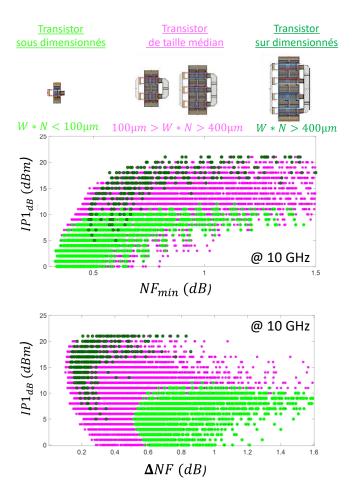

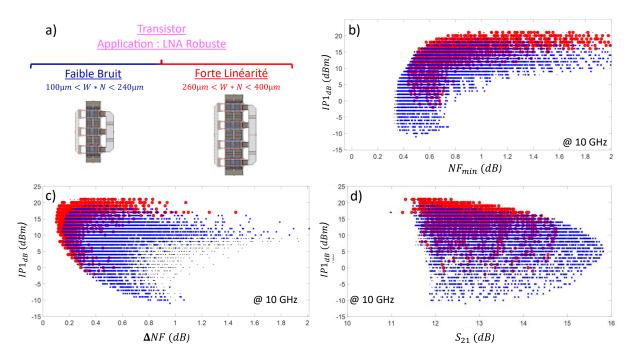

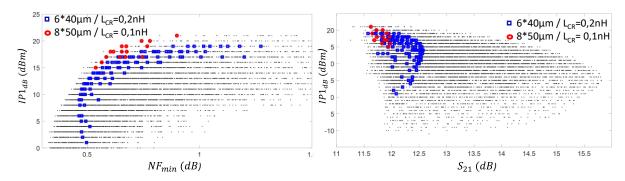

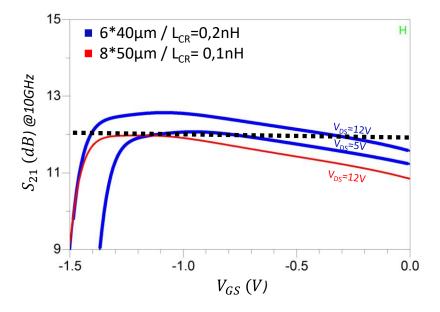

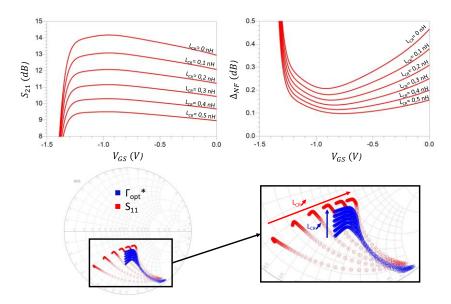

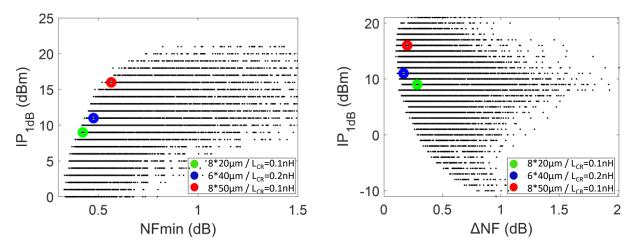

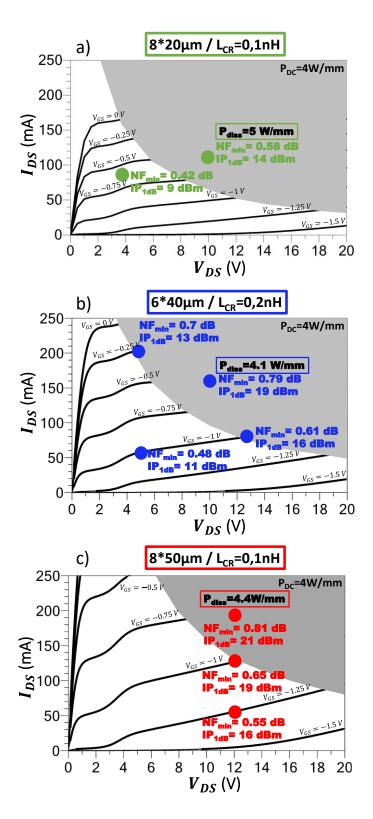

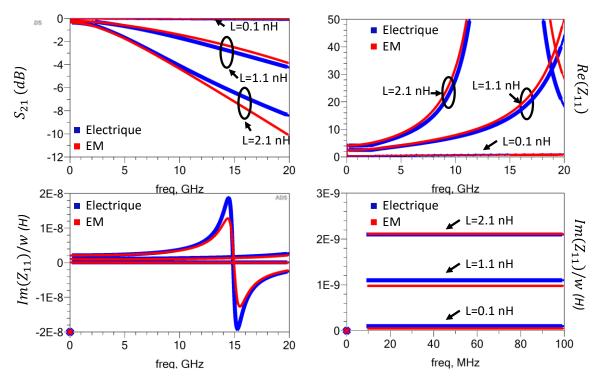

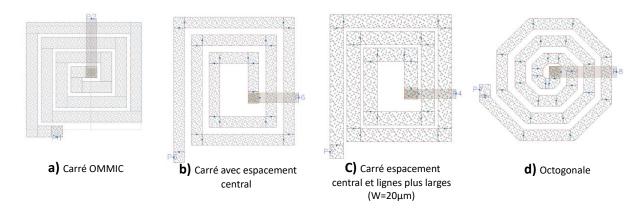

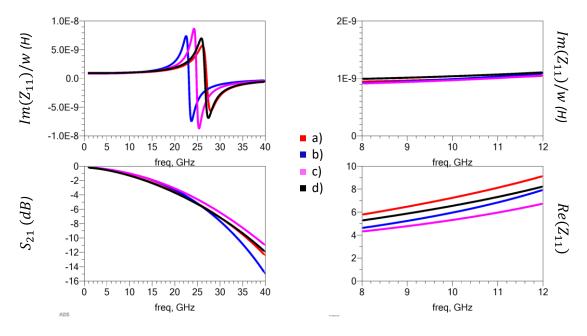

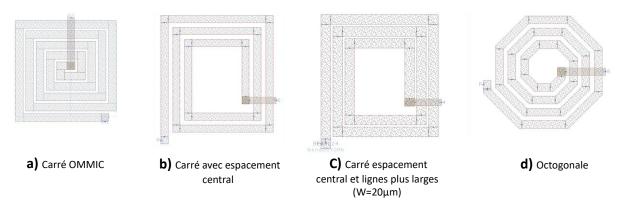

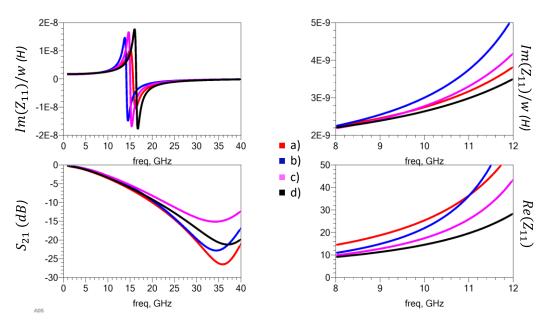

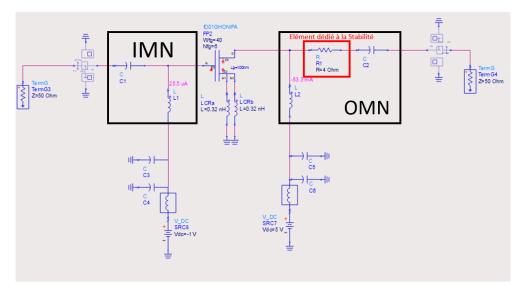

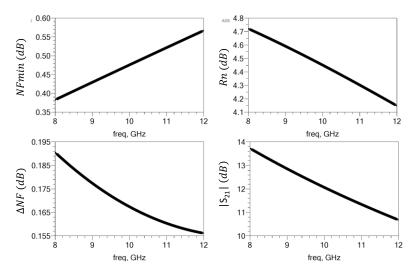

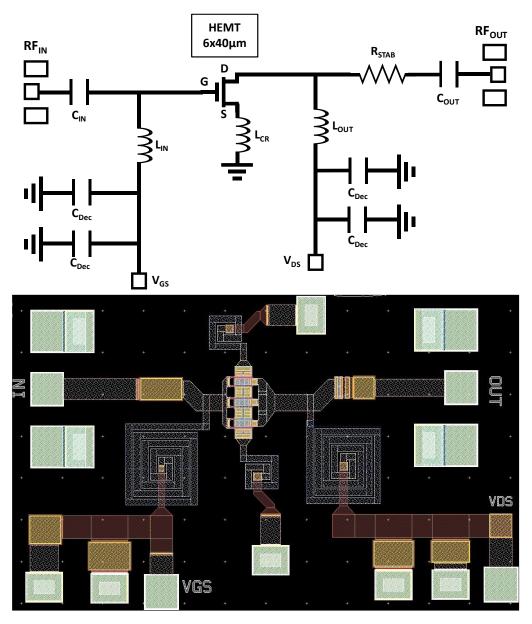

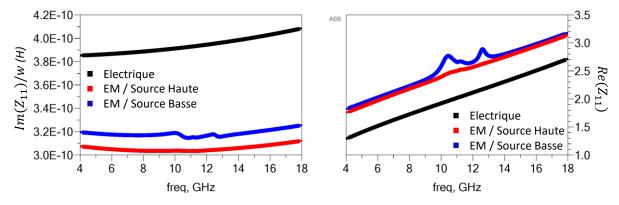

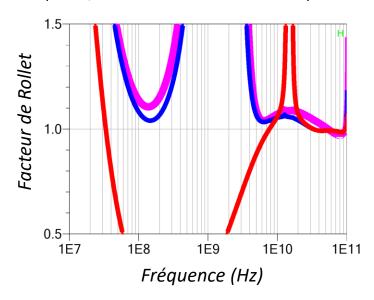

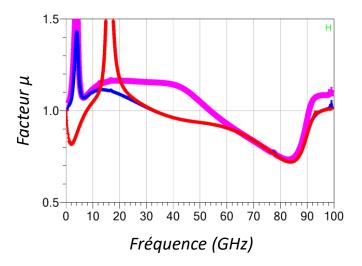

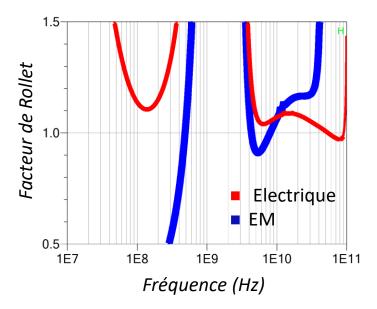

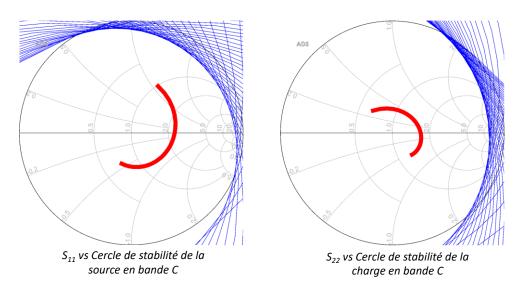

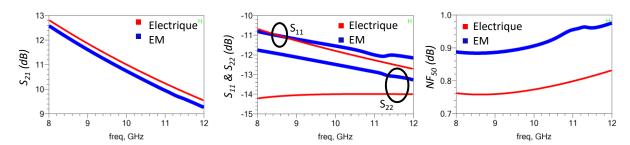

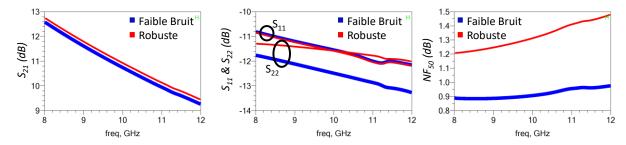

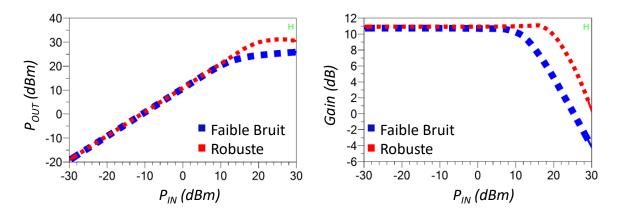

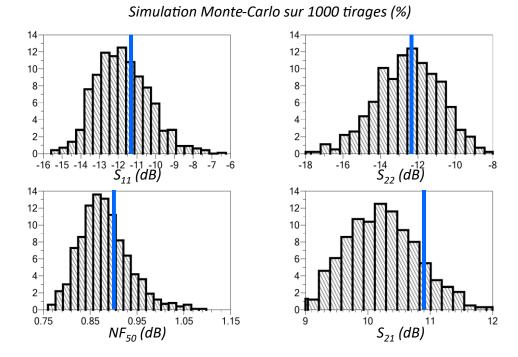

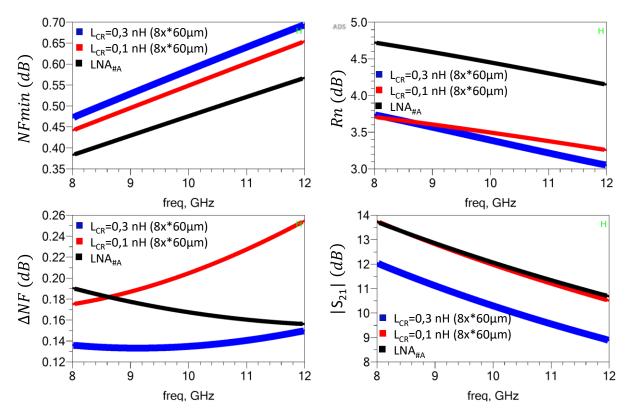

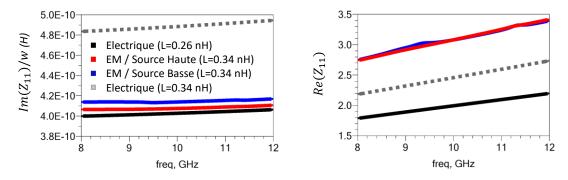

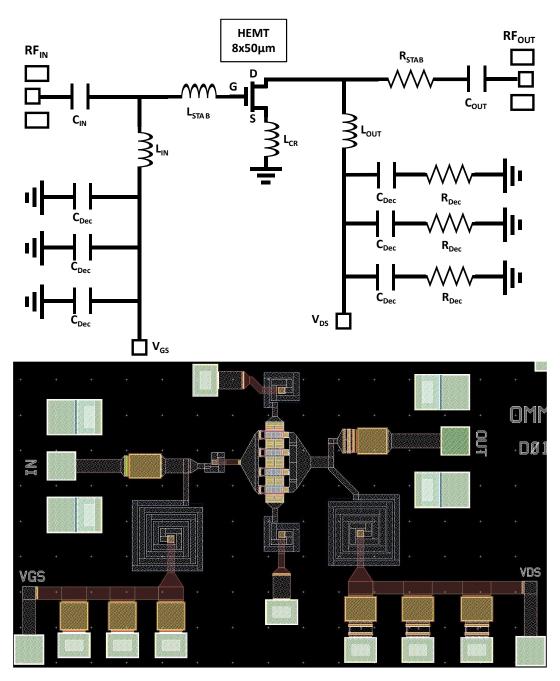

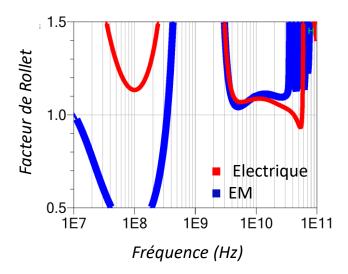

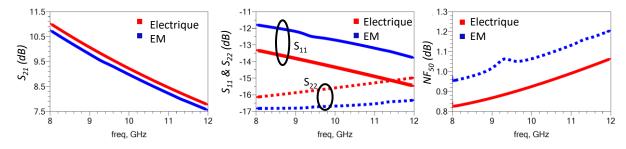

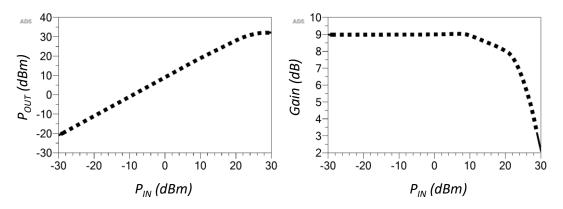

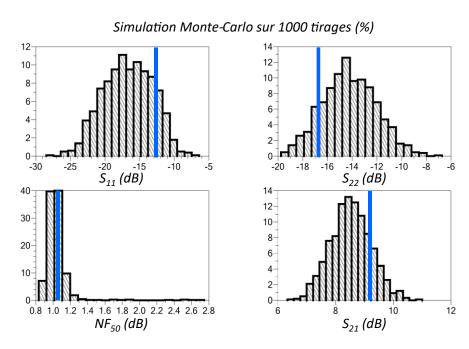

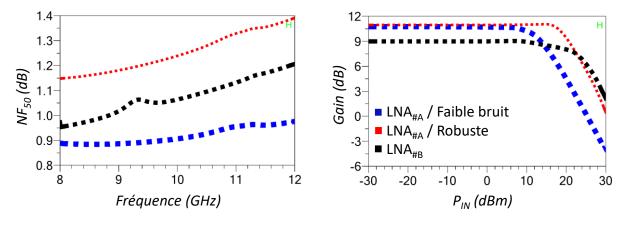

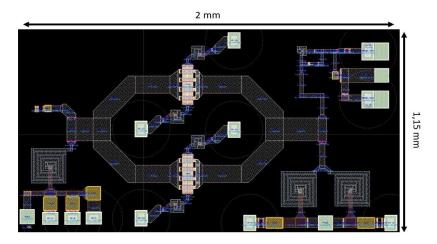

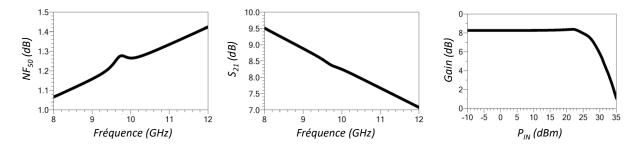

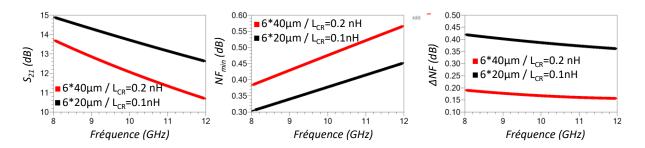

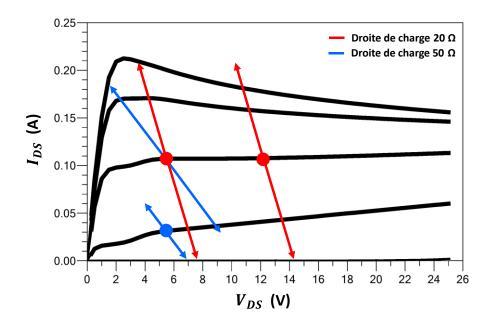

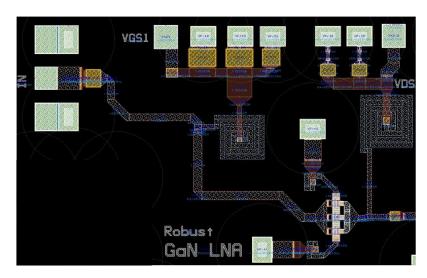

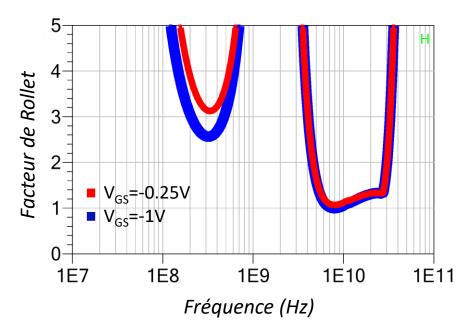

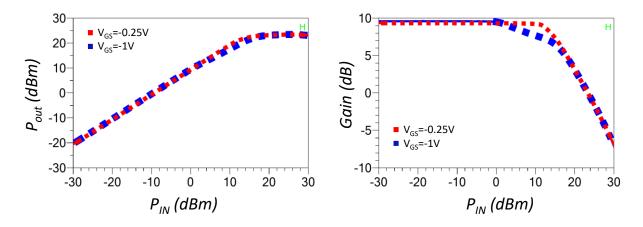

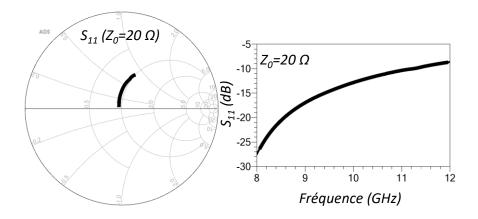

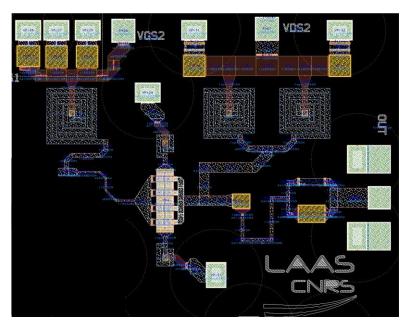

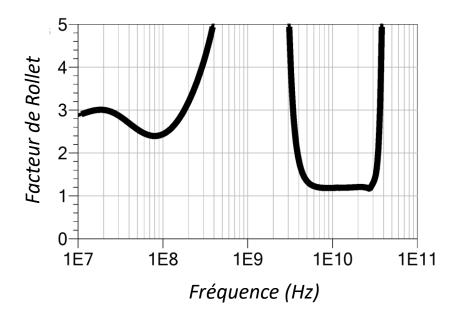

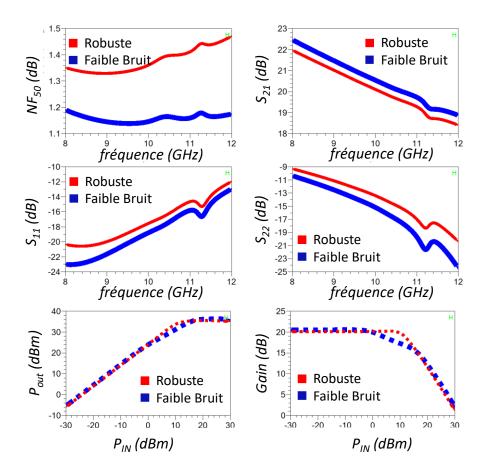

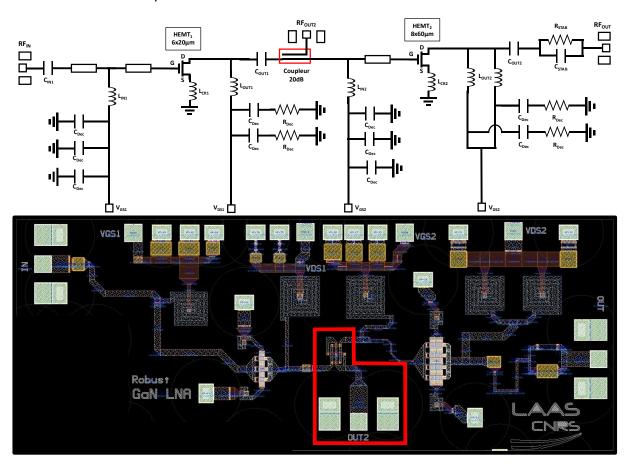

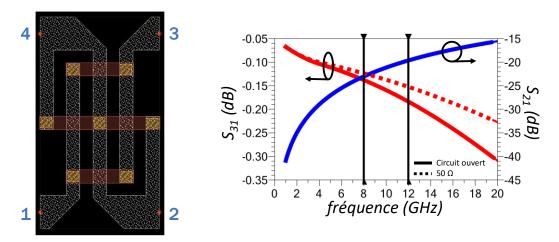

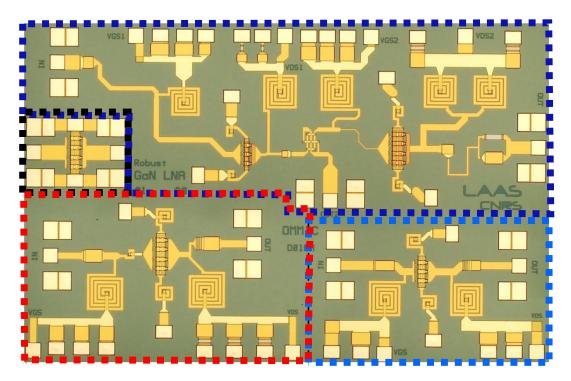

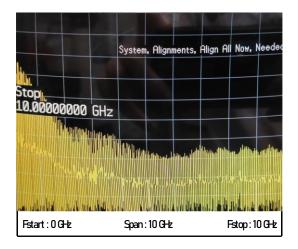

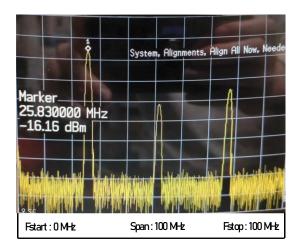

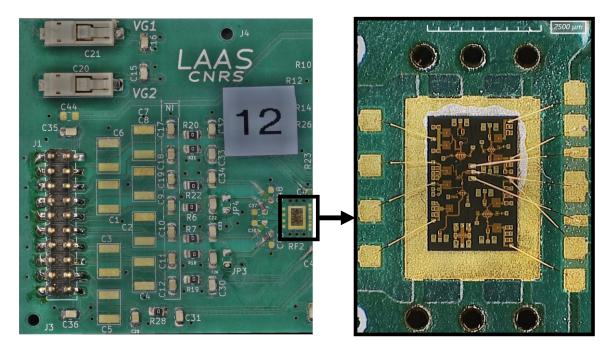

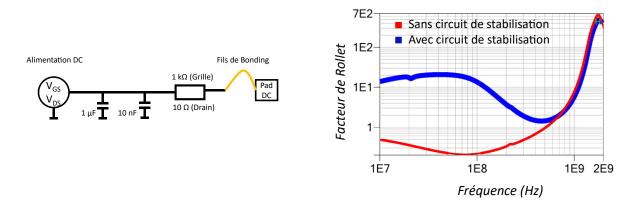

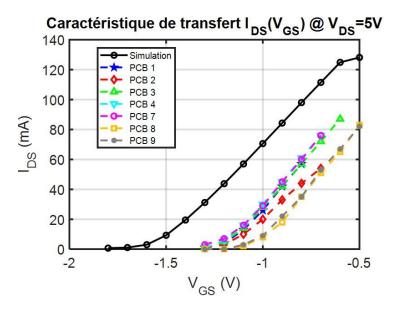

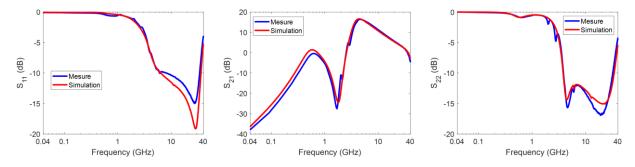

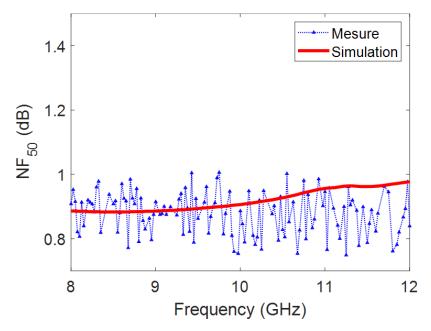

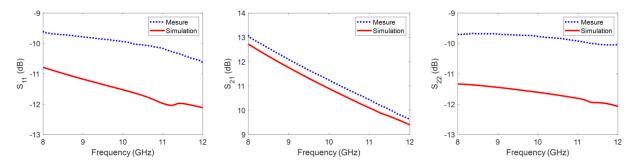

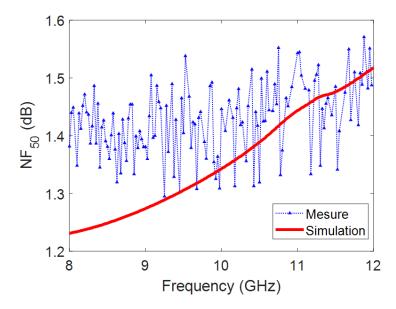

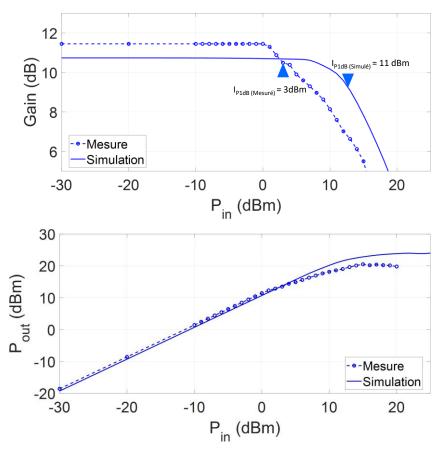

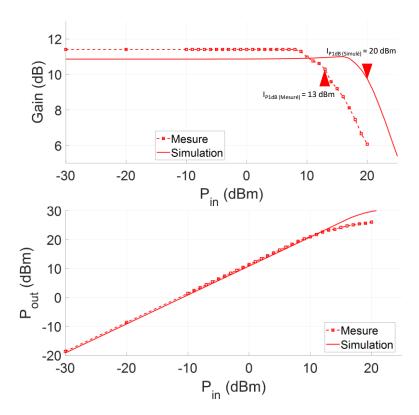

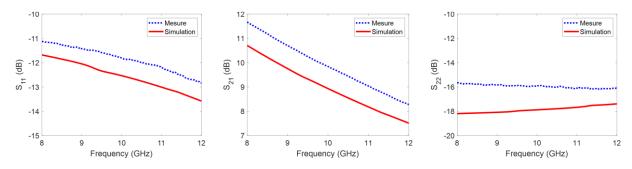

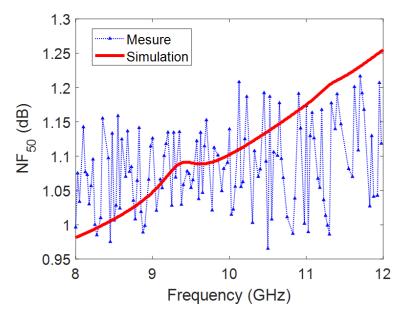

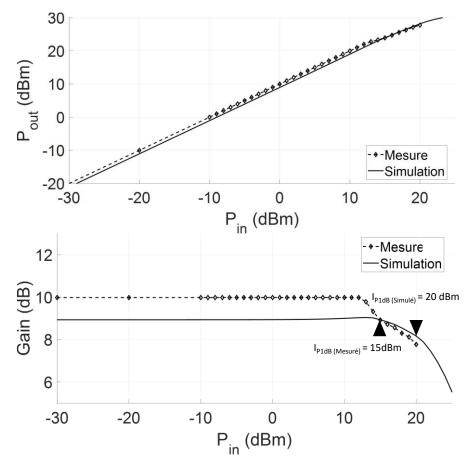

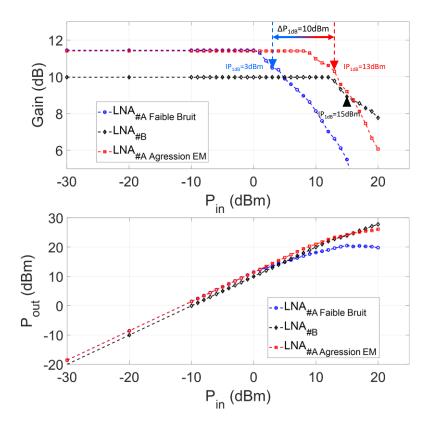

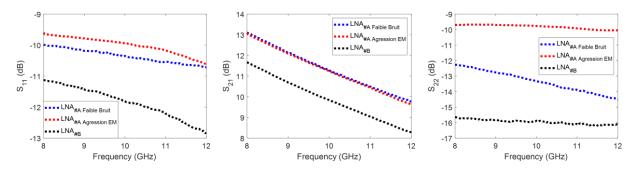

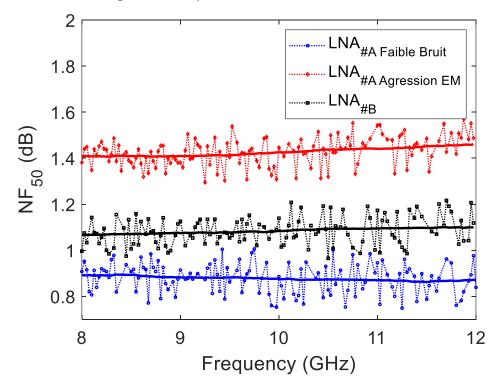

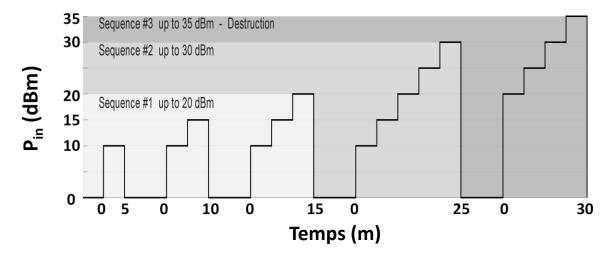

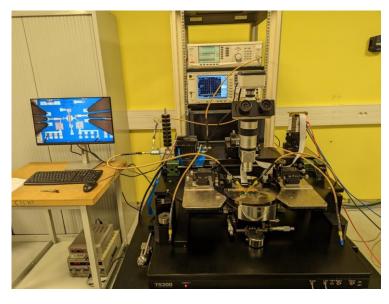

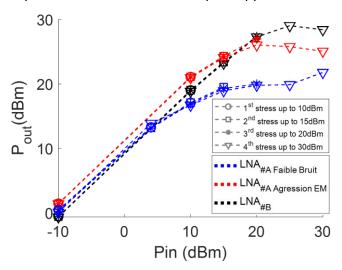

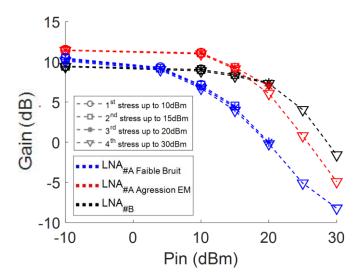

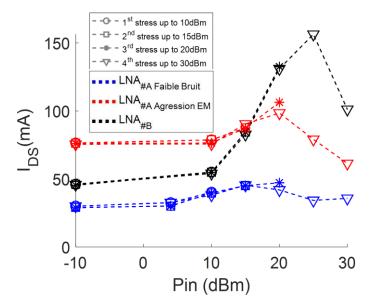

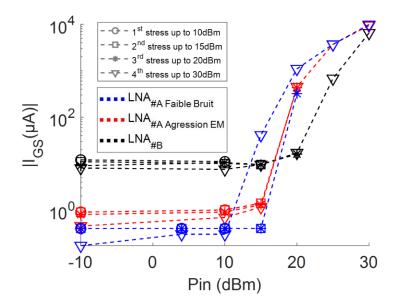

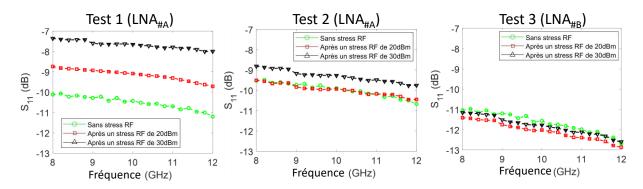

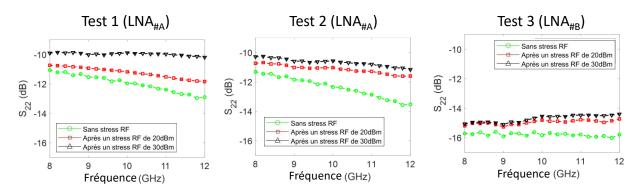

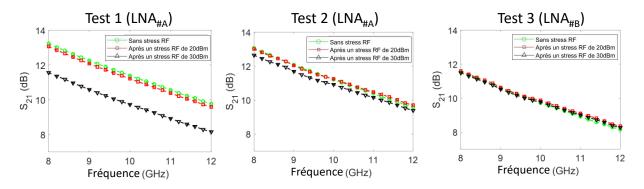

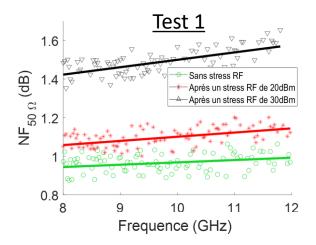

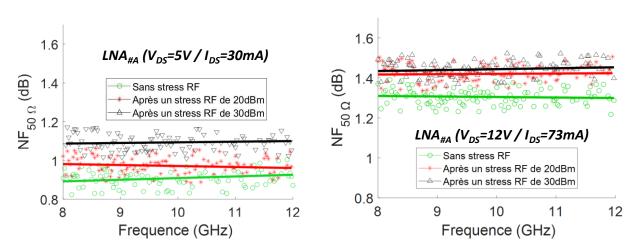

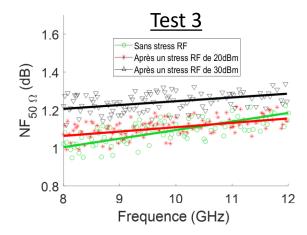

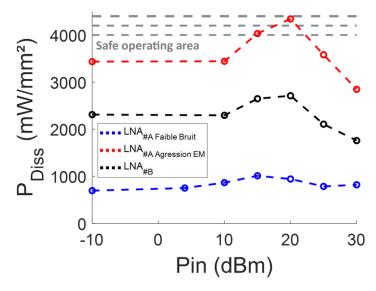

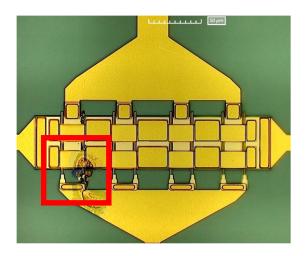

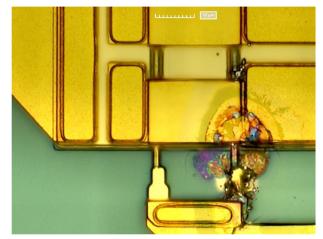

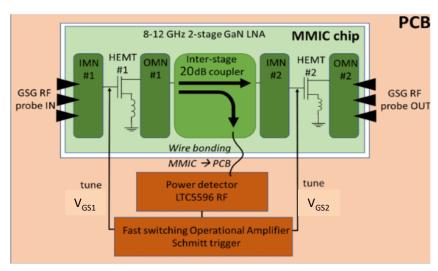

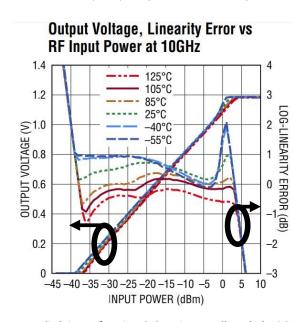

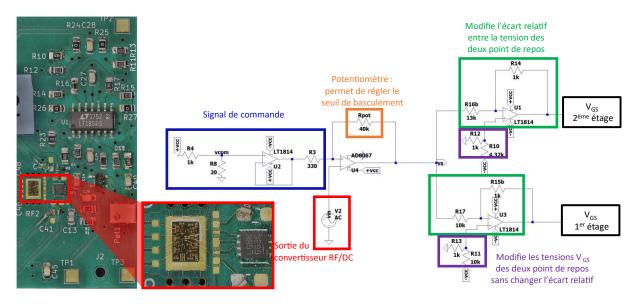

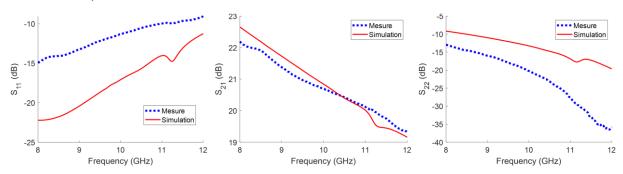

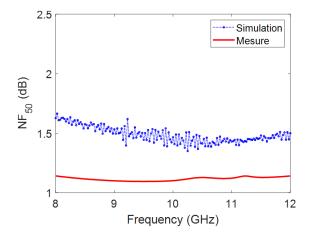

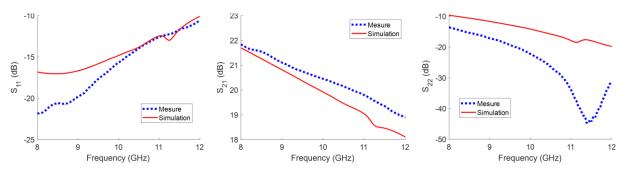

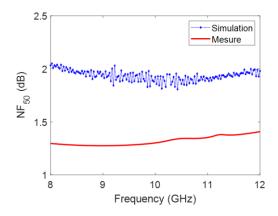

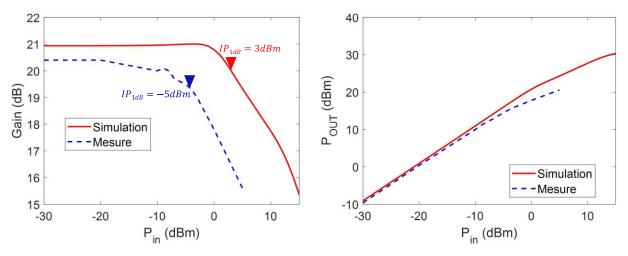

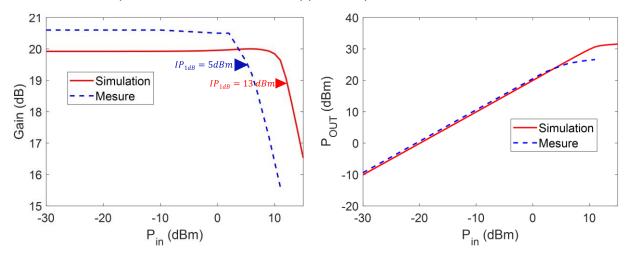

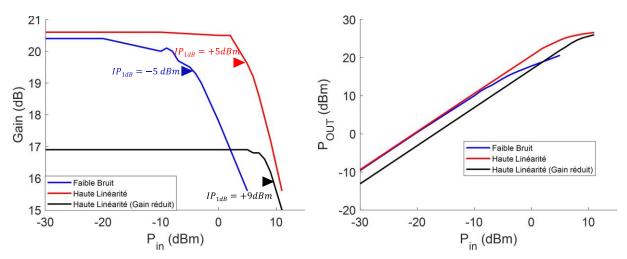

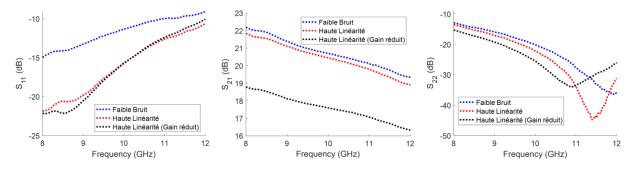

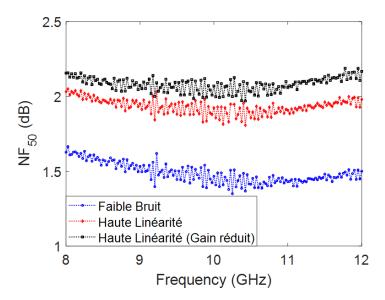

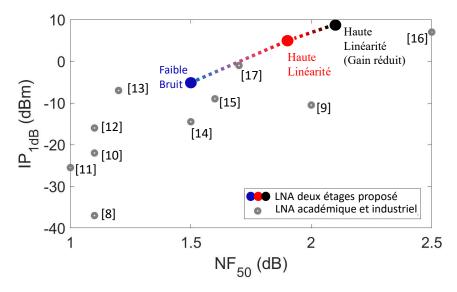

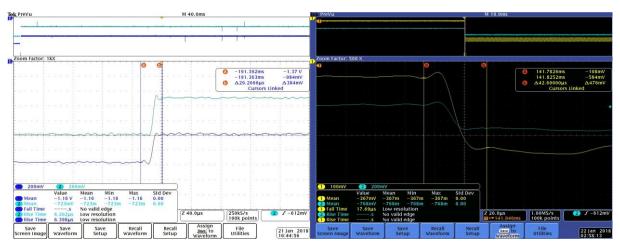

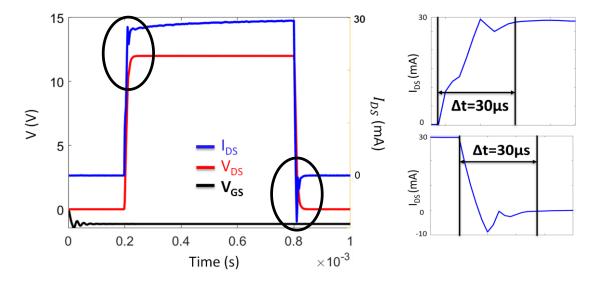

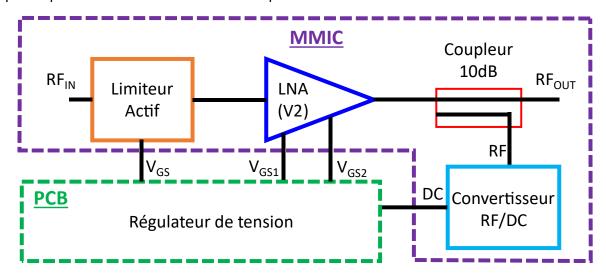

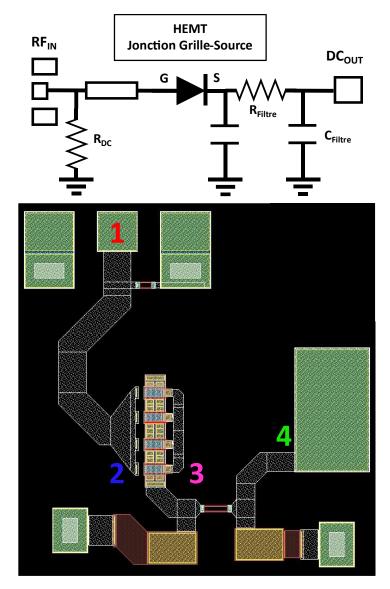

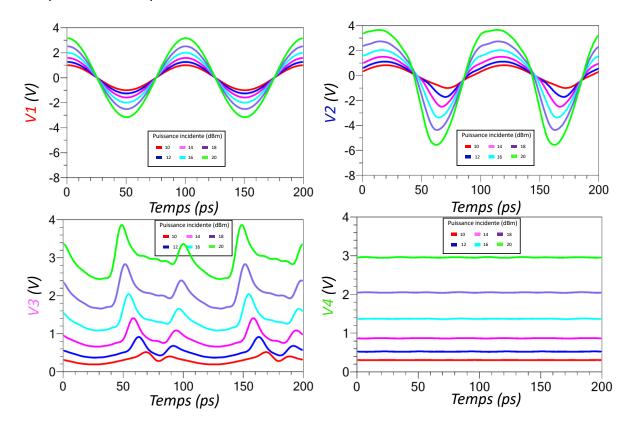

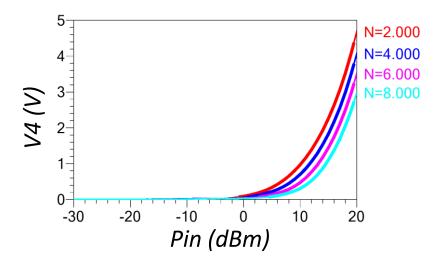

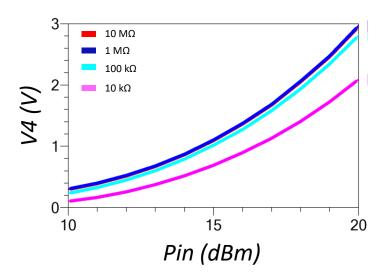

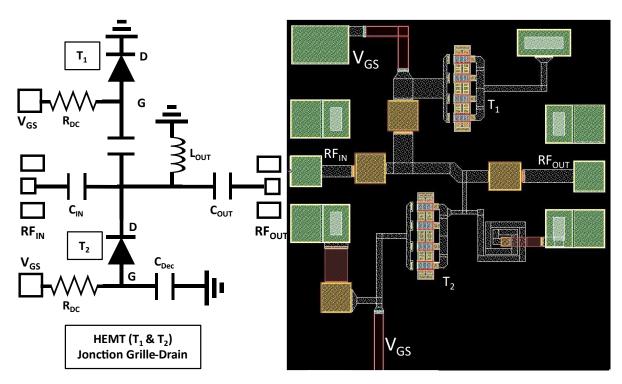

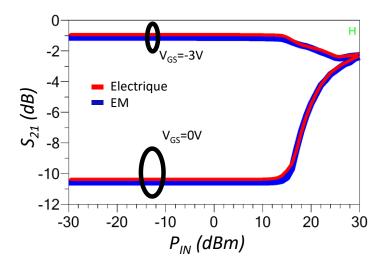

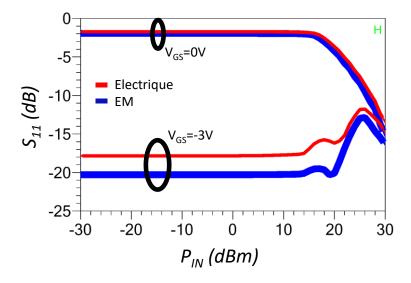

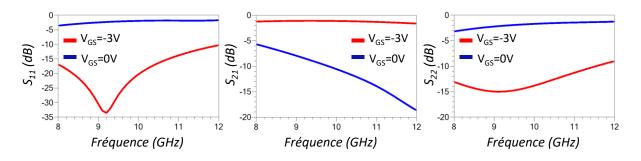

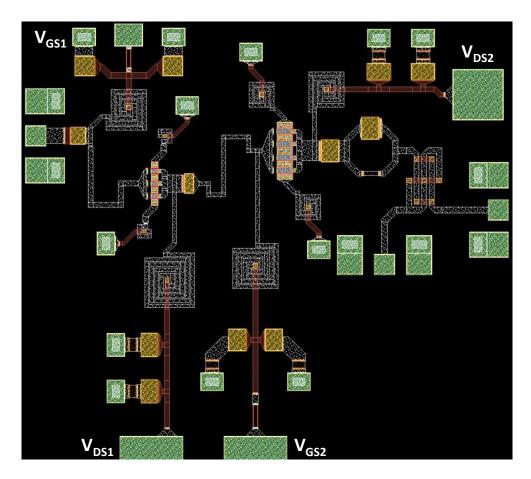

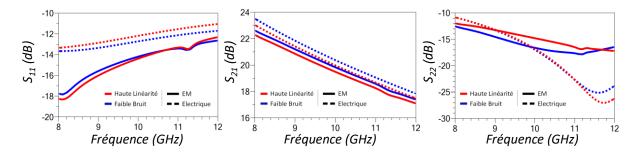

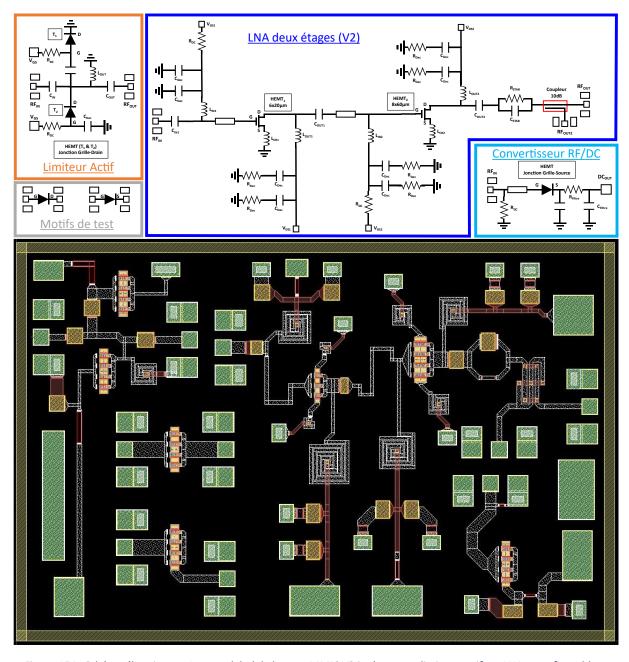

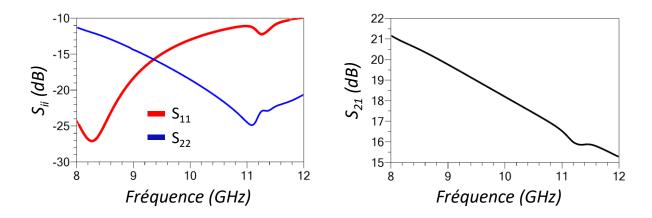

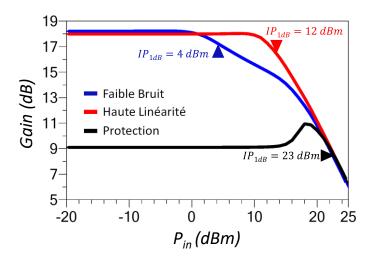

Tableau 1 : Constante de maille, désaccord de maille avec le GaN, conductivité thermique, coefficient d'expansion thermique et isolation thermique pour les différents candidats pouvant jouer le rôle de substrat pour une technologie GaN