## Design and characterization of readout ASICs for SiPM detectors in pico-second timing measurements for the CMS HGCAL experiment

José González Martínez

#### ▶ To cite this version:

José González Martínez. Design and characterization of readout ASICs for SiPM detectors in pico-second timing measurements for the CMS HGCAL experiment. Micro and nanotechnologies/Microelectronics. Institut Polytechnique de Paris, 2024. English. NNT: 2024IPPAX004. tel-04694842

#### HAL Id: tel-04694842 https://theses.hal.science/tel-04694842v1

Submitted on 11 Sep 2024

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Design and characterization of readout ASICs for SiPM detectors in pico-second timing measurements for the CMS HGCAL experiment.

Thèse de doctorat de l'Institut Polytechnique de Paris préparée à l'École polytechnique

École doctorale n°626 Ecole doctorale de l'Institut Polytechnique de Paris (ED IP Paris)

Spécialité de doctorat : Électronique et optoélectronique

Thèse présentée et soutenue à Palaiseau, le 27 Février 2024, par

#### JOSÉ DAVID GONZÁLEZ MARTÍNEZ

#### Composition du Jury:

Florian Beaudette

Directeur de Recherche CNRS LLR Président

Katja Krüger

Senior researcher. Deutsches Elektronen-Synchrotron DESY Rapporteuse

Rémi Cornat

Directeur adjoint technique CNRS IN2P3 Rapporteur

Paul Aspell

Senior engineer. CERN - CMS Examinateur

Giulia Hull

Ingénieure de Recherche Hors Classe, CNRS IJCLab Examinatrice

Christophe de La Taille

Professeur à l'École Polytechnique - CNRS OMEGA Directeur de thèse

## **Agradecimientos**

Me gustaría expresar mi más profunda gratitud a mi director de tesis, Christophe De La Taille. Tiene una experiencia increíble en diseño microelectrónico, pruebas e instrumentación, y siempre estuvo dispuesto a ayudarme, hacer comentarios y sugerir nuevas publicaciones o pruebas. Su apoyo y orientación fueron esenciales durante todo mi doctorado.

También quiero dar las gracias a mis revisores, Katja Krüger y Rémi Cornat, por su detallada revisión de mi tesis y sus valiosos comentarios. También agradezco a Paul Aspell, Giulia Hull y Florian Beaudette por haber aceptado dedicar parte de su tiempo en examinar mi trabajo de tesis, como parte del jurado.

A mis compañeros de laboratorio en OMEGA, siempre dispuestos a ayudar o platicar durante las pausas para el café. Agradezco especialmente a Damien Thienpont por su ayuda para aprender sobre el chip HGCROC, que fue indispensable. También agradezco a Maxime Morenas que compartiera conmigo el viaje de doctorado y a Anne-Myriam por ayudarme con la complejidad de los asuntos administrativos franceses.

A mis colegas del experimento CMS, en particular de los laboratorios DESY y CERN, agradezco a Mathias Reinecke su colaboración y apoyo, especialmente durante las pruebas de SiPMs. También me gustaría agradecer la ayuda de Arnaud Steen, Sebastien Extier y Elena Vernazza durante las pruebas de radiación en CERN.

Mi agradecimiento también a mis amigos en Europa, que se convirtieron en mi segunda familia. Su compañía hizo que esta experiencia fuera memorable y significativa. Además, doy las gracias a mis amigos de México, que desde allá siempre han estado presentes.

Agradezco profundamente a mi prometida, Brenda Olivas, por su apoyo constante. Su amor, consejos y guía durante las dificultades del doctorado fueron invaluables, y estoy agradecido de tenerla a mi lado.

Todo esto no habría sido posible sin la educación que me dieron mis padres, Malú Martínez y David González. A mi hermana, Lupita González, y a toda mi familia, les agradezco enormemente por sus oraciones y cariño, incluso desde lejos con nuestras videollamadas todos los domingos.

Finalmente, doy gracias a Dios por las innumerables bendiciones que, sin Él, no hubiera podido venir aquí y trabajar en este doctorado.

## **Acknowledgements**

I would like to express my deepest gratitude to my thesis supervisor, Christophe De La Taille. He has exceptional expertise in microelectronics design, testing and instrumentation, and was always willing to help, provide comments and suggest new publications or tests. His support and guidance were essential throughout my Ph.D. journey.

I also want to thank my reviewers, Katja Krüger and Rémi Cornat, for their detailed review of my thesis and valuable feedback. I'm also grateful to Paul Aspell, Giulia Hull and Florian Beaudette for agreeing to spend some of their time reviewing my thesis work as part of the jury.

To my lab colleagues in OMEGA, each of them was always ready to help and chat during coffee breaks. I am especially grateful for Damien Thienpont's hard work and assistance in understanding the HGCROC ASIC, which was indispensable. I also appreciate Maxime Morenas for sharing the Ph.D. journey with me and Anne-Myriam's help with the complexity of French administrative matters.

To my colleagues from the CMS experiment, particularly those at DESY and CERN, I thank Mathias Reinecke for his collaboration and support, especially during SiPM testing. I would also like to acknowledge Arnaud Steen, Sebastien Extier and Elena Vernazza's help during radiation tests at CERN.

My thanks go also to my friends in Europe, who became my second family. Your presence made this experience memorable and meaningful. Moreover, I thank my friends in México, who were always present despite the distance.

I deeply thank my fiancée, Brenda Olivas, for her constant support. Her love, advice and insights into the complexities of Ph.D. life were priceless, and I am grateful to have her by my side.

This academic journey would not have been possible without the education provided by my parents, Malú Martínez and David González. To my sister, Lupita González and my entire family, I express my deepest gratitude for their prayers and continuous love, even from far away, with our Sunday video calls.

Finally, I thank God for the countless blessings that, without Him, I could not have come here and work on this Ph.D.

## **Contents**

| Ą  | grade                           | cimientos                                                     |                                        |

|----|---------------------------------|---------------------------------------------------------------|----------------------------------------|

| A  | cknov                           | vledgements                                                   | ii                                     |

| C  | onten                           | ts                                                            | i۷                                     |

| Re | ésum                            | é de la thèse en Français                                     | vi                                     |

| 1  | 1.1<br>1.2                      | Oduction Overview Objectives and Contributions Thesis outline | 2                                      |

| 2  | 2.1<br>2.2<br>2.3               | 2.3.1 The High Luminosity Large Hadron Collider               | 10<br>10<br>13<br>14<br>16<br>17<br>19 |

| 3  | 3.1<br>3.2<br>3.3<br>3.4<br>3.5 | Introduction                                                  | 24<br>24<br>29<br>30                   |

Contents

|   | 3.7 | Front-End Electronics for SiPM                             | 8.9 |

|---|-----|------------------------------------------------------------|-----|

| 4 |     |                                                            |     |

| 4 |     | <b>ICROC : The SiPM Readout ASIC of HGCAL</b> Introduction |     |

|   | 4.1 |                                                            |     |

|   | 4.2 | H2GCROC architecture overview                              |     |

|   |     | 4.2.1 Interface blocks                                     |     |

|   | 4.0 | 4.2.2 Power of the ASIC                                    |     |

|   | 4.3 | Very Front-End ASIC design                                 |     |

|   |     | 4.3.1 Current conveyor                                     |     |

|   |     | 4.3.2 Preamplifier                                         |     |

|   |     | 4.3.3 Shaper                                               |     |

|   |     | 4.3.4 Discriminators                                       |     |

|   |     | 4.3.5 ADC                                                  |     |

|   |     | 4.3.6 TDC                                                  |     |

|   |     | 4.3.7 Data and trigger paths                               |     |

|   | 4.4 | Charge and time measuring techniques 6                     |     |

|   |     | 4.4.1 Small charge injection simulations                   | 0   |

|   |     | 4.4.2 Time-of-arrival simulations                          | 1   |

|   |     | 4.4.3 Large charge injection simulations                   | 3   |

|   |     | 4.4.4 Noise of the system                                  | 6   |

|   |     | 4.4.5 Integration of the Readout ASIC with SiPM Detectors  | 6   |

|   | 4.5 | Methodologies for Calibration of the ASIC                  | 0   |

|   |     | 4.5.1 Analog and reference voltage probes                  | 0   |

|   |     | 4.5.2 Channel trimming                                     | 1   |

|   |     | 4.5.3 Internal Injection                                   | 1   |

|   |     | 4.5.4 Gain calibration of the FE                           |     |

|   |     | 4.5.5 Calibration for SiPM detectors                       |     |

|   |     | 4.5.6 SiPM Leakage current compensation                    |     |

|   | 4.6 | Conclusion                                                 |     |

|   |     | 001101010111111111111111111111111111111                    | Ŭ   |

| 5 | H2G | CROC ASIC Characterization 8                               | 9   |

|   | 5.1 | Introduction                                               | 0   |

|   | 5.2 | Measurement Setup and Procedures                           | 0   |

|   |     | 5.2.1 Internal and External injection setup                | 2   |

|   |     | 5.2.2 SiPM under test                                      |     |

|   |     | 5.2.3 Photon injection                                     |     |

|   | 5.3 | Methodologies for calibration of the ASIC                  |     |

|   | 0.0 | 5.3.1 Gain configuration of the ASIC                       |     |

|   |     | 5.3.2 Pedestal adjustment                                  |     |

|   |     | 5.3.3 Time threshold calibration                           |     |

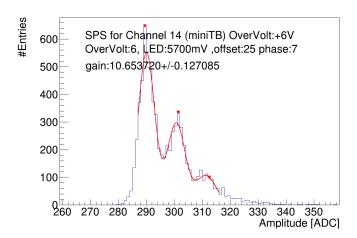

|   |     | 5.3.4 Single photon counting                               |     |

|   |     | g .                                                        |     |

|   |     | <b>O</b>                                                   |     |

|   | E 4 | 5.3.6 TDC calibration                                      |     |

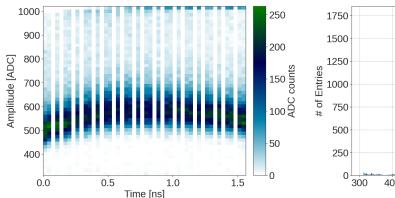

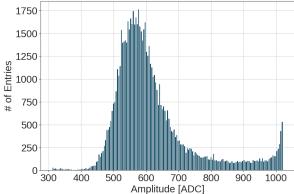

|   | 5.4 | Charge and time measurement performance                    |     |

|   |     | 5.4.1 ADC performance for charge measurement               |     |

|   |     | 5.4.2 Time-over-threshold technique for charge measurement | 1   |

vi Contents

|                 | 5.5                      | 5.4.3 Time-of-arrival measurement                                                                                                                                                                                                                                                   | 111<br>112                                                         |  |  |

|-----------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|--|--|

|                 | 5.6<br>5.7<br>5.8<br>5.9 | 5.5.3 Cross-talk 5.5.4 Trigger path measurements Temperature analysis Radiation tolerance of H2GCROC 5.7.1 TID Setup 5.7.2 TID campaigns 5.7.3 SEE Setup 5.7.4 Single Event Effect Campaigns 5.7.5 SiPM irradiation effects Power consumption and robustness of the chip Conclusion | 114<br>115<br>116<br>118<br>120<br>122<br>132<br>133<br>136<br>137 |  |  |

| 6               | ۸۹۱                      | C Validation and Verification                                                                                                                                                                                                                                                       | 141                                                                |  |  |

| 0               | 6.1<br>6.2               | Introduction                                                                                                                                                                                                                                                                        | 141<br>141<br>142<br>143<br>148<br>151<br>153<br>154<br>156        |  |  |

| 7               | Gen                      | eral Conclusions                                                                                                                                                                                                                                                                    | 159                                                                |  |  |

| Bil             | Bibliography 16          |                                                                                                                                                                                                                                                                                     |                                                                    |  |  |

| List of Figures |                          |                                                                                                                                                                                                                                                                                     |                                                                    |  |  |

| Lis             | List of Tables           |                                                                                                                                                                                                                                                                                     |                                                                    |  |  |

| Lis             | List of Equations 1      |                                                                                                                                                                                                                                                                                     |                                                                    |  |  |

| Acronyms 1      |                          |                                                                                                                                                                                                                                                                                     |                                                                    |  |  |

## Résumé de la thèse en Français

La physique des particules a toujours recherché un modèle précis permettant de comprendre et de prédire le comportement de notre univers. L'humanité continue de s'approcher des modèles les plus précis et les plus complexes grâce au développement de nouvelles technologies. Nous recherchons la particule la plus petite et la plus générique qui forme tout ce que nous connaissons, contribuant ainsi à une meilleure compréhension de notre monde et de l'univers.

Cependant, la taille minuscule des particules subatomiques constitue un défi de taille. Au fil des ans, les physiciens ont réussi à détecter et à visualiser ces particules. Des détecteurs avancés peuvent désormais identifier et caractériser diverses particules en mesurant leur énergie, leur quantité de mouvement et leur temps. Les accélérateurs permettent d'étudier la composition de la matière en accélérant les particules élémentaires à des vitesses proches de celle de la lumière. La collision de ces particules les décompose, donnant naissance à d'autres particules qui constituent la matière observée. Des détecteurs à grande échelle mesurent l'énergie et étudient les particules issues de ces collisions. Initialement, la collecte d'événements photographiques était utilisée dans les détecteurs d'accélérateurs pour reconstruire les particules générées lors des collisions. Aujourd'hui, l'enregistrement de données électroniques ouvre de nombreuses possibilités, facilitant les expériences à haut débit qui mesurent les particules avec une résolution de l'ordre de la picoseconde et offrant la possibilité de découvrir de nouvelles particules ou interactions.

Les connaissances actuelles sur la composition et le comportement de la matière sont consolidées dans le modèle standard de la physique des particules, qui explique les particules élémentaires et leurs interactions. Au cours des 15 dernières années, nous sommes entrés dans une nouvelle ère de précision dans la mesure de l'énergie des jets de particules. Les calorimètres disposent désormais d'excellentes capacités d'imagerie, ce qui permet de reconstruire avec précision les particules produites lors d'une collision. Cependant, avec l'émergence de nouveaux projets de physique des particules, il existe une demande pour des systèmes encore plus précis et de nouvelles techniques pour répondre aux questions posées par le modèle standard. Les calorimètres ayant une durée de vie opérationnelle limitée, il devient nécessaire de les remplacer, ce qui permet aux nouveaux projets d'améliorer la précision des mesures et les capacités des calorimètres tout en optimisant les algorithmes de flux de particules.

L'expérience CMS (Compact Muon Solenoid collaboration) a permis des avancées et des découvertes significatives en caractérisant les particules fondamentales et leurs interactions telles qu'elles sont décrites par le modèle standard de la physique. Le détecteur fonctionne au sein du Grand collisionneur de hadrons (LHC) au CERN. Cependant, malgré les excellents résultats obtenus dans ce collisionneur, il est nécessaire d'améliorer les capacités de lecture de la luminosité d'au moins un ordre de grandeur tout en maintenant une grande précision afin de répondre aux exigences des expériences complexes à venir. Le calorimètre à haute granularité (HGCAL) est en cours de développement et devrait être pleinement opérationnel d'ici 2029 [1]. Le HGCAL augmentera le nombre de pièges à particules et améliorera la précision tout en

conservant le concept de détection des couches.

Les progrès réalisés dans le domaine des détecteurs suscitent également des attentes en matière d'électronique frontale, en particulier face à des niveaux de rayonnement anticipés qui pourraient être dix fois plus élevés que ceux initialement expérimentés dans la conception du CMS [2]. En conséquence, de nouveaux circuits intégrés à application spécifique (ASIC) sont en cours de développement pour détecter une gamme plus large de signaux, offrir une meilleure résolution de mesure et améliorer la précision des informations sur le temps d'arrivée. La tolérance aux rayonnements et la réduction du bruit des ASIC sont essentielles pour obtenir des mesures plus précises. En outre, le traitement des données après numérisation représente un ajout précieux aux ASIC, car il permet de sélectionner des données significatives parmi le nombre croissant d'interactions au niveau des détecteurs et d'atténuer la quantité excessive de données résultant d'une luminosité plus élevée.

La complexité de l'application exige une augmentation du nombre de fonctionnalités dans la puce. Dans le domaine analogique, des blocs précis doivent être ajustés en fonction de plusieurs paramètres, tandis que la partie numérique nécessite une mémoire et une logique complexe pour sélectionner des données significatives. En outre, les ASIC doivent améliorer la résistance aux radiations, en augmentant la taille des transistors les plus impactants dans les blocs analogiques et en triplant la logique numérique pour protéger le traitement des données au sein de la puce.

Dans la conception des ASIC, la technologie CMOS (complementary metal oxide semiconductor technology) s'impose comme la technologie la plus efficace et la plus largement utilisée, grâce à la flexibilité des transistors MOS en tant que blocs de construction fondamentaux. Chaque conception analogique commence au niveau transistor, impliquant la sélection de l'architecture et de la taille des transistors pour répondre aux exigences spécifiées. La conception d'un ASIC implique généralement la connexion de plusieurs modules, tels que des amplificateurs, des convertisseurs analogique-numérique (ADC), des discriminateurs, des shapers, des convoyeurs de courant (CC), etc.

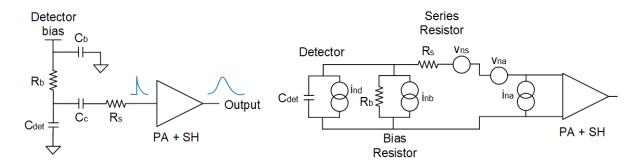

L'électronique front-end est essentielle pour répondre aux spécifications de lecture des détecteurs photomultiplicateurs au silicium (SiPM). Un SiPM se compose d'un réseau de diodes à avalanche à photon unique (SPAD) intégrées dans un seul capteur, où chaque SPAD fonctionne comme un pixel. Lorsqu'il est exposé à des impulsions lumineuses, chaque pixel recevant un photon génère un pic de courant de la même magnitude. Alors que l'amplificateur de charge classique est un choix standard pour la lecture dans les environnements de rayonnement en raison de son faible bruit, il peut ne pas être la solution optimale pour les détecteurs SiPM.

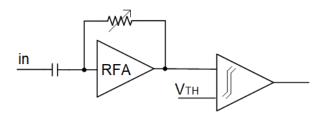

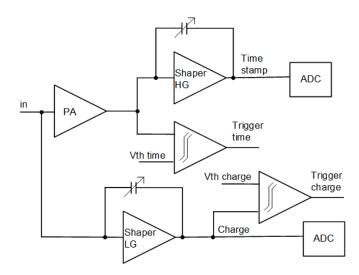

Dans la littérature, trois configurations principales sont généralement employées pour la lecture des détecteurs SiPM : le préamplificateur de tension, l'amplificateur radiofréquence et le convoyeur de courant. Chaque architecture présente des avantages et des inconvénients, avec des innovations en matière de réduction du bruit, de précision de la synchronisation et de plage dynamique. Ces avancées reflètent la recherche constante de performances accrues en matière de lecture SiPM.

Les ASIC HGCROC sont des systèmes électroniques frontaux dédiés, conçus en technologie TSCM 130 nm pour la lecture des détecteurs au silicium et des SiPM du nouveau HGCAL. Au cours de la phase conceptuelle, il a été déterminé que l'utilisation d'un ASIC similaire ou identique pour les deux types de capteurs sur le détecteur serait avantageuse [2]. Cependant, cette décision a posé un défi important pour le développement du H2GCROC pour la lecture SiPM. Les capteurs SiPM présentent des avantages, notamment un gain plus élevé et un coût inférieur à celui des capteurs au silicium. Cependant, ils sont moins tolérants aux rayonnements et présentent des capacités plus importantes qui augmentent avec la taille du capteur. En ce qui concerne la charge, le signal d'entrée du H2GCROC sera environ 30 fois plus important

que le maximum attendu des capteurs au silicium.

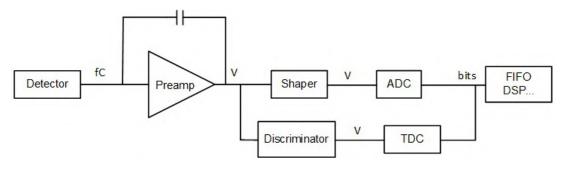

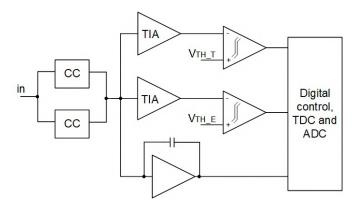

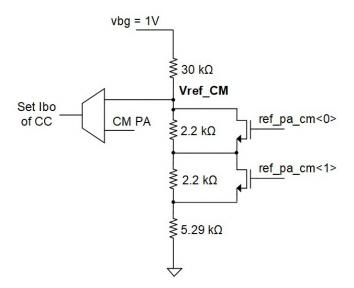

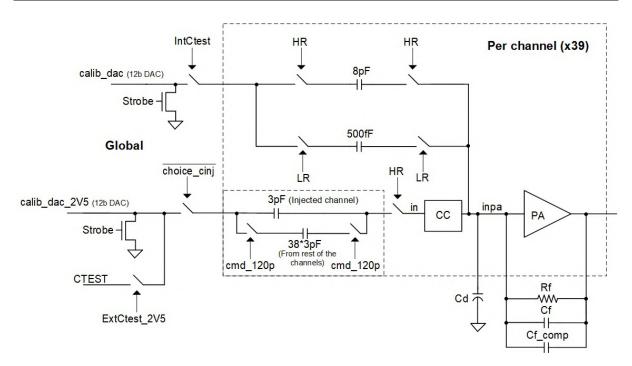

Pour relever ce défi, il a été nécessaire de développer une variante du HGCROC qui adapte le signal d'entrée à la gamme de charges possible dans la limite de la capacité de la même architecture frontale. Le H2GCROC lit les SiPM couplés à des tuiles scintillantes dans les sections hadroniques arrière, où les contraintes de rayonnement sont moins sévères. La solution mise en œuvre utilise un convoyeur de courant conçu explicitement pour les SiPM, capable d'atténuer le signal de courant tout en maintenant une impédance compatible avec l'entrée du préamplificateur du frontal. Par la suite, les autres aspects de la puce conservent les mêmes fonctionnalités que le HGCROC, avec des ajustements mineurs dans les paramètres de configuration pour tenir compte des plages de charge des SiPM comme prévu. Le H2GCROC peut lire les données de charge à l'aide d'un ADC et d'un TDC pour la technique du temps sur seuil (time-over-threshold ou TOT). Un module TDC dédié fournit des informations temporelles pour les mesures du temps d'arrivée (time-of-arrival ou TOA) des particules [3].

L'une des contributions de cette thèse a été de modifier certains blocs pour rectifier la correction des dommages dus à l'irradiation avec des SiPMs irradiés. Les SiPMs irradiés génèrent un courant de fuite aux entrées du canal. La compensation du courant de fuite a été augmentée de 290  $\mu$ A à 1,5 mA. Un dispositif de mesure et d'analyse des SiPM a également été proposé et construit pour évaluer l'injection de photons dans les installations d'OMEGA.

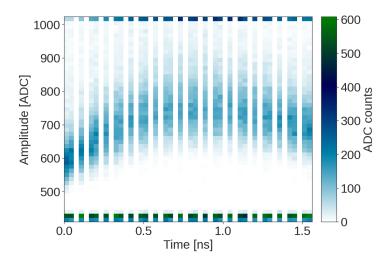

Des essais approfondis en laboratoire des deuxième et troisième versions de la puce sont en cours depuis 2020. La puce présente un haut degré de configurabilité, avec des paramètres permettant d'ajuster le gain, la forme et les seuils temporels, ce qui permet des mesures précises à la fois de la charge et du temps.

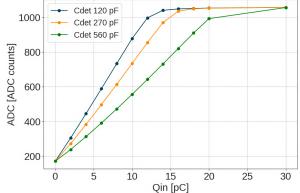

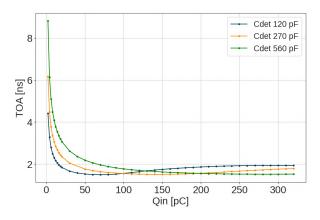

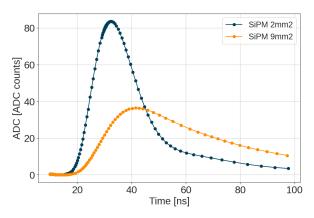

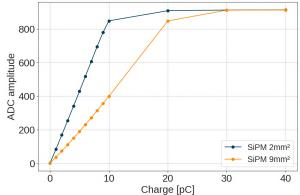

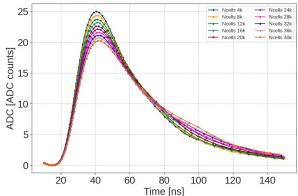

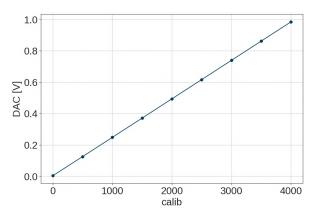

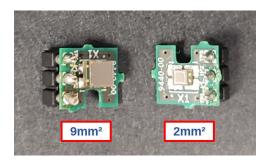

La puce peut lire des charges de 160 fC à 320 pC avec un bruit inférieur à 100 fC, en consommant 11,8 mW par canal. Les circuits d'étalonnage à l'intérieur de la puce permettent la lecture de spectres à photon unique en utilisant la configuration d'étalonnage tout en compensant les variations entre les canaux à l'aide d'un DAC pour la compensation de la tension continue aux entrées du canal. Compte tenu de l'environnement opérationnel de l'expérience, l'ASIC s'est avéré fonctionner efficacement à des températures allant de -39 °C à 50 °C. En ce qui concerne les mesures de temps, l'ASIC a une résolution inférieure à 100 ps. L'ASIC a été testé avec des SiPMs ayant des caractéristiques similaires aux SiPMs finaux de HGCAL avec des surfaces de 2 mm², 4 mm², et 9 mm². L'augmentation de la surface du SiPM produit un bruit electronique plus important, réduit le gain de charge et la résolution temporelle des mesures. Cependant, une plus grande surface de SiPM produit plus de photons à partir du MIP et génère un rapport MIP-bruit plus important. Le choix final des SiPM est à l'étude dans le cadre de l'expérience CMS qui analyse l'utilisation de SiPM de grande surface uniquement.

La caractérisation expérimentale des effets du rayonnement sur l'ASIC a été examinée avec des irradiations TID au CERN. En outre, des tests d'effets à événement unique (SEE) ont été réalisés à l'aide de tests aux ions lourds (effectués au cyclotron de l'UCL à Louvain) et de tests aux protons (effectués à Arronax à Nantes) spécifiquement sur la version Si de l'ASIC afin d'évaluer les blocs partagés avec H2GCROC. L'ASIC s'est avéré tolérant aux radiations jusqu'à 19 Mrad.

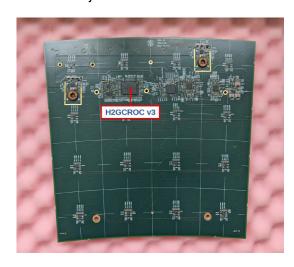

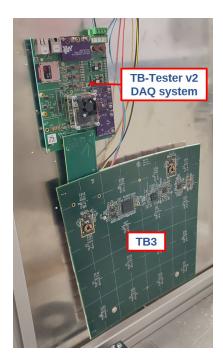

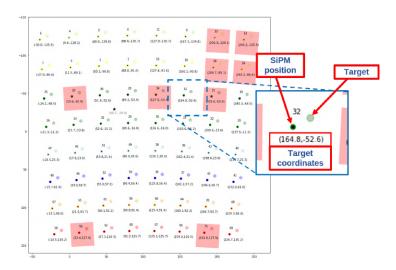

Le faisceau d'essai offre un environnement plus proche de ce qui sera rencontré dans HG-CAL. Les mesures effectuées pendant le faisceau d'essai à DESY ont fourni des données expérimentales cruciales, permettant un examen détaillé des performances de l'ASIC dans un environnement opérationnel réaliste. H2GCROCv3 a lu avec succès les données MIP d'une carte entièrement équipée de SiPMs de 4 mm². La capacité de l'ASIC à mesurer les variations des différents SiPMs connectés à la puce a été analysée en lisant le spectre de photons uniques de chaque SiPM.

En résumé, l'ASIC H2GCROC a démontré sa capacité à répondre aux exigences de l'ex-

périence HGCAL. Cependant, quelques modifications seront nécessaires pour la prochaine version finale de l'ASIC (v3b).

Les travaux menés dans le cadre de ce programme de doctorat ont respecté l'organisation du projet et de la qualité du CERN, y compris les diverses séquences d'examen et les étapes du projet. De plus, les engagements des deux laboratoires, OMEGA et LLR, ont été suivis de près par le responsable de CMS France et la division de physique des particules du DAS de l'IN2P3.

Les recherches menées au cours de cette thèse ont permis de faire progresser de manière significative la compréhension des détecteurs SiPM et de leur conception ASIC dans le contexte de la physique des particules. Cette thèse analyse principalement l'ASIC H2GCROC, justifiant ses choix de conception tout en mettant en évidence ses forces et ses faiblesses. De plus, cette thèse offre des perspectives pour de futures conceptions d'ASIC pour des applications de lecture SiPM.

### **Chapter 1**

### Introduction

#### **Contents**

| 1.1 | Overview                     | 1 |

|-----|------------------------------|---|

| 1.2 | Objectives and Contributions | 2 |

| 1.3 | Thesis outline               | 3 |

#### 1.1 Overview

In the last 15 years, we have entered a new era of precision in measuring particle jet energies. Calorimeters now possess excellent imaging capabilities, allowing us to capture precise information for reconstructing all particles produced in a collision [4]. Nevertheless, the new particle physics projects demand even more precise systems and novel techniques to address existing questions of the standard model of particle physics. Since calorimeters have a limited operational lifetime, replacement becomes necessary, allowing new projects to improve measurement precision and calorimeter capabilities while optimizing particle flow algorithms [5].

The Compact Muon Solenoid collaboration (CMS) experiment has made significant advances and discoveries by characterizing fundamental particles and their interactions as described by the standard model of physics. The detector operates within the Large Hadron Collider (LHC) at CERN. However, despite the excellent results achieved at this collider, there is a need to improve the luminosity reading capabilities by at least an order of magnitude while maintaining high precision to meet the requirements of upcoming complex experiments. The High Granularity Calorimeter (HGCAL) is developing and is expected to be fully operational by 2029 [1]. The HGCAL will increase the calorimeter granularity to enhance the precision while retaining the concept of layer detection.

However, pointing to better detectors also raises expectations for the performance of frontend electronics, particularly in the face of anticipated radiation levels that may be ten times higher than initially experimented in the CMS design [2]. As a result, new Application-Specific Integrated Circuits (ASICs) are under development to detect a broader range of signals, offer improved measurement resolution and enhance the precision of time-of-arrival information. Addressing radiation tolerance and reducing ASIC noise is essential to achieving more precise measurements [5]. Additionally, post-digitization data treatment represents a valuable addition to ASICs, assisting in selecting meaningful data from the increasing number of interactions at detectors and mitigating the data overload resulting from higher luminosity.

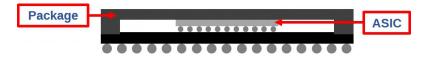

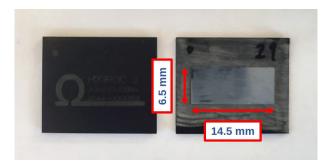

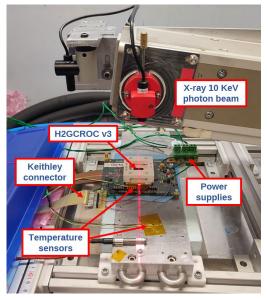

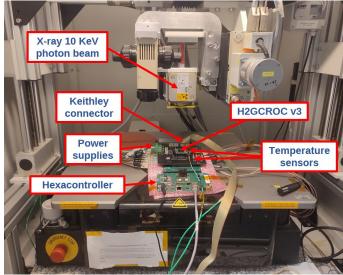

The HGCROC ASICs are dedicated very front-end electronics designed for reading out the

HGCAL, which will replace the current end-cap calorimeters in the CMS experiment at the LHC. The H2GCROC ASIC was specifically designed to read out the Silicon Photo Multipliers (SiPMs) coupled with scintillating tiles in the back hadronic sections, where radiation constraints are less severe. Within the chip, the front-end comprises a current conveyor and a preamplifier intended to capture the high signal levels from SiPMs, with expected charges falling in the range of pC per Minimum Ionizing Particle (MIP). Extensive laboratory testing of the second and third chip versions has been underway since 2020. This work contains an in-depth examination of the very front-end's design and performance, including irradiation campaigns and ASIC performance during beam tests.

The front-end architecture of HGCROC ASICs can read charge data using an ADC and TDC for the time-over-threshold (TOT) technique. A dedicated TDC module provides time information for particles' time-of-arrival (TOA) measurements [3]. The front-end electronics responsible for developing these techniques and modules must meet stringent requirements, including low noise, integral linearity, accurate timing, broad charge dynamic range, rapid shaping time and high radiation tolerance [6].

#### 1.2 Objectives and Contributions

Among the two ASICs developed for reading out the HGCAL detectors, H2GCROC was designed for reading out SiPMs coupled with scintillating tiles in the hadronic calorimeter. The primary objective of this work is to provide insight into the design of this ASIC and to justify the decisions made in both the very front-end and the digital components of the chip. In this manuscript, the reader will gain an understanding of how calorimeters used in particle physics function and their connection to readout ASICs and associated electronics. Then, it will be possible to understand the planned HGCAL experiments that use the SiPM detectors, the H2GCROC ASIC and the primary challenges associated with their design.

From the numerous H2GCROC requirements, the experimental characterization of radiation effects on the ASIC will be deeply examined. Total lonizing Dose (TID) irradiations for H2GCROC were conducted at CERN to assess the chip's performance in the presence of accumulated irradiation damage. Additionally, Single Event Effects (SEE) testing was performed using heavy-ion tests (conducted at the UCL cyclotron in Louvain) and proton tests (conducted at Arronax in Nantes) specifically on the Si-version of the ASIC to evaluate shared blocks with H2GCROC.

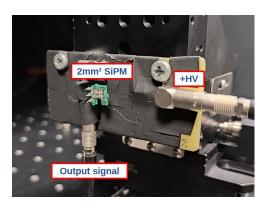

This thesis will delve into the analog design of the ASIC and analyze it using Cadence design tools. The work started with the second version of the chip, which had already been fabricated. Initially, the chip was analyzed to comprehend its structure, and subsequent improvements were implemented. One contribution of this dissertation was modifying certain blocks to rectify irradiation damage correction with irradiated SiPMs. A SiPM measurement and analysis setup was also proposed and constructed to assess photon injection at OMEGA using the fabricated chips. SiPMs with characteristics similar to those explicitly designed for HGCAL were employed in this evaluation.

The work conducted during this Ph.D. program adhered to CERN's project and quality organization, including various review sequences and project milestones. Furthermore, the CMS France manager and the DAS particle physics division of IN2P3 closely monitored the commitments of the two laboratories, OMEGA and LLR.

The research carried out during this Ph.D. program has significantly advanced the understanding of SiPM detectors and their ASIC design in particle physics. This dissertation primarily focuses on analyzing the H2GCROC ASIC, providing justification for its design choices while

1.3. Thesis outline 3

highlighting its strengths and weaknesses. Moreover, it offers insights for future ASIC designs for SiPM readout applications.

#### 1.3 Thesis outline

Chapter 2 provides a comprehensive overview of the physics involved in calorimeter detectors, offering insights into the fundamentals of particle physics. The chapter elaborates on the characteristics of the High Granularity Calorimeter (HGCAL) within the CMS experiment and the specific requirements for ASIC design tailored to the various sensors integrated into the detector.

Chapter 3 of this thesis delves into the comprehensive understanding of SiPM technology and its implications for designing a front-end readout ASIC. Furthermore, it analyzes state-of-the-art ASICs for reading Silicon Photo Multipliers (SiPMs). It explores various front-end techniques in the literature, providing insights into their results, advantages and disadvantages.

Chapter 4 delves into the architecture of the H2GCROC ASIC. It begins by explaining the primary structure of the chip, followed by an in-depth exploration of the very front-end of an H2GCROC channel, including the distinctive characteristics of different analog blocks. Additionally, the chapter analyzes the impact of a SiPM connected in a single channel. Simulation analyses are employed to assess the chip's performance at this stage. Subsequently, the chapter describes the differences between the last two versions of the chip, detailing the modifications made and the reasons behind them. Finally, it provides a comprehensive overview of the calibration processes necessary to utilize the ASIC effectively.

The principal contribution of this dissertation lies in the characterization of the chip. Chapter 5 initiates with an introduction to the various setups used for measuring the ASIC's performance. It then proceeds with an in-depth exploration of the calibration process, accompanied by quantified results before and after calibration. The chapter presents the performance of charge measurement and time resolution derived from measurements conducted on a dedicated test bench employing SiPMs of different sizes. Furthermore, it investigates the diverse functionalities of the chip, starting with charge and time measurements and exploring the diverse ASIC features. Lastly, the chapter offers an overview of the results obtained from irradiation campaigns, supported by corresponding analyses.

Chapter 6 starts with the ASIC's performance during beam tests. It consolidates the main components of the thesis, including the state-of-the-art analysis (Chapter 3), simulation results (Chapter 4) and ASIC characterization results (Chapter 5). It provides overall conclusions and compares the chip's characterization with simulations and project specifications. An analysis of the advantages and disadvantages is conducted by comparing the ASIC's performance with other SiPM readout techniques found in the literature, and avenues for potential improvements are explored.

## **Chapter 2**

## Background of the CMS HGCAL Experiment

#### **Contents**

| 2. | .1 Introduction                                                          |  |

|----|--------------------------------------------------------------------------|--|

| 2. | .2 Standard Model of Particle Physics 6                                  |  |

| 2. | .3 Accelerators for Particle Physics                                     |  |

|    | 2.3.1 The High Luminosity Large Hadron Collider                          |  |

|    | 2.3.2 The Compact Muon Solenoid Experiment                               |  |

| 2. | .4 Calorimeters for particle physics                                     |  |

|    | 2.4.1 The High Granularity Calorimeter of CMS                            |  |

| 2. | .5 Importance of Timing Measurements in High-Energy Physics 16           |  |

| 2. | .6 Role of SiPM Detectors in the CMS HGCAL Experiment                    |  |

|    | 2.6.1 SiPM-on-Tile                                                       |  |

| 2. | .7 Requirements for the very Front-End ASIC for SiPM Readout on HGCAL 20 |  |

| 2. | .8 Conclusion                                                            |  |

|    |                                                                          |  |

#### 2.1 Introduction

Particle physics has always pursued a precise model that understands and predicts our universe's behavior. Humanity continues to approach the most accurate and complex models thanks to the development of new technologies. We seek the smallest and most generic particle that forms everything we know, contributing to a deeper understanding of our world and the universe.

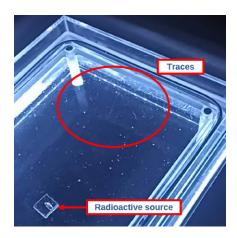

However, a significant challenge with sub-atomic particles is their minuscule size. Over the years, physicists have successfully detected and visualized these particles. Early detectors relied on the human eye to observe traces left by particles passing through specific environments. In 1911, Charles Thomson Rees Wilson introduced the fog chamber [7], which made visible the trails of ions left by ionizing particles. During that era, the traces' distance, thickness, and curvature helped study the particles. Figure 2.1 displays a photograph of a fog chamber reading the traces of particles produced by a radioactive source.

Advanced detectors can now identify and characterize various particles by measuring their energy, momentum and time. Accelerators provide a tool to study the composition of matter.

FIGURE 2.1 – Photograph of a fog chamber and a trace made by a particle coming from a radioactive source.

The fundamental principle involves accelerating elementary particles to speeds close to the speed of light. Consequently, the collision of these particles decomposes them, giving rise to other particles that constitute the matter we observe. Large-scale detectors measure the energy and study the particles created in these collisions. Initially, photographic event collection was utilized in accelerator detectors to reconstruct particles generated during collisions. Presently, recording electronic data opens up numerous possibilities, facilitating high-rate experiments that measure particles with picosecond resolution and offering the potential to discover new particles or interactions.

The existing knowledge about the composition and behavior of matter is consolidated in the Standard Model of particle physics, explaining elementary particles and their interactions. However, despite significant advancements in understanding matter, the Standard Model remains incomplete. Numerous unanswered questions persist, and theories are yet to be proven or refuted.

#### 2.2 Standard Model of Particle Physics

The Standard Model of particle physics is a theory that describes the fundamental interactions and elementary particles. Its development started in 1970, resulting from various theories and experimental studies. The Standard Model's success lies in its ability to predict a broad range of phenomena, approximating the nature at distance scales as small as  $10^{-18}$  m [8]. Much like the periodic table in chemistry enables predictions about the properties of unstudied elements, the Standard Model explains particle interactions and has successfully predicted particles discovered in experiments. Nevertheless, the Standard Model has limitations, forcing the exploration of new theories to achieve a more fundamental theory.

Particle physicists describe nature using four fundamental forces: gravity, the weak force, electromagnetism and the strong force [9].

Gravity defines the attraction between objects with mass, initially described by Isaac Newton in his book Principia Mathematica [10]. Albert Einstein later augmented these observations with his general theory of relativity in 1916 [11], conceptualizing gravity as the curvature of spacetime caused by the mass and energy of objects. While gravity influences the motion of planets, stars and galaxies, it is notably the weakest of the fundamental forces, especially at atomic scales, where other forces overshadow its effects.

The weak force, or weak nuclear interaction, is responsible for particle decay, transforming

one subatomic particle into another. For instance, when a neutrino interacts closely with a neutron, the neutron transitions into a proton, and the neutrino transforms into an electron. This force is also present in the nuclear fusion reactions powering the sun.

The electromagnetic force operates between charged particles, incorporating electric and magnetic forces. The magnetic component acts when opposite charges attract one another, and the same charges are repelled from each other. The electric component creates a field by which the charges can influence each other. Charged particles in motion generate a magnetic field. This force is responsible for friction, elasticity, the normal force and the force holding solids together [9].

The strong nuclear force binds fundamental particles to form larger particles, holding quarks together to create protons and neutrons. It is the strongest fundamental force and part of the force that keeps protons and neutrons within an atom's nucleus.

The Standard Model of particle physics describes all except gravity from the four fundamental forces in the language of quantum gauge field theories. The Standard Model sorts elementary particles based on their charges and outlines their interaction via the fundamental forces. The electromagnetic interaction, governed by quantum electrodynamics (QED), influences particles with an electric charge. The weak interaction, described by quantum flavor dynamics (QFD), influences particles with a weak charge. The weak and electromagnetic forces are unified in the Standard Model through a single electroweak gauge theory. Finally, the strong interaction, governed by quantum chromodynamics (QCD), influences particles with a color charge.

Particles in the Standard Model include fermions and their antiparticles, having equal charge quantities but opposite charges. Fermions, which exhibit half-integer spin, are categorized into quarks and leptons. A spin is the intrinsic angular momentum of a particle. Quarks, such as up (u), down (d), charm (c), strange (s), top (t) and bottom (b), have a color charge and interact with the strong force. Leptons, including the electron (e), muon  $(\mu)$ , tau  $(\tau)$ , electron-neutrino  $(\nu_e)$ , muon-neutrino  $(\nu_\mu)$  and tau-neutrino  $(\nu_\tau)$ , have either a neutral charge (neutrinos) or a negative unity charge. Fermions are organized into three families, featuring two quarks and two leptons. The first family's fermions constitute matter in nature, such as electrons, protons (composed of two u quarks and one u quark) and neutrons (composed of two u quarks and one u quark). The heavier particles of the second and third families are short-lived, decaying into quarks and leptons of the first family via the weak force.

Massless particles called photons  $(\gamma)$  mediate interactions in QED. In QCD, gluons (g), also massless, facilitate interactions by carrying color charge and binding quarks to form hadrons. Baryons, consisting of three quarks with distinct colors, and mesons, comprising one quark and one antiquark, exemplify the particles created through the strong force. The weak force involves interactions mediated by charged  $W^+$ ,  $W^-$  and neutral  $Z^0$  bosons.

While characterized by a high degree of symmetry [8], the Standard Model exhibits symmetry breaking in certain particles due to the Higgs field. Particles interacting with the Higgs field acquire mass, as they cannot travel at the speed of light. The Higgs boson particle (H) couples to any mass particle, including itself [12]. Figure 2.2 illustrates the elementary particles of the Standard Model with their main known characteristics.

The mathematical formulation of the Standard Model is complex. However, it is encoded in a concise four-line description known as the Lagrangian (Equation 2.1). As a quantum field theory, the Standard Model revolves around quantum fields, with particle excitations representing the elementary particles [12]. The Lagrangian delineates the kinematics and dynamics of the quantum system, presented here in a simplified form. It underscores that the Standard Model is grounded in a mathematical framework capable of predicting the behavior of known quantum particles. A more detailed exposition of this formula is available in [12].

#### three generations of matter interactions / force carriers (fermions) (bosons) Ш 1 Ш =2.2 MeV/c =1.28 GeV/c ≈173.1 GeV/d ≈124.97 GeV/c² charge H t C g u spin higgs up charm top gluon **DUARKS** S d b γ down strange bottom photon =0.511 MeV/c2 =105,66 MeV/c2 =91.19 GeV/c2 ≈1.7768 GeV/c е Z μ τ electron muon tau Z boson **EPTONS** ±1 Ve W $\nu_{\mu}$ ντ electron muon tau W boson neutrino neutrino neutrino

#### **Standard Model of Elementary Particles**

FIGURE 2.2 – Summary of the Standard Model of particle physics [13].

$$\mathcal{L} = -\frac{1}{4} F_{\mu\nu} F^{\mu\nu}$$

$$+ i \bar{\psi} D \psi + h.c.$$

$$+ \psi_i y_{ij} \psi_j \phi + h.c.$$

$$+ |D_{\mu} \phi|^2 - V(\phi)$$

(2.1)

The Standard Model is the most important high-energy physics theory but has several limitations. Notably, it lacks a particle for gravitational interactions and explains only 5% of the universe. Dark matter (25%) and dark energy (70%) remain unaccounted for in the Standard Model [12]. Physicists are actively exploring modifications or improvements, with Supersymmetry emerging as one of the theories under consideration. This theory declares a connection between bosons and fermions, introducing new particles that may address some of the Standard Model's problems [8].

#### 2.3 Accelerators for Particle Physics

Particle accelerators play a crucial role in particle physics, taking charged particles to velocities near the speed of light and high energies. These accelerators enable the exploration of particle nature and behavior under extreme conditions, emulating conditions similar to those present in the early universe, such as high energies and low temperatures. Through collisions with targets or opposing particles, accelerated particles generate interactions that help physicists comprehend the properties of matter and the fundamental forces governing our universe.

When particles collide at high energies, they produce more primitive particles that compose the matter. These newly formed particles exist briefly before decaying into other, more common particles. Accelerators precisely measure these newly generated particles' mass, charge and

#### momentum.

There are two primary types of particle accelerators. Linear accelerators (LINACs) employ radiofrequency cavities to accelerate the particles in a straight line, often serving as injectors for larger accelerators. An example is the proposed International Linear Collider (ILC) [14]. Circular accelerators, such as cyclotrons and synchrotrons, utilize magnetic fields to bend particle trajectories in a circular path. As particles follow the same circuit, they gain energy with each revolution. However, the magnetic fields must be robust enough to maintain particles in their circular orbit; otherwise, further energy boosts become unfeasible. Synchrotrons can accelerate particles in opposite directions, leading to collisions within large detectors for energy measurement.

In particle physics, Luminosity is a crucial parameter, characterizing the intensity of particle collisions in an accelerator. It quantifies the rate at which particles collide within a specific volume, offering insights into the performance and capabilities of particle colliders. Luminosity depends on factors such as beam energy, the number of particles in each beam and the cross-sectional area of the beams at the interaction point. Luminosity is measured in units of  $cm^{-2}s^{-1}$ , representing the number of collisions per second in a particle beam with a cross-sectional area. Integrated Luminosity measures the total number of particle collisions accumulated over a specific period in a particle physics experiment and is usually expressed in  $fb^{-1}$ , where 1 fb corresponds to  $10^{-39}\ cm^2$ .

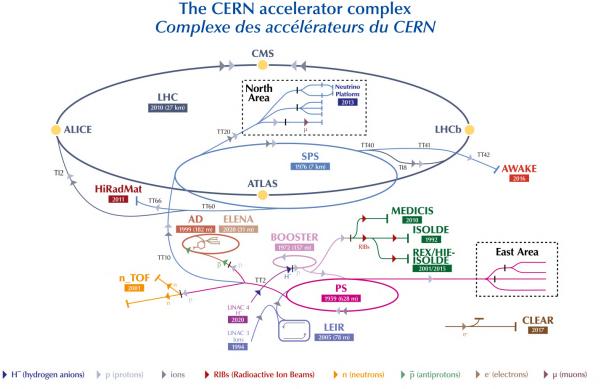

LHC - Large Hadron Collider // SPS - Super Proton Synchrotron // PS - Proton Synchrotron // AD - Antiproton Decelerator // CLEAR - CERN Linear

Electron Accelerator for Research // AWAKE - Advanced WAKefield Experiment // ISOLDE - Isotope Separator OnLine // REX/HIE-ISOLDE - Radioactive

EXperiment/High Intensity and Energy ISOLDE // MEDICIS // LEIR - Low Energy Ion Ring // LINAC - LINear ACcelerator //

n\_TOF - Neutrons Time Of Flight // HiRadMat - High-Radiation to Materials // Neutrino Platform

FIGURE 2.3 - The CERN accelerator complex [19].

One example of an accelerator is the Large Hadron Collider (LHC) [15] of CERN. Operational since 2010, the LHC accelerates proton beams in its underground ring with a diameter of 27 km to a beam energy of 7 TeV. Four main detectors (ALICE, ATLAS, CMS and LHCb) capture energy from proton-proton collisions. The collision energy produced is 13 TeV, with a nominal instantaneous luminosity of  $L=1\times 10^{34}~cm^{-2}s^{-1}$ . In 2012, ATLAS and CMS discovered the Higgs boson, the last missing particle in the current Standard Model of particle physics ([16], [17]). In 2017, the beam cross-section was reduced by 40%, increasing collision probability and producing a luminosity of  $L=1.58\times 10^{34}~cm^{-2}s^{-1}$ .

Figure 2.3 illustrates CERN's accelerator complex. The Linear Accelerator 4 (LINAC 4) [18] accelerates negative hydrogen ions to high energies, serving as the source for LHC's proton beams. Within LINAC 4, hydrogen ions, composed of a hydrogen atom with an additional electron, reach speeds of 160 MeV before proceeding to the Proton Synchrotron booster, which leaves only protons accelerated to 2 GeV to the Proton Synchrotron (PS). After passing through the PS, the particles advance to the Super Proton Synchrotron, reaching up to 450 GeV, ultimately arriving at the LHC, where particles are accelerated to 6.5 TeV and collisions occur at 13 TeV.

#### 2.3.1 The High Luminosity Large Hadron Collider

The LHC stands as one of the most significant achievements in physics in recent years, particularly for its discovery of the Higgs boson. Although the LHC continues to contribute to in-depth investigations of the Higgs boson and the Standard Model, its operation is ending. To address this, the development of the new High Luminosity Large Hadron Collider (HL-LHC) is underway. The HL-LHC is prepared to enhance measurements within the Standard Model and facilitate explorations of physics beyond its confines.

The primary objective of the HL-LHC is to achieve a peak luminosity of  $L=5\times 10^{34}~cm^{-2}s^{-1}$ . In its initial operations, the LHC achieved 20 collisions per bunch crossing (BX = 25 ns). Subsequently, the number of collisions per BX increased to 60 in 2017. Projections for the HL-LHC anticipate reaching 140 collisions per BX with a peak at 200 collisions. The goal is to reach an integrated luminosity of 300 fb<sup>-1</sup> annually, accumulating to 3000 fb<sup>-1</sup> after a decade of operation. These ambitious objectives necessitate upgrading key components, including new-technology superconducting magnets and current leads [20].

The anticipated increase in Luminosity will improve the precision of couplings between particles. This enhancement is crucial for meticulously measuring the properties of the Higgs boson, as any deviations from the Standard Model could indicate the existence of new physics. Additionally, the HL-LHC is pointed to investigate the rare decay  $H \to \mu\mu$  involving particles of the second family. Moreover, the upgraded Luminosity opens avenues for exploring theories involving extra dimensions or Supersymmetry. There is considerable anticipation surrounding Supersymmetry studies, as it is believed to represent the next phase beyond the Standard Model, providing explanations for the light mass of the Higgs boson and offering a potential candidate for dark matter [20].

#### 2.3.2 The Compact Muon Solenoid Experiment

The Compact Muon Solenoid (CMS) experiment is situated at CERN's LHC, approximately 100 meters underground near the French village of Cessy [21]. Its primary goal is to understand the nature of electroweak symmetry via the Higgs mechanism. Additionally, it actively seeks discoveries that could validate novel theories, such as Supersymmetry or those involving

extra dimensions. It investigates the particles that can be produced at the TeV energy scale to accomplish those objectives.

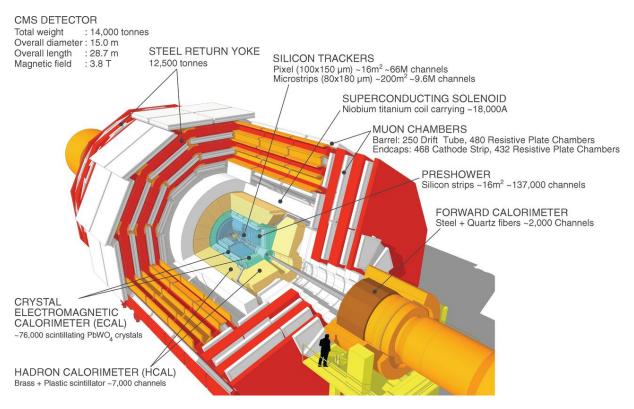

The CMS detector employs a trace detection concept featuring multiple layers to capture collisions-generated particles. Protons, accelerated by the LHC, collide at high energies near the CMS detector's focal point. Figure 2.4 provides a 3D view of the CMS detector. The initial LHC design aims to generate 20 collisions every 25 ns, producing approximately 1000 charged particles. Managing this amount of data and overcoming pileup effects needs high-granularity detectors with excellent time resolution. Consequently, the detector comprises millions of detector channels requiring meticulous synchronization [21].

FIGURE 2.4 – 3D view of the CMS detector showing its main components [22].

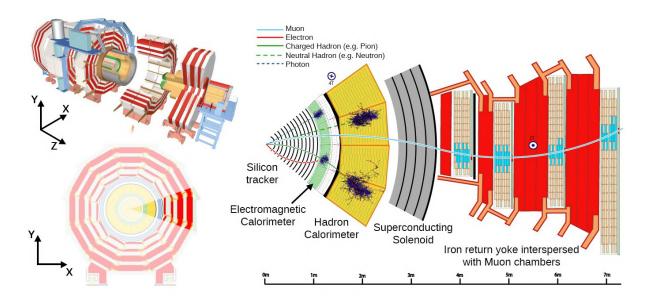

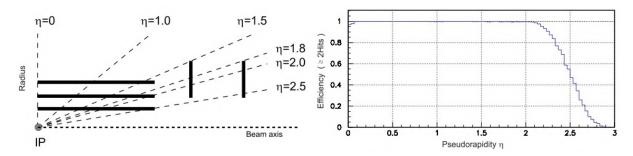

Figure 2.5 illustrates one slice of the CMS detector. A 4-T superconducting solenoid magnet is placed at the detector's center, bending the paths of charged particles to measure their momentum. At the magnet's core, the detector includes a Tracker detector, an Electromagnetic Calorimeter (CE-E) and a Hadron Calorimeter (CE-H). Surrounding the magnet are muon chambers and the Forward Calorimeter. In addition to particle energy, the pseudorapidity  $\eta$  is a valuable variable expressing the particle's trajectory angle relative to the beamline. The CMS tracking system aims for high-resolution and efficient reconstruction of electrons, hadrons and muons, achieving better than 98% efficiency with  $|\eta| < 2.5$ .

Given the LHC's collision rate of every 25 ns, the trigger system plays a crucial role in discriminating relevant data. Based on silicon detector technology, it quickly chooses relevant events for further analysis, reducing the vast data rate to approximately 100 events per second [21]. Figure 2.6 depicts the pseudorapidity coverage of the inner tracker.

The CE-E is a hermetic homogeneous calorimeter made of Lead-tungstate crystals. The configuration of the magnetic field and the radiation levels in the different parts of CE-E led to the use of Avalanche Photodiodes (APDs) in the central barrel part and vacuum phototriodes (VPTs) in the endcaps [21]. The CE-H employs plastic scintillators to measure hadron jets,

FIGURE 2.5 - Summary of particle detection in one slice of the CMS detector [23].

FIGURE 2.6 – Geometrical layout of the pixel detector of the CMS tracker and hit coverage as a function of pseudorapidity  $\eta$  [21].

neutrinos and exotic particles through missing transverse energy.

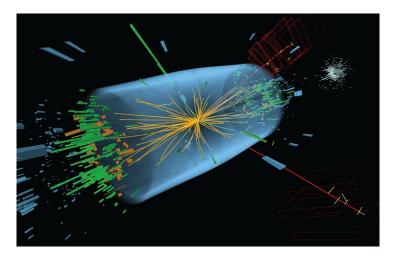

FIGURE 2.7 – Event recorded with the CMS detector in 2012 from a proton-proton collision at the energy of 8 TeV. It shows an event of the Higgs boson decay to a pair of Z bosons that subsequently decay to a pair of electrons (green lines) and a pair of muons (red lines) [22].

The muon system serves three primary purposes: muon detection, momentum measurement and participation in triggering. Gaseous particle detectors assist in muon identification, enabling the system to detect processes like the anticipated decay of  $H \to ZZ$  or  $H \to ZZ*$ , resulting in four leptons. Figure 2.7 presents an example of an event recorded with the CMS detector in 2012 from a proton-proton collision at an energy of 8 TeV. It depicts an event of  $H \to ZZ$  that subsequently decays into a pair of electrons, visible as green lines in the center, and a pair of muons passing through the detectors, presented as red lines.

#### 2.4 Calorimeters for particle physics

Calorimeters are detectors designed to measure the energy of high-energy particles produced in particle collisions. Following a collision, particles deposit their energy in various detectors as they pass through the calorimeter. Different particles interact with different materials, and the measured energy reflects the total absorption in matter. When a high-energy particle interacts with the absorber material, it initiates a shower of secondary particles.

The absorber material is enveloped by an active medium sensitive to the produced secondary particles. The active medium absorbs the energy and simultaneously generates the measured signal. The active medium can be scintillating crystals, liquids, or gaseous detectors. The signals generated are proportional to the energy deposited by the incident particles. For example, calorimeters using scintillating crystals read the light emitted from the scintillation process, with the light's intensity being proportional to the deposited energy. These signals can then be detected by photomultiplier tubes or silicon photomultipliers (SiPMs) and converted into measurable quantities.

In high-energy physics detectors, a shower's energy is determined by the full jet measured in the calorimeter's active material. Both tracking detectors and calorimeters are essential for event reconstruction since neutral particles produce a signal only in calorimeters. Simultaneously, momentum measurements obtain the energy of all other charged particles in the tracker with better resolution than calorimeters. Ultimately, both detectors must combine the information of measured signals, and the total reconstructed energy is the sum of all particle energies [5].

Calorimeters require precise calibration to convert the produced signals into accurate energy measurements. Typically, the detector is calibrated using known energy sources or standard particle beams.

There are two types of calorimeters: Electromagnetic and Hadronic Calorimeters. Electromagnetic calorimeters are optimized to measure the energy of electrons and photons. They employ materials that interact strongly with these particles, leading to the production of electromagnetic showers. Electrons and positrons are generated in electromagnetic showers and create more through ionization and radiation, forming a cascade of particles or showers. In contrast, Hadronic Calorimeters are designed to measure the energy of hadrons such as protons, neutrons, or mesons. They utilize dense materials that interact strongly with hadrons.

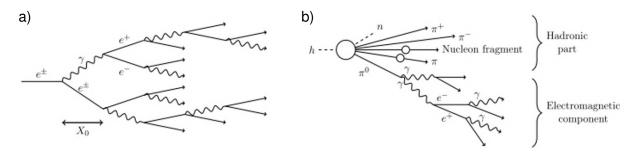

The main interactions of particles measured by calorimeters are electromagnetic and hadron showers. Electromagnetic showers are initiated by a photon entering the calorimeter volume, as depicted in Figure 2.8 a). In this type of shower, secondary particles lose most of their energy through direct ionization, annihilation for positrons and Coulomb-scattering for photons. Afterward, no additional secondary particles are generated, and the electrons and positrons are captured within one radiation length. Contrarily, hadron showers (Figure 2.8 b)) involve strong interactions with the absorber nuclei. The initial energy produces secondary particles generated in nuclear reactions, traveling a longer distance than in electromagnetic showers [5].

FIGURE 2.8 – Formation of showers in the calorimeter. a) Electromagnetic shower. b) Hadronic shower with the electromagnetic component [5].

#### 2.4.1 The High Granularity Calorimeter of CMS

With excellent imaging capabilities, Calorimeters capture precise information to reconstruct all particles produced in a collision. However, new particle physics projects require even more precise systems with novel techniques and methods to address existing questions about the current Standard Model.

Electronic laboratories are actively developing more precise technology and circuit designs to enhance collider resolution in the search for new physics. As classical calorimeters become outdated, ongoing projects aim to improve measurement precision by optimizing particle flow algorithms. The new calorimeters must be highly granular in imaging detection, incorporated into compact systems [5].

The CMS experiment continues to make significant advances and discoveries, describing the observed fundamental particles and their interactions within the Standard Model. Currently, the detector is operating at the Large Hadron Collider at CERN. However, although this collider has achieved excellent physics results, the new HL-LHC points to developing better detectors that can manage the increasing Luminosity and read the collisions per bunch crossing to fulfill the specifications of the new and complex future experiments planned. The HL-LHC will have ten times more Luminosity than the current LHC, creating challenges such as higher radiation levels, more simultaneous interactions and increased particle fluxes [6]. The High Granularity Calorimeter (HGCAL) is currently under development and is expected to start operations in the new HL-LHC in 2029.

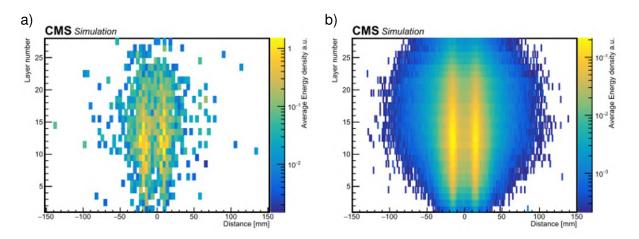

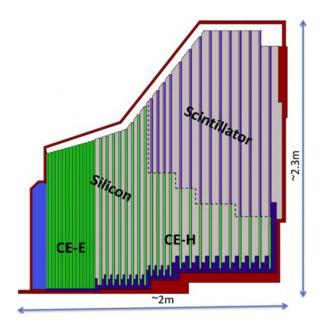

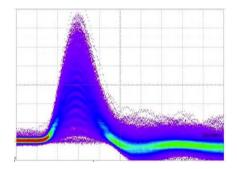

The HGCAL is an imaging calorimeter comprising an electromagnetic and hadronic compartment. The complexity of calorimetry provides substantial information for pattern recognition in experiments [1]. Figure 2.9 illustrates the simulated energy deposits from photon showers in a CMS simulation of HGCAL. The HGCAL offers information in five dimensions : energy, x, y, z and time. This information is ideal for particle-flow reconstruction, enabling the individual reconstruction of electromagnetic and hadronic showers. The tracker allows for the refinement of electron and converted photon reconstruction. The calorimeter's granularity also facilitates excellent identification of electrons, protons and muon performance [1].

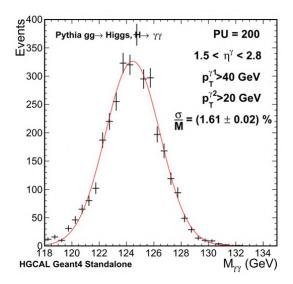

One example of calorimeter performance is shown in Figure 2.10, where the reconstructed mass of photon pairs from  $H\to\gamma\gamma$  is noticeable [1].

HGCAL plays a crucial role in identifying and measuring quarks, gluons and neutrinos by determining the energy and direction of jets and missing transverse energy flow in events. Silicon detectors will read the particle energy produced by the collision in the CE-E and front part of CE-H, and silicon photomultipliers will be used in the back hadronic part.

A photomultiplier consists of a photocathode and an electron multiplier. Photons absorbed in the photocathode release electrons proportional to the number of photons coming from the

FIGURE 2.9 – Energy deposited in HGCAL cells by pairs of unconverted photons; a) a single event containing a pair of photons; b) several thousand of such events [2].

FIGURE 2.10 – Reconstructed mass of photon pairs from  $H \to \gamma \gamma$  [2].

scintillator; the electrical signal is a current pulse proportional to the particle's energy. This current pulse, integrated over time, contains the signal charge. The pulse shape does not change with the charge; only the peak amplitude changes and provides information about the signal charge [24]. The two ASICs developed by OMEGA facilitate the readout of the HGCAL detectors. HGCROC reads out the silicon pads of the electromagnetic and front hadronic sections, while H2GCROC reads out the SiPMs coupled to the scintillating tiles of the back hadronic sections.

Table 2.1 details the number of channels and corresponding ASICs for each part of the calorimeter. The back hadronic part is expected to have around 9000 ASICs to read out the more than 380,000 SiPMs on the plastic scintillators [2]. Scintillation detectors use indirect detection, converting absorbed energy into visible light. The number of scintillation photons is proportional to the absorbed energy. Subsequently, the photomultiplier detects the scintillation light.

|                        | CE-E  | CE-H  |              |

|------------------------|-------|-------|--------------|

|                        | Si    | Si    | Scintillator |

| Area [m²]              | 368   | 215   | 487          |

| Channels [k]           | 3916  | 1939  | 389          |

| Si modules (Tileboard) | 16008 | 8868  | (3960)       |

| Partial modules        | 1008  | 1452  | -            |

| 72 channel ASICs       | 60324 | 31596 | 8496         |

TABLE 2.1 - HGCAL number of channels and ASICs. [2].

#### 2.5 Importance of Timing Measurements in High-Energy Physics

The time data can be used to implement software compensation for the calorimeter response, assisting in the event reconstruction. Simulations presented in [25] demonstrate how the time compensation may improve the shower decomposition in the particle algorithm, reducing the process's uncertainties.

Performing a time-of-arrival measurement in a calorimeter layer allows us to assign a precise time for both charged particles and photons. This information, coupled with energy measurements, reduces the inclusion of pileup particles in event reconstruction, as the spread of the collision time of pileup interactions is about 200 ps [26].

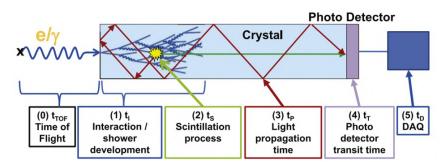

FIGURE 2.11 – Schematic of the most relevant contributions of timing measurements in a monolithic, large scintillating crystal [26].

The time scales associated with the timing measurement using a monolithic crystal calorimeter are displayed in Figure 2.11. When the photon or electron enters the crystal, it travels at the speed of light, interacting and creating a shower-producing scintillation light. The time  $t_l$  corresponds to the time between the entry of the photon and the first interaction. The scintillation process has a duration of  $t_S$ . The time  $t_P$  is associated with the propagation of the scintillation light from the point of interaction to the photodetector. After that, the photodetector converts the scintillation light into an electrical signal. The duration of this process corresponds to the photodetector signal transit time  $t_T$ . Finally, the time necessary for the data acquisition (DAQ) is the  $t_D$ . All these periods contribute to the total time resolution. The new information will improve the datasets necessary to perform precise measurements of the Higgs couplings, probe rare Higgs processes, study W bosons and search for physics beyond the standard model [26].

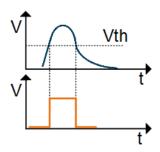

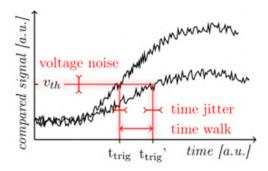

Challenges in timing measurements for particle physics are numerous, considering factors such as photon statistics, photon transport, rise time, decay time and the quantum efficiency of photodetectors. It has been observed [27] that a circuit, including an amplifier connected to a discriminator, can mitigate the effects of these factors, leading to improved timing measurements for SiPM.

However, timing measurements for particle physics face a unique challenge, as the delay and jitter of ASICs can be on the same order of magnitude as the timing resolution. Increasing the resolution of the next stage (time-to-digital converter) requires a significant increment in area and power consumption. A potential solution is to enhance the conditioning of the input signal, reducing noise and improving linearity in the first stage of the chain [28].

The jitter can be measured with the time difference between the chip's output signals and the trigger from the wave generator. The time resolution depends on the threshold level settings. Thus, the threshold must be lower than the Minimum Ionizing Particle (MIP). The noise of the readings sets the limitation for threshold position. The precision of timing measurement depends on the intrinsic performance of the complete chain, encompassing the sensor, amplifier, discriminator and TDC, together with the clock distribution system [1].

FIGURE 2.12 – Hits of a vector boson fusion  $H \to \gamma \gamma$  event with charge > 12 fC; a) without timing requirement and b) after removal of hits with  $|\Delta t| > 90 \ ps$ . [2]

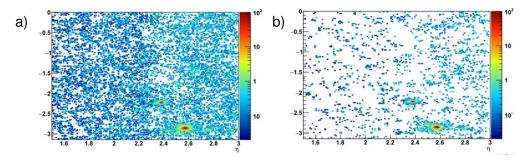

In Higgs boson production, the vertex that decays into two photons poses a significant challenge to measure accurately. Timing information can be utilized to localize the vertex [29]. For example, Figure 2.12 illustrates the hits with charge > 12 fC of a vector boson fusion  $H \to \gamma\gamma$  event. Figure 2.12 a) shows all the pileups without a timing requirement, and Figure 2.12 b) demonstrates the improved jet reconstruction and energy estimation after removing hits with  $|\Delta t| > 90~ps$  due to time discrimination, resulting in less impact from complete pileup [1].

#### 2.6 Role of SiPM Detectors in the CMS HGCAL Experiment

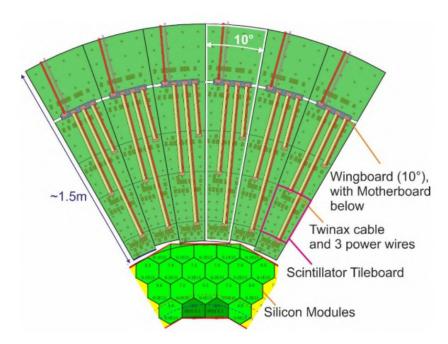

The new HGCAL (Figure 2.13) comprises two endcaps, each with 26 electromagnetic layers and 21 layers of the hadronic calorimeter. The CE-E region and the first part of the CE-H will use hexagonal silicon modules with more than 6 million detector channels in approximately 620 m² of silicon. The layers combine silicon modules with trapezoidal scintillator modules in the back part of the hadronic calorimeter. The scintillator modules are composed of Tileboard printed circuit boards (PCBs) that use plastic scintillator tiles and SiPMs containing 380,000 detector channels in a scintillator area of approximately 480 m² [30].

The irradiation levels expected at the experiment defined the decision to use silicon detectors and SiPMs. SiPMs were placed in every part of HGCAL where they can operate and maintain good behavior after the expected radiation. Tileboards of different sizes are connected to form a 10° detector unit. Six units are placed next to each other and assembled with silicon modules into cassettes that cover 60°. Six cassettes complete the calorimeter around the beam. Figure 2.14 presents one of the 60° cassettes with silicon modules and Tileboards. In HGCAL, the detectors will be operated at -30 °C and have a magnetic field of up to 3.8 T. The cooling of the Tileboards is made by a copper layer where the boards are mounted [30].

FIGURE 2.13 – Side view of the High granularity calorimeter of CMS [31].

FIGURE 2.14 – Top view to a mixed 60 ° cassette of a detector layer, including scintillator tile-boards of the CE-H on top and the silicon modules of the CE-E at the bottom [30].

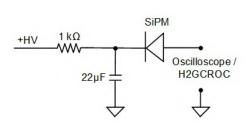

The Tileboards are designed in 8 different sizes to build the cassettes. The number of SiPMs on a Tileboard varies from 48 to 96. The H2GCROC ASIC can read up to 72 channels so some Tileboards will use two H2GCROC ASICs. Linear regulators generate all noise-sensitive supply voltages of the chip. The power of the Tileboards is made thanks to two DC-DC converters (bPOL12 [32]) that take 10 V as input and provide voltages of 1.5 V and 3.3 V. The ASIC ALDO2 [33] generates the SiPM bias voltage. The Tileboard uses the GBT-SCA [34] that monitors all supply voltages, SiPM bias voltage and temperature, and communicates with the H2GCROC ASIC.

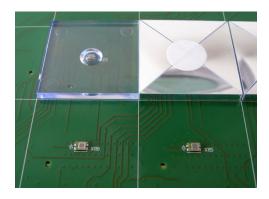

#### 2.6.1 SiPM-on-Tile

The SiPM and the tile form the SiPM-on-tile detector; Figure 2.15 presents the tile design. They have a cavity for the SiPMs and will be individually wrapped. Each detector on the board has an ultraviolet LED next to the SiPM. This LED is used for calibration and to monitor the SiPM gain. The H2GCROC can trigger the LED system to send an optical pulse of 6 ns into the scintillating tiles. An external DC voltage from the motherboard adjusts the LED's voltage amplitude to control the light intensity.

FIGURE 2.15 – CALICE scintillator tiles with a central dimple, wrapped and unwrapped, mounted on SiPMs and used as a prototype for the HGCAL project [35].

The measured noise depends on the gain configured in the H2GCROC ASIC and the capacitance of the SiPM, which increases with the area. In HGCAL, regions with higher radiation levels will experience more damage to the scintillator and the SiPM. Therefore, the detectors must capture as many photons from the scintillator as possible in these zones. The number of photons captured increases linearly with the SiPM area, while the noise increases only with the square root of the SiPM area.

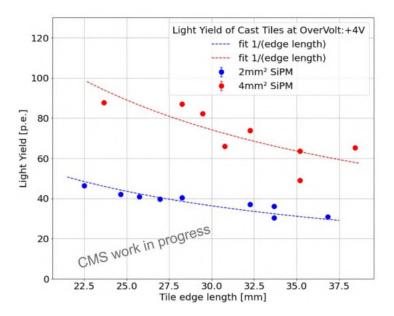

Although larger SiPMs produce a higher signal-to-noise ratio (SNR), smaller SiPMs are cheaper. During the project definition stage, two SiPM areas were selected : 2 mm² and 4 mm². The smaller SiPMs were planned to be used in areas with lower radiation levels. The two SiPM sizes were compared by calculating the Light Yield of both detectors. The Light Yield utilizes the amplitude signal generated by the MIP and the SiPM gain obtained from calibration using the following equation :

$$Light\_Yield[p.e.] = \frac{MIP_{amplitude}[ADC]}{SiPMgain[ADC/p.e.]}$$

(2.2)

The system is designed to have a SNR > 3 for the MIP during the HGCAL lifetime [36]. From the H2GCROC ASIC, the MIP is measured in ADC counts, and the SiPM gain is the ADC counts produced by one photon. The SiPM-on-tile with SiPMs of the selected areas was analyzed in [30]. Figure 2.16 presents the Light Yield measured in photons; The larger SiPM produces a higher Light Yield even with the noise increment coming from its higher capacitance. This increment comes from the large amount of light absorbed by the large detector area.

The increase in Light Yield observed in larger SiPM detectors led to a discussion on incrementing the selected SiPM areas for the calorimeter. Recent test measurements aim to use 9 mm<sup>2</sup> SiPMs for all scintillator tiles, as the price difference compared to 2 mm<sup>2</sup> and 4 mm<sup>2</sup> SiPMs was found to be relatively small [37].

The information from each H2GCROC is sent by two data e-links and four trigger e-links at 1.28 Gbps. The ECON-D reads the data links and performs zero suppression before trans-

FIGURE 2.16 – Light Yield of scintillator tiles using the 2 mm<sup>2</sup> and 4 mm<sup>2</sup> SiPMs [30].

mission. The ECON-T takes the trigger information from H2GCROC to select and compress interesting data using preprogrammed trigger algorithms. One LpGBT ASIC [38] per ECON board collects the data.

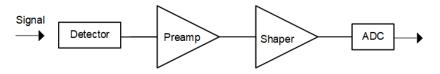

## 2.7 Requirements for the very Front-End ASIC for SiPM Readout on HGCAL

Pointing to the best detectors also increases expectations for the behavior of front-end electronics, especially regarding radiation levels. For this reason, new chips are being developed to handle the increased amount of data at faster speeds, improving radiation tolerance and reducing noise for precise measurements. Application-specific integrated circuits (ASICs) for particle physics require an analog front-end to convert the charge signal to a voltage with a defined shape, enabling digitization with the use of analog-to-digital converters (ADCs) [5]. The front-end electronics must generate output signals with low noise, a large dynamic range, integral linearity and high-precision time measurements.

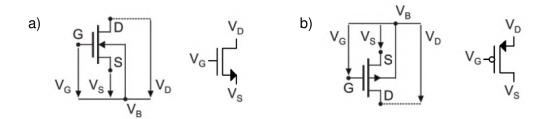

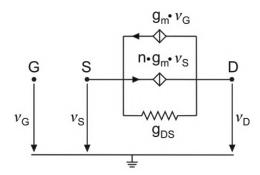

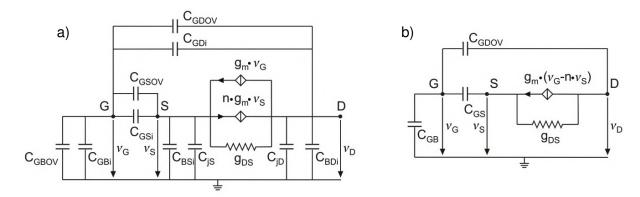

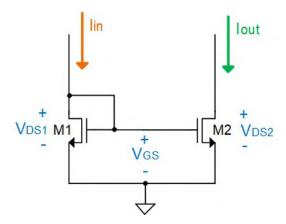

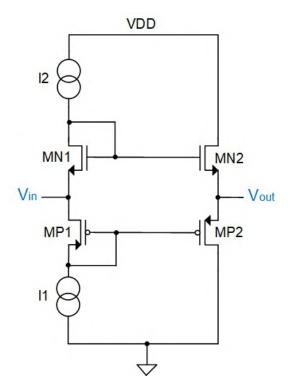

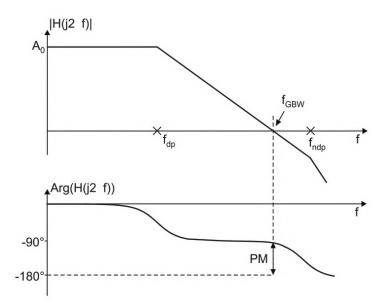

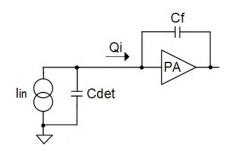

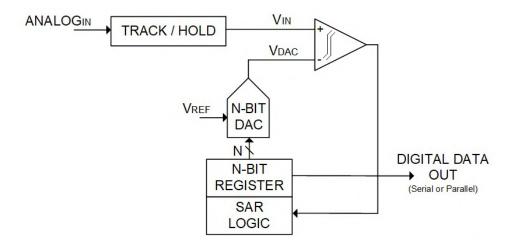

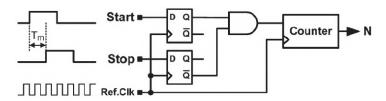

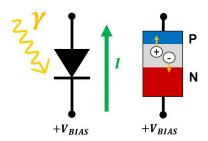

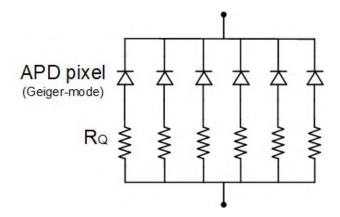

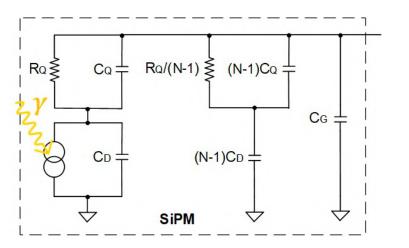

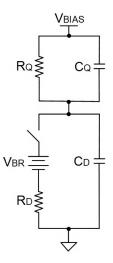

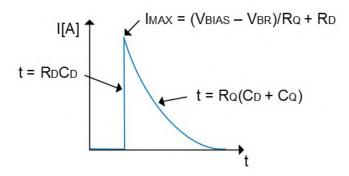

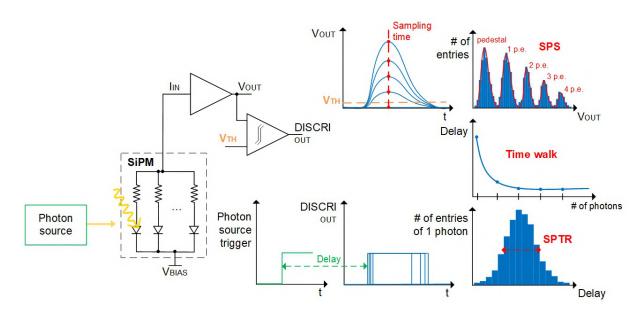

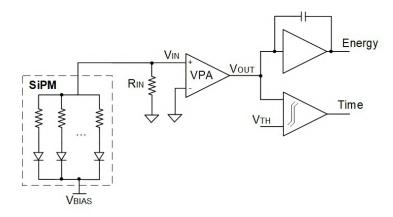

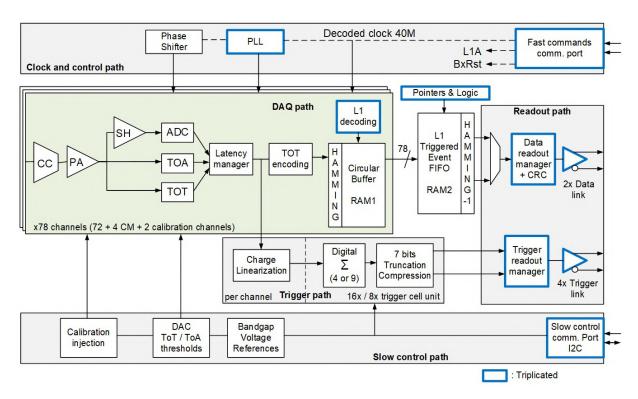

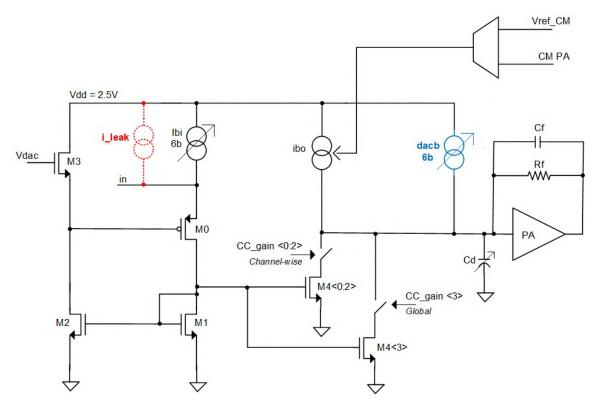

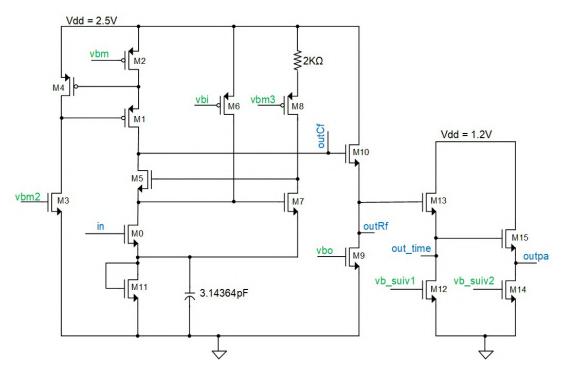

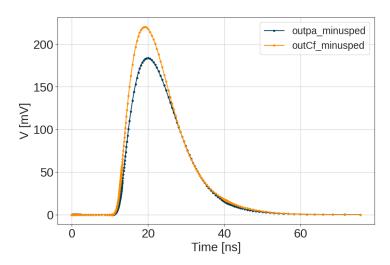

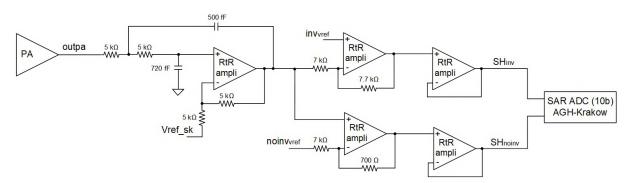

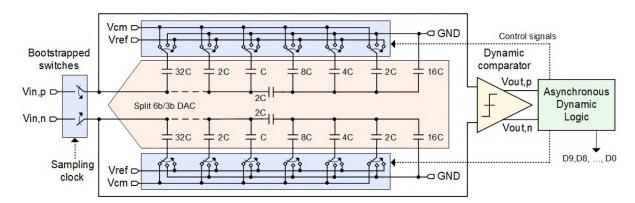

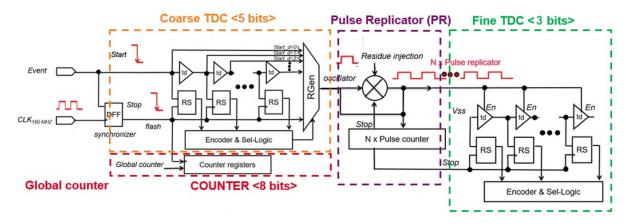

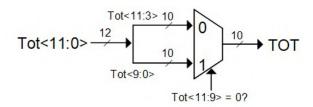

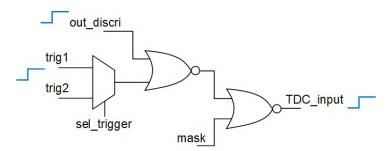

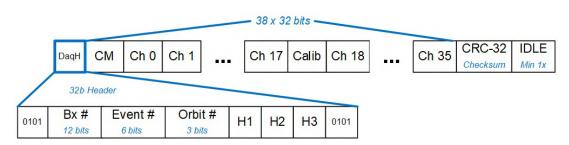

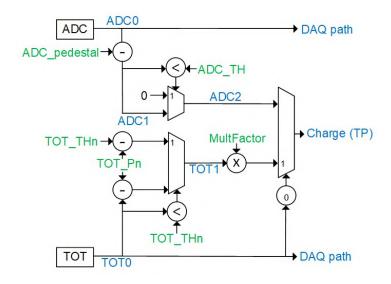

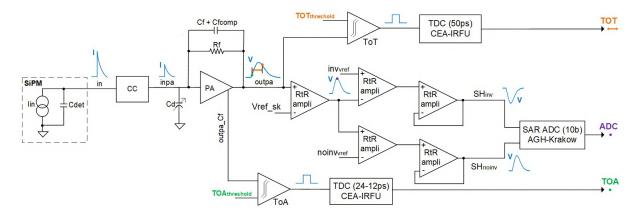

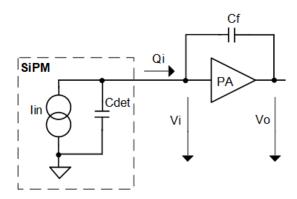

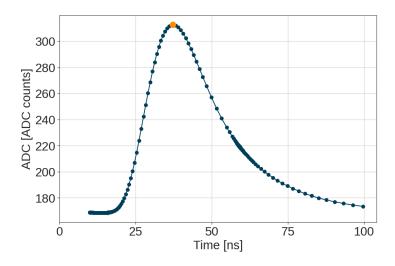

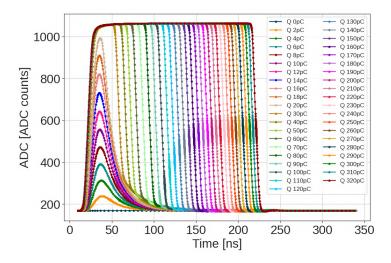

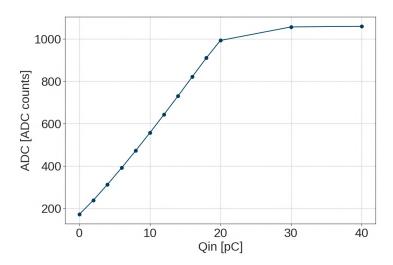

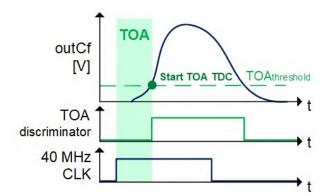

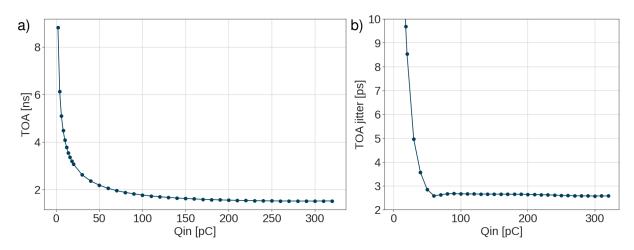

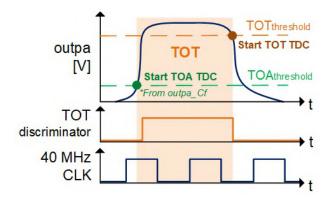

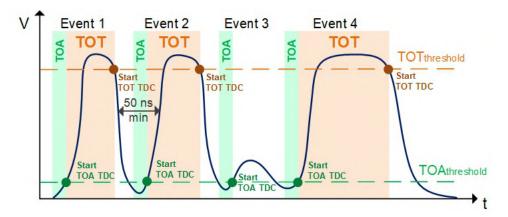

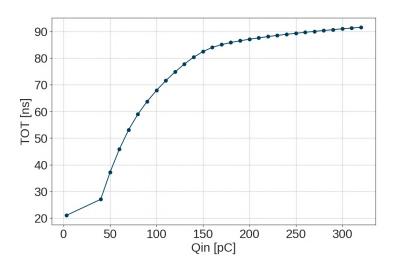

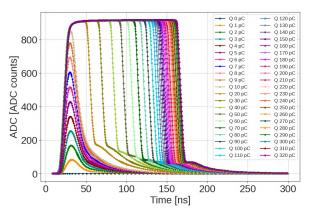

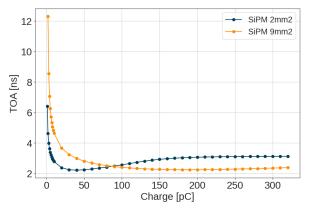

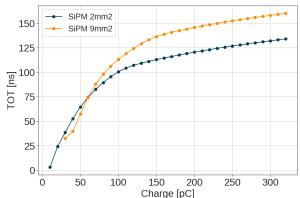

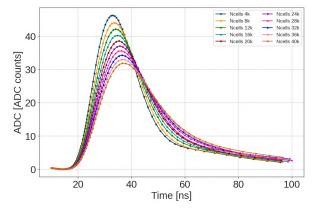

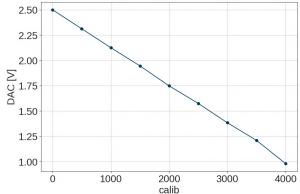

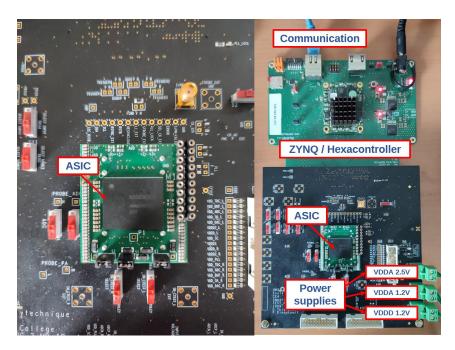

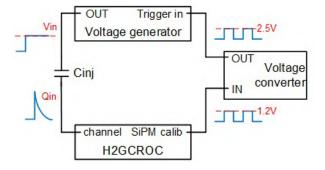

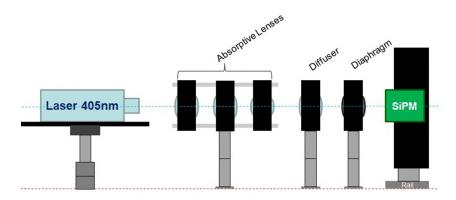

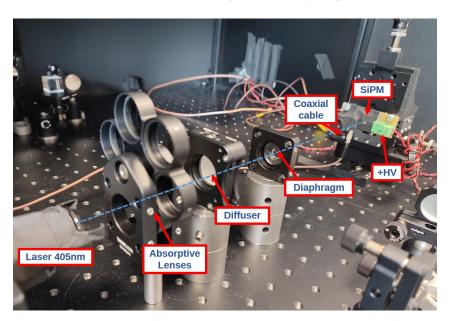

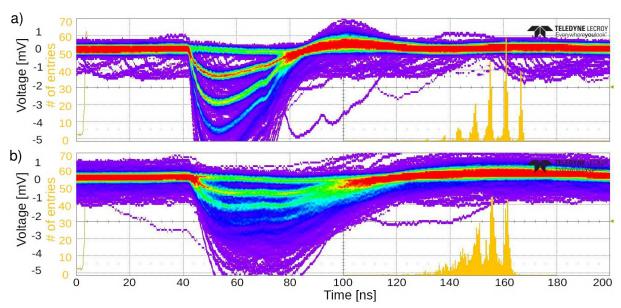

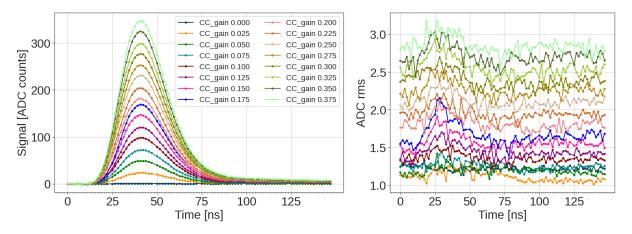

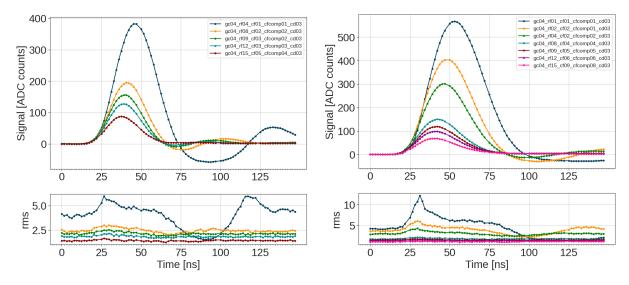

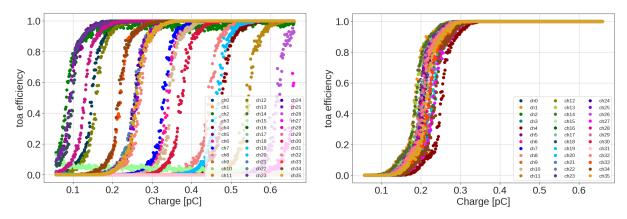

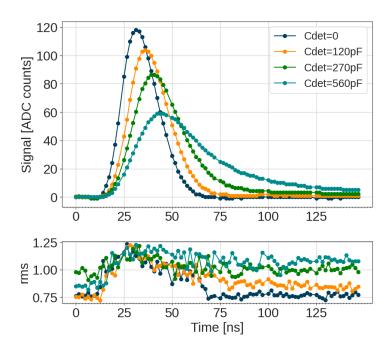

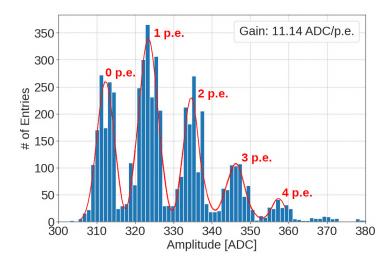

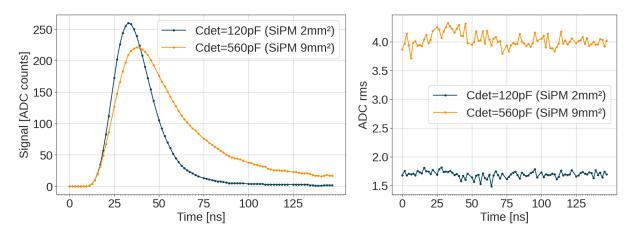

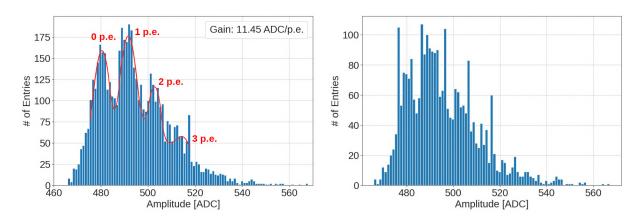

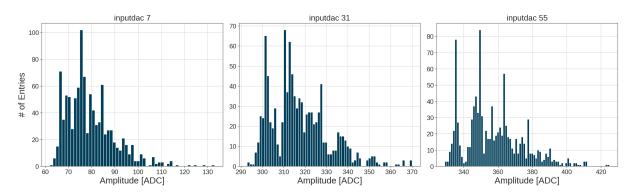

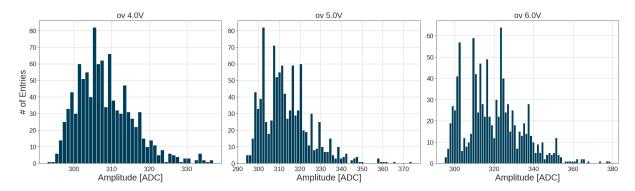

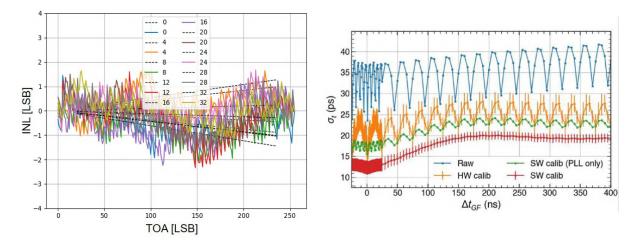

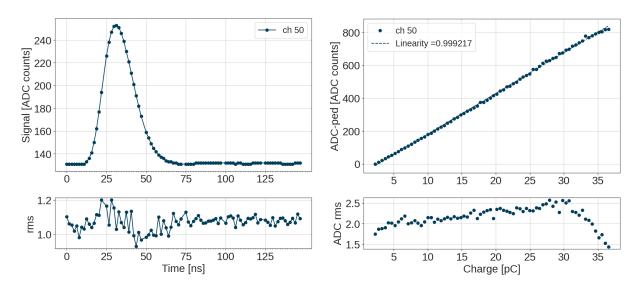

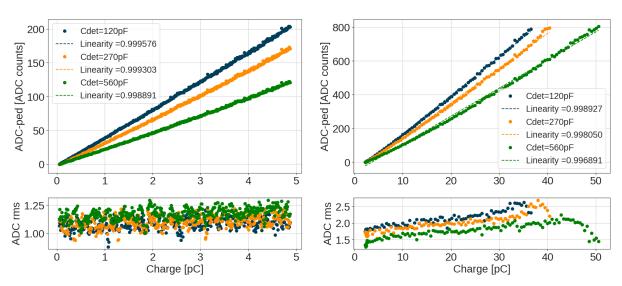

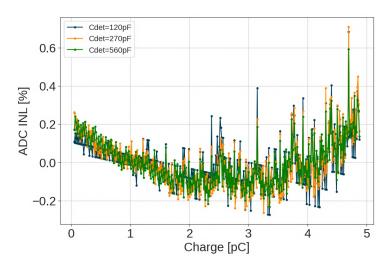

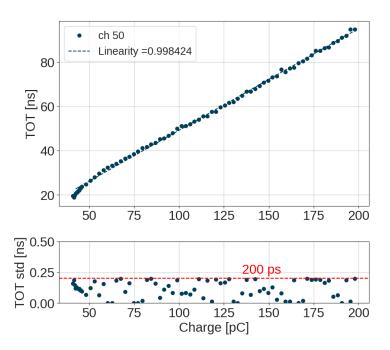

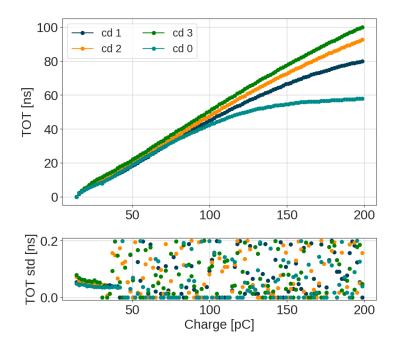

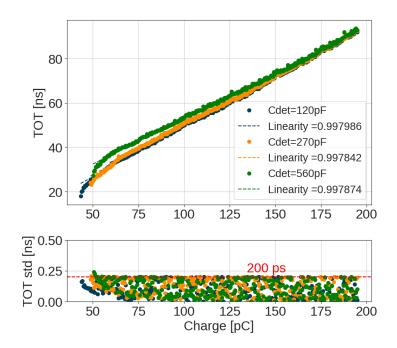

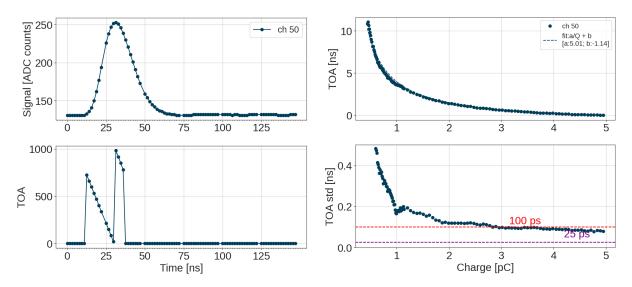

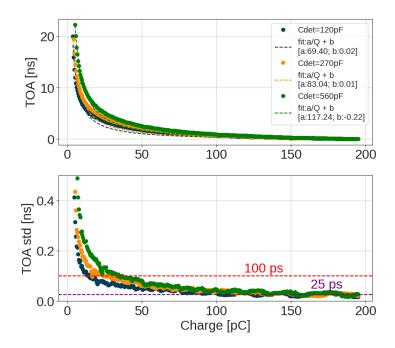

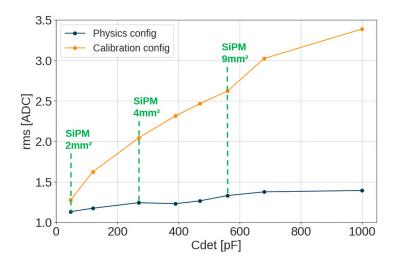

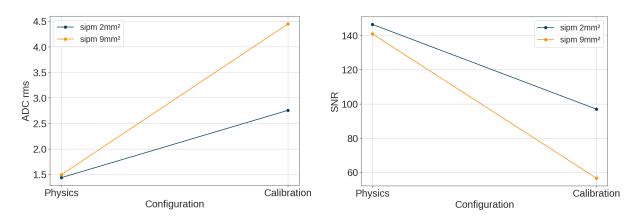

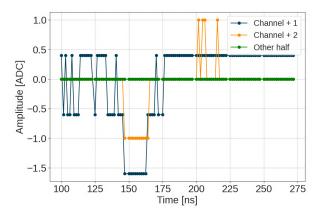

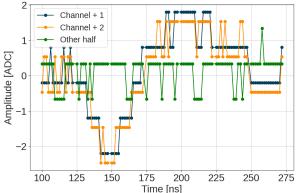

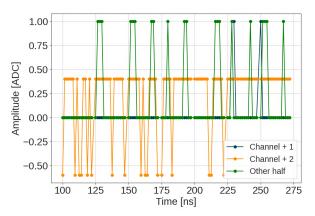

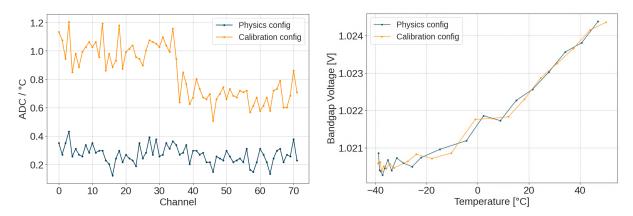

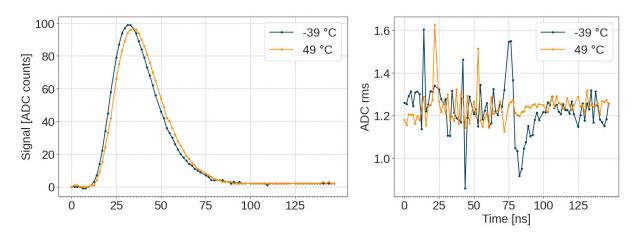

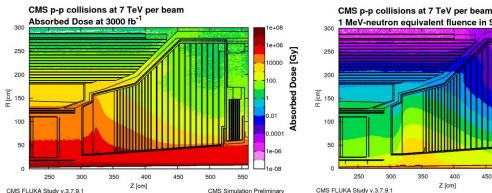

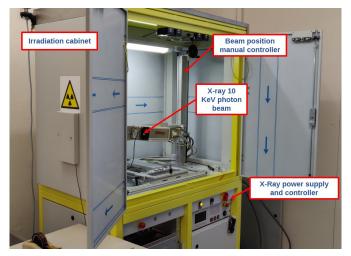

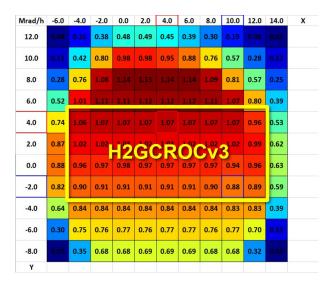

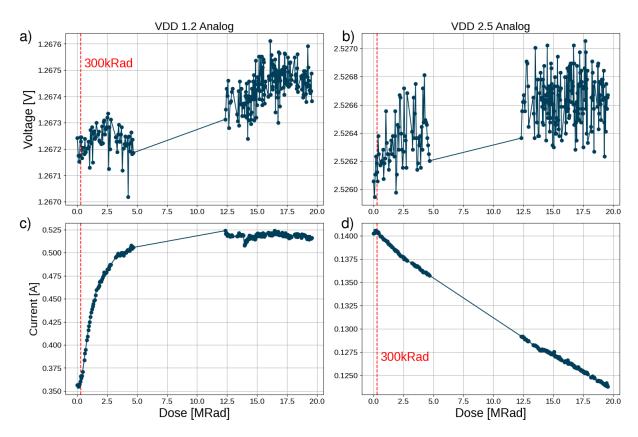

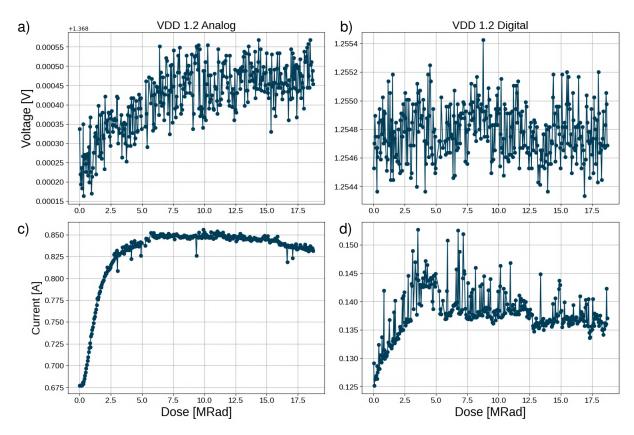

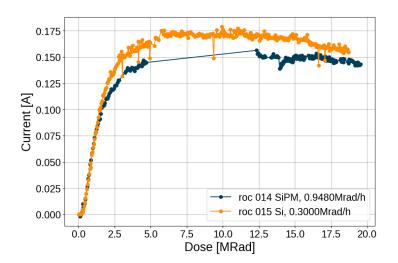

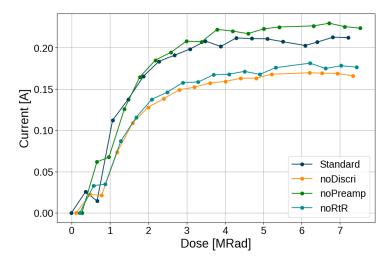

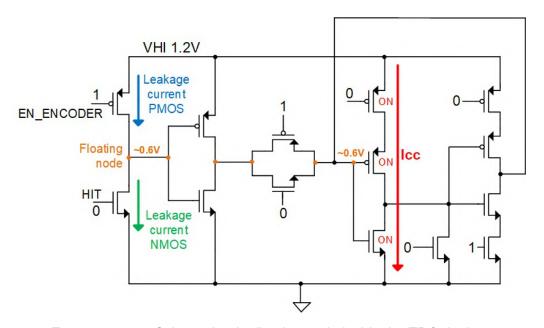

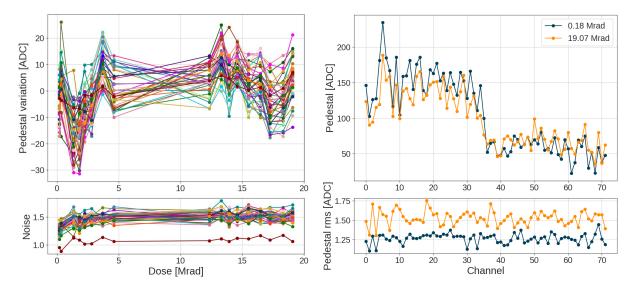

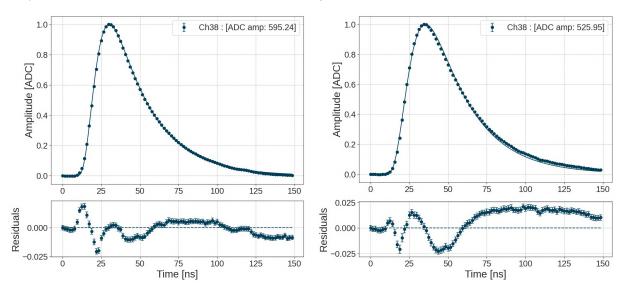

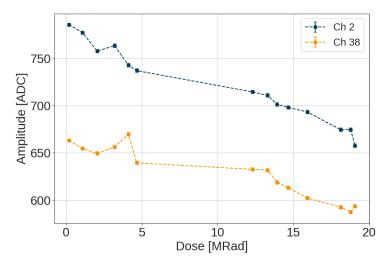

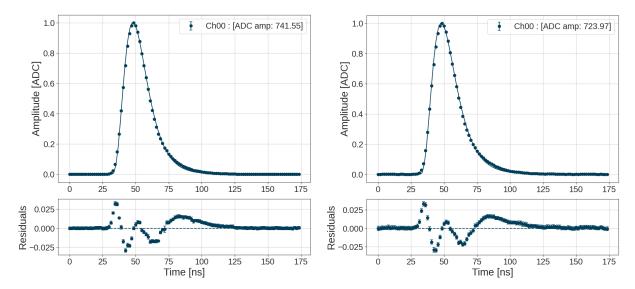

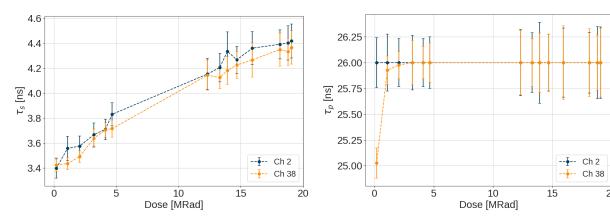

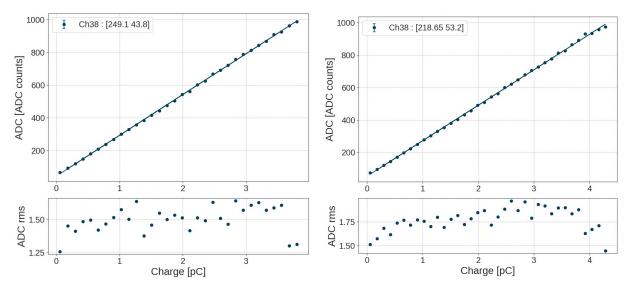

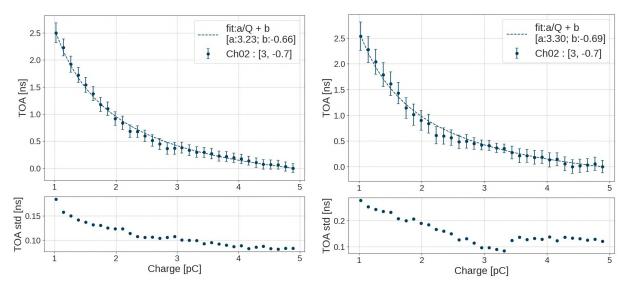

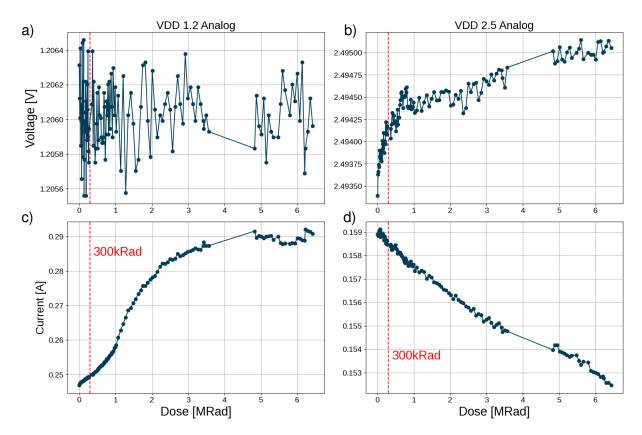

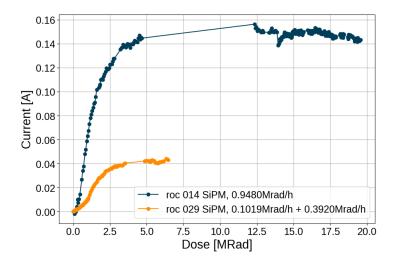

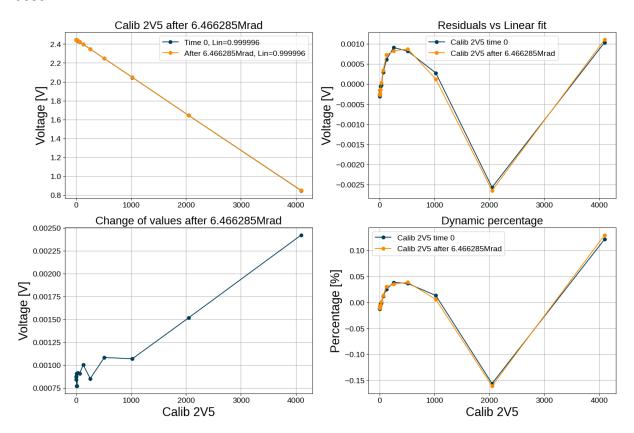

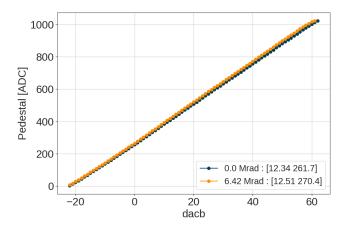

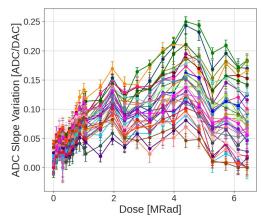

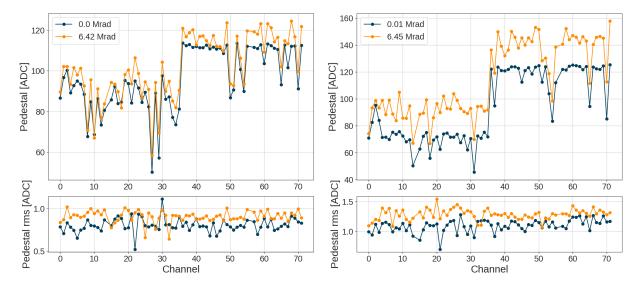

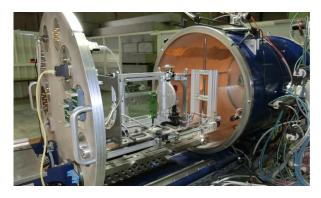

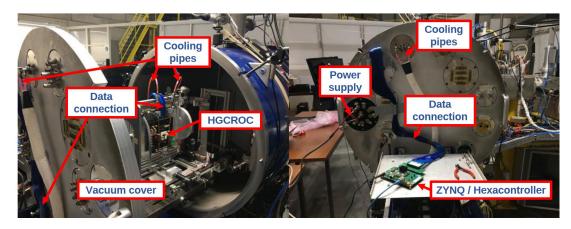

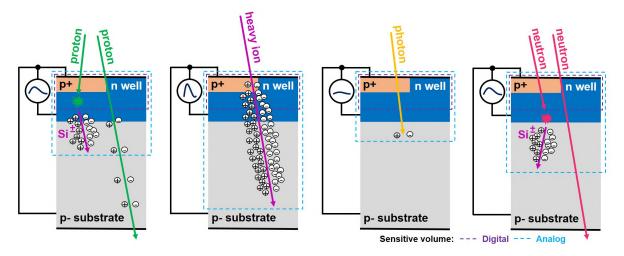

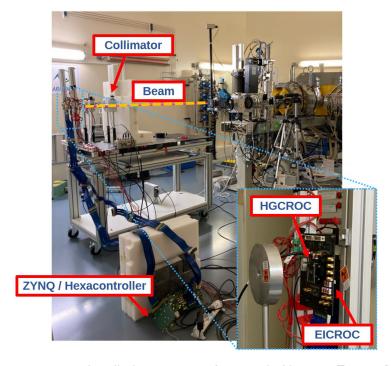

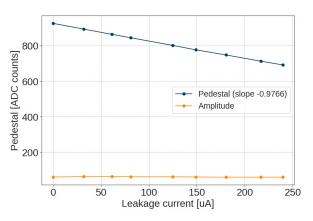

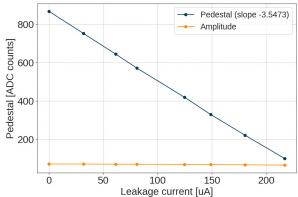

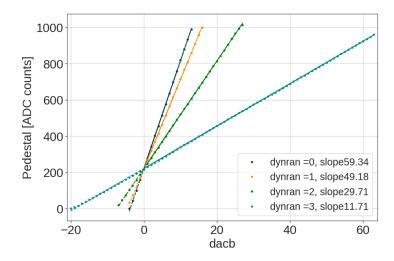

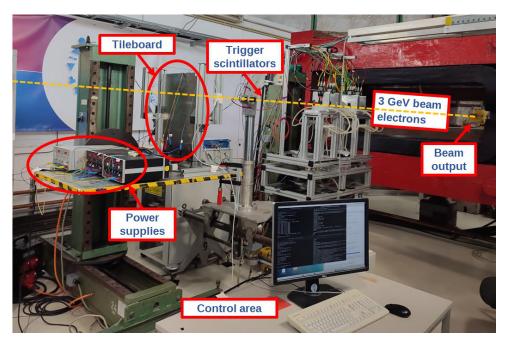

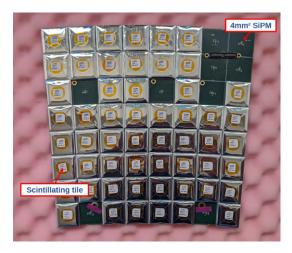

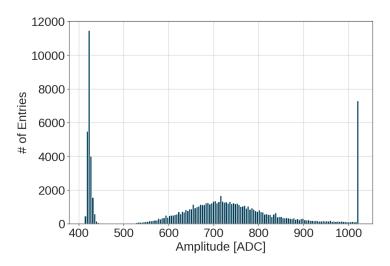

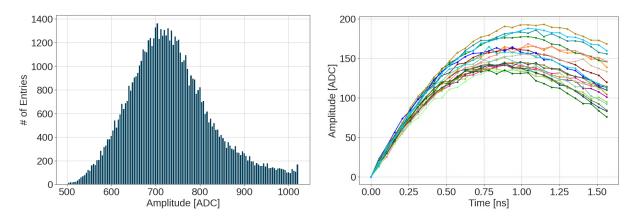

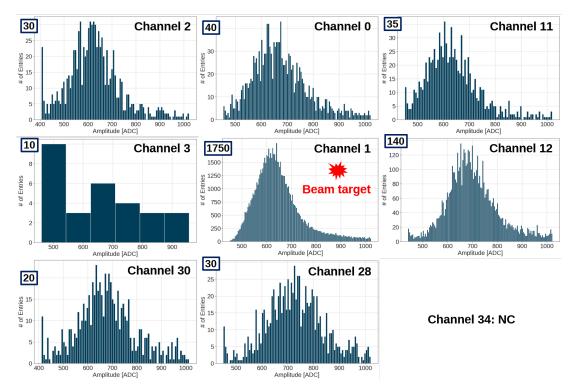

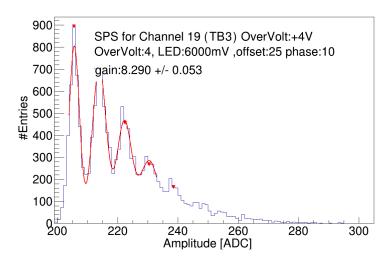

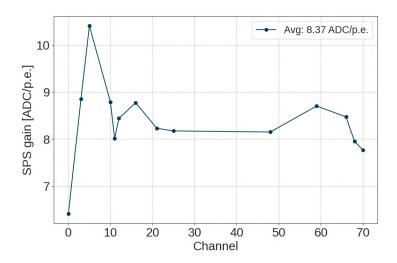

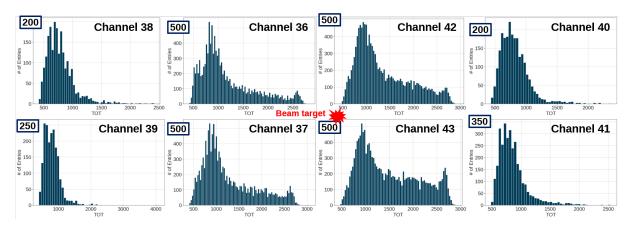

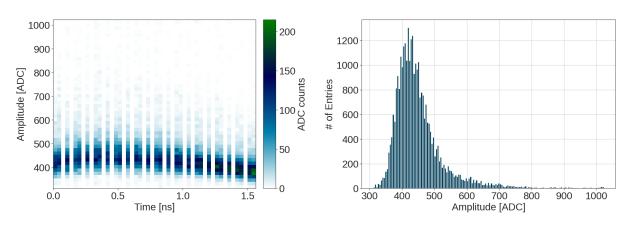

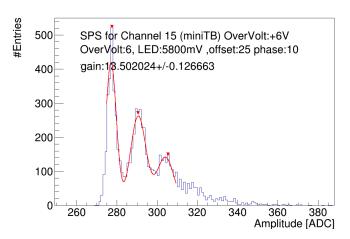

The ASIC design for calorimeters is a challenging task. Today, advanced technologies and components with small sizes and versatile functions can be combined to develop custom electronics with analog and digital designs, all on the same chip. Mixed-signal designs, which read analog signals and digitize information, are known as system-on-chip (SoC) when they integrate all functionalities required for a specific application.