## Circuit partitioning for multi-FPGA platforms

Julien Rodriguez

#### ▶ To cite this version:

Julien Rodriguez. Circuit partitioning for multi-FPGA platforms. Computer Science [cs]. Université de Bordeaux, 2024. English. NNT: 2024BORD0153. tel-04731886

## HAL Id: tel-04731886 https://theses.hal.science/tel-04731886v1

Submitted on 11 Oct 2024

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## THÈSE

PRÉSENTÉE À

## L'UNIVERSITÉ DE BORDEAUX

ÉCOLE DOCTORALE DE MATHÉMATIQUES ET D'INFORMATIQUE

par Julien Rodriguez

POUR OBTENIR LE GRADE DE

### DOCTEUR

SPÉCIALITÉ : INFORMATIQUE

## Partitionnement de circuits pour plate-formes multi-FPGA

Soutenue le 6 septembre 2024

#### Devant la commission d'examen composée de :

| M. Çevdet Aykanat  Mme Lélia Blin  M. François Pellegrini M. Viet Hung Nguyen .  M. Dirk Stroobandt  Invités - Encadrants | Professeur, Université de Bilkent | Rapporteur<br>Présidente<br>Directeur<br>Examinateur<br>Rapporteur |

|---------------------------------------------------------------------------------------------------------------------------|-----------------------------------|--------------------------------------------------------------------|

| M. François Galea                                                                                                         | Ingénieur de Recherche, CEA       | Encadrante                                                         |

| Mme Lilia Zaourar                                                                                                         | Ingénieure de Recherche, CEA      | Encadrante                                                         |

#### Remerciements

Je tiens à remercier l'ensemble des personnes qui ont contribué, de près ou de loin, à l'élaboration de ma thèse de doctorat.

Je remercie Çevdet Aykanat et Dirk Stroobandt d'avoir accepté de rapporter mon manuscrit. Je remercie également Lélia Blin et Viet Hung Nguyen d'avoir accepté d'en être examinateurs.

Je souhaite profondément remercier mon directeur de thèse, François Pellegrini, qui m'a accompagné avec pédagogie pendant toute la durée de mon doctorat, tant sur des problématiques scientifiques que personnelles. Je remercie aussi l'équipe encadrante CEA, tout particulièrement François Galea qui, au-delà de ses conseils scientifiques, m'a enrichi dans d'autres domaines.

Mon doctorat avait la particularité d'être partagé entre deux sites : le CEA-List à Saclay et l'Inria à Bordeaux. Je remercie mes camarades de l'Inria pour les séminaires, les parties de baby-foot et de bowling, qui étaient d'agréables moments : rares, courts, mais intenses. Je remercie également, Caaliph, Fatma, Kods, et Mihail pour les riches discussions que nous avons eues.

Je tiens à remercier l'Association du CEA des thésards d'Île-de-France (ACTIF) pour les nombreux moments de distraction auxquels j'ai pu participer et pour la confiance que ses membres m'ont accordée en m'élisant vice-président. Pendant mon mandat, j'ai eu l'honneur d'organiser le voyage scientifique annuel, grâce à l'aide précieuse de mon camarade Adrien Roberty.

Je souhaite également remercier mes camarades Jonathan Fontaine et Valentin Gilbert, voisins de bureau, habitués des pauses cafés et du desk-basket. Jonathan, je me souviendrai toujours de ma première expérience en conférence internationale que nous avons partagée, riche en présentations et en casquettes. Je pense également à Simon Tollec et Pierre-Emmanuel Clet qui ont animé notre open space.

Comment ne pas mentionner et remercier également mes collègues de l'open space voisin : Samira Aït Bensaid, pour les discussions intéressantes sur les stratégies de recrutement ; Marc Renard, pour les apports en fruits, et Guillaume Roumage pour les entraı̂nements athlétiques. Un remerciement spécial à Clément Fauchereau, amateur comme moi de poésies et de raisins.

Merci à Daniel Vert, Gabriella Bettonte, Lucas Phab et Valentin Gilbert pour les riches discussions en informatique quantique.

Je tiens à remercier la famille de ma compagne, qui m'a proposé à plusieurs reprises un espace très confortable pendant mes phases de rédaction en région Parisienne. Cathy, merci d'avoir été présente quand il fallait perdre au billard pour me remonter le moral, merci pour tout.

Je remercie fortement ma famille qui m'a accompagné avant, pendant et qui m'accompagnera sans doute après ce chapitre de ma vie, en particulier mes parents à qui je dédie l'ensemble de mon travail.

Un FPGA ('Field Programmable Gate Array') est un circuit intégré comprenant un grand nombre de ressources logiques programmables et interconnectables, qui permettent de mettre en œuvre, par programmation, un circuit électronique numérique tel qu'un microprocesseur, un accélérateur de calcul ou un système hybride complexe sur puce. Les FPGA sont largement utilisés dans le domaine de la conception de circuits intégrés, car ils permettent d'obtenir très rapidement des circuits prototypes, sans avoir à fabriquer la puce sur silicium. Cependant, certains circuits sont trop grands pour être mis en œuvre sur un seul FPGA. Pour résoudre ce problème, il est possible d'utiliser une plate-forme composée de plusieurs FPGA fortement interconnectés, qui peut être considérée comme un seul FPGA virtuel donnant accès à toutes les ressources de la plate-forme. Cette solution, bien qu'élégante, pose plusieurs problèmes. En particulier, les outils existants ne tiennent pas compte de toutes les contraintes du problème de placement à résoudre pour cartographier efficacement un circuit sur une plate-forme multi-FPGA. Par exemple, les fonctions de coût actuelles ne sont pas conçues pour minimiser les temps de propagation du signal entre les registres du FPGA, ni pour prendre en compte les contraintes de capacité induites par le routage des connexions. L'objectif de ce travail de doctorat est de concevoir des modèles de partitionnement et de placement d'hypergraphes adaptés au problème de placement des circuits sur une plate-forme multi-FPGA. Ces modèles seront spécifiquement conçus pour répondre aux objectifs et aux critères de performance définis par les concepteurs de circuits.

Mots-clés partitionnement, hypergraphe

Laboratoire d'accueil Centre d'intégration Nano-INNOV - CEA-LIST - Université Paris-Saclay, 2 Bd Thomas Gobert, 91120 Palaiseau

ii J. Rodriguez

#### Title Circuit partitioning for multi-FPGA platforms

An FPGA ('Field Programmable Gate Array') is an integrated circuit comprising a large number of programmable and interconnectable logic resources, which allow one to implement, by programming, a digital electronic circuit such as a microprocessor, a compute accelerator or a complex hybrid system-on-chip. FPGAs are widely used in the field of integrated circuits design, because they allow one to obtain prototype circuits very quickly, without having to manufacture the chip on silicon. However, some circuits are too big to be implemented on a single FPGA. To address this issue, it is possible to use a platform consisting of several highly interconnected FPGAs, which can be seen as a single virtual FPGA giving access to all the resources of the platform. This solution, although elegant, poses several problems. In particular, the existing tools do not account for all the constraints of the placement problem to be solved in order to efficiently map a circuit onto a multi-FPGA platform. For example, current cost functions are not designed to minimize signal propagation times between FPGA registers, nor do they take into account the capacity constraints induced by the routing of connections. The aim of this PhD work is to design hypergraph partitioning and placement models adapted to the problem of circuit layout on a multi-FPGA platform. These models will be specifically designed to meet the objectives and performance criteria defined by circuit designers.

**Keywords** partitioning, hypergraph

**Hosting Laboratory** Centre d'intégration Nano-INNOV - CEA-LIST - Université Paris-Saclay, 2 Bd Thomas Gobert, 91120 Palaiseau

iv J. Rodriguez

## Contents

|                  | Ren                   | nerciem  | ents                                            | i   |

|------------------|-----------------------|----------|-------------------------------------------------|-----|

| $\mathbf{R}_{0}$ | ésum                  | ıé éten  | du en français                                  | 1   |

|                  |                       |          |                                                 | 3   |

|                  |                       |          |                                                 | 4   |

|                  |                       |          |                                                 | 6   |

| In               | $\operatorname{trod}$ | uction   |                                                 | 7   |

|                  | Digi                  | tal elec | tronic circuits                                 | 8   |

|                  | Fiel                  | d-Progr  | cammable Gate Arrays                            | 8   |

|                  |                       |          |                                                 | 9   |

|                  |                       |          |                                                 | 0   |

|                  | Out                   | line .   |                                                 | . 1 |

| 1                | Def                   | inition  | ns 1                                            | .3  |

| _                | 1.1                   |          |                                                 | 4   |

|                  |                       | 1.1.1    | V1 0 1                                          | 4   |

|                  |                       | 1.1.2    | 1                                               | 6   |

|                  |                       | 1.1.3    | <i>y</i> 1                                      | 20  |

|                  | 1.2                   | _        | V1 0 1                                          | 24  |

|                  | 1.2                   | 1.2.1    | ÿ                                               | 24  |

|                  |                       | 1.2.2    |                                                 | 25  |

|                  | 1.3                   |          | ı v                                             | 26  |

|                  | 1.0                   | 1.3.1    |                                                 | 26  |

|                  |                       | 1.3.2    |                                                 | 27  |

|                  |                       | 1.3.3    |                                                 | 29  |

|                  | 1.4                   |          | 1 71 6 1                                        | 32  |

|                  |                       |          |                                                 |     |

| 2                | Sta                   |          | he art in circuit and hypergraph partitioning 3 |     |

|                  | 2.1                   |          | ioning methods and applications                 |     |

|                  |                       | 2.1.1    | Hypergraph bipartitioning                       |     |

|                  |                       | 2.1.2    | Graph-based hypergraph partitioning             | 7   |

|   |     | 2.1.3 Static mapping                                                 |

|---|-----|----------------------------------------------------------------------|

|   | 2.2 | Computational complexity                                             |

|   | 2.2 | 2.2.1 Complexity of partitioning                                     |

|   |     | 2.2.2 Complexity of clustering                                       |

|   | 2.3 | Partitioning and mapping tools                                       |

|   | 2.0 | 2.3.1 METIS, HMETIS and KHMETIS                                      |

|   |     | 2.3.2 PATOH and KPATOH                                               |

|   |     | 2.3.3 KASPAR, KAHIP and KAHYPAR                                      |

|   |     | 2.3.4 TOPOPART and TRITONPART                                        |

|   |     | 2.3.5 SCOTCH and PT-SCOTCH                                           |

|   |     | 2.3.6 Conclusion                                                     |

|   | 2.4 | Algorithmic approaches to hypergraph partitioning and placement . 41 |

|   |     | 2.4.1 Deterministic approaches                                       |

|   |     | 2.4.2 Probabilistic approaches                                       |

|   | 2.5 | Conclusion                                                           |

|   |     |                                                                      |

| 3 | Exp | perimental setup and methodology 55                                  |

|   | 3.1 | Critical path in red-black hypergraphs                               |

|   |     | 3.1.1 Hypergraphs                                                    |

|   |     | 3.1.2 Red-black hypergraphs                                          |

|   | 3.2 | Benchmarks                                                           |

|   |     | 3.2.1 ITC99                                                          |

|   |     | 3.2.2 Titan                                                          |

|   |     | 3.2.3 Chipyard and neural networks circuits                          |

|   | 0.0 | 3.2.4 File formats for the red-black hypergraph                      |

|   | 3.3 | Target topologies                                                    |

|   |     | 3.3.1 4-FPGA topologies                                              |

|   | 0.4 | 3.3.2 8-FPGA topologies                                              |

|   | 3.4 | Conclusion                                                           |

| 4 | Alg | orithms for coarsening 73                                            |

|   | 4.1 | Clustering                                                           |

|   |     | 4.1.1 Hypergraph Clustering                                          |

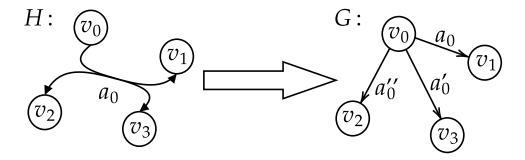

|   |     | 4.1.2 Circuit clustering when replication is allowed                 |

|   |     | 4.1.3 Circuit clustering when replication is not allowed 76          |

|   |     | 4.1.4 Conclusion                                                     |

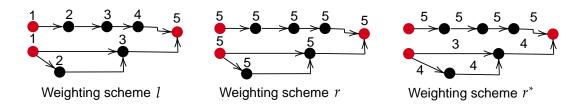

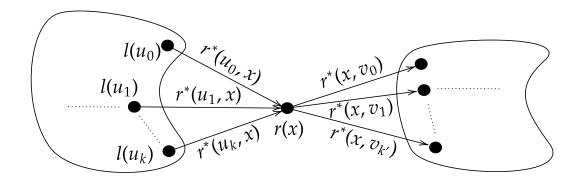

|   | 4.2 | Model and weighting schemes                                          |

|   |     | 4.2.1 Clustering problem model                                       |

|   |     | 4.2.2 Weighting schemes                                              |

|   |     | 4.2.3 Conclusion                                                     |

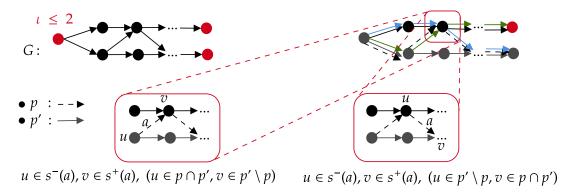

|   | 4.3 | Polynomial algorithms for a specific class of DAHs                   |

|   |     |                                                                      |

vi J. Rodriguez

|   |      | 4.3.1             | Path intersection                                          | 82  |

|---|------|-------------------|------------------------------------------------------------|-----|

|   |      | 4.3.2             | A polynomial algorithm for red-black hypergraph clustering | 84  |

|   |      | 4.3.3             | NP-Completeness                                            | 89  |

|   |      | 4.3.4             | Conclusion                                                 | 92  |

|   | 4.4  | A par             | ameterized M-approximation algorithm for red-black hyper-  |     |

|   |      | graph             | clustering                                                 | 93  |

|   |      | 4.4.1             | Binary Search Clustering (BSC)                             | 93  |

|   |      | 4.4.2             | Heavy-edge matching                                        | 97  |

|   |      | 4.4.3             | Conclusion                                                 | 99  |

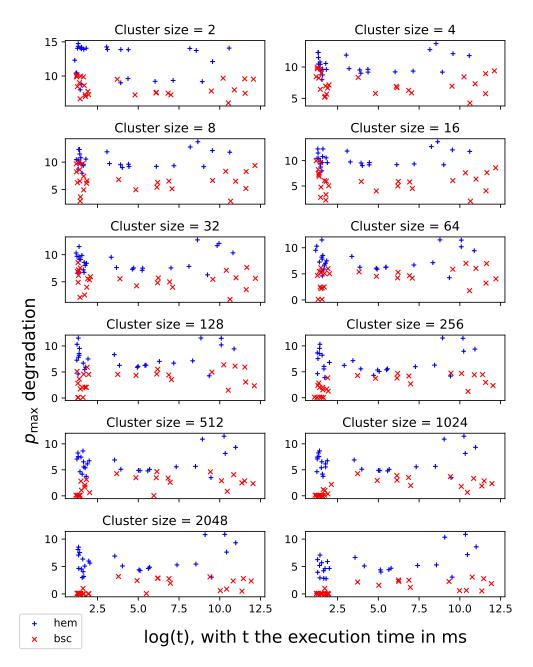

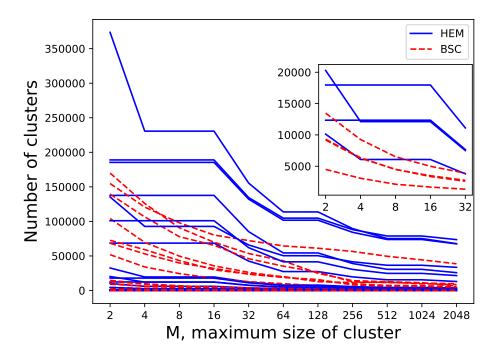

|   | 4.5  | Exper             | imental Results                                            | 100 |

|   | 4.6  | Concl             | usion                                                      | 103 |

| 5 | Init | ial par           | rtitioning                                                 | 105 |

|   | 5.1  | Graph             | and hypergraph partitioning                                | 106 |

|   | 5.2  | Traver            | rsal algorithms                                            | 107 |

|   |      | 5.2.1             | Initial partitioning based on breadth-first search         |     |

|   |      |                   | driven by vertex criticality                               | 108 |

|   |      | 5.2.2             | Initial partitioning based on Depth-First Search           |     |

|   |      |                   | driven by vertex criticality                               |     |

|   |      | 5.2.3             | Critical Connected Components/Cone Partitioning            |     |

|   |      | 5.2.4             | Conclusion                                                 |     |

|   | 5.3  | _                 | er programming                                             |     |

|   |      | 5.3.1             | Model                                                      |     |

|   |      | 5.3.2             | Symmetries                                                 |     |

|   |      | 5.3.3             | Path degradation                                           |     |

|   | _ ,  | 5.3.4             | Conclusion                                                 |     |

|   | 5.4  |                   | ing the initial partition                                  |     |

|   | 5.5  | -                 | imental results                                            |     |

|   |      | 5.5.1             | Integer programming results                                |     |

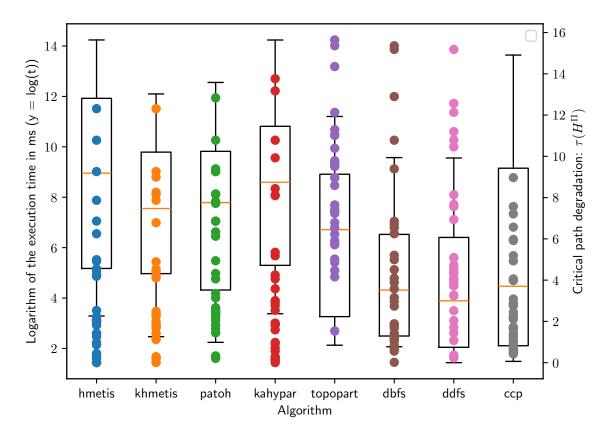

|   |      | 5.5.2             | Results for DBFS, DDFS and CCP with min-cut tools          |     |

|   | F 6  | 5.5.3             | Results for connectivity cut cost                          |     |

|   | 5.6  | Conci             | usion                                                      | 145 |

| 6 | Ref  |                   | 0                                                          | 145 |

|   | 6.1  |                   | ement algorithms                                           |     |

|   |      | 6.1.1             | The Kerninghan - Lin Algorithm                             |     |

|   |      | 6.1.2             | The Fiduccia-Mattheyses Algorithm (FM)                     |     |

|   |      | 6.1.3             | K-way Fiduccia-Mattheyses (KFM)                            |     |

|   |      | $\frac{6.1.4}{-}$ | Delay K-partitioning Fiduccia-Mattheyses (DKFM)            |     |

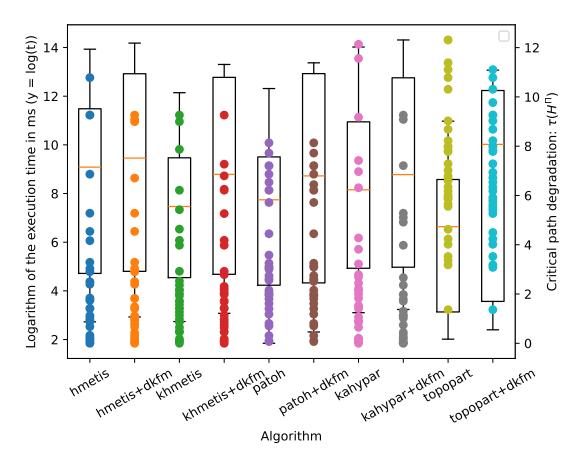

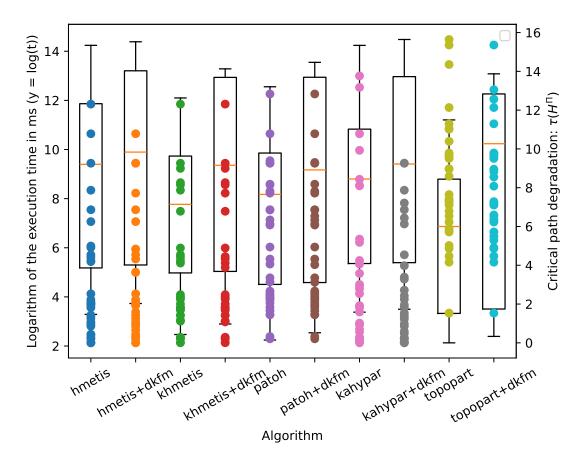

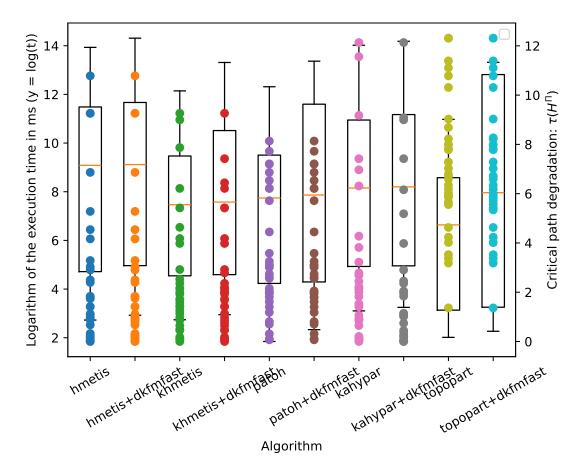

|   | 6.2  | _                 | imental results                                            |     |

|   |      | 6.2.1             | Methodology                                                | 160 |

|   |      |                   |                                                            |     |

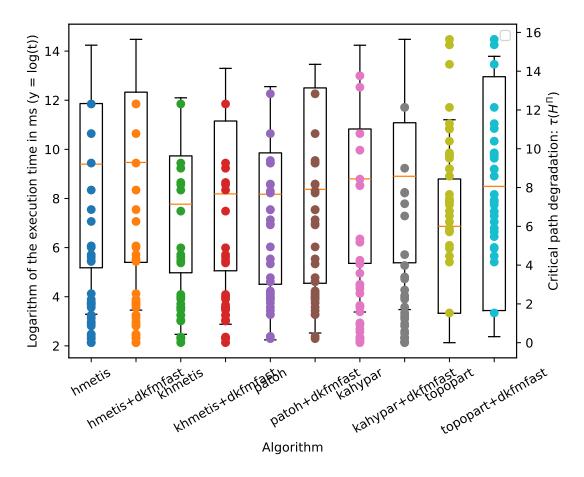

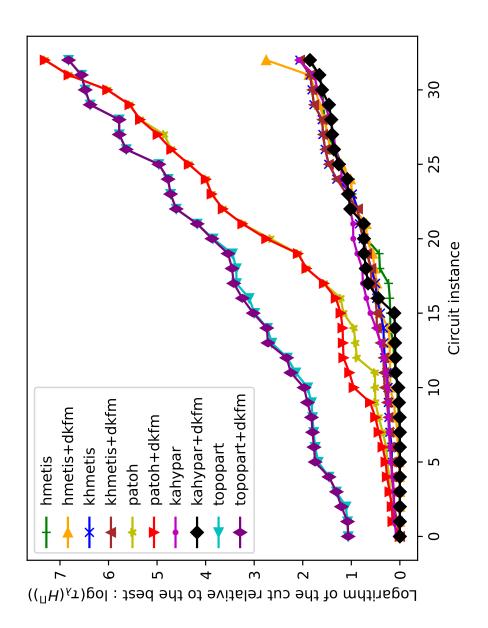

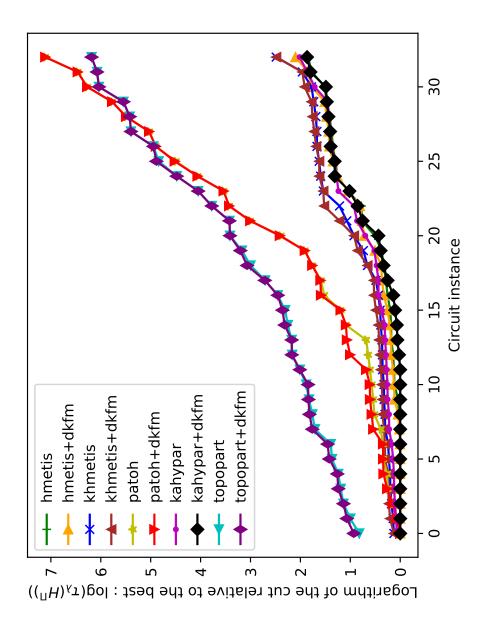

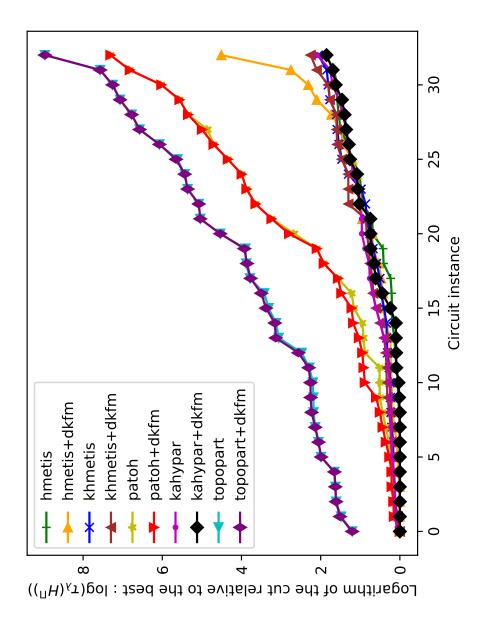

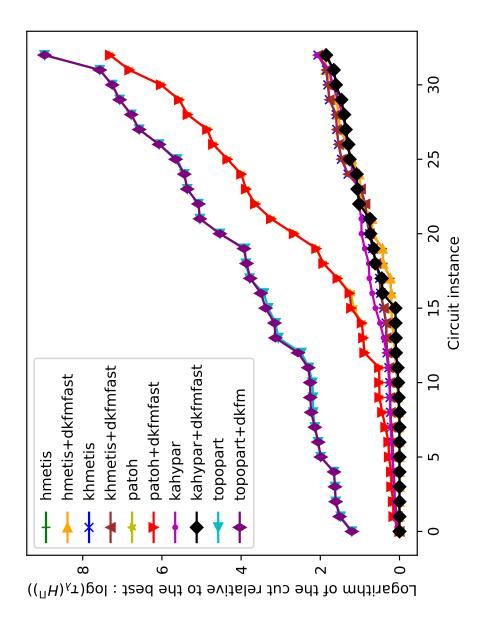

|              |        | .2.2 Results of DKFM on critical path degradation           | 161   |

|--------------|--------|-------------------------------------------------------------|-------|

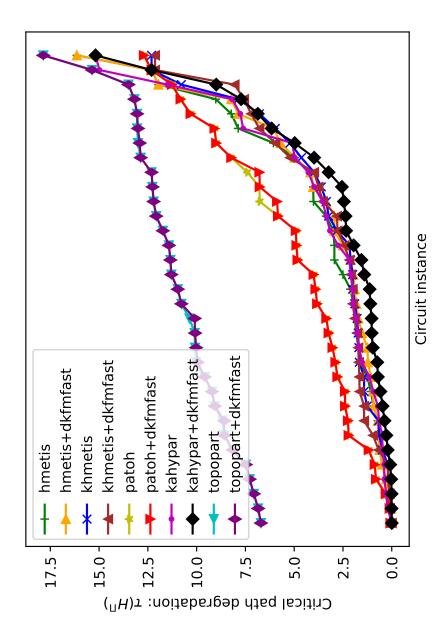

|              |        | .2.3 Results of DKFMFAST on critical path degradation       | 167   |

|              |        | .2.4 Results of connectivity cost degradation with DKFM     | 174   |

|              | 6.3    | Conclusion                                                  | 178   |

| Co           | onclu  | on and Perspectives                                         | 179   |

|              | Sum    | ary of the dissertation                                     | 180   |

|              | The    | AISIN software                                              | 182   |

| $\mathbf{A}$ | Exp    | rimental results                                            | 185   |

|              | A.1    | Tumerical results of clustering algorithms                  | 186   |

|              | A.2    | Tumerical results of initial partitioning algorithms        | 199   |

|              |        | 1.2.1 Critical path evaluation                              | 199   |

|              |        | 1.2.2 Connectivity cost results                             | 212   |

|              |        | A.2.3 Balance cost of partition                             | 217   |

|              | A.3    | Jumerical results of refinement algorithms: DKFM and DKFMFA | ST222 |

|              |        | 1.3.1 Numerical results of DKFM                             | 222   |

|              |        | A.3.2 Numerical results of DKFMFAST                         | 269   |

| Re           | efere  | es                                                          | 317   |

| Ρι           | ıblica | ions                                                        | 339   |

|              | Con    | ences                                                       | 339   |

|              |        |                                                             |       |

viii J. Rodriguez

# List of Figures

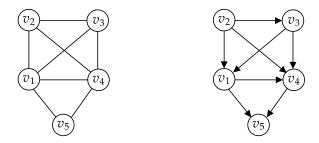

| 1.1        | Examples of a graph and a directed graph.                    | 15 |

|------------|--------------------------------------------------------------|----|

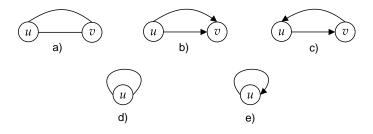

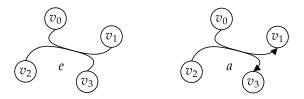

| 1.2        | Examples of loops and multiple arcs and edges                | 15 |

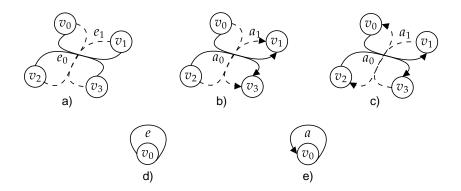

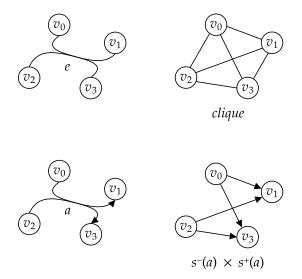

| 1.3        | An example of hyperedge (e) and hyperarc (a)                 | 17 |

| 1.4        | Examples of hyperloops and multiple hyperarcs and hyperedges | 18 |

| 1.5        | Example of graph representation for hypergraph neighbors     | 19 |

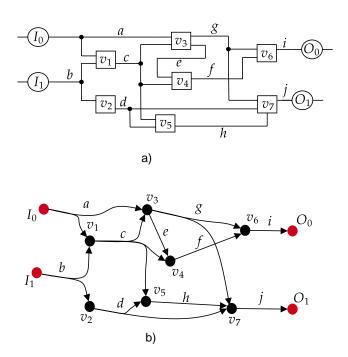

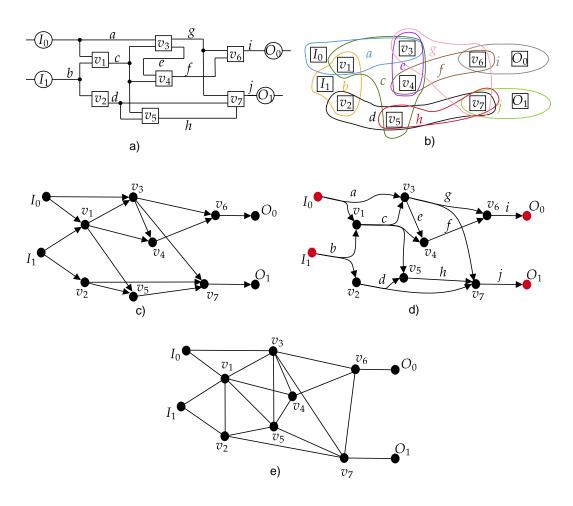

| 1.6        | Circuit and its Red-Black Hypergraph model                   | 22 |

| 1.7        | Circuit composed of two combinatorial blocks                 | 23 |

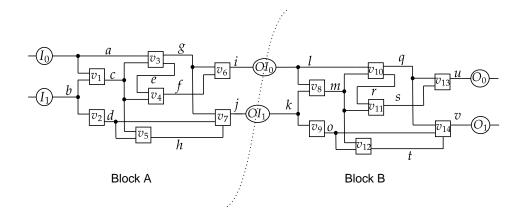

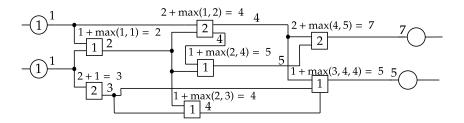

| 1.8        | Circuit cell propagation delay                               | 25 |

| 1.9        | Circuit cell retro-propagation of critical paths             | 25 |

| 1.10       | Connectivity and Cut size                                    | 27 |

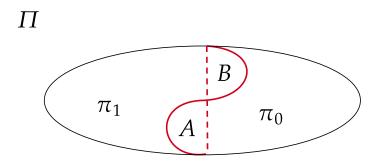

| 1.11       | Example of a cut path                                        | 28 |

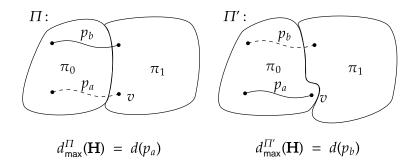

|            | Example of path mapping                                      | 28 |

| 1.13       | Circuit models                                               | 30 |

| 1.14       | Limitation of classical graph model for partitioning         | 31 |

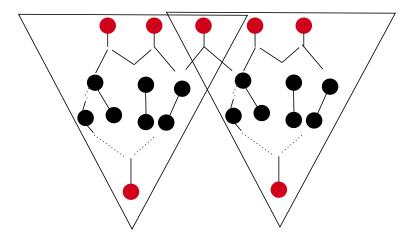

| 2.1        | An example of a red-black hypergraph with two cones          | 41 |

| 2.2        | The multilevel scheme.                                       | 44 |

|            |                                                              |    |

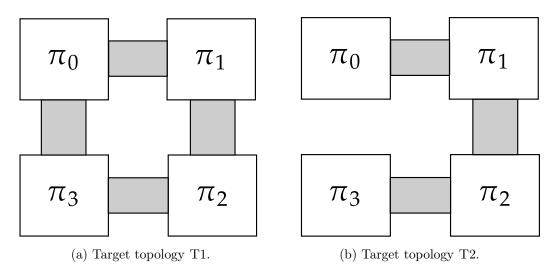

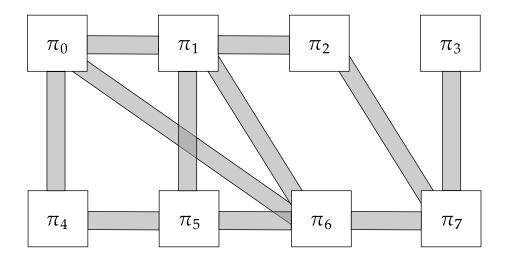

| 3.1        | Target topologies T1 and T2                                  | 71 |

| 3.2        | T4: the ICCAD 2019 contest target topology for problem B     | 72 |

| 4.1        | Example of partitioning with replication                     | 77 |

| 4.2        |                                                              | 80 |

| 4.3        |                                                              | 81 |

| 4.4        | Example of vertex-vertex relations in a hyperarc             | 81 |

| 4.5        |                                                              | 83 |

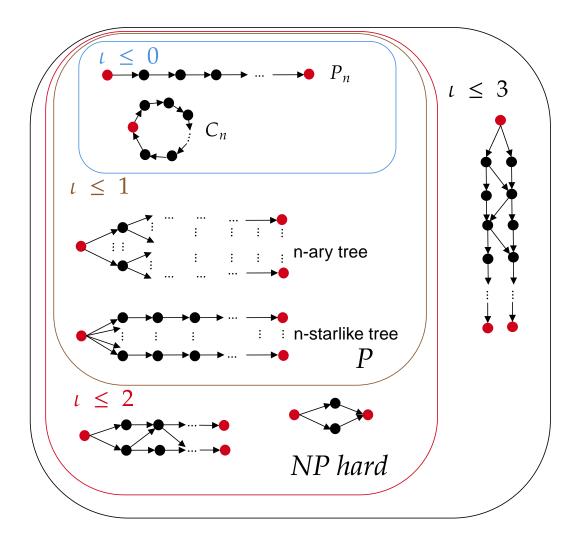

| 4.6        | Some graph structures as a function of the $\iota$ metric    | 85 |

| 4.7        | <u> </u>                                                     | 89 |

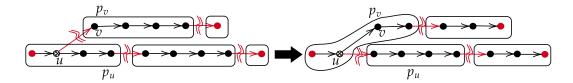

|            | Example of cluster reduction for two neighboring paths       | 09 |

| 4.8        |                                                              | 91 |

| 4.8<br>4.9 | Example of cluster reduction for two heighboring paths       |    |

| -              | son between the number of clusters produced by BSC and    | )2          |

|----------------|-----------------------------------------------------------|-------------|

|                |                                                           |             |

|                | etex in 2 DAHs                                            |             |

|                | DDFS and DBFS                                             |             |

|                | of two cone components                                    |             |

|                | del                                                       | <u> 1</u> 2 |

| _              | of a symmetric solution for min-cut that is not symmetric | ٦٢          |

| -              | ath                                                       |             |

|                | radation during coarsening phase                          |             |

|                | the partition to a target topology                        |             |

|                | or T1                                                     |             |

|                | or topology $T2$                                          |             |

|                | or T4                                                     |             |

|                | or T5                                                     |             |

|                | n T6.                                                     |             |

|                | vity-minus-one cost results on target topology T314       |             |

|                | vity-minus-one cost results on target topology T614       |             |

| 5.15 Connecti  | vicy-initias-one cost results on target topology 10       | E4          |

| 6.1 Example    | of initial bipartition and refinement                     | 17          |

| 6.2 Critical p | eath effects during refinement pass                       | 52          |

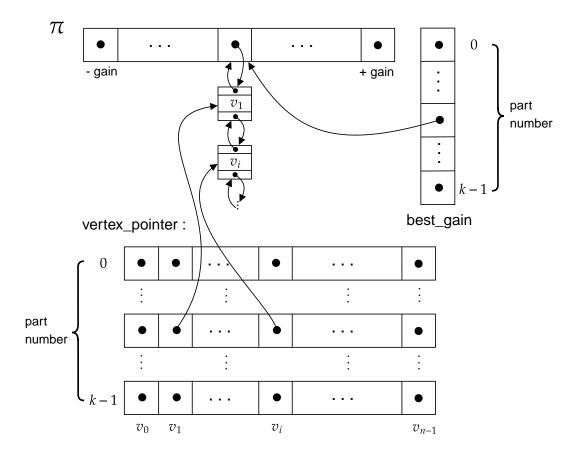

| 6.3 FM Data    | structures extended for the DKFM algorithm                | 56          |

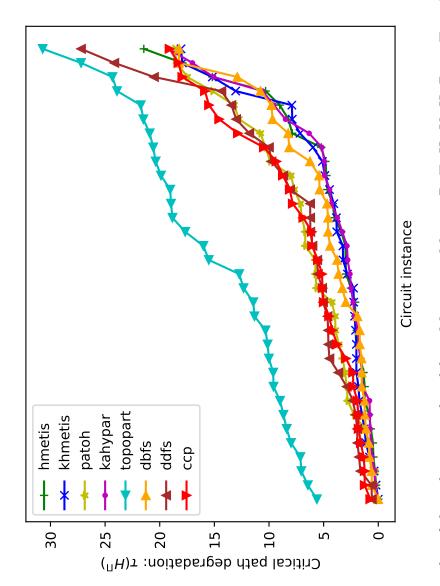

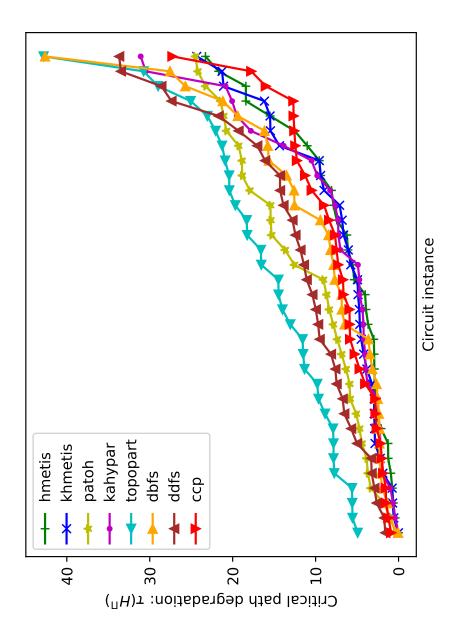

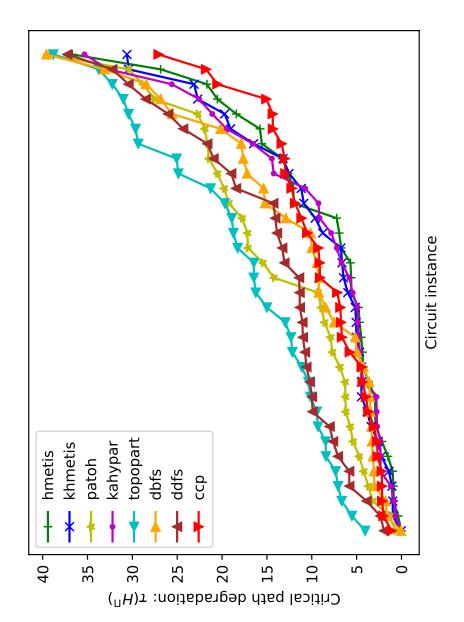

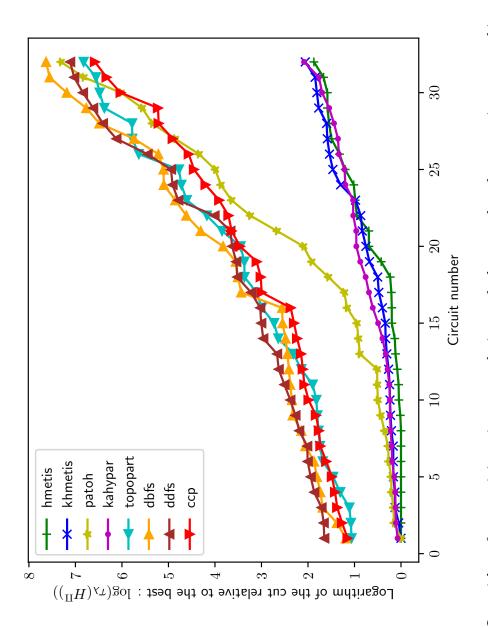

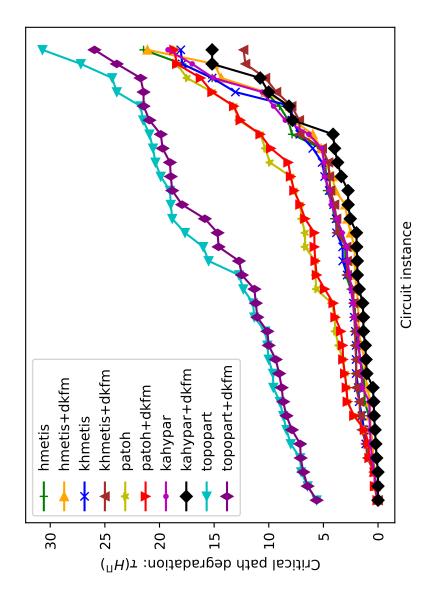

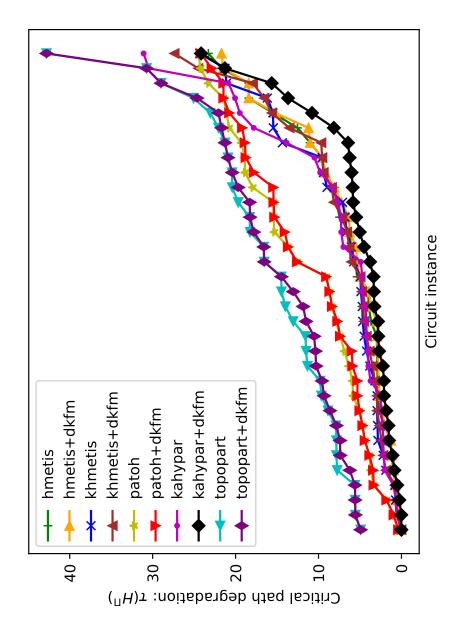

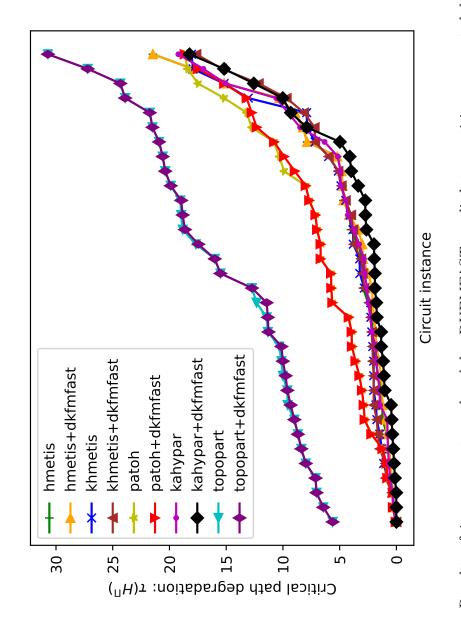

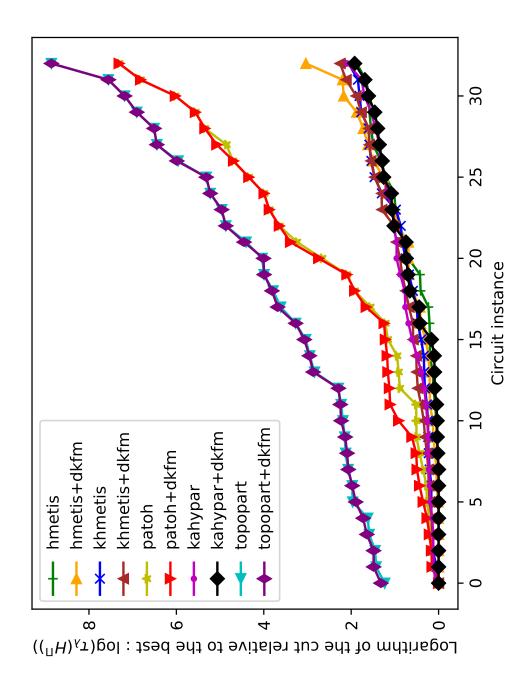

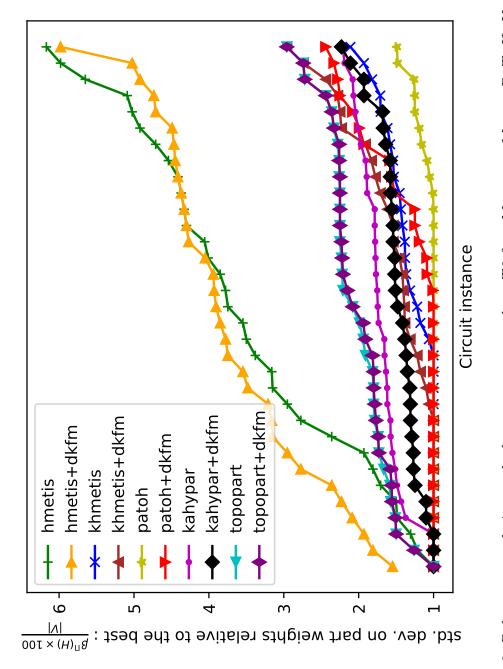

| 6.4 Results o  | f DKFM on T1                                              | 32          |

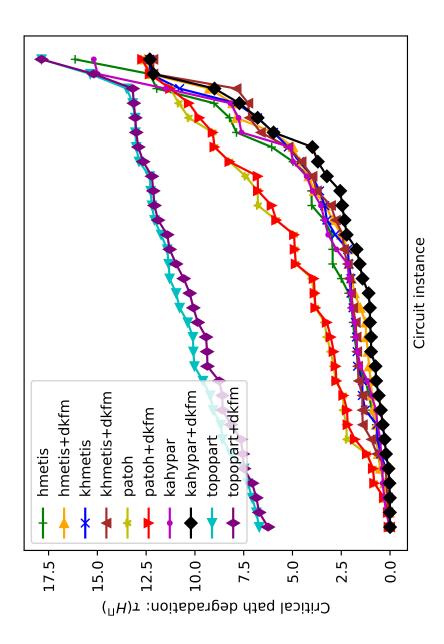

| 6.5 Results of | f DKFM on T2                                              | 3           |

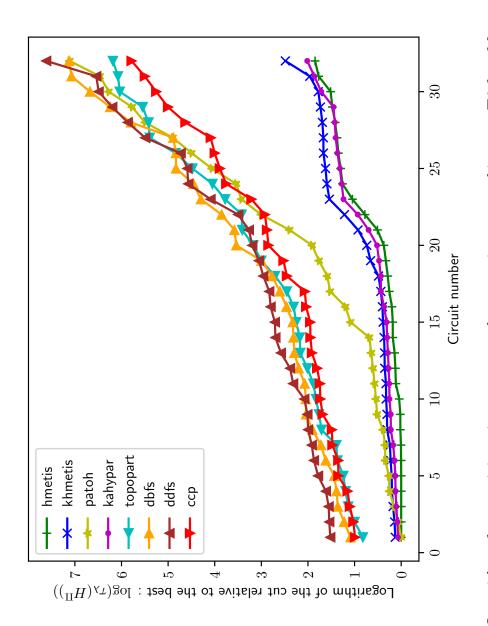

|                | n T3 for DKFM                                             |             |

|                | f DKFM on T4                                              |             |

|                | f DKFM on T5                                              |             |

|                | n T6 for DKFM                                             |             |

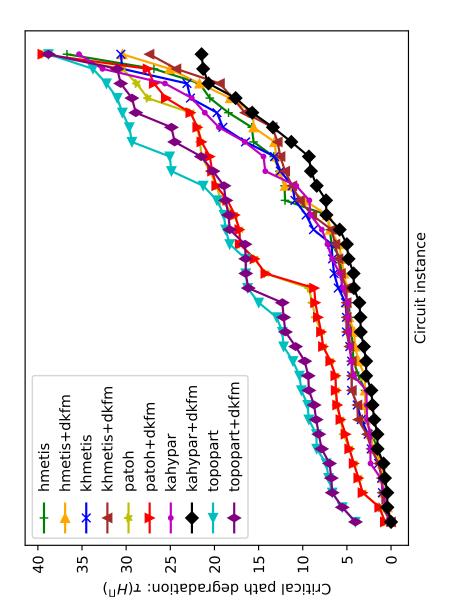

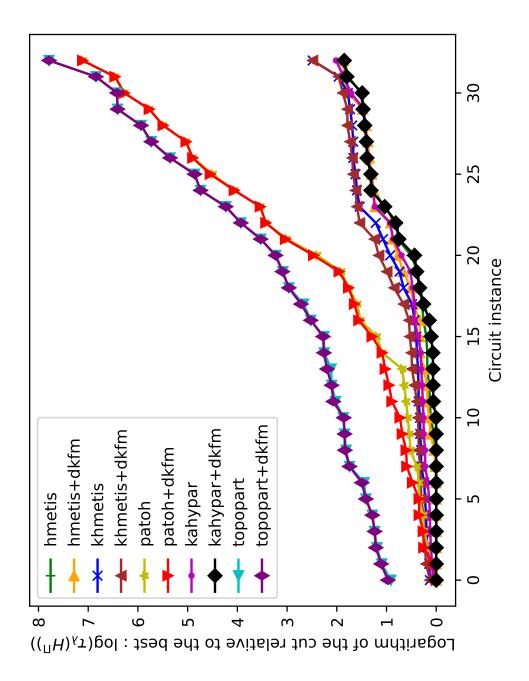

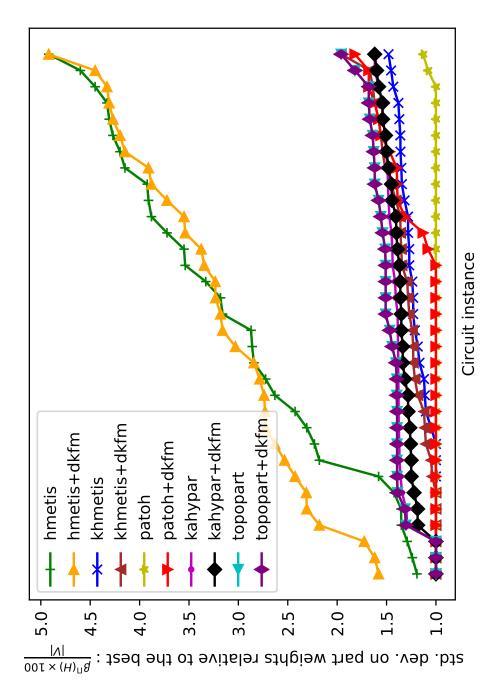

|                | f DKFMFAST on T1                                          |             |

|                | f DKFMFAST on T2                                          |             |

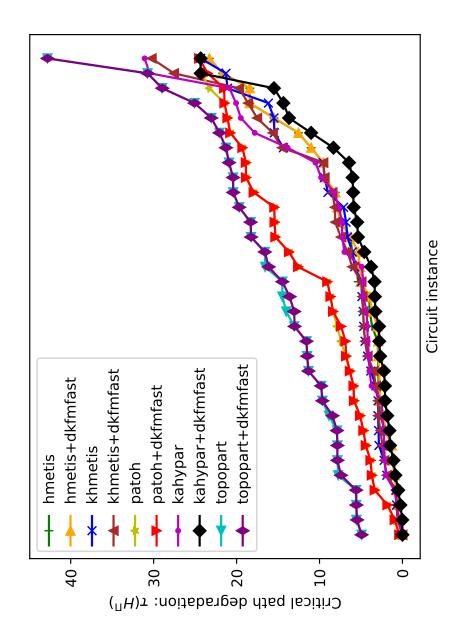

|                | n T3 for DKFMFAST                                         |             |

|                | f DKFMFAST on T4                                          |             |

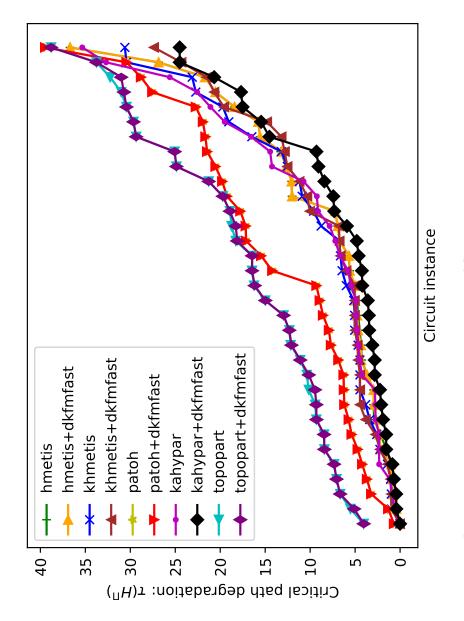

|                | f DKFMFAST on T5                                          |             |

|                | n T6 for DKFMFAST                                         |             |

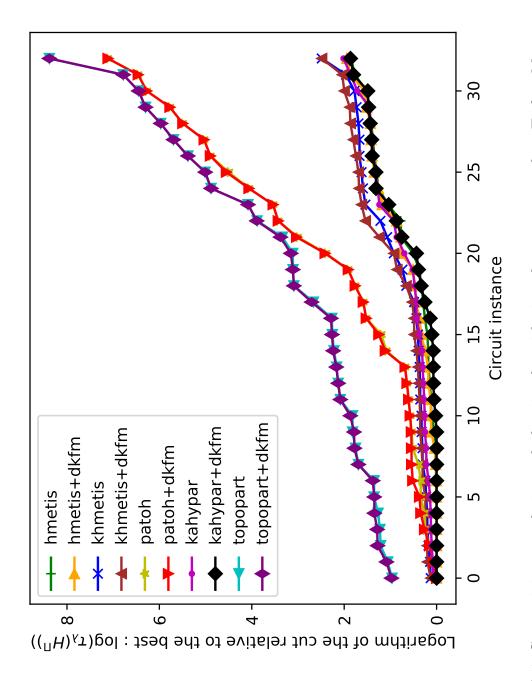

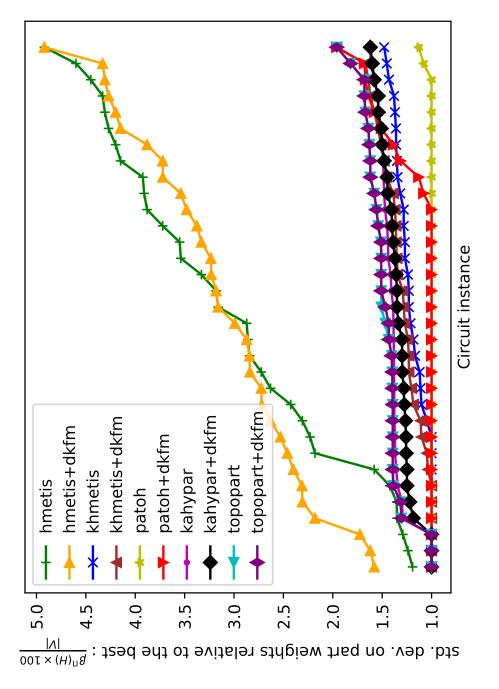

|                | vity cost on target topology T3 with DKFM                 |             |

| 6.17 Connectiv | vity cost on target topology T6 with DKFM                 | 77          |

| A.1 Connectiv  | vity cost on target topology T1                           | 36          |

|                | vity cost on target topology T1                           |             |

|                |                                                           |             |

| A.3 Connectiv  | vity cost on target topology T4                           | 0           |

### List of Figures

| A.4 Connectivity cost on target topology T5                  |

|--------------------------------------------------------------|

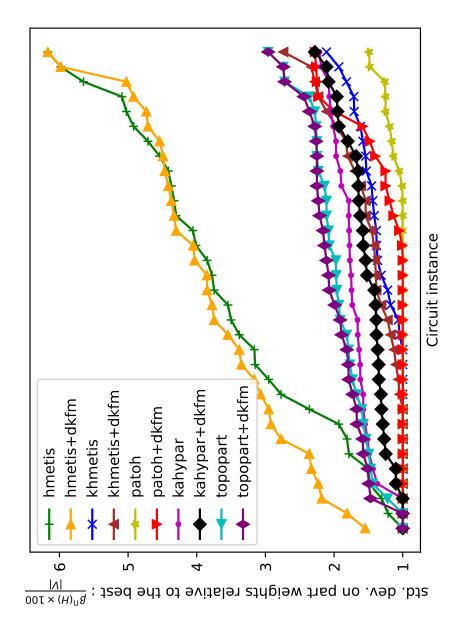

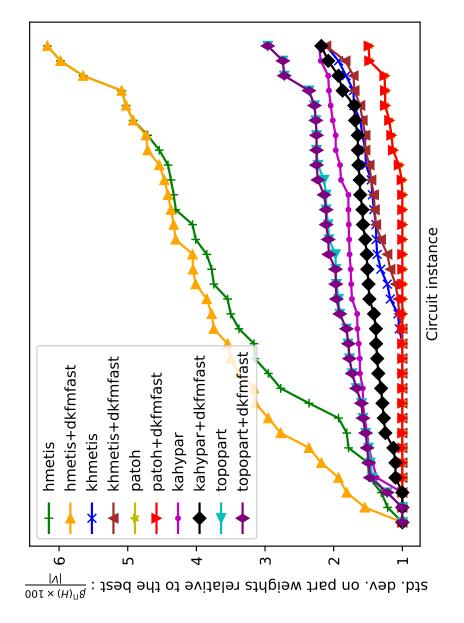

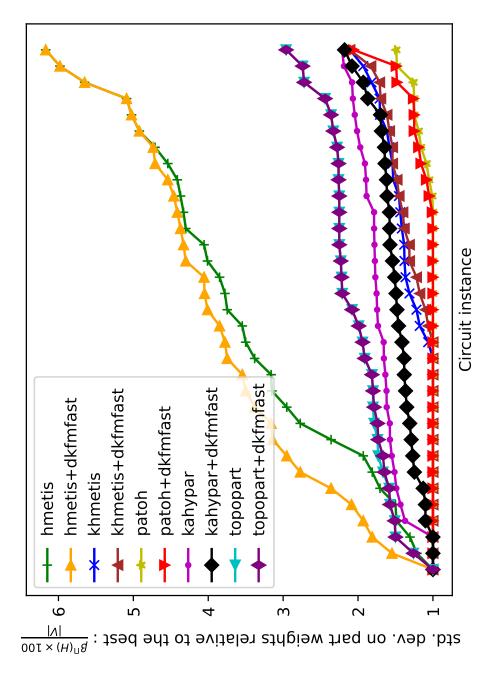

| A.5 Balance cost on target topology T1 with DKFM             |

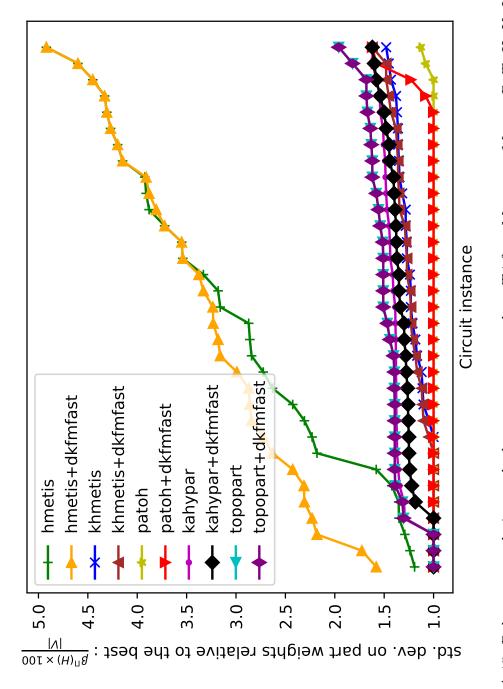

| A.6 Balance cost on target topology T2 with DKFM             |

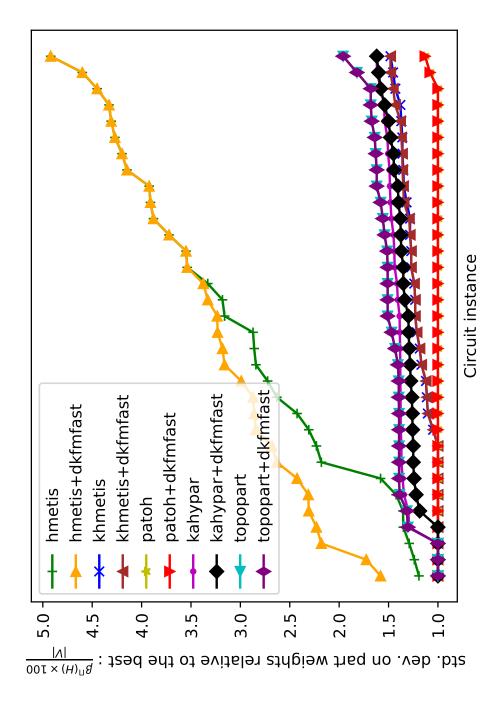

| A.7 Balance cost on target topology T4 with DKFM             |

| A.8 Balance cost on target topology T5 with DKFM             |

| A.9 Connectivity cost of DKFMFAST on target topology T1 283  |

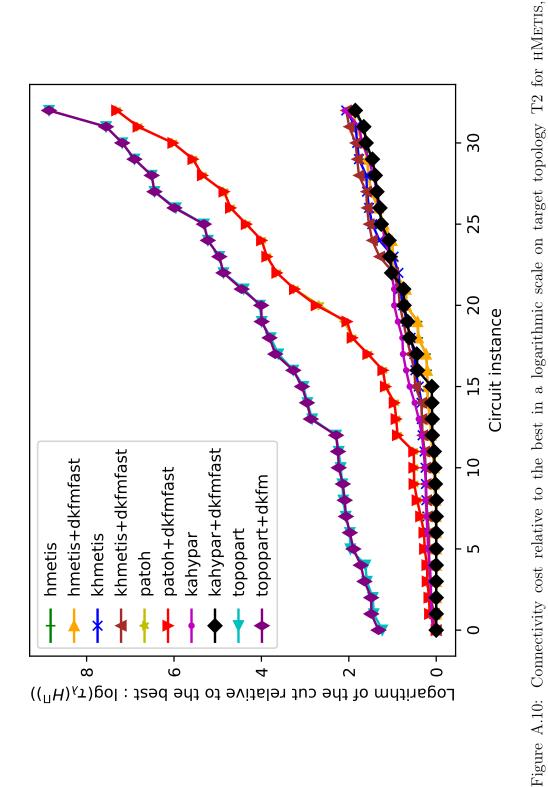

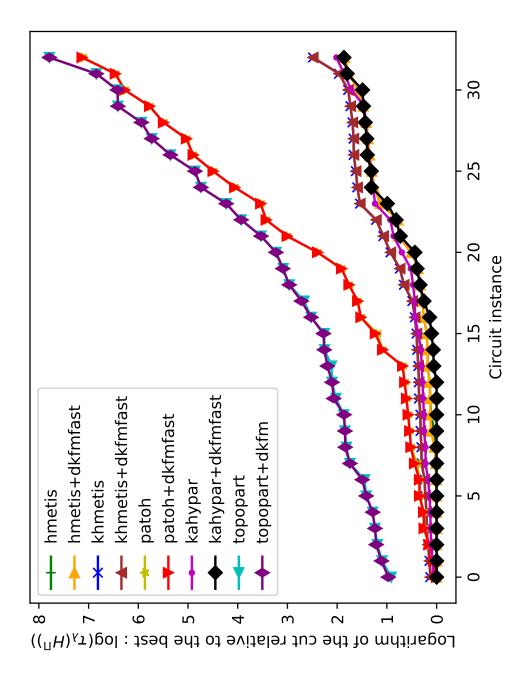

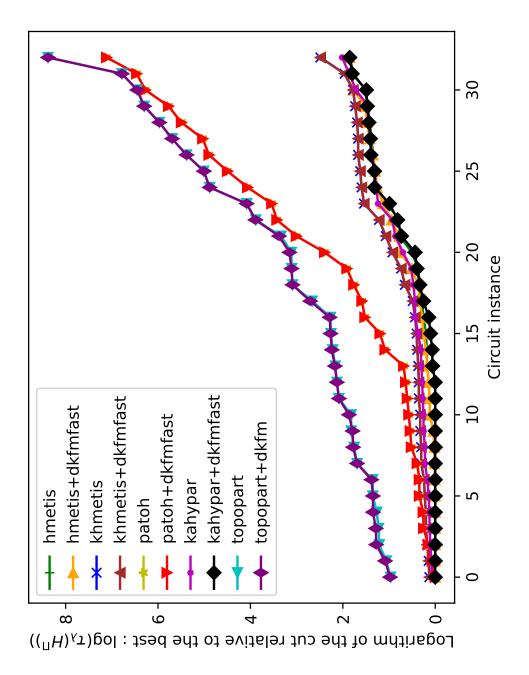

| A.10 Connectivity cost of DKFMFAST on target topology T2 284 |

| A.11 Connectivity cost of DKFMFAST on target topology T4 285 |

| A.12 Connectivity cost of DKFMFAST on target topology T5 286 |

| A.13 Balance cost on target topology T1 with DKFMFAST 300    |

| A.14 Balance cost on target topology T2 with DKFMFAST 301    |

| A.15 Balance cost on target topology T4 with DKFMFAST 302    |

| A.16 Balance cost on target topology T5 with DKFMFAST 303    |

xii J. Rodriguez

## List of Tables

| 1.1 | Notation summary                                                                                                 |

|-----|------------------------------------------------------------------------------------------------------------------|

| 3.1 | Characteristics of the ITC99 benchmark instances 61                                                              |

| 3.2 | Paths statistics for the ITC99 benchmark                                                                         |

| 3.3 | Applications of the Titan benchmark instances                                                                    |

| 3.4 | Characteristics of the Titan benchmark instances                                                                 |

| 3.5 | Paths statistics for the Titan benchmark                                                                         |

| 3.6 | Characteristics of the Chipyard benchmark instances                                                              |

| 3.7 | Paths statistics for the Chipyard benchmark instances 69                                                         |

| 5.1 | Definitions of indices and sets                                                                                  |

| 5.2 | Definitions of parameters                                                                                        |

| 5.3 | Definitions of variables                                                                                         |

| 5.4 | Results on path-cost $(f_p)$ degradation factor of partitions compared to those of produced by KHMETIS           |

| 5.5 | Results on connectivity-minus-one cost degradation factor of partitions compared to those of produced by KHMETIS |

| A.1 | Path cost results of clustering algorithms with a maximum size equal to 2                                        |

| A.2 | Path cost results of clustering algorithms with a maximum size equal to 4                                        |

| A.3 | Path cost results of clustering algorithms with a maximum size equal to 8                                        |

| A.4 | Path cost results of clustering algorithms with a maximum size equal to 16                                       |

| A.5 | Path cost results of clustering algorithms with a maximum size equal to 32                                       |

| A.6 | Path cost results of clustering algorithms with a maximum size equal to 64                                       |

| A.7 Path cost results of clustering algorithms with a maximum size equal to 128                                  |       |

|------------------------------------------------------------------------------------------------------------------|-------|

| A.8 Path cost results of clustering algorithms with a maximum size equal                                         |       |

| to 256                                                                                                           |       |

| A.9 Path cost results of clustering algorithms with a maximum size equal                                         |       |

| to 512                                                                                                           |       |

| A.10 Path cost results of clustering algorithms with a maximum size equal to 1024                                |       |

| to 1024                                                                                                          |       |

| to 2048                                                                                                          | . 197 |

| A.12 Path cost results of clustering algorithms with a maximum size equal                                        |       |

| to 4096                                                                                                          | . 198 |

| A.13 Results for critical path: $d_{\text{max}}^{\Pi}(H)$ , on target T1 for circuits in ITC                     |       |

| set                                                                                                              | . 200 |

| set                                                                                                              | . 201 |

| A.15 Results for critical path: $d_{\text{max}}^{\Pi}(H)$ , on target T3 for circuits in ITC                     |       |

| set                                                                                                              | . 202 |

| A.16 Results for critical path: $d_{\max}^{\Pi}(H)$ , on target T4 for circuits in ITC                           |       |

| Set                                                                                                              | . 203 |

| A.17 Results for critical path: $d_{\text{max}}^{\Pi}(H)$ , on target T5 for circuits in ITC set                 | . 204 |

| A.18 Results for critical path: $d_{\text{max}}^{\Pi}(H)$ , on target T6 for circuits in ITC                     |       |

| set                                                                                                              | . 205 |

| A.19 Results for critical path: $d_{\max}^{\Pi}(H)$ , on target T1 for circuits in Chip-                         |       |

| yard and Titan sets                                                                                              | . 206 |

| A.20 Results for critical path: $d_{\text{max}}^{\Pi}(H)$ , on target T2 for circuits in Chipyard and Titan sets | . 207 |

| A.21 Results for critical path: $d_{\text{max}}^{\Pi}(H)$ , on target T3 for circuits in Chip-                   |       |

| yard and Titan sets.                                                                                             | . 208 |

| A.22 Results for critical path: $d_{\text{max}}^{\Pi}(H)$ , on target T4 for circuits in Chip-                   |       |

| yard and Titan sets.                                                                                             |       |

| A.23 Results for critical path: $d_{\text{max}}^{\Pi}(H)$ , on target T5 for circuits in Chipyard and Titan sets |       |

| A.24 Results for critical path: $d_{\text{max}}^{\Pi}(H)$ , on target T6 for circuits in Chip-                   |       |

| yard and Titan sets                                                                                              |       |

| A.25 Results for connectivity cost: $f_{\lambda}(H^{\Pi})$ , on target T3 for circuits in                        |       |

| ITC set                                                                                                          |       |

| A.26 Results for connectivity cost: $f_{\lambda}(H^{\Pi})$ , on target T6 for circuits in                        |       |

| ITC set                                                                                                          | . 214 |

xiv J. Rodriguez

| A.27 Results for connectivity cost: $f_{\lambda}(H^{1})$ , on target T3 for circuits in            |    |

|----------------------------------------------------------------------------------------------------|----|

| Chipyard and Titan sets                                                                            | 15 |

| A.28 Results for connectivity cost: $f_{\lambda}(H^{\Pi})$ , on target T6 for circuits in          |    |

|                                                                                                    | 16 |

| A.29 Results for balance cost: $\beta(H^{\Pi})$ , on target T3 for circuits in ITC set.23          | 18 |

| A.30 Results for balance cost: $\beta(H^{\Pi})$ , on target T6 for circuits in ITC set.22          |    |

| A.31 Results for balance cost: $\beta(H^{\Pi})$ , on target T3 for circuits in Chip-               |    |

|                                                                                                    | 20 |

| A.32 Results for balance cost: $\beta(H^{\Pi})$ , on target T6 for circuits in Chip-               |    |

|                                                                                                    | 21 |

| A.33 Results for critical path: $d_{\max}^{\Pi}(H)$ , on target T1 for circuits in ITC             |    |

|                                                                                                    | 23 |

| A.34 Results for critical path: $d_{\max}^{\Pi}(H)$ , on target T2 for circuits in ITC             |    |

|                                                                                                    | 24 |

| A.35 Results for critical path: $d_{\text{max}}^{\Pi}(H)$ , on target T3 for circuits in ITC       |    |

|                                                                                                    | 25 |

| A.36 Results for critical path: $d_{\max}^{\Pi}(H)$ , on target T4 for circuits in ITC             |    |

|                                                                                                    | 26 |

| A.37 Results for critical path: $d_{\max}^{\Pi}(H)$ , on target T5 for circuits in ITC             |    |

|                                                                                                    | 27 |

| A.38 Results for critical path: $d_{\max}^{\Pi}(H)$ , on target T6 for circuits in ITC             |    |

|                                                                                                    | 28 |

| A.39 Results for critical path: $d_{\text{max}}^{\Pi}(H)$ , on target T1 for circuits in Chip-     |    |

|                                                                                                    | 29 |

| A.40 Results for critical path: $d_{\text{max}}^{\Pi}(H)$ , on target T2 for circuits in Chip-     |    |

| yard and Titan sets                                                                                | 30 |

| A.41 Results for critical path: $d_{\text{max}}^{\Pi}(H)$ , on target T3 for circuits in Chip-     |    |

| V                                                                                                  | 31 |

| A.42 Results for critical path: $d_{\text{max}}^{\Pi}(H)$ , on target T4 for circuits in Chip-     |    |

| yard and Titan sets                                                                                | 32 |

| A.43 Results for critical path: $d_{\text{max}}^{\Pi}(H)$ , on target T5 for circuits in Chip-     |    |

| yard and Titan sets                                                                                | 33 |

| A.44 Results for critical path: $d_{\text{max}}^{\Pi}(H)$ , on target T6 for circuits in Chip-     |    |

| yard and Titan sets                                                                                | 34 |

| A.45 Results for connectivity cost: $f_{\lambda}(H^{\Pi}) \times 10^3$ , on target T1 for circuits |    |

|                                                                                                    | 40 |

| A.46 Results for connectivity cost: $f_{\lambda}(H^{\Pi}) \times 10^3$ , on target T2 for circuits |    |

|                                                                                                    | 41 |

| A.47 Results for connectivity cost: $f_{\lambda}(H^{\Pi}) \times 10^3$ , on target T3 for circuits |    |

| in ITC set                                                                                         | 42 |

|                                                                                                    |    |

| A.48 Results for connectivity cost: $f_{\lambda}(H^{\Pi}) \times 10^3$ , on target T4 for circuits                                                                                    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| in ITC set                                                                                                                                                                            |

| A.49 Results for connectivity cost: $f_{\lambda}(H^{\Pi}) \times 10^3$ , on target T5 for circuits in ITC set                                                                         |

| A.50 Results for connectivity cost: $f_{\lambda}(H^{\Pi}) \times 10^3$ , on target T6 for circuits                                                                                    |

| in ITC set                                                                                                                                                                            |

| A.51 Results for connectivity cost: $f_{\lambda}(H^{\Pi}) \times 10^3$ , on target T1 for circuits                                                                                    |

| in Chipyard and Titan sets. $\dots \dots \dots$                                       |

| A.52 Results for connectivity cost: $f_{\lambda}(H^{\Pi}) \times 10^3$ , on target T2 for circuits                                                                                    |

| in Chipyard and Titan sets                                                                                                                                                            |

| A.53 Results for connectivity cost: $f_{\lambda}(H^{\Pi}) \times 10^3$ , on target T3 for circuits                                                                                    |

| in Chipyard and Titan sets                                                                                                                                                            |

| A.54 Results for connectivity cost: $f_{\lambda}(H^{\Pi}) \times 10^3$ , on target T4 for circuits                                                                                    |

| in Chipyard and Titan sets                                                                                                                                                            |

| A.55 Results for connectivity cost: $f_{\lambda}(H^{\Pi}) \times 10^3$ , on target T5 for circuits                                                                                    |

| in Chipyard and Titan sets                                                                                                                                                            |

| A.56 Results for connectivity cost: $f_{\lambda}(H^{\Pi}) \times 10^3$ , on target T6 for circuits                                                                                    |

| in Chipyard and Titan sets                                                                                                                                                            |

| A.57 Results for balance cost: $\beta(H^{\Pi})$ , on target T1 for circuits in ITC set.257                                                                                            |

| A.58 Results for balance cost: $\beta(H^{\Pi})$ , on target T2 for circuits in ITC set.258                                                                                            |

| A.59 Results for balance cost: $\beta(H^{\Pi})$ , on target T3 for circuits in ITC set.259 A.60 Results for balance cost: $\beta(H^{\Pi})$ , on target T4 for circuits in ITC set.260 |

| A.60 Results for balance cost: $\beta(H^{\Pi})$ , on target T5 for circuits in ITC set.261                                                                                            |

| A.62 Results for balance cost: $\beta(H^{\Pi})$ , on target T6 for circuits in ITC set.262                                                                                            |

| A.63 Results for balance cost: $\beta(H^{\Pi})$ , on target T1 for circuits in T1C set.202                                                                                            |

| yard and Titan sets. $\dots \dots \dots$                                              |

| A.64 Results for balance cost: $\beta(H^{\Pi})$ , on target T2 for circuits in Chip-                                                                                                  |

| yard and Titan sets                                                                                                                                                                   |

| A.65 Results for balance cost: $\beta(H^{\Pi})$ , on target T3 for circuits in Chip-                                                                                                  |

| yard and Titan sets                                                                                                                                                                   |

| A.66 Results for balance cost: $\beta(H^{\Pi})$ , on target T4 for circuits in Chip-                                                                                                  |

| yard and Titan sets                                                                                                                                                                   |

| A.67 Results for balance cost: $\beta(H^{\Pi})$ , on target T5 for circuits in Chip-                                                                                                  |

| yard and Titan sets                                                                                                                                                                   |

| A.68 Results for balance cost: $\beta(H^{\Pi})$ , on target T6 for circuits in Chip-                                                                                                  |

| yard and Titan sets                                                                                                                                                                   |

| A.69 Results of DKFMFAST effects on critical path: $d_{\text{max}}^{\Pi}(H)$ , on target T1 for circuits in ITC set                                                                   |

| T1 for circuits in ITC set                                                                                                                                                            |

| T2 for circuits in ITC set                                                                                                                                                            |

| 12 for offettion in 11 C 500                                                                                                                                                          |

xvi J. Rodriguez

| A.71 Results of DKFMFAST effects on critical path: $d_{\text{max}}^{\Pi}(H)$ , on target       |     |

|------------------------------------------------------------------------------------------------|-----|

|                                                                                                | 272 |

| A.72 Results of DKFMFAST effects on critical path: $d_{\text{max}}^{\Pi}(H)$ , on target       |     |

| T4 for circuits in ITC set                                                                     | 273 |

| A.73 Results of DKFMFAST effects on critical path: $d_{\text{max}}^{\Pi}(H)$ , on target       |     |

| T5 for circuits in ITC set                                                                     | 274 |

| A.74 Results of DKFMFAST effects on critical path: $d_{\text{max}}^{\Pi}(H)$ , on target       |     |

| T6 for circuits in ITC set                                                                     | 275 |

| A.75 Results of DKFMFAST effects on critical path: $d_{\text{max}}^{\Pi}(H)$ , on target       |     |

| T1 for circuits in Chipyard and Titan sets                                                     | 276 |

| A.76 Results of DKFMFAST effects on critical path: $d_{\text{max}}^{\text{II}}(H)$ , on target |     |

| T2 for circuits in Chipyard and Titan sets                                                     | 277 |

| A.77 Results of DKFMFAST effects on critical path: $d_{\max}^{\Pi}(H)$ , on target             |     |

| T3 for circuits in Chipyard and Titan sets                                                     | 278 |

| A.78 Results of DKFMFAST effects on critical path: $d_{\max}^{\Pi}(H)$ , on target             | a-a |

| T4 for circuits in Chipyard and Titan sets                                                     | 279 |

| A.79 Results of DKFMFAST effects on critical path: $d_{\max}^{\Pi}(H)$ , on target             | 200 |

| T5 for circuits in Chipyard and Titan sets                                                     | 280 |

| A.80 Results of DKFMFAST effects on critical path: $d_{\text{max}}^{\Pi}(H)$ , on target       | 001 |

| T6 for circuits in Chipyard and Titan sets                                                     | 281 |

| A.81 Results of DKFMFAST effects on connectivity cost: $f_{\lambda}(H^{\Pi}) \times 10^3$ ,    | 207 |

| on target T1 for circuits in ITC set                                                           | 287 |

| A.82 Results of DKFMFAST effects on connectivity cost: $f_{\lambda}(H^{\Pi}) \times 10^3$ ,    | 200 |

| on target T2 for circuits in ITC set                                                           | 288 |

| A.83 Results of DKFMFAST effects on connectivity cost: $f_{\lambda}(H^{\Pi}) \times 10^3$ ,    | 289 |

| on target T3 for circuits in ITC set                                                           | 209 |

| on target T4 for circuits in ITC set                                                           | 290 |

| A.85 Results of DKFMFAST effects on connectivity cost: $f_{\lambda}(H^{\Pi}) \times 10^3$ ,    | 290 |

| on target T5 for circuits in ITC set                                                           | 291 |

| A.86 Results of DKFMFAST effects on connectivity cost: $f_{\lambda}(H^{\Pi}) \times 10^3$ ,    | 201 |

| on target T6 for circuits in ITC set                                                           | 292 |

| A.87 Results of DKFMFAST effects on connectivity cost: $f_{\lambda}(H^{\Pi}) \times 10^3$ ,    | 202 |

| on target T1 for circuits in Chipyard and Titan sets                                           | 293 |

| A.88 Results of DKFMFAST effects on connectivity cost: $f_{\lambda}(H^{\Pi}) \times 10^3$ ,    |     |

| on target T2 for circuits in Chipyard and Titan sets                                           | 294 |

| A.89 Results of DKFMFAST effects on connectivity cost: $f_{\lambda}(H^{\Pi}) \times 10^3$ ,    |     |

| on target T3 for circuits in Chipyard and Titan sets                                           | 295 |

| A.90 Results of DKFMFAST effects on connectivity cost: $f_{\lambda}(H^{\Pi}) \times 10^3$ ,    |     |

| on target T4 for circuits in Chipyard and Titan sets                                           | 296 |

| • •                                                                                            |     |

| A.91 Results of DKFMFAST effects on connectivity cost: $f_{\lambda}(H^{\rm II}) \times 10^{3}$ , |     |

|--------------------------------------------------------------------------------------------------|-----|

| on target T5 for circuits in Chipyard and Titan sets                                             | 297 |

| A.92 Results of DKFMFAST effects on connectivity cost: $f_{\lambda}(H^{\Pi}) \times 10^3$ ,      |     |

| on target T6 for circuits in Chipyard and Titan sets                                             | 298 |

| A.93 Results of DKFMFAST effects on balance cost: $\beta(H^{\Pi})$ , on target                   |     |

| T1 for circuits in ITC set                                                                       | 304 |

| A.94 Results of DKFMFAST effects on balance cost: $\beta(H^{\Pi})$ , on target                   |     |

| T2 for circuits in ITC set                                                                       | 305 |

| A.95 Results of DKFMFAST effects on balance cost: $\beta(H^{\Pi})$ , on target                   |     |

| T3 for circuits in ITC set                                                                       | 306 |

| A.96 Results of DKFMFAST effects on balance cost: $\beta(H^{\Pi})$ , on target                   |     |

| T4 for circuits in ITC set                                                                       | 307 |

| A.97 Results of DKFMFAST effects on balance cost: $\beta(H^{\Pi})$ , on target                   |     |

| T5 for circuits in ITC set                                                                       | 308 |

| A.98 Results of DKFMFAST effects on balance cost: $\beta(H^{\Pi})$ , on target                   |     |

| T6 for circuits in ITC set                                                                       | 309 |

| A.99 Results of DKFMFAST effects on balance cost: $\beta(H^{\Pi})$ , on target                   |     |

| T1 for circuits in Chipyard and Titan sets                                                       | 310 |

| A.10¢Results of DKFMFAST effects on balance cost: $\beta(H^{\Pi})$ , on target                   |     |

| T2 for circuits in Chipyard and Titan sets                                                       | 311 |

| A.101Results of DKFMFAST effects on balance cost: $\beta(H^{\Pi})$ , on target                   |     |

| T3 for circuits in Chipyard and Titan sets                                                       | 312 |

| A.102Results of DKFMFAST effects on balance cost: $\beta(H^{\Pi})$ , on target                   |     |

| T4 for circuits in Chipyard and Titan sets                                                       | 313 |

| A.103Results of DKFMFAST effects on balance cost: $\beta(H^{\Pi})$ , on target                   |     |

| T5 for circuits in Chipyard and Titan sets                                                       | 314 |

| A.104Results of DKFMFAST effects on balance cost: $\beta(H^{\Pi})$ , on target                   |     |

| T6 for circuits in Chipyard and Titan sets                                                       | 315 |

xviii J. Rodriguez

# Résumé étendu en français

Un FPGA ("Field Programmable Gate Array") est un circuit intégré comprenant un grand nombre de ressources logiques programmables et interconnectables. Ces ressources permettent d'implémenter, par programmation, un circuit électronique numérique tel qu'un microprocesseur, un accélérateur de calculs ou un système hybride complexe sur puce. Les FPGA sont largement utilisés dans le domaine de la conception de circuits intégrés, car ils permettent d'obtenir des circuits prototypes très rapidement, sans devoir fabriquer la puce sur silicium. Cependant, certains circuits sont trop grands pour être implantés sur un seul FPGA. Pour résoudre ce problème, il est possible d'utiliser une plate-forme composée de plusieurs FPGA fortement interconnectés, qui peuvent être considérés comme un seul FPGA virtuel donnant accès à toutes les ressources de la plateforme. Cette solution, bien qu'élégante, pose plusieurs problèmes. En particulier, les outils existants ne tiennent pas compte de toutes les contraintes du problème de placement à résoudre pour placer efficacement un circuit sur une plate-forme multi-FPGA. Par exemple, les fonctions de coût actuelles ne sont pas conçues pour minimiser le temps de propagation des signaux entre les registres, qui est pourtant crucial pour la performance du prototype résultant, ni ne prennent en compte les contraintes de capacité induites par le routage des connexions.

Le processus typique de conception de matériel électronique numérique comprend plusieurs étapes, incluant le prototypage, la vérification, le placement et le routage, qui peuvent concerner de très grands circuits logiques. Les méthodes mises en œuvre au cours de ces étapes tirent souvent parti d'approches de type « diviser pour régner », afin de séparer les circuits en sous-circuits de plus petites tailles. Ces sous-systèmes sont plus faciles à manipuler et visent à réduire le travail sur le circuit global.

Pour prototyper de grands circuits qui ne peuvent être implantés dans un seul FPGA, une plate-forme multi-FPGA est nécessaire. Dans ce cas, l'approche « diviser pour régner » est utilisée pour diviser les circuits en plusieurs morceaux, un pour chaque FPGA. Pour produire des partitions valables, il faut tenir compte des limites de capacité de chaque FPGA et des liens d'interconnexion. En outre, les partitions doivent éviter d'augmenter la longueur du chemin le plus long, appelé chemin critique. En effet, pour les circuits VLSI, la longueur du chemin critique détermine la fréquence maximale à laquelle le circuit peut fonctionner, et le placement de longs chemins sur plusieurs FPGA est susceptible de dégrader le chemin critique, du fait du temps de traversée plus long entre les deux composants.

L'objectif de cette thèse est de concevoir des modèles de partitionnement et de placement d'hypergraphes adaptés au problème de l'implantation de circuits sur une plate-forme composée de plusieurs FPGA. Ces modèles seront spécifiquement conçus pour répondre aux objectifs et aux critères de performance définis par les

concepteurs de circuits.

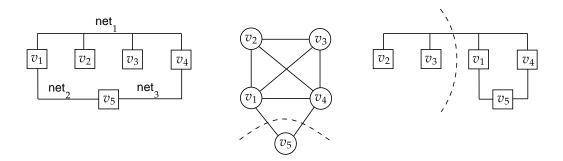

Le partitionnement d'hypergraphe multi-contraintes (MCHP) est couramment utilisé pour résoudre le problème de partitionnement de circuits et de prototypage. Dans ce contexte, les sommets de l'hypergraphe modélisent les broches des composants logiques et les hyperarêtes de l'hypergraphe représentent les fils qui les relient. Le problème de partitionnement équilibré des graphes est un problème NP-Difficile [125] pour lequel il n'existe pas de facteur d'approximation constant [11] à moins que P = NP.

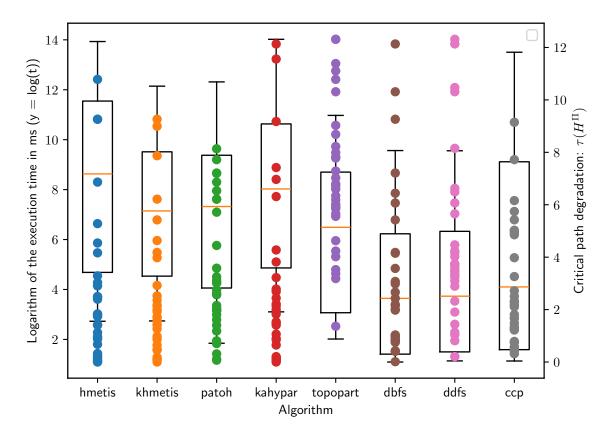

Au cours des 30 dernières années, plusieurs outils de partitionnement d'hypergraphes ont été développés, tels que HMETIS et son dérivé KHMETIS, PATOH et KAHYPAR. Ces outils cherchent à minimiser la coupe (ou *min-cut*) entre les différentes parties calculées, cette coupe pouvant être mesurée selon différentes métriques.

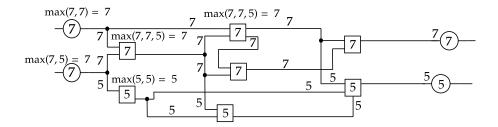

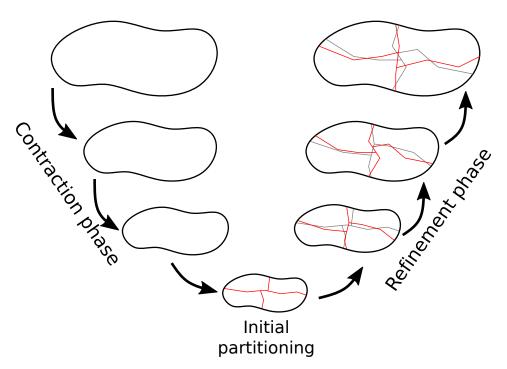

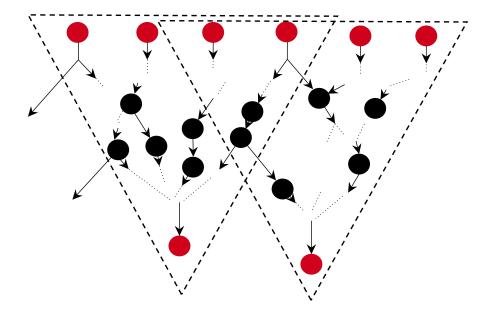

Pour répartir les sommets entre les différentes parties, ces outils utilisent un schéma multi-niveaux, qui se compose de trois phases: contraction, partitionnement initial, et raffinement. La phase de contraction utilise récursivement une méthode de regroupement pour transformer le problème en un problème plus petit, qui possède les mêmes propriétés topologiques. Ensuite, un partitionnement initial est calculé sur le plus petit problème. Enfin, pour chaque niveau, la solution du niveau le plus grossier est prolongée jusqu'au niveau le plus fin, puis affinée à l'aide d'un algorithme d'optimisation locale. L'utilisation du schéma multi-niveaux permet de réduire le temps de calcul par rapport à une approche de partitionnement directe, les algorithmes de partitionnement les plus coûteux n'étant appliqués qu'aux hypergraphes les plus petits, alors que les algorithmes d'otimisation locale sont moins gourmands en ressources du fait qu'ils n'opèrent que sur une zone réduite des hypergraphes, à savoir la frontière entre les parties déjà trouvées.

### État de l'art

De nombreuses approches ont été tentées pour améliorer les performances du partitionnement de circuits. Nous présentons ici quelques travaux récents sur le partitionnement de circuits pour le prototypage rapide qui prennent en compte les contraintes de performance. Beaucoup de ces travaux utilisent des outils de partitionnement min-cut existants, utilisés comme des boîtes noires, au sein d'algorithmes plus complexes, en pondérant les sommets et arêtes des hypergraphes afin de prendre en compte des contraintes supplémentaires que le partitionneur doit respecter.

Par exemple, dans [4], les auteurs présentent une approche multi-objectif basée sur HMETIS. Les auteurs déterminent un ensemble fini de chemins les plus critiques à chaque étape de partitionnement, en utilisant un coût tenant compte de trois facteurs : la longueur du chemin critique, le nombre de fois où les chemins

de longueur critique sont coupés et le poids des hyperarcs associés aux chemins critiques.

Dans [38], les auteurs comparent une méthode classique utilisant HMETIS pour le partitionnement, suivie d'un algorithme de placement, à une approche dérivée qui effectue du placement et du routage pendant l'étape de partitionnement. Les résultats produisent de meilleures valeurs de chemin critique par rapport à l'approche en deux étapes. Plus récemment, dans [127], les auteurs effectuent un pré-traitement et un post-traitement de l'hypergraphe considéré afin d'intégrer l'objectif de minimisation du chemin critique dans la métrique de la taille de coupe, en utilisant HMETIS comme outil de partitionnement. Cependant, la minimisation de la taille des coupes n'est souvent pas l'objectif le plus pertinent. En outre, le fait de biaiser les fonctions de coût min-cut pour prendre en compte la minimisation du coût de chemins est insuffisant.

#### Contributions

Nos travaux portent sur le calcul du partitionnement équilibré d'hypergraphes avec minimisation de *coût du chemin critique*, en plus de l'objectif classique de la minimisation de coupe, qui est toujours pertinent pour nous car il contribue à réduire les contraintes de capacité de communication entre FPGA.

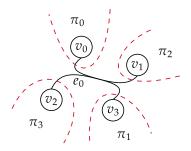

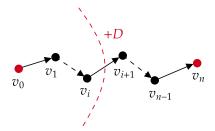

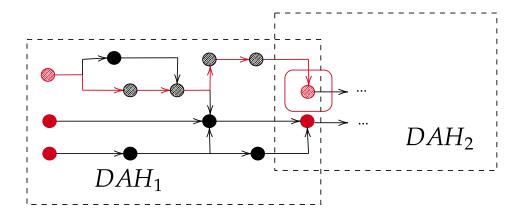

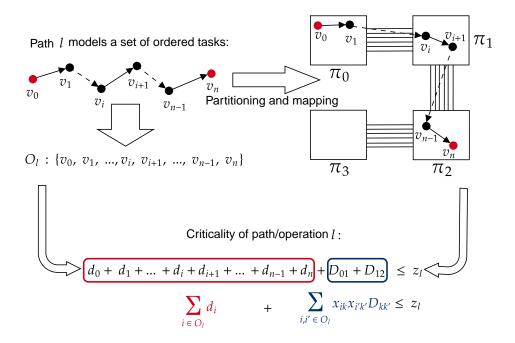

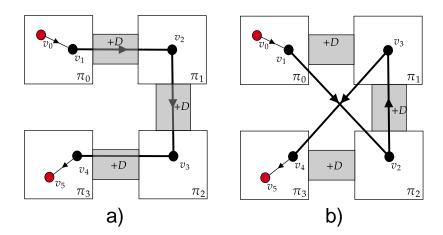

La première contribution de cette thèse est la définition d'une représentation spécifique des circuits électroniques numériques qui consiste en une union d'hypergraphes acycliques orientés (ou DAH, pour directed acyclic hypergraph) [160]. L'hypergraphe global représentant l'ensemble du circuit est supposé être connexe; dans le cas contraire, ses composantes connexes peuvent être traitées indépendamment, aux capacités des FPGA près. Les sommets source et puits de chaque DAH sont étiquetés en rouge, tandis que les autres sommets sont en noir. Les sommets rouges représentent généralement des registres et des ports d'entrée sortie (E/S) et peuvent être partagés entre plusieurs DAH, ce qui rend connexe l'hypergraphe global. Les sommets noirs représentent des circuits combinatoires. Une fonction de coût des chemins modélise l'impact d'une coupe sur les chemins des DAHs pendant le partitionnement. Chaque partition d'un hypergraphe entraînera des coupures le long de certains chemins, induisant un coût de traversée supplémentaire. Notre objectif est de trouver une partition qui réduise la longueur maximale du chemin entre deux sommets rouges, qui correspond au temps minimum nécessaire pour calculer et sauvegarder les données de l'état du circuit dans les registres, et qui minimise également la taille de la coupe. Dans notre contexte, nous supposons que le coût de routage entre les parties puisse être non uniforme.

La plupart des méthodes actuelles de partitionnement de circuits sont basées sur des outils de partitionnement de graphes à usage général disponibles publique-

ment. Cependant, les outils de partitionnement actuels utilisent un modèle de coût qui n'est pas adapté au problème traité dans cette thèse. De plus amples détails sur les méthodes actuelles et leurs limites peuvent être trouvés dans le chapitre 2.

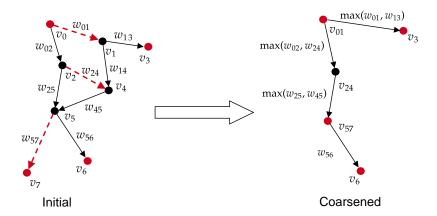

L'accent est d'abord mis sur les algorithmes de regroupement, c'est-à-dire les algorithmes dont l'objectif est de réduire la taille du problème. Ces algorithmes procèdent par fusion de sommets, c'est-à-dire que deux sommets deviennent un seul sommet ayant un poids égal à la somme des deux sommets regroupés. A ce titre, cette thèse propose une étude sur la pertinence du choix des sommets à fusionner. Dans cette étude, nous proposons de pondérer un couple de sommets en fonction du chemin critique local qui les traverse. Sur la base de cette stratégie de pondération, nous proposons une adaptation de l'algorithme de contraction d'hypergraphes Heavy Edge Matching (HEM), ainsi qu'un algorithme de regroupement de sommets (clustering), appelé Binary Search Clustering (BSC). Les résultats expérimentaux démontrent que l'algorithme BSC est plus performant que l'algorithme HEM sur notre modèle de pondération précité. La poursuite de nos travaux sur ce problème de regroupement concerne le rapport d'approximation paramétré par la taille maximum d'un groupe (cluster). Nous démontrons sous certaines hypothèses, une amélioration du rapport d'approximation, c'est-à-dire, le rapport entre le cout de la pire solution et la meilleure solution.

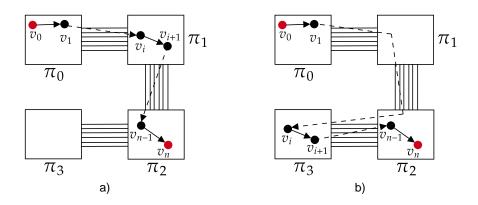

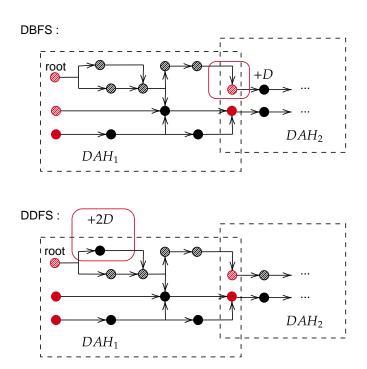

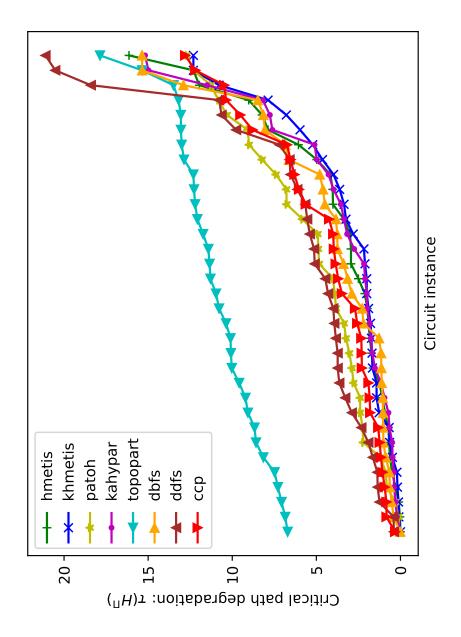

D'autres contributions de cette thèse concernent des algorithmes de partitionnement gloutons, présentés pour la première fois dans notre travail [160], et une approche de programmation en nombres entiers basée sur des contraintes d'ordonnancement tirées de notre travail [161]. Les algorithmes gloutons sont basés sur des algorithmes de parcours d'hypergraphe tels que le parcours en largeur et le parcours en profondeur. Nous avons aussi étudié un algorithme basé sur le calcule des composantes connexes. Afin de créer plusieurs composantes, nous fixons une taille à ne pas dépasser pour chaque composante. Dans nos travaux, nous tirons profit de notre schéma de pondération afin de guider l'algorithme de calcul des composantes connexes dans l'hypergraphes. Notons que ces algorithmes ne tiennent pas compte de la topologie cible. De fait, les résultats obtenus nous montrent que ces algorithmes sont performants vis-à-vis de l'état de l'art sur des topologies totalement connectées (graphe complet), mais moins efficaces pour d'autres topologies.

La suite de nos travaux s'est concentrée sur une extension de l'algorithme de recherche locale proposé par C. Fidducia et R. Mattheyses [75]. Notre algorithme étendu, appelé DKFM, permet d'optimiser la dégradation du chemin critique d'un circuit pour une partition passée en paramètre. Nous avons remarqué lors de nos expérimentations que notre algorithme DKFM permet de réduire la dégradation du chemin critique. Cependant, comme DKFM est un algorithme de recherche local, l'optimisation reste limitée vis-à-vis de partitions initiales calculées sans

tenir compte de la topologie cible.

### Perspectives

Tous nos algorithmes ont été mis en œuvre en langage C, dans un cadre logiciel composé de structures de données pour représenter notre modèle d'hypergraphe rouge-noir, ainsi que des routines de service auxiliaires. Le problème de partitionnement adressé dans cette thèse diffère du problème de partitionnement traité par les outils HMETIS, KHMETIS, KAHYPAR et PATOH et, à notre connaissance, il n'existe pas d'outil public dédié à notre problème de partitionnement. Nous avons donc décidé de formaliser notre travail dans le logiciel RAISIN. Cet outil comprend un schéma de partitionnement composé des algorithmes présentés dans cette thèse, y compris une adaptation de notre algorithme de raffinement appelé DKFM. Notre algorithme de raffinement tient compte de la topologie mais peut ne pas être en mesure de fixer un partitionnement initial ne tenant pas compte de la topologie, car un algorithme de raffinement local n'est pas conçu pour reconsidérer les décisions globales. Par conséquent, la prise en compte de la topologie cible devrait être intégrée dans les algorithmes de partitionnement initial.

Notons également qu'il existe des biais d'approximation sur les chemins, crées pendant la phase de contraction. En effet, lorsque des sommets sont fusionnés ensemble, des faux chemins peuvent être crée et pris en compte. Par conséquent le maintient d'un cohérence sur chemins combinatoire doivent être étudiés et ajoutés au sein des algorithmes de contractions afin de faciliter le travail pour les algorithmes de partitionnement initiaux et de raffinement.

## Introduction

In the context of prototyping digital circuits on a multiple Field Programmable Gate Array (FPGA), the circuit may be divided into smaller, manageable sections that can be implemented on separate Field-Programmable Gate Arrays (FPGAs) for testing and validation. This process is a crucial step in designing and testing large, complex digital systems.

### Digital electronic circuits

A digital electronic circuit is a system of interconnected electronic components that manipulate discrete, binary signals to perform specific functions. Unlike analog circuits, which deal with continuous, varying signals, digital circuits operate using two discrete states: 0 (low) and 1 (high). These states represent binary logic levels and are used to represent information in a form that can be easily processed, stored, and transmitted by digital systems like computers. A digital circuit consists of several key components that collectively process binary signals, enabling boolean manipulation of information in electronic devices. Logic gates are the basic building blocks that perform basic boolean operations such as AND, OR and NOT, based on input signal values. Flip-flops, also denoted as registers, are used to store temporary data at fixed moments in time, determined by a global clock signal that periodically oscillates between 0 and 1. This is useful for both temporary storage and global synchronization between parts of the circuit. Therefore, digital electronic circuits are globally synchronized by the clock signal. Logic gates and flip-flops are the elementary blocks for constructing more complex structures: counters generate sequences of binary numbers, essential for applications such as timing and event counting. Multiplexers and demultiplexers make it easier to route signals to different destinations. Arithmetic and Logic Units (ALUs) perform arithmetic and logic operations. Memory units store data and instructions, distinguishing between volatile (such as RAM) and non-volatile (such as ROM) types. Microprocessors and controllers act as central processing units, executing instructions in digital systems. Together, these components enable electronic devices to process information with precision and reliability. A microprocessor or controller is an assembly of different types of units as described above.

### Field-Programmable Gate Arrays

A Field Programmable Gate Array (FPGA) is a versatile electronic device that primarily consists of a matrix of programmable logic gates, a configurable interconnect network, programmable memories, clock management, input/output interfaces, a power management system. The logic gate array is the heart of the

FPGA, providing configurable blocks to perform various logic operations. Depending on the FPGA used, other elements may be present, such as hardwired multipliers or accelerators for neural network inference. Interconnects are used to link these elements and provide the necessary connections. Programmable memory resources are used to store data. The device also contains mechanisms for managing the clock signal, pins for I/O, a configuration block for storing parameters, and a power management system to ensure proper operation. Depending on the specific design, additional features such as specialized interfaces may be present for specific applications. These specific resources enable the implementation of complex digital electronic circuits by interconnecting them. FPGAs are reprogrammable after fabrication, allowing rapid design iterations and customization for specific tasks [28]. Their parallel processing capability, derived from an array of programmable logic devices connected by configurable routing resources, makes them exceptionally efficient for tasks requiring simultaneous operations. This feature is critical for accelerating computations in scientific applications, such as high-performance computing for simulation and scientific modeling. Their adaptability and programmability are essential in scientific research and development, enabling rapid prototyping and testing of novel algorithms and hardware designs. Overall, FPGAs are a cornerstone technology in modern digital electronics, with far-reaching implications for scientific and technological progress.

### Circuit partitioning for rapid prototyping

Circuit partitioning consist in dividing the circuit into different parts. In the context of circuit prototyping, a circuit is synthesized and implemented on an FPGA. When a circuit is too large to fit into a single FPGA, a multi-FPGA platform may be used. The step of partitioning a digital circuit for a multi-FPGA platform for rapid prototyping is a critical methodology in digital system design. It involves breaking down a complex electronic circuit into smaller, manageable sections that can then be implemented on separate FPGAs for testing and validation. This process allows designers to distribute the computational load across multiple FP-GAs, enabling the system to handle more complex tasks than a single FPGA could handle alone.

Partitioning must aim to optimize performance, resource utilization, and communication between FPGAs. Partitioning can potentially reduce circuit performance because communication between two FPGAs adds some amount of delay. Moreover, multi-FPGA platforms cannot be fully interconnected, so additional routing delay can also affect circuit performance. By carefully assigning specific modules or functions to different FPGAs, engineers can strike a balance between minimizing inter-FPGA communication and ensuring that each FPGA has suffi-

cient resources to perform its designated tasks effectively. This approach is particularly valuable when designing large-scale digital systems, such as high-performance computing applications, where the complexity and computational demands require the use of multiple FPGAs working together.

The effectiveness of the partitioning strategy will greatly influence the success of the multi-FPGA prototype.

A formal definition for the problem of circuit partitioning for multi-FPGAs platform can be found in Chapter 1, section 1.3.

#### Contributions

The first contribution of this thesis is the definition of the red-black hypergraph model, which is an extension of hypergraphs dedicated to the representation of digital electronic circuits. This representation allows us to better model physical constraints such as how partitioning affects performance, which is one of the main objectives addressed in this thesis. Based on this abstraction, we design a cost model and specific algorithms to solve the circuit partitioning problem for multi-FPGA platforms. Most current circuit partitioning methods are based on publicly available general-purpose graph partitioning tools. However, current partitioning tools use a cost model that is not suited for the problem addressed in this thesis. More details on current methods and their limitations can be found in Chapter 2.

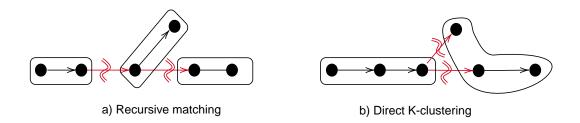

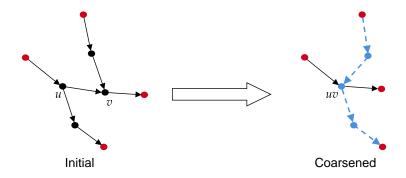

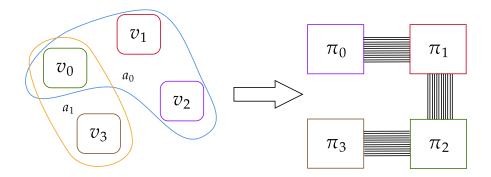

Existing tools take advantage of the *multilevel framework*, which consists of three phases: *coarsening*, *initial partitioning* and *refinement*. The coarsening phase recursively uses a clustering method to transform the circuit model into a smaller one. During the second phase, an initial partitioning is computed on the resulting smaller circuit. Then, in the third phase, an algorithm is applied at each recursion level to prolong the computed circuit partition to the upper level and subsequently refine it. The multilevel framework reduces computation time compared to a direct partitioning approach. Computation time is important because partitioning a large circuit is a difficult and time-consuming problem. This is why this thesis presents algorithms for each stage of the multilevel framework.

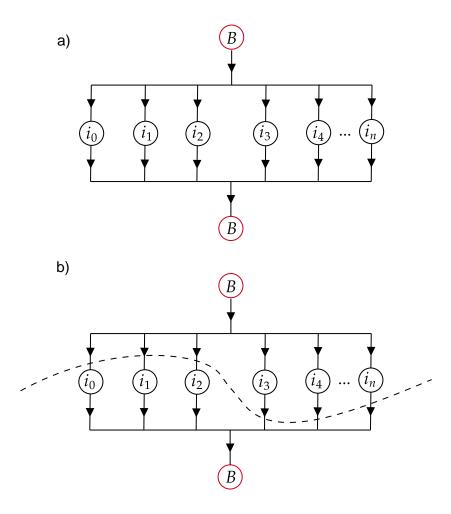

The initial focus is on clustering algorithms, *i.e.*, algorithms whose goal is to reduce problem size. These algorithms proceed by merging elements, *i.e.*, two elements become a single element with a weight equal to the sum of the weights of the merged elements. For that matter, this thesis proposes a study on the relevance of the choice of the elements to be merged. Based on this study, an adaptation of the Heavy Edge Matching (HEM) algorithm is proposed, as well as a clustering algorithm with variable cluster size, called Binary Search Clustering (BSC). Experimental results demonstrate that BSC performs better than HEM on our circuit model. An improved result for the approximation complexity parameterized by

cluster size is also presented in this study on clustering algorithms [162].