# Programming Models and Runtime Systems for Heterogeneous Architectures

Sylvain Henry

## ► To cite this version:

Sylvain Henry. Programming Models and Runtime Systems for Heterogeneous Architectures. Other [cs.OH]. Université Sciences et Technologies - Bordeaux I, 2013. English. NNT: 2013BOR14899. tel-00948309

# HAL Id: tel-00948309 https://theses.hal.science/tel-00948309v1

Submitted on 18 Feb 2014  $\,$

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés. Numéro d'ordre: 4899

# THÈSE

### présentée à

### L'UNIVERSITÉ BORDEAUX 1

École Doctorale de Mathématiques et Informatique de Bordeaux

par Sylvain HENRY

POUR OBTENIR LE GRADE DE

# DOCTEUR

SPÉCIALITÉ : INFORMATIQUE

\*\*\*\*\*\*

# Modèles de programmation et supports exécutifs pour architectures hétérogènes

Programming Models and Runtime Systems for Heterogeneous Architectures

### Composition du jury

| Président :                                                           | M. Luc Giraud, Directeur de Recherche à Inria                                                                                                                                                              |

|-----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rapporteurs :                                                         | M. Jean-François Méhaut, Professeur à l'Université de Grenoble<br>M. François Bodin, Professeur à l'Unviersité de Rennes                                                                                   |

| <i>Examinateurs :</i><br>(directeur de thèse)<br>(directeur de thèse) | M. Eric Petit, Ingénieur de Recherche à l'Université de Versailles Saint Quentin<br>M. Denis Barthou, Professeur à l'Institut Polytechnique de Bordeaux<br>M. Alexandre Denis, Chargé de Recherche à Inria |

### Résumé en français

Le travail réalisé lors de cette thèse s'inscrit dans le cadre du calcul haute performance sur architectures hétérogènes. Pour faciliter l'écriture d'applications exploitant ces architectures et permettre la portabilité des performances, l'utilisation de supports exécutifs automatisant la gestion des certaines tâches (gestion de la mémoire distribuée, ordonnancement des noyaux de calcul) est nécessaire. Une approche bas niveau basée sur le standard OpenCL est proposée ainsi qu'une approche de plus haut niveau basée sur la programmation fonctionnelle parallèle, la seconde permettant de pallier certaines difficultés rencontrées avec la première (notamment l'adaptation de la granularité).

Mots-clés : calcul haute performance, architectures hétérogènes, supports exécutifs, OpenCL

### Contexte de la recherche

L'évolution des architectures des super-calculateurs montre une augmentation ininterrompue du parallélisme (nombre de cœurs, etc.). La tendance récente est à l'utilisation d'architectures hétérogènes composant différentes architectures et dans lesquelles certains cœurs sont spécialisés dans le traitement de certains types de calculs (e.g. cartes graphiques pour le calcul massivement parallèle).

Les architectures matérielles ont influencé les modèles et les langages de programmation utilisés dans le cadre du calcul haute performance. Un consortium s'est formé pour établir la spécification OpenCL permettant de répondre au besoin de disposer d'une interface unifiée pour utiliser les différents accélérateurs. Cette spécification s'inspire notamment de l'interface CUDA développée par NVIDIA pour ses propres accélérateurs graphiques. Depuis lors, de nombreux fabricants fournissent une implémentation OpenCL pour piloter leurs accélérateurs (AMD, Intel, etc.).

L'écriture d'applications utilisant l'interface OpenCL ou les autres interfaces de bas niveau est notoirement difficile, notamment lorsqu'on cherche à écrire des codes qui puissent être portables entre différentes architectures hétérogènes. C'est pourquoi la tendance actuelle est au développement de supports exécutifs (*runtime systems*) permettant d'automatiser la gestion des ressources matérielles (mémoires, unités de calcul, etc.). Ces supports exécutifs s'utilisent par le biais de modèles de programmation de plus haut niveau, notamment par la création explicite de graphes de tâches. Cependant, aucun standard pour ces modèles de programmation n'a encore émergé.

Lors de cette thèse, en nous inspirant des supports exécutifs existants, nous nous sommes intéressés au développement de supports exécutifs plus avancés à différents points de vue : simplicité du modèle de programmation fourni à l'utilisateur, portabilité des performances notamment par le support de l'automatisation de l'adaptation de la granularité des tâches, support des interfaces de programmation reconnues (dans notre cas l'interface OpenCL), etc.

### Démarche adoptée

Deux approches ont été menées en parallèle lors de cette thèse : la première consistait à partir du standard OpenCL qui propose un modèle de programmation standard de bas niveau (ges-

tion explicite des mémoires et des noyaux de calcul par l'utilisateur) et à l'étendre de façon à intégrer des mécanismes de gestion de la mémoire et d'ordonnancement des noyaux automatisés. La seconde approche consistait à ne pas nous imposer de contrainte sur le modèle de développement fourni à l'utilisateur de façon à pouvoir proposer celui qui nous semblerait le plus adapté au but poursuivi.

### Extension du standard OpenCL

Nous avons développé notre propre implémentation de la spécification OpenCL ayant la particularité de ne piloter aucun accélérateur directement mais d'utiliser les autres implémentations OpenCL disponibles pour cela. Afin de fournir les mécanismes existants dans certains supports exécutifs (gestion de la mémoire et ordonnancement des noyaux de calculs automatiques) nous avons choisi de faire utiliser le support exécutif StarPU par notre implémentation, d'où son nom SOCL pour StarPU OpenCL. Tout d'abord nous avons fourni une plateforme unifiée : avec OpenCL, les implémentations fournies par les fabricants d'accélérateurs ne peuvent interagir entre elles (synchronisations, etc.) alors que par l'intermédiaire de SOCL elles peuvent. Pour cela, toutes les entités OpenCL ont été encapsulées dans SOCL et les mécanismes manquants ont pu être ajoutés.

Afin d'ajouter le support automatique de la gestion de la mémoire distribuée, nous avons fait en sorte que chaque *buffer* OpenCL alloué par l'application avec SOCL alloue une *Data* StarPU : lorsqu'un noyau de calcul utilise un de ces *buffers*, StarPU se charge de le transférer dans la mémoire appropriée. De la même façon, les noyaux de calculs (*kernels*) créés à partir de SOCL sont associés à des *codelets* StarPU puis à des tâches StarPU lorsqu'ils sont exécutés. De cette façon, SOCL bénéficie des mécanismes d'ordonnancement automatique des noyaux de calculs fournis par StarPU. Enfin, les contextes OpenCL (i.e. ensembles d'accélérateurs) sont associés aux contextes d'ordonnancement de StarPU de sorte qu'il est possible de contrôler précisément l'ordonnancement automatique fourni par SOCL à travers un mécanisme préexistant dans OpenCL.

### Approche par programmation fonctionnelle parallèle

Les approches actuelles pour la programmation des architectures parallèles hétérogènes reposent majoritairement sur l'utilisation de programmes séquentiels auxquels on adjoint des mécanismes pour définir du parallélisme (typiquement par le truchement de la création d'un graphe de tâches). Nous nous sommes intéressés à une approche différente dans laquelle on utilise un modèle de programmation intrinsèquement parallèle : modèle fonctionnel pur avec évaluation en parallèle. Notre choix s'est porté sur ce modèle du fait de sa similitude avec la programmation d'architectures hétérogènes : les noyaux de calculs sont des fonctions pures (sans effets de bords autres que sur certains de leurs paramètres), les dépendances entre les noyaux de calculs décrivent le plus souvent des dépendances de type flot de données. Nous avons donc proposé un modèle fonctionnel parallèle et hétérogène dans lequel on combine des noyaux de calculs écrits avec des langages de bas niveau (OpenCL, C, Fortran, CUDA, etc.) et un langage de coordination purement fonctionnel.

Pour notre première implémentation, nommée HaskellPU, nous avons combiné le compilateur GHC avec le support exécutif StarPU. Cela nous a permis de montrer qu'il était possible de créer un graphe de tâches à partir d'un programme fonctionnel et qu'il était possible de modifier statiquement ce graphe en utilisant les règles de réécriture de GHC. Afin de mieux contrôler l'évaluation parallèle des programmes fonctionnels et l'exécution des noyaux de calculs sur les accélérateurs, nous avons conçu une seconde implémentation nommée ViperVM totalement indépendante de GHC et de StarPU.

### **Résultats obtenus**

Notre implémentation du standard OpenCL montre qu'il est possible de l'étendre pour améliorer la portabilité des applications sur les architectures hétérogènes. Les performances obtenues avec plusieurs applications que nous avons testées sont prometteuses. Toutefois cette approche a ses limites, notamment à cause du modèle de programmation proposé, et il nous a été difficile d'implémenter un mécanisme permettant l'adaptation automatique de la granularité des noyaux de calculs.

L'approche de haut niveau basée sur la programmation fonctionnelle hérite de tous les travaux sur la manipulation de programmes dans le formalisme de Bird-Meertens en particulier et de ce point de vue est beaucoup plus prometteuse. Notre implémentation montre que les performances obtenues sont du même ordre que celle obtenues avec les supports exécutifs existants, avec l'avantage supplémentaire de permettre des optimisations à la compilation et à l'exécution.

Ces travaux ont donné lieu à différentes publications en conférence (RenPAR'20), en *work-shop* (FHPC'13) et dans un journal (TSI 31) ainsi qu'à un rapport de recherche Inria.

### Résumé en anglais

This work takes part in the context of high-performance computing on heterogeneous architectures. Runtime systems are increasingly used to make programming these architectures easier and to ensure performance portability by automatically dealing with some tasks (management of the distributed memory, scheduling of the computational kernels...). We propose a low-level approach based on the OpenCL specification as well as a high-level approach based on parallel functional programming.

Keywords: high-performance computing, heterogeneous architectures, runtime systems, OpenCL

Cette thèse a été préparée au sein du laboratoire Inria Bordeaux - Sud-Ouest dans l'équipe Runtime dirigée par le professeur Raymond Namyst.

(iv)

### Remerciements

Comme il est d'usage de remercier toutes les personnes qui ont compté sur la période de réalisation de cette thèse, en guise de prolégomènes j'aimerais faire des excuses anticipées à l'endroit de celles et ceux que j'aurais pu oublier. Je me rattraperai dans la prochaine.

Je dois à Yves Métivier de m'avoir suggéré de considérer poursuivre en thèse après l'obtention de mon diplôme d'ingénieur. Qu'il en soit remercié car, sans son conseil, je n'aurais pas trouvé ma voie (en tout cas pas tout de suite). Je remercie Raymond Namyst de m'avoir accueilli au sein de son équipe et de m'avoir trouvé un financement (public), ce qui relevait de la gageure. Je remercie mes deux encadrants, Denis Barthou et Alexandre Denis, pour le temps qu'ils m'ont consacré et pour leur soutien *in fine* à la piste de recherche que je souhaitais explorer – utilisant la programmation fonctionnelle – qui est pourtant perçue comme en opposition avec l'objectif de haute performance poursuivi. Enfin, je souhaite remercier chaleureusement les autres membres du jury, Jean-François Méhaut, François Bodin, Luc Giraud et Eric Petit, qui ont tous pris le temps de relire le manuscrit et m'en ont fait des retours constructifs.

Lors de ces quatre années au sein du laboratoire INRIA<sup>1</sup>, j'ai été amené à rencontrer et côtoyer de nombreuses personnes que j'aimerais ici remercier. Tout d'abord les membres permanents de l'équipe Runtime : Sylvie, Raymond, qui a toujours une histoire sympa à raconter, Pierre-André, Emmanuel, Samuel, Olivier, Nathalie, merci pour tes conseils pour ma soutenance, Marie-Christine, qui m'a incité à positiver un peu plus, Guillaume et Brice, qui devraient s'installer de façon permanente dans l'open-space des thésards à la fois pour l'animation et la température. Je tiens également à remercier les anciens doctorants de l'équipe qui m'ont passé le relais : Broq, Paulette, les "bip-bip café" se sont arrêtés avec ton départ, Jérôme, Cédric, Louis-Claude, Stéphanie, tu avais raison à propos de l'interpellation "Alors la rédaction ?".

De nombreux collègues sont devenus des amis : François, avec ses chatons, ses absences et ses nombreux liens NSFW, Bertrand, préparateur sportif, fan de mamies à vélo et jamais avare d'une contrepètrie, Paul-Antoine, notre référence en linguistique anglaise et française, pratiquant un sport de collégien sans en avoir honte (CO), Cyril, globe-trotter cinéphile, capable de faire Agen–Villeneuve-sur-Lot à pied dans la boue et de nuit et maître de la réalisation de scripts divers et variés, Andra, qui a enduré une équipe masculine de thésards à l'humour léger et qui n'est pas la dernière à proposer d'aller boire des bières, Sébastien, adepte de la crasse mitraillette et des fruits de mer et d'une discrétion de violette de façon générale. Courage à vous, si je l'ai fait, vous pouvez le faire !

La liste serait incomplète si j'oubliais Manu auprès duquel j'ai appris de nombreuses choses notamment sur l'engagement, la philo, etc. Merci pour tous les conseils et toutes les sorties également. Géraldine, qui est toujours de bon conseil (e.g. préparer sa soutenance bien en avance) et à qui je dois beaucoup, notamment qui m'a sauvé la mise pour l'organisation de mon pot de thèse et qui m'a encouragé et reboosté lorsque j'en avais besoin (sans parler de nos goûts musicaux communs :)). Aurélien, qui m'a fait découvrir Mano Solo et les joies de la randonnée dans les Encantats. Merci pour tous les conseils avisés également. Merci également à Abdou, Pascal, Mathieu, Damien et George pour toutes les restaurants, les barbecues et autres sorties. Merci à Ludo pour son soutien dans notre "croisade" contre l'obscurantisme impératif

<sup>&</sup>lt;sup>1</sup>Transformé depuis 2011 en Inria "Inventeurs du monde numérique" (cf "No Logo" de Naomi Klein sur le concept du *branding*)

et pour toutes les discussions intéressantes. Merci à François du SED pour sa bonne humeur et nos discussions. Enfin, merci à Antoine R., bon courage à Zurich, Corentin, Yannick, Cyril R., pour les discussions sur la place du travail dans la société et pour l'humour toujours fin et distingué, Yohan, pour la découverte de la gastronomie réunionnaise, Nicolas, Marc, Julie, et son obsession pour les chaussures, Astrid, la parachutiste, Laëtitia, Aude et Lola, pour leur bonne humeur, Andres, pour toutes nos discussions lorsqu'on partageait le même bureau et par la suite, Julien, Pierre, Allyx, la musique dans la peau...

En dehors du laboratoire, je souhaite remercier tous ceux qui ont rendu mon séjour bordelais et, plus globalement, ces quatre années, plus agréables. Matthieu, Philippe, Benoit, Mellie, Jérémie et Pierre, compagnons d'infortune de classe prépa et qui en sont restés de véritables amis. Simon & Cécilia, Claire, Stéfanie & Michel, Cédric & Marie, Rémi & Laure, Rémi & Frédérique, Benoit & Christelle, Cyril & Sarah, amis rencontrés à l'ENSEIRB. Le groupe du Bassin : Caroline, Nelly & Nicolas, Pauline, Clémentine, Laurie, Quentin, Antoine, Eric, François, Laëtitia, sans oublier Marlène. Tous ceux avec qui j'ai fait de la musique : Romain, Mathieu, François, Benjamin, Antoine, Xavier, David R., Myriam, David J., Alexandra, Stéphanie...Tous les camarades et amis Francisco, Anne, Bertrand, Brigitte L., Brigitte D., Marie-Claude, Maïa, Pierre, Édouard, Grégoire, Jean-Claude, Yves, Yannick...Beaucoup de souvenirs impérissables (congrès, etc.). Merci également à Irina, tu me dédicaceras ton livre ?, Alexandre, tu vois maintenant qu'on avait bien raison, Jeoffrey, courage pour la fin de ta thèse, Mélanie, Charlotte, Ophélie...

N'étant pas excessivement démonstratif d'ordinaire, je tiens à profiter de l'occasion pour remercier ma famille, mon frère et ma soeur et en particulier mes parents qui ont supporté que je passe une grande partie de mon adolescence à lire de nombreux livres de programmation et à passer un temps incommensurable à mettre en pratique, souvent jusqu'aux petites heures du matin, parfois au détriment d'autres activités, et qui m'ont apporté leur soutien indéfectible durant cette thèse comme toujours auparavant. J'en profite également pour les remercier d'avoir soutenu, encouragé et enduré ma deuxième passion, légèrement plus bruyante, à savoir la pratique de la batterie...

Enfin je remercie ceux qui sont une source d'inspiration et de motivation pour moi et qui ne doivent pas se trouver souvent cités, si jamais, dans les remerciements d'une thèse en informatique : Hiromi Uehara, Dave Weckl, Chick Corea, Simon Phillips, Vinnie Colaiuta, Sting, Jean-Luc Mélenchon, Jacques Généreux...

# **CONTENTS**

### Introduction

| Ι  | Tow  | vard Heterogeneous Architectures 5 |                                                     |    |

|----|------|------------------------------------|-----------------------------------------------------|----|

|    | I.1  | Introd                             | uction                                              | 6  |

|    | I.2  | Multi-                             | Core and Clusters Programming                       | 7  |

|    | I.3  | Hetero                             | ogeneous Architectures                              | 11 |

|    |      | I.3.1                              | Many-Core and Accelerators                          | 11 |

|    |      | I.3.2                              | Programming Many-Core                               | 13 |

|    |      | I.3.3                              | Programming Heterogeneous Architectures (Host Code) | 14 |

|    | I.4  | Gener                              | ic Approaches to Parallel Programming               | 23 |

|    |      | I.4.1                              | Parallel Functional Programming                     | 25 |

|    |      | I.4.2                              | Higher-Order Data Parallel Operators                | 26 |

|    |      | I.4.3                              | Bird-Meertens Formalism                             | 27 |

|    |      | I.4.4                              | Algorithmic Choice                                  | 28 |

|    | I.5  | Conclu                             | usion                                               | 28 |

| II | soc  | CL: Aut                            | omatic Scheduling Within OpenCL                     | 31 |

|    | II.1 | Introd                             | uction                                              | 32 |

|    | II.2 | Towar                              | d Automatic Multi-Device Support into OpenCL        | 32 |

|    |      | II.2.1                             | Unified OpenCL Platform                             | 33 |

|    |      | II.2.2                             | Automatic Device Memory Management                  | 34 |

|    |      | II.2.3                             | Automatic Scheduling                                | 35 |

|    |      | II.2.4                             | Automatic Granularity Adaptation                    | 36 |

|    | II.3 | Imple                              | mentation                                           | 39 |

1

|     | II.4   | Evalua  | ation                                                   | 41 |

|-----|--------|---------|---------------------------------------------------------|----|

|     |        | II.4.1  | Matrix Multiplication                                   | 41 |

|     |        | II.4.2  | Black-Scholes                                           | 42 |

|     |        | II.4.3  | Mandelbrot Set Image Generation                         | 44 |

|     |        | II.4.4  | LuxRender                                               | 46 |

|     |        | II.4.5  | N-body                                                  | 46 |

|     | II.5   | Conclu  | asion                                                   | 48 |

| III | Hete   | erogene | ous Parallel Functional Programming                     | 53 |

|     | III.1  | Introd  | uction                                                  | 54 |

|     |        | III.1.1 | Rationale                                               | 55 |

|     |        | III.1.2 | Related Works                                           | 56 |

|     |        | III.1.3 | Overview of the Involved Concepts                       | 57 |

|     | III.2  | Hetero  | ogeneous Parallel Functional Programming Model          | 58 |

|     |        | III.2.1 | Configuring an Execution                                | 58 |

|     |        | III.2.2 | Parallel Evaluation of Functional Coordination Programs | 59 |

|     | III.3  | ViperV  | /Μ                                                      | 73 |

|     |        | III.3.1 | Implementation                                          | 73 |

|     |        | III.3.2 | Evaluation                                              | 77 |

|     | III.4  | Conclu  | usion                                                   | 80 |

| Co  | onclus | sion an | d Perspectives                                          | 83 |

| Α   | Hasl   | kellPU  |                                                         | 87 |

| В   | Rew    | rite Ru | les                                                     | 91 |

| С   | Mat    | rix Add | lition Derivation                                       | 95 |

| D   | Mat    | rix Mul | tiplication Derivation                                  | 97 |

# INTRODUCTION

Scientific applications require a huge amount of computing resources. In particular, some applications such as simulations of real world phenomena can increase the precision of their results or widen the domain of their simulation so that they can use as many computing resources as can be made available. Hence high-performance computer architectures are consistently improved to sustain the computing needs.

During a substantial period of time, thanks to advances in miniaturization, architectures have been enhanced by increasing their clock speeds and by adding mechanisms to alleviate the slow-downs induced by the slowest components (typically memory units). With a minor impact on application codes, newer architectures were able to provide enhanced performance. However this process has come to an end because further improvements of the same nature would come at too much a price to pay, especially regarding power consumption and heat (the "Power wall"). Instead, the trend has become to conceive architectures composed of simpler and slower processing elements but concentrating a lot of them ("many-core" architectures). As these new architectures are not well-suited to execute common applications and operating system and because they would imply performance loss of the unparalelizable sequential parts of applications (cf Amdahl's law), they are often used as auxilliary accelerators. These architectures composed of a host multi-core and some many-core accelerators are called *heterogeneous* architectures and are the subject of the work presented here. In Top500 [1] and Green500 [2] supercomputer lists of June 2013, there are 4 architectures with accelerators (INTEL Xeon Phi, NVIDIA K20x...) in both top 10 and the remaining 6 architectures are mostly IBM BlueGene/Q which have followed the same trend.

Programming heterogeneous architectures is very hard because codes executed on accelerators (that we will refer to as *computational kernels* or *kernels* in the remainder of this document) are often intrinsically difficult to write because of the complexity of the accelerator architecture. In addition, writing the code to manage the accelerators (*host code* executed by the host multi-core) is very cumbersome, especially because each accelerator has its own constraints and capabilities. Host codes that use low-level frameworks for heterogeneous architectures have to explicitly manage allocations and releases in each memory as well as transfers between host memory and accelerator memories. Moreover, computational kernels must be explicitly compiled, loaded and executed on each device without any help from the operating system.

Runtime systems have been developed as substitutes for missing operating system features such as computational kernel scheduling on heterogeneous devices and automatic distributed

memory management. However, there has been no convergence to a standard for these runtime systems and only two specifications, namely OpenCL and OpenACC, are widely recognized despite them being very low-level (OpenCL) or of limited scope (OpenACC). As a consequence, we decided to use OpenCL specification as a basis to implement a runtime system (called SOCL and presented in Chapter II) that could be considered as a set of OpenCL extensions so that its acceptance factor is likely to be higher than other runtime systems providing their own interfaces. It provides automatic distributed device memory management and automatic kernel scheduling extensions as well as a preliminary support for granularity adaptation.

The programming model used by SOCL, thus inherited from OpenCL and based on a graph of asynchronous commands, makes the implementation of some optimizations such as automatic granularity adaptation very hard. This difficulty is shared with some other runtime systems that use a programming model based on graphs of tasks such as StarPU or StarSS. In particular, most of them lack a global-view of the task graph because the latter is dynamically built, hence inter-task transformations cannot be easily implemented as runtime systems cannot predict their impact on tasks that will be submitted later on. A solution is to use a more declarative language to build the task graph to let the runtime system analyze it so that transformations can be performed more easily. Frameworks such as DaGUE [28] use a dependency analysis applied to an imperative loop nest to infer task dependencies and store the task graph in a form more easily usable by the runtime system.

In Chapter III we present a solution alleviating parallel functional programming so that we do not need a dependency analysis nor an intermediate form to store task graphs. We show that this approach has a great potential because it is very close to both state-of-the-art programming paradigms used by runtime systems for heterogeneous architectures and highlevel functional programming languages. This convergence of two distinct research domains – programming languages and high-performance computing – is very inspiring. The specific characteristics of high-performance programs such as the lack of user interaction during the execution and the fact that they consist in transforming a (potentially huge) set of data into another set of data make them an ideal fit for functional programming.

In this last chapter, the work we describe is still in progress. We show that the solution we propose combines several previous works such as parallel functional programming, computational kernel generation from high-level data-parallel operators, transformation of functional programs as in the Bird-Meertens calculus, algorithmic choice... The automatic granularity adaptation method we propose uses several of these mechanisms and is based on heuristics that would need to be evaluated in real cases. Hence we need a complete implementation of a runtime system supporting our approach, which we did not have yet. Completing the implementation of this integrated environment is our next objective. One of the major design constraint we have established is to make it easily extendable to facilitate collaborations between people from different communities (scheduling, high-performance computing, programming language and type systems...) so that they could all use it as a playground to test their algorithms, as well as very easy to use for end users.

## **Outline and Contributions**

In Chapter I, the evolution of high-performance computing architectures toward heterogeneous ones and the frameworks used to program them are presented. Generic high-level approaches that are not tied to a specific kind of architecture are also considered.

**SOCL** Our first contribution is an OpenCL implementation called SOCL that is described in Chapter II. It provides a unified OpenCL platform that fix many shortcomings of the OpenCL implementation multiplexer (the installable client driver) so that it is beneficial even for applications directly using the low-level OpenCL API. In addition, it offers automatic device memory management so that buffers are automatically evicted from device memory to host memory to make room in device memory if necessary. It also extends OpenCL contexts so that they become scheduling contexts into which kernels can be automatically scheduled by the runtime system. Finally, preliminary support for automatic granularity adaptation is included.

**Heterogeneous Parallel Functional Programming** Our second contribution, presented in Chapter III is a programming model for heterogeneous architectures. By combining the high-level parallel functional programming approach and low-level high-performance computational kernels, it paves the way to new algorithms and methods, especially to let runtime systems automatically perform granularity adaptation. ViperVM, a preliminary implementation of this programming model is also presented.

(3)

I find digital computers of the present day to be very complicated and rather poorly defined. As a result, it is usually impractical to reason logically about their behaviour. Sometimes, the only way of finding out what they will do is by experiment. Such experiments are certainly not mathematics. Unfortunately, they are not even science, because it is impossible to generalise from their results or to publish them for the benefit of other scientists.

C. A. R. Hoare

Although Fortress is originally designed as an object-oriented framework in which to build an array-style scientific programming language, [...] as we've experimented with it and tried to get the parallelism going we found ourselves pushed more and more in the direction of using immutable data structures and a functional style of programming. [...] If I'd known seven years ago what I know now, I would have started with Haskell and pushed it a tenth of the way toward Fortran instead of starting with Fortran and pushing it nine tenths of the way toward Haskell.

Guy Steele, Strange Loop 2010 Keynote

# CHAPTER I

# TOWARD HETEROGENEOUS ARCHITECTURES

| I.1 | Introd | uction                                              |

|-----|--------|-----------------------------------------------------|

| I.2 | Multi- | Core and Clusters Programming                       |

| I.3 | Hetero | ogeneous Architectures                              |

|     | I.3.1  | Many-Core and Accelerators                          |

|     | I.3.2  | Programming Many-Core                               |

|     | I.3.3  | Programming Heterogeneous Architectures (Host Code) |

| I.4 | Gener  | ic Approaches to Parallel Programming               |

|     | I.4.1  | Parallel Functional Programming                     |

|     | I.4.2  | Higher-Order Data Parallel Operators                |

|     | I.4.3  | Bird-Meertens Formalism                             |

|     | I.4.4  | Algorithmic Choice                                  |

| I.5 | Conclu | usion                                               |

## **Chapter abstract**

In this chapter, we present the evolution of high-performance architectures towards heterogeneous ones that have become widespread in the last decade. We show how imperative programming approaches that are based on the Von Neumann architecture model have been adapted to deal with the new challenges introduced by each kind of architecture. Finally, we present models and languages that drop the lineage with the Von Neumann model and propose more radical approaches, considering the root of some of the issue is the use of this model. A comprehensive description of the architecture evolution is out of the scope

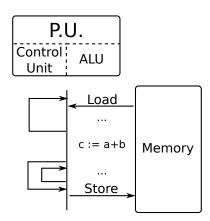

Figure I.1: Von Neumann architecture model

of this document. Here we mainly stress on the breakthroughs that have led to the current situation and the foreseen future of which heterogeneous architectures are very likely to be part of.

## I.1 Introduction

Thanks to miniaturization, the number of transistors that can be stored initially on integrated circuits and later on microprocessors keeps increasing. This fact is commonly referred to as Moore's law. Indeed, in 1965 Gordon Moore has conjectured that the number of transistors would double approximately every two years and this conjecture has been empirically verified. As a consequence, architectures have evolved in order to advantage of these new transistors.

The architecture model that has prevailed and that is at the root of most programming languages still in use today (e.g. imperative languages) is referred to as the Von Neumann model. Architectures based on this model are composed of two main units as shown in Figure I.1: a memory unit and a processing unit. In this basic model, instructions are executed in sequence and can be of the following types: memory access (load or store), arithmetic operation, control instruction (i.e. branches). Actual architectures are of course more complex than the Von Neumann model. Memory hierarchies have been introduced to speed-up memory accesses. Multicore architectures contain tens of processing units and several memory units. Processing units themselves contain more execution units (SIMD units, floating-point units...), execute instructions in parallel and at much higher clock frequencies. Finally, clusters interconnect thousands of these architectures together through high-performance networks.

The complexity of these architectures has been pushed as far as possible to enhance performance without having to change programs much until the *power-wall* has been faced: energy consumption and temperature rise have become too high to continue this way. The alternative direction that has been taken instead consisted in conceiving architectures containing a very large amount of comparatively simple processing units with a very low power consumption. This way, the degree of parallelism has been increased to thousands of simultaneous instruction executions inside a single processor, hence these architectures are often referred to as *many-core* architectures. The price to pay for this architecture design shift has been the necessity to write specific codes able to take advantage of so many threads.

Most many-core architectures are not designed to handle tasks such as user interaction or controller management (disks, etc.). Hence, many-core architectures are often used on devices used as accelerators and interconnected with a multi-core that is able to perform the aforementioned tasks. Heterogeneous architectures are these architectures composed of a multi-core alongside an arbitrary number of accelerators of different kinds. The main topic of this document is the programming of these heterogeneous architectures, not of a specific one in particular but the coordination of codes executed on accelerators and on the host as well as memory management.

### I.2 Multi-Core and Clusters Programming

Programming languages, frameworks and runtime systems used for high-performance computing are often very close to the underlying architecture in the sense that they do not offer much abstraction and give full control to hardware provided mechanisms. As such programming multi-core architectures for high-performance computing is usually done by explicitly instantiating several threads that are executed independently by each processing unit. Clusters are similarly exploited by explicitly spawning at least one process per node.

Some level of abstraction is necessary to enhance code portability, productivity, etc. but the introduced abstraction mechanisms must not have a high perceptible impact on performance. As such, we can say that the rather low-level approaches presented in this section are conceived from the bottom-up (abstractions are added carefully) while in Section I.4, we present approaches conceived from the top-down (starting from a high-level of abstraction, we want to produce codes that match the underlying architecture as best as possible).

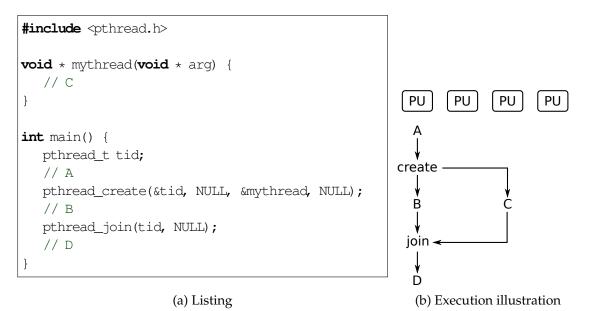

Threading APIs such as POSIX thread (PThread) API [53] are the most basic way for an application to exploit multi-core architectures. It lets applications start the execution of a function in a new thread. Both the current thread and the newly created one share global variables while local variables (typically allocated on the stack) are private to each thread. Listing I.2a shows a example of code using POSIX threads whose execution is depicted in Figure I.2b. Synchronization primitives are provided in order to let a thread wait for another one in particular (join), to create mutually exclusive regions that only one thread can execute at a time (mutex), etc.

Another thread API example is Cilk [126] that lets programmers execute C functions by different threads just by prefixing function calls with the spawn keyword. A work-stealing policy is then used to perform load-balancing on the different processing units [26]. A Cilk procedure, prefixed with the keyword cilk, can spawn other Cilk procedures and wait for their completion with the sync keyword.

Low-level thread APIs are quite burdensome to use, especially for programs that regularily create parallel regions (i.e. regions of code simultaneously executed by several threads). OpenMP [14] is a framework that is used to easily manage this kind of regions in C or Fortran codes. Compiler annotations are used to indicate to delimit regions that are then executed in parallel by a specified number of threads. Listing I.3a shows an example of a C code using OpenMP to create a parallel region executed by 5 threads as depicted in Figure I.3b. OpenMP provides synchronization primitives such as barriers to force all threads of a parallel region to

7

Figure I.2: POSIX Thread API example. The thread created by pthread\_create executes code labelled as C in parallel with the code labelled as B executed by the main thread.

wait all of the others before continuing their execution.

As it often happens that applications have to distribute loop iterations over a pool of threads, OpenMP provide specific annotations to transform a for loop into a forall loop. The latter indicates to the compiler and runtime system that each loop iteration can be executed in parallel. In this case, the loop iterator is used to identify which loop iteration is being executed. OpenMP loop annotations can be used on loop nests producing nested parallelism: a tree of parallel threads. OpenMP implementations such as ForestGomp [32] exploit this nested parallelism to automatically enhance thread mapping on NUMA architectures.

In order for applications to use more computational power and to be able to exploit bigger data sets, processors have been interconnected to form clusters. As such, an application can simultaneously uses thousands of processing units and memory units. There are numerous networking technologies such as Infiniband, Quadrics, Myrinet or Ethernet. Usually, applications do not use the low-level programming interface provided by these technologies but use higher level programming models.

Message Passing Interface (MPI) is a standardized interface that mainly allows applications to use synchronous message-passing communication. Basically, one process is executed on each node of the cluster and a unique identifier is given to each of them. Processes can exchange data by sending messages to other processes using these identifiers. The communication is said to be synchronous because messages are transmitted through the network only when both the sender and the receivers are ready. As such, messages are transferred directly to their final destination, avoiding most superfluous data copy that would be involved if the data transfer started before the receiver had indicated where the data was to be stored eventually. MPI provides synchronization primitives between processes [58].

MPI uses a mapping file to indicate where (i.e. onto which workstation) each MPI process is to be executed. MPI implementations are responsible for the correct and efficient transport

```

#include <omp.h>

int main() {

// A

#pragma omp parallel num_threads(5)

{

Δ

int id = omp_get_thread_num();

printf("My_id: %d\n", id); // B

id=2

↓id=0

id=4

id=1

id=3

В

В

B

В

}

В

// C

}

С

(a) Listing

(b) Execution illustration

```

Figure I.3: OpenMP parallel region example. Each thread of the parallel region has a different value of id

of the messages. The network topology is not exposed to applications and the implementation has to optimize the path followed by messages through the network. This is especially true for collective operations such as reductions or broadcasts which involve several nodes.

Using a synchronous message-passing model can be hard because it is easy for a programmer to introduce bugs such as a process stalled on a send operation because of a receiving process that is never ready to receive. The actor model is an alternative that allows asynchronous message-passing between processes. Basically, an actor is a process or a thread to which a message box is associated. Actors can post messages into message boxes of other actors and consult their own message boxes when they want. Charm++ uses asynchronous message passing between active objects called *chares*. Remote communication is possible by using proxy chares originally called *branch-office chares* (BOC) [84]. Erlang programming language [15] is also based on the actor model and has influenced several newer languages such as Scala that provides an actor library using a syntax borrowed from Erlang [72]. The actor model can be more amenable to implement functionalities such as fault tolerance or load-balancing. An actor can be moved from a node to another by copying its private data comprising its message box. Charm++ uses a default mapping if there is no user-provided one and then uses dynamic load-balancing strategies to move *chares* from one processing unit to another [138].

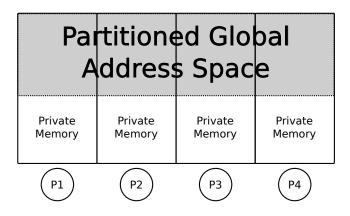

*Partitioned Global Address Space* (PGAS) is a shared memory model where each thread owns a portion of a virtually shared memory in addition to its private memory as shown in Figure I.4. Threads can access the following memories sorted by affinity: locale private memory, locale shared memory and remote shared memories. Many languages implement this model. On the one hand, some of them extend existing languages such as Unified Parallel C (UPC) [45] which is based on C, Co-Array Fortran (CAF) [109] and High-Performance Fortran (HPF) [57] which are based on Fortran, Titanium which is based on Java [77] and XcalableMP [106] which provides compiler annotations for C and Fortran. On the other hand, some of them are new languages dedicated to the model such as x10 [119] which is mostly influenced by Java though or ZPL and its successor Chapel [40].

Some frameworks use a global view instead of the local view typically used in SPMD model

Figure I.4: Partitioned Global Address Space (PGAS) memory model

where each thread does something different depending on its unique identifier. With the global view model of programming, programs are written as if a single thread was performing the computation and it is the data distribution that indicates how the parallelization is done. HPF [57] is a language based on Fortran (Fortran 90 for HPF 1.0 and Fortran 95 for HPF 2.0) that uses the global view model. It provides directives to specify data mapping on "processors" (DISTRIBUTE and ALIGN). Similarily, ZPL [39, 93] and its successor Chapel [40] are languages that use imperative data-parallel operators on arrays. Array domains (or *regions*) are first class citizens in these languages. For two arrays defined on the same domain, the runtime system only ensures that two values having the same index in the two arrays are stored in the same physical memory but the domain can be distributed among any number of cluster nodes.

Virtual address space model consists in partitioning a single address space in pages that can be physically transferred from one memory to another without modifying the virtual address space. Compared to the PGAS model, memory accesses are always performed locally but may imply preliminary page transfers. Similarly, *Single System Image* (SSI) model consists in letting a distributed operating system distribute processes and data using a virtual address space on a distributed architecture. Kerrighed, openMOSIX, OpenSSI and Plurix [59, 96] are examples of such operating systems. A mix between the virtual address space model and the PGAS model is used on NUMA architectures (cf Section I.2) that can be seen as a cluster on a chip. Basically, memory accesses in remote memories can be performed as in the PGAS model but libraries such as libnuma or hwloc [33] can be used to move a page from one NUMA node to the other.

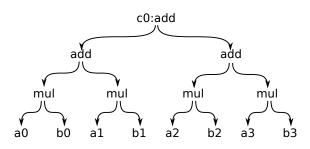

*Shared objects* model can be seen as a kind of virtual address space model with different page granularities. Data (objects) are allocated in the virtual address space and an object handle is associated with each of them. Threads must use these handles to be allowed to accede to the object contents in a specific mode (read-only, write-only or read-write mode). Data may be copied into a local memory before a thread uses it and coherency is automatically maintained by a runtime system. Note that an object handle is not necessarily an address. For instance it can be an opaque object or an integer. Compared to single address space and virtual address space models, pointer arithmetic cannot be used to arbitrarily read or write memory and object handles must be used instead. Jade [115, 116] uses the shared objects model. *Local pointers* are used to temporarily get access to shared objects using a specified access mode enforced by the system. Jade targets shared memory and distributed memory architectures.

(10)

Similarly, StarPU [16, 17] also uses the shared objects model on heterogeneous architectures (cf Section I.3). Tasks are explicitly created with shared objects as parameters and task-specific access modes. Data are transferred on appropriate devices before task execution.

One of the main difficulty faced by programmers using clusters is to correctly map processes of an application to the network topology. Given a trace of the communications between processes and a description of the network topology, algorithms such as TreeMatch [83] produces an efficient mapping of processes to cluster nodes.

Because using low-level programming models for parallel computing is hard, some models and languages have introduced high-level concepts to enhance productivity. For instance, MapReduce is a model of framework which has roots in the Bird-Meertens Formalism (cf Section I.4.3) and that has been successfully applied to compute on clusters. If a computation follows a given pattern, programmers only have to give some functions to the framework and the input collection of data. The framework automatically distributes tasks on cluster nodes, performs load-balancing and may even support fault tolerance. Examples of such frameworks are Google MapReduce [50] and Hadoop [134]. Another example is Fortress [125] which has been designed to be the successor to Fortran and is mostly inspired by Java, Scala and Haskell languages. It has been conceived alongside x10 [119] and Chapel [40] for the DARPA's "High Productivity Computing System" project [98] initiated in 2002.

It is not uncommon to use several frameworks at the same time. For instance, OpenMP for intra-node parallelism using shared memory and MPI for inter-node communications using messages. In Section I.3.3, we show that by adding accelerators to some of the nodes, it is often necessary to use an additional framework such as OpenCL or CUDA or to substitute on of the framework used with another supporting heterogeneous architectures.

### I.3 Heterogeneous Architectures

Programming languages, frameworks and runtime systems presented in the previous section had to be adapted to support heterogeneous architectures. In addition, newer approaches dedicated to these kinds of architectures have been developed. In this section we present several accelerators, then we show how to exploit them. We distinguish codes that are executed on the accelerators and the host code executed on a commodity multi-core and used to manage them.

### I.3.1 Many-Core and Accelerators

Many-core architecture is a term coined to refer to the trend of increasing the number of cores up to tens, hundreds or even thousands of cores, in particular by simplifying the core that is duplicated. Indeed, by removing units used to speed up the basic Von Neumann architecture such as out-of-order execution management unit (Cell, ATOM, Xeon Phi...), virtual memory management unit (Cell's SPE, GPUs...), cache management units (Cell's SPE, GPUs...) and by decreasing the frequency, the number of cores that can be stored on a chip can be increased significantly. These many-core architectures often present themselves as accelerators that can be used in conjunction with a classic multi-core architecture. This heterogeneity is dealt with in the next section.

(11)

The Cell BroadBand Engine architecture (known as Cell BE or Cell) was among the first widespread heterogeneous architectures prefiguring the many-core trend. Conceived by Sony, Toshiba and IBM, it featured a modest Power4 multi-core called Power Processing Element (PPE) that was slower than the best architectures at the time such as the Power6. In addition, 8 cores called Synergistic Processing Elements (SPE) have been introduced on the chip and connected to the PPE and the memory unit through a fast ring network called *Element Interconnect Bus* (EIB) [6]. Each SPE has its own 256KB scratchpad memory called Local Store (LS) and an associated DMA unit to transfer data between the different LS and the main memory. The major difference of this architecture compared to previous multi-core architectures is that it requires explicit management of the SPE. Programs executed on SPE have to be compiled with a dedicated compiler and explicitly loaded at runtime by an host application executed by the PPE. Due to the limited amount of memory available on local stores, programs have to be relatively small prefiguring computational kernels used on subsequent accelerators such as GPUs. In addition, local stores do not use virtual memory units and are explicitly managed using direct addressing. DMA units have to be explicitly configured to transfer data from one memory unit to another. For the first time, a widespread architecture was not using a shared memory model (be it NUMA). Most of the forthcoming many-core architectures followed this road too.

Graphics processing units (GPU) are specialized chips that speed up graphic rendering by performing embarrassingly parallel computations such as per vertex or per pixel ones in parallel. They have been made increasingly programmable to the point that are used to perform generic scientific computing, not only graphic rendering. In the early days, only a few levels of the graphic pipeline were programmable using shaders through graphics API such as OpenGL's GLSL, Microsoft's HLSL and NVIDIA's Cg [101]. Now most details of their architecture are exposed through API no longer dedicated to graphics such as CUDA and OpenCL. NVIDIA GPU architectures are composed of several processing units called Streaming Multi-Processors (SM) and a single main memory. Each SM has its own scratchpad memory called *shared memory* as it is shared amongst every execution unit contained in the SM. Fermi and Kepler architectures introduced a L2 cache memory. Moreover they allow part of the shared memory to be configured as a L1 cache while the other part is still used as a scratchpad. Streaming multiprocessors contain bundles of execution units which have the same size. Every execution unit of a bundle executes the same instruction at the same time but on different data. Similarly, AMD GPU architectures are composed of several SIMD computation engines that differ from streaming multi-processors mostly because they contain several thread processors (TP) that are VLIW processors [137]. The memory hierarchy is very similar though. Using accelerators such as GPUs is hard, not only because of their intrinsic complexity but because programs have to explicitly manage data transfers between main memory and accelerator memories. Architectures embedding a CPU and a GPU on the same package have been introduced. For instance, AMD Fusion accelerated processing units (APU) such as Bulldozer or Llano use a unified north bridge to interconnect a CPU core and a GPU core.

Intel's answer to the rise of high performance computing using GPUs has been to provide accelerators based on x86 ISA. It started with the *Single-chip Cloud Computer* (SCC) prototype, a Cluster-on-Chip architecture composed of 48 cores (24 dual-core processing units). Each core executes its own instance of the Linux operating system and the main memory is split so that each core has its own private region in it. A part of the main memory is shared between all the cores but the hardware does not ensure any cache coherency. Each core has a 8kB on-die shared-memory called *Message-Passing Buffer* (MPB) that can be used to implement software

cache coherence policies. Frameworks based on message-passing such as MPI can be used to program the SCC as if it was a cluster [43]. Intel *Many Integrated Core* (MIC) [46], branded as Xeon Phi, is the successor of the Larrabee prototype and is a full-fledged accelerator. It contains up to 61 cores interconnected to 8 memory controllers through a high performance bidirectional ring network. Contrary to the SCC, cache coherence is ensured on the MIC through a distributed tag directory.

Accelerators tend to share many properties with low power consumption architectures such as those used in embedded devices to the point that there is a convergence and that the same system-on-a-chip architectures can be used both for high performance computing and embedded uses (video, networking, etc.). Tilera's TILE-Gx [3] architecture can be composed of up to 72 cores interconnected through a proprietary on-chip network called *iMesh*. Kalray's MPPA 256 [4] chip contains 256 VLIW cores – 16 clusters of 16 cores – interconnected with a network-on-chip (NoC). Platform 2012 (P2012) [103], now known as STHorm, is another example of a SoC using a NoC to interconnect cores.

### I.3.2 Programming Many-Core

Existing frameworks for multi-core architectures and for clusters cannot be used directly on many-core architectures such as GPUs or Cell BE. The complex memory hierarchy dismisses most frameworks for shared-memory architectures. In addition, constraints on IOs (memory allocation, etc.) and memory sizes make models such as MPI unsuitable. An exception to this is Intel Xeon Phi that can be programmed with MPI because its architecture is closer to multi-core than to a GPU.

Many-core architecture vendors often provide proprietary frameworks: IBM's Cell SDK [81], NVidia's CUDA [110], ATI's Stream SDK [11]...In addition, some frameworks that may use more abstract models target several architectures. Among the different frameworks and models, OpenCL and OpenACC are two specifications that have been endorsed by a large panel of vendors.

OpenCL [69] inherits from NVidia's CUDA and thus is especially suitable for GPU computing as the programming model matches closely the architecture model. CUDA and OpenCL let programmers write computing kernels by using an SPMD programming model similar to the one used in OpenMP. Independent groups of threads (work-groups of work-items in OpenCL) are executed in parallel. Threads of a group have access to a shared memory and can be synchronized by explicitly using barriers in the kernel code. No synchronization can occur between threads of different groups but all threads of every group have access to the same global memory<sup>1</sup>. Threads perform explicit transfers between global memory and their shared memory. Listing I.1 shows a simple matrix addition kernel written using OpenCL C language. Thread identifiers are obtained with the get\_global\_id built-in function. Shared memory is not used in this example.

OpenACC [71] specification defines a set of compiler annotations (*pragmas*) for C and Fortran programs similar to those of OpenMP. Instead of explicitly writing a kernel by using a SPMD model, these annotations let programmers indicate which loop nests should be converted into equivalent kernels. Hints can be given by the programmers to enhance the gener-

<sup>&</sup>lt;sup>1</sup>Some OpenCL implementations allows synchronizations between groups by providing atomic operations in global memory (see OpenCL base and extended atomics extensions).

- Heterogeneous Architectures

Listing I.1: OpenCL Matrix Addition kernel

ation of the kernels. OpenHMPP [36] is a superset of the OpenACC pragmas that influenced the OpenACC specification. Additional pragmas are used to target architectures containing several accelerators. Similarly to OpenACC and OpenHMPP, Par4All [12] is a compiler for sequential C and Fortran programs that uses polyhedral analysis on loop nests and source-to-source transformations to target other frameworks for multi-core and many-core architectures such as OpenMP, OpenCL and CUDA.

Brook [34] is an extension to C language dedicated to streaming processors which have been adapted to use GPUs as streaming co-processors. AMD's Stream SDK [11] is based on Brook. Streams of data (i.e. collections) can be defined and kernels can operate on them element-wise or reductions can be applied. Listing I.2 shows a matrix-vector multiplication y = Ax written with Brook. Streams are created by using the syntax <d0, d1...> after a variable declaration to indicate the dimensions of the stream. x is automatically duplicated to match the size of A in order to perform mul kernel element-wise with results stored in T. Then T is reduced by using the sum kernel in the second dimension so that the result can be stored in y.

### I.3.3 Programming Heterogeneous Architectures (Host Code)

Different programming models can be used to coordinate the execution of the computational kernels on the accelerators. The difficulty lies in the huge variety of heterogeneous architectures that can be encountered and that have to be supported by an application. Indeed it is common to have an architecture with several accelerators, potentially from different vendors connected to a host multi-core architecture. Each accelerator can contain a variable amount of memory, capabilities (e.g. available execution units, degree of parallelism...) may vary between the different devices and transfer bandwidths and latencies may be different between host memory and accelerator memories. A major advantage of using heterogeneous architectures is that a device with a small degree of parallelism and executed at a high frequency can be used in conjunction with massively parallel devices. The former executes the operating system

```

Listing I.2: Matrix-Vector Multiplication y = Ax written with Brook

```

```

kernel void mul (float a<>, float b<>, out float c<>) {

c = a * b;

}

reduce void sum (float a<>, reduce float r<>) {

r += a;

}

float A<50,50>;

float x<1,50>;

float T<50,50>;

float y<50,1>;

mul(A,x,T);

sum(T,y);

```

and intrinsically sequential parts of applications while the latter are used to offload computationally intensive kernels. However this has to be handled either directly by the application in its host program or by the framework that manages the accelerators.

Using an heterogeneous architecture means having to handle different programs for different kinds of processing units. It has a major impact on the compilation chain typically used for homogeneous architectures: several programs or kernels may have to be written, several compilers may have to be used and compilations may have to be performed at execution time to ensure portability. For instance, OpenCL specification defines an API to handle kernel compilation at execution time for OpenCL compliant devices [69]. Additionally, an intermediate representation for OpenCL kernels is being specified [70] in order to make runtime compilations more efficient as some optimizations could be performed before execution time. Program loading on homogeneous architectures are transparently handled by the operating system but it is no longer the case with some heterogeneous architectures, especially those where devices have very few kilobytes of memory such as the Cell. Programs may have to be explicitly loaded into device memory and are subject to out-of-memory errors. Program loading techniques such as *code overlay* may have to be used.

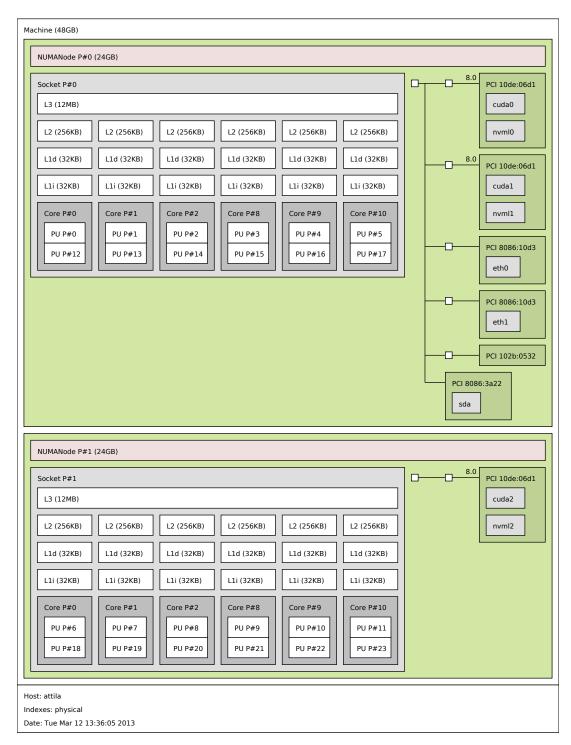

The first step for a typical application to exploit an heterogeneous architecture is to discover the available accelerators and the way they are connected to the host. hwloc [33] is a generic tool that can be used by applications to gather information about an architecture: memory hierarchy, NUMA sockets, physical and logical cores, connected devices... For instance, Figure I.5 is obtained on a NUMA architecture with three NVIDIA GPUs. Each NUMA socket contains 6 cores (i.e. processing units) that use SMT so that there are two logical processing units for a physical one. Two GPUs are connected to the first socket and the other is connected to the other. Main memory is split in two parts of 24GB each. GPU memory capacity is not shown on this representation. Other frameworks for heterogeneous architectures such as OpenCL can retrieve the list of available accelerators.

DMA transfers between memory units can be affected by the topology of the interconnec-

Figure I.5: NUMA architecture with three GPUs. The host is a multi-core with 12 dual-threaded cores (6 cores per NUMA socket). Two GPUs are connected to the first socket and the third is connected to the second socket, hence NUIOA factors are likely to be observed.

(16)

Figure I.6: Offload Model

tion network similarly to NUMA architectures. As DMA are often used to perform IO (hard disk controllers, network interface controllers...), it is called *Non-Uniform Input-Output Access* (NUIOA). In Figure I.5, network interface controllers are connected to the first socket, thus NUIOA effects are likely to be observable. Some architectures contain additional units to enhance transfers between devices. INTEL QuickData Technology [133] – part of INTEL I/O Acceleration Technology (I/OAT) – adds a DMA unit that can be used to perform DMA transfers between network interface controllers (NIC) and memory units as well as between memory units (for instance from one in a given NUMA socket to another). INTEL Direct Cache Access (DCA) technology allows controllers such as NICs to explicitly preload data into caches to speed up processing unit accesses to these data that are supposed to quickly follow. [78]

If the configuration of the platform (i.e. number and kind of devices) is known at compilation time, it is possible to statically assign codes that executed by an accelerator and codes executed by the host multi-core. For instance, Sequoia [54] is an extension for C language that has been mostly used to program the Cell. It lets programmers define functions that perform computations (*leaf tasks*) and functions that structure parallelism (*inner tasks*). For each target architecture, a mapping file is used to indicate the kind of task (leaf or inner) that will be executed by processing units corresponding to each level of the memory hierarchy.

An alternative to the static mapping of tasks on devices is to use a runtime system to dynamically schedule them. We distinguish three methods to schedule kernels executions on accelerators and data transfers between host memory and accelerator memories: offload, command graph and task graph.

```

Listing I.3: HMPP Basic Usage Example

```

```

#pragma hmpp foo codelet, target=CUDA, args[a].io=inout

void foo(int a[10], const int b[10]) {

...

}

int A[10], B[10];

int main(void) {

for (int j = 0; j < 2; ++j) {

#pragma hmpp foo callsite

foo(A, B);

}

return 0;

}</pre>

```

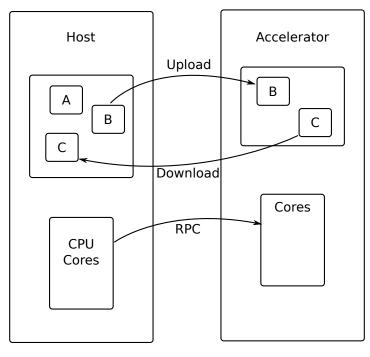

### I.3.3.1 Offloading Model

The offloading model is the one used by OpenACC and OpenHMPP. It basically supposes that a single accelerator is used, thus the memory model can be much simpler. Figure I.6 shows the memory model that is used where data can be uploaded on the accelerator and then downloaded in host memory. At some points in the host program, computations are offloaded on the accelerator, similarly to remote procedure calls (RPC). The execution can either be synchronous or asynchronous. Input data are transfered in accelerator memory before kernel execution if necessary and output data are transfered back in host memory after kernel execution if required. Listing I.3 presents an host code using HMPP to offload the function foo on a GPU supporting CUDA.

An issue with this model is that data transfers do not overlap with host code or kernel executions. Explicit data transfer commands or prefetch hints have to be used to get best performance. HMPP provides advancedload and delegatedstore annotations to trigger an upload data transfer in advance and to postpone a download data transfer respectively. Extensions to this model are provided to support multiple devices. HMPP lets applications choose onto which devices allocations have to be made and kernels are executed by devices that own the data. However, for a full low-level support of architectures with multiple accelerators it is often better to resort to frameworks such as OpenCL.

### I.3.3.2 Command Graph Based Frameworks

The offload approach works well when only a single accelerator is used and when precise control of the data transfers is not required. Otherwise, it is often better to use another approach that gives full control of the devices (memory management, kernel management, data transfer management, etc.) to the application such as the command graph approach. With this approach, applications dynamically build a graph of commands that are executed asynchronously by the different devices in parallel. The edges in the command graph indicate dependencies between them so that a command is executed only when all of its dependencies

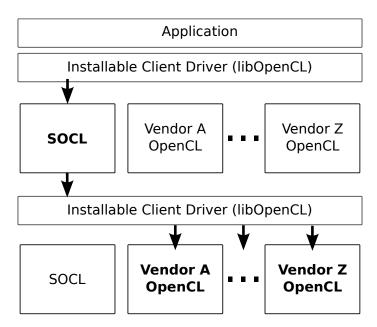

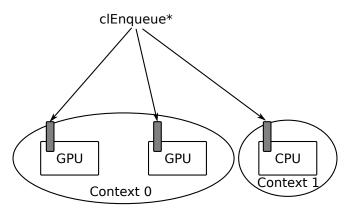

have completed. OpenCL [69] specification implements the command graph model. It defines a programming interface (API) for the *host* to submit commands to one or several *computing devices*. Several OpenCL devices from different vendors can be available on a given architecture. Each vendor provides an implementation of the OpenCL specification, called a *platform*, to support its devices. The mechanism used to expose all platforms available for an application is called the Installable Client Driver (ICD). From the ICD and the platforms, the applications can retrieve platform information, in particular the list of available devices for this platform.

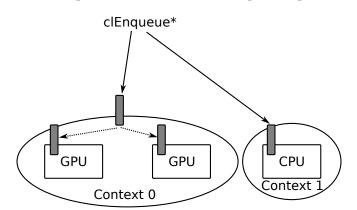

Devices that need to be synchronized, to share or exchange data can be grouped into *context* entities. *Only devices from the same platform can belong to the same context*. The data buffers required for the execution of computing kernels are created and associated with a context, and are lazily allocated to a device memory when needed. *Commands* are executed by computing devices and are of three different types: kernel execution, memory transfer and synchronization. These commands can be submitted to *command queues*. *Each command queue can only be associated with a single device*. Commands are issues in-order or out-of-order, depending on the queue type. Barriers can be submitted to out-of-order command queues to enforce some ordering. Synchronization between commands submitted to queues associated with different devices is possible using *event* entities *as long as command queues belong to the same context*. Events give applications a finer control of the dependencies between commands. As such they subsume command queue ordering and barriers. Each command can be associated with an event, raised when then command completes. The dependences between commands can be defined through the list of events that a command is waiting for. Listing I.4 shows a basic OpenCL host code to execute a kernel on the first available OpenCL device.

The OpenCL ICD is badly designed in that it does not allow devices of different platforms to be easily synchronized. Moreover the OpenCL API is a very low-level one and many extensions have been conceived to make it easier to use, for instance by providing a more unified platform, automatic kernel scheduling, automatic kernel partitioning...

IBM's OpenCL Common Runtime [80] provides a unified OpenCL platform consisting of all devices provided by other available implementations. Multicoreware's GMAC (Global Memory for Accelerator) [105] allows OpenCL applications to use a single address space for both GPU and CPU kernels. Used with TM (Task Manager), it also supports automatic kernel scheduling on heterogeneous architectures using a custom programming interface. Kim et al. [89] proposes an OpenCL framework that considers all available GPUs as a single GPU. Their framework expresses code for a single GPU and partitions the work-groups among the different devices, so that all devices have the same amount of work. Their approach does not handle heterogeneity among GPUs, not a hybrid architecture with CPUs and GPUs, and the workload distribution is static. Besides, data dependences between tasks are not considered since work-groups are all independent. De La Lama et al.[91] propose a compound OpenCL device in order to statically divide the work of one kernel among the different devices. Maestro[124] is a unifying framework for OpenCL, providing scheduling strategies to hide communication latencies with computation. Maestro proposes one unifying device for heterogeneous hardware. Automatic load balance is achieved thanks to an auto-tuned performance model, obtained through benchmarking at install-time. This mechanism also helps to adapt the size of the data chunks given as parameters to kernels.

Mechanisms for automatic scheduling and load-balancing of the OpenCL kernels on multidevices architectures have been investigated. A static approach to load partitioning and schedul-

Listing I.4: OpenCL host code example

```

// List platforms and devices

clGetPlatformIDs(..., &platforms);

clGetDeviceIDs(platforms[0], ..., &devices);

// Create a context for devices of the first platform

context = clCreateContext(devices, ...);

// Load and build a kernel

program = clCreateProgramWithSource(...);

clBuildProgram(program, ...);

kernel = clCreateKernel(program, ...);

// Create a command queue on the first device

queue = clCreateCommandQueue(context, devices[0], ...);

// Allocate buffers

b1 = clCreateBuffer(context, ...);

b2 = clCreateBuffer(context, ...);

// Initialize the input buffer "b1"

clEnqueueWriteBuffer(queue, b1, ..., &inputData, ...);

// Configure and execute the kernel

clSetKernelArg(kernel, 0, ..., b1);

clSetKernelArg(kernel, 1, ..., b2);

clEnqueueNDRangeKernel(queue, kernel, ...);

// Retrieve result from output buffer "b2"

clEnqueueReadBuffer(queue, b2, ..., &outputData, ...);

// Wait for the completion of asynchronous commands:

// write buffer, kernel execution and read buffer

clFinish(queue);

// Release entities

clReleaseBuffer(b1);

clReleaseBuffer(b2);

clReleaseKernel(kernel);

clReleaseProgram(program);

```

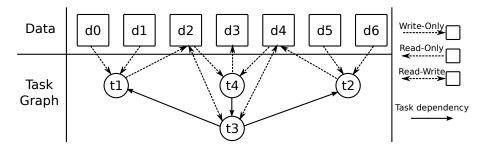

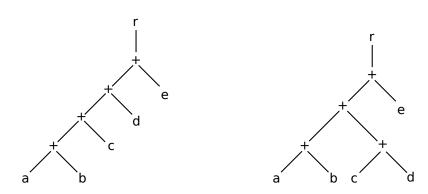

Figure I.7: Example of task-graph

ing is presented by Grewe and O'Boyle [67]. At runtime, the decision to schedule the code on CPU or GPU uses a predictive model, based on decision trees built at compile time from microbenchmarks. However, the case of multiple GPU is not directly handled, and the decision to schedule a code to a device does not take into account memory affinity considerations. Besides, some recent works use OpenCL as the target language for other high-level languages (for instance, CAPS HMPP [52] and PGI [136]). Grewe *et al.* [68] propose to use OpenMP parallel programs to program heterogeneous CPU/GPU architectures, based on their previous work on static predictive model. Boyer *et al.* [29] propose a dynamic load balancing approach, based on an adaptive chunking of data over the heterogeneous devices and the scheduling of the kernels. The technique proposed focuses on how to adapt the execution of one kernel on multiple devices.

Amongst other OpenCL extensions, SnuCL [88] is an OpenCL framework for clusters of CPUs and GPUs. The OpenCL API is extended so as to include functions similar to MPI. Besides, the OpenCL code is either translated into C for CPU, or Cuda for GPUs. The SnuCL runtime does not offer automatic scheduling between CPUs and GPUs. Moreover, SnuCL does not handle multi-device on the same node.

In Chapter II, we present our OpenCL implementation called SOCL that was among the first ones to provide a unified platform allowing devices of different platforms to be easily used jointly. In addition, by using OpenCL contexts as scheduling contexts, it lets applications use automatic kernel scheduling in a controlled manner. Besides, it automatically handles device memories and uses host memory as a swap memory to evict data from device memories when required. Finally, preliminary support for automatic granularity adaptation is supported too. SOCL is at the junction of frameworks using the command graph model and task graph based runtime systems.

#### I.3.3.3 Task Graph Based Runtime Systems

The command graph model as implemented by OpenCL lets applications explicitly schedule commands on available devices of an heterogeneous architectures. As it is extremely tedious to do properly and efficiently, a more abstract task graph model has been used by several frameworks such as StarPU [17] or StarSS [18, 113]. With these frameworks, applications dynamically build a task graph that is similar to a command graph containing only kernel execution commands not associated with a specific device. The runtime system is responsible of scheduling kernel executions and data transfers appropriately to ensure both correctness and performance. Figure I.7 shows a task graph and data used by each task.

- Heterogeneous Architectures -

Listing I.5: StarPU codelet definition example

```

struct starpu_codelet cl =

{

.where = STARPU_CPU | STARPU_CUDA | STARPU_OPENCL,

/* CPU implementation of the codelet */

.cpu funcs = {

sgemm_cpu_func

#ifdef __SSE__

, sgemm_sse_func

#endif

, NULL},

/* CUDA implementation of the codelet */

.cuda_funcs = {sgemm_cuda_func, NULL},

/* OpenCL implementation of the codelet */

.opencl_funcs = {sgemm_opencl_func, NULL},

.nbuffers = 2,

.modes = {STARPU_R, STARPU_RW},

};

```

A task is not exactly the same thing as a kernel. Indeed, in order to be able to schedule a task on different devices of an heterogeneous architecture, several kernels performing the same operation but on different architectures have to be grouped together to compose a task. For instance, SGEMM kernels written in CUDA, OpenCL and C can compose a SGEMM task. Listing I.5 shows how a task is usually defined with StarPU (in this case it is called a codelet) while Listing I.6 shows how it is defined with StarSS.

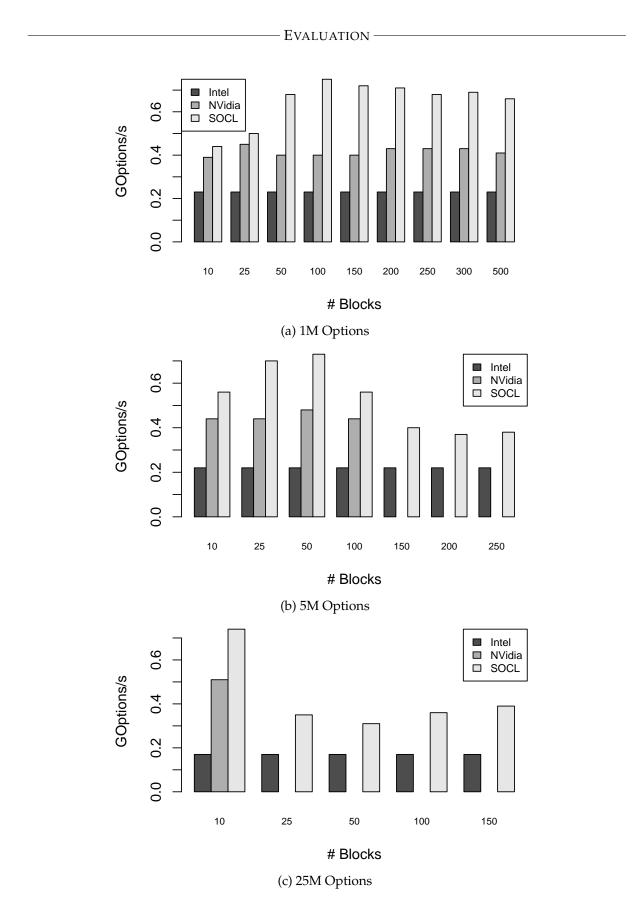

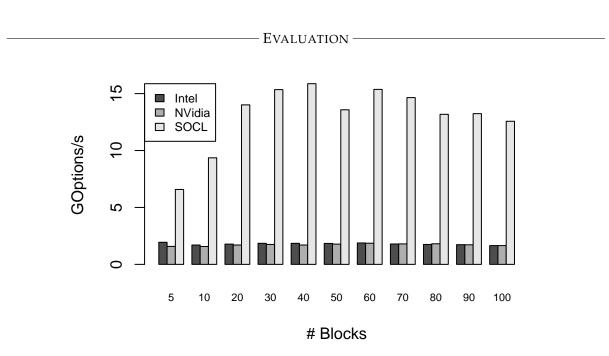

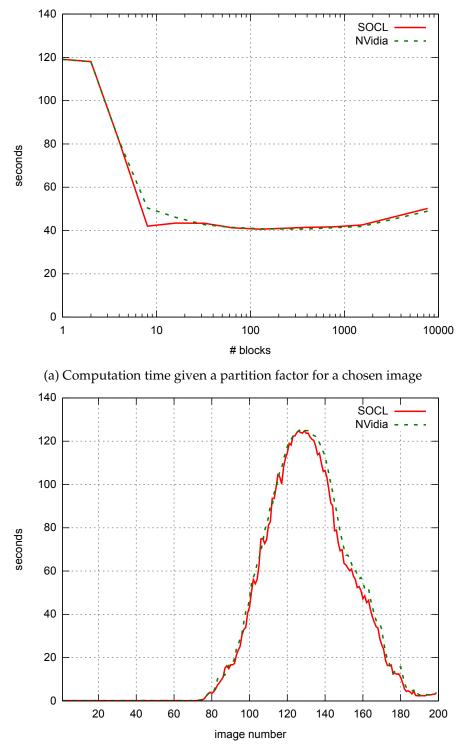

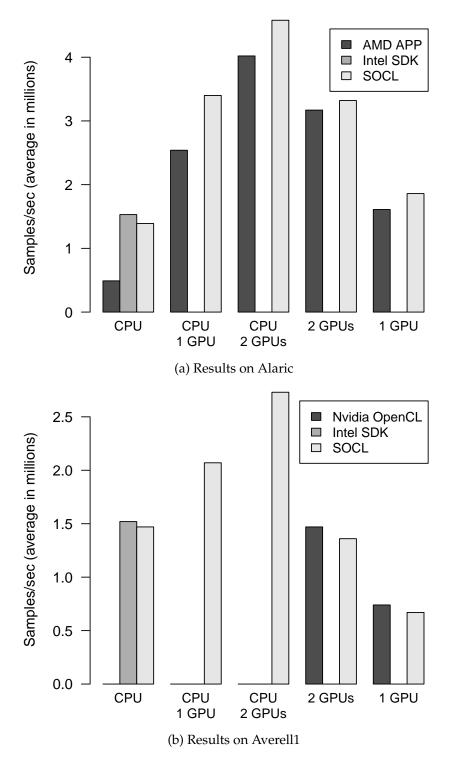

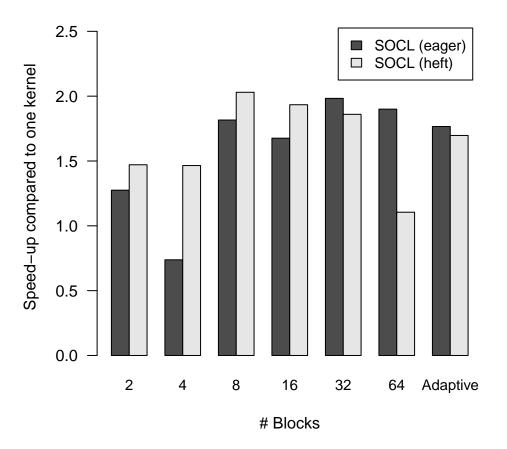

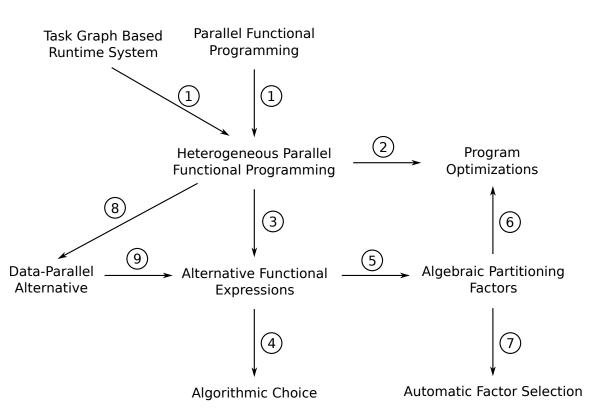

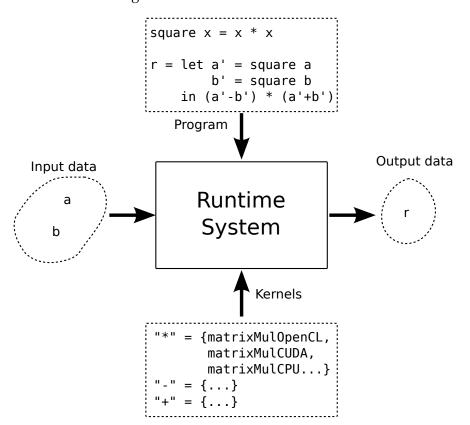

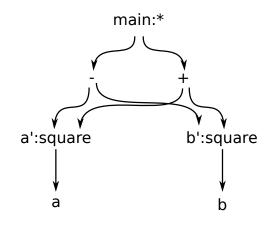

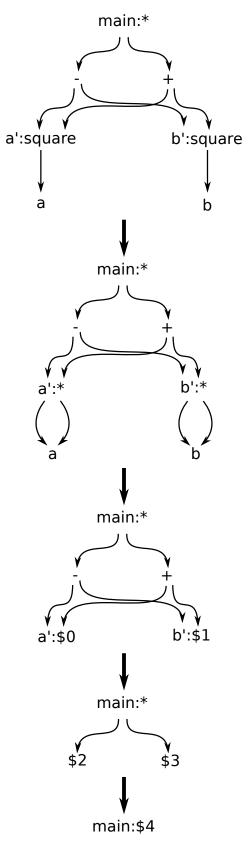

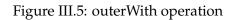

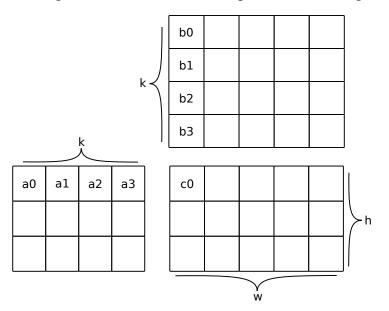

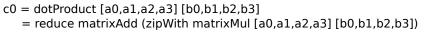

Listing I.7 shows how a task is created and submitted using StarPU API. First, data are registered in host memory. StarPU uses a shared-object memory model and transfers data as required in the different device memories. Then a task entity is created associated with the cl codelet and using the previously registered data and is submitted. Tasks are executed asynchronously thus the task\_wait\_for\_all primitive is used to wait for its completion. Finally, data are unregistered, meaning that the host memory is ensured to contain data in a coherent state. To make a task depends on some others, StarPU provides explicit and implicit mechanisms. When the implicit mode is enabled, task dependencies are inferred from task data access modes and task submission order: the last task accessing a data in write mode has its identifier stored alongside the data and subsequent access to this data by another task adds a dependence between the two tasks. Listing I.8 shows how to explicitly declare dependencies between several tasks. Task t2 will be executed only when both t1 and t3 have completed. Nevertheless, StarPU may perform some data transfers for t2 in advance to speed up the execution.