# Modélisation à haut niveau d'abstraction pour les systèmes embarqués

Matthieu Moy

### ► To cite this version:

Matthieu Moy. Modélisation à haut niveau d'abstraction pour les systèmes embarqués. Systèmes embarqués. Université de Grenoble, 2014. tel-01054555

### HAL Id: tel-01054555 https://theses.hal.science/tel-01054555v1

Submitted on 7 Aug 2014

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

Unité Mixte de Recherche UJF - CNRS - Grenoble INP

Centre Équation 2, avenue de VIGNATE F-38610 GIERES tel : +33 456 52 03 41 fax : +33 456 52 03 44 http://www-verimag.imag.fr

# UNIVERSITÉ DE GRENOBLE

# Habilitation à Diriger des Recherches

Spécialité Informatique

Présentée et soutenue publiquement par

Matthieu Moy

$13~\mathrm{mars}~2014$

# Modélisation à haut niveau d'abstraction pour les systèmes embarqués

# High-level Models for Embedded Systems

### JURY

Frédéric Pétrot Gérard Berry Rolf Drechsler Marco Roveri Samarjit Chakraborty Benoît Dupont de Dinechin

Professeur à Grenoble INP, France Professeur au Collège de France Professeur à l'Université de Brême, Allemagne Senior Researcher, Fondazione Bruno Kessler, Italie Professeur à l'université technique de Munich, Allemagne Directeur Technique, Kalray, France

Université Joseph Fourier

Président

Rapporteur

Rapporteur

Rapporteur

Examinateur

Examinateur

$\mathbf{2}$

### $\operatorname{BibT}_{E}X$ :

```

@PhdThesis{hdr-moy,

author = {Matthieu Moy},

title = {High-level Models for Embedded Systems},

school = {Univ. Grenoble Alpes, VERIMAG, F-38000 Grenoble, France},

year = {2014},

url = {http://www-verimag.imag.fr/~moy/?Habilitation-a-Diriger-des},

type = {Habilitation \'a Diriger des Recherches ({HDR})},

address = {Verimag},

}

```

-1

# Foreword

This document is my "habilitation" manuscript ("Habilitation à Diriger des Recherches", or HdR in French). It is a summary of the research I did on high-level modeling of embedded systems in the past decade.

The document tries to find the right trade-off between a short summary and an exhaustive and detailed document following two principles. First, verbatim reuse of the content of existing is avoided. Instead of repeating what has already been published, I try to give a different point of view, favoring examples over the general case, intuition over formalization, and figures over textual explanations. Hopefully, this should motivate the reader to search for more details in the existing publications. On the other hand, each contribution is presented with enough detail to let the reader understand the principles, intuition and design choices behind the approaches.

Each of my publications and supervised students/post-docs is cited in the document. The reader can find more information about them in the references at the end of the document (chapter 7). More details about myself and the collaborative projects I've been involved in are available in a separate file.

The document is best viewed in colors, A4 paper, but a black and white print is also readable.

Enjoy your reading!

# Acknowledgments

This document summarizes almost 12 years of my career. The list of people who should be thanked for their positive impact on these 12 years is long, and I will undoubtedly forget many of them.

There are short-term "thank you" for people who contributed to my habilitation document and defense. Thanks to Gérard Berry, Rolf Drechsler and Marco Roveri for the time they spent reviewing the manuscript; to Samarjit Chakraborty and Benoît Dupont de Dinechin for their role as examiners and to Frédéric Pétrot for accepting to be president of my Jury.

I would also like to thank people who made the day of the defense such a pleasant experience. Those who made videoconferencing possible, those who took care of the buffet, those who attended the talk, and those who enjoyed the Crémant and the macarons with me afterwards.

Thanks to people who helped me to prepare the habilitation, for their comments on drafts of the manuscript and during defense rehearsals.

There are also many long-term "thank you", for all the colleagues with whom I interacted the last 12 years, and who make me what I am today. To Oded Maler, who gave me a first taste of what research is, and then to Florence Maraninchi and Laurent Maillet-Contoz who supervised my Ph.D, and initiated the STMicroelectronics/Verimag collaboration which guided most of my works. To all the colleagues with whom I co-supervised students or co-authored articles. And of course, a warm "thank you" to all students and post-docs I supervised.

Finally, thanks to my girlfriend.

# Contents

| 1        | Intr | Introduction                                                             |    |  |  |

|----------|------|--------------------------------------------------------------------------|----|--|--|

|          | 1.1  | Embedded systems                                                         | 9  |  |  |

|          |      | 1.1.1 Complexity of Hardware                                             | 10 |  |  |

|          |      | 1.1.2 The Importance of Software                                         | 10 |  |  |

|          |      | 1.1.3 Constrained Systems                                                | 10 |  |  |

|          |      | 1.1.4 Modeling and Virtual Prototyping                                   | 11 |  |  |

|          | 1.2  | Contributions to Various Model-Based Approaches                          | 12 |  |  |

|          |      | 1.2.1 Virtual Prototyping and Simulation of System-on-Chips              | 12 |  |  |

|          |      | 1.2.2 Formal Verification of Functional Properties                       | 15 |  |  |

|          |      | 1.2.3 Formal Models for Non-Functional Properties                        | 17 |  |  |

|          | 1.3  | Organization of the document                                             | 19 |  |  |

| Ι        | Fui  | nctional Properties                                                      | 21 |  |  |

| <b>2</b> | Ver  | ification and Abstract Interpretation                                    | 23 |  |  |

|          | 2.1  | Abstract Interpretation of Java Sequential Programs                      | 23 |  |  |

|          | 2.2  | Model-checking Concurrent Java Programs                                  | 25 |  |  |

|          | 2.3  | From Bounded Model-Checking to Abstract Interpretation                   | 26 |  |  |

|          |      | 2.3.1 Bounded Model-Checking                                             | 26 |  |  |

|          |      | 2.3.2 State of the Art Abstract Interpretation                           | 27 |  |  |

|          | 2.4  | New Abstract Interpretation Techniques                                   | 29 |  |  |

|          |      | 2.4.1 Combining Path focusing and Guided Static Analysis                 | 29 |  |  |

|          |      | 2.4.2 Disjunctive Invariants                                             | 30 |  |  |

|          |      | 2.4.3 Real-Life Experimentations                                         | 31 |  |  |

| 3        | Cor  | npilation and Verification for SystemC                                   | 33 |  |  |

| -        | 3.1  | SystemC Front-ends                                                       | 34 |  |  |

|          |      | 3.1.1 Challenges in Writing SystemC Front-ends                           | 34 |  |  |

|          |      | 3.1.2 Existing Approaches for SystemC Front-Ends                         | 34 |  |  |

|          |      | 3.1.3 Pinapa: a First Attempt at a Dynamic Approach                      | 36 |  |  |

|          |      | 3.1.4 PinaVM: a SystemC front-end Based on an Executable Representation  | 37 |  |  |

|          | 3.2  | Verification of SystemC/TLM                                              | 38 |  |  |

|          |      | 3.2.1 Overview of Verification Approaches                                | 38 |  |  |

|          |      | 3.2.2 PinaVM Backend for SPIN                                            | 41 |  |  |

|          |      | 3.2.3 Transforming C++ and SystemC Code into Synchronous Languages using |    |  |  |

|          |      | SSA                                                                      | 42 |  |  |

|          |      | 3.2.4 PinaVM Backend for 42                                              | 45 |  |  |

|          | 3.3  | Another Application of Compilation: Optimizing Compiler                  | 45 |  |  |

|          |      | 3.3.1 Motivations and Principle                                          | 45 |  |  |

| 3.3.2 | Direct Memory Interface: a Manual Optimization | 46 |

|-------|------------------------------------------------|----|

| 3.3.3 | Integrating Tweto with PinaVM                  | 47 |

### II Non-functional Properties

### **49**

| 4 | Nor   | n-functional Properties in TLM                                            | 51 |

|---|-------|---------------------------------------------------------------------------|----|

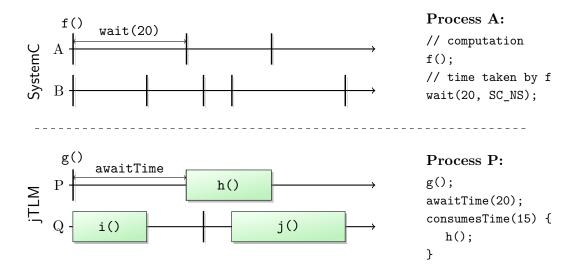

|   | 4.1   | Time and Concurrency                                                      | 51 |

|   |       | 4.1.1 Time and Concurrency in SystemC                                     | 51 |

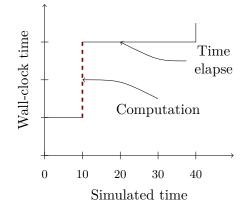

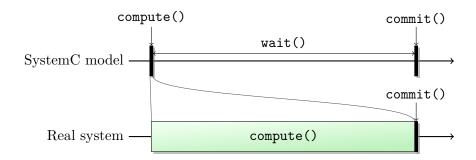

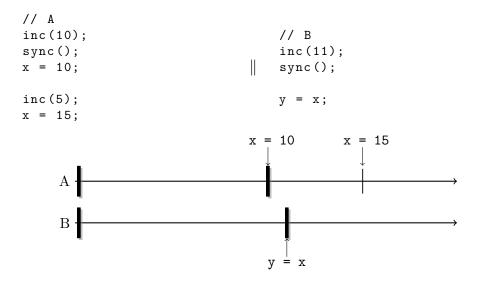

|   |       | 4.1.2 Temporal Decoupling and Performance Optimizations                   | 53 |

|   |       | 4.1.3 Limitations of the Concurrency Model of SystemC/TLM                 | 55 |

|   |       | 4.1.4 jTLM: an Experimentation Platform for Transaction-Level Modeling    | 57 |

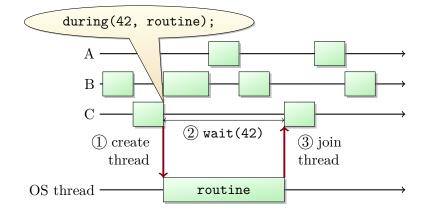

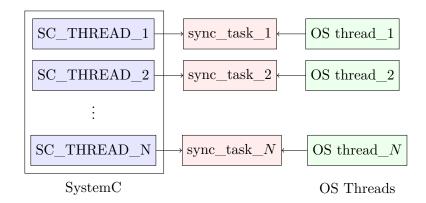

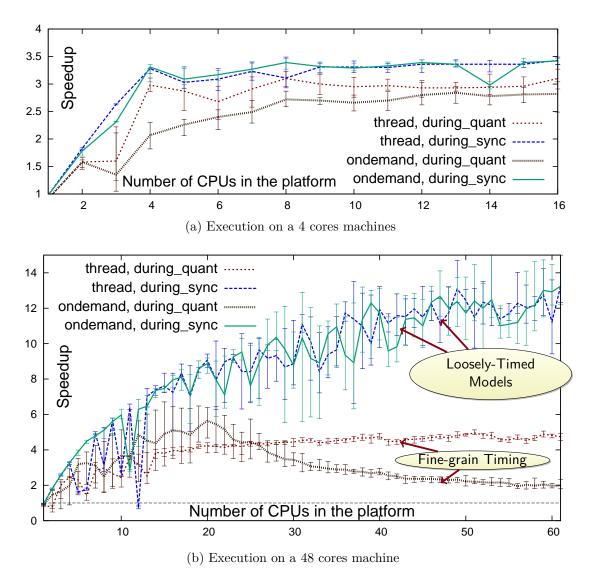

|   |       | 4.1.5 Parallelization with sc-during: Adapting jTLM's Ideas to SystemC    | 60 |

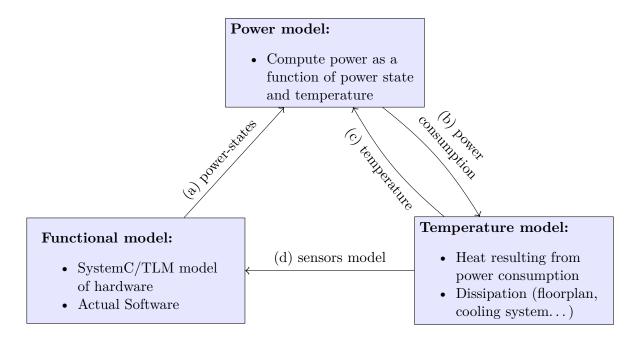

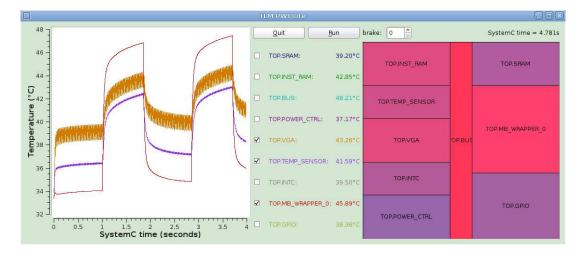

|   | 4.2   | Power and Temperature Estimation                                          | 66 |

|   |       | 4.2.1 Power Management in Modern System-on-Chips                          | 66 |

|   |       | 4.2.2 Virtual Prototyping for Power Aware Systems                         | 67 |

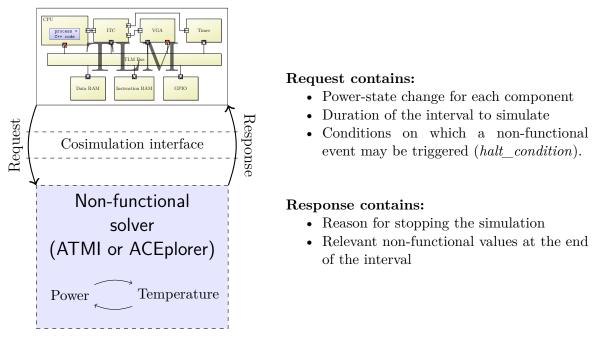

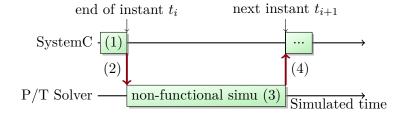

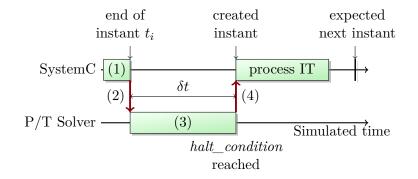

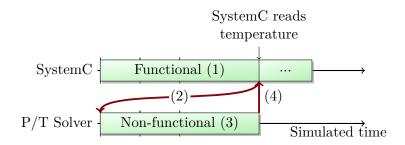

|   |       | 4.2.3 Cosimulation of a Functional Simulator with a Non-Functional Solver | 69 |

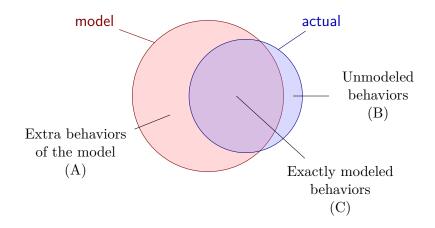

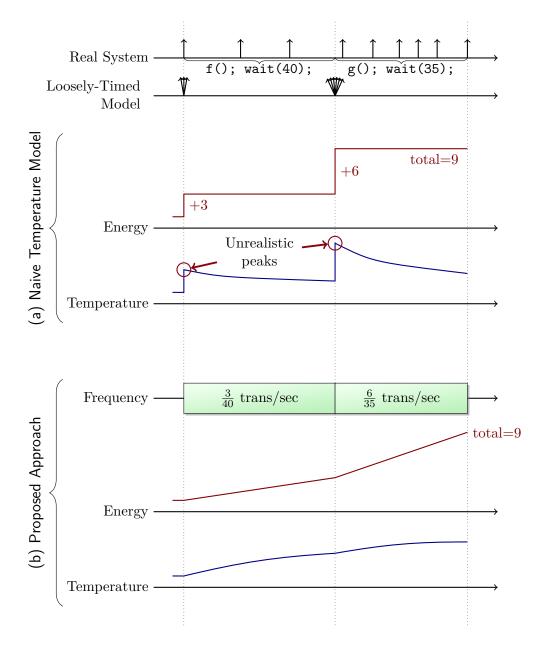

|   |       | 4.2.4 Functional and Non-functional Models and Loose Timing               | 70 |

|   |       | 4.2.5 Validity and Precision of the Models                                | 76 |

| 5 | For   | mal Model of Time: Real-Time Calculus                                     | 77 |

| Ŭ | 5.1   | Modular Performance Analysis and Real-Time Calculus                       | 77 |

|   | 5.2   | Modular Performance Analysis and Timed Automata                           | 79 |

|   | 5.3   | Using Lustre as an Intermediate Language in MPA: ac2lus                   | 79 |

|   | 5.4   | The Causality Problem                                                     | 82 |

|   | 0.1   | 5.4.1 Defining Causality                                                  | 82 |

|   |       | 5.4.2 Solving the Causality Problem: The Causality Closure                | 83 |

|   |       | 5.4.3 Implementation in ac2lus for $\mathcal{U}pac$ Curves                | 85 |

|   | 5.5   | Towards a more General MPA Framework                                      | 86 |

|   |       |                                                                           |    |

| C | onclu | usion and References                                                      | 89 |

| 6  | Conclusion       |         |                                                                | 89  |

|----|------------------|---------|----------------------------------------------------------------|-----|

|    | 6.1              | Summ    | ary and General Principles                                     | 89  |

|    | 6.2              | Future  | Directions                                                     | 90  |

|    |                  | 6.2.1   | Performance Optimization for SystemC Simulations               | 91  |

|    |                  | 6.2.2   | Thermal Modeling for Systems-on-a-Chip                         | 91  |

|    |                  | 6.2.3   | Formal Verification of SystemC Programs                        | 91  |

|    |                  | 6.2.4   | Modular Performance Analysis: Beyond Real-Time Calculus?       | 92  |

|    |                  | 6.2.5   | Abstract Interpretation                                        | 92  |

|    |                  | 6.2.6   | Implementation of Critical Systems on Multi-Core Architectures | 92  |

| 7  | Refe             | erences | 5                                                              | 93  |

|    | 7.1 Bibliography |         | 93                                                             |     |

|    | 7.2 Students     |         |                                                                | 103 |

| In | $\mathbf{dex}$   |         |                                                                | 110 |

# Chapter 1

# Introduction

There are no airplanes, only computers that fly. There are no cars, only computers we sit in. There are no hearing aids, only computers we put in our ears.

- Cory Doctorow, The coming war on general computation (2011)

This document summarizes my research over the last decade. The research was done in the Verimag laboratory. I will recall the work done during my Ph.D (2002-2005), and present the one done as a permanent member, since 2006. I contributed to several areas related to high-level modeling of embedded systems. The contributions presented in this document can be classified according to several criteria: functional properties (does the system produce the right result?) or non-functional ones (does it produce the result at the right time? How much resources does it use?); formal models or simulation-based approaches; targeting software or hardware... The contributions are summarized below in Section 1.2.

A large part of the research deals with virtual prototypes for Systems-on-a-Chip and was done in close collaboration with STMicroelectronics. The collaboration was initiated by my Ph.D, and continued since then with 2 collaborative projects, 3 joint Ph.D, plus the OpenES project which just started. This industrial partnership naturally implies a pragmatic approach: we have to take into account existing tools and workflows, not just propose new ones. In this case, the standard is SystemC/TLM, a set of libraries on top of C++. As a consequence, we have to deal with the complexity of C++.

### 1.1 Embedded systems

*Embedded systems* can be defined as computing systems that are not computers. Interestingly, while it seems natural to associate computer science with computers, only 2% of processors today are used in general-purpose workstations [Har04].

The evolution of general purpose computers and the one of embedded systems have both been following Moore's law, leading to an amazing complexity of hardware in terms of number of transistors and hardware components. One point that distinguishes most embedded systems is that their complexity is usually exposed to the programmer: while each generation of Pentium processor is more complex than the previous one, porting software to new hardware is usually as simple as a recompilation, if at all needed. On the other hand, most embedded systems come with a set of sensors and actuators, and have an architecture that is at least partially visible to the software.

Because of the diversity of embedded systems, it is hard to make any general statement about "embedded systems" without refining the definition. In this document, "embedded systems" will usually refer to consumer electronic devices, with an emphasis on complex systems.

#### 1.1.1 Complexity of Hardware

The need for performance optimization (both to provide more computing power and to consume less energy) has led to architectures where the functionality is split across multiple components. In a typical system, the non-performance critical parts can be implemented in software, but the intensive computations are delegated to some specific hardware. One option is to use a fully specialized hardware component (*IP* blocks, for *Intellectual Property*), that the software will have to program properly. A dedicated IP is more efficient both in terms of power consumption and speed than a software implementation.

Another trend is to use *many-core* accelerators like STMicroelectronics' *STHorm* (formerly known as *Platform 2012*) [MBF<sup>+</sup>12] or Kalray's *Multi-Purpose Processor Array (MPPA)* [Kal12]. These many-core systems break the common "shared memory SMP" programming model. First, the number of processors is too high to allow efficient cache-consistency, so the processors in the array use local memories and explicit transfers, usually using dedicated DMA components, to the global memory. Then, the high processor density is only possible because the individual processors are simple enough. For example, Kalray's MPPA 256 counts 256 cores (with plans to increase to 1024), plus 16 cores for the I/O subsystems, using its own proprietary core technology. STHorm is made of clusters of 16 STxP70 processors. Such processors typically cannot run a general purpose operating system; e.g., Kalray's MPPA cluster cores work non-preemptively. This is acceptable for very specialized computation, but unacceptable for high-level application code, hence the full system should contain at least one more general purpose processor. The result is a highly heterogeneous system, with several pieces of software compiled for different processors and possibly different operating systems.

#### 1.1.2 The Importance of Software

While dedicated hardware is essential for performance, there is also a number of good reasons to move the complexity of the system to the software part. The programming models available in software developments are much richer and allow solving algorithmically hard problems in fewer lines of code (see for example how easy it is to do dynamic memory allocation or recursive calls in software). Many embedded systems run an operating system like Linux, which can manage concurrency between applications, resource sharing and easy access to the underlying hardware.

A key advantage of software is that it brings a lot of flexibility since it is possible to update it at any stage of the system's life-cycle (unlike fixing hardware bugs, which may require refabrication of the masks and cost millions of dollars before shipping the first fixed chip!). Unless a hardware implementation can be completely trusted, a software implementation is usually preferred for any critical part of the system.

As a result, systems are composed of a large number of hardware and software components that depend on each other. It is not sufficient to validate each component individually to ensure the correct behavior of the system. Both the architectural choices and the functional behavior need to be validated at the *system-level*, i.e., considering the whole hardware platform together with the software that runs on it.

#### 1.1.3 Constrained Systems

Interaction with the environment enforces constraints on the design of a system. Most embedded systems are real-time systems: either *soft real-time* systems, for which the interaction with the environment is supposed to be performed at the right time or *hard real-time*, for which the interaction needs to be performed at the right time. In consumer electronics, systems are usually soft real-time (for example, a multimedia application will produce unpleasant glitches, or sound/image desynchronization if it is badly timed).

#### 1.1. EMBEDDED SYSTEMS

Other *non-functional properties* like silicon area, power consumption and temperature can also become very important. For mobile devices, the power consumption obviously impacts the battery life, but a high power consumption is not always acceptable even for permanently plugged devices. Not only power consumption has an environmental impact, but it also has a financial cost: a chip that consumes too much requires a more expensive packaging and may need a cooling system, possibly noisy for the user. Worse, power consumption peaks can lead to overheating that can physically damage the chip, or to undervoltage that can break the functional behavior. In general, bad thermal behavior (high temperature or temperature gradient) lead to faster aging of the silicon.

Power-saving can be done at various levels. Obviously, optimizing the silicon electrical conductivity and transistor capacitance at the lowest, physical level can change the consumption of the chip (e.g., using FD-SOI [His01] instead of bulk CMOS). Optimizations can also be done within synthesizers, to minimize bit flips for a given computation, or to reduce silicon area. But a large part of optimization opportunities in modern systems is found at the system-level: a global *power management* policy should be able to switch off components that are not used and to reduce the voltage to the minimum required to accomplish the currently running tasks. Reducing the voltage saves energy but implies reducing the frequency hence slowing down the computation.

In traditional computers, these constraints can often be managed with a *best-effort* policy, i.e., make computers "as fast as possible" and consume "as little power as possible". This is generally not possible with embedded systems: over-dimensioning the design to meet the constraints may not be acceptable given the competitivity of the domain, and an under-dimensioned system may be unusable (e.g., a set-top box that is not able to deliver the video stream in real-time is basically useless). It is therefore important not only to be able to optimize these non-functional properties, but also to be able to evaluate them and validate the system taking them into account as early as possible in the design flow.

#### 1.1.4 Modeling and Virtual Prototyping

A common practice is to write *models*, i.e., simplified versions of the real system, before the system is available. There are many kinds of models, depending on the intended application. In *model-driven development*, models are used as the starting point of the implementation flow, using automatic or semi-automatic code generation tools. But not all of them are used to derive an implementation. Models of the physical environment can be used for testing or verification, but obviously won't be embedded in the real system. A thriving trend is *virtual prototyping*, where an executable model of the system is developed early in the design flow to validate some architectural choices or for embedded software development, but not directly to derive an implementation.

Virtual prototyping allows activities that were previously performed on the real system to be performed in a virtual, i.e., software-simulated, platform. Virtual prototypes can be seen as executable specifications of the system. They may be used as reference models for validation of the real system, but are usually not meant to be the starting point of automatic synthesis. Instead, a manual refinement or rewrite has to be performed.

The evolution of programming languages has allowed programmers to abstract away many hardware specificities. From binary machine code to assembler, and then to imperative languages like C, compilers have allowed abstracting away the instruction coding. Some modern languages allow even more distance between the code written and the way it will run on the machine.

For example, the *Lustre* [BCH<sup>+</sup>85] programming language allows the programmer to write a highly parallel, synchronous, and data-flow description of the system, and lets the compiler do the job of statically scheduling the operations and generating the imperative code. At this level,

one can either refer to the description as "programs", since it is executable and can be compiled to assembly code, or as "models", since it allows abstract reasoning, and even formal proofs (e.g., Lesar [HLR92] or Nbac [Jea03]). In the work presented below, Lustre is used either as an intermediate formal language (Sections 3.2.1 and 3.2.3) or as a modeling language (Section 5.3). We also used Lustre as an implementation language for a toy NXT-robot controller with Valentin Bousson.

The domain of hardware design has followed a similar evolution: from gate-level to RTL, synthesizers have allowed abstracting away the implementation details of state-machines and registers, and modern *high-level synthesizers* are able to generate hardware from simple enough sequential C code [GDC92].

These approaches are appealing, but not always applicable. The subset of C accepted by high-level synthesizers is much smaller than the one developers would like to use for very highlevel modeling. Dedicated languages are purposely limited to prevent dangerous constructs like dynamic memory allocation. Most of the work presented in this report focuses on models that are not meant to be used directly for implementation. An exception is the work done on abstract interpretation, which applies directly to software implementations, not to models or prototypes. The following section presents several categories of approaches, and classifies the contributions of the document in these categories.

### **1.2** Contributions to Various Model-Based Approaches

#### 1.2.1 Virtual Prototyping and Simulation of System-on-Chips

The Register Transfer Level (RTL) abstraction level is the entry point of the hardware synthesis flow. While more abstract than gate-level designs, RTL programs still require the developer to describe all the micro-architecture of the platform, i.e., describe each register, each pipeline stage, each communication element and each state-machine behavior at each clock tick. As a result, RTL programs simulate very slowly, and the simulation speed is inversely proportional to the size of the platform. For large systems, RTL simulation is applicable on individual components, but far too slow for a day-to-day use at the system-level (for example, booting an operating system can take tens of hours at this level [HYH<sup>+</sup>11]).

Various techniques have been proposed to speed up RTL simulations. Optimizers like Verilator [Sny12] or Carbon Model Studio [CDS13] can generate higher-level programs from synthesizable code, achieving an important simulation speedup. Performance-consuming parts of the RTL system can be replaced by a faster simulator: typically an RTL processor can be replaced by a faster *Instruction Set Simulator (ISS)*, which interprets the software's executable binary without simulating all the details of the processor. These techniques provide a valuable speedup, but are far from sufficient to turn a 10 hours simulation into a delay short enough to be acceptable in the typical "compile/debug&execute" cycle of a software developer. We need several orders of magnitude of speedup, and cannot hope for such a speedup without a major change in the level of abstraction.

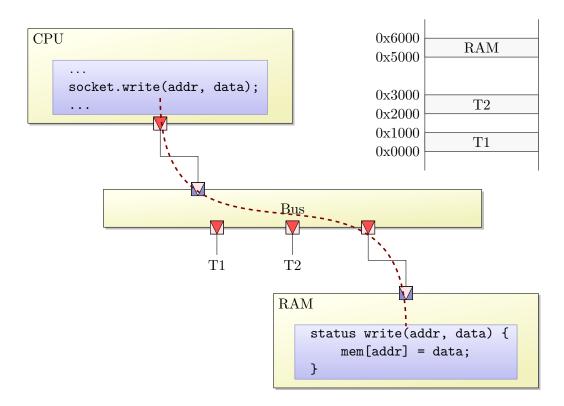

The Transaction-Level Modeling (TLM) [Ghe05, Ope08] level of abstraction was introduced in response to this problem. One can find many definitions of TLM, and even the definition standardized by IEEE and the Accellera Systems Initiative (ASI, formerly OSCI) consortium is declined in several flavors. A first, simple definition can be given as "a model in which we describe everything that is needed for the software to execute, and only this".

In this context, "software" includes low-level software such as drivers, so the definition implies that the address map of the platform be modeled properly. This in turn implies that the overall architecture of the platform be reflected in a TLM model, including register sets. Also, a notion of concurrency must be visible in the model, since the software can run scenarios like "program a computation in component A, then program component B, and then get the result of component A", which requires *concurrency* between components A and B.

On the other hand, many details that appear in an RTL design are abstracted away in TLM. For example, the bus protocol is abstracted into a very simple interface based on function calls; in short, the initiator components call functions of the target components similarly to what is done in remote-procedure call frameworks. The micro-architecture within components can also be abstracted away. For example, from the software point of view, it is sufficient to know that a processor executes an instruction set, but the pipeline and cache need not be visible for the software to execute.

The industry-standard for TLM is SystemC [Ope11], which adds to C++ the missing elements for TLM. The first addition is a notion of simulated concurrency. Although SystemC programs are usually executed sequentially, the system they represent can be parallel. A SystemC program contains a set of processes that are executed in interleaving semantics by a scheduler. SystemC provides a notion of *simulated time*: concurrency between two processes is simply modeled by the fact that they execute at the same simulated time.

SystemC was originally designed for levels of abstractions lower than TLM. In particular, the communication mechanisms were directly inspired from the VHDL and Verilog ones (e.g., the sc\_signal with  $\delta$ -cycle mechanism). SystemC 2.0 introduced the notion of user-defined communication channels, allowing users to define their own higher-level channels. Based on this infrastructure, different companies started developing in-house protocols for TLM. During my Ph.D, I could follow the birth and evolutions of the TAC protocol [ST05] proposed by STMicroelectronics, while for example, GreenSoCs which was both a partner and a competitor was developing GreenBus [Gre07]. Then started the standardization process, required for interoperability. Most participants were pushing the solution they had already deployed internally. A first compromise was TLM-1.0, in 2005, which standardized the principle of communication based on function call, but left the argument and return type of this function (tlm\_transport\_if::transport()) unspecified. The way data was exchanged was described, but the content of transaction was not. Therefore, the standard provided no complete solution to the interoperability problem. The standardization process continued with TLM-2.0 [Ope08], 3 years later, where the content of transaction (payload) was standardized. Finally, the TLM-2 OSCI standard was incorporated in the SystemC IEEE standard in its latest version (1666-2011).

Essentially, a transaction transports an address, a piece of data of arbitrary length, a command (e.g., read, write, ...) and a status (ok, error, ...). Additional fields are provided to allow different modeling styles and optimizations.

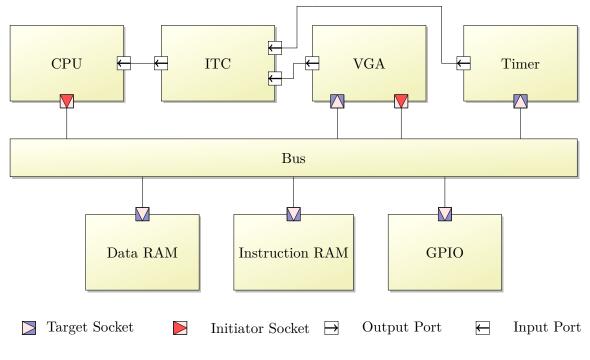

Figure 1.1 shows a graphical view of an example TLM platform. The example is extracted from a lab-work given to Ensimag students in my SystemC/TLM course [Moy12a]. The actual platform is a small system running on an FPGA and executing Conway's Game of Life. It contains a processor, a timer (to control when a new image should be computed), a VGA video controller, a *General Purpose Input-Output (GPIO)* component to manage buttons for user-interaction, a *Universal Asynchronous Receiver Transmitter (UART)* that can send data to a computer over a serial link, an *InTerrupt Controller (ITC)*, and two RAMs. The TLM platform is very simple (it fits in 1000 lines of C++ code), especially when compared to the RTL one (around 10,000 lines of VHDL). However, following the principle presented above, the platform contains just enough detail to execute software, and the same C code can run on the real system and on the TLM platform.

Each box on Figure 1.1 corresponds to a SystemC component, which contains functions to be called through their target socket, some active process code, or both. Most communication is done through a shared bus, modeled by a TLM-2 channel. Interrupts (IRQ) do not need the expressiveness of TLM-2, as they transport no data nor address. They are modeled as simple SystemC signals.

Figure 1.1: Graphical View of an Example TLM Platform

#### Contributions in the Area of Virtual Prototyping

We made the following contributions to the area of virtual prototyping with TLM:

- We developed dedicated compilation techniques for SystemC. SystemC cannot be considered as a "normal" programming language [MMK10], since it is implemented as a library for C++, and the equivalent of a compiler front-end should be able to extract information that are built during the execution of the simulator, before the actual simulation starts. We present techniques implemented in the tool *PinaVM* [MM10b] that extract both the behavior of processes and the architecture of the platform, and is able to link these together. This contribution will be presented in Section 3 and has been published in [MMK10, MM10a]. It is a continuation of the work done during my Ph.D [MMMC05b, MMMC06, Moy05b] which will be briefly recalled too.

- Based on this tool, we developed an *optimizing compiler*, dedicated to SystemC. This compiler uses the information provided by the front-end PinaVM to perform optimizations like function inlining across an interconnect, hence requires a visibility on the architecture and a knowledge of SystemC's semantics. This contribution will be presented in Section 3.3.

- We identified some limitations of the traditional model of time and concurrency in SystemC/TLM with respect to faithfulness. In particular, we show that some memory-model related bugs cannot be discovered with existing techniques. This contribution is presented in Section 4.1.1 and has been published in [FMMCM11].

- We developed a new TLM simulator called jTLM (for "Java TLM"). This simulator was initially created to study the TLM level of abstraction without the constraints of SystemC, and was then used as an experimentation framework to develop new features like the

#### 1.2. CONTRIBUTIONS TO VARIOUS MODEL-BASED APPROACHES

notion of *task with duration*. Tasks with duration allow a more efficient parallelization and partially solves the faithfulness issue presented above. This contribution will be presented in Section 4.1.4 and has been published in [FM11b, FM11a].

- The notion of tasks with duration developed in jTLM was then adapted to SystemC, providing the same benefits, but without the need for a specialized scheduler. The result is the sc-during library [Moy12b, Moy13]. It will be presented in section 4.1.5.

- We contributed to the development and validation of a "Smart FIFO" [HCG<sup>+</sup>13], a model of a FIFO component which minimizes context-switches using temporal decoupling. Unlike most approaches, the Smart FIFO guarantees that the behavior obtained with temporal decoupling is equivalent to a behavior produced by a non-decoupled model.

- We developed new approaches and tools for estimation of non-functional properties like *power consumption* and *temperature* at different levels of abstraction. These tools allow co-simulating a functional model with a non-functional solver that models power consumption and temperature dissipation. The cosimulation interface [BMM<sup>+</sup>13b] is very general, but its application to loosely timed systems requires some work to avoid unrealistic results like spurious temperature peaks in simulation when they would not happen in the real system [BMM13a]. This contribution will be presented in section 4.2.4.

#### **1.2.2** Formal Verification of Functional Properties

Virtual-prototyping and simulation-based approaches have had a number of success stories in the industry. However, an obvious limitation of these approaches is that the validation is done on a finite number of executions. It can be desirable to get more formal guarantees about the system, hence to work with more formal models. Formal verification is essential for critical embedded systems, and may also increase the reliability or reduce the testing effort of non-critical systems.

While simulation-based approaches are inherently limited in scope, formal approaches are limited in theory by Rice's theorem, stating that no non-trivial analysis method can be at the same time:

- 1. Automatic: in the form of an algorithm that terminates in finite time without human intervention,

- 2. Sound: results provided by the analysis are proved to hold on the system,

- 3. Complete: any property that holds can be exhibited by the analysis,

- 4. Unbounded: not limited to bounded execution or state-space.

Relaxing any of these conditions allows an analysis to be performed, and indeed correspond to one domain of software verification. Relaxing constraint 1 (*automation*) is done by proofassistants that require the intuition of a human user to carry out the proof. Bug-finding techniques (e.g., testing, or lint-tools that only apply heuristics to find common bad patterns in the code) may not be *sound* (constraint 2) in the sense that a system validated with testing or linting has no guarantee to be actually correct. Relaxing constraint 3 (*completeness*) leads to techniques that may actually prove properties, but may be unable to answer (i.e., answer "yes" or "don't know" when asked to prove a property). One approach in this category is abstract interpretation, developed below. Relaxing the last constraint (4, *boundedness*), the state-space becomes finite and can be exhaustively explored, which is done in *model-checking* approaches. The boundedness can be applied on the length of execution traces, or on the size of the statespace. In the first case, the term *Bounded Model-Checking* (*BMC*) is used. BMC can formally prove that no property violation can occur in less than N steps, but cannot prove properties valid for any execution. A common technique in bounded model-checking is to encode an execution trace of size N, starting from an initial state and ending in an error state, into a logic formula, and then check for the satisfiability of this formula. If the formula is satisfiable, then a model of this formula represents a counter-example. If not, the property is proved for any execution of size N. If the formula is purely Boolean, the satisfiability problem is called *SAT*. If the formula is not purely Boolean, then SAT-solving techniques can be combined with an external theory to form a *Satisfiability Modulo Theories (SMT)* solver.

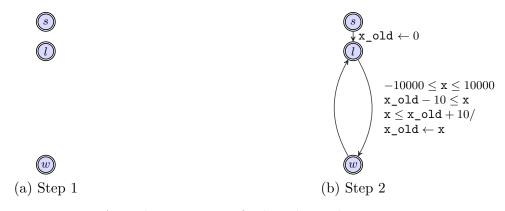

Abstract interpretation is a theory that allows the automatic, sound analysis of a possibly unbounded system (e.g., a system that contains numerical variables). Abstract interpretation associates a set of possible variables valuations with each program point. The concrete set of variable valuations being potentially infinite, it has to be abstracted in a so-called *abstract value*, which has a finite machine representation. The set of possible abstract values is called the *abstract domain*. Different abstract domains provide different precision and algorithmic costs. For example, the domain of intervals allows an algorithmically cheap analysis, but cannot represent relations between variables. The polyhedra domain is more expressive and usually provides more precise results, but most operations are exponential in the number of variables.

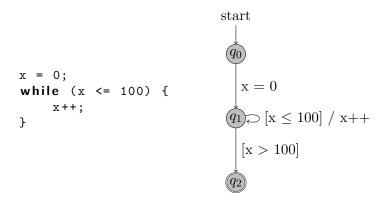

The analysis propagates abstract values from program points to program points until a fixpoint is reached. The termination of the iteration can be ensured by a widening operator. Figure 1.2 illustrates this on a very simple example.

Figure 1.2: Traditional Abstract Interpretation on a Simple Example

The analysis associates a set of possible values V(q) for the variable **x** with each program point q (in this case, control-points of the control-flow graph). Initially, we start with an underapproximation of the possible valuations:  $V(q_0) = ] - \infty, +\infty[$  and  $V(q_1) = V(q_2) = \emptyset$ . Then, the analysis propagates the values on the transition  $q_0 \to q_1$ , yielding  $V(q_1) = \{0\}$ . The selfloop  $q_1 \to q_1$  can then be applied, providing successive values  $[0, 1], [0, 2], \ldots$  for  $V(q_1)$ . The succession of values could be large, or even infinite, so the widening operator is used to enforce and speed up convergence. For example, after computing [0, 1] and [0, 2], the widening operator can interpolate the set directly to  $V(q_1) = [0, +\infty[$ . At this point, the transition  $q_1 \to q_2$  become fireable, yielding  $V(q_2) = [0, +\infty[\cap]100, +\infty[=]100, +\infty[$ . After this, firing any transition does not exhibit any new value: a fixpoint of the iterations with widening is reached and the valuations we obtained provide a safe invariant for the program. We can further tighten the invariant with *narrowing* iterations: perform one or several more iterations without widening, and without performing a union with the previous invariant candidate. The narrowing iterations can recover part of the precision that was lost by widening.

#### Contributions in the Area of Verification

We made the following contributions related to formal verification:

#### 1.2. CONTRIBUTIONS TO VARIOUS MODEL-BASED APPROACHES

- We developed several verification tools for sequential programs. Some of the tools are merely reproduction of traditional verification techniques (abstract interpretation, model-checking). The tool PAGAI, on the other hand, first implemented state-of-the-art static analysis using abstract interpretation together with SMT solving, and then allowed proposing new techniques that combined and improved the existing ones. PAGAI also allowed a comparison of existing and new techniques on real-life programs. These analyzers will be presented in Section 2 and have been published in [HMM12b, HMM12a].

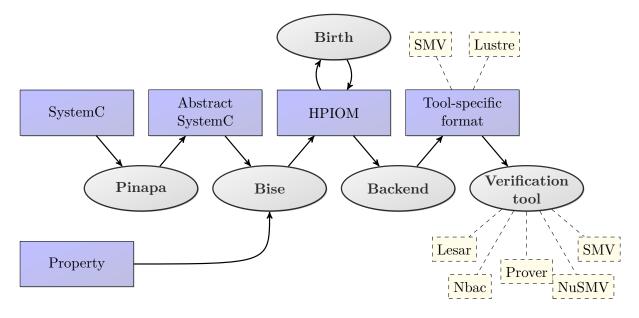

- We developed verification tools dedicated to SystemC. Borrowing some ideas from the LusSy [MMMC05a, Moy05a, Moy05b, MMMC06] tool, developed as part of my Ph.D, we provided new techniques to exploit co-routine semantics of SystemC, and the properties of the Static Single Assignment (SSA) form used as intermediate format in modern compilers for formal verification. This contribution will be presented in Section 3.2; it led to the publications [BGM<sup>+</sup>09b, TCMM07, MMJ11, MMC<sup>+</sup>08].

#### **1.2.3** Formal Models for Non-Functional Properties

Simulation-based approaches can also be insufficient to enforce non-functional properties. Although functional correctness is often more important than non-functional properties (e.g., a slow computer is preferred to a computer that crashes periodically), embedded systems can also require that some non-functional properties be formally verified.

For example, in a hard real-time system, strong guarantees are needed on the Worst-Case Execution Time (WCET) of a task, or on the Worst-Case Traversal Time (WCTT) of an event to process in a data-flow system. Doing formal WCET analysis on a TLM model for a complex hardware/software system would not be possible, as it would require analyzing the product of a relatively complex and detailed hardware model, by the compiled software.

Formal models are needed to conduct a formal proof, but such models cannot be automatically extracted from the implementation. This differs from formal verification presented above where the formal model on which the analysis runs is usually extracted automatically from the program under analysis.

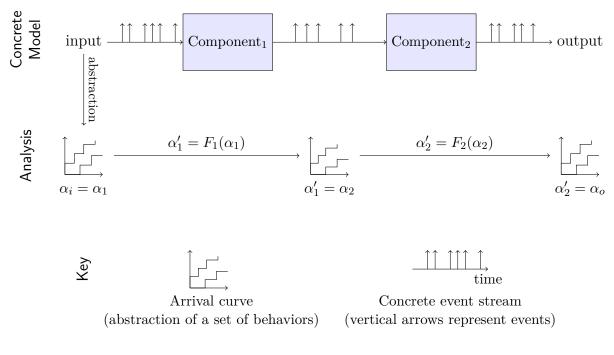

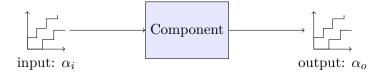

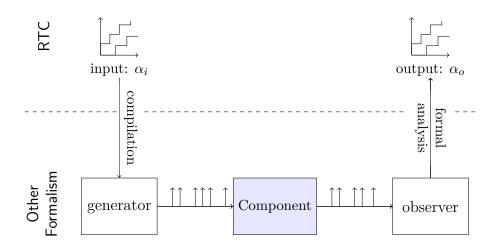

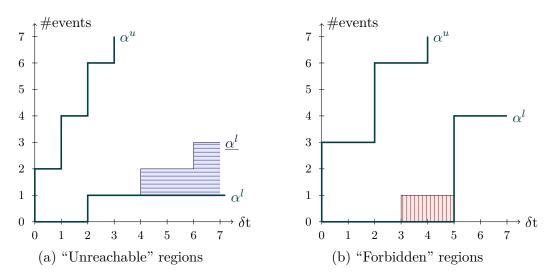

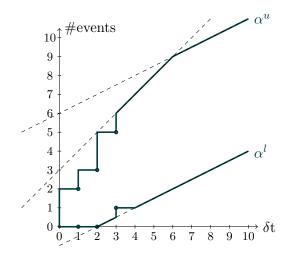

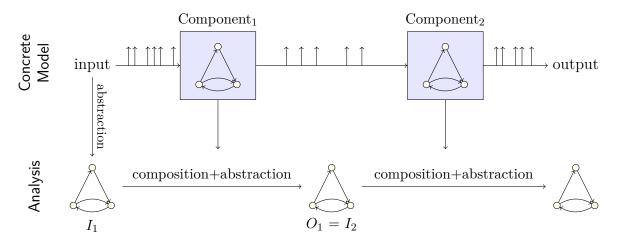

Part of this document describes the work carried out in formal models for performance analysis. The starting point is the Modular Performance Analysis (MPA) with Real-Time Calculus (RTC) [TCN00] developed by Lothar Thiele *et al.* based on the Network Calculus [LBT01] theory. The idea is to model a system with a set of components communicating together through event streams, as sketched in Figure 1.3. The actual data exchanged between components is abstracted away; since events contain no information, one can only count the number of occurrences of an event over a time interval. Figure 1.3 shows only the events to be processed, but the MPA framework is more general and allows modeling computing resource in the same way. The analysis is then done by manipulating abstractions of event streams called *arrival curves*, which specify bounds on the number of events that can arrive during any time interval. In Real-Time Calculus, arrival curves are usually manipulated by pairs: the lower curve ( $\alpha^l$ ) specifies a lower bound and the upper curve ( $\alpha^u$ ) an upper bound. For example, a pair of arrival curves can express: "between 1 and 5 events can arrive per second, and no more than 10 events can arrive during a period of 5 seconds".

The analysis in MPA is done component per component: the arrival curves of output streams for each component are computed as functions of the input arrival curves. In Figure 1.3, for example, the analysis for Component<sub>1</sub> applies the function  $F_1$  to the input arrival curve  $\alpha_1$ to compute an output arrival curve  $\alpha'_1$  (by convention, input curves are usually denoted as  $\alpha$  and output as  $\alpha'$ ). This output arrival curve is in turn used as the input for the second component (i.e.,  $\alpha_2 = \alpha'_1$ ). If the system is composed of N components, the analysis will require

Figure 1.3: Modular Performance Analysis

N computations on arrival curves. In case of cyclic dependencies, a fixpoint can be computed iteratively [JPTY08].

Originally, the analysis of a component within MPA was done in a purely analytic manner, using Real-Time Calculus formulas. When the component is simple enough (e.g., greedy processing element, which processes events as fast as possible given the available resource, and stores unprocessed elements in a FIFO buffer), this approach can provide optimal hard bounds, for a low algorithmic complexity. Unfortunately, a limitation of pure RTC is that it cannot handle the notion of state within a component. Our goal when we started using MPA was to handle performance in a more general way than only timing, in particular to be able to deal with power consumption. Before thinking about extending RTC with power consumption properties, the very first step was to deal with the timing of power-managed components, i.e., components that can be switched off or put in some degraded mode to reduce their consumption. This kind of state-based specification cannot be handled directly by Real-Time Calculus.

An alternative to pure RTC is to analyze individual components using more expressive analysis technique, typically using an automata-based formalism and some state-space exploration techniques such as model-checking. This can be done within the MPA framework if the state-based analysis can use arrival curves as input, and produce arrival curves. This kind of approach has been experimented with a dedicated automaton formalism called *event-count automata* [PCTT07], and adapted to traditional *timed automata* [Upp07, LPT09, LPT10]. The idea is to write adapters from RTC to the automata-based formalism: on the way out of RTC, the arrival curves are compiled into automata that produce the set of event streams specified by arrival curves, and on the way back to RTC, an observer computes the minimum and maximum number of events over a time interval. The analysis of one component can be done using expensive model-checking algorithms, but it should be noted that the analysis of individual components is done individually, hence the overall complexity still grows linearly with the number of components, although it may grow exponentially with their size.

#### **Contributions in the Area of Non-Functional Properties**

The contributions to the Modular Performance Analysis theoretical framework improve the connection from RTC to state-based formalisms following two directions:

- We provide two new connections from RTC to state-based formalisms and tools. We improve existing approaches for the connection to timed automata and the Uppaal [LPY97] model-checking tool, allowing some granularity-based abstractions for better performance, and provide a connection to the Lustre language, which allows using abstract interpretation and Satisfiability Modulo Theory (SMT) tools to analyze modules within MPA. These contributions will be presented in Sections 5.3 and 5.2, and led to the publications [ALM10, AM10a].

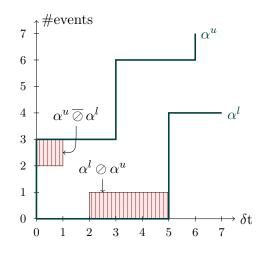

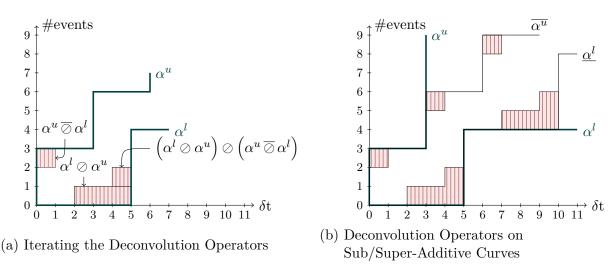

- We identified and defined formally the *causality problem* in Real-Time Calculus. This problem occurs when the upper and lower curves of a pair of arrival curve provide conflicting constraints (e.g., specify a stream that must emit at least 4 events, but at most 3 in a given time window). We explain why the MPA framework did not have to deal with the causality problem with traditional pure-RTC analysis, and how it is problematic when connecting to some other formalisms. We provide a transformation called the *causality closure* that allows getting rid of these conflicting constraints. The causality closure is first defined for the most general case, and then issues specific to some particular classes of curves are solved. This contribution will be presented in Section 5.4.1 and has been published in [AM10b, AM11].

### **1.3** Organization of the document

The document is organized in two parts. The first part deals with functional properties and their verification in several contexts: we first present verification techniques for general-purpose programs in Chapter 2, and present some uses of verification tools and new compilation techniques in the context of SystemC/TLM in Chapter 3. The second part presents some work on non-functional properties. Chapter 4 deals with time, power consumption, and temperature of systems-on-chips modeled at the TLM level. Chapter 5 presents our contributions on modular performance analysis with real-time calculus, which are very abstract models used to derive timing properties.

CHAPTER 1. INTRODUCTION

# Part I Functional Properties

# Chapter 2

# Verification and Abstract Interpretation

Any sufficiently advanced bug is indistinguishable from a feature.

Rich Kulawiec

This chapter presents the work on verification of general-purpose languages. They range from simplistic tools that only reproduce some well-known verification methods to new techniques, combining or improving recent advances in static analysis. One point they have in common is that all the tools deal with common programming languages, as opposed to formal languages specifically designed to be verified. In practice, some of the tools do have limitations and manage only a subset of the language being studied, but the subset is always large enough to verify at least small programs, without any human intervention and manual translation, following Gérard Berry's *WYPIWYE* (What You Prove Is What You Execute) principle [Ber89].

The next section starts with some simple experiments to implement traditional verification techniques in some particular contexts (as part of short internships). The reader familiar with abstract interpretation and model-checking may want to skip to Section 2.3.2 where recent advances in abstract interpretation are presented. Finally, Section 2.4 present new techniques that combine and improve state-of-the-art abstract interpretation.

### 2.1 Abstract Interpretation of Java Sequential Programs

Our first goal was to apply static analysis on Java programs, which was done during the internship of Loic Crétin, co-supervised by David Monniaux and myself. One nice property of Java in this context is that it is a "safe" language, in the sense that "segmentation faults" and most undefined behavior that are common in C are avoided by construction in Java (forced variable initialization, no pointer arithmetic...). Dealing with a general purpose language however has a cost, since writing a Java compiler front-end from scratch alone would have been longer than the time allocated to the internship. It was therefore clear that we had to maximize code reuse, and most technical constraints derived from this. This emphasis for code reuse can be seen as a technical constraint, but it also has an interesting side effect: it forced us to focus on the fundamental concepts of abstract interpretation, and delegate any technical detail to other tools.

We clearly needed a front-end that could make an intermediate representation easily available. We have chosen to reuse the Java front-end of the Eclipse IDE, by implementing the analyzer as an Eclipse plugin: refactoring tools and smart completion rely on the fact that the IDE permanently has access to the Abstract Syntax Tree (AST) of the program being edited, and this AST is made available to plugins. Also, we obviously didn't want to re-implement a non-trivial abstract domain. The Apron library [JM09] provides a nice abstraction layer on top of several abstract domains. The caller of the library only uses abstract operators, and the library decides on the abstract domain implementation. Since Apron is written in C, this forced us to use a bridge between Java and C, for which we chose Java Native Access (JNA).

On the theoretical point of view, one (unusual) choice was to work on the abstract syntax tree of the program directly, instead of working on a control-flow graph as most abstract interpretation tools do. This choice was partly inspired by the implementation of ASTREE [CCF<sup>+</sup>05] analyzer. One obvious advantage is that the AST was already available, and using it directly avoided the need for another intermediate format. The approach has more subtle advantages: it makes the iteration over the program a very simple recursive tree traversal (while the order in which control points should be visited in control-flow based abstract interpretation is a non-trivial issue), and can be more efficient in terms of memory, since the abstract values associated with program points can be stored in local variables, and freed when the analysis of a part of the program is completed. On the cons side, working on the AST forces a well-structured program: goto statements would be hard to deal with, but this is not a problem in Java where this construct does not exist.

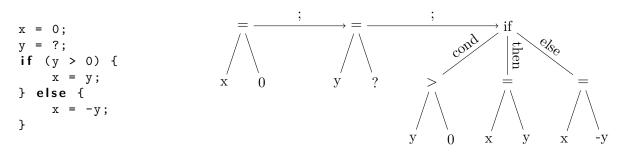

Figure 2.1 shows an example program with its abstract syntax tree. We use ? to represent non-determinism (i.e., "y = ?" can yield any value for y). We explain the behavior using the intervals abstract domain. Clearly, while the analysis will not discover any property on the value of y, it does discover  $x \ge 0$  at the end of the program (we work with mathematical, unbounded integers, although the actual semantics would be modulo  $2^n$  in Java).

Figure 2.1: Example Program and Abstract Syntax Tree

The management of sequence (; in the code and AST) is done the usual way. The if statement is analyzed using Algorithm 1.

| Algorithm 1 Analysis of if statements                                                                  |

|--------------------------------------------------------------------------------------------------------|

| function ANALYZE(IfStatement tree, $I_{precondition}$ )                                                |

| $I_{cond} \leftarrow \texttt{ANALYZE}(\texttt{tree.cond})$                                             |

| $I_{then} \leftarrow \text{ANALYZE}(\texttt{tree.then}, I_{precondition} \sqcap I_{cond})$             |

| $I_{else} \leftarrow \text{ANALYZE}(\texttt{tree.else}, I_{precondition} \sqcap \text{not}(I_{cond}))$ |

| $\mathbf{return}  I_{then} \sqcup I_{else}$                                                            |

| end function                                                                                           |

Applied to our example, this computes  $I_{cond} = y > 0$ ,  $I_{then} = x \in (]0, +\infty[ \sqcap ] -\infty, +\infty[) = x \in ]0, +\infty[$  and  $I_{else} = x \in ([0, +\infty[ \sqcap ] -\infty, +\infty[) = x \in [0, +\infty[$ . It then derives the invariant  $I = I_{then} \sqcup I_{else} = x \in [0, +\infty[$  at the end of program. Note that the recursive calls to ANALYZE could be done on any tree, including nested **if**, **while**, ... (in the actual code, this uses a visitor design pattern, so there is one function ANALYZE per kind of node).

The management of loops requires a bit more work, but remains relatively simple too. The

pseudo-code is given in Algorithm 2:

One can see the fixpoint iteration, and the use of the *widening* operator  $\nabla$  instead of an abstract union  $\sqcup$  to enforce convergence. The widening operator satisfies by definition  $x \sqsubseteq x \nabla y$ ,  $y \sqsubseteq x \nabla y$  and for any sequence  $x_n$ , the sequence  $y_n$  defined by  $y_0 = x_0$  and  $y_{n+1} = y_n \nabla x_{n+1}$  converges in a finite number of steps.

Interestingly, with this implementation, the wording "abstract interpretation" is really meaningful since the implementation is very similar to the one of a *concrete* interpreter, but manipulating abstract values.

This small tool was essentially an exercise in style, but it was interesting to show that a static analyzer for a reasonable subset of a real-language could be developed in a few hundred lines of code. Small variants of the analysis algorithm can be implemented quickly too, for example, implementing a narrowing iteration to increase the precision basically consists in adding one more application of the transition function before the **return** statement of Algorithm 2.

One unfortunate lesson to learn from this experience though is that code reuse can also lead to many technical complications. Depending both on Eclipse's plugin API and on C code was probably a mistake as it brought us the technical issues of multi-language programming, and we probably spent more time fighting against bugs of the tools we used than on real theory.

### 2.2 Model-checking Concurrent Java Programs

The year after, we offered a similar internship to Romain Salles. The goals were similar to the one of Loic Crétin, in that it was essentially an exercise to understand the basics of formal verification. Learning from our past experience, we avoided heavyweight dependencies, to avoid too much distraction due to purely technical issues. On the other hand, we kept the idea of working on a general purpose language and the choice of Java. This time, we experimented model-checking of concurrent Java programs.

Clearly, writing a new model-checker was out of reach given the time limitations, so we opted for a translation-based approach: compile the program to be verified into the input language of an existing verification tool. In this case, the verification tool was NuSMV [CCG<sup>+</sup>02], a tool inspired from SMV [McM93] offering several symbolic model-checking algorithms.

Again, we didn't want to write our own compiler front-end. We decided to verify the Java byte-code instead of working on the source code (or an abstract representation like an AST). First, verifying the byte-code can give more guarantees because it gives sound results even in the presence of compiler bugs. Also, working on byte-code is sometimes easier since syntactic sugar in the source code has already been lowered to simpler constructs. The *ObjectWeb ASM* Library [BLC02] allowed us to easily read and manipulate Java bytecode.

The choice of bytecode as input language however had a drawback: Java's bytecode is stackbased, and we cannot encode an unbounded stack in NuSMV. Recovering the expression abstract tree from the bytecode would be possible but non-trivial, so we chose the brute-force approach, by computing statically a bound on the size of the stack (which is easy since we do only intraprodecural analysis), and encode the stack as a static array of variables (in our case, an array of Boolean variables since we dealt only with Booleans).

The tool was able to model-check Dekker's mutual exclusion algorithm. It is clearly limited in the accepted subset of Java as input language, and also makes a naive approximation of the underlying memory model: the program makes the assumption that memory accesses are all atomic and immediately visible to other threads. The Java memory model is indeed more relaxed (operations are not atomic, and they are guaranteed to be visible by others only after an explicit synchronization).

### 2.3 From Bounded Model-Checking to Abstract Interpretation

#### 2.3.1 Bounded Model-Checking

Continuing on the series, we offered an internship on the development of a small model-checker based on SAT-solving (Julien Henry's Master I). We considered only loop-free functions, and intra-procedural analysis, so the problem was decidable by construction (i.e., we did not have to bound the size of execution explicitly). We used LLVM [LA04] as a compiler infrastructure, which allowed us to take C, C++ or even Ada as input language: the LLVM front-ends (clang or llvm-gcc) could be used as independent, external tools, to generate the LLVM bitcode. The LLVM bitcode is the intermediate format, available in either human-readable form, binary file, or data structure.

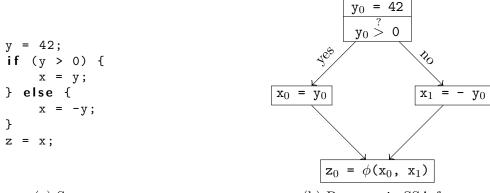

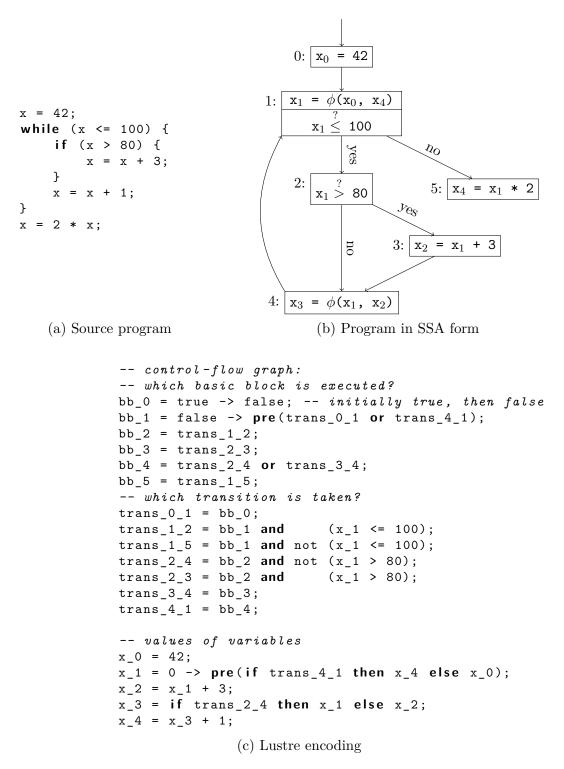

It is in *Static Single Assignment (SSA)* [CFR<sup>+</sup>91] form. This means that a succession of assignments on the same source variable like the one in Figure 2.2.(a) is translated into a set of assignments on multiple versions of the variable, as is done in Figure 2.2.(b).

| x = 0;             | $x_0 = 0;$              |

|--------------------|-------------------------|

| x = 42;            | $x_1 = 42;$             |

| x = x + 1;         | $x_2 = x_1 + 1;$        |

| (a) Source program | (b) Program in SSA form |

Figure 2.2: Static Single Assignment (SSA) example

This makes the encoding into a SAT or SMT formula straightforward for most constructs: each SSA variable takes only one value during an execution of the code, so the translation into SMT problem can basically create one SMT variable per SSA variable.

The if statements require some attention. The encoding into SSA already converted conditionals into a *Control-Flow Graph (CFG)* as illustrated by Figure 2.3. Control-flow splits are done by a conditional jump at the end of a basic-block. Control-flow joins use the special  $\phi$ instruction to get the value from the right incoming branch.  $\phi(x_0, x_1)$  reads simply as "if the control comes from the first incoming branch, then return  $x_0$  else return  $x_1$ ".

The encoding as an SMT problem uses one SMT Boolean variable  $b_i$  per basic block.  $b_i$  is true if the path considered goes through the basic block *i*. Then,  $\phi$  statements can be encoded as **if** statements over  $b_i$  variables. For example, the program in Figure 2.3 is encoded in the logic formulas of Figure 2.4.

Loops (or generally, any edge going backward in the control flow) cannot be directly encoded with this scheme. A loop unrolling could have been used (like CBMC [CKL04]) to perform bounded-model checking, that is, prove that no property violation can occur in less than N loop iterations for a given N. This wasn't done by lack of time, and because the encoding could be

(a) Source program

(b) Program in SSA form

Figure 2.3: SSA and Conditional Statements

| $y_0 = 42$                                                        | $\wedge b_0 = true$                |

|-------------------------------------------------------------------|------------------------------------|

| $\wedge x_0 = y_0$                                                | $\wedge b_1 = y_0 > 42$            |

| $\wedge x_1 = -y_0$                                               | $\wedge b_2 = y_0 \le 42$          |

| $\wedge z_0 = \text{if } b_1 \text{ then } x_0 \text{ else } x_1$ | $\wedge b_3 = b_1 \text{ or } b_2$ |

Figure 2.4: Encoding of the Program as SMT formula

used as a building block of an abstract interpreter without having to deal with loops, as we will show in the next section.

#### 2.3.2 State of the Art Abstract Interpretation

In parallel with the work on bounded-model checking, we worked with Marc Pégon on abstract interpretation, also using LLVM. The result was a tool implemented using a modern framework able to deal with a reasonable subset of C, but using only traditional abstract interpretation techniques. Then, the work continued with Julien Henry's Master II, in which we caught up with state-of-the-art abstract interpretation techniques, still using LLVM. In addition to the traditional abstract interpretation, two techniques were implemented in a tool called *PAGAI*: guided static analysis and path focusing.

```

1

void rate_limiter() { // (s)

2

int x_old = 0;

3

while (1) { // (l)

4

// non-deterministic number between -100000 and 100000

int x = input(-100000, 100000);

5

\mathbf{6}

if (x > x_{old}+10) x = x_{old} + 10;

7

// (m)

8

if (x < x_{old} - 10) x = x_{old} - 10;

9

x_old = x;

10

// do nothing any number of times

while (wait()) {} // (w)

11

12

}

}

13

```

Figure 2.5: Motivating example: a rate limiter in C

As a motivating example, consider the C program in Figure 2.5, implementing a rate-limiter.

This program has several specificities that make it hard to analyze with traditional abstract interpretation:

- 1. It contains two related if statements in sequence. A naive analysis will have to perform an abstract union at the control-flow merge (labeled (m)) in between. As a result, the values obtained from the first "then" branch are used in the analysis of the second "then" branch, even though the path where both if statements enter the "then" branch is infeasible.

- 2. It contains a nested while loop (line 11), which makes the narrowing inefficient.

#### **Guided Static Analysis**

Guided static analysis [GR07] performs the traditional ascending and narrowing iterations on a subset of the CFG, and then considers larger subsets. The analysis terminates when the subgraph cannot grow anymore. The narrowing iterations are applied at each intermediate steps of the analysis, before considering a new subgraph. It can recover precision that would have been impossible to recover at the end of the analysis. In the example above, issue 2 makes narrowing ineffective. Guided static analysis alone is not sufficient in this case, but the combined technique presented below solves the problem (by never including this transition in the subgraph, since it is not needed to make the invariant grow). Typically, a widening operator can activate infeasible transitions, but guided static analysis avoids propagating the precision before applying one narrowing sequence. Guided static analysis avoids propagating the precision loss of the widening operator to the whole CFG by applying it on a subset.

#### Path Focusing

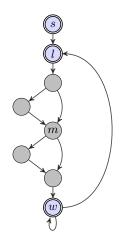

Path focusing [MG11] can improve precision by avoiding unnecessary abstract unions operations at control flow merges (issue 1 above). In traditional abstract interpretation, abstract unions are computed after each if/then/else construct, resulting in loss of precision if the union of abstract values cannot be represented exactly by an abstract value (e.g., if the union is not convex when working with polyhedra, a convex hull has to be computed). Instead of working on the control flow graph (CFG), path focusing works on the expanded multigraph: it considers only a subset of control points  $P_R$  (typically, loop heads), and paths from one point of  $P_R$  to another as edges of the multigraph. The expanded multigraph of the rate-limiter is shown in Figure 2.6.

(a) Control Flow Graph

(b) Expanded multigraph

Figure 2.6: CFG and multigraph for the rate-limiter with  $P_R = \{s, l, w\}$

#### 2.4. NEW ABSTRACT INTERPRETATION TECHNIQUES

The multigraph can be exponentially larger than the source program, but is never represented explicitly. Instead, it is modeled as an SMT formula that we call the *implicit multigraph*. The algorithm queries the SMT solver "is there a path starting from the current invariant candidate that would make the invariant grow?". In other words, it asks for the existence of a path pthat starts from the invariant candidate, complies with the semantics of the program, and ends outside the invariant candidate. If the query is satisfiable, the SMT solver provides a model that can be interpreted as a path between  $P_R$  points, and the corresponding abstract transformation is applied on this path. If the query is unsatisfiable, then the analysis has already reached the fixpoint, and the invariant candidate is actually an invariant.

### 2.4 New Abstract Interpretation Techniques

At the start of Julien Henry's Ph.D, the tool PAGAI was implementing state-of-the-art abstract interpretation techniques, including guided static analysis and path focusing that were never experimented on real programs before, but included no new techniques. Experiments showed that path focusing and guided static analysis could both provide tighter invariants, but in different cases. PAGAI was then improved to combine both techniques and to compute disjunctive invariants, i.e., compute the invariant as a list of abstract values at each program points (which can avoid abstract unions that would lose information) [HMM12b].

#### 2.4.1 Combining Path focusing and Guided Static Analysis

The combined algorithm of PAGAI uses SMT queries to perform the analysis on the implicit multigraph (like path focusing), but works on an ascending sequence of multigraphs like guided static analysis. An overall view of the algorithm can be found in Algorithm 3.

```

Algorithm 3 Overall view of the combined algorithm

1: A' \leftarrow initial locations \triangleright Points in P_R than may be the starting point of new feasible paths

\triangleright Points in P_R that may be the source of an interesting path

2: A \leftarrow \emptyset

3: P \leftarrow \emptyset

\triangleright Paths in the current subset

4: while A' \neq \emptyset do

▷ Compute a larger sub-multigraph

repeat

5:

Compute new path starting from A'

\triangleright Updates A, A' and P

6:

until A' = \emptyset

7:

repeat

\triangleright Ascending iterations on sub-multigraph P

8:

9:

Get and remove p_i from A

for all path (p_i \rightarrow p_j) that can make the p_j invariant grow do

10:

Update invariant of p_j

11:

Add p_i to A and A'

12:

end for

13:

until A = \emptyset

14:

Perform narrowing iterations on P

15:

16: end while

```

The outer loop iterates over the ascending sequence of multigraphs. Like guided static analysis, the algorithm makes it possible to run a narrowing sequence on a sub-multigraph before analyzing new paths. The inner loop lines 8-14 essentially applies path focusing to the sub-multigraph P.

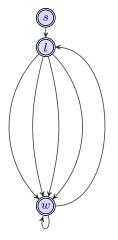

On the example of the rate-limiter of Figure 2.5, the analysis would compute the ascending

Figure 2.7: Ascending sequence of sub-multigraphs

sequence of sub-multigraphs of Figure 2.7: initially, the multigraph is empty  $(P = \emptyset, Figure 2.7.(a))$ . Then, a set of 3 "interesting paths" are computed (Figure 2.7.(b)).

"interesting paths" are paths that are not yet in P, and that can make the candidate invariant grow with a single iteration. They are computed using SMT solving. Initially, the only interesting path is  $(s \rightarrow l)$ , which yields the candidate invariant  $\mathbf{x}_{old} = 0$  at program location l. Then, there are several interesting paths from l to w, and the SMT solver may return any of them. If it returns the path going through both "else" branches of the if statements, then the candidate invariant at w will be  $\mathbf{x}_{old} \in [-10, 10]$ . The self-loop around w is not considered as it does not make the invariant grow. The back edge from w to l makes the invariant grow at land is therefore added to the sub-multigraph. Other transitions from l to w are not considered as they would not make the invariant grow.

Then, path focusing ascending iterations are computed on the sub-multigraph, and narrowing is applied to recover precision. Since the self-loop is not considered, the narrowing can recover  $x_old \in [-10000, 10000]$  at points l and w. No other interesting path are found afterwards so the analysis terminates.

#### 2.4.2 Disjunctive Invariants

Another contribution of PAGAI is the ability to compute *disjunctive invariants*. The traditional abstract interpretation algorithm computes one invariant at each program point. When two candidate invariants are computed for the same point, an abstract union is performed to merge them into one. Instead, we keep the union symbolic by computing a list of *disjuncts*: each program point  $p_i$  is associated with m disjuncts  $X_{i,j}$  for  $j \in \{1, \ldots, m\}$ , representing the invariant  $\bigvee_{j \in \{1,\ldots,m\}} X_{i,j}$ . An algorithm had been proposed earlier [GZ10], but relied on an exhaustive enumeration of path. PAGAI improves the existing algorithm by using SMT queries instead of an enumeration.

The idea shared between [GZ10] and the algorithm in PAGAI [HMM12b] is to store a list of disjuncts for each program points. The number of elements in the list is bounded by a fixed number M, chosen a priori. Instead of considering paths from a program location to another, the analysis considers paths from a disjunct  $X_{i,j}$  to another. When considering path number kstarting from  $X_{i,j}$ , with destination state  $p_{i'}$ , the value computed along the path is merged in the disjunct  $X_{i',\sigma_i(j,k)}$ . In other words, the mapping function  $\sigma$  returns the target disjunct into which the new abstract value should be merged. The  $\sigma$  function can be computed on the fly during the analysis: the analysis starts with an undefined  $\sigma$ . When the value  $\sigma_i(j,k)$  is required but undefined, the analysis computes the image of  $X_{i,j}$  by the path, and tries to find a target disjunct where the abstract union would not lose information. If no such disjunct is found, then we set  $\sigma_i(j, k)$  to either a fresh disjunct (if less than M disjuncts have already been allocated),

Figure 2.8: Experimental Results of PAGAI

or to the m-th disjunct.

Interestingly, the idea of using SMT queries to find interesting paths also applies to disjunctive invariant computations. Not only the choice of the path to consider can use SMT, but the computation of  $\sigma$ , and the choice of the source disjunct to be used can also benefit from it. The formulas submitted to the SMT solver are a bit more complex than the ones used for path focusing and the combined algorithm of Section 2.4.1, as they have to quantify also on the source and target disjunct ("is there a source disjunct for which one of the target disjuncts would grow?" instead of "is there path for which the target invariant would grow?"). Clearly, the analysis is slower, but experimental results show that the precision is improved in many cases [HMM12a].

#### 2.4.3 Real-Life Experimentations

PAGAI being implemented as an analyzer for LLVM bitcode, it can take any program accepted by the LLVM front-end. PAGAI has no model of the actual memory, and considers only LLVM registers (essentially, local variables and no pointers). However, memory accesses are abstracted in a sound way: **store** operations are ignored, and **load** operations return a non-deterministic value. The analysis on arbitrary code is therefore sound with only a few exceptions (integers and floating points variables are considered as mathematical integers and reals respectively).

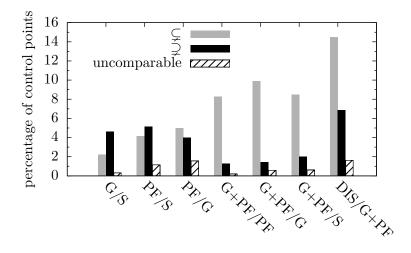

This allowed us to compare several techniques with the same tool, on real programs. Experimental comparison is necessary because all of the analysis are non-monotonic: being more precise at some point in the analysis can lead to loss of precision later (e.g., by triggering a widening), hence it is impossible for an algorithm to be strictly better than another. A summary of the comparison between techniques is shown in Figure 2.8. Techniques are classical abstract interpretation (S), *Guided Static Analysis* (G), *Path-focusing* technique (PF), our combined technique (G+PF), and its version with disjunctive invariants (DIS). The  $\subsetneq$  bars (resp.  $\supseteq$ ) gives the percentage of invariants stronger (more precise; smaller with respect to inclusion) with the left-side (resp. right-side) technique, and "uncomparable" gives the percentage of invariants that are uncomparable, i.e neither greater nor smaller; the code points where both invariants are equal make up the remaining percentage. For example, the entry "G+PF/G" shows that the combined analysis (G+PF) is better than guided static analysis alone in almost 10% of the cases (grey bar), worse in a bit more that 1% of cases (dark bar), and uncomparable in 0.6% of cases (hatched bar). The full comparison is available in [HMM12a].

The results show that state-of-the art techniques like guided static analysis and path focusing,

and the new proposed techniques can improve the precision in a few percent of the cases, but unsurprisingly, can also lose precision.

PAGAI is open-source and available from http://pagai.forge.imag.fr/. The real-life experiments showed the robustness of PAGAI: the tool can actually handle large and complex codebases. It has also been used by external teams to experiment new features like localized widening [AS13].

# Chapter 3

# Compilation and Verification for SystemC

Even perfect program verification can only establish that a program meets its specification. Much of the essence of building a program is in fact the debugging of the specification.

— Fred Brooks, No Silver Bullet (1986)