# A stepwise compositional approach to model and analyze system C designs at the transactional level and the delta cycle level

Nesrine Harrath

## ► To cite this version:

Nesrine Harrath. A stepwise compositional approach to model and analyze system C designs at the transactional level and the delta cycle level. Computers and Society [cs.CY]. Conservatoire national des arts et metiers - CNAM, 2014. English. NNT: 2014CNAM0957. tel-01142684

## HAL Id: tel-01142684 https://theses.hal.science/tel-01142684v1

Submitted on 15 Apr 2015

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## ÉCOLE DOCTORALE INFORMATIQUE, TÉLÉCOMMUNICATIONS ET ÉLECTRONIQUE de Paris (EDITE)

ÉQUIPE VESPA - LABORATOIRE CEDRIC LABORATOIRE U2IS - ENSTA ParisTech

## THESE DE DOCTORAT

présentée par : Nesrine HARRATH

soutenue le : 04 Novembre 2014

pour obtenir le grade de : Docteur du Conservatoire National des Arts et Métiers Discipline/Spécialité : Informatique

A Stepwise Compositional Approach to Model and Analyze SystemC Designs at the Transactional Level and the Delta

Cycle Level

### THÈSE DIRIGÉE PAR

| Prof. Kamel Barkaoui | Département Info, Cedric, Cnam Paris. |

|----------------------|---------------------------------------|

| Prof. Bruno Monsuez  | ENSTA ParisTech-U2IS.                 |

#### RAPPORTEURS

| Prof. Alain Merigot  | IEF, Université Paris-Sud.                             |

|----------------------|--------------------------------------------------------|

| Prof. Mohamed Shawky | Université de Technologie de Compiègne, Heudiasyc Lab. |

#### EXAMINATEURS

| Dr. Samia Bouzefrane   | Cedric, Cnam                                       | Examinatrice |

|------------------------|----------------------------------------------------|--------------|

| Prof. Zhiwu Li         | System Control Automation Group, Xidian University | Examinateur  |

| Prof. Pierre Paradinas | Cedric, Cnam                                       | Examinateur  |

| Dr. Franck Vedrine     | Institut Carnot, CEA LIST                          | Examinateur  |

#### Remerciements

Passage obligatoire mais sincère envers les personnes qui ont contribué de loin ou de prêt á la réussite de ce travail.

Je remercie sincèrement Mohamed Shawky et Alain Merigot pour avoir rapporté cette thèse. Je suis extrêmement reconnaissante pour leur travail et surtout pour leurs commentaires avisés et pertinents. Je suis aussi très honorée de compter comme membre de jury Pierre Paradinas, Samia Bouzefrane, Franck Vedrine et Zhiwu Li.

Je suis très réconnaissante envers mon co-directeur de thèse Bruno Monsuez avec qui j'ai travaillé pendant mon stage de master en 2009 et puis ma thèse. J'ai pris énormément de plaisir d'être une de ses doctorantes. Malgré ses engagements, il a su m'écouter, discuter avec moi et surtout avoir confiance en mes capacités.

J'ai une grande gratitude envers mon directeur de thèse Kamel Barkaoui qui m'a accueillie au sein de son équipe VESPA/CEDRIC au CNAM. Il m'a beaucoup aidée que ce soit à l'échelle professionnelle qu à l'échelle humaine. Je lui remercie aussi pour nos discussions sincères.

Je n'oublie pas tous mes collègues au laboratoire Informatique et Ingénierie des Systèmes à l'ENSTA ParisTech.

Un grand merci à tous mes collègues du travail à la RATP avec qui j'ai passé une agréable année, c'est grâce à leur soutien et bonne humeur que j'ai pu accomplir aisément et tranquillement ma dernière année de thèse : Khalid, Sebti, Nassim, Elena, Marie-Hélène.

Milles merci à ma chère Nayma, avec qui j'ai passé des moments de folie qui m'ont permise d'oublier mes moments de stress. *Muchas gracias*.

Un grand merci à ma très chère copine Nesrine et ses deux filles Alaa et Oumayma. A mes copines : Natalia, Catherine, Abir, Khawla, Islem, Souhair et Ouided. A Mondher, je te remercie, pour avoir supporté mes hauts et mes bas.

Pour finir, je tiens à remercier tous les membres de ma famille qui m'ont soutenue et supportée pendant ces trois ans...et qui le font depuis bien plus longtemps! A mes nièces et neveux : Wissal, Rabeb, Chahd, Ayoub, Adem, Mohamed, Tasnim, Dhia, Loujayn et Mohamed.

Je remercie particulièrement ma très chère maman Meriem qui y tient une place très importante dans ma vie.

Nesrine Harrath

Je dédie ce travail à ma mère Meriem, à la mémoire de mon père Mohamed et à la Tunisie, mon pays que j'aime.

## Résumé Détaillé

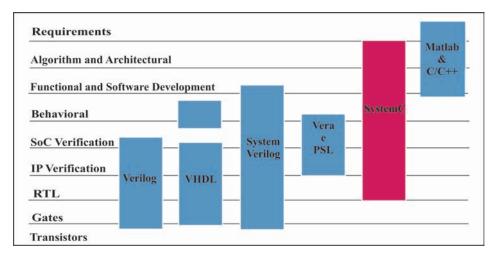

La conception des systèmes embarqués est une conception à la fois matérielle et logicielle. Traditionnellement, les composants logiciels d'un système sont écrits dans un langage de programmation comme C ou C++, alors que la partie matérielle est écrite dans un langage de description tels que VHDL ou Verilog. Cette approche a plusieurs inconvénients : tout d'abord, le concepteur était obligé d'apprendre et de comprendre plusieurs langages de programmation. De plus, au début du processus de la conception, il est souvent difficile de savoir laquelle des parties est à implémenter dans le matériel ou le logiciel. En outre, si la partition de la conception du matériel et du logiciel doit être modifiée plus tard, des coûts et des délais de conception s'ajoutent. Cela motive l'idée d'utiliser des langages uniformes de conception des systèmes afin de fournir la clarté, l'exhaustivité et l'exactitude lors du processus de la conception. Récemment, C et C++ ont été proposés comme base pour créer des spécifications exécutables. Toutefois, ces langages sont conçus pour l'écriture des programmes des ordinateurs, pas pour décrire les ordinateurs ou d'autres composants matériels. Par conséquent, ils ne possèdent pas des fonctionnalités et caractéristiques nécessaires pour décrire les horloges, les signaux, la réactivité et le traitement en parallèle. SystemC explore la première option, il a été récemment mis en place à partir de la librairie des classes C++ pour la conception de la spécification exécutable et de la simulation cycle accurate du hardware en C ++. C'est un support pour les données orientées hardware comme les modules, les ports et les signaux. En réalité, il y avait deux objectifs majeurs dans la conception SystemC :

- Fournir un seul langage qui permet la vérification des différents systèmes à différents niveaux d'abstraction.

- Permettre aux concepteurs des systèmes de décrire leurs modèles au niveau RTL, sans les traduire en un langage HDL.

Aujourd'hui, il existe des outils de haut niveau de synthèse des modules SystemC. Ceci a poussé l'industrie à adopter à grande échelle ce langage de conception matérielle-logicielle. En raison de ces caractéristiques, SystemC offre les avantages suivants :

- □ La spécification exécutable : un modèle écrit en SystemC peut être compilé et exécuté à la fois.

- □ Accélération de la simulation : SystemC est basé sur le langage C++, dont la vitesse de la simulation est élevée par rapport à d'autres langages comme VHDL ou Verilog.

- Un haut niveau d'abstraction : par rapport à des langages de description matérielle,

C++ a la capacité de modéliser des concepts très abstraits de façon élégante. Cette caractéristique est donc intègrée dans SystemC.

- □ Implémentation indépendente de l'architecture cible : un modèle présenté dans un langage de description matérielle est généralement spécifique pour une architecture bien définie. Cependant, un modèle décrit en SystemC peut être implémenté soit dans une partie matérielle soit logicielle.

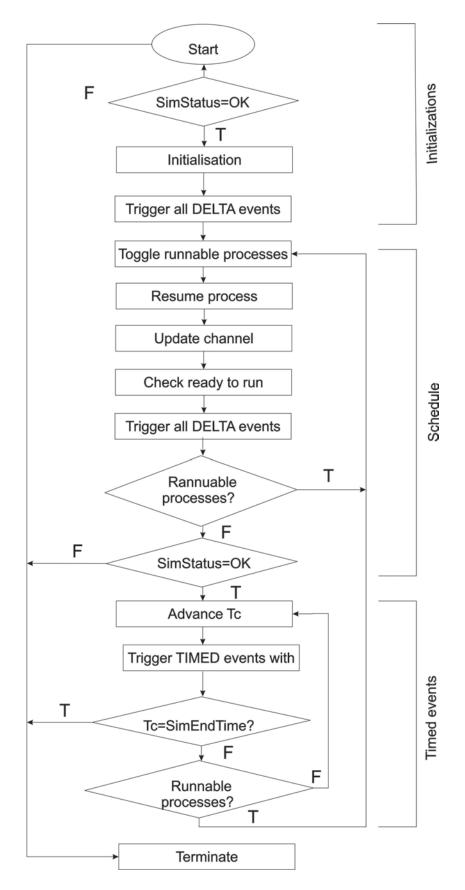

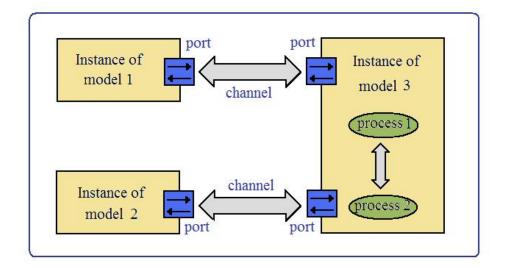

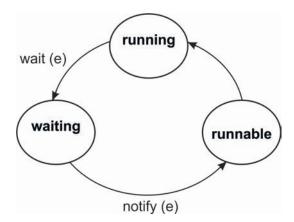

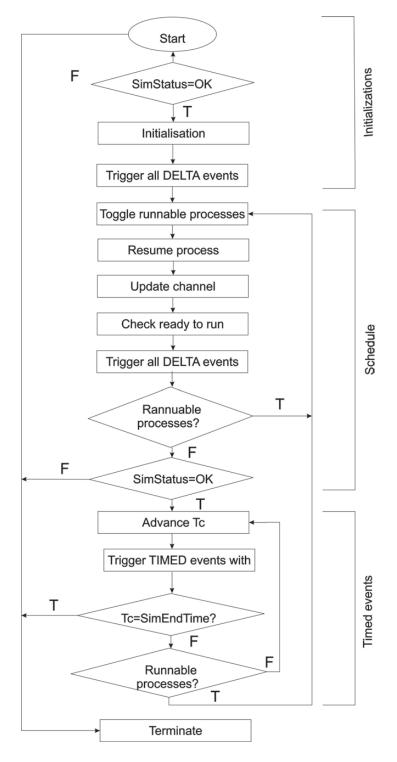

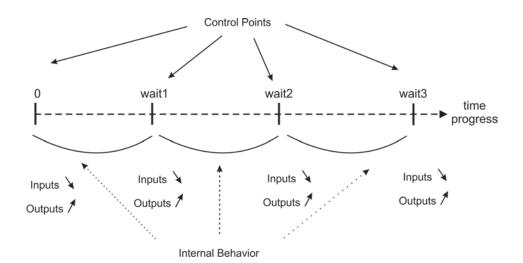

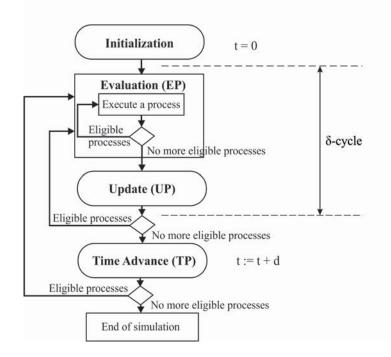

En outre, le simulateur SystemC introduit la notion importante du delta-cycle comme étant l'unité fondamentale de la simulation. L'ordonnanceur (Scheduler) SystemC peut être vu comme un moteur d'évènements : les communications à travers les ports et les canaux, les horloges et les actions des modules sont déclenchés par différents évènements. Le scheduler qui détermine l'ordre d'exécution des processus au sein de l'architecture et ce selon la liste des évènements de sensibilité des processus et les notifications d'événements qui se produisent. La sémantique de ce scheduler a été définie en utilisant les règles des ASM et des sémantiques dénotationnelles. L'unité de base de la simulation est le delta-cycle et une procédure de simulation est donc une séquence de delta-cycles. L'ordonnanceur gère plusieurs tableaux, parmi lesquels nous sommes particulièrement intéressés à la table des processus exécutables (runnable processes : processus qui sont prêts à être exécutés au cours du delta-cycle). Voici une

brève description d'un delta-cycle : un delta-cycle commence lorsque la table des processus exécutables est non vide. L'ordonnanceur exécute ces processus un par un, dans un ordre prédéfini. Chaque processus soit il s'exécute jusqu'à sa fin soit il est suspendu à nouveau (par une commande wait par exemple). Dans le cas où un évènement immédiat est notifié au cours de l'exécution d'un processus, l'ordonnanceur ajoute les processus qui sont actuellement sensibles à cet événement dans la table des processus exécutables. Les delta évènements et les évènements temporisés qui sont générés pendant l'exécution d'un processus seront stockés dans d'autres tables. La table des processus est vidée lorsque tous les processus sont exécutés, et la phase d'exécution de ces processus est appelée une phase d'évaluation. L'ordonnanceur détecte les delta évènements notifiés pendant la phase d'évaluation : s'il ya des processus qui sont sensibles à ces événements, alors il les ajoute à la table des processus. Cette procédure est appelée phase de delta-notification. Si la table des processus est non-vide, l'ordonnanceur entre au prochain delta-cycle et recommence la phase d'évaluation de nouveau. Autrement, il cherche les évènements temporisés qui sont notifiés pendant la phase d'évaluation et ajoute les processus qui sont sensibles à ces événements dans la table des procéssus. C'est ce qu'on appelle la phase de timed-notification. L'ordonnanceur incrémente ensuite le temps de la simulation et entre au prochain delta-cycle. Le processus de la simulation est affecté par l'initialisation des processus, leur exécution et leur ordre, l'activation des événements et les erreurs rencontrées lors de la simulation. La figure ci-dessous montre un diagramme de processus de la simulation en SystemC. En effet, une procédure de simulation peut être considérée comme une succession de delta cycles. Toutes les interactions au sein d'un delta cycle sont abstraites de la perspective de la modélisation. Une telle abstraction est censée fournir une garantie que l'ensemble de ces interactions devrait fonctionner correctement. Autrement dit, les analyses et les vérifications de plus haut niveau peuvent se faire sans prendre en considération ce qui se passe entre les delta cycles. Toutefois, cela est probablement le grand inconvénient de SystemC, comme l'espace du processus final à l'intérieur d'un delta cycle peut être très grand. Un problème typique est le lien de causalité entre les cycles d'attente des processus, qui provoque l'arrêt inattendu du système. En outre, l'accès aux ressources partagées peut mettre en cause des liens de compétitivité entre les processus et, par conséquent, tomber dans un comportement non-déterministe au niveau de delta-cycles. Néanmoins, ceci n'est certainement pas souhaitable dans la conception du matériel.

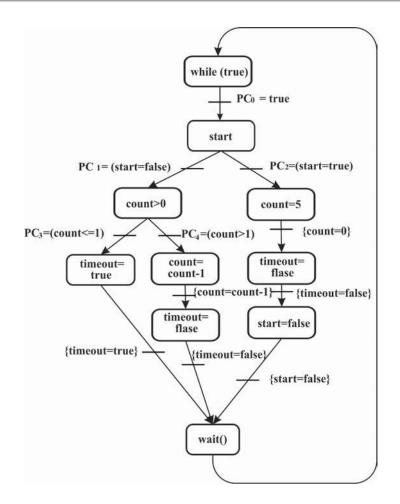

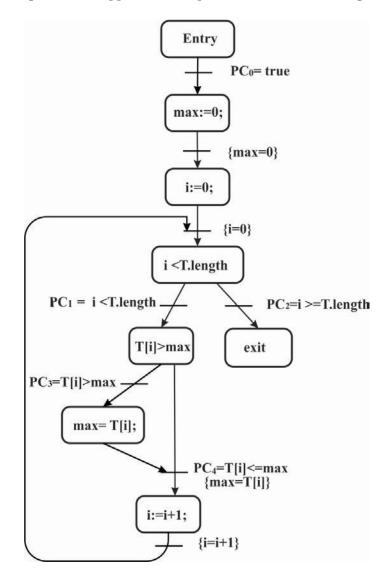

FIGURE 1 – Algorithme de la simulation de l'ordonnanceur SystemC.

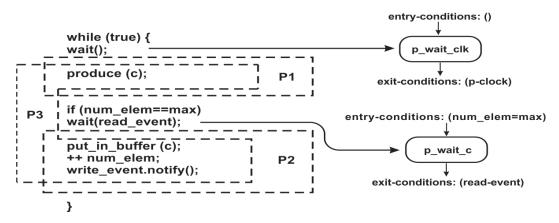

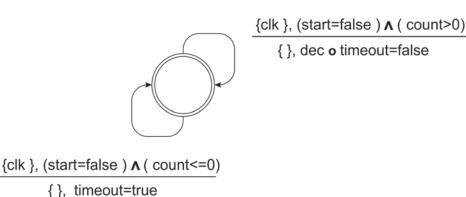

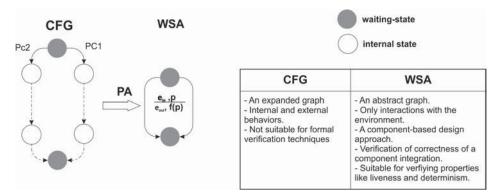

Pour résoudre ce problème, nous proposons une méthode de modélisation et de vérification des systèmes en utilisant le modèle des SystemC Waiting-State Automata. Ceci est basé sur le fait que la plupart des propriétés importantes dépend fortement de la manière dont les processus passent d'un état d'attente à un autre, qui est en effet contrôlé par l'odonnanceur. Nous proposons d'abord une manière de construire l'automate dit minimal de chaque processus, par l'analyse de ses états d'attente. Ensuite nous définissons des algorithmes pour la composition de l'automate du système global et des algorithmes de la réduction de manière à définir l'abstraction au niveau des delta-cycles. Ces algorithmes sont conformes au simulateur SystemC, qui définit la sémantique de l'exécution du langage. Les vérifications peuvent se faire à la fois au niveau de l'automate de chaque processus et au niveau de l'automate composé du système. Nous discutons aussi quelques extensions basées sur ce modèle, comme l'ajout de compteurs et de temps au niveau des transitions, de sorte que d'autres propriétés peuvent aussi être vérifiées.

Notre approche de vérification a deux objectifs :

- Assurer que l'introduction d'un nouveau composant ne compromet pas la correction du système initial (sans revérifier le système en entier).

- Détecter les problèmes liés à la composition des composants du système dont l'exécution peut s'avérer conflictuelle.

Plusieurs tentatives ont été faites pour modéliser des composants SystemC d'une manière formelle (un aperçu sur les travaux connexes est présenté au chapitre 6). Mais chacun d'eux a des restrictions et des limites : soit le modèle proposé décrit SystemC à un niveau d'abstraction plus bas (RTL ou cycle accurate) (par exemple le travail de Drechsler et Grosse [De02] and [De03]). Donc leur modèle ne permet pas de traiter le niveau transactionnel (TLM). Soit, ils ne supportent pas la notion de delta cycle : l'unité fondamentale de SystemC. En effet ces modèles ne peuvent pas faire face à des proprietés telles que la concurrence entre des composants parallèles et le temps continu (par exemple le travail de Kroening et Sharigina [KS05]).

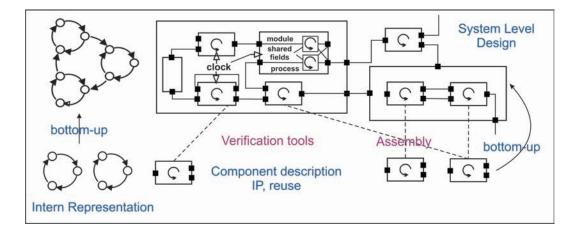

Le modèle du SystemC waiting state automata (WSA), comme présenté initialement par Zhang, Vèdrine et Monsuez dans [YZM07], supprime les contraintes précédemment mentionnées. Nous proposons d'utiliser ce modèle dans une approche bottom-up pour décrire les composants SystemC au niveau transactionnel et au niveau des delta cycles. Le modèle du SystemC WSA est basé sur l'analyse des instructions wait/notify en SystemC : mécanisme de base qui joue un rôle important dans la simulation en SystemC. Nous avons adopté la modélisation des systèmes complexes en utilisant les automates parce qu'ils permettent de modéliser le parallélisme entre différents composants. Ceci est essentiel surtout pour la description du matériel. Ce choix sera différent si nous modélisons des systèmes distribués composés de quelques composants hétérogènes communiquant en parallèle ou dans le cas de composants séquentiels. Bien que, les réseaux de petris par exemple, sont considérés comme étant plus appropriés pour gérer le parallélisme. Ils ont encore un problème considérable qui est l'explosion combinatoire du nombre d' états du système qui est significativement réduit dans notre modèle. Par ailleurs, d'autres inconvénients des réseaux de petris sont : d'une part, ils ne permettent pas la représentation du système à différents niveaux d'abstraction, plus précisément le niveau des delta-cycles. D'autre part, les réseaux de petris ne permettent pas d'exprimer des propriétés telles que le temps et les compteurs, qui permettent de représenter l'évolution dynamique du système comme on le fait dans le modèle des SystemC WSA.

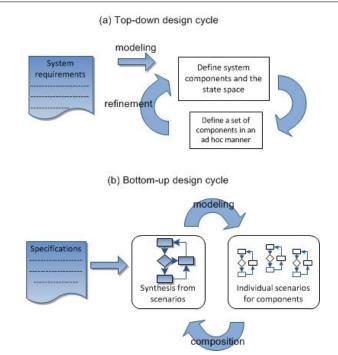

Dans cette thèse, nous adoptons une approche bottom-up interne basée sur le SystemC WSA en opposition à l'approche top-down (Chapitre 3) : l'approche commence à partir d'une description bas niveau des composants SystemC. Puis elle rassemble tous les composants afin de construire un modèle global pour l'ensemble du système. Mais avant de composer tous les composants ensemble, il est impératif de s'assurer que chaque composant vérifie bien les contraintes spécifiques et qu'il est en mesure d'introduire progressivement les concepts de qualité du service (Qos).

Il y a plusieurs motivations derrière l'utilisation des automates des SystemC WSA pour représenter les composants SystemC : premièrement, il est essentiel de donner une représentation interne de chaque composant du système en utilisant un système de transition d'état. Il est en effet plus facile de vérifier les propriétés sur les composants individuels plutôt que sur l'ensemble du système. Deuxièmement, donner une représentation finie d'un système infini est l'un des récents axes de recherche pour la modélisation des systèmes complexes. En outre, comme mentionné dans [YZM07, HM09, HM12], le modèle de SystemC WSA est conforme à la sémantique de simulation en SystemC car il représente le comportement des composants du système au niveau du delta cycle. En plus le modèle permet de représenter le système à différents niveaux d'abstraction du niveau système jusqu'au niveau des deltacycles. Le modèle permet aussi de séparer le comportement interne du comportement global de chaque composant qui est essentiel lors de la modélisation des systèmes parallèles. Ainsi, dans le modèle des SystemC WSA, on considère que les états où les composants sont en communication avec l'environnement. En conséquence, les états internes qui représentent les comportements locaux de chaque composant sont exclus lors de la représentation du système. Contrairement à d'autres modèles formels utilisés pour vérifier les composants SystemC tels que dans [AHT06, KS05, MFM06, KMS06], le modèle des SystemC WSA est différent car il considère que les interactions et les communications entre les processus et la façon dont ils sont gérés par le simulateur SystemC. Il suppose que le comportement d'un processus entre deux états d'attente est abstrait dans le modèle final.Le modèle représente deux informations principales :

- L'ensemble des conditions d'entrée qui activent et suspendent l'exécution d'un processus et l'ensemble des conditions de sortie qui sont générés.

- □ Les points de synchronisation qui représentent les instructions wait en SystemC. Ils sont utilisés pour synchroniser entre les processus communicants au niveau des delta-cycles.

L'idée principale derrière le SystemC WSA est de construire un automate pour chaque processus. l'automate est construit à partir de l'ensemble des états d'attente. Il est donc considéré comme une abstraction ou une représentation minimale du programme initial. C'est pour celà, on appelle chaque automate un automate minimal, nous allons utiliser cette notation tout au long de cette thèse.

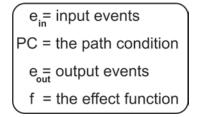

Le modèle des SystemC waiting-state automata (WSA) est un système de transitions Adéfini sur un ensemble de variables globales  $\mathcal{V}$ . C'est un triplet  $A = (S; E; \mathcal{T})$ , avec S est l'ensemble des états, E est l'ensemble des évènements et  $\mathcal{T}$  est l'ensemble des transitions. Chaque transition est un 6-uplet  $(s; e_{in}; p; e_{out}; f; s')$ :

- $\Box$  s et s' sont deux états dans S, ils représentent respectivement l'état initial et l'état final;

- $\Box$   $e_{in}$  et  $e_{out}$  sont deux évènements tels que :  $e_{in} \subseteq E$ ;  $e_{out} \subseteq E$ ;

- □ p est un prédicats défini sur les variables dans  $\mathcal{V}$ , i.e.,  $FV(p) \subseteq \mathcal{V}$ , avec FV(p) représente l'ensemble des variables libres dans p;

#### $\Box$ f est la fonction définie sur $\mathcal{V}$ ;

On note  $s \xrightarrow{e_{in}, p} s'$  pour chaque transition  $(s; e_{in}; p; e_{out}; f; s')$ . L'ensemble des fonctions  $\mathcal{F}(A)$  de l'automate A(V) est défini à partir des fonctions dans  $A(\mathcal{V}) : \mathcal{F}(A) = \{f | \exists t \in \mathcal{T}s.t. \ proj_6^5(t) = f\}$ , avec  $proj_6^5$  est la projection cinquième de la transition dans l'automate. On note aussi  $proj_6^1, \ proj_6^2, \ proj_6^3, \ proj_6^4, \ proj_6^6$  qui représentent respectivement l'état initial s, l'évènement d'entrée  $e_{in}$ , le prédicat p, l'évènement de sortie  $e_{out}$  et l' 'état de sortie s'.

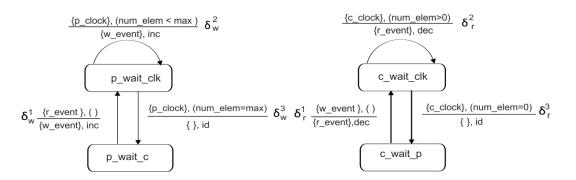

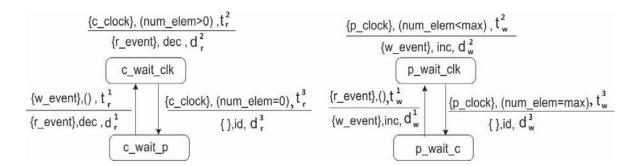

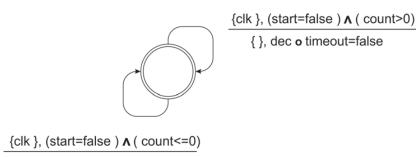

Ensuite, nous proposons d'étendre le modèle avec des paramètres tels que les informations temporelles et les compteurs. Les automates paramétrés sont utilisés pour étudier divers problèmes de synthèse. Ils sont également utilisés pour modéliser des programmes, dont le comportement dépendra des valeurs des entrées de l'environnement [RAV93]. Les paramètres sont également utilisés pour modéliser les ressources du modèle (tels que le temps, la mémoire) qui sont consommées par les transitions. Nous utilisons tout d'abord la première extension du modèle en utilisant les compteurs comme présenté dans [YZM07]. Les automates avec compteurs sont essentiellement utilisés pour modéliser les systèmes distribués et concurrents et pour vérifier les propriétés comme le problème d'accessibilité, vivacité et le déterminisme. Les auteurs dans [YZM07] utilisent les compteurs pour vérifier d'autres propriétés : déduire les relations entre les conditions d'entrée et les conditions de sortie au niveau de chaque transition du modèle. Dans cette thèse, nous reprenons la même définition des automates avec compteurs comme dans [YZM07]. Mais, nous développons d'avantages l'utilisation des compteurs sur l'automate, et nous spécifions quelques exemples par rapport l'utilisation du paramètre. De plus, nous étendons le modèle avec d'autres paramètres : les informations temporelles, ce qui n'a pas été fait dans le travail précédent. On note respectivement  $(\delta)$ , (t)et (d) le compteur, le temps de début de la transition associée et sa durée. Chaque paramètre est défini sur une transition :  $(\delta)$  représente le nombre de fois que la transition a été franchie, (t) est le temps de début d'exécution de la transition et (d) est la durée de la transition, une fois déclenchée.

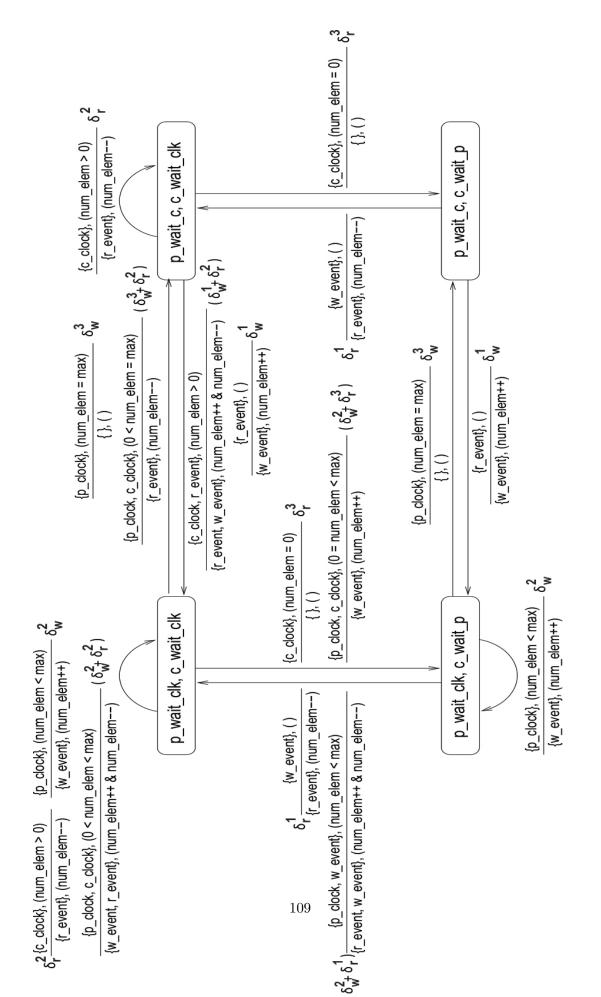

L'idée de notre approche est de définir d'abord un automate minimal pour chaque processus, puis de composer l'ensemble des automates afin de construire un automate pour le système global qui peut être finalement utilisé pour faire du model-checking. Nous procédons tout d'abord à la composition symbolique qui consiste à composer l'ensemble des états d'attente de tous les composants qui sont exécutés en parallèle afin de constuire l'automate du système global dans une approche bottom-up. En d'autres termes, les composants doivent synchroniser au niveau des états globaux et procéder de façon indépendante au niveau des états locaux. Néanmoins, la composition parallèle des composants SystemC peut provoquer des cycles de causalité entre les procéssus s'exécutant en parallèle . La vérification lors de la composition nécessite en premier lieu de détecter les états dits *unsafe* qui représentent les processus qui sont en attente mutuelle, dans le but d'avoir une analyse plus approfondie basée sur les automates. En outre, la composition symbolique des automates minimaux est récursive au sein de chaque module SystemC.

La composition symbolique des automates est aussi utilisée pour détecter le déterminisme au niveau du module : d'abord, on construit l'automate minimal pour chaque composant. Ensuite, tous les automates sont composés ensemble. Si l'automate composé ne contient pas des transitions non-déterministes, on peut confirmer que le modèle est déterministe. La détection des transitions non-déterministes peut être effectuée sans faire la composition. On peut simplement vérifier si  $f \circ f' = f' \circ f$ , où  $f \in \mathcal{F}(A)$ ;  $f' \in \mathcal{F}(A')$  (A, A' sont deux automates composés). Cependant, une telle détection n'est pas toujours possible surtout dans le cas où certaines transitions non-deterministes sont jamais déclenchées. En fait, de telles transitions peuvent être supprimées après la composition dans le cadre du raffinement de l'automate composé.

L'algorithme de la compostion symbolique est défini comme suit :

- $\Box (s_1, s'_1) \xrightarrow{e_{in}, p} (s_2, s'_1) \in \mathcal{T}" \text{ pour chaque état } s_1 \xrightarrow{e_{in}, p} s_2 \in \mathcal{T} \text{ et } s'_1 \xrightarrow{e'_{in}, p'} s'_2 \in \mathcal{T}', \text{ ou bien } e'_{in} \not\subseteq e_{in} \text{ ou } p \not\Rightarrow p'.$

- $\Box (s_1, s'_1) \xrightarrow[e'_{out}, f']{e'_{out}, f'} (s_1, s'_2) \in \mathcal{T}" \text{ pour chaque état } s_1 \xrightarrow[e_{out}, f]{e_{out}, f} s_2 \in \mathcal{T} \text{ et } s'_1 \xrightarrow[e'_{out}, f']{e'_{out}, f'} s'_2 \in \mathcal{T}', \text{ ou bien } e_{in} \not\subseteq e'_{in} \text{ ou } p' \not\Rightarrow p.$

$$\Box (s_1, s'_1) \xrightarrow{e_{in} \cup e'_{in}, p \wedge p'}_{e_{out} \cup e'_{out}, f \circ f'} (s_2, s'_2) \in \mathcal{T}" \text{ pour chaque état } s_1 \xrightarrow{e_{in}, p}_{e_{out}, f} s_2 \in \mathcal{T} \text{ et } s'_1 \xrightarrow{e'_{in}, p'}_{e'_{out}, f'} s'_2 \in \mathcal{T}'.$$

On a défini aussi les algorithmes de composition pour les automates étendus avec les compteurs et le temps. Ces algorithmes sont basés sur l'algorithme défini précédement mais qui étend aussi l'utilisation des paramètres de l'automate. En effet, on définit des morphismes qui définissent les relations entres les paramètres de l'automate composé en fonction des automates minimaux des composants. On représente ci-dessous les algorithmes de composition des automates étendus après ajout des différents morphismes :

- 1. Automates avec compteurs :

- $\Box \ \Pi(s_1, e_{in}, p, e_{out}, f, s_2, \delta) := \{\delta^*\} \bigcup \Pi(s_1, e_{in}, p, e_{out}, f, s_2, \delta) \text{ et } (s_1, s_1') \xrightarrow{e_{in}, M_c(p), \delta^*}_{e_{out}, f} \\ (s_2, s_1') \in \mathcal{T}'' \text{ pour chaque transition } s_1 \xrightarrow{e_{in}, p, \delta}_{e_{out}, f'} s_2 \in \mathcal{T} \text{ pour chaque état } s_1' \in S' \text{ tel} \\ \text{que pour chaque transition } s_1' \xrightarrow{e_{in}', p', \delta'}_{e_{out}, f', s_2'} s_2' \in \mathcal{T}', \text{ soit } e_{in}' \nsubseteq e_{in} \text{ ou } p \neq p', \\ \Box \ \Pi(s_1', e_{in}', p', e_{out}', f', s_2', \delta') \qquad := \qquad \{\delta^*\} \bigcup \Pi(s_1', e_{in}', p', e_{out}', f', s_2', \delta') \\ \text{et}(s_1, s_1') \xrightarrow{e_{in}', M_c(p'), \delta^*}_{(e_{out}', f')} (s_1, s_2') \in \mathcal{T}'' \text{ pour chaque transition } s_1' \xrightarrow{e_{in}, p, \delta'}_{e_{out}, f'} s_2' \in \mathcal{T}' \text{ et} \\ \text{pour chaque état } s_1 \in S \text{ tel que pour chaque transition } s_1 \xrightarrow{e_{in}, p, \delta}_{e_{out}, f} s_2 \in \mathcal{T}, \text{ soit} \\ e_{in} \nsubseteq e_{in}' \oplus e_{in}'$

- $\Box \Pi(s_1, e_{in}, p, e_{out}, f, s_2, \delta) := \{\delta^*\} \bigcup \Pi(s_1, e_{in}, p, e_{out}, f, s_2, \delta)$ et  $\Pi(s'_1, e'_{in}, p', e'_{out}, f', s'_2, \delta') := \{\delta^*\} \bigcup \Pi(s'_1, e'_{in}, p', e'_{out}, f', s'_2, \delta')$ et  $(s_1, s'_1) \xrightarrow{e_{in} \bigcup e'_{in}, M_c(p \wedge p'), \delta^*}_{e_{out} \bigcup e'_{out}, f \circ f'} (s_2, s'_2) \in \mathcal{T}'',$ pour chaque pair de transitions  $s_1 \xrightarrow{e_{in}, p, \delta}_{e_{out}, f} s_2 \in \mathcal{T}$ et  $s'_1 \xrightarrow{e'_{in}, p', \delta'}_{e'_{out}, f'} s'_2 \in \mathcal{T}'.$

- □ En ce qui concerne la transition  $(s_1, e_{in}, p, e_{out}, f, s_2, \delta_{s_1}^{s_2})$ , le morphisme  $M_c$ mappe le compteur  $\delta$  à la somme des compteurs des transitions dans  $\Pi(s_1, e_{in}, p, e_{out}, f, s_2, \delta)$

$$M(\delta) \to \sum_{\delta^* \in \Pi(s_1, e_{in}, p, e_{out}, f, s_2, \delta_{s_1}^{s_2})} \delta^*.$$

- 2. Automates temporisés :

- $\Box \ \Pi(s_1, e_{in}, p, t, e_{out}, f, d, s_2) := \{t^*, d^*\} \bigcup \Pi(s_1, e_{in}, p, t, e_{out}, f, d, s_2)$ et  $(s_1, s_1') \xrightarrow{e_{in}, M_t(p), M_d(p), t^*}_{e_{out}, f, d^*} (s_2, s_1') \in \mathcal{T}'' \text{ pour chaque transition } s_1 \xrightarrow{e_{in}, p, t}_{e_{out}, f, d} s_2 \in \mathcal{T} \text{ et}$ pour chaque état  $s_1' \in S'$  tel que pour chaque transition  $s_1' \xrightarrow{e_{in}', p', t'}_{e_{out}, f', d', s_2'} s_2' \in \mathcal{T}',$ soit  $e_{in}' \not\subseteq e_{in}$  ou  $p \not\Rightarrow p'$ ,

- $\Box \Pi(s'_1, e'_{in}, p', t', e'_{out}, f', d', s'_2) := \{t^*, d^*\} \bigcup \Pi(s'_1, e'_{in}, p', t', e'_{out}, f', d', s'_2) \text{ et} \\ (s_1, s'_1) \xrightarrow{e'_{in}, M_t(p'), M_d(p'), t^*}_{e'_{out}, f', d^*} (s_1, s'_2) \in \mathcal{T}'' \text{ pour chaque transition } s'_1 \xrightarrow{e'_{in}, p', t'}_{e'_{out}, f', d^*} s'_2 \in \mathcal{T}' \\ \text{et pour chaque état } s_1 \in S \text{ tel que pour chaque transition } s_1 \xrightarrow{e_{in}, p, t}_{e_{out}, f, d} s_2 \in \mathcal{T}, \text{ soit} \\ e_{in} \nsubseteq e'_{in} \text{ ou } p' \nrightarrow p, \end{cases}$

- □ Pour chaque transition  $(s_1, e_{in}, p, t_{s_1}^{s_2}, e_{out}, f, d_{s_1}^{s_2}, s_2)$ , le morphisme  $M_t$  mappe les temps de début t au *min* des temps de début des transitions dans  $\Pi(s_1, e_{in}, p, t, e_{out}, f, d, s_2)$

$$M(t) \rightarrow min_{t^* \in \Pi(s_1, e_{in}, p, t, e_{out}, f, d, s_2)} t^*$$

□ Pour chaque transition  $(s_1, e_{in}, p, t_{s_1}^{s_2}, e_{out}, f, d_{s_1}^{s_2}, s_2)$ , le morphisme  $M_d$  mappe les durées d à la somme des durées définies dans  $\Pi(s_1, e_{in}, p, t, e_{out}, f, d, s_2)$

$$M(d) \to d \ge \sum_{d^* \in \Pi(s_1, e_{in}, p, t, e_{out}, f, d, s_2)} d^*.$$

- 3. Automates avec temps et compteurs :

- $\Box \Pi(s_1, e_{in}, p, t, \delta, e_{out}, f, d, s_2) := \{t^*, d^*, \delta^*\} \bigcup \Pi(s_1, e_{in}, p, t, \delta, e_{out}, f, d, s_2) \text{ et} \\ (s_1, s_1') \xrightarrow{e_{in}, M_t(p), M_c(p), M_d(p), t^*, \delta^*}_{e_{out}, f, d^*} (s_2, s_1') \in \mathcal{T}'' \text{ pour chaque transition } s_1 \xrightarrow{e_{in}, p, t, \delta}_{e_{out}, f, d} \\ s_2 \in \mathcal{T} \text{ et pour chaque état } s_1' \in S' \text{ tel que pour chaque transition } s_1' \xrightarrow{e_{in}', p', t', \delta'}_{e_{out}, f, d', s_2'} \\ s_2' \in \mathcal{T}', \text{ soit } e_{in}' \nsubseteq e_{in} \text{ ou } p \nRightarrow p',$

- $\Box \Pi(s'_1, e'_{in}, p', t', \delta', e'_{out}, f', d', s'_2) := \{t^*, d^*, \delta^*\} \bigcup \Pi(s'_1, e'_{in}, p', t', \delta', e'_{out}, f', d', s'_2)$ et  $(s_1, s'_1) \xrightarrow{e'_{in}, M_t(p'), M_c(p'), M_d(p'), t^*, \delta^*}_{e'_{out}, f', d^*} \land (s_1, s'_2) \in \mathcal{T}''$  pour chaque transition  $s'_1 \xrightarrow{e'_{in}, p', t', \delta'}_{e'_{out}, f', d'} s'_2 \in \mathcal{T}'$  et pour chaque état  $s_1 \in S$  tel que pour chaque transition  $s_1 \xrightarrow{e_{in}, p, t, \delta}_{e_{out}, f, d} s_2 \in \mathcal{T}$ , soit  $e_{in} \nsubseteq e'_{in}$  ou  $p' \not\Rightarrow p$ ,

- $\Box \Pi(s_1, e_{in}, p, t, \delta, e_{out}, f, d, s_2) := \{t^*, d^*, \delta^*\} \bigcup \Pi(s_1, e_{in}, p, t, \delta, e_{out}, f, d, s_2) \text{ et}$  $\Pi(s'_1, e'_{in}, p', t', \delta', e'_{out}, f', d', s'_2) := \{t^*, d^*, \delta^*\} \bigcup \Pi(s'_1, e'_{in}, p', t', \delta', e'_{out}, f', d', s'_2) \text{ et}$  $(s_1, s'_1) \xrightarrow{e_{in} \bigcup e'_{in}, M_t(p \land p'), M_c(p \land p'), M_d(p \land p'), t^*, \delta^*}_{e_{out} \bigcup e'_{out}, f \circ f', d^*} (s_2, s'_2) \in \mathcal{T}'', \text{ pour chaque pair de}$  $\operatorname{transitions} s_1 \xrightarrow{e_{in}, p, t, \delta}_{e_{out}, f, d} s_2 \in \mathcal{T} \text{ et } s'_1 \xrightarrow{e'_{in}, p', t', \delta'}_{e'_{out}, f', d'} s'_2 \in \mathcal{T}'.$

□ Pour chaque transition  $(s_1, e_{in}, p, t_{s_1}^{s_2}, \delta_{s_1}^{s_2}, e_{out}, f, d_{s_1}^{s_2}, s_2)$ , le morphism  $M_t$  mappe le temps de début de la transition t au *min* du temps de début défini dans  $\Pi(s_1, e_{in}, p, t, e_{out}, f, d, s_2)$

$$M(t) \to min_{t^* \in \Pi(s_1, e_{in}, p, t, \delta, e_{out}, f, d, s_2)} t^*$$

□ Le morphisme  $M_d$  mappe la durée d à la somme des durées définies dans  $\Pi(s_1, e_{in}, p, t, \delta, e_{out}, f, d, s_2)$

$$M(d) \to d \ge \sum_{d^* \in \Pi(s_1, e_{in}, p, t, \delta, e_{out}, f, d, s_2)} d^*.$$

□ Le morphisme  $M_c$  mappe les compteurs  $\delta$  à la *somme* des durées des transitions définies dans  $\Pi(s_1, e_{in}, p, e_{out}, f, s_2, \delta)$

$$M(\delta) \to \sum_{\delta^* \in Pi(s_1, e_{in}, p, t, \delta, e_{out}, f, d, s_2, \delta_{s_1}^{s_2})} \delta^*.$$

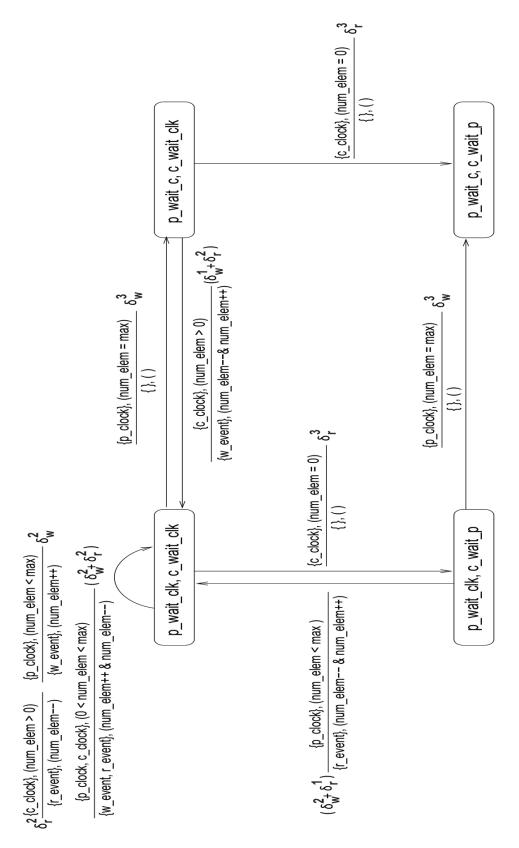

Au cours de la composition symbolique, toutes les transitions possibles entre les états symboliques sont générées. Ces transitions contiennent les *transitions sûres*, les *transitions impossibles*, les *transitions redondantes* et les *transitions réductibles*. Définissons tout d'abord chaque catégorie de transitions.

- □ Les transitions sûres : Elles représentent l'ensemble des transitions possibles générés lors de l'exécution symbolique. Ces transitions sont généralement déclenchées à la fois dans les automates minimaux et l'automate composé.

- □ Les transitions impossibles : Elles représentent l'ensemble des transitions qui ne peuvent jamais être déclenchées dans l'automate composé. Elles sont impossibles, soit parce que leurs conditions d'entrée ne peuvent jamais être vraies, ou parce qu'elles correspondent à des états unsafe comme on a expliqué précédemment.

- □ Les transitions redondantes : Elles représentent l'ensemble des transitions qui ont les mêmes conditions d'entrée et les conditions de sortie. Dans ce cas, il est préférable de ne conserver qu'une seule transition.

□ Les transitions réductibles : Elles représentent une séquence de transitions consécutives qui sont inter-indépendantes, c'est à dire, les conditions de sortie d'une transition représentent les conditions d'entrée dans la transition consécutive. Dans ce cas, toutes les transitions sont fusionnées ensemble et transformées en une seule transition.

La réduction symbolique est une étape ultérieure qui consiste à garder seulement la trace des transitions sûres. C'est une étape importante pour construire l'automate final. Ainsi, au cours de cette étape on réduit toutes les transitions impossibles, on remplace les transitions redondantes et on gère l'ensemble des transitions réductibles. On considère l'influence de l'environnement sur l'exécution du système, à savoir, éliminer l'ensemble des comportements qui ne peuvent pas se produire dans l'automate composé. En outre, la réduction consiste en la concaténation des transitions, à savoir, l'incidence d'une certaine transition peut immédiatement déclencher une autre transition. On peut donc remplacer les deux transitions par une nouvelle.

L'algorithme de la réduction symbolique est défini comme suit : Supposons un automate  $A(V) = (S; E; \mathcal{T})$ , telle que  $\mathcal{T}$  contient des transitions réductiles, soit  $\mathcal{T}_0 := \mathcal{T}$ ,  $\mathcal{T}_{remove} := \{\}$  et  $\mathcal{T}_{new} := \{\}$ . On définit ci dessous les différentes étapes de la réduction symbolique définies à partir de l'automate composé.

- 1. pour chaque pair de transitions réductibles  $(t_1, t_2)$  et son contractum  $t_3$ , avec  $t_1, t_2 \in \mathcal{T}_0$ , soit  $\mathcal{T}_{remove} := \mathcal{T}_{remove} \cup t_1, t_2$  et  $\mathcal{T}_{new} := \mathcal{T}_{new} \cup t_3$ ;

- 2. on répète les étapes précédentes pour toutes les transitions dans  $T_0$ ;

- 3. soit  $\mathcal{T}_0 := (\mathcal{T}_0 / \mathcal{T}_{remove}) \cup \mathcal{T}_{new}, \mathcal{T}_{remove} := \{\} \text{ et } \mathcal{T}_{new} := \{\};$

- s'il ya d'autres transitions réductibles dans T<sub>0</sub>, on reprend l'étape 1 et on refait le même scénario; sinon, soit T' := T<sub>0</sub>.

L'automate réduit est donc  $(S, E, \mathcal{T}')$ .

Notons qu'à ce stade, les évènements de l'automate final peuvent être divisés en deux ensembles : l'ensemble des événements provenant de *l'environnement*  $E_e$  et l'ensemble des évènements internes  $E_i$ . Les événements de l'environnement sont des événements générés par le simulateur SystemC, qui sont généralement des évènements temporels tels que les événements liés aux horloges. En utilisant la dernière classification des événements, l'automate composé peut être réduit à nouveau en supprimant ces transitions dont les évènements sont liés à l'environnement, c'est à dire, les transitions où  $e_{in} \notin E_e$ .

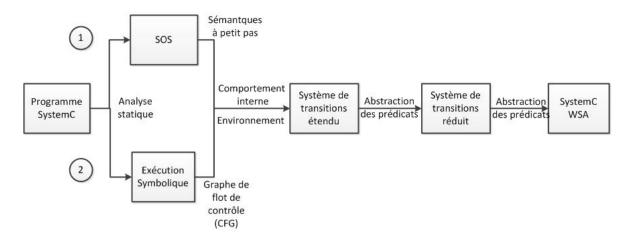

Les automates des SystemC WSA sont des systèmes de transition qui sont extraits manuellement à partir des descriptions SystemC [YZM07]. Donc il faut définir un ensemble d'étapes de construction automatique du modèle; ceci est la principale contribution de cette thèse. On a aussi prouvé que le modèle est conforme au système initial, puis on l'a validé durant l'étape de la construction automatique. Pour construire les automates abstraits, nous suivons

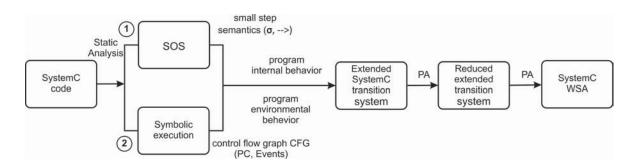

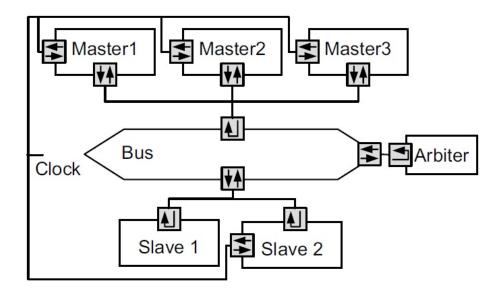

FIGURE 2 – Les étapes de construction automatique des SystemC WSA

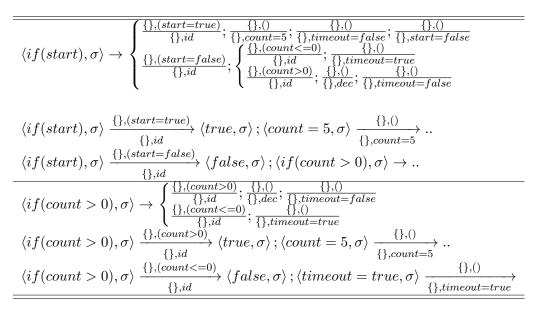

les différentes étapes comme indiqué dans la Figure 2:(1) Nous avons besoin d'écrire correctement la sémantique formelle du langage SystemC. Nous avons ainsi utilisé une sémantique à petit pas appelée sémantique opérationnelle de Plotkin [Plo04]. Le but de développer une telle sémantique est (i) de fournir une description complète et non ambigue du langage, (ii) d'exécuter pas à pas le programme initial et (iii) de détecter l'effet de cette analyse sur le comportement gloal du système. On distingue aussi entre le comportement interne et le comportement global de chaque module SystemC. Toutes ces informations sont présentées dans la syntaxe de la sémantique opérationnelle du programme. Nos sémantiques capturent non seulement la structure des composants SystemC, mais aussi le comportement de la composition parallèle des composants communicants. Nous avons donc modélisé aussi le comportement de l'ordonnanceur. Nous supposons que chaque module se comporte soit localement en utilisant ses variables locales ou communique avec l'environnement à travers ce qu'on appelle les variables d'environnement. Les variables locales sont des signaux de sortie, des variables internes, des canaux de sortie, les événements de sortie, et le compteur de programme pour les processus. Les variables d'environment sont des signaux d'entrée, les événements d'entrée, les canaux d'entrée et les variables globales. En ce qui concerne la sémantique de la simulation en SystemC[WRM01], il existe au plus un processus qui réagit avec l'environnement. Nous pouvons visualiser localement les instants au cours desquels les réactions se produisent, en observant l'état (les variables C de et les compteurs ordinaux pour chaque processus) du procéssus, noté  $\sigma$  et son environnement (événements, les canaux, les signaux, les processus, etc), noté E. Pour décrire comment une instruction modifie les configurations de l'environnement, nous écrivons nos règles comme suit :

$$\langle stmt, \sigma \rangle \xrightarrow{E}_{E_o} \langle stmt', \sigma \rangle$$

où :

- stmt est une instruction SystemC qui correspond à l'emplacement du compteur de programme, avant la transition, et *stmt*' est l'emplacement du compteur du programme après la transition,

- $\sigma$  et  $\sigma'$  sont respectivement l'état initial et l'état final au cours de la réaction. Ils représentent une fonction  $\mathcal{V} \cup \mathcal{CH} \mapsto values$ , où  $\mathcal{V}$  est l'ensemble des variables locales et partagées et  $\mathcal{CH}$  est l'ensemble des canaux.

- E est l'environnement (ensemble des événements et des variables qui activent le processus) dans lequel la transition s'est exécutée.  $E_o$  est l'environnement émis en sortie pendant la transition. En général, un environnement est un 5-uplet  $E = (E^i, E^{\delta}, E^T, \mathcal{V}, \mathcal{RQ})$ où :

- $\hfill\square$   $E^i$  est l'ensemble des événements immédiats,

- $\hfill\square$   $E^{\delta}$  est l'ensemble des prochains de lta événements,

- $\hfill\square$   $E^T$  est l'ensemble des Timed événements,

- $\Box \ \mathcal{V}$  est l'ensemble des delta mises à jour des variables.

□  $\mathcal{RQ}$  est une séquence constituée des demandes en attente de mise à jour les canaux. Une demande est une paire  $(ch, exp(\sigma))$  où  $ch \in C\mathcal{H}$  et  $exp(\sigma)$  représente la valeur attribuée à ch.

Pour indiquer que l'environnement de sortie  $E_o$  ne change pas, on utilise la notation suivante –. Soit, il y a pas d'événements émis au cours de la transition, soit les variables restent inchangés ou bien les canaux ne sont pas modifiés. Notre sémantique est similaire à celle de Shyamasundar[RSK07] où une sémantique complète du langage SystemC est proposée. Dans notre approche, nous insistons particulièrement sur trois points principaux :

- capturer le comportement réactif lors de la simulation en SystemC.

- spécifier un réseau de composants synchrones et asynchrones qui communiquent soit à un très haut niveau ou bien via les événements à un niveau plus bas.

- spécifier deux niveaux de temps : le cycle de delta et le temps de simulation.

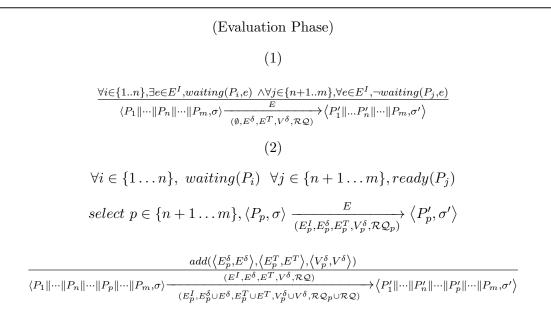

En outre, au cours de notre formalisation et surtout pendant la composition parallèle, nous distinguons entre les trois phases du processus de simulation (en réponse à l'algorithme de simulation en SystemC (Figure 1) : C'est une principale contribution de notre sémantique. Nous intègrons la simulation du scheduler dans une composition parallèle de processus concurrents. Cette composition est indépendante de l'ordonnanceur lui-même. L'ordonnanceur est alors dispensé du processus de modélisation. Il est déjà présenté principalement dans la composition parallèle.

Nos sémantiques ont deux avantages principaux : d'abord, elles commencent à partir d'une description de bas niveau du composant SystemC (au niveau du delta cycle), qui met en évidence l'évolutivité de l'approche globale. Deuxièmement, nous ne devons pas modéliser séparément l'ordonnancer. Ainsi, l'automate composé sera généré indépendant de la politique d'ordonnancement ce qui nous permet de gagner en termes de coût de modélisation et de vérification. Nous allons présenter la sémantique de certaines constructions séquentielles (y compris les affectations, les instructions liées des canaux, les instructions liées aux événements, les instructions conditionnelles, les instructions wait). Nous présentons aussi les sémantiques de la composition parallèle où l'on distingue entre les trois étapes de la sémantique SystemC qui est la principale contribution de notre travail par rapport aux travaux existants en formalisation de la sémantique du SystemC utilisant les notations SOS.

| [          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| assignment | $\langle var \ v, \sigma \rangle \xrightarrow{-} \langle \epsilon, \sigma[v] \rangle$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|            | $<\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| if         | $\langle if \ b \ then \ p \ else \ q,\sigma \rangle \xrightarrow{-} \langle \epsilon,\sigma' \rangle$                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|            | $<\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|            | $\langle if \ b \ then \ p \ else \ q,\sigma \rangle \xrightarrow{-} \langle \epsilon,\sigma' \rangle$                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|            | $<\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| while      | $\langle while (b) do p, \sigma \rangle \xrightarrow{-} \langle \epsilon, \sigma' \rangle$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|            | $<\!\!b,\!\sigma\!\!>\rightarrow<\!\!false,\!\sigma\!\!>$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|            | $\langle while (b) do p, \sigma \rangle \xrightarrow{-} \langle \epsilon, \sigma \rangle$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|            | $ch \in Channels \land \sigma(ch) \neq exp(\sigma)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Les canaux | $ \begin{array}{c} \hline \langle ch!!exp,\sigma \rangle & \xrightarrow{E^{I},E^{\delta},E^{T},\mathcal{V},\mathcal{RQ}} \\ \hline & \xrightarrow{E^{I},E^{\delta},E^{T},\mathcal{V},\mathcal{RQ} \backslash (ch,exp(\sigma))} \\ \hline & ch \in Channels, v \in \mathcal{V} \end{array} \\ \hline \end{array} \\ \left. \begin{array}{c} \langle ch !!exp,\sigma \rangle & \xrightarrow{E^{I},E^{\delta},E^{T},\mathcal{V},\mathcal{RQ} \backslash (ch,exp(\sigma))} \\ \hline & \downarrow \\ \rangle \\ \hline & \downarrow \\ \rangle \\ \hline \end{array} \right. $ |

|            | $\langle ch??exp,\sigma  angle \stackrel{E}{-} \langle \epsilon, \sigma[v/ch]  angle$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| notify     | $ \begin{array}{c} \overbrace{\langle e.notify(),\sigma\rangle}{\xrightarrow{E}} \langle \epsilon,\sigma\rangle \\ \langle e.notify_{-}\delta(),\sigma\rangle \xrightarrow{E} \langle \epsilon,e,\emptyset,\emptyset \\ \langle e.notify_{-}t(),\sigma\rangle \xrightarrow{E} \langle \epsilon,\sigma\rangle \\ \langle e.notify_{-}t(),\sigma\rangle \xrightarrow{E} \langle \epsilon,\sigma\rangle \\ \hline \end{array} $                                                                                                                                               |

| nouny      | $\langle e.notify_{-}\delta(),\sigma angle \xrightarrow{E} \langle \epsilon,\sigma angle$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|            | $\langle e.notify_{-t}(),\sigma  angle \xrightarrow{E} \langle \epsilon,\sigma  angle$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| wait       | $\frac{e \notin E}{\langle wait(e), \sigma \rangle \xrightarrow{E}} \langle wait(e), \sigma \rangle}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|            | $\frac{e \in E}{\langle wait(e), \sigma \rangle \xrightarrow{E}_{-} \langle \epsilon, \sigma \rangle}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

TABLE 1 – Sémantiques opérationnelles de quelques instructions SystemC

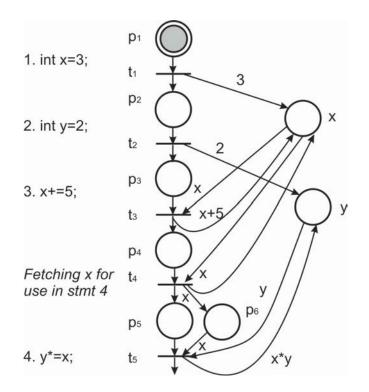

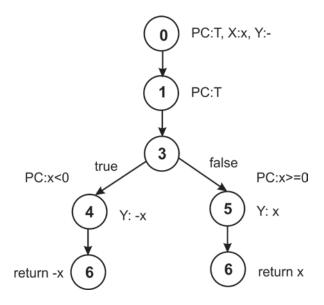

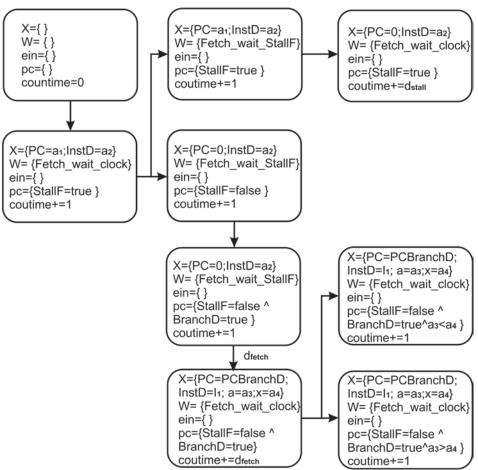

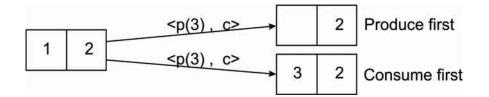

(2) Nous procédons à des techniques d'exécution symbolique (SE) [Kin76] pour générer le graphe de flot de contrôle du programme. Nous l'appelons **exécution symbolique conjointe** car nous combinons à la fois l'exécution symbolique et la sémantique opérationnelle. Les principaux objectifs de l'application de l'exécution symbolique sont : générer premièrement les différentes traces d'exécution du système et deuxièmement exprimer le programme en utilisant des formules logiques à la place des expressions réelles. Cette étape est une étape primordiale pour appliquer les techniques d'abstraction des prédicats qui représentent l'étape suivante. L'exécution symbolique est une extension de l'exécution réelle ayant pour paramètres d'entrée l'ensemble des opérateurs de base de langage exprimés sous forme de prédicats et comme sortie un ensemble de formules symboliques définis sur ces prédicats.

Prenons comme exemple un programme écrit dans un langage de programmation quelconque, on suppose que les variables du programme sont de type entiers signés et que le programme contient des instructions simples type IF ( avec des clauses THEN et ELSE), des instructions GO-TO et des entrées ( paramètres de procédure, variables globales, operations read). On prend comme expressions arithmétiques les opérateurs basiques pour les entiers comme l'addition (+), la soustraction (-) et la multiplication (x). On suppose qu'une expression booléenne utilisée dans l'instruction IF est un simple test supposant que l'expression arithmétique est non-négative (*i.e.arith.expr*  $\geq$  0). L'exécution symbolique de ce programme consiste à tranformer cette description sous forme de symbôles mathématiques sans toucher ou changer la sémantique du programme. On suppose qu'à chaque fois une nouvelle valeur est demandée, elle sera fournie à partir de la liste des symbôles suivants :  $(a_1, a_2, \ldots, a_n)$ . Puis selon la nature de l'instruction correspondante à chaque ligne du code, on associe une fontion algébrique définie sur ces variables. Le paramètre état d'exécution d'un programme correspond aux valeurs des variables et le PC (path condition). Il pointe sur l'instruction en cours d'exécution.

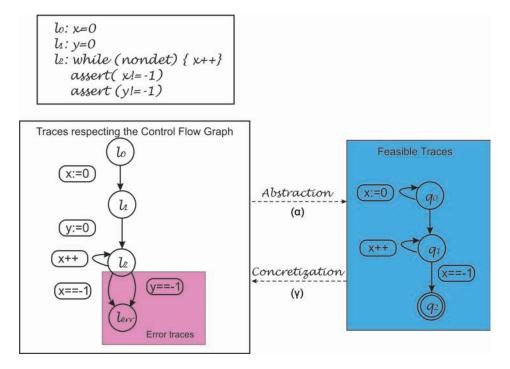

(3) Nous procédons à des techniques d'abstraction de prédicats (PA)[FQ02] pour déterminer tout d'abord les relations entre les formules logiques générées pendant l'exécution symbolique des automates parallèles. Ensuite, ces techniques permettent de fusionner les chemins entre chaque deux états d'attente dans le graphe de flot de contrôle. Le but final est de construire l'automate du SystemC WSA à partir du graphe de flot de contrôle qui est annoté avec des formules logiques définies à partir des variables globales et des informations sur les événements de l'environnement.

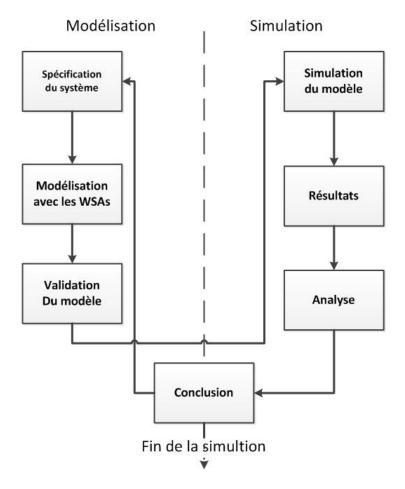

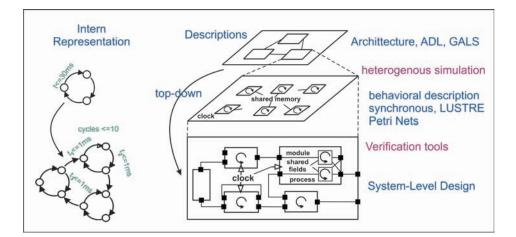

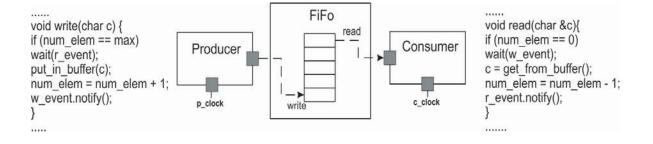

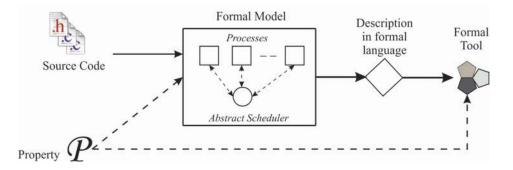

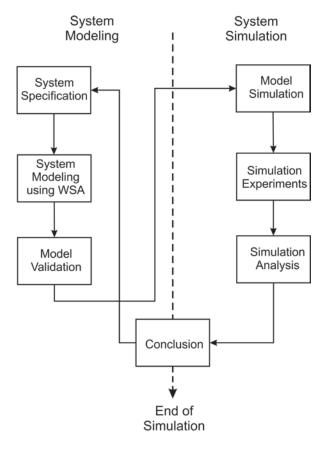

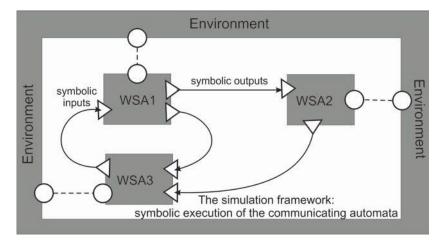

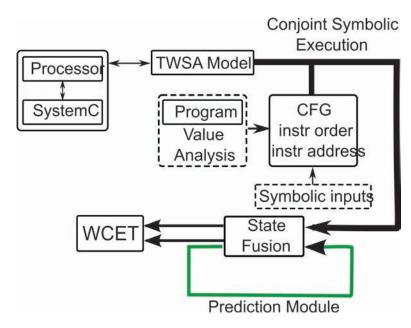

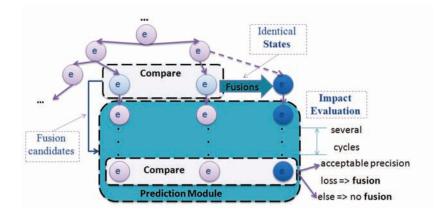

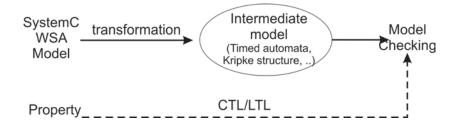

Enfin, nous proposons d'utiliser le modèle des SystemC waiting state automata dans trois applications diffèrentes. Tout d'abord, nous présentons une approche globale pour modéliser et simuler symboliquement les systèmes embarqués logiciels et matériels en utilisant les SystemC WSA (comme présenté dans la figure ci-dessous). Nous montrons que notre approche garantit

FIGURE 3 – La modélisation et la simulation symbolique des composants SystemC à l'aide des SystemC WSA

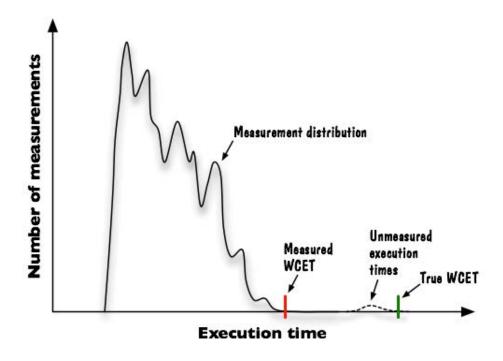

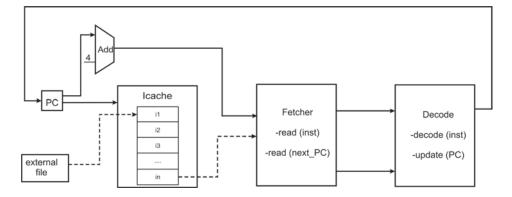

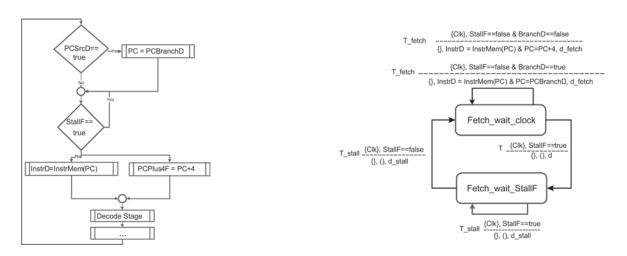

une simulation rapide des systèmes embarqués. Ensuite, nous présentons notre méthodologie pour calculer et estimer le pire temps d'exécution (WCET) en utilisant le modèle des Timed SystemC WSA et comparer la méthodologie à des méthodologies existantes. Nous utilisons le modèle des Timed SystemC WSA pour modéliser le matériel, puis nous exécutons symboliquement le programme sur le modèle abstrait. Nous procédons à une technique de fusion intelligente présenté dans des travaux éxistants dans notre équipe pour donner une estimation précise du WCET. Cette application est un travail conjoint qui réunit deux domaines de recherche à l'ENSTA ParisTech. Nous avons ensuite proposé d'utiliser des techniques de vérification notamment les techniques du *model checking* pour vérifier d'autres propriétés sur le modèle des SystemC waiting state automata. Nous énumérons aussi les principaux anomalies qui se produisent en raison de la concurrence et de l'accès aux ressources partagées entre les composants s'exécutant en parallèle. Nous proposons une solution pour éviter ces anomalies en utilisant les automates des SystemC WSA.

#### (La phase d'évaluation)

$$(1)$$

$$\underbrace{\forall i \in \{1..n\}, \exists e \in E^{I}, waiting(P_{i}, e) \land \forall j \in \{n+1..m\}, \forall e \in E^{I}, \neg waiting(P_{j}, e)}_{\langle P_{1} \| \cdots \| P_{n} \| \cdots \| P_{m}, \sigma \rangle} \xrightarrow{E}_{(\emptyset, E^{\delta}, E^{T}, V^{\delta}, \mathcal{R} Q)} \langle P_{1}' \| \cdots P_{n}' \| \cdots \| P_{m}, \sigma' \rangle}$$

$$(2)$$

$$\forall i \in \{1...n\}, waiting(P_{i}) \forall j \in \{n+1...m\}, ready(P_{j})$$

$$select \ p \in \{n+1...m\}, \langle P_{p}, \sigma \rangle \xrightarrow{E}_{(E_{p}^{I}, E_{p}^{\delta}, E_{p}^{T}, V_{p}^{\delta}, \mathcal{R} Q_{p})} \langle P_{p}', \sigma' \rangle$$

$$\underbrace{add(\langle E_{p}^{\delta}, E^{\delta} \rangle, \langle E_{p}^{T}, E^{T} \rangle, \langle V_{p}^{\delta}, V^{\delta} \rangle)}_{(E_{p}^{I}, E_{p}^{\delta} \cup E^{\delta}, E_{p}^{T} \cup U^{\delta}, \mathcal{R} Q_{p} \cup \mathcal{R} Q)} \langle P_{1}' \| \cdots \| P_{n}' \| \cdots \| P_{p}' \| \cdots \| P_{m}, \sigma' \rangle$$

#### (La phase de mise à jour)

$\frac{\forall (ch,v) \in RQ}{\langle P_1 \| \cdots \| P_n, \sigma \rangle \xrightarrow{(E^I, E^{\delta}, E^T, V^{\delta}, \mathcal{RQ})} (E^I, E^{\delta}, E^T, V^{\delta}, \emptyset)} \langle P_1 \| \cdots \| P_n, \sigma[v/ch] \rangle}$

#### (La phase des delta-cycles)

$$\frac{\forall i \in \{1..n\}, waiting(P_i)}{\langle P_1 \| \cdots \| P_n, \sigma \rangle \xrightarrow{(\emptyset, E^{\delta}, E^T, V^{\delta}, \mathcal{RQ})} (E^{\delta}, \emptyset, E^T, \emptyset, \mathcal{RQ})} \langle P_1 \| \cdots \| P_n, \sigma [V^{\delta}/V] \rangle$$

(La phase d'avancement du temps)

$\frac{\forall i \in \{1..n\}, waiting(P_i)}{\langle P_1 \| \cdots \| P_n, \sigma \rangle \xrightarrow{(\emptyset, \emptyset, E^T, \mathcal{RQ})} (E^T, \emptyset, \emptyset, \emptyset, \mathcal{RQ})} \langle P_1 \| \cdots \| P_n, \sigma[V^{\delta}/V] \rangle}$

## Contents

| 1        | Intr | oduction                                                | 9  |

|----------|------|---------------------------------------------------------|----|

|          | 1.1  | Context                                                 | 10 |

|          | 1.2  | Summary of Contributions                                | 11 |

|          |      | 1.2.1 Research Questions                                | 12 |

|          |      | 1.2.2 Contributions                                     | 12 |

|          | 1.3  | Outline                                                 | 13 |

|          |      |                                                         |    |

| <b>2</b> | The  | e System-on-Chip Design Flow                            | 17 |

|          | 2.1  | Introduction                                            | 17 |

|          | 2.2  | SoC Bottlenecks                                         | 18 |

|          |      | 2.2.1 Explosive Complexity                              | 19 |

|          |      | 2.2.2 Time-to-Market Pressure                           | 20 |

|          |      | 2.2.3 Cost                                              | 20 |

|          | 2.3  | Traditional vs New SoC Design Flow                      | 20 |

| 3        | Тор  | -Down and Bottom-Up Approaches in the Conceptual Design | 23 |

|          | 3.1  | The Top-Down Approach                                   | 24 |

|          | 3.2  | The Bottom-Up Approach                                  | 25 |

|          | 3.3  | Conclusion                                              | 26 |

| 4 | Tra | nsaction-Level Modeling (TLM)         | 29 |  |

|---|-----|---------------------------------------|----|--|

|   | 4.1 | Introduction                          | 29 |  |

|   | 4.2 | Attempts at Raising Abstraction Level | 30 |  |

|   | 4.3 | The Transaction Level Modeling        | 31 |  |

|   |     | 4.3.1 Description of TLM              | 33 |  |

|   |     | 4.3.2 The Modeling Approach with TLM  | 34 |  |

|   |     | 4.3.3 The Novel Design Flow with TLM  | 35 |  |

|   | 4.4 | Conclusion                            | 36 |  |

| 5 | Sys | vstemC Language                       |    |  |

|   | 5.1 | Introduction                          | 37 |  |

|   | 5.2 | Structure of a SystemC Model          | 38 |  |

|   |     | 5.2.1 Syntax                          | 39 |  |

|   |     | 5.2.2 Processes                       | 41 |  |

|   |     | 5.2.3 Channels                        | 41 |  |

|   |     | 5.2.4 Events                          | 43 |  |

|   |     | 5.2.5 Time in SystemC                 | 45 |  |

|   | 5.3 | SystemC Scheduler                     | 45 |  |

|   | 5.4 | The TLM Library                       | 48 |  |

$\mathbf{27}$

I System Level Modeling with SystemC

## II Modeling with SystemC Waiting State Automata (WSA) 49

| 6 | Intr | oduction and Related Works                                      | 51 |

|---|------|-----------------------------------------------------------------|----|

|   | 6.1  | Introduction                                                    | 52 |

|   | 6.2  | Existing Static Approaches in SystemC Modeling and Verification | 52 |

|   | 6.3                  | Summary                                                          | 56  |

|---|----------------------|------------------------------------------------------------------|-----|

| 7 | $\mathbf{Sys}$       | temC Waiting State Automata                                      | 59  |

|   | 7.1                  | Motivations and General Approach                                 | 60  |

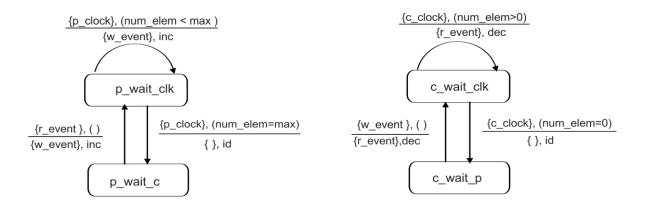

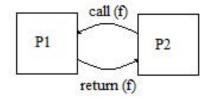

|   | 7.2                  | Example                                                          | 62  |

|   | 7.3                  | Syntax                                                           | 66  |

|   | 7.4                  | Model Properties                                                 | 68  |

|   | 7.5                  | Conclusion                                                       | 69  |

| 8 | $\mathbf{Syn}$       | abolic Composition and Reduction of SystemC WSA                  | 71  |

|   | 8.1                  | The Symbolic Composition of the SystemC WSA                      | 72  |

|   | 8.2                  | The Symbolic Reduction of the SystemC WSA                        | 75  |

|   | 8.3                  | Conclusion                                                       | 79  |

| 9 | $\mathbf{Ext}$       | ending the SystemC Waiting State Automata with Counters and with | L   |

|   | $\operatorname{Tin}$ | ne                                                               | 81  |

|   | 9.1                  | Extending the SystemC WSA with Counters                          | 82  |

|   |                      | 9.1.1 Syntax                                                     | 84  |

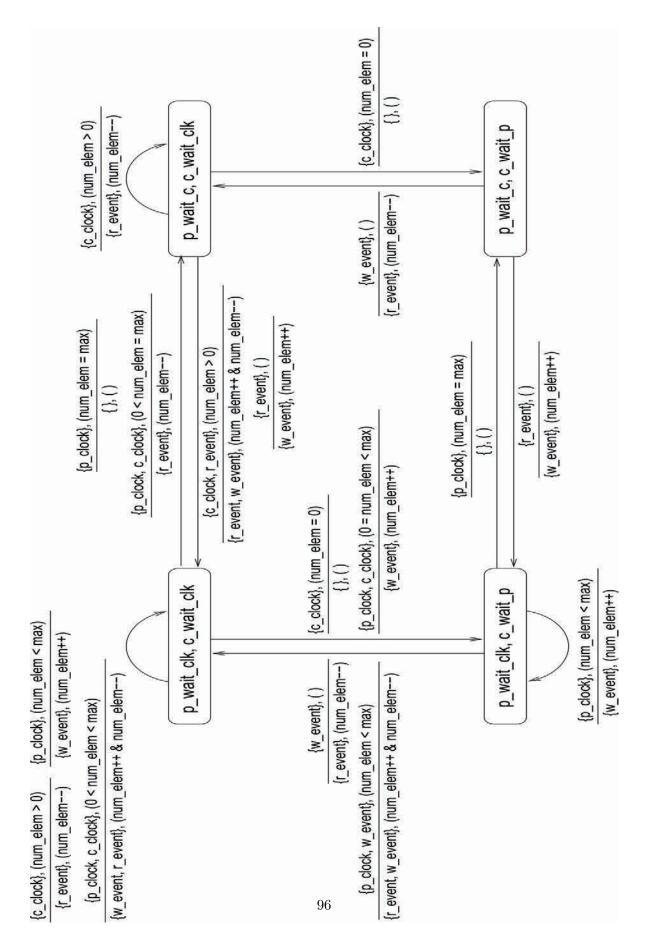

|   |                      | 9.1.2 The Symbolic Composition                                   | 85  |

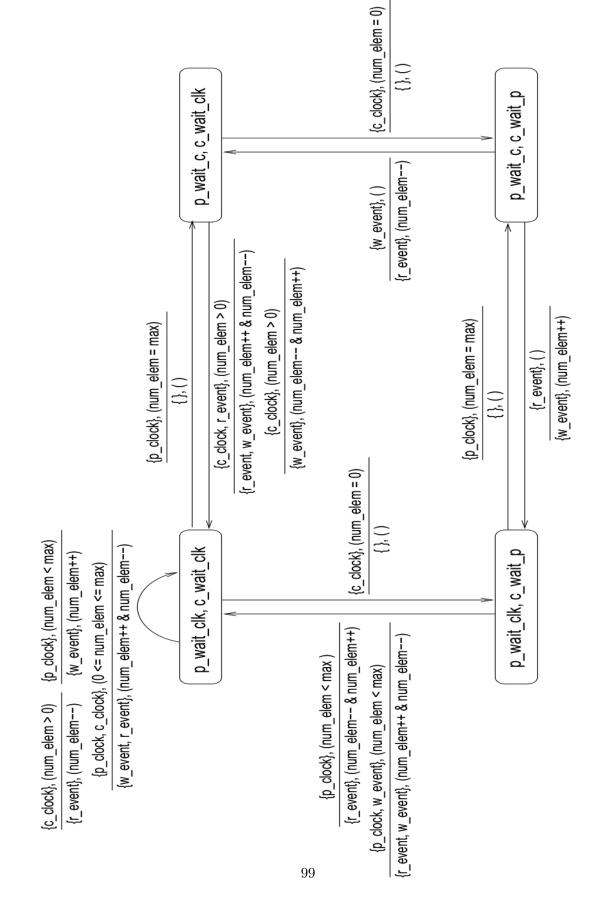

|   |                      | 9.1.3 The Symbolic Reduction                                     | 88  |

|   | 9.2                  | Extending the SystemC WSA with Time                              | 90  |

|   |                      | 9.2.1 Syntax                                                     | 92  |

|   |                      | 9.2.2 Symbolic Composition                                       | 94  |

|   |                      | 9.2.3 Symbolic Reduction                                         | 97  |

|   | 9.3                  | Extending the SystemC WSA with Counters and Time                 | 100 |

|   |                      | 9.3.1 Syntax                                                     | 101 |

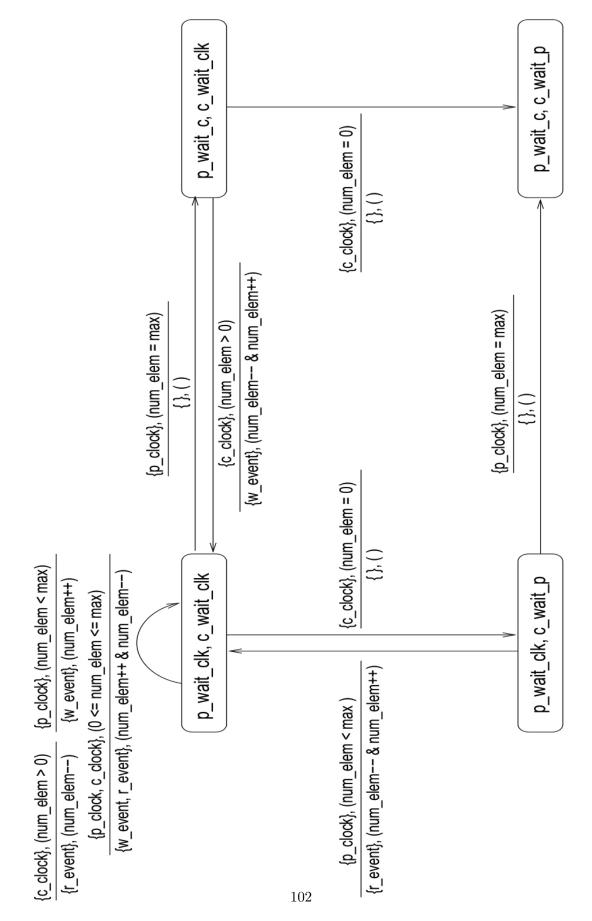

|   |                      | 9.3.2 Symbolic Composition                                       | 102 |

|   |                      | 9.3.3 Symbolic Reduction                                         | 104 |

|   | 9.4                  | Conclusion                                                       | 106 |

|   |                      |                                                                  |     |

| 11 Mapping SystemC Designs to SystemC WSA                               | 111     |

|-------------------------------------------------------------------------|---------|

| 11.1 Determining Constituent Components                                 | <br>111 |

| 11.2 SystemC WSA of the Components                                      | <br>112 |

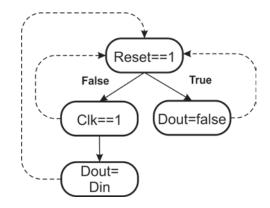

| 11.2.1 SystemC WSA of SC_METHOD Processes $\ldots \ldots \ldots \ldots$ | <br>112 |

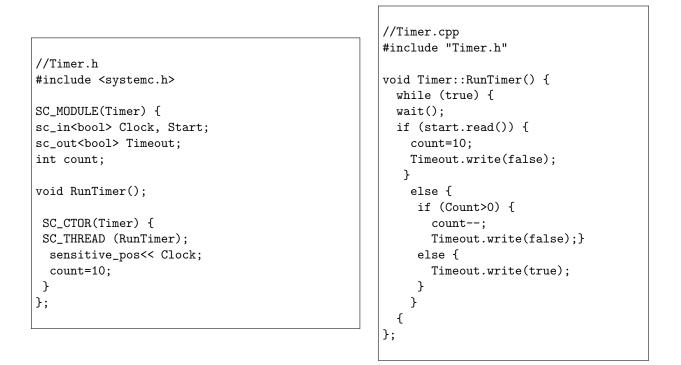

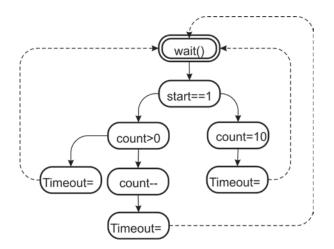

| 11.2.2 SystemC WSA of SC_THREAD Processes                               | <br>113 |

## III Automatic Generation of SystemC Waiting State Automata from SystemC Codes 117

| 12 Intr | oduction (Global Approach)                             | 119                      |

|---------|--------------------------------------------------------|--------------------------|

| 12.1    | Formal Semantics of the Programming Language           | 120                      |

|         | 12.1.1 Subset of SystemC                               | 121                      |

|         | 12.1.2 SystemC Operational Semantics                   | 122                      |

| 12.2    | Symbolic Execution                                     | 124                      |

| 12.3    | Abstract Analysis and Traces Merging                   | 125                      |

|         | 12.3.1 Galois Connection                               | 126                      |

|         | 12.3.2 Fixed points Computation                        | 127                      |

|         | 12.3.3 Widening Operators                              | 127                      |

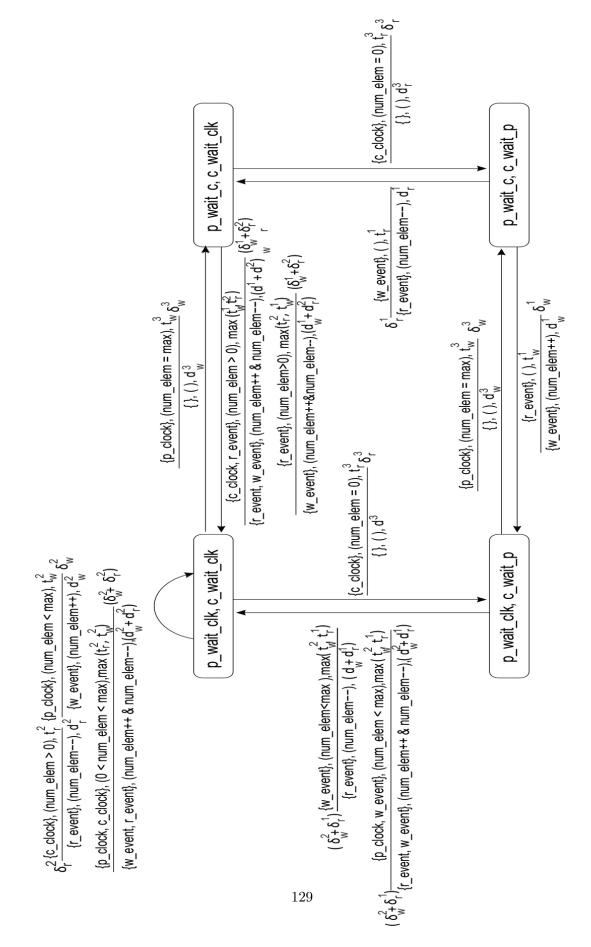

|         | 12.3.4 Traces merging                                  | 129                      |

| 13 Fori | mal Semantics of SystemC                               | 131                      |

| 13.1    | Motivations and Related Works                          | 132                      |

| 13.2    |                                                        | 105                      |

|         | Formal Semantics of SystemC                            | 135                      |

|         | Formal Semantics of SystemC    13.2.1 Basic Statements | $135 \\ 138$             |

|         |                                                        |                          |

|         | 13.2.1 Basic Statements                                | 138                      |

|         | 13.2.1 Basic Statements                                | $138\\138$               |

|         | 13.2.1 Basic Statements                                | 138<br>138<br>139        |

|         | 13.2.1       Basic Statements                          | 138<br>138<br>139<br>140 |

| 13.3 Conclusion                                                                    | 144 |

|------------------------------------------------------------------------------------|-----|

| 14 Applying Static Analysis to Automatically Generate the SystemC Waiting          | 5   |

| State Automata                                                                     | 147 |

| 14.1 Abstracting Low Level Semantics of SystemC to High Level Semantics            | 148 |

| 14.1.1 Introduction                                                                | 148 |

| 14.1.2 Example                                                                     | 149 |

| 14.1.3 Extended Symbolic Execution                                                 | 150 |

| 14.1.4 Abstracting Operational Semantics of a Subset of System<br>C $\ .\ .\ .\ .$ | 152 |

| 14.1.5 The Abstracted Operational Semantics vs the SystemC Waiting State           |     |

| Automata Semantics                                                                 | 155 |

| 14.2 Predicate Abstraction                                                         | 156 |

| 14.2.1 Background                                                                  | 156 |

| 14.2.2 Handling Execution Traces Without Loops                                     | 160 |

| 14.2.3 Handling Loops                                                              | 164 |

| 14.2.4 Conclusion                                                                  | 169 |

| 14.3 The Simple Bus Case Study                                                     | 170 |

| 15 Conclusion                                                                      | 179 |

| $\mathbf{IV}$ | Applications of the SystemC WSA Model | 181 |

|---------------|---------------------------------------|-----|

|---------------|---------------------------------------|-----|

| 16 Introduction                                                                            | 183        |

|--------------------------------------------------------------------------------------------|------------|

| 17 Modeling and Simulation of SystemC Programs using the SystemC WSA                       | 185        |

| 17.1 Introduction                                                                          | 185        |

| 17.2 Modeling and Simulation with the System<br>C WSA $\ldots \ldots \ldots \ldots \ldots$ | 186        |

| 17.3 Summary                                                                               | 188        |

| 18 Hardware/Software Co-verification (Worst Case Execution Time Estimation                 | <b>i</b> - |

| tion Workflow Based on the Timed WSA Model of SystemC Designs)                             | 191        |

| 20                         | 20 Conclusion and Prospects 2 |                                                   |     |  |  |  |  |  |  |

|----------------------------|-------------------------------|---------------------------------------------------|-----|--|--|--|--|--|--|

| V Conclusion and Prospects |                               |                                                   |     |  |  |  |  |  |  |

|                            |                               | 19.2.2 Checked properties                         | 211 |  |  |  |  |  |  |

|                            |                               | 19.2.1 Introduction                               | 209 |  |  |  |  |  |  |

|                            | 19.2                          | Applying Model Checking Techniques to SystemC WSA | 209 |  |  |  |  |  |  |

|                            |                               | 19.1.2 Liveness and Determinism                   | 208 |  |  |  |  |  |  |

|                            |                               | 19.1.1 Introduction                               | 208 |  |  |  |  |  |  |

|                            | 19.1                          | Anomalous Behaviors                               | 207 |  |  |  |  |  |  |

| 19                         | App                           | lying Verification Techniques to SystemC WSA      | 207 |  |  |  |  |  |  |

|                            | 18.5                          | Conclusion                                        | 205 |  |  |  |  |  |  |

|                            |                               | 18.4.3 Intelligent States Fusion                  | 204 |  |  |  |  |  |  |

|                            |                               | 18.4.2 Conjoint Symbolic Execution                | 199 |  |  |  |  |  |  |

|                            |                               | 18.4.1 Value Analysis $\ldots$                    | 199 |  |  |  |  |  |  |

|                            | 18.4                          | WCET Estimation                                   | 197 |  |  |  |  |  |  |

|                            | 18.3                          | Modeling the Processor                            | 196 |  |  |  |  |  |  |

|                            | 18.2                          | Related Works                                     | 195 |  |  |  |  |  |  |

|                            | 18.1                          | Introduction                                      | 193 |  |  |  |  |  |  |

| 20.1 Results and | l Discussi | on.   | <br>• | ••• | <br> | · | <br>• | • | ••• | <br>• | • | <br>• | • | <br>• | <br>• | 215 |

|------------------|------------|-------|-------|-----|------|---|-------|---|-----|-------|---|-------|---|-------|-------|-----|

| 20.2 Prospects   |            | • • • | <br>• |     | <br> |   |       | • |     |       | • |       |   | <br>• |       | 219 |

|                  |            |       |       |     |      |   |       |   |     |       |   |       |   |       |       |     |

|                  |            |       |       |     |      |   |       |   |     |       |   |       |   |       |       |     |

| List of Figures  | <b>225</b> |

|------------------|------------|

| List of Acronyms | 229        |

| Bibliography     | 233        |

# CHAPTER 1

## Introduction

| 1.1 Context                  | 10 |

|------------------------------|----|

| 1.2 Summary of Contributions | 11 |

| 1.2.1 Research Questions     | 12 |

| 1.2.2 Contributions          | 12 |

| 1.3 Outline                  | 13 |

Nowadays, embedded systems are more and more integrated in critical applications such as : automobile, avionics, satellites, telecommunications, medical equipments, etc. They are usually composed of deeply integrated but heterogeneous hardware and software components. Those components are developed under severe **resource limitations** (i.e., small processors, tiny memory and low power) and under **high quality requirements** (i.e., speed, real-time constraints, accuracy, consumption and an operational long life-cycle). As a consequence, the job of design engineers has become more tricky and challenging, due to the intensive increasing gap between the cost, the embedded functions, and the performance of those systems.

To meet the high quality standards in nowadays embedded systems and to satisfy the rising industrial demands, the automatization of the developing process of those systems is gaining more and more importance. A major challenge is to develop an automated approach that can be used for the integrated verification and validation of complex and heterogeneous HW/SW systems.

### 1.1 Context

Traditionally, embedded systems were developed by separating the hardware part from the software part. It takes several iterations in the design process to reach an implementation that is functionally correct and that satisfies the performance requirements. Those iterations consume large amounts of costly development time, especially because they occur in a phase where the design is already implemented with a lot of details involved. Yet, this technique is no long appropriate for nowadays embedded system design due to market pressure that require **quick**, **valid**, **efficient** and **safe** systems.

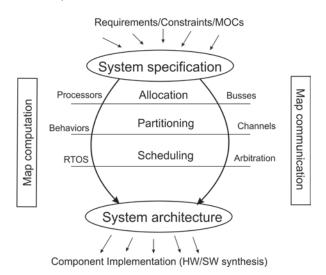

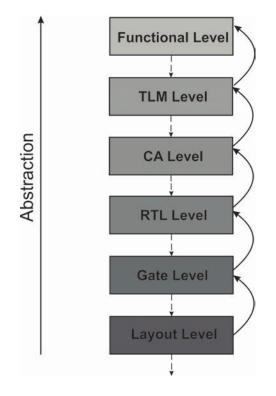

Thus, due to the design trends mentioned above, new modeling languages that support both hardware and software co-design have emerged. Among others, we mention the SystemC language[sys], which is a system level design language that supports design space exploration and performance evaluation efficiently throughout the whole design process even for large and complex HW/SW systems. SystemC is a C++ based modeling framework that supports system-level modeling, architectural exploration, performance modeling, software development, functional verification, and high-level synthesis.

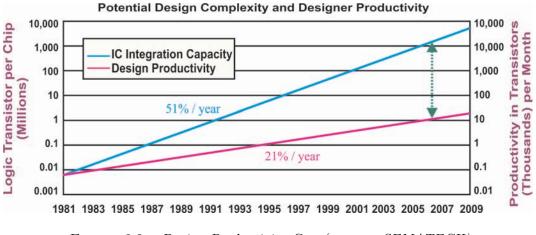

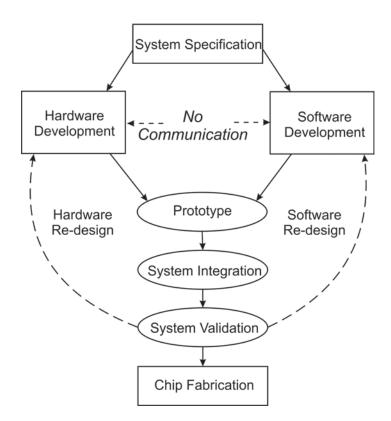

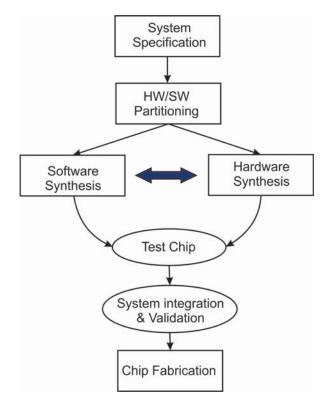

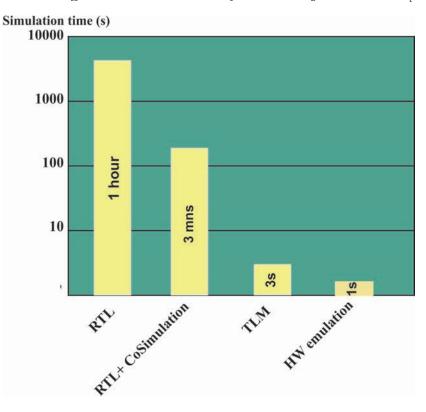

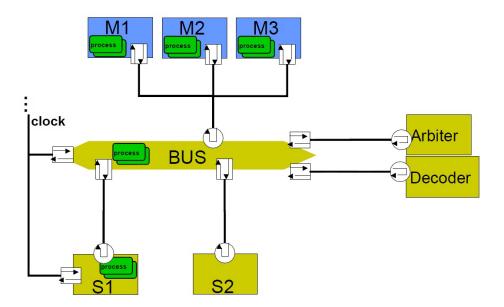

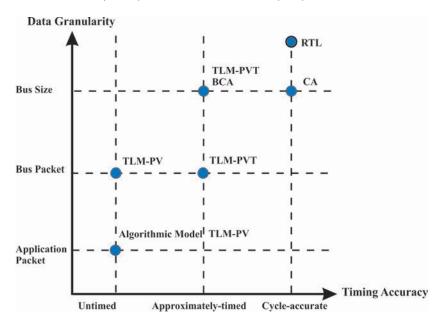

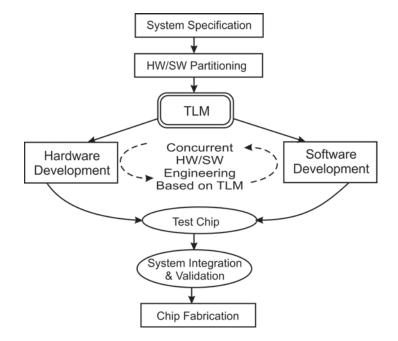

SystemC allows the description of both hardware and software parts. Besides, it allows to execute designs at different levels of abstraction. As a consequence, co-simulation, which can be defined as the simultaneous execution of hardware and software, is used to **verify** and **validate** the embedded system throughout the whole design process. However, co-simulation is necessary because it ensure that models are stepwise refined throughout the conceptual design, but still be *not sufficient* : First, because it cannot cover all possible execution scenarios in particular for real-time, non deterministic and non-terminating systems. Second, it is very difficult to ensure the consistency between different abstraction levels, or to reuse verification results in later development stages. Finally, and more precisely, the evaluation of the simulation results should be done manually by the designer, which needs to be computed automatically. Due to the previous limitations, we need to exploit new methodologies for program analysis and verification, to help designers detect and correct errors in early stages of the conceptual design before proceeding to implementation.