### Built-In Self-Test of Flexible RF Transmitters Using Nonuniform Undersampling

Emanuel Dogaru

#### ▶ To cite this version:

Emanuel Dogaru. Built-In Self-Test of Flexible RF Transmitters Using Nonuniform Undersampling. Other. CentraleSupélec, 2015. English. NNT: 2015CSUP0004. tel-01331561

### HAL Id: tel-01331561 https://theses.hal.science/tel-01331561v1

Submitted on 14 Jun 2016

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

No. d'ordre : 2015-04-TH

### CentraleSupélec

#### ÉCOLE DOCTORALE STITS

"Sciences et Technologie de l'Information, des Télécommunications et des Systèmes"

### THÈSE DE DOCTORAT

**DOMAINE: STIC** Spécialité: Electronique

Soutenue le 06 mars 2015

par:

#### Emanuel DOGARU

### Built-In Self-Test of Flexible RF Transmitters Using Nonuniform Undersampling

Directeur de thèse:

Philippe BENABES

Professeur, chef du département (CentraleSupélec)

**Encadrants**:

Filipe VINCI DOS SANTOS

Professeur, chef de la Chaire Thales/Supélec Ingénieur (Thales Communications & Security)

Joel THIBAULT

William REBERNAK

Ingénieur (Thales Communications & Security)

Composition du jury:

Rapporteurs:

Raymond QUÉRÉ Serge BERNARD

Professeur, Directeur adjoint (XLIM-CNRS-Limoges) Chargé de Recherche (LIRMM/CNRS Montpellier)

Examinateurs:

Souhil MEGHERBI

Professeur (Université Paris-Sud)

Salvador MIR Filipe VINCI DOS SANTOS Professeur, Directeur de Recherches (CNRS/Laboratoire TIMA)

Philippe BENABES

Professeur, chef de la Chaire Thales/Supélec Professeur, chef du département (CentraleSupélec)

Membres invités : William REBERNAK Ingénieur (Thales Communications & Security)

### Acknowledgments

I would like to thank many people who have encouraged and assisted me throughout my PhD study. Foremost, I would like to express sincere gratitude to my advisor Prof. Filipe Vinci for his guidance and support, his infinite patience and all the time invested in my work during the past three years. His invaluable feedback and suggestions contributed to the clarity of this dissertation. I would like to thank M. William Rebernak for giving me the opportunity and the freedom to pursue this research. I thank M. Joël Thibault for his interest in my test strategy and for accepting to take over this project after the retirement of M. Rebernak. It has been a great experience to work with all of them.

I would like to thank my PhD committee members Prof. Raymond Quéré and Prof. Serge Bernard for spending their valuable time in providing me feedback. I would also like to thank Prof. Philippe Benabes for accepting to supervise this project.

The last three years would have not been the same without the support of all my friends and colleagues who made the time spent at Supélec such an enjoyable chapter of my life. I would like to mention: Gisela Olga L., Mickael B., Daniel C., Ashish R., Ivana A., and all my friends from Telecom Department.

The Romanian friends were also an important and fun part of my life in France. Special thanks go to: Andreea-Madalina Serban, Ionela P., Catalin T., Cosmin N., Iuliana P., Catalin & Gabriela R., Madalina E., Razvan T., Ovidiu I., Ana-Maria D., Cristina B., Ionut & Andreea P., Marta B., Florin S., and Valentin T.

I would like to reserve my deepest thanks to my parents for their constant encouragement and support. Their lessons will guide me for the rest of my life.

### **Abstract**

The advent of increasingly powerful Integrated Circuits (IC) has led to the emergence of the Software Defined Radio (SDR) concept, which brought the sector of secured mobile communications into a new era. The outstanding performance of these systems results from optimal trade-offs among advanced analog/Radio Frequency (RF) circuitry, high-speed reconfigurable digital hardware and sophisticated real-time software. The inherent sophistication of such platforms poses a challenging problem for product testing. Currently deployed industrial test strategies face rising obstacles due to the costlier RF test equipment, longer test time and lack of flexibility. Moreover, an SDR platform is field-upgradeable, which means it will support standards and scenarii not considered during the design phase. Therefore, an in-field test strategy is not anymore 'a nice to have' feature but a mandatory requirement. In this context, our research aims to invent and develop a new test methodology able to guarantee the correct functioning of the SDR platform post-fabrication and over its operational lifetime. The overall aim of our efforts is to reduce post-manufacture test cost of SDR transceivers by leveraging the reconfigurability of the platform.

For tactical radio units that must be field-upgradeable without specialized equipment, Built-in Self-Test (BIST) schemes are arguably the only way to ensure continued compliance to specifications. In this study we introduce a novel RF BIST architecture which uses Periodically Nonuniform Sampling (PNS2) of the transmitter (TX) output to evaluate compliance to spectral mask specifications. Our solution supports a stand-alone implementation, is scalable across a wide set of complex specifications and can be easily applied for in-field testing with small added hardware. Compared to existing analog/RF test techniques, this approach is not limited to a given TX architecture and does not rely on an ad-hoc TX model, which makes it ideal for SDR testing.

**Keywords**: RF BIST, Mixed-Signal/RF Test, In-Field Test, Software Radios, Periodically Nonuniform Sampling, Subsampling

### Résumé

Le secteur de communications sécurisés et portables connait une véritable révolution avec l'apparition des plateformes dites radios logicielles (Software Defined Radios, SDRs). Les performances exceptionnelles de ces systèmes sont les résultats d'une interaction assez complexe et souvent peu évidente entre le logiciel embarqué, le circuit de traitement numérique et les blocs mixtes analogiques/RF. Cette complexité limite la testabilité du produit fini. La méthodologie de test utilisée actuellement a atteint ses limites dues au cout élevé, le long temps de test et le bas degré de généralisation. De plus, les plateformes SDRs peuvent évoluer sur le terrain et elles vont supporter des standards et des scénarios qui n'ont pas été considérés pendant le la phase de conception. Donc, une stratégie de test sur le terrain (en ligne) n'est plus une caractéristique optionnelle mais une nécessité. Dans ce contexte, le but de notre recherche est d'inventer et développer une méthodologie de test capable de garantir le bon fonctionnement d'une plateforme SDR après la production et pendant sa vie. Notre objectif final est de réduire le coût du test en profitant de la reconfigurabilité de la plateforme.

Pour les radios logicielles qui doivent être mises à jour sur le terrain sans équipement spécial, les stratégies Built-In Self-Test (BIST) sont, sans doute, le seul moyen de garantir la conformité aux spécifications. Dans ce mémoire, nous introduisons une nouvelle architecture de test RF BIST qui utilise la technique de sous-échantillonnage nonuniforme à la sortie de l'émetteur (TX) d'une SDR afin d'évaluer la conformité de la masque spectrale. Notre solution s'appuie sur une implémentation autonome, est modulable et peut être appliquée pour le test sur le terrain avec des modifications minimes. Par rapport aux autres techniques de test analogiques/RF, cet approche ne dépends pas de la architecture du TX, ni d'un modèle ad-hoc, ce qui est idéale pour le test des SDRs.

Mots clés : RF BIST, Test analogique mixt/RF, test sur terrain, radio logicielle, SDR, sous-échantillonnage nonuniform de deuxième ordre, sous-échantillonnage

# **Contents**

| A                         | bstra | $\mathbf{ct}$ |                                                                         |    | v    |

|---------------------------|-------|---------------|-------------------------------------------------------------------------|----|------|

| $\mathbf{R}$              | ésum  | é             |                                                                         |    | vii  |

| $\mathbf{C}$              | onter | $_{ m nts}$   |                                                                         |    | ix   |

| $\mathbf{S}_{\mathbf{J}}$ | ymbo  | ls & Ab       | brevations                                                              |    | xiii |

| Li                        | st of | Figures       |                                                                         |    | xv   |

| 1                         | Intr  | oduction      | n                                                                       |    | 1    |

|                           | 1.1   | Backgro       | ound                                                                    |    | 1    |

|                           | 1.2   | Previous      | s Work                                                                  |    | 2    |

|                           | 1.3   | Our Wo        | rk                                                                      |    | 3    |

|                           | 1.4   | Research      | h Contributions                                                         |    | 4    |

|                           | 1.5   | Thesis (      | Organisation                                                            | •  | 5    |

| <b>2</b>                  | Rés   | umé (Fr       | ançais)                                                                 |    | 7    |

|                           | 2.1   | Introduc      | ction                                                                   |    | 7    |

|                           | 2.2   | Radio lo      | ogicielle                                                               |    | 8    |

|                           | 2.3   | Test RF       | ·<br>· · · · · · · · · · · · · · · · · · ·                              |    | 9    |

|                           |       | 2.3.1         | l'est et testabilité des systèmes électroniques                         |    | 9    |

|                           |       | 2.3.2 I       | Défis dans le test des systèmes RF                                      |    | 11   |

|                           |       | 2.3.3 H       | Etat de l'art du domaine de testabilité des systèmes RF                 |    | 12   |

|                           |       | 2.3.4         | Conclusions                                                             |    | 15   |

|                           | 2.4   | Applicat      | tion de la technique de sous-échantillonnage non-uniforme au test intég | ré |      |

|                           |       | des éme       | tteurs RF flexibles                                                     |    | 16   |

|                           |       | 2.4.1 I       | ntroduction                                                             |    | 16   |

|                           |       | 2.4.2         | Outil théoriques                                                        |    | 17   |

|                           |       | 2.4.3 I       | Description générale de l'architecture de test                          |    | 22   |

|                           |       | 2.4.4 I       | Résultats en simulation                                                 |    | 23   |

|   |                        | 2.4.5 Conclusions et perspectives                     | 27 |

|---|------------------------|-------------------------------------------------------|----|

| 3 | Soft                   | tware Defined Radio                                   | 29 |

|   | 3.1                    | Introduction                                          | 29 |

|   | 3.2                    | Some History                                          | 30 |

|   | 3.3                    | What is an SDR                                        | 30 |

|   | 3.4                    | SDR Architectures                                     | 31 |

|   |                        |                                                       | 32 |

|   |                        |                                                       | 35 |

|   |                        |                                                       | 36 |

|   | 3.5                    |                                                       | 12 |

|   | 5.5                    | •                                                     | 12 |

|   |                        |                                                       |    |

|   |                        | 0                                                     | 13 |

|   |                        |                                                       | 13 |

|   |                        | <u>.</u>                                              | 18 |

|   |                        | 3.5.5 Digital FoMs                                    | 19 |

|   |                        | 3.5.6 Final Remarks on FoMs for RF Transceivers       | 50 |

|   | 3.6                    | Conclusions                                           | 50 |

| 4 | $\mathbf{R}\mathbf{F}$ | Testing                                               | 1  |

| _ | 4.1                    | 8                                                     | 51 |

|   | 1.1                    | · · · · · · · · · · · · · · · · · · ·                 | 52 |

|   | 4.2                    |                                                       | 54 |

|   |                        | 9 , 9                                                 |    |

|   | 4.3                    | 1 1                                                   | 66 |

|   | 4.4                    |                                                       | 58 |

|   |                        | •                                                     | 58 |

|   |                        | 6                                                     | 60 |

|   |                        | 4.4.3 Model-Based RF Test Strategies                  | 31 |

|   |                        | 4.4.4 Alternate Tests                                 | 3  |

|   | 4.5                    | Conclusions                                           | 8  |

| 5 | Uno                    | dersampling                                           | 9  |

|   | 5.1                    | Introduction                                          | 39 |

|   | 5.2                    |                                                       | 70 |

|   | 5.3                    |                                                       | 70 |

|   | 5.5                    |                                                       | 72 |

|   |                        | * U                                                   |    |

|   |                        | 1 0                                                   | 74 |

|   |                        |                                                       | 78 |

|   | 5.4                    | Conclusions                                           | 30 |

| 6 | SDI                    | R Test Strategy                                       | 31 |

|   | 6.1                    | Introduction                                          | 31 |

|   | 6.2                    | General Description of the Proposed Test Architecture | 33 |

|   | 6.3                    | 1                                                     | 35 |

|   |                        |                                                       | 36 |

|   |                        | 1                                                     | 36 |

|   |                        |                                                       | 38 |

|   | C 1                    |                                                       |    |

|   | 6.4                    |                                                       | 38 |

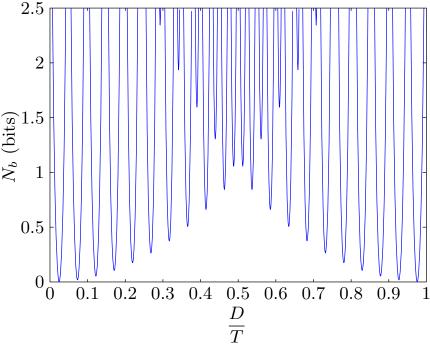

|   |                        | 6.4.1 Choice of <i>D</i>                              | 38 |

|    |       | 6.4.2  | Reconstruction Robustness w.r.t. Uncertainties in $D$ | . 90  |

|----|-------|--------|-------------------------------------------------------|-------|

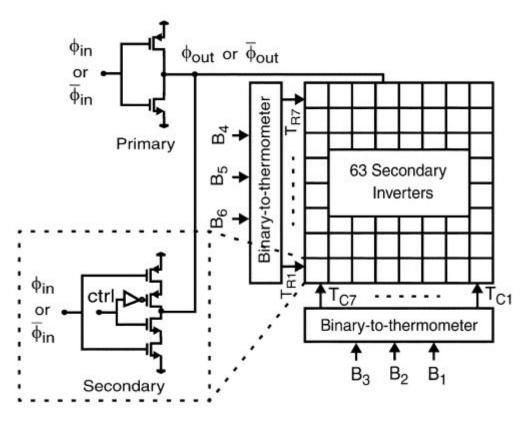

|    |       | 6.4.3  | DCDE Practical Implementation                         | . 90  |

|    |       | 6.4.4  | Delay Estimation                                      | . 91  |

|    | 6.5   | Sampl  | e and Hold Elements                                   |       |

|    |       | 6.5.1  | Charge-domain sampling                                | . 103 |

|    |       | 6.5.2  | Improved BIST Architecture Based on CBS               | . 105 |

|    | 6.6   | Simula | ation Results                                         | . 105 |

|    |       | 6.6.1  | General Simulation Parameters                         | . 106 |

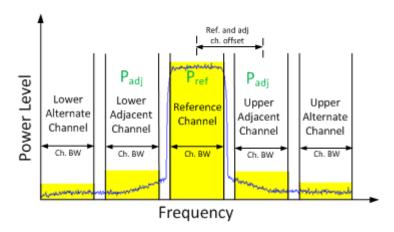

|    |       | 6.6.2  | Adjacent Channel Power Ratio estimation               | . 107 |

|    |       | 6.6.3  | Digital PNS2 Reconstruction                           | . 108 |

|    |       | 6.6.4  | Analysis of Time-Skew Detection Techniques            | . 111 |

|    |       | 6.6.5  | ACPR Simulation                                       | . 117 |

|    | 6.7   | Conclu | asions                                                | . 119 |

| 7  | Con   | clusio | ns and Future Work                                    | 121   |

|    | 7.1   | Conclu | asions                                                | . 121 |

|    | 7.2   | Future | e Work                                                | . 122 |

| Bi | bliog | graphy |                                                       | 123   |

# Symbols & Abbrevations

| *                   | Convolution operator                      | k                  | $\left\lceil \frac{2f_l}{B} \right\rceil$ |

|---------------------|-------------------------------------------|--------------------|-------------------------------------------|

| $\beta$             | Kaiser window parameter                   | $k^+$              | k+1                                       |

| $\delta(t)$         | Dirac impulse                             | $n_w$              | Number of FIR taps                        |

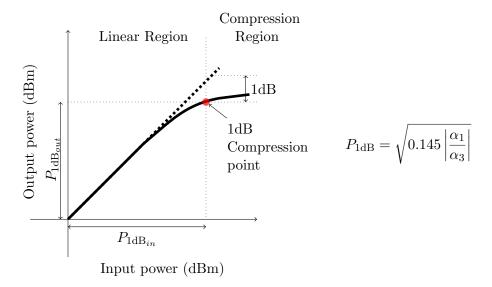

| $\hat{x}$           | Estimate of parameter $x$                 | $P_{\mathrm{1dB}}$ | 1dB Compression Point                     |

| $\lceil * \rceil$   | ceiling operation                         | ACPR               | Adjacent Channel Power Ratio              |

| $\lfloor * \rfloor$ | floor operation                           | ADC                | Analog to Digital Converter               |

| $\mu$               | Step parameter for LMS algorithm          | AM                 | Amplitude Modulated                       |

| $arepsilon_G$       | Gain mismatch between two channels        | AMS                | Analog and Mixed Signals                  |

| B                   | Signal Bandwidth                          | ATE                | Automatic Test Equipment                  |

| D                   | Phase delay between 2 ADCs                | auRX               | auxiliary receiver                        |

| D                   | ,                                         | BER                | Bit Error Rate                            |

| $f(\cdot)$          | Continuous time function                  | BIST               | Built-In Self-Test                        |

| F(f)                | Frequency domain representation           | CBS                | Charge-Based Sampling                     |

| $f[\cdot]$          | Discrete time function                    | DCDE               | Digitally Controlled Delay Element        |

| $f_c$               | Career Frequency                          | $\mathrm{DfT}$     | Design for Testability                    |

| $f_l, f_H$          | RF signal position, $f_l = f_c - B/2$ and | DUT                | Device Under Test                         |

|                     | $f_H = f_c + B/2$                         | EVM                | Error Vector Magnitude                    |

| $f_s$               | Sampling frequency                        | FC                 | Fault Coverage                            |

| $J(\cdot)$          | Quadratic cost function                   | FIR                | Finite Impulse Response                   |

| FM<br>FoM | Frequency Modulated                    | PNS2 | Periodically Nonuniform Sampling of Second order |

|-----------|----------------------------------------|------|--------------------------------------------------|

| I/Q       | Figure of Merit  In phase: Quadrature  | QAM  | Quadrature Amplitude Modulation                  |

| IC        | Integrated Circuits                    | RF   | Radio Frequency                                  |

| IMD       | Intermodulation Distortion             | RMS  | Root-Mean-Square                                 |

| IP3       | Third Order Interception Point         | RX   | Receiver                                         |

| LMS       | Least Mean Squares                     | SDR  | Software Defined Radio                           |

| LNA       | Low Noise Amplifier                    | SNR  | Signal-to-Noise Ratio                            |

| LO        | Local Oscillator                       | SoC  | System on Chip                                   |

| MLMS      | S Multivariable Least Mean Squares     | TIAD | C Time-Interleaved Analog-to-Digital             |

| OFDN      | M Orthogonal Frequency-Division Multi- |      | Converter                                        |

|           | plexing                                | TX   | Transmitter                                      |

| PA        | Power Amplifier                        | VBS  | Voltage-Based Sampling                           |

| PAE       | Power-Added Efficiency                 | WCDI | MA Wideband Code Division Multiple               |

| PCB       | Printed Circuit Boards                 |      | Access                                           |

| PHY       | Physical layer                         | YL   | Yield Loss                                       |

# **List of Figures**

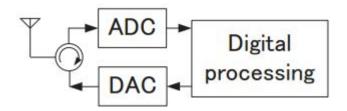

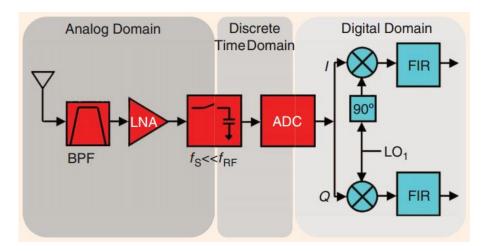

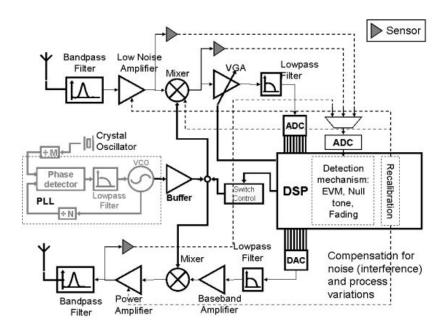

| 1.1  | General architecture of an SDR                                                                                                                                                                   | 2  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2  | FlexNet. Vehicular wideband SDR platform sold by Thales Communications and                                                                                                                       |    |

|      | Security                                                                                                                                                                                         | 4  |

| 2.1  | Architecture générale d'une SDR                                                                                                                                                                  | 8  |

| 2.2  | Automated RF test equipment ATES500 developed by DiagnoSYS                                                                                                                                       | 12 |

| 2.3  | Principe du bouclage                                                                                                                                                                             | 13 |

| 2.4  | Principe des tests alternatifs                                                                                                                                                                   | 15 |

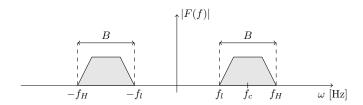

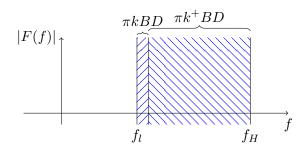

| 2.5  | Bandpass Signal                                                                                                                                                                                  | 17 |

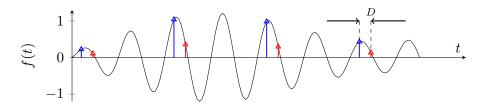

| 2.6  | Time domain representation of PNS2 operation                                                                                                                                                     | 18 |

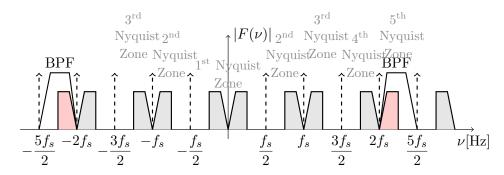

| 2.7  | Frequency spectrum illustration of standard bandpass sampling                                                                                                                                    | 18 |

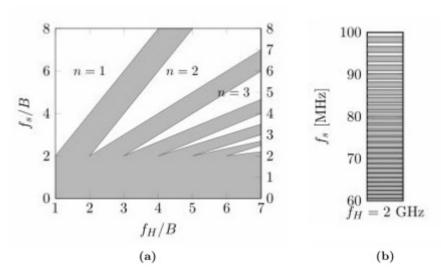

| 2.8  | The constraints on the sampling rate $f_s$ for undersampling [Vaughan et al., 1991]:                                                                                                             |    |

|      | 2.8a in general case and 2.8b a particular case where $f_H = 2.03$ GHz and $B = 30$                                                                                                              |    |

|      | MHz. The white regions are situations where the undersampling will not result                                                                                                                    |    |

|      | in aliasing. The gray regions represent conditions where alias is occurring                                                                                                                      | 19 |

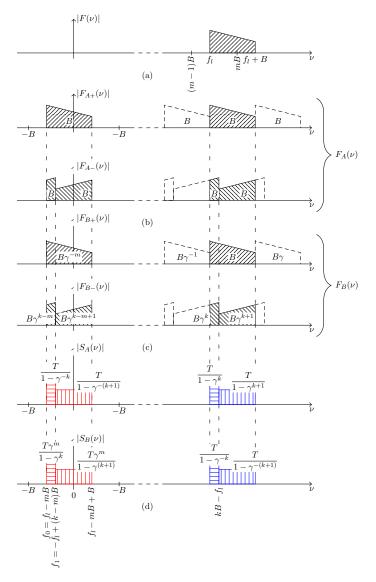

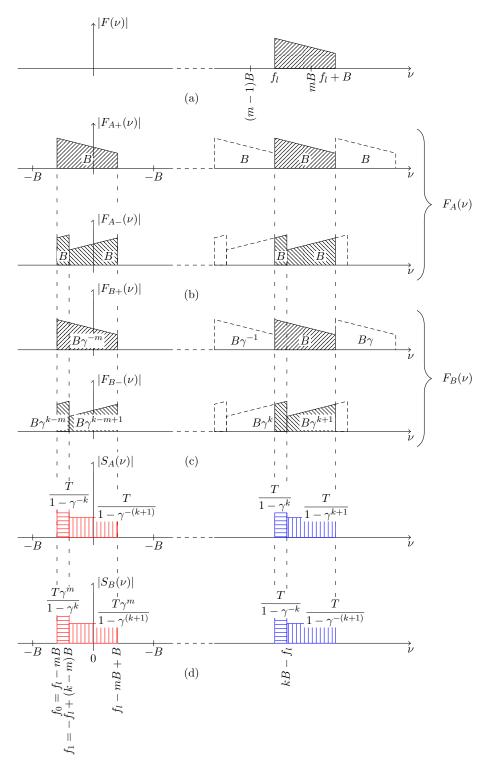

| 2.9  | Periodically nonuniform bandpass sampling of second order. Fig. 2.9a represents                                                                                                                  |    |

|      | the original passband signal to be reconstructed. Fig 2.9b sketches the spectrum                                                                                                                 |    |

|      | $F_A(\nu)$ resulting from sampling by the sample set A. The top figure shows only the                                                                                                            |    |

|      | positive frequency components $F_{A+}(\nu)$ resulting from sampling, while the bottom                                                                                                            |    |

|      | figure shows only the negative frequency components $F_{A-}(\nu)$ . The spectra of the set B is depicted as $F_{B+}(\nu)$ and $F_{B-}(\nu)$ in Fig. 2.9c. $S_A(\nu)$ and $S_B(\nu)$ in Fig. 2.9d |    |

|      | represent the interpolants (reconstructing filters) which are designed to restore                                                                                                                |    |

|      | the original signal                                                                                                                                                                              | 21 |

| 2.10 |                                                                                                                                                                                                  |    |

|      | ification required to implement the loopback circuitry within the transceiver to                                                                                                                 |    |

|      | enable self-test                                                                                                                                                                                 | 22 |

| 2.11 | Complete block diagram of the proposed BIST architecture                                                                                                                                         | 23 |

| 2.12 | Block diagram of the simulated homodyne transmitter                                                                                                                                              | 24 |

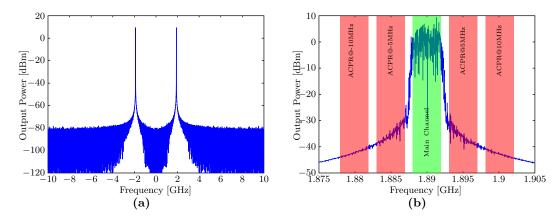

| 2.13 | ACPR Measurement. Left figure shows the power spectrum of the signal at the output of the receiver. A FFT transform of $2^{19}$ points was used. The right figure shows the same spectrum around the center frequency $f_c$ . The main channel and |    |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 0.14 | the adjacent channels used for ACPR calculation are highlighted                                                                                                                                                                                    | 25 |

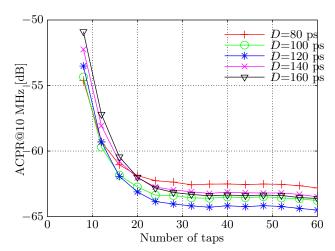

| 2.14 | Evolution of the ACPR estimate w.r.t. the number of taps in FIR implementation and the value of $D$                                                                                                                                                | 25 |

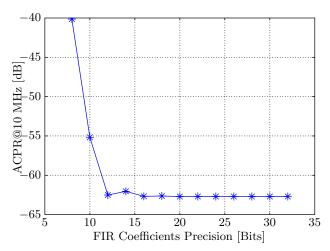

| 9 15 | Evolution of the ACPR estimate w.r.t. FIR filters taps precision                                                                                                                                                                                   | 26 |

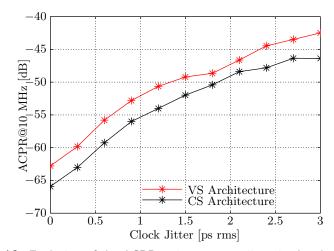

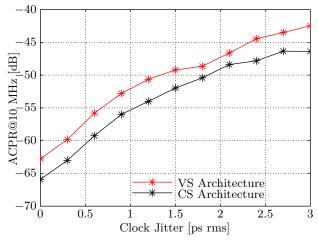

|      | Evolution of the ACPR estimate w.r.t. jitter in the clock oscillator                                                                                                                                                                               | 26 |

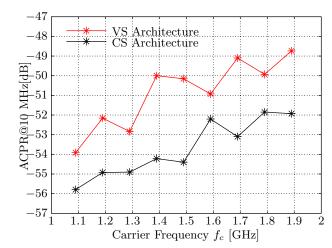

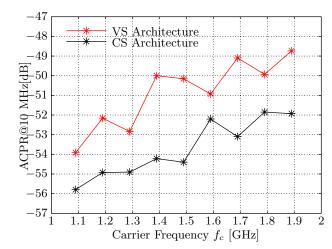

|      | Evolution of the ACPR estimate w.r.t. carrier frequency                                                                                                                                                                                            | 27 |

| 3.1  | SDR concept as envisioned by Mitola [Mitola, 1993]                                                                                                                                                                                                 | 31 |

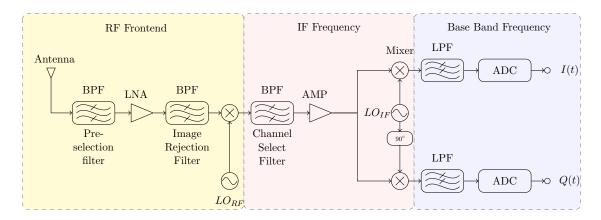

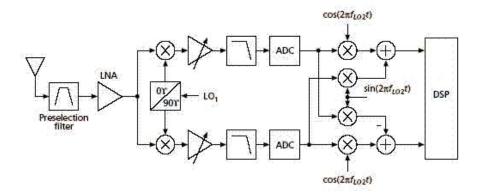

| 3.2  | Architecture of a heterodyne receiver                                                                                                                                                                                                              | 32 |

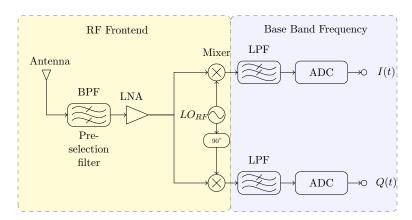

| 3.3  | Architecture of a Zero-IF receiver                                                                                                                                                                                                                 | 34 |

| 3.4  | Architecture of a low IF receiver                                                                                                                                                                                                                  | 35 |

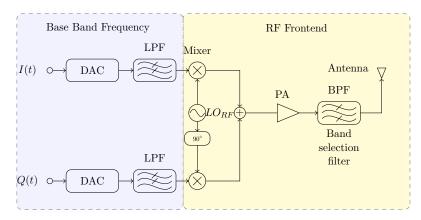

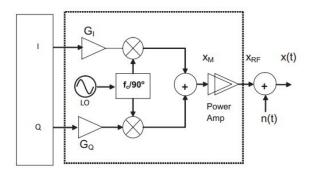

| 3.5  | Architecture of a homodyne transmitter                                                                                                                                                                                                             | 36 |

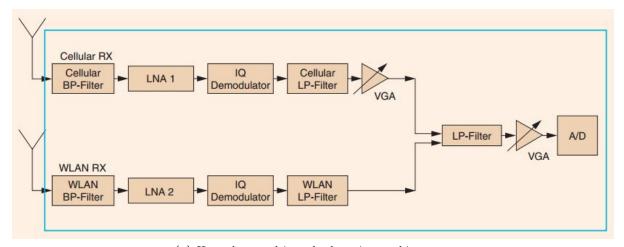

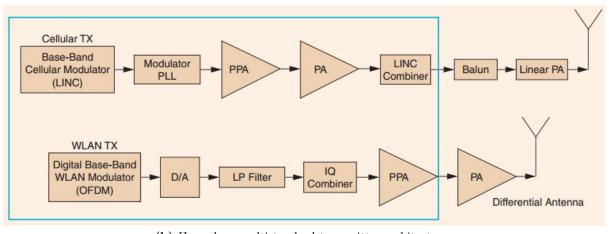

| 3.6  | Architecture of a multistandard terminal as proposed by Agnelli et al. [2006]                                                                                                                                                                      | 38 |

| 3.7  | Architecture of a bandpass sampling receiver [Cruz et al., 2010]                                                                                                                                                                                   | 40 |

| 3.8  | Two-stages bandpass receiver [Fudge et al., 2013]                                                                                                                                                                                                  | 41 |

| 3.9  | ACPR Definition                                                                                                                                                                                                                                    | 43 |

| 3.10 | Definition of the 1 dB compression point                                                                                                                                                                                                           | 45 |

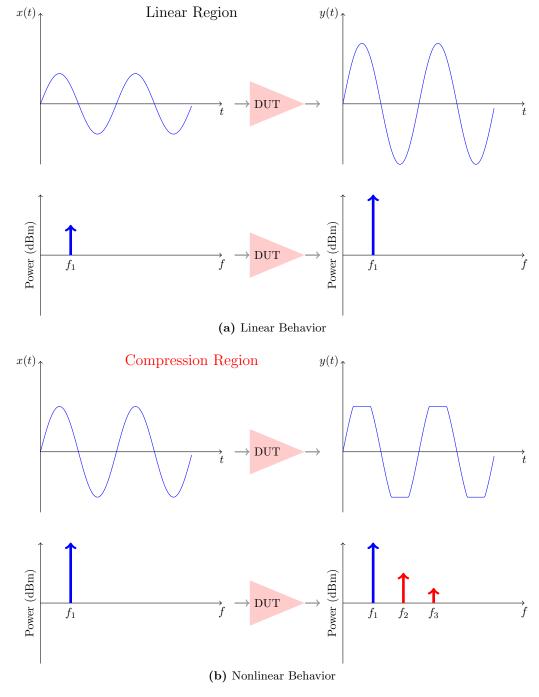

| 3.11 | Visualizing the effects of non-linearity                                                                                                                                                                                                           | 46 |

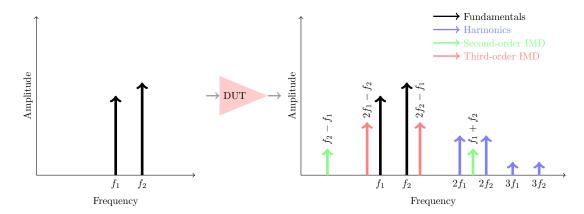

|      | Intermodulation distortion - Graphical representation                                                                                                                                                                                              | 47 |

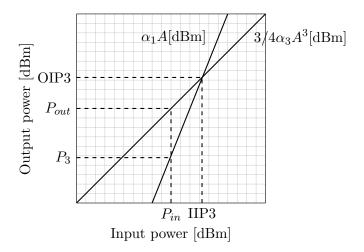

|      | IP3 - Graphical representation                                                                                                                                                                                                                     | 48 |

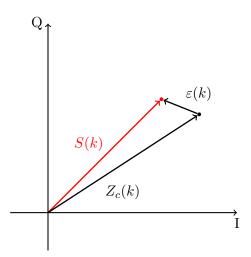

| 3.14 | EVM definition                                                                                                                                                                                                                                     | 49 |

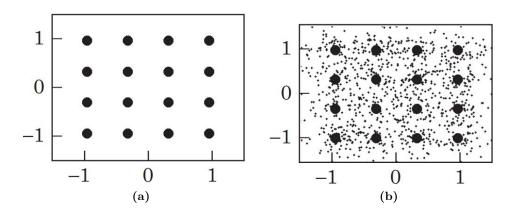

|      | Constellation diagram of a 16QAM signal. Two levels of noise power have been                                                                                                                                                                       |    |

|      | considered                                                                                                                                                                                                                                         | 50 |

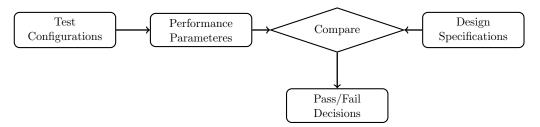

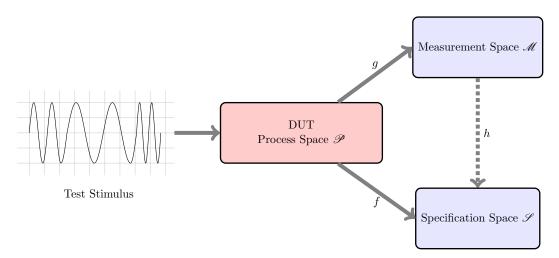

| 4.1  | Specifications-based test strategy [Cheng and Chang, 2010]                                                                                                                                                                                         | 54 |

| 4.2  | Automated RF test equipment ATES500 developed by DiagnoSYS                                                                                                                                                                                         | 56 |

| 4.3  | Instrumentation employed in testing a software defined radio transmitter where                                                                                                                                                                     |    |

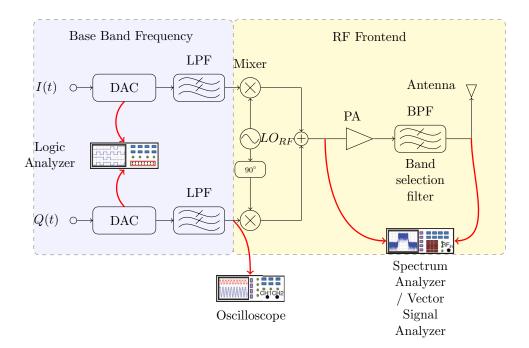

|      | several instruments are combined                                                                                                                                                                                                                   | 57 |

| 4.4  | Loopback test architecture                                                                                                                                                                                                                         | 58 |

| 4.5  | Model of an generic quadrature transmitter [Acar and Ozev, 2007]                                                                                                                                                                                   | 62 |

| 4.6  | Principles of the alternate test paradigm                                                                                                                                                                                                          | 64 |

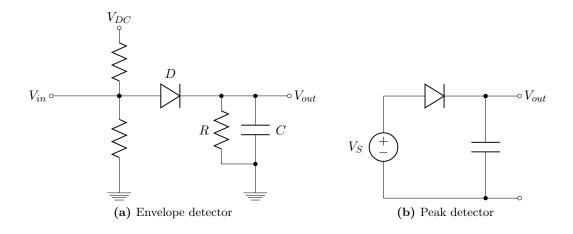

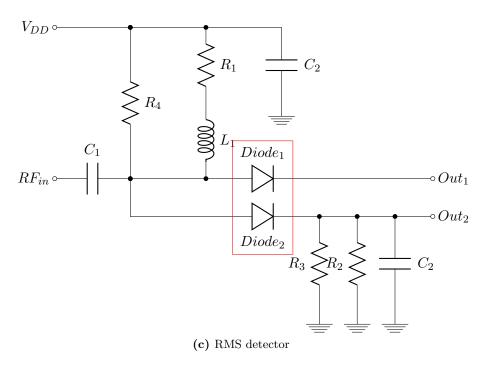

| 4.7  | Three on-chip circuits that can be used as RF sensors for alternate tests [Natara-                                                                                                                                                                 |    |

|      | jan et al., 2008]                                                                                                                                                                                                                                  | 65 |

| 4.8  | Alternate-test-based tuning and testing strategy [Chatterjee et al., 2009]                                                                                                                                                                         | 67 |

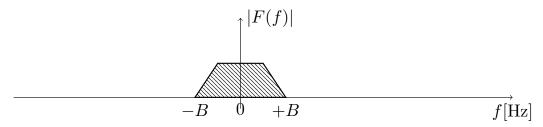

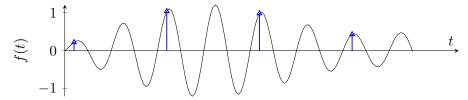

| 5.1  | Sampling of a typical baseband signal                                                                                                                                                                                                              | 71 |

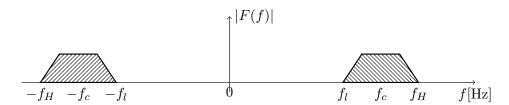

| 5.2  | A bandpass signal occupying a bandwidth $B$ and located around $f_c$                                                                                                                                                                               | 71 |

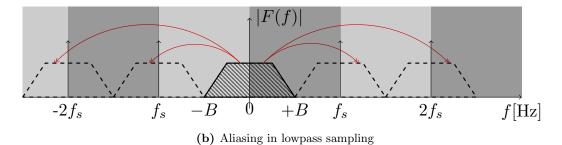

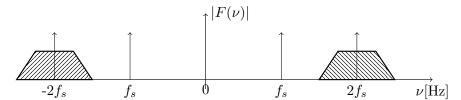

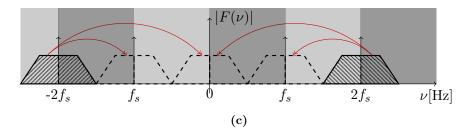

| 5.3  | Graphical representation of spectral replication of undersampling                                                                                                                                                                                  | 73 |

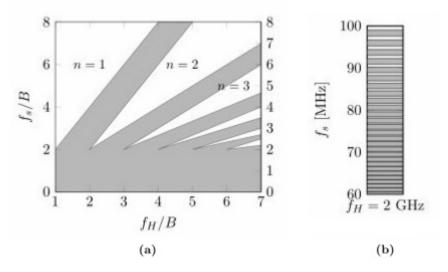

| 5.4  | The constraints on the sampling rate $f_s$ for undersampling [Vaughan et al., 1991]:                                                                                                                                                               |    |

|      | 5.4a in general case and 5.4b a particular case where $f_H = 2.03$ GHz and $B = 30$                                                                                                                                                                |    |

|      | MHz. The white regions are situations where the undersampling will not result                                                                                                                                                                      |    |

|      | in aliasing. The gray regions represent conditions where alias is occurring                                                                                                                                                                        | 73 |

| 5.5  | Graphical representation of periodically nonuniform bandpass sampling of second                                                                                                                                                                    |    |

|      | order                                                                                                                                                                                                                                              | 76 |

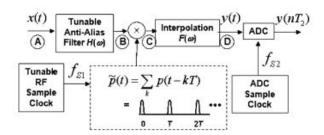

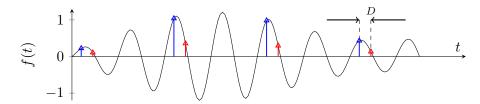

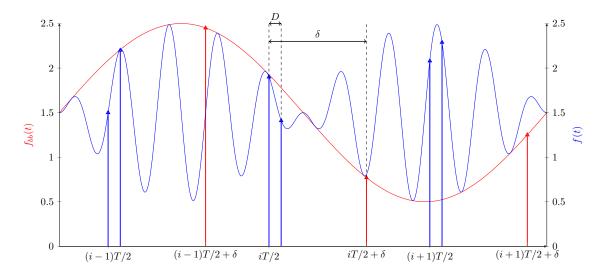

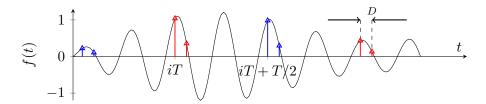

| 5.6  | Time domain representation of PNS2 operation                                                                                                                                                                                                       | 77 |

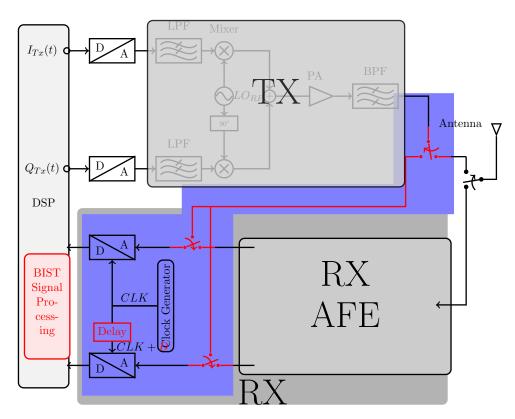

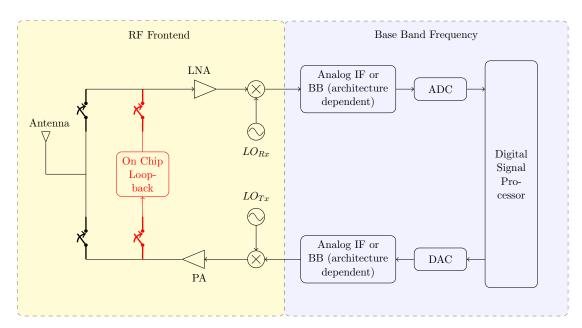

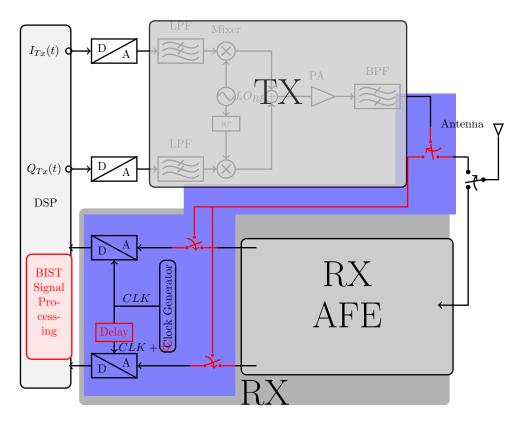

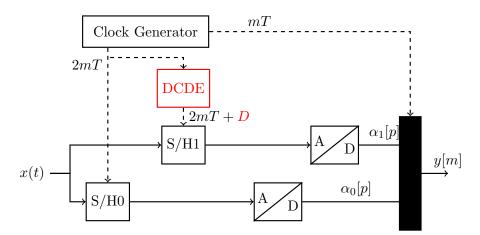

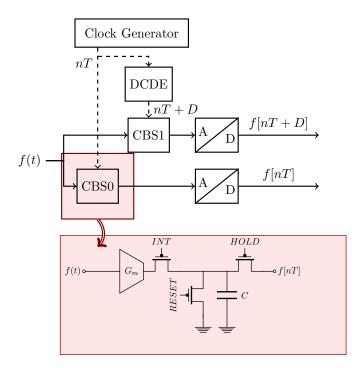

| 6.1  | Block diagram of the proposed BIST architecture. The red blocks are the modification required to implement the loopback circuitry within the transceiver to enable self-test |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

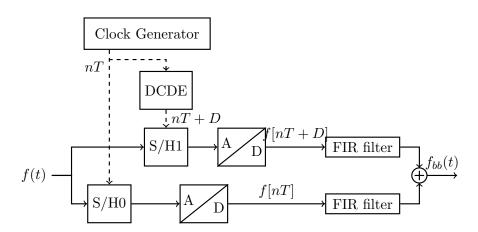

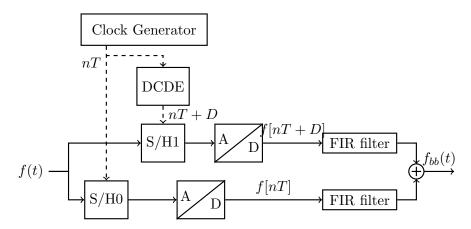

| 6.2  | Complete block diagram of the proposed BIST architecture                                                                                                                     |

| 6.3  | Graphical representation of the sampling process for digital PNS2 reconstruction 87                                                                                          |

| 6.4  | An estimate relation between the number of bits of resolution lost while inter-                                                                                              |

|      | polating a bandpass signal and the value of D. A particular case: $k = 20$ and                                                                                               |

|      | $\Delta k = 0.5.$                                                                                                                                                            |

| 6.5  | Architecture of 6-bit DCDE [Haftbaradaran and Martin, 2008] 91                                                                                                               |

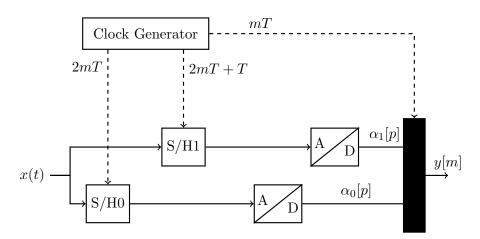

| 6.6  | Block diagram of two channel time-interleaved ADC architecture                                                                                                               |

| 6.7  | Block diagram of the proposed BIST architecture                                                                                                                              |

| 6.8  | Frequency spectrum at the output of a two channel TIADC affected by a time-                                                                                                  |

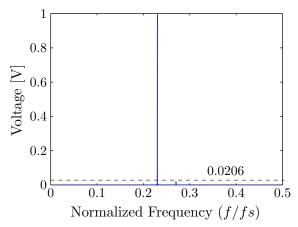

|      | skew of $d = 172$ ps, for an input sinewave of amplitude 1 and frequency $0.23f_s$ . 94                                                                                      |

| 6.9  | Block diagram of the time-skew detector as proposed by Jamal et al. [2004] 95                                                                                                |

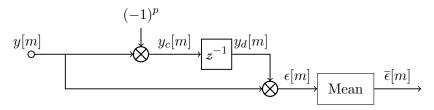

|      | Time domain representation of PNS2 sampling                                                                                                                                  |

|      | Frequency domain operation of the PNS2 technique                                                                                                                             |

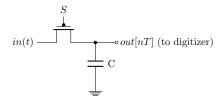

|      | Typical voltage sampling circuit                                                                                                                                             |

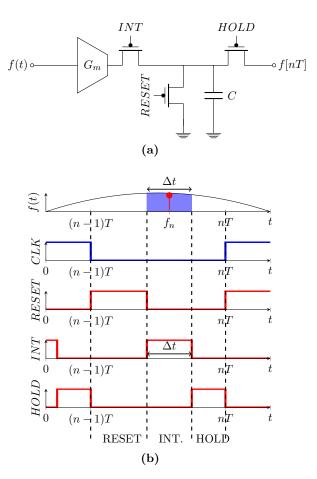

|      | Circuit diagram and operating principle of a charge-domain sampler 104                                                                                                       |

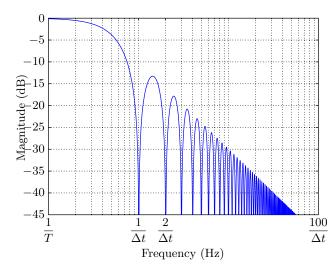

|      | Transfer function of an ideal CBS circuit. $\Delta t$ is the period of integration 105                                                                                       |

| 6.15 | Block diagram of the improved BIST architecture                                                                                                                              |

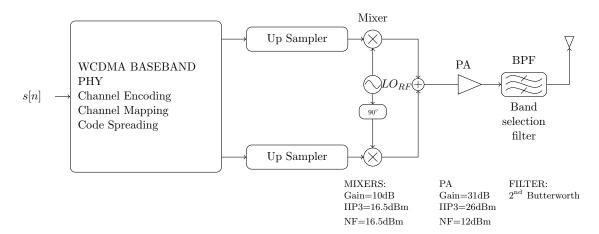

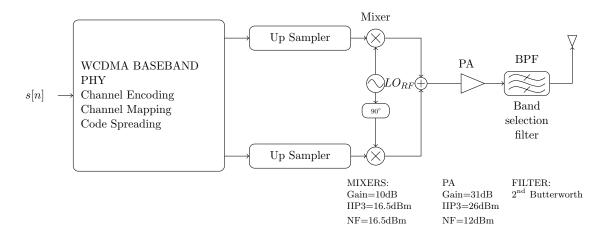

| 6.16 | Block diagram of the simulated homodyne transmitter                                                                                                                          |

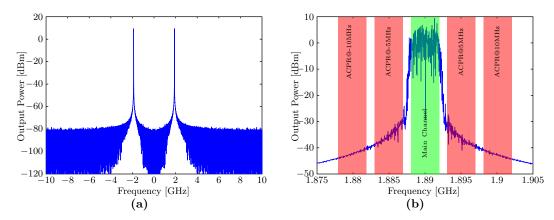

| 6.17 | ACPR Measurement. Left figure shows the power spectrum of the signal at the                                                                                                  |

|      | output of the receiver. A FFT transform of 2 <sup>19</sup> points was used. The right figure                                                                                 |

|      | shows the same spectrum around the center frequency $f_c$ . The main channel and                                                                                             |

|      | the adjacent channels used for ACPR calculation are highlighted $108$                                                                                                        |

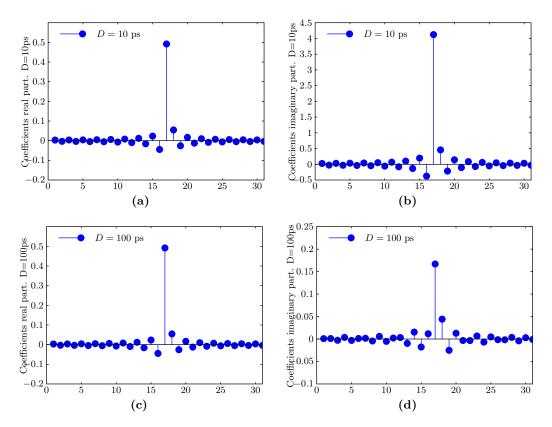

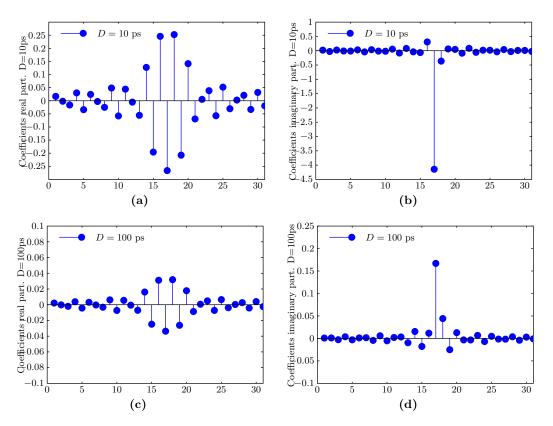

| 6.18 | Influence of the value of $D$ on the magnitude of the first FIR coefficients 109                                                                                             |

| 6.19 | Influence of the value of $D$ on the magnitude of the second FIR coefficients 110                                                                                            |

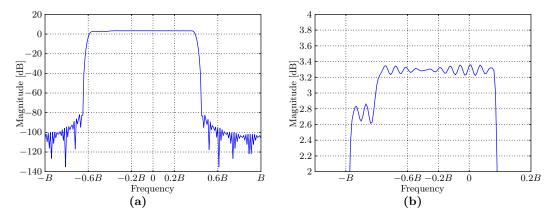

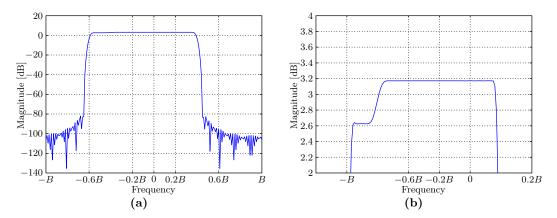

|      | Frequency response of the first interpolant when no Kaiser windowing is used $$ $110$                                                                                        |

| 6.21 | Frequency response of the first interpolant when a Kaiser window with a $\beta = 6$                                                                                          |

|      | parameter is used                                                                                                                                                            |

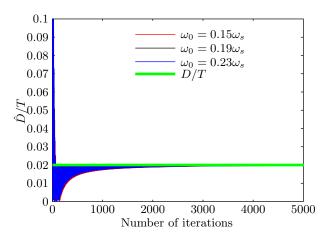

| 6.22 | Time-skew estimation over time. It can be observed that the estimations $\hat{D}/T$                                                                                          |

|      | converge to ideal value of $D/T$ every time. However the quality of the estimation                                                                                           |

|      | peaks when $\omega_0 = \omega_s/4$ and worsens at higher input frequency                                                                                                     |

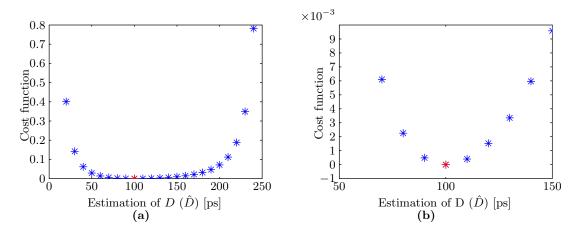

| 6.23 | Cost function for several values of $\hat{D}$ . Fig. 6.23b plots a zoom of the left figure                                                                                   |

|      | around $\hat{D} = D$                                                                                                                                                         |

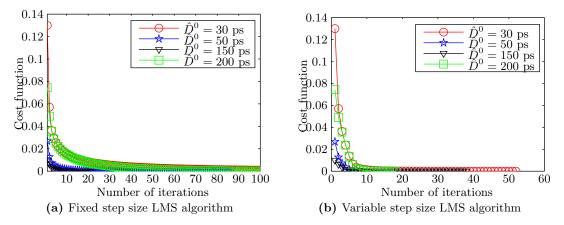

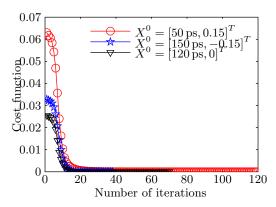

|      | LMS algorithm: evolution of cost function for several values of $\hat{D}_0$                                                                                                  |

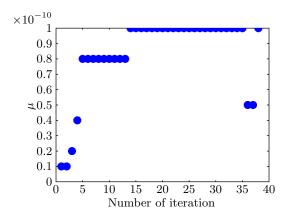

|      | Evolution of the step size parameter for an initial value of $\hat{D}^0 = 150 \text{ ps} \dots \dots 114$                                                                    |

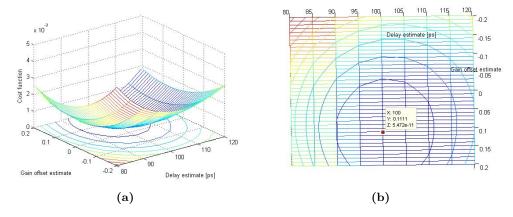

|      | Cost function $J(\hat{D}, \widehat{\varepsilon_G})$ for several values of $\hat{D} \in [80 \text{ ps}, 120 \text{ ps}]$ and $\widehat{\varepsilon_G} \in [-0.2, 0.2]$        |

|      | Multivariable LMS: evolution of the cost function for several value of $X^0$ 116                                                                                             |

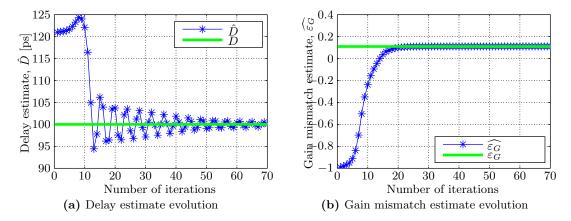

|      | Multivariable LMS: evolution of the estimates $X$                                                                                                                            |

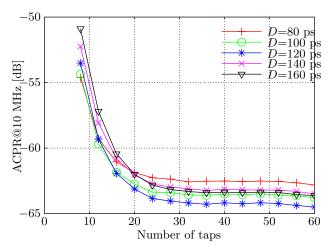

| 0.29 | Evolution of the ACPR estimate w.r.t. the number of taps in FIR implementation                                                                                               |

| 6 20 | and the value of $D$                                                                                                                                                         |

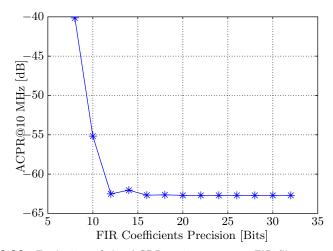

|      | Evolution of the ACPR estimate w.r.t. FIR inters taps precision                                                                                                              |

|      | Evolution of the ACPR estimate w.r.t. pitter in the clock oscillator                                                                                                         |

| 0.02 | Envolution of the ACL it estimate with carrier frequency                                                                                                                     |

### Chapter 1

### Introduction

### 1.1 Background

The unabated improvement in speed and integration density of integrated circuits (IC) has made possible the Software Defined Radio concept proposed by Mitola [Mitola, 1993]. An SDR is a Radio in which some (or all) of the physical layer functions are programmable. The advent of the Software-Defined Radio (SDR) platform [Woh et al., 2011] can be traced back to the defense industry, motivated by the fact that the multitude of increasingly complex military digital communication standards could not coexist in the field without a novel, flexible radio architecture. Consequently to the introduction of the SDR paradigm, nowadays reliable and interoperable terminals spanning hand-held, vehicular, airborne and dismounted radios, as well as base-stations (fixed and maritime) are routinely deployed.

The benefits of SDR, compared to the traditional radio systems, are compelling:

- Traditional hardware based radio devices limit cross-functionality and can only be modified through physical intervention. By contrast, software defined radio technology provides an efficient and comparatively inexpensive solution to this problem, allowing multi-mode, multi-band and/or multi-functional wireless devices that can be enhanced using software upgrades.

- SDR enables a family of radio products to be implemented using a common platform architecture, allowing new products to be more quickly introduced into the market.

- SDR enables software to be reused across different radio products, reducing development costs dramatically.

- Remote reprogramming, allowing debugging to be carried out while a radio is in service, thus reducing the effort and costs associated with operation and maintenance.

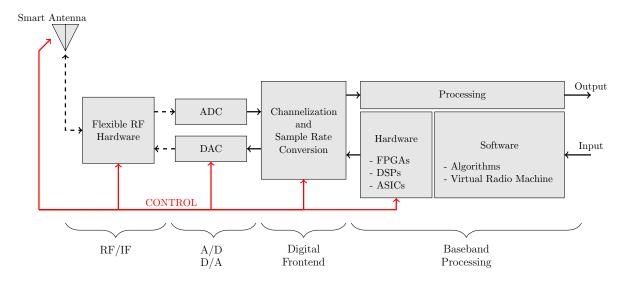

The outstanding flexibility and performance of these radios result from careful trade-offs among advanced analog/RF circuitry, high-speed reconfigurable digital hardware and sophisticated real-time software (Fig. 1.1). However, the inherent adaptability of these multistandard platforms hinders the testability of the finished units. Established mixed-signal and RF test strategy are either too time-consuming (thus costly) or can't ensure compliance with several modulations standards, including those yet to appear. Unlike conventional transmitters, SDR

Figure 1.1: General architecture of an SDR

platforms must satisfy strict requirements under a wide variety of operating modes. Furthermore, rugged tactical radio units are expected to remain in service for many years, continuously evolving to support newer standards, through software-only field upgrades. Finally, an SDR tactical radio could possibly remain in storage or reserve for long periods, and then be reactivated, reprogrammed and put in active service in a matter of minutes. Ensuring the operational compliance of the terminal in such a dynamic situation over timespans of years is a vital concern. Thus, new test strategies must be invented, able to cover thoroughly and efficiently all key specifications of the radio unit. In this context, the aim of our work is to invent and develop a new test methodology able to guarantee the correct functioning of the SDR platform post-fabrication and over its operational lifetime

#### 1.2 Previous Work

Over the past few years, analog and mixed-signal test and testability has been a subject of intense research. Traditional production testing of transceivers relies on specialized machines, known as Automated Test Equipment (ATE) units, [Wolf et al., 2006; Cruz et al., 2010]. ATEs are fast, accurate and reconfigurable, but also very expensive and hard to master. Besides, they are too cumbersome and fragile for the harsh conditions typical of tactical radio deployments. These shortcomings gave impulse to continuing research efforts for cost effective alternatives.

One such alternative, borrowed from digital testing research, is the idea of introducing Built-In Self-Test (BIST) techniques to eliminate or reduce the need for external instrumentation. Analog and mixed-signal (AMS) BIST techniques consist in placing the test circuitry directly on the same die (or on-board) as the desired Device Under Test (DUT) and generally entail additional circuitry and reuse of resources available (DSP, converters, memory). Compared to the digital test strategies that have matured to a high-level of automation (insertion of test ports and generation of test vectors), the test of AMS BIST strategies are still device (or architecture) specific. It could be argued that this is mainly because, contrariwise to digital circuits, truly generic analog faults model are yet to be defined.

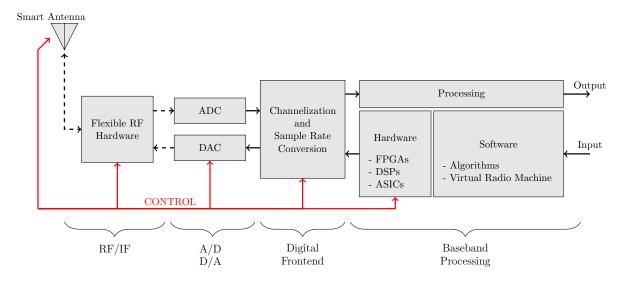

Several AMS BIST techniques targeting specifically RF transceivers (RF BIST) have been proposed. The loopback approach is one of the most cited RF BIST technique [Onabajo et al., 2009; Negreiros et al., 2007; Dabrowski and Bayon, 2004; Nassery and Ozev, 2012; Haldes

et al., 2005]. In a nutshell, RF loopback consists in using the transmitting part (TX) to excite some parts or all of the receiver (RX). The key feature is to add components that allow the reconfiguration of the on-board (or on-chip) resources to carry out some type of characterization.

Loopback BIST is an attractive proposition, although it has two major drawbacks. The first one is fault masking, a situation where a (non-catastrophic) failure of the TX is covered up by an exceptionally good RX, or the inverse. A marginal product could then go undetected (test escapes). The second drawback of BIST loopback is that it is not applicable directly to all transceivers architectures (e.g. [Dabrowski and Ramzan, 2010]). In spite of its shortcomings, loopback BIST has been often implemented and reported as effective: Onabajo et al. [2009]; Negreiros et al. [2007]; Dabrowski [2003]; Dabrowski and Bayon [2004]; Haldes et al. [2005]; Nassery and Ozev [2012]. The large number of publications shows the continuing interest in the topic.

Several sensitization techniques that aim to improve loopback observability (i.e. combat fault masking) have been proposed. In Erdogan and Ozev [2008]; Nassery and Ozev [2012] the authors rely on analytical behavioral models and simple input stimuli (sinusoid or multi-tone signals) to extract the most important nonlinearities and IQ imbalances in a quadrature transceiver (phase mismatch, gain mismatch, DC offset, and time-skew). This approach yields few test-escapes and demands low computational effort. However, it is limited by the completeness of the model. Under configurations unforeseen by the model, the entire test strategy will fail.

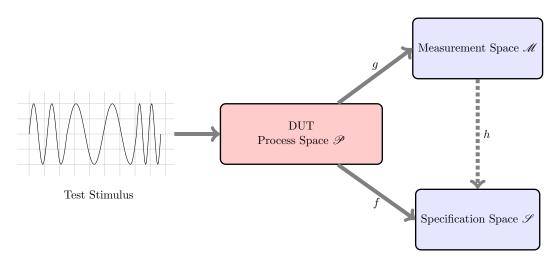

Another interesting RF BIST strategy is 'alternate test', in which the standard specifications are predicted from a set of 'easily' measurable parameters that are strongly correlated with the specifications one wishes to check [Natarajan et al., 2008; Halder et al., 2008; Haider et al., 2003; Maliuk et al., 2010]. The alternate tests are based on heuristic models, obtained a priori through simulations. These alternate tests are prone to errors such as test-escapes and yield loss, which are hard to predict. Test metrics coverage estimation techniques can help only if an extremely large number of units can be measured beforehand. Tactical radio unit production runs are far below these numbers.

It's evident that the SDR unit itself is a sophisticated RF instrument, i.e. a powerful platform that could be harnessed for test purposes, if some form of BIST strategy could be devised and implemented on it. However, the adoption of the previous mentioned RF BIST proposals for tactical SDR platforms is inherently hampered by the fact that RF systems BIST schemes generally target a fixed architecture, are optimized for a specific standard, or require very large training sets, and are, as such, better suited for factory test of mass market products. Test strategies that use a given fault model must necessarily hold assumptions on the operation modes of the radio, whereas in SDR platforms nearly all aspects are field-configurable. In this scenario, specification-based testing seems unavoidable. The outstanding challenge for SDR testing is then how to conduct specification testing without external equipment.

#### 1.3 Our Work

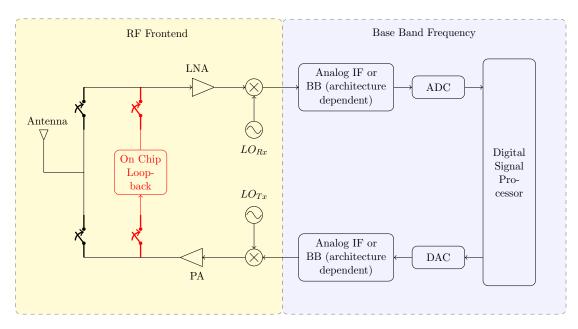

The aim of our work is to propose and develop a new test methodology able to guarantee the correct functioning of the SDR platform. An example of such a platform, developed by Thales Communications & Security, is shown in Fig. 1.2. Our key idea is to use an alternate loopback path to observe the TX output signal just ahead of the antenna. The output waveform is routed back into the last stage of the main receiver (RX) chain (the ADCs), by using a small amount of analog circuitry, some digital control of clock delays, and a lot of complex signal processing. In effect, an auxiliary subsampling receiver (auRX) based on Periodically Nonuniform Sampling of second order (PNS2) provides an alternate demodulation path to characterize the main TX.

**Figure 1.2:** FlexNet. Vehicular wideband SDR platform sold by Thales Communications and Security.

This is feasible because the demodulation channel requirements in TX test mode are somewhat less stringent (i.e. no blockers) than during normal radio use.

We propose two similar implementations differing on how the sampling process is carried out: a voltage-based sampling (VBS) implementation and a charge-based sampling (CBS) implementation. The VBS BIST implementation places stringent requirements on the added undersampling circuitry, and suffers from jitter in the two clock signals driving them. The CBS implementation, lessens these burdens by means of charge-domain sampling. The effectiveness of the two BIST architectures was verified by way of simulations using a behavioral model of an homodyne transmitter written in Matlab. We conducted a theoretical analysis, built a model from analytical equations, and then ran extensive simulations. The two architectures were compared. The results of the comparison show that the CBS BIST architecture performs better, is more robust against clock jitter and is easier to implement. The CBS auRX loopback gives us an accurate estimate of TX performance across the whole output frequency range while relaxing the technological requirements on the added circuit blocks.

A crucial specification for TX compliance is the Adjacent Channel Power Ratio (ACPR), which is rarely addressed by existing BIST techniques [Halder et al., 2008] due to the complexity of the measurement. Our proposed BIST scheme aims to fill this gap and extract the ACPR accurately. It can also handle less demanding measurements, such as Third Order Interception Point (IP3), gain, and I/Q imbalance without any hardware modifications, using existing signal processing algorithms.

Our test solution is scalable across a wide set of complex specifications and can be easily applied for in-field testing with modest additional cost. Compared to existing analog/RF test techniques, this approach is not limited to a given TX architecture and does not rely on an ad-hoc TX model, which makes it ideal for SDR testing. Interestingly, our approach can also be profitably applied in TX architectures that use pre-distortion compensation to improve power amplifier (PA) linearity, when the RX channel is idle.

#### 1.4 Research Contributions

The overall objective of the research described in this dissertation is to develop an low-cost SDR BIST strategy for post-manufacturing and in-field test.

First, we invented a novel BIST architecture for SDR testing, aimed at specification test using loopback. The specification-based test strategy relies on the I/Q RX ADCs and PNS2 to characterize the TX path separately from the RX path. Our initial efforts target spectral

mask estimation at the output of the TX for any mode of operation and architecture. We show that this architecture lends itself well to a simple standalone implementation and can be wholly implemented within the SDR platform.

The main obstacle for the PNS2 reconstruction is to have an accurate estimate of an incrementally controlled delay element. We introduced an LMS-based estimation algorithm that addresses the uncertainties in our BIST architecture: time delay and gain mismatch. Our algorithm solves these issues robustly and opens the road for a complete self-calibrating BIST architecture.

Finally, we developed an improved implementation of the BIST architecture which uses CBS that is more robust and performs better.

### 1.5 Thesis Organisation

This dissertation is organized as follows. Chapter 3 briefly presents the most common architectures of an SDR platform. The fundamentals figures of merit that quantify the performance of an RF transceiver are quickly reviewed. The purpose of this section is to give a better understanding of the challenges faced by the test engineers when dealing with modern transceivers platforms.

The state of the art in the field of testability of RF systems is introduced in Chapter 4. The most frequently reported RF test strategies are discussed. As the field of SDR testing is relatively new, the literature is focusing mainly on the test of consumer products RF devices. The discussion is centered around the possibility of adjusting these techniques so they will meet the challenges introduced by the flexibility of an SDR platform.

Chapter 5 introduces the mathematical tools on which our proposed test strategy is based. The concept of periodically nonuniform sampling (PNS2) is explained by relating it with classic Nyquist sampling and undersampling. Then, we discuss the advantages of PNS2 over other possibilities and we motivate our choice. The most critical limitations of PNS2 are also given considerable attention.

Chapter 6 gives the implementation of our proposed test strategy. Two different architectures are discussed and compared. Here we examine the concerns and potential problems that could arise and we propose solutions to mitigate them. The models and the simulations parameters are also explained in here. Extensive simulations show the feasibility and the potential of the proposed technique.

The final chapter presents our conclusions and perspectives for future works. We list several directions of research that arose from this study.

# Résumé (Français)

### 2.1 Introduction

Le secteur des communications sécurisés et portables connait une véritable révolution avec l'apparition des plateformes dites radios logicielles (Software Defined Radios, SDRs). Dans ces plateformes, une grande partie des fonctionnalités de la radio sont obtenues grâce au logiciel et à des blocs électroniques numériques programmables. Ceci confère au produit fini une grande flexibilité pour s'adapter à une large gamme de modulations et scénarios d'utilisation, mais aussi la possibilité d'une économie d'effort de développement par l'utilisation du même code sur plusieurs générations de plateformes matérielles.

Les caractéristiques effectives du produit fini sont le résultat d'une interaction complexe et souvent peu évidente entre le logiciel embarqué, le circuit de traitement numérique et le bloc mixte RF/analogique (voir Fig. 2.1). Le développement de chacun de ces composants au niveau de l'état de l'art requiert des connaissances approfondies et des outils spécifiques.

Le SDR est une plateforme multifonctions flexible, configurable par logiciel et pouvant évoluer dans le futur. Actuellement, ces plateformes sont testées essentiellement par le bias des applications existantes, c.à.d. avec des montages ad hoc difficilement modifiables en utilisant des ATE (Automatic Test Equipments). Cette méthodologie a atteint ses limites dues au coût élevé de l'outillage RF externe, du long temps de test et du manque de flexibilité. Pour réduire le cout de test et par conséquence le coût du produit, l'industrie requiert des stratégies de test capables d'identifier rapidement les unités défectueuses de façon indépendemment de leur application. Dans ce contexte, le but de notre recherche est d'inventer et développer une méthodologie de test capable de garantir le bon fonctionnement d'une plateforme SDR après la production et sur le terrain.

Dans ce manuscrit, on introduit une nouvelle architecture de rebouclage qui est conçue pour éviter le masquage et pour permettre un test complet des transrecepteurs SDR en fin de production et sur le terrain. L'idée fondamentale de notre proposition est de tester d'abord l'émetteur en utilisant un circuit auxiliaire BIST. Le but de ce circuit est de sous-échantillonner le signal à la sortie de TX et de le transférer au processeur numérique à l'aide des deux convertisseurs CAN intégrés dans la chaine de réception. La conversion du signal RF est réalisée en utilisant une technique de sous-échantillonnage non-uniforme décrite plus en détail dans une section future. Cette approche permet d'éviter le masquage de défauts dans la technique de rebouclage

Figure 2.1: Architecture générale d'une SDR

classique, est flexible et supporte une implémentation simple.

Nos efforts initiaux se focalisent sur la caractérisation du masque spectral à la sortie du TX. Plus particulièrement, on s'intéresse à la mesure de la puissance dans les canaux adjacents (Adjacent Channels Power Ratio - ACPR) qui est très rarement adressé dans les BISTs existantes à cause de la complexité des leurs mesures. Néanmoins, notre technique peut mesurer des spécifications moins compliqués en utilisant des algorithmes de traitement de signal sans modifications hardware.

La contribution principale de nos travaux consiste dans la proposition d'une technique de test d'un émetteur SDR basée sur la technique de sous-échantillonnage nonuniforme. Celle ci permet la caractérisation de TX dans toutes les modes d'opération. Notre but final est d'éliminer les problèmes de masquage de défauts existants dans un rebouclage classique.

Ce chapitre consiste en un résumé du rapport en anglais et il est structuré comme suit. La première section résume les plus importantes caractéristiques qui définissent une radio logicielle. La section suivant décrite l'état de l'art du domaine de testabilité des systèmes mixtes RF/Analogiques en général, en se focalisant en particulier sur le cas des transceivers radio. Ensuite, notre architecture de test et des résultats obtenus en simulation sont présentés. La dernière section contient des conclusions et perspectives pour de futurs travaux.

### 2.2 Radio logicielle

Une radio logicielle est un émetteur/récepteur radio réalisé principalement par logiciel et dans une moindre mesure par matériel. Dans un système radio classique, l'émission/réception est assurée par des composants matériels (oscillateurs, filtres) spécifiques et adaptés aux systèmes auxquels il est destiné. Il n'est donc souvent pas possible d'utiliser d'autres systèmes sans changer le matériel et donc l'intégralité du récepteur. C'est l'avancement des plateformes (DSP, FPGA) et des algorithmes de traitement numériques qui a permis l'apparition des radios logicielles. Dans ces systèmes, les traitements réalisés classiquement par des circuits analogiques (filtrage, décimation, démodulation, décodage) peuvent être désormais réalisés de façon logicielle. Cela confère une universalité et une grande adaptabilité à l'émetteur/récepteur. En effet, il suffit de changer ou d'adapter le logiciel pour fonctionner avec un système radio différent.

Dans la littérature la radio logicielle a été présentée pour la première fois par Mitola dans Mitola [1993]. Aujourd'hui les radios logicielles sont utilisées par exemple dans les réseaux radiomobiles (GSM, UMTS, etc.) au niveau des stations de base (BTS, Base Transceiver Stations) et comme systèmes de communications militaires. Les avantages d'une radio logicielle par rapport à une structure classique de transceiver RF sont :

- le développement de plusieurs produits radios en utilisant une seule architecture, ce qui écourte le délai de commercialisation

- permettre la réutilisation du logiciel par différents produits radios ce qui réduit le cout de développement

- la programmation à distance qui permet la mise-à-jour et la maintenance du produit à distance

Idéalement, une radio logicielle ne serait composée que par des unités de traitement numérique connectés par l'intermédiaire de CNAs et de CANs à l'antenne. Cependant, un schéma idéal n'est pas réalisable à cause des limites technologiques et on retrouve dans une radio logicielle des composants analogiques : amplificateurs de puissance, mélangeurs. Ils sont les composants analogiques/mixtes qui limitent la testabilité des plateformes SDRs qui constituent le coeur de notre recheche.

#### 2.3 Test RF

Dans le chapitre précédent nous avons décrit la complexité et la flexibilité des plateformes SDR. Nous avons vu que, pour l'utilisateur final ceci confère au produit fini la possibilité pour s'adapter à une large gamme de formations et scénarii d'utilisation. De plus, pour le client s'ajoute la possibilité d'une économie d'effort de développement par l'utilisation du code sur plusieurs générations de plateformes matérielles.

Néanmoins, les caractéristiques effectives du produit fini sont le résultat d'une interaction complexe et souvent peu évidente entre le logiciel embarqué, le circuit de traitement numérique et le bloc mixte RF/analogique. Cette complexité rend le test du produit fini extrêmement compliqué et coûteux.

Dans cette section, on expose une vue d'ensemble des techniques de test des circuits électroniques les plus prometteuses. Ensuite, on analysera comment ces techniques peuvent être adaptées pour le test des plateformes radio logicielles.

#### 2.3.1 Test et testabilité des systèmes électroniques

Réaliser le test d'un circuit signifie détecter qu'un circuit ne fonctionne pas conformément aux spécifications (pour des raisons de fonctionnalité logique, de vitesse de fonctionnement ou encore de niveaux électriques). Dans la majorité des cas, le test sert uniquement à distinguer les circuits « bons », c'est-à-dire pouvant être livrés au client, des circuits « mauvais » qui sont à éliminer. La cause exacte du mauvais fonctionnement n'a la plupart du temps pas à être analysée.

Dans certains cas cependant, la cause du mauvais fonctionnement doit être identifiée. C'est le cas d'une plateforme SDR qui est modulaire et où l'identification de la cause et du mauvais module est souhaitée. Dans ce cas, le test n'est plus suffisant ; il doit être complété par une phase de diagnostic, qui nécessite une analyse beaucoup plus longue et détaillée. La technique de test que l'on a proposé cible donc l'identification de la cause du mauvais fonctionnement.

Le mauvais fonctionnement d'un circuit peut provenir d'une erreur de conception, d'un problème lors de la fabrication ou d'un problème survenant pendant l'exécution de l'application, soit à cause du vieillissement du circuit, soit à cause de son environnement (radiations, particules, etc.). Dans cette recherche, on s'intéresse aux techniques de test qui ont pour objectif la détection de problèmes liés à la fabrication ou au vieillissement, mais pas à la conception. En fin de fabrication le circuit est supposé exempt d'erreur de conception.

On peut distinguer deux types de test : test hors ligne et test en ligne. Un test dit hors ligne correspond au test de fin de fabrication effectué lorsque le circuit n'est pas encore placé dans son environnement opérationnel. Par opposition, un test en ligne est un test exécuté par le circuit, alors qu'il est connecté dans son environnement opérationnel et que l'application est en cours d'exécution. Le test peut être effectué en parallèle de l'application (test en ligne continu) ou pendant certaines interruptions courtes (test en ligne périodique). Pour une radio logicielle qui est capable d'évoluer sur le terrain, le test en ligne est essentiel pour garantir le bon fonctionnement du système après une mise à jour. Pendant notre recherche nous nous sommes intéressés au test hors ligne ainsi que au test en ligne des ces plateformes.

Que le test de la fonction du circuit soit effectué en ligne ou hors ligne, il peut utiliser soit une approche fonctionnelle, soit une approche structurelle.

L'approche fonctionnelle consiste à définir des vecteurs de test permettant de parcourir tous les modes de fonctionnement possibles du circuit, tels qu'ils sont spécifiés dans la fiche technique (ou le cahier des charges). Un tel test est très proche des simulations faites par un concepteur pour vérifier l'absence d'erreur de conception. Dans le cas d'un circuit très simple, purement combinatoire, cette approche revient à vérifier la table de vérité de la fonction globale réalisée par le circuit. Une telle approche a deux inconvénients dans le cas d'un circuit complexe :

- tout d'abord, l'exhaustivité du test n'est généralement pas envisageable et la tentative de détecter le plus grand nombre de problèmes possibles conduit à des séquences de test excessivement longues ;

- peut-être encore plus important, aucune mesure fiable n'existe pour indiquer le niveau de qualité atteint par un jeu de vecteurs de test fonctionnels

L'approche structurelle consiste à partir de la structure interne du circuit et à vérifier le bon fonctionnement des éléments de base. L'objectif d'une approche structurelle n'est pas de détecter des erreurs de conception, une telle vérification se doit de permettre la validation de la fonctionnalité globale du circuit.

L'avantage de cette approche est de permettre l'obtention de séquences de test plus courtes et d'une quantification du niveau de qualité du test, pour des hypothèses de dysfonctionnement données. L'inconvénient est justement une efficacité limitée à ces hypothèses, c'est-à-dire au modèle de fautes choisi. Aujourd'hui l'approche structurelle est utilisée plutôt par les tests des circuits numériques. Ceci est possible parce que pour les circuits numériques il a été développé des modèles qui couvrent une bonne partie des défauts existants. Les circuits analogiques mixtes ne disposent pas de modèles suffisement généralisés et, pour l'instant, le test de ces circuits est basé presque complètement sur des approches fonctionnelles.

Enfin une stratégie de test n'est jamais parfaite. Ça signifie qu'il y a une probabilité finie qu'un circuit bon soit considéré mauvais où qu'un circuit mauvais passe le test. Aucune de ces situations n'est pas souhaitable. Afin de quantifier les performances d'une stratégie de test deux facteurs de mérite sont souvent utilisés Yield Loss (YL) et Fault Coverage (FC) qui sont

définis comme suit :

$$YL = \frac{\text{number of healthy circuits that fail the test}}{\text{number of good circuits}}$$

$$FC = 1 - \frac{\text{number of faulty circuits that pass the test}}{\text{number of faulty circuits}}$$

(2.1)

L'objectif de chaque stratégie de test est donc de maximiser le FC et minimiser le YL.

#### 2.3.2 Défis dans le test des systèmes RF

La croissance rapide de la complexité des circuits et l'évolution vers la haute intégration (VLSI – Very Large Scale Integration) rendent le test du circuit en production extrêmement difficile et couteux. En effet, il est estimé que le test des circuits AMS/RF peut couter jusqu'à 50 % du cout total de production. Afin de réduire ce coût il est donc indispensable de développer de nouvelles méthodologies de test plus efficaces. Dans cette section on analyse quels sont les défis rencontrées par le monde académique et industriel.

En parallèle de l'accroissement de complexité des circuits AMS, on remarque aussi une évolution vers la haute densité des circuits imprimés et des technologies d'encapsulation. Ceci fait apparaître un problème de points d'accès et donc une accessibilité limité. Par contre, la capacité de contrôler et observer les sorties de chaque bloc est nécessaire pour la caractérisation complète d'un circuit. Afin d'améliorer l'observabilité et la contrôlabilité, une solution habituelle est d'ajouter circuits auxiliaires qui permettrons de générer de stimuli et de mesurer les performances du circuit à tester. Cependant, dans ce cas il faut faire attention de ne pas détériorer les performances du circuit à tester. Surtout la chaine RF qui est particulièrement sensible.

Malgré l'augmentation considérable de la complexité des circuits, la pression ne cesse de s'accroître pour diminuer les temps de conception et le coût de production. Comme le test est un facteur important dans le coût total de production, il est nécessaire que la stratégie de test soit à bas coût.

Comme déjà discuté dans la section précédente, si les circuits numériques bénéficient de modèles bien généralisés, ce n'est pas la même situation pour les circuits analogiques mixtes ou il manque des modèles universellement acceptés et rapide à simuler. Par conséquence les ingénieurs de test doivent attendre la fabrication du prototype pour pouvoir commencer à déboguer. Aujourd'hui, les experts sont d'accord que ce flux de production séquentielle/test n'est plus rentable et il doit être reconsidéré.

Ensuite, en plus des défis classiques précédemment rappelés, les plateformes SDRs introduisent de nouveaux challenges encore plus difficiles à respecter : les besoins de flexibilité. Par rapport aux systèmes de communication classiques, les radios logicielles sont capables de communiquer dans un spectre très large bande de fréquences et de standards de modulation. De même façon, une stratégie de test doit garantir que la plateforme fonctionne correctement dans tous ces scénarii.

Enfin, il faut noter que les SDRs sont utilisées dans un nombre croissant d'applications critiques, au niveau de vies humaines (comme par dans les applications militaires) ou au niveau financier (domaine bancaire). En parallèle, la probabilité de défaillances transitoires augmente avec l'évolution des technologies. Un aspect de test jusque-là méconnu dans la plupart des domaines commence donc à se démocratiser : réaliser un test du circuit pendant l'exécution normal de l'application et non pas seulement en fin de fabrication ou en maintenance. Un test en ligne est obligatoire pour les SDRs qui doivent garantir le bon fonctionnement du circuit pendant toute sa vie.

Pour résumer cette section, les chercheurs et les industriels n'ont pas encore convergé vers une stratégie de test AMS/RF généralisée. Toutefois, ils sont d'accord que la meilleure solution