## Intégration des techniques de vérification formelle dans une approche de conception des systèmes de contrôle-commande: application aux architectures SCADA

Soraya Mesli Kesraoui

## ▶ To cite this version:

Soraya Mesli Kesraoui. Intégration des techniques de vérification formelle dans une approche de conception des systèmes de contrôle-commande: application aux architectures SCADA. Automatique / Robotique. Université de Bretagne Sud, 2017. Français. NNT: 2017LORIS442. tel-01738049

# HAL Id: tel-01738049

https://theses.hal.science/tel-01738049v1

Submitted on 20 Mar 2018

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### THESE / UNIVERSITE BRETAGNE SUD

UFR Sciences et Sciences de l'Ingénieur sous le sceau de l'Université Bretagne Loire

Pour obtenir le titre de :

DOCTEUR DE L'UNIVERSITE BRETAGNE-SUD

Mention : STIC

**Ecole Doctorale SICMA**

présentée par

## Soraya Mesli Kesraoui

Préparée à l'unité mixte de recherche : Lab-STICC (UMR 6285), IRISA (UMR 6074), CRIStAL (UMR 9189)

Établissement de rattachement : Université Bretagne Loire

# Intégration des techniques de vérification formelle dans une approche de conception des systèmes de contrôle-commande :

Application aux architectures SCADA

#### Thèse soutenue le 11 mai 2017

devant la commission d'examen composée de :

#### M. Yamine Ait Ameur

Professeur, IRIT (UMR 5505), École Nationale Supérieure d'électronique, d'électrotechnique, d'Informatique, d'Hydraulique et de Télécommunications / Président

#### M. Christophe Kolski

Professeur, LAMIH (UMR 8201), Université de Valenciennes et du Hainaut-Cambrésis / Rapporteur

#### M. Olivier H. Roux

Professeur, IRCCyN (UMR 6597), École Centrale de Nantes / Rapporteur

#### Mme. Pascale Marangé

Maître de Conférences, CRAN (UMR 7039), Université de Lorraine / Examinateur

#### M. Pascal Berruet

Professeur, Lab-STICC (UMR 6285), Université Bretagne Sud, Lorient / Directeur de thèse

## M. Armand Toguyeni

Professeur, CRIStAL (UMR 9189), École centrale de Lille / Co-directeur

#### M. Flavio Oquendo

Professeur, IRISA (UMR 6074), Université Bretagne Sud, Vannes / Co-directeur

#### M. Alain Bignon

Docteur, Responsable R&I, Segula Technologies, Lanester / Responsable industriel CIFRE

"Je dédie cette thèse à mes chers parents."

## Remerciements

Ho que c'est difficile d'écrire et de trouver les mots justes pour exprimer mes remerciements et ma gratitude envers celles et ceux qui m'ont soutenu durant ces trois années de thèse.

Je remercie tout d'abord Alain BIGNON qui a cru en moi et qui m'a proposé ce sujet de thèse. Je te remercie aussi pour tes conseils, pour ton encadrement et surtout pour ton soutien jusqu'à la dernière minute. Tu resteras toujours "Mon meilleur chef!".

Je remercie également messieurs Pascal BERRUET, Armand TOGUYENI et Flavio OQUENDO d'avoir accepté d'encadrer cette thèse. Travailler sous la direction de trois professeurs avec des contraintes de distance n'est pas toujours évident, mais vous avez su rendre ce travail agréable. Je vous remercie surtout pour l'intérêt que vous avez porté à mes travaux, pour le suivi, les conseils, votre disponibilité et aussi pour la bonne ambiance qui a rythmé nos réunions.

Je souhaite remercier messieurs Christophe KOLSKI et Olivier H. ROUX d'avoir accepté de relire ces travaux. Je remercie également monsieur Yamine AIT AMEUR d'avoir accepté d'examiner et de présider le jury de cette thèse. Je remercie aussi madame Pascale MARANGE d'avoir bien voulu accepter la charge d'examinateur.

Je tiens aussi à remercier le personnel des laboratoires lab-STICC et L'IRISA pour leur professionnalisme. Je n'oublie pas de remercier les doctorants du Lab-STICC (Amandine POR-CHER, Fanny GUENNOC, Rani KHAN, Thomas TOUBLANC) et de l'IRISA pour les discussions très enrichissantes qu'on a pu avoir au cours de ces années de thèse.

Je remercie également et chaleureusement mes collègues de Segula Technologies, surtout l'équipe du midi : Perine Le SENECHAL, Éric LE BRIS, Sophie PRAT, Laurianne BOULHIC, Olga GOUBALI, Nicolas AUFFRET, Davy RODIER et Fabien SILONE. Merci à Perine, Olga et Laurianne d'avoir relu et corrigé les chapitres de cette thèse. Merci à Eric d'avoir accepté de participer à mes multiples entretiens. Merci à vous tous pour les bons moments qu'on a pu partager. Je remercie aussi Raoul DJOUSSE, Landry RAHAMEFY et Franck NGANKAM d'avoir participé et contribué à mes travaux.

Je tiens spécialement à remercier mes amies depuis toujours : Sonia, Farisa, Dihia, Nassima, Loulou et Kahina. Merci pour votre soutien et votre amitié. Cette thèse m'a aussi permis de rencontrer des personnes formidables comme Olga GOUBALI et Asma BENMESSAOUD GABIS. Je te remercie Olga pour ton soutien et d'avoir toujours cru en moi. Tu as toujours su me communiquer ta joie de vivre et ta bonne humeur dans les moments difficiles. Je te remercie Asma pour les bons moments passés ensemble et pour toutes les discussions imaginables et inimaginables qu'on a pu avoir.

Je remercie spécialement mes parents qui ont toujours étaient là pour moi et qui ont toujours cru en moi. Je remercie aussi mes frères et sœurs : Ouissem, Sabrina, Toufik et Cherif. Je tiens aussi à remercie mes beaux-parents de m'avoir considéré comme leur fille et de m'avoir toujours soutenue. Je remercie aussi Salim, Djamila et Zazi.

Je n'oublie pas de remercier la personne qui m'a supporté durant ces trois années de thèse. Je te remercie Djamal d'être toujours à mes côtés et d'avoir supporté mes nombreuse crises de stresse et d'angoisse. Je suis convaincu que sans toi, cette thèse n'aura pas eu lieu. Merci!

Je remercie tous ceux qui ont contribué de prés ou de loin à cette thèse.

Cette thèse est le fruit d'une collaboration entre l'entreprise SEGULA Technologies, acteur majeur des métiers de l'ingénierie, et trois laboratoires de recherches : Le Lab-STICC, l'IRISA et CRIStAl. Le Lab-STICC est un pôle de référence en recherche sur les systèmes communicants. L'IRISA de Vannes est un pôle de référence en recherche sur les architectures logicielles, l'analyse et le traitement d'images, la fouille de données, l'interaction gestuelle, l'informatique mobile et décisionnelle. CriStAL est un pôle de référence en recherche sur l'ingénierie des données et de modèles, les systèmes embarqués temps réels, le traitement d'image, le génie logiciel et la conception système.

Segula Engineering France 165 rue de la Montagne du Salut BP 50256 - 56602 Lanester Cedex

Tel: +33 (0)2 97 87 73 07 www.segulatechnologies.com

Laboratoire des Sciences et Techniques de l'Information, de la Communication et de la Connaissance (Lab-STICC) de Lorient, UMR 6285

Centre de Recherche Christiaan Huygens Rue de Saint Maudé 56321 Lorient Cedex

Tel: +33 (0)2 97 87 45 60

www.lab-sticc.fr

Institut de Recherche en Informatique et Systèmes Aléatoires (IRISA) de Vannes, UMR 6074

Campus de Tohannic

Bâtiment ENSIBS, rue Yves Mainguy

BP 57356017 Vannes cedex Tel: +33 (0)2 97 01 72 35 www-irisa.univ-ubs.fr

Centre de Recherche en Informatique, Signal et Automatique (CRIStAL) de Lille, UMR 9189

Université Lille 1

Bâtiment M3 extension, Avenue Carl Gauss

59655 Villeneuve d'Ascq Cedex

www.cristal.univ-lille.fr

# Sommaire

| So | mma    | nire                                                               | V    |

|----|--------|--------------------------------------------------------------------|------|

| Ta | ıble d | les figures                                                        | ix   |

| Li | ste d  | es tableaux                                                        | xi   |

| Gl | lossai | ire                                                                | xiii |

| C  | ontri  | butions scientifiques                                              | 1    |

| In | trodi  | action générale                                                    | 1    |

| I  | Con    | itexte et état de l'art                                            | 7    |

| 1  | Con    | texte et problématiques                                            | 9    |

|    | 1.1    | Introduction                                                       | 10   |

|    | 1.2    | L'ingénierie système : contexte académique                         | 10   |

|    |        | 1.2.1 La spécification des exigences                               | 11   |

|    |        | 1.2.2 La vérification des exigences                                | 15   |

|    | 1.3    | Conception des systèmes de contrôle-commande : contexte industriel | 18   |

|    |        | 1.3.1 Les systèmes de contrôle-commande                            | 18   |

|    |        | <ul><li>1.3.2 L'architecture SCADA</li></ul>                       | 19   |

|    |        | commande                                                           | 20   |

|    |        | 1.3.4 Génération automatique des programmes de contrôle-commande   | 23   |

|    | 1.4    | Problématiques et verrous scientifiques                            | 29   |

|    |        | 1.4.1 Problématiques                                               | 29   |

|    |        | 1.4.2 Verrous scientifiques                                        | 30   |

|    | 1.5    | Conclusion                                                         | 31   |

| 2  | État   | de l'art : systematic mapping                                      | 33   |

|    | 2.1    | Introduction                                                       | 34   |

|    | 2.2    | État de l'art au travers des revues de la littérature existante    | 34   |

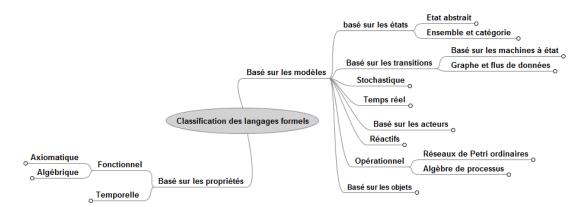

|    |        | 2.2.1 Classification des langages formels                          | 34   |

ii Sommaire

|    |     | 2.2.2   | Comparaison des langages de spécification                                 | 36 |

|----|-----|---------|---------------------------------------------------------------------------|----|

|    |     | 2.2.3   | Utilisation des méthodes formelles                                        | 36 |

|    |     | 2.2.4   | Bilan sur les revues de la littérature existantes                         | 37 |

|    | 2.3 | Métho   | de                                                                        | 37 |

|    | 2.4 | Étape   | 1 : Définition du protocole                                               | 38 |

|    |     | 2.4.1   | Définition des questions de recherche                                     | 38 |

|    |     | 2.4.2   | Stratégie de la recherche                                                 | 39 |

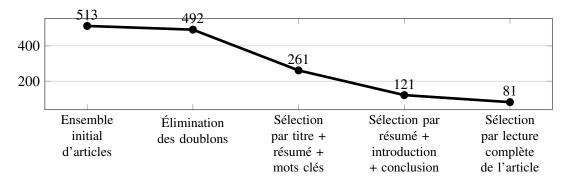

|    |     | 2.4.3   | Sélection des articles                                                    | 40 |

|    |     | 2.4.4   | Extraction des données et classification                                  | 40 |

|    |     | 2.4.5   | Évaluation de la validité de l'étude                                      | 41 |

|    | 2.5 | Étape 2 | 2 : Conduction                                                            | 42 |

|    | 2.6 | Étape : | 3 : Rapport de synthèse                                                   | 44 |

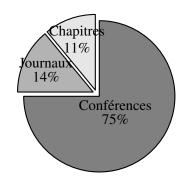

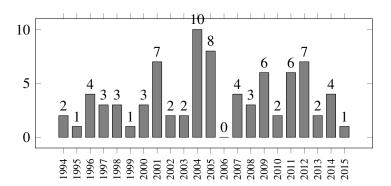

|    |     | 2.6.1   | Résultats démographiques                                                  | 44 |

|    |     | 2.6.2   | Proposition d'une classification des langages formels                     | 45 |

|    | 2.7 | Résult  | ats obtenus                                                               | 48 |

|    |     | 2.7.1   | QR1 : Quels sont les langages de spécification utilisés pour la vérifica- |    |

|    |     |         | tion formelle?                                                            | 48 |

|    |     | 2.7.2   | QR2 : Comment a été réalisée la vérification formelle ?                   | 52 |

|    |     | 2.7.3   | QR3 : Quels sont les objectifs de la vérification formelle ?              | 54 |

|    | 2.8 | Conclu  | asion et Discussions                                                      | 58 |

|    |     | 2.8.1   | Bilan                                                                     | 58 |

|    |     | 2.8.2   | Propositions                                                              | 58 |

|    |     |         |                                                                           |    |

| II | Ap  | proche  | es de vérification formelle : propositions méthodologiques                | 61 |

| 3  | Ván | Gaatian | formelle d'une chaîne de contrôle-commande élémentaire                    | 63 |

| 3  | 3.1 |         | action                                                                    | 64 |

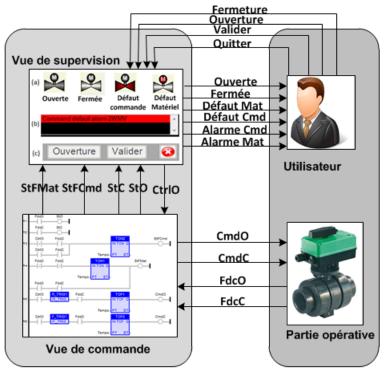

|    | 3.1 |         | ble illustratif : V2VM                                                    | _  |

|    | 3.2 | 3.2.1   | Comportement de l'utilisateur                                             |    |

|    |     | 3.2.1   | L'interface de supervision                                                | 65 |

|    |     | 3.2.2   | Le programme de commande                                                  | 66 |

|    |     | 3.2.4   | La partie opérative                                                       | 66 |

|    |     | 3.2.5   | Les exigences de conception                                               | 67 |

|    | 3.3 |         | Rete et travaux connexes                                                  | 67 |

|    | 3.3 | 3.3.1   | Vérification formelle des programmes de commande                          | 67 |

|    |     | 3.3.2   | Vérification formelle des interfaces de supervision                       | 68 |

|    |     | 3.3.3   | Manques dans les travaux existants et problématique associée              | 69 |

|    | 3.4 |         | eation formelle d'une chaîne de contrôle-commande élémentaire             | 69 |

|    | 3.4 | 3.4.1   |                                                                           | 70 |

|    |     | 3.4.1   | Concepts utilisés                                                         | 70 |

Sommaire

|   |     | 3.4.2                                     | Approche générale                                                   | . 72                                               |

|---|-----|-------------------------------------------|---------------------------------------------------------------------|----------------------------------------------------|

|   |     | 3.4.3                                     | Formalisation d'une chaîne de contrôle-commande élémentaire         | . 74                                               |

|   |     | 3.4.4                                     | Vérification formelle d'une chaîne de contrôle-commande élémentaire | . 85                                               |

|   | 3.5 | Conclu                                    | usion                                                               | . 85                                               |

| 4 | Vér | ification                                 | n formelle des modèles de conception (P&ID)                         | 87                                                 |

|   | 4.1 | Introd                                    | uction                                                              | . 88                                               |

|   | 4.2 | Exemp                                     | ple illustratif: P&ID                                               | . 88                                               |

|   | 4.3 | Conte                                     | xte et travaux connexes                                             | . 89                                               |

|   |     | 4.3.1                                     | Vérification des P&IDs                                              | . 89                                               |

|   |     | 4.3.2                                     | Les architectures logicielles                                       | . 90                                               |

|   | 4.4 | Appro                                     | che proposée                                                        | . 91                                               |

|   |     | 4.4.1                                     | Concepts utilisés                                                   | . 91                                               |

|   |     | 4.4.2                                     | Vérification formelle des diagrammes P&ID                           | . 93                                               |

|   |     | 4.4.3                                     | Un style architectural pour la norme ANSI/ISA-5.1                   | . 93                                               |

|   |     | 4.4.4                                     | Génération des modèles Alloy à partir des P&ID                      | . 98                                               |

|   |     | 4.4.5                                     | Formalisation des exigences et vérification formelles des P&ID      | . 99                                               |

|   |     | 4.4.6                                     | Aide à l'analyse des résultats                                      | . 100                                              |

|   | 4.5 | Conclu                                    | usion                                                               | . 104                                              |

| 5 | Imn | lémenta                                   | ation                                                               | 109                                                |

| _ | 5.1 |                                           | uction                                                              |                                                    |

|   | 5.2 |                                           | odologie mise en œuvre                                              |                                                    |

|   |     | 5.2.1                                     | Concepts IDM utilisés                                               |                                                    |

|   |     | 5.2.2                                     | Outils et langages utilisés                                         |                                                    |

|   | 5.3 | Flot de                                   | e vérification des composants standards                             |                                                    |

|   |     | 5.3.1                                     | Opération de modélisation de la tâche utilisateur                   |                                                    |

|   |     | 5.3.2                                     | Opération de transformation de HAMSTERS en AT intermédiaire (AT'    |                                                    |

|   |     | 5.3.3                                     | *                                                                   | , ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,            |

|   |     |                                           | Opération de transformation des IHM SCADA en AT'                    |                                                    |

|   |     | 5.3.4                                     | Opération de transformation des IHM SCADA en AT'                    | . 122                                              |

|   |     | 5.3.4<br>5.3.5                            | Opération de transformation des IHM SCADA en AT'                    | . 122<br>. 126                                     |

|   |     |                                           | Opération de transformation des programmes LD en AT'                | . 122<br>. 126<br>. 134                            |

|   |     | 5.3.5                                     | Opération de transformation des programmes LD en AT'                | . 122<br>. 126<br>. 134<br>. 136                   |

|   |     | 5.3.5<br>5.3.6                            | Opération de transformation des programmes LD en AT'                | . 122<br>. 126<br>. 134<br>. 136                   |

|   |     | 5.3.5<br>5.3.6<br>5.3.7                   | Opération de transformation des programmes LD en AT'                | . 122<br>. 126<br>. 134<br>. 136<br>. 137          |

|   | 5.4 | 5.3.5<br>5.3.6<br>5.3.7<br>5.3.8<br>5.3.9 | Opération de transformation des programmes LD en AT'                | . 122<br>. 126<br>. 134<br>. 136<br>. 137<br>. 138 |

|   | 5.4 | 5.3.5<br>5.3.6<br>5.3.7<br>5.3.8<br>5.3.9 | Opération de transformation des programmes LD en AT'                | . 122<br>. 126<br>. 134<br>. 136<br>. 137<br>. 138 |

<u>iv</u> Sommaire

|   |     | 5.4.3    | Opération de spécification des exigences                                | . 142 |

|---|-----|----------|-------------------------------------------------------------------------|-------|

|   |     | 5.4.4    | Opération d'épuration                                                   |       |

|   |     | 5.4.5    | Opération de transformation de P&ID en Alloy                            |       |

|   |     | 5.4.6    | Opération de vérification                                               | . 147 |

|   |     | 5.4.7    | Opération de visualisation des erreurs                                  |       |

|   |     | 5.4.8    | Opération de correction                                                 |       |

|   |     | 5.4.9    | Bilan                                                                   | . 151 |

|   | 5.5 | Conclu   | usion                                                                   | . 152 |

| 6 | App | lication | à des cas industriels                                                   | 153   |

|   | 6.1 | Introd   | uction                                                                  | . 154 |

|   | 6.2 | Vérific  | cation formelle de V2VM : Étude de cas                                  | . 154 |

|   |     | 6.2.1    | Opération de modélisation de la tâche utilisateur                       | . 154 |

|   |     | 6.2.2    | Opération de transformation de HAMSTERS en AT                           | . 155 |

|   |     | 6.2.3    | Opération de transformation des IHM SCADA en AT                         | . 156 |

|   |     | 6.2.4    | Opération de transformation des programmes LD en AT                     | . 158 |

|   |     | 6.2.5    | Opération de modélisation du composant physique en AT                   | . 159 |

|   |     | 6.2.6    | Opération de spécification des exigences en CTL                         | . 161 |

|   |     | 6.2.7    | Vérification formelle de V2VM                                           | . 161 |

|   |     | 6.2.8    | Validité                                                                | . 163 |

|   |     | 6.2.9    | Bilan de la vérification formelle de la V2VM                            |       |

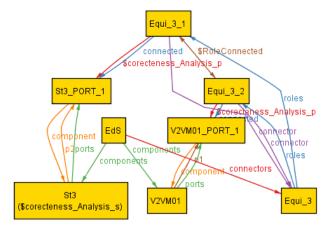

|   | 6.3 | Vérific  | cation formelle du P&ID du système EdS : Etude de cas                   | . 164 |

|   |     | 6.3.1    | Opération de construction                                               | . 164 |

|   |     | 6.3.2    | Opération de spécification des exigences                                | . 165 |

|   |     | 6.3.3    | Opération d'épuration et de transformation du P&ID en Alloy             | . 168 |

|   |     | 6.3.4    | Opération de vérification                                               | . 168 |

|   |     | 6.3.5    | Opération de visualisation des erreurs                                  | . 169 |

|   |     | 6.3.6    | Validité                                                                | . 169 |

|   |     | 6.3.7    | Bilan de la vérification formelle du P&ID du système EdS                | . 170 |

|   | 6.4 | Conclu   | usion                                                                   | . 171 |

| 7 | Con | clusion  |                                                                         | 173   |

|   | 7.1 | Introd   | uction                                                                  | . 173 |

|   | 7.2 | Rappe    | l des contributions                                                     | . 174 |

|   |     | 7.2.1    | Intégration de la vérification formelle dans une démarche de conception | n 174 |

|   |     | 7.2.2    | Aide à l'obtention des modèles formels                                  | . 175 |

|   |     | 7.2.3    | Application à des cas d'étude concrets                                  | . 176 |

|   | 7.3 | Perspe   | ectives                                                                 | . 176 |

|   |     | 7.3.1    | Extensions des flots proposés                                           |       |

|   |     | 7.3.2    | Aide à la spécification des exigences                                   | . 177 |

| C     |      |   |

|-------|------|---|

| Somma | ire. | 7 |

|       |      |   |

|    |                                                    | 7.3.3 Vérification formelle du système global                          | . 178 |  |

|----|----------------------------------------------------|------------------------------------------------------------------------|-------|--|

| Bi | bliog                                              | raphie                                                                 | 205   |  |

| Aı | nnexe                                              | es es                                                                  | 209   |  |

| A  | Don                                                | nées de la Systematic Mapping                                          | 209   |  |

|    | A.1                                                | Requêtes de recherche dans les différentes bases                       | . 209 |  |

|    | A.2                                                | Listes des articles retenus pour la systematic mapping                 | . 210 |  |

| В  | Guide d'entretien réalisé avec les experts métiers |                                                                        |       |  |

|    | B.1                                                | Présentation                                                           | . 215 |  |

|    | B.2                                                | Analyse des exigences                                                  | . 215 |  |

|    | B.3                                                | Analyse de la conception système                                       | . 216 |  |

|    | B.4                                                | Analyse de la vérification                                             | . 216 |  |

|    | B.5                                                | Confrontation avec le P&ID, la commande, et l'interface de supervision | . 216 |  |

| C  | Mod                                                | lèle complet de V2VM                                                   | 219   |  |

|    | C.1                                                | Tâches utilisateurs                                                    | . 219 |  |

|    | C.2                                                | Interface de supervision                                               | . 220 |  |

|    | C.3                                                | Programme de commande                                                  | . 222 |  |

|    |                                                    | C.3.1 Composant physique                                               | . 223 |  |

|    | C.4                                                | Extrait d'un contre-exemple Alloy en XML                               | . 223 |  |

| D  | Gra                                                | mmaire VB en xtext                                                     | 225   |  |

<u>vi</u> Sommaire

# Table des figures

| 1    | Organisation de ce manuscrit                                           | 3  |

|------|------------------------------------------------------------------------|----|

| 1.1  | Représentation d'un système de contrôle-commande                       | 18 |

| 1.2  | L'architecture SCADA                                                   | 19 |

| 1.3  | Architecture simpliste d'un système interactif                         | 20 |

| 1.4  | Cycle opérationnel d'un API                                            | 21 |

| 1.5  | Le projet Anaxagore                                                    | 27 |

| 1.6  | Structure d'un composant standard dans Anaxagore                       | 28 |

| 1.7  | Flot de conception Anaxagore                                           | 29 |

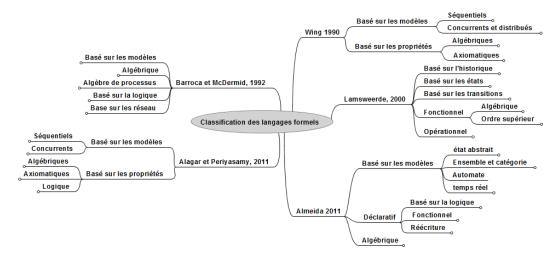

| 2.1  | Classifications existantes des langages formels                        | 35 |

| 2.2  | Le processus de la revue systématique                                  | 38 |

| 2.3  | Évolution de la sélection des articles pertinents                      | 43 |

| 2.4  | Provenance des articles                                                | 44 |

| 2.5  | Nombre d'articles par an                                               | 44 |

| 2.6  | Nuage des mots clés                                                    | 45 |

| 2.7  | Classification des langages formels                                    | 46 |

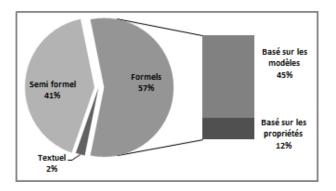

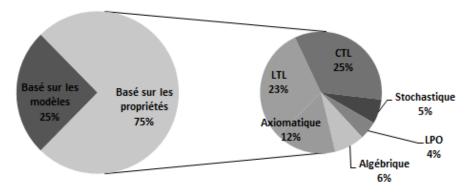

| 2.8  | Type des langage de spécification des systèmes                         | 48 |

| 2.9  | Langages basés sur les modèles                                         | 49 |

|      | Langages basés sur les propriétés                                      | 49 |

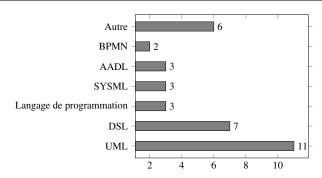

|      | Langages semi-formels                                                  | 50 |

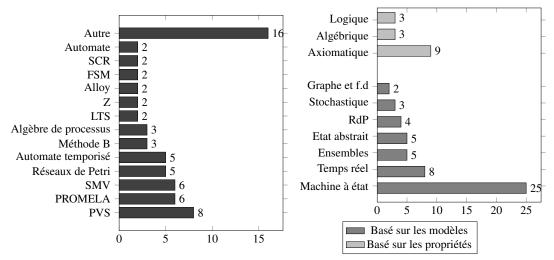

| 2.12 | Types des langages formels                                             | 50 |

| 2.13 | Classes des langages formels                                           | 50 |

| 2.14 | Type des langages de spécification des propriétés                      | 51 |

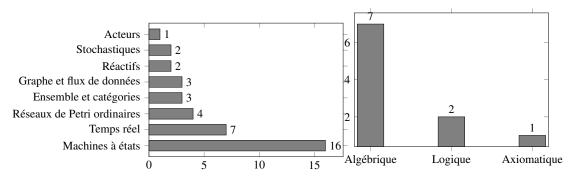

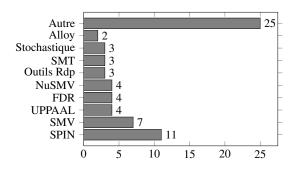

| 2.15 | Les Model-Checkers                                                     | 52 |

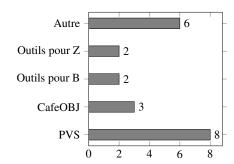

| 2.16 | Les theorem provers                                                    | 52 |

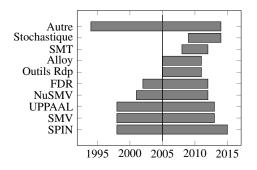

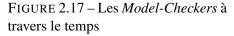

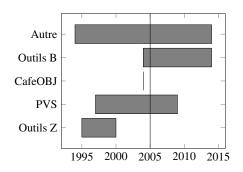

| 2.17 | Les Model-Checkers à travers le temps                                  | 53 |

| 2.18 | Les <i>Theorem-Provers</i> à travers le temps                          | 53 |

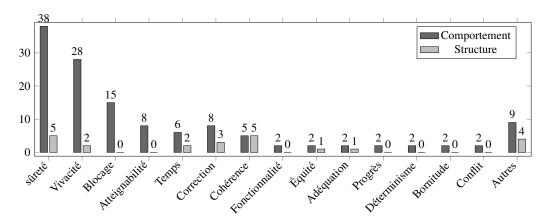

| 2.19 | Les propriétés vérifiées par chaque technique formelle                 | 54 |

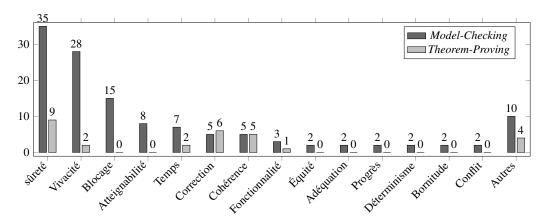

| 2.20 | Le domaine de la vérification                                          | 55 |

| 2.21 | Les propriétés vérifiées dans chaque facette du système                | 56 |

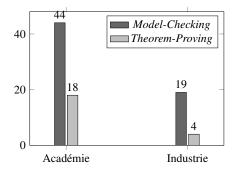

| 2.22 | Utilisation des méthodes formelles dans l'industrie et dans l'académie | 56 |

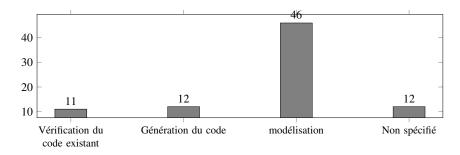

| 2.23 | L'objectif général de l'utilisation des méthodes formelles             | 57 |

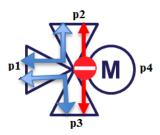

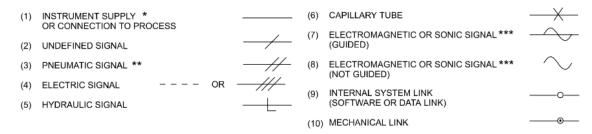

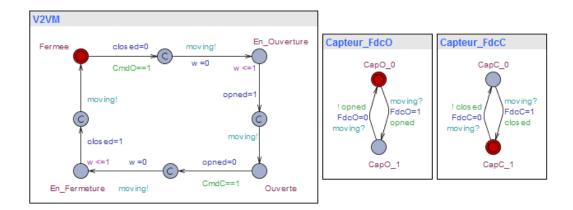

| 3.1  | Les différentes vues de la V2VM                                        | 65 |

| 3.2  | Exemple d'automate temporisé dans UPPAAL                               | 71 |

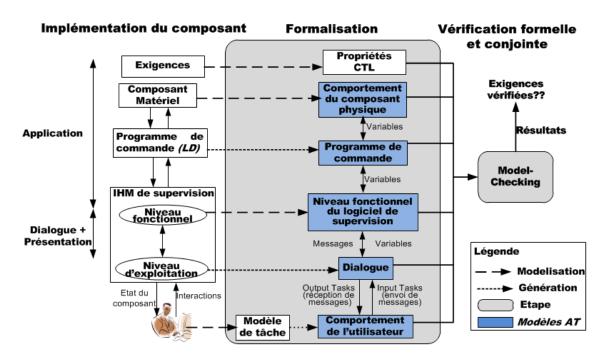

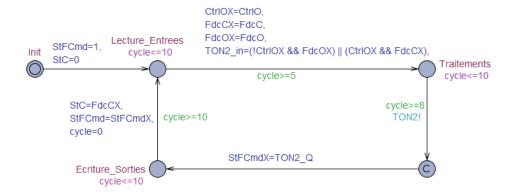

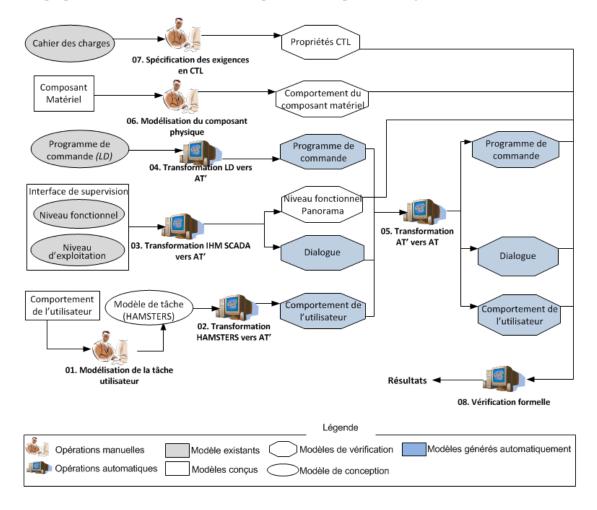

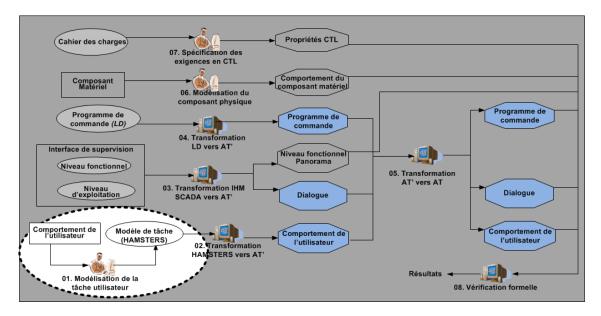

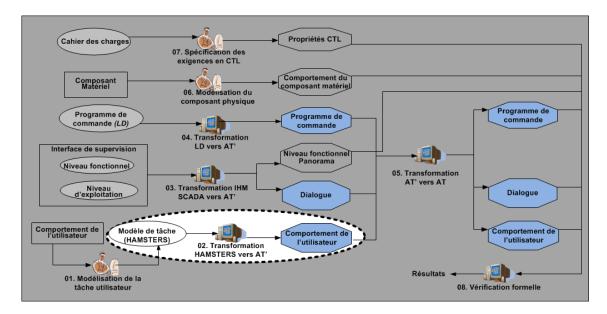

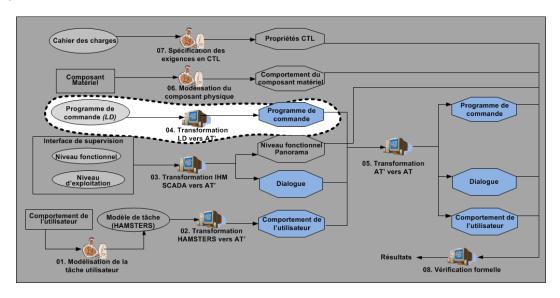

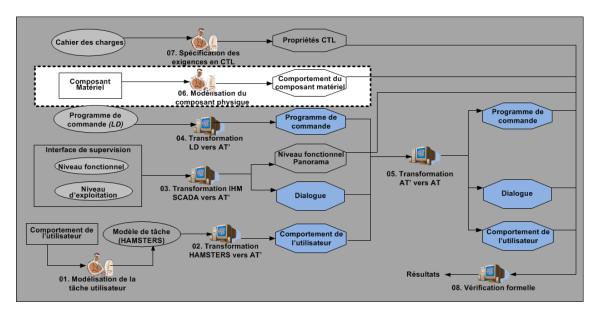

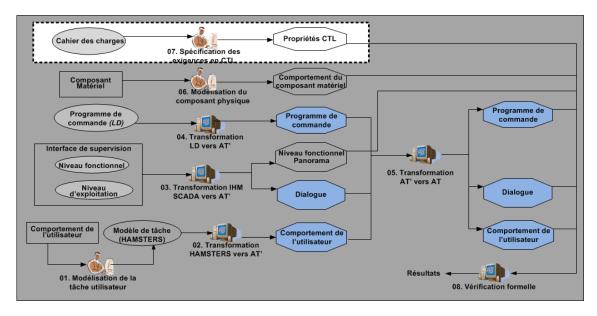

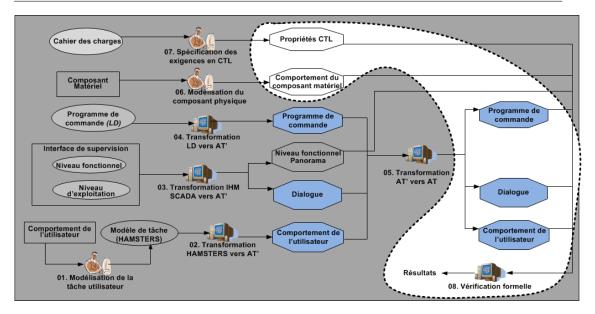

| 3.3  | Approche de vérification formelle des composants standards             | 73 |

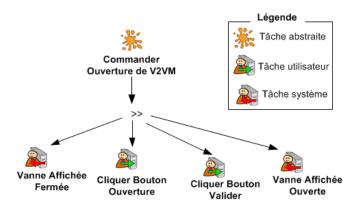

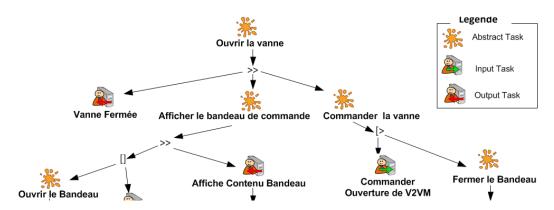

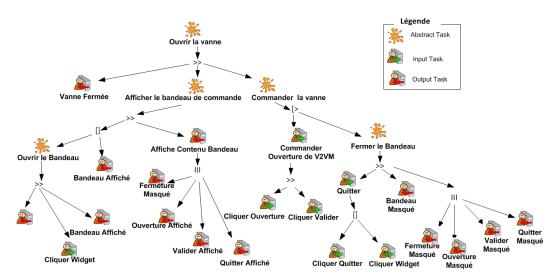

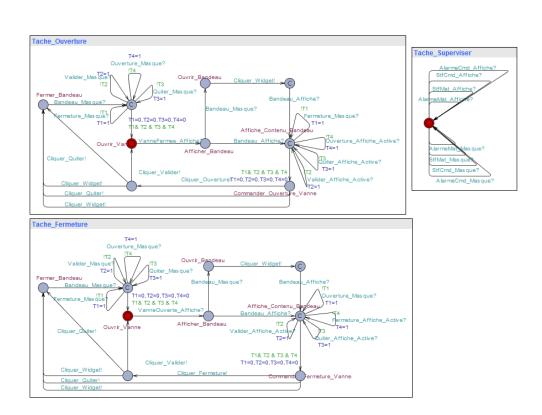

| 3.4  | Extrait de la tâche <i>Ouvrir la vanne</i> dans la notation Hamsters   | 74 |

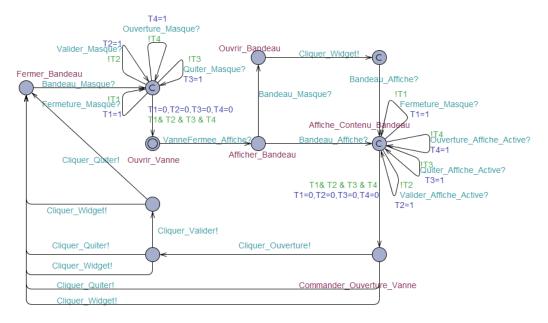

| 3.5  | Automate temporisé correspondant au modèle de tâches de la figure 3.4  | 76 |

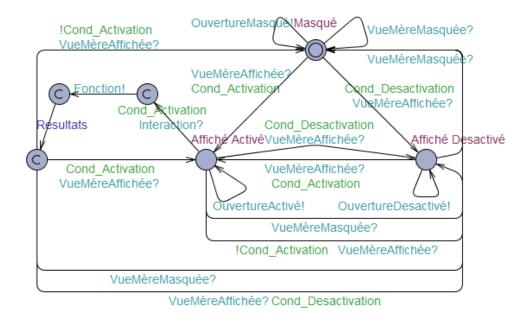

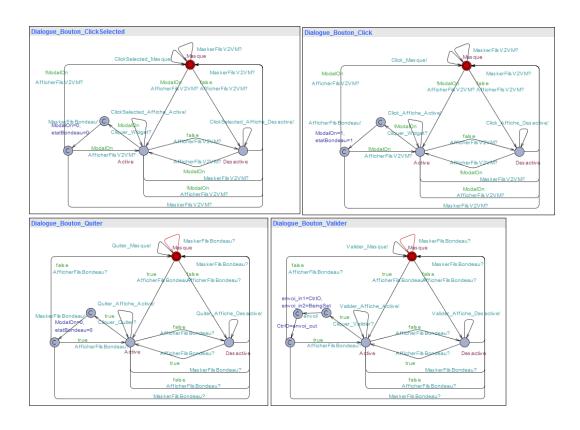

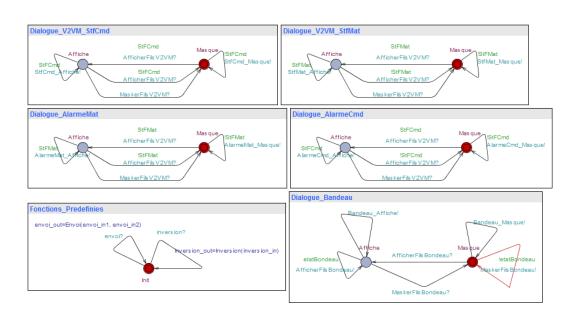

| 3.6  | Modélisation de l'IHM, Niveau exploitation: Objet de commande          | 78 |

viii Table des figures

| 3.7  | Modélisation de l'IHM, Niveau exploitation : Objet informationnel               | . 78 |

|------|---------------------------------------------------------------------------------|------|

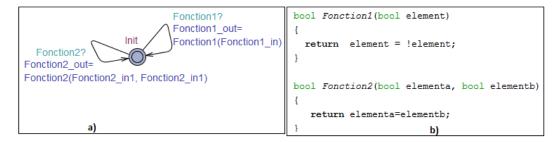

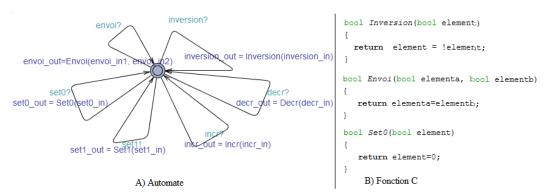

| 3.8  | Modélisation de l'IHM, Les fonctions prédéfinies : a) Automate temporisé des    |      |

|      | fonctions, b) Code C des fonctions                                              | . 79 |

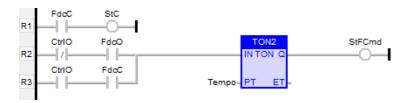

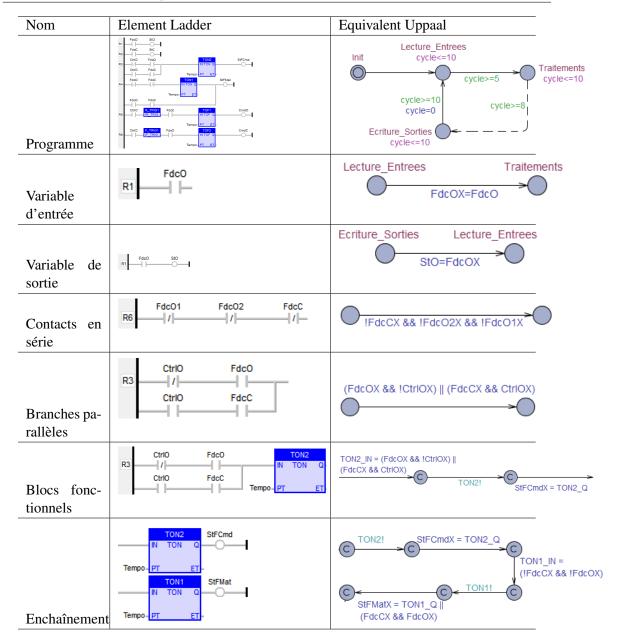

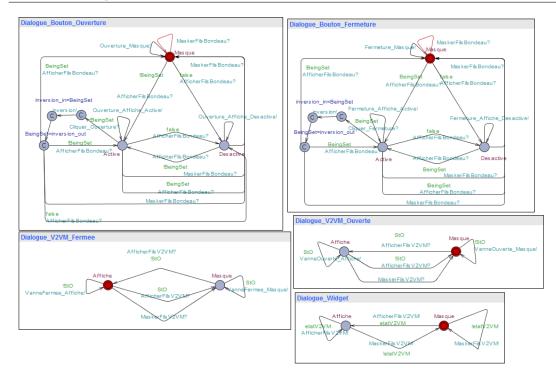

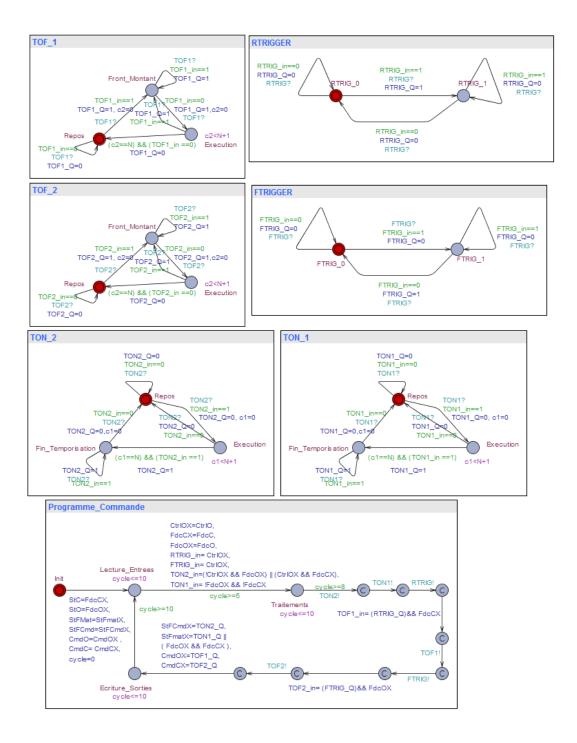

| 3.9  | Exemple d'un programme LD                                                       | . 80 |

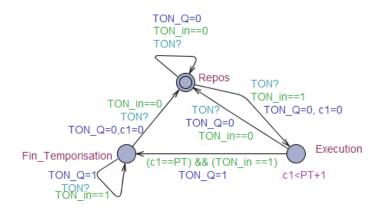

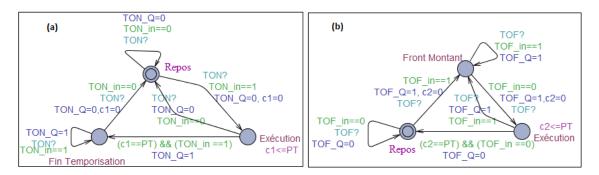

| 3.10 | Modélisation des temporisateurs ; (a) TON ; (b) TOF ;                           | . 80 |

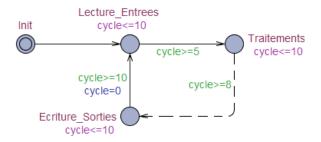

| 3.11 | Automate initial                                                                | 81   |

| 3.12 | Communication Automate principal et temporisateur                               | . 82 |

| 3.13 | Modélisation du programme LD de l'exemple 3.9                                   | . 82 |

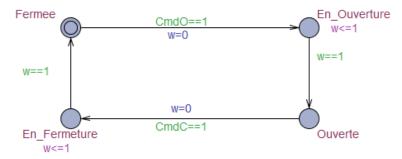

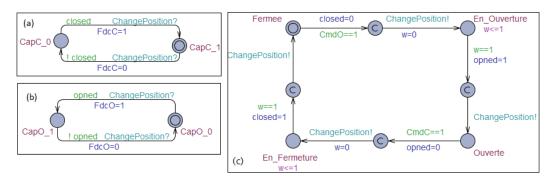

| 3.14 | Modélisation du comportement d'une vanne                                        | . 83 |

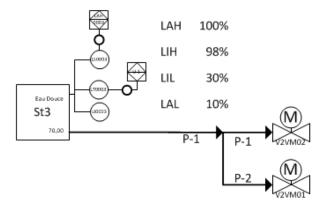

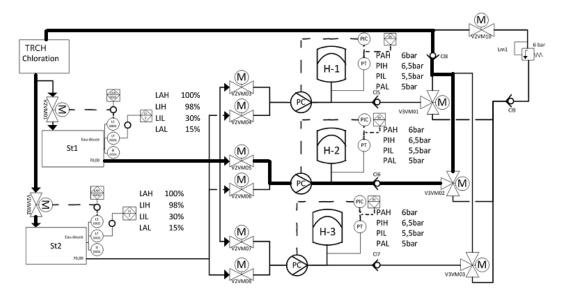

| 4.1  | Exemple de diagramme P&ID                                                       | . 88 |

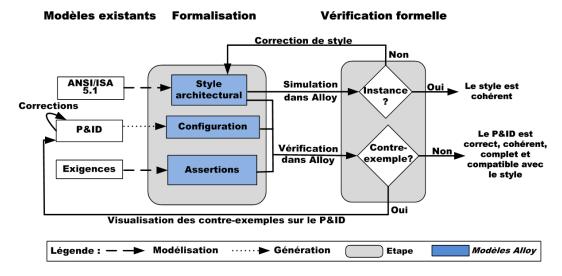

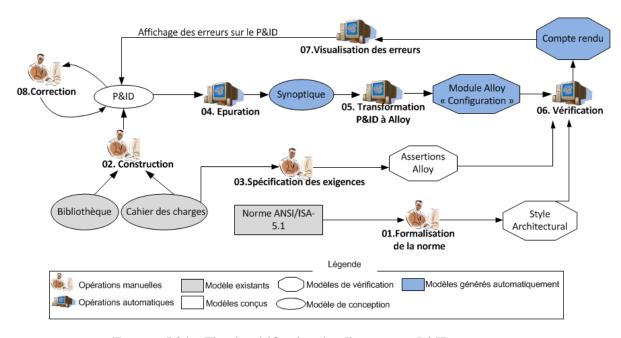

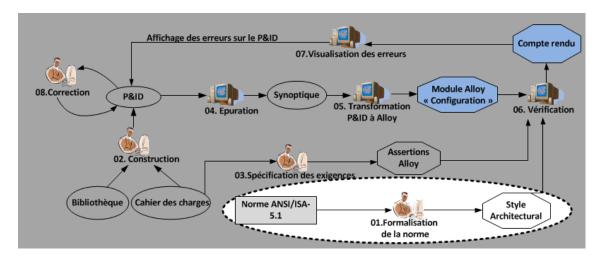

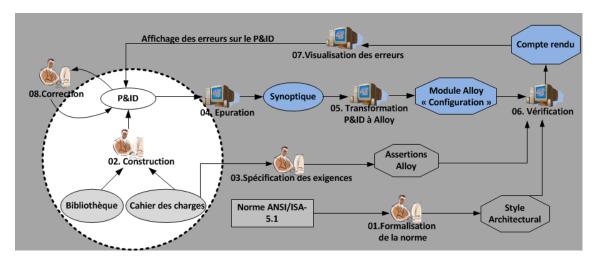

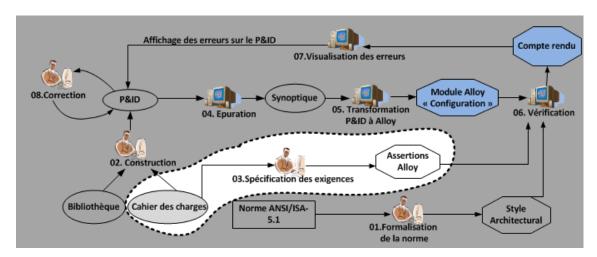

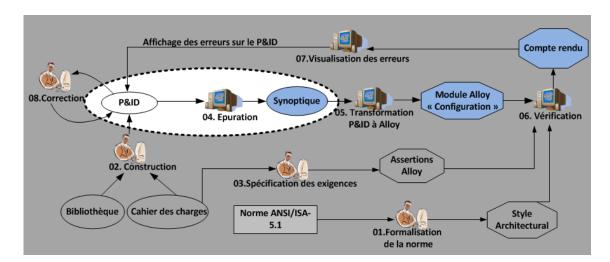

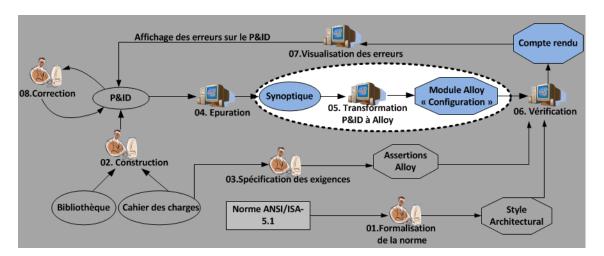

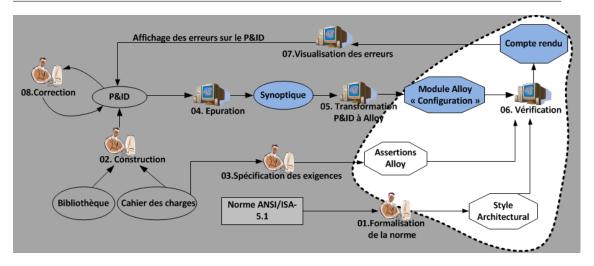

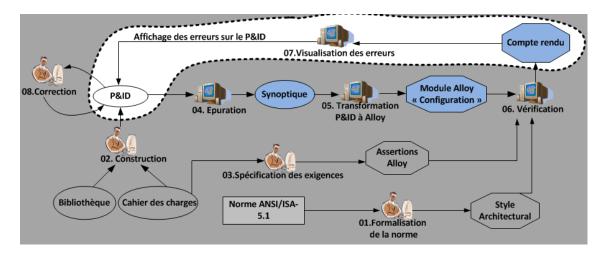

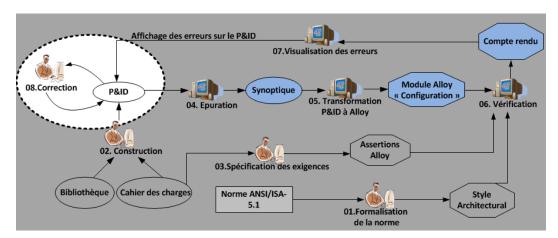

| 4.2  | Approche générale de vérification des P&ID                                      | 93   |

| 4.3  | Vanne trois voies motorisée (V3VM)                                              |      |

| 4.4  | Les connecteurs dans la norme ANSI/ISA-5.1                                      | 96   |

| 4.5  | La vérification de la cohérence du style : (a) L'instance retournée par Alloy ; |      |

|      | (b) Le P&ID correspondant                                                       | 98   |

| 4.6  | Extrait d'un contre-exemple retourné par l'outil Alloy                          | 100  |

| 4.7  | Data State Reference Model (DSRM) de Chi [2000]                                 | 103  |

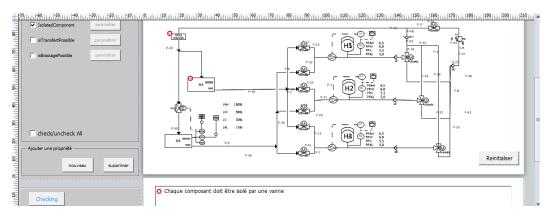

| 4.8  | Outil de vérification et de visualisation des erreurs                           | 105  |

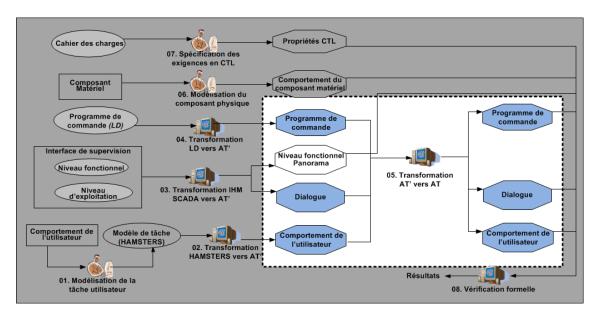

| 5.1  | Méthodologie mise en œuvre dans le projet de recherche                          | 111  |

| 5.2  | Outils                                                                          | 113  |

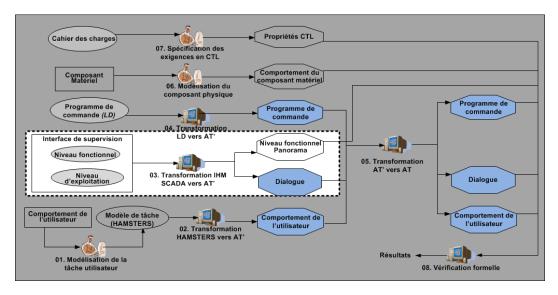

| 5.3  | Flot de vérification des composants standards                                   | 115  |

| 5.4  | Modélisation de la tâche utilisateur                                            | 116  |

| 5.5  | Extrait de modèle de tâches HAMSTERS                                            | 117  |

| 5.6  | Transformation de HAMSTERS en AT'                                               | 117  |

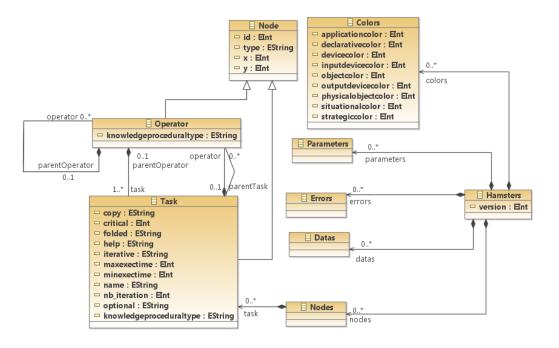

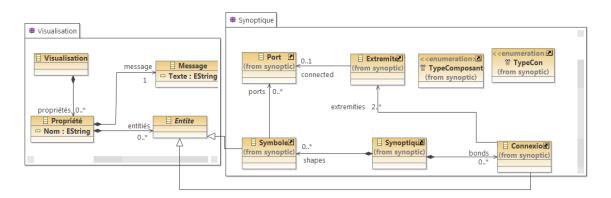

| 5.7  | Méta-modèle HAMSTERS                                                            | 118  |

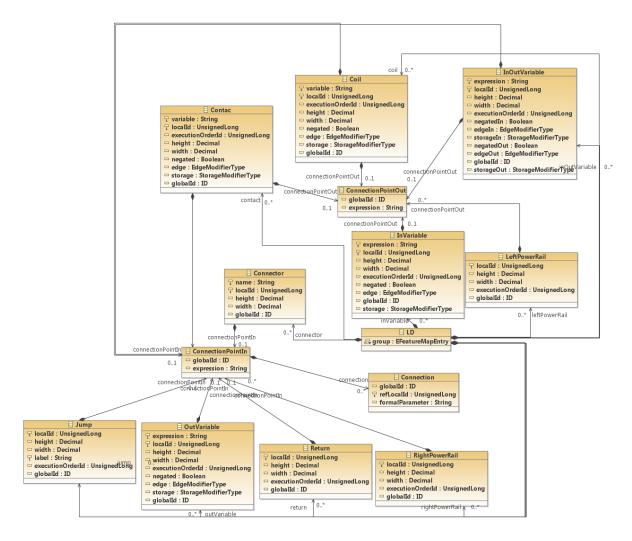

| 5.8  | Méta-modèle UPPAAL intermédiaire [Gerking 2013]                                 | 120  |

| 5.9  | Transformation des IHM SCADA en AT'                                             | 122  |

| 5.10 | Extrait du Méta-modèle Panorama E2                                              | 124  |

| 5.11 | Formalisation des fonctions prédéfinies dans Panorama E2 en : A) Automate       |      |

|      | temporisé; B) Fonctions C                                                       | 125  |

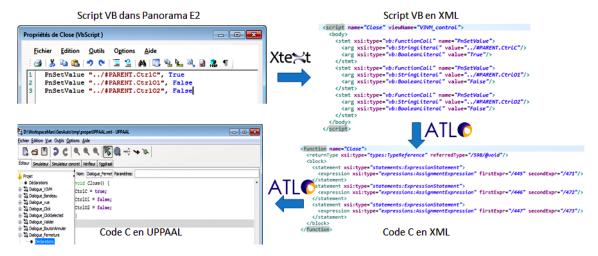

| 5.12 | Transformation des codes VB en C                                                | 125  |

| 5.13 | Transformation des programme LD en AT'                                          | 126  |

|      | Extrait d'un modèle Straton (fichier XML)                                       |      |

| 5.15 | Méta-modèle Straton                                                             | 128  |

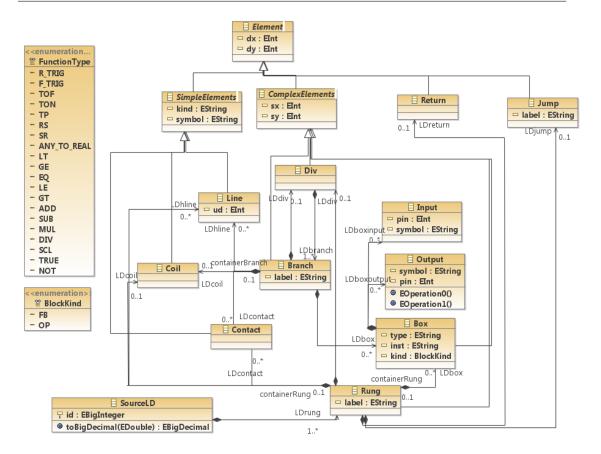

| 5.16 | Méta-modèle Beremiz                                                             | 129  |

| 5.17 | Règle ATL de transformation des éléments en parallèles                          | 133  |

|      | Transformation de AT' en AT                                                     |      |

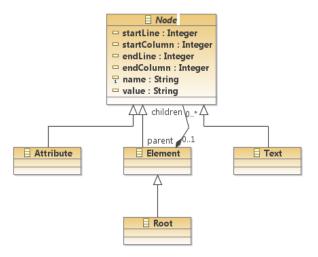

| 5 10 | Méta-modèle XMI                                                                 | 135  |

Table des figures ix

| 5.20 | Extrait d'un modèle XML                                                        |

|------|--------------------------------------------------------------------------------|

| 5.21 | Opération de modélisation du composant physique en AT                          |

| 5.22 | Opération de spécification des exigences en CTL                                |

| 5.23 | Vérification formelle par UPPAAL                                               |

| 5.24 | Flot de vérification des diagrammes P&ID                                       |

| 5.25 | Opération de formalisation de la norme ANSI/ISA                                |

| 5.26 | Opération de construction                                                      |

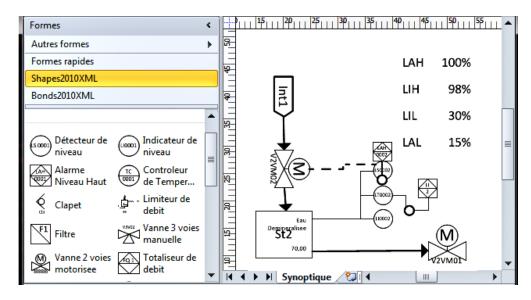

| 5.27 | Exemple d'un P&ID saisi sous Visio à partir d'une bibliothèque                 |

| 5.28 | Opération de spécification des exigences                                       |

| 5.29 | Opération d'épuration                                                          |

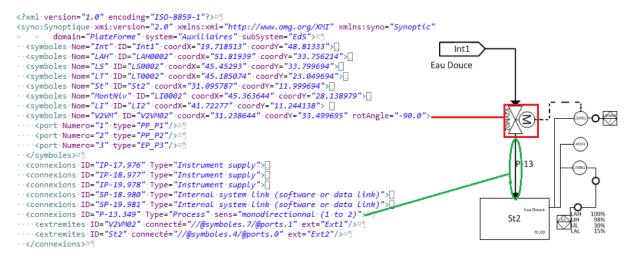

| 5.30 | Extrait du modèle synoptique correspondant au P&ID de la figure 5.27 144       |

| 5.31 | Opération de transformation des diagrammes P&ID en Alloy                       |

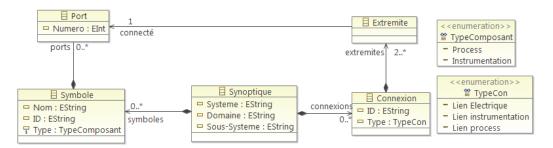

| 5.32 | Le méta-modèle des diagrammes P&ID [Bignon 2012]                               |

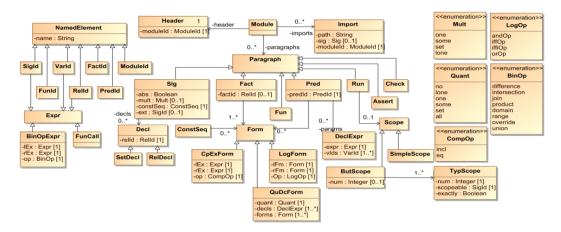

| 5.33 | Le métamodèle Alloy [Garis et al. 2012]                                        |

| 5.34 | Opération de vérification formelle                                             |

| 5.35 | Opération de visualisation des erreurs sur le P&ID                             |

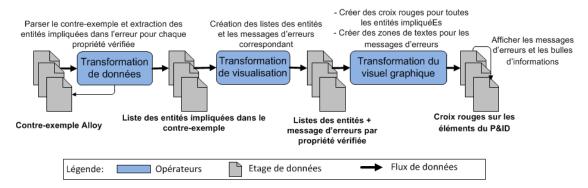

| 5.36 | Flot de visualisation des contre-exemples Alloy sur les diagrammes P&ID 149    |

| 5.37 | Méta-modèle pour la visualisation des erreurs                                  |

| 5.38 | Opération de correction                                                        |

| 6.1  | La tâche <i>Ouvrir la vanne</i> en HAMSTERS                                    |

| 6.2  | Automate temporisé généré à partir du modèle HAMSTERS de la figure 6.1 156     |

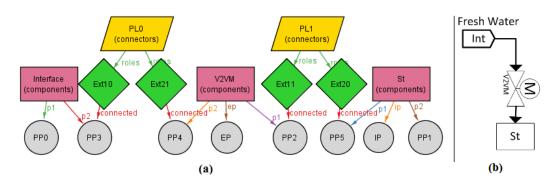

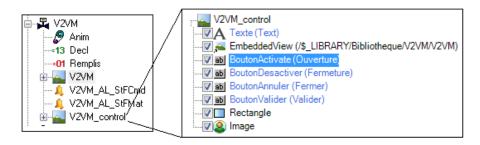

| 6.3  | Implémentation de la V2VM dans Anaxagore                                       |

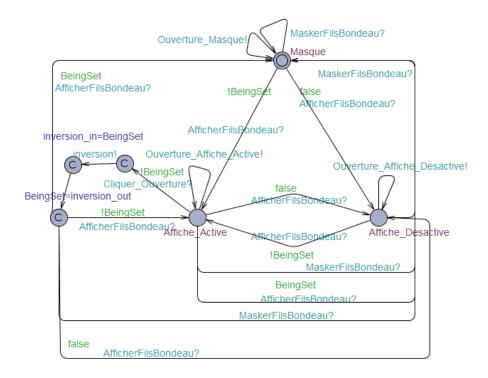

| 6.4  | Automate temporisé généré à partir du bouton Ouverture                         |

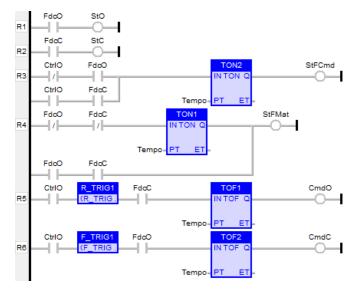

| 6.5  | Programme LD de la V2VM                                                        |

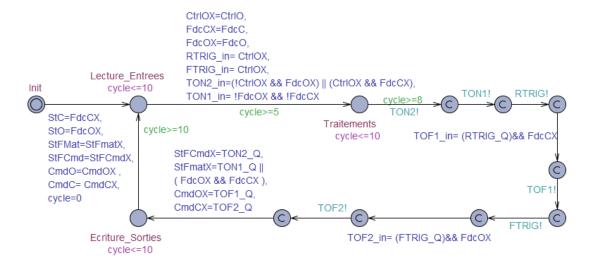

| 6.6  | Automate temporisé généré automatiquement à partir du programme LD de la       |

|      | figure 6.5                                                                     |

| 6.7  | Modélisation du composant matériel : (a) Capteur fin de course-fermeture ; (b) |

|      | Capteur fin de course-ouverture ; (c) La vanne                                 |

| 6.8  | Simulation du contre-exemple dans Straton                                      |

| 6.9  | Un extrait du diagramme P&ID du système EdS                                    |

| 6.10 | Visualisation du contre-exemple                                                |

| C 1  | E di la di la VM                                                               |

| Cal  | Extrait du contre-exemple en XML                                               |

Table des figures

# Liste des tableaux

| 2.1 | Fiche de relecture pour l'extraction de données                          |

|-----|--------------------------------------------------------------------------|

| 2.2 | Provenance des articles et sélections                                    |

| 2.3 | Citations                                                                |

| 2.4 | Les propriétés vérifiées par domaines d'application                      |

| 3.1 | Les différentes variables booléennes de la V2VM                          |

| 3.2 | Correspondances des opérateurs entre CTL et UPPAAL                       |

| 3.3 | Transformation des tâches en signaux                                     |

| 3.4 | Transformation des opérateurs de tâches en automates temporisés          |

| 4.1 | Visualisation des contre-exemples Alloy sur le P&ID                      |

| 5.1 | Tableau récapitulatif des différences entre Straton et Beremiz           |

| 5.2 | Règles de transformations des éléments Ladder en UPPAAL                  |

| 6.1 | Composition du modèle complet de la V2VM                                 |

| 6.2 | Récapitulatif de la vérification formelle du P&ID du système EdS 170     |

| 6.3 | Temps de génération des modèles UPPAAL pour les composants de la biblio- |

|     | thèque Anaxagore                                                         |

| A.1 | Requêtes de recherche pour les différentes bases                         |

| A.2 | Articles retenus pour l'étude                                            |

## Glossaire

ADL: Architecture Description Languages. 90

**API**: Automate Programmable Industriel. 19–22, 67, 79, 81, 113, 126, 130

**AT**: Automates temporisés. 70, 80, 86, 161

ATL: Atlas Transformation Language. 134, 135

**CTL**: Computation Tree Logic. ix, 13, 48, 51, 63, 68, 70, 71, 73, 74, 85, 137, 164

**EdS**: Eau douce Sanitaire. iv, ix, xi, 153, 154, 164–171, 176

**IDE**: Integrated Development Environment. 113

IDM: Ingénierie Dirigée par les Modèles. 26, 27, 68, 69, 93, 111, 112, 114, 152, 175

**IHM**: Interface Homme-Machine. iii, iv, vii, viii, 19–25, 27, 29, 30, 64, 65, 67–69, 73, 74, 76, 78, 79, 81, 83, 84, 86, 109, 110, 112, 114–116, 122, 123, 125, 126, 137, 153, 154, 156, 161, 164, 174, 176, 177

**LD**: Ladder Diagram. iii, iv, viii, 22, 28, 68, 73, 74, 79–82, 86, 109, 110, 112, 126–130, 153, 158, 162, 175

LTL: Linear Temporal Logic. 48, 51, 68

**P&ID**: Piping and Instrumentation diagram. iii–v, viii, ix, xi, 4, 5, 26–29, 59, 87–94, 96–106, 109, 110, 114, 138–154, 164–172, 175–178, 216, 217

SCADA: Supervisory Control And Data Acquisition. 19, 20, 24, 76, 77, 79

UML: Unified Modeling Language. 14, 24, 49–51

**XML**: eXtensible Markup Language. 102, 112, 114, 116, 118, 119, 126, 127, 130, 134, 135, 150, 151, 168

xiv Glossaire

## Contributions scientifiques

## Conférences internationales avec comité de lecture :

- **1. Soraya MESLI-KESRAOUI**, Armand TOGUYENI, Alain BIGNON, Flavio OQUENDO, Djamal KESRAOUI, Pascal BERRUET: Formal and Joint Verification of Control Programs and Supervision Interfaces for Socio-technical Systems Components. In: *13th IFAC Symposium on Analysis, Design, and Evaluation of Human-Machine Systems HMS* 2016 Kyoto, Japan, 30 August 2 September 2016 49 (2016), Nr. 19, p. 426–431

- **2. Soraya MESLI-KESRAOUI**, Alain BIGNON, Djamal KESRAOUI, Armand TOGUYENI, Flavio OQUENDO, Pascal BERRUET: Vérification Formelle de Chaînes de Contrôle-Commande d'Éléments de Conception Standardisés. In: *MOSIM 2016, 11ème Conférence Francophone de Modélisation, Optimisation et Simulation, Montréal, Québec, Canada, 22 24 Août, 2016.*

- **3. Soraya MESLI-KESRAOUI**, Djamal KESRAOUI, Flavio OQUENDO, Alain BIGNON, Armand TOGUYENI, Pascal BERRUET: Formal Verification of Software-Intensive Systems Architectures Described with Piping and Instrumentation Diagrams. p. 210–226. In: TEKINERDOGAN, Bedir (Editor); ZDUN, Uwe (Editor); BABAR, Ali (Editor): Software Architecture: 10th European Conference, ECSA 2016, Copenhagen, Denmark, November 28 December 2, 2016, Proceedings. Cham: Springer International Publishing, 2016. URL http://dx.doi.org/10.1007/978-3-319-48992-6\_16. ISBN 978-3-319-48992-6

La conception des systèmes complexes fait intervenir des concepteurs provenant d'horizons techniques très variés. Les systèmes de contrôle-commande, en particulier, parce qu'ils nécessitent des connaissances avancées concernant le système piloté, le système pilotant et l'utilisateur, illustrent cet état de fait. La communication entre les concepteurs associés demeure souvent très compliquée notamment du fait de la variété des langages techniques utilisés. Ces problèmes de communication et d'interprétation de spécifications peuvent conduire à des erreurs de conception et au non respect du cahier des charges. Une étude a montré que 70% des erreurs des produits logiciels trouvent leur origine dans les phases de spécification et de conception [Selby et Selby 2007], et que 72% de ces erreurs sont détectées dans les phases de test ou en opération [Pham 2007]. La détection tardive des erreurs entraine une explosion des délais ainsi que les coûts de re-conception.

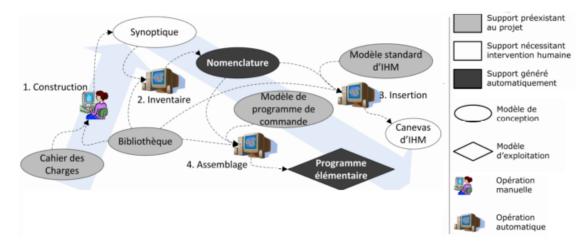

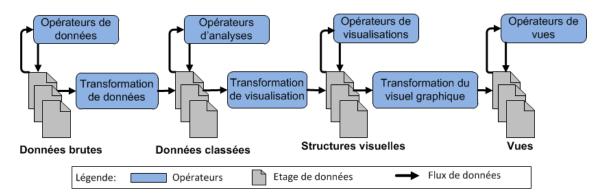

Dans le but de maîtriser la conception des systèmes de contrôle-commande, des démarches de conception plus rigoureuses et de plus en plus automatisées sont adoptées. La démarche de conception ascendante, par exemple, se focalise plus sur la réutilisation du code en adoptant une forte standardisation des composants constitutifs du système. La conception consiste ainsi en l'agrégation de plusieurs composants réutilisables. Bien qu'elle offre une forte réutilisation, cette démarche manque souvent de cohérence entre les composants utilisés et de vision globale du système à concevoir. Á contrario, la démarche, dite descendante, se focalise sur une vision plus générale en se basant sur des modèles de haut niveau. L'idée derrière cette démarche consiste à spécifier le système par un modèle abstrait décrivant un point de vue de conception, qui sera raffiné ou transformé en modèles décrivant d'autres points de vue, garantissant ainsi une certaine cohérence entre les modèles de départ et les modèles générés. Cependant, le raffinage et la transformation peuvent engendrer la propagation d'erreurs vers les modèles raffinés ou transformés. De plus, ces modèles manquent de modularité et sont donc difficilement réutilisables. Á l'issue de ces deux démarches, la démarche mixte a émergé. Elle combine les deux premières démarches pour garantir, d'une part, la modularité et la réutilisation du code par l'utilisation d'un ensemble de composants prédéfinis "sur étagère" et, d'autre part, l'intégration d'une cohérence et d'une vision globale offertes par les modèles. En pratique, elle consiste donc en la construction d'un modèle structurel en s'appuyant sur des composants standards du domaine. Ensuite les modèles de contrôle-commande sont générés par intégration des modèles de contrôle-commande de chaque composant apparaissant dans le modèle structurel du système.

Cependant, la démarche mixte hérite des deux démarches, ascendante et descendante, de leurs avantages et aussi de leurs inconvénients. Les composants prédéfinis doivent être libres de tout défaut afin de garantir la qualité des systèmes conçus à partir de ces composants. Les modèles quant à eux, doivent intégrer les différentes exigences et recommandations du cahier des charges. Ils doivent être complets, cohérents et corrects afin de garantir la qualité des systèmes obtenus après raffinage de ces modèles.

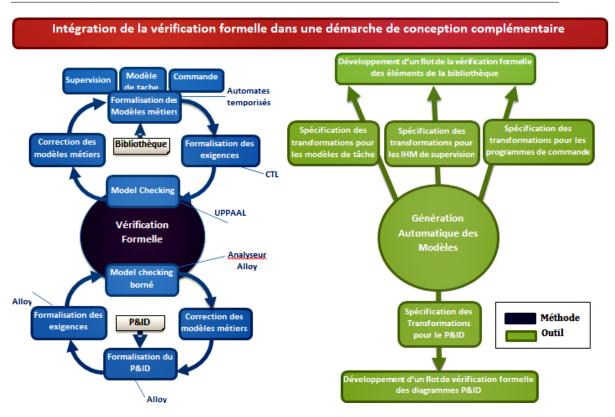

## **Contexte**

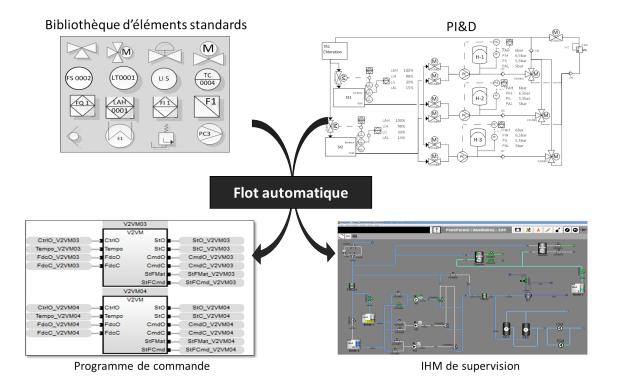

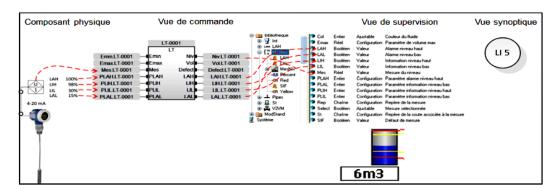

Des études menées précédemment par SEGULA Technologies en collaboration avec le Lab-STICC ont abouti à la définition d'une démarche de conception conjointe de programme de commande et d'interface de supervision [Bignon et al. 2010, Bignon 2012, Bignon et al. 2013, Goubali et al. 2014]. Cette démarche (mixte) s'appuie sur deux piliers fondamentaux, le premier est la standardisation des composants de conception et le deuxième l'utilisation de modèles métier maîtrisés par les experts pour la spécification de leur système. Les modèles métier sont obtenus par une approche ascendante d'agrégation des éléments de conception. Les programmes de commande et les interfaces de supervision sont obtenus par une approche descendante de raffinages successifs des modèles métiers mettant en œuvre les concepts de l'ingénierie dirigée par les modèles. Bien qu'assurant déjà une bonne cohérence, la démarche proposée ne permet pas la vérification au plus tôt des programmes générés. Nos travaux, s'inscrivant dans la continuité de ces résultats, étudient les apports de différentes techniques de vérification formelle au sein de la démarche précédemment développée.

Nos travaux, réalisés au cours d'une thèse CIFRE (Convention Industrielle de Formation à la Recherche en Entreprise) entre l'entreprise Segula Technologies et les laboratoires de recherche : LabSTICC, IRISA et CRIStAL, se placent dans le contexte de la mise en œuvre de boucles de pilotage pour les systèmes de contrôle-commande. Pour s'inscrire dans la démarche "first time right", il est nécessaire de proposer des méthodes de conception intégrants des aspects de vérification et de rebouclage rapide inhérent à tout processus de conception.

## Problématique

Garantir la qualité d'un système revient à vérifier son respect vis-à-vis du cahier des charges, son aptitude à assurer les fonctionnalités demandées et aussi son bon fonctionnement. Les techniques de vérification formelle ont démontré leur efficacité dans la détection des erreurs et la garantie de la qualité des systèmes. Ces techniques basées essentiellement sur des notations mathématiques offrent un moyen robuste pour la détection et la correction des erreurs de conception. Elles sont basées sur une description en langages formels du système, sur-lequel un ensemble de propriétés est vérifié.

Cependant, plusieurs obstacles limitent l'utilisation de ces techniques dans le monde industriel [Bjørner et Havelund 2014]. Le manque d'automatisme, cas du *Theorem-Proving* par exemple, l'explosion combinatoire des états, dans le cas du *Model-Checking*, et la difficulté de la manipulation des notations formelles par des concepteurs métier, restent les plus récurrentes.

## Objectifs de la thèse

L'objectif général de nos travaux de thèse consiste à introduire des boucles de vérification formelles dans les processus de conception des systèmes de contrôle-commande complexes,

afin de garantir la qualité des systèmes produits par la détection et l'élimination des erreurs dans les phases de conception.

Nous ambitionnons de répondre à trois objectifs émergeant de notre contexte de travail. Le premier consiste à garantir la qualité des composants prédéfinis utilisés dans la conception des systèmes de contrôle-commande afin de limiter la propagation des erreurs vers le système complet. Le deuxième objectif vise à garantir la qualité des modèles métiers utilisés pour le raffinage. Ces modèles doivent être complets et cohérents. Ils intègrent aussi bien des exigences fonctionnelles que des exigences non-fonctionnelles. Par ailleurs, les notations formelles étant peu accessibles à notre public de concepteurs visé, le troisième objectif de nos travaux porte sur les moyens de faciliter l'obtention des modèles formels dans un contexte industriel.

## Structuration du manuscrit

Nous avons proposé, à travers ce travail de recherche, des contributions méthodologiques et aussi techniques pour garantir la qualité des systèmes de contrôle-commande, en utilisant les méthodes formelles. La suite du manuscrit est structurée en trois parties regroupant sept chapitres.

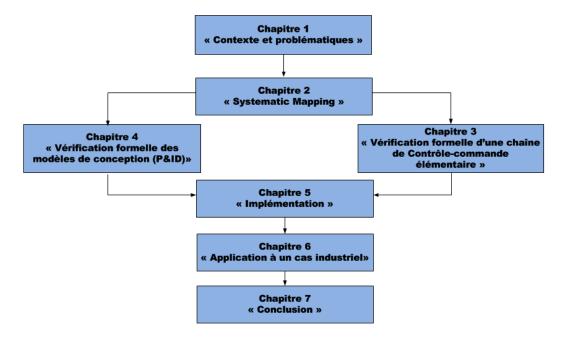

FIGURE 1 – Organisation de ce manuscrit

La première partie, composée des chapitres 1 et 2, présente le contexte de ce travail de thèse et un état de l'art scientifique.

Le chapitre 1 présente le contexte industriel et académique des travaux présentés dans ce manuscrit. Il présente aussi un aperçu des méthodes et démarches de conception des systèmes

de contrôle-commande. Il se termine par une présentation détaillée de la problématique et les verrous scientifiques de nos travaux de thèse.

Le chapitre 2 dresse un état de l'art, relatif à nos travaux, issu d'une revue systématique de la littérature. Nous présentons, dans ce chapitre, le protocole suivi pour l'élaboration de la revue systématique et son application pour l'extraction des articles pertinents. Nous présentons, ensuite, les résultats concernant l'usage des méthodes formelles dans le domaine industriel et académique que nous discutons, à la fin du chapitre.

La deuxième partie présente les différentes contributions méthodologiques. Elle est constituée des chapitres : 3, 4.

Le chapitre 3 présente, en détail, notre approche de vérification d'une chaîne de contrôlecommande élémentaire utilisée dans une démarche de conception ascendante. En effet, nous présentons, à travers un exemple de composant standard, la formalisation des différentes vues de ce composant en automates temporisés. Ensuite, nous listons les différents types de propriétés qu'un composant standard doit vérifier. Enfin, nous écrivons ces propriétés en CTL et nous les vérifions par *Model-Checking* sous UPPAAL.

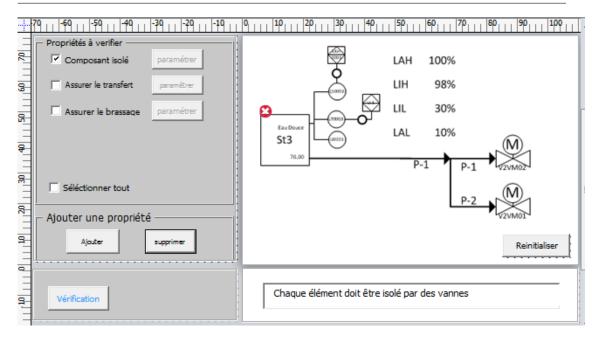

Le chapitre 4 présente notre approche de vérification formelle des diagrammes P&ID (approche descendante). Dans ce chapitre, nous proposons et nous définissons un style architectural, en Alloy, pour la norme ANSI/ISA-5.1 qui régit la construction de diagrammes P&ID. Nous présentons aussi la formalisation et la génération automatique des modèles Alloy à partir des diagrammes P&ID. Sur ces modèles combinés avec le style architectural, nous vérifions, par *Model-Checking*, la complétude, la cohérence, la compatibilité de ces diagrammes à la norme ANSI/ISA-5.1 [ISA 1992] et aussi leur conformité au cahier des charges i.e. leur satisfaction des exigences fonctionnelles et non-fonctionnelles. Dans le cas où l'outil d'analyse retourne un contre-exemple (non satisfaction d'une exigence), nous proposons aussi une visualisation de celui-ci sur les diagrammes P&ID afin d'assister les concepteurs dans la compréhension et la correction d'erreurs.

La troisième partie de ce manuscrit, aborde nos contributions de mise en œuvre et d'application. Elle est composée des chapitres 5 et 6.

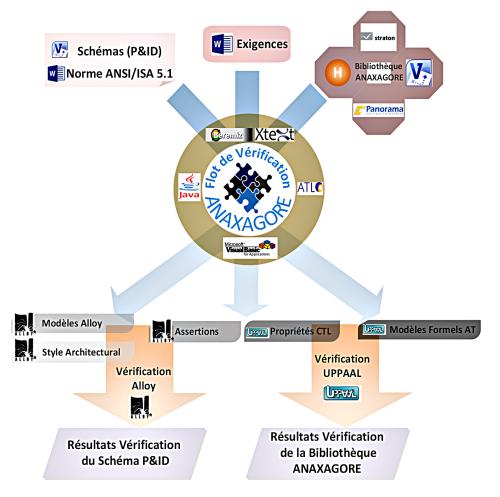

Dans le chapitre 5, nous présentons l'automatisation de nos approches sous la forme de deux flots de vérification semi-automatisés. Le premier flot supporte notre approche de vérification formelle des composants standards. Il porte sur la génération automatique par transformation de modèles, des automates temporisés à partir des différentes vues des composants standards. Le deuxième est dédié à la vérification des diagrammes P&ID et consiste en la génération des modèles Alloy à partir des diagrammes P&ID. Ces deux flots ainsi que les différentes transformations de modèles permettant la génération automatique de modèles formels sont présentés dans ce chapitre.

Dans le chapitre 6, nous appliquons nos deux approches de vérification formelle à des cas industriels concrets. L'approche de vérification des composants standards a été appliquée sur la

vanne deux voies motorisée (V2VM). Par ailleurs, nous appliquons notre deuxième approche sur le P&ID du système de stockage, de production et de distribution d'eau douce embarquée dans un navire (EdS).

Enfin, le chapitre 7 conclut ce manuscrit par un rappel des différentes contributions présentées et les perspectives pour des recherches futures liées à cette thèse.

# Première partie Contexte et état de l'art

# Contexte et problématiques

**Résumé :** Dans ce chapitre, nous présentons et situons le contexte académique et industriel de cette thèse. Le contexte académique porte sur l'ingénierie système, la spécification des exigences, les langages de spécification, la vérification formelle et les méthodes formelles. Le contexte industriel porte sur la conception des systèmes de contrôle-commande complexes. Tout d'abord, nous présentons l'architecture générale d'un système de contrôle-commande, puis nous nous focalisons sur l'architecture SCADA. Ensuite, nous présentons les différentes approches traditionnelles pour la conception des systèmes de contrôle-commande et celles basées sur la génération automatique. Enfin, nous abordons et présentons les problématiques liées à cette thèse et les différents verrous scientifiques qui en découlent.

## Sommaire

| 1.1 | Introd | uction                                                                             | 8  |

|-----|--------|------------------------------------------------------------------------------------|----|

| 1.2 | L'ingé | nierie système : contexte académique                                               | 8  |

|     | 1.2.1  | La spécification des exigences                                                     | 9  |

|     | 1.2.2  | La vérification des exigences                                                      | 13 |

| 1.3 | Conce  | ption des systèmes de contrôle-commande : contexte industriel .                    | 16 |

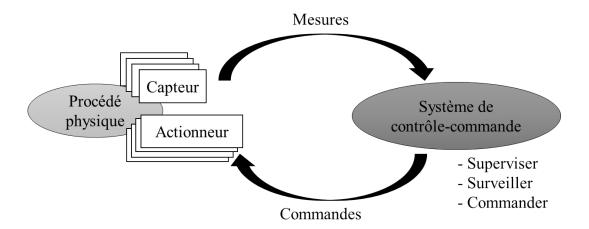

|     | 1.3.1  | Les systèmes de contrôle-commande                                                  | 16 |

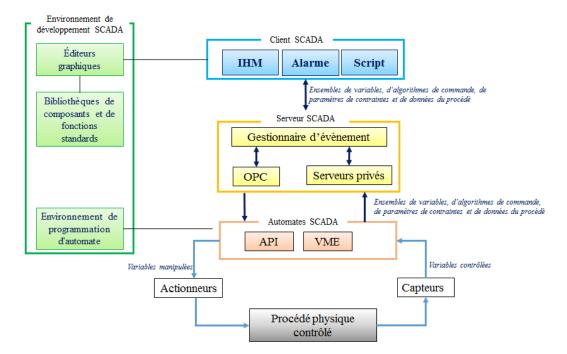

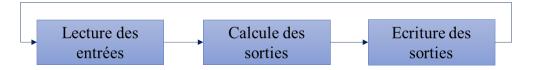

|     | 1.3.2  | L'architecture SCADA                                                               | 17 |

|     | 1.3.3  | Approches traditionnelles pour la conception des systèmes de contrôle-<br>commande |    |

|     | 1.3.4  | Génération automatique des programmes de contrôle-commande                         |    |

| 1.4 | Problé | matiques et verrous scientifiques                                                  | 27 |

|     | 1.4.1  | Problématiques                                                                     | 27 |

|     | 1.4.2  | Verrous scientifiques                                                              | 28 |

| 1.5 | Concl  | usion                                                                              | 29 |

|     |        |                                                                                    |    |

## 1.1 Introduction

Le besoin d'amélioration imposé aux industriels, ainsi que le besoin de rendre les systèmes plus performants, plus sûrs, plus ergonomiques, offrant toujours plus de fonctionnalités aux utilisateurs, ne font qu'augmenter la complexité des systèmes. Cette complexité se traduit par l'augmentation importante de la taille des composants et des fonctionnalités. Elle a pour conséquences de nécessiter des équipes de développement de taille importante et souvent composées d'intervenants appartenant à divers domaines de l'ingénierie.

Une étude menée dans le domaine du génie logiciel, impliquant 14 systèmes complexes et comportant 3418 erreurs, montre que 70% des erreurs sont introduites lors des phases d'analyse (spécification et conception) [Selby et Selby 2007]. Ces résultats sont similaires à ceux de Sourisse et Boudillon [1997], qui trouvent que le pourcentage des erreurs introduites dans les phases d'analyse approche les 79%. Ces erreurs sont détectées généralement tardivement dans le cycle de vie d'un système et leurs corrections font exploser les coûts. D'autres études montrent que 72% des erreurs sont détectées à la livraison [Pham 2007] et que le coût relatif aux corrections augmente considérablement au fil du temps [Boehm et al. 1981]. En effet, plus l'erreur est détectée tard dans le cycle de vie, plus le coût relatif à sa correction est élevé. Les investigations montrent aussi que 95% des erreurs pourraient être détectées et éliminées dans la phase où elles sont introduites, contre 47% dans les phases ultérieures [Selby et Selby 2007]. L'adoption de méthodes qui offrent des outils et techniques pour gérer la complexité d'un système et contrôler sa conception et sa réalisation permettent de diminuer considérablement l'introduction des erreurs dans chaque phase du cycle de développement.

Les grands concepteurs de système complexes, comme la NASA, se sont rendus compte, dès les années 60, de la nécessité de définir des démarches rigoureuses et outillées afin d'assister la conception des systèmes complexes. Ces démarches sont connues sous le nom de l'*Ingénierie système* (IS).

## 1.2 L'ingénierie système : contexte académique

L'ingénierie système est une démarche dédiée à la réalisation des systèmes complexes. Son but est de cadrer le processus du développement d'un système. Elle propose des méthodes et outils pour maitriser le développement des systèmes durant toutes les phases du cycle de vie, à savoir : la définition des besoins des clients, la conception, la réalisation, l'intégration et la vérification. Elle permet, ainsi, de gérer la complexité des systèmes, en diminuant le risque d'introduction des erreurs. Plusieurs normes, telles-que ANSI/EIA-632 [EIA/ANSI-632 1999], IEEE1220 [IEEE-1220 1999], ISO 15288 [ISO-15288 2002] visent à encadrer la conception des systèmes complexes en adoptant l'IS. Nous retenons la définition suivante pour la notion d'IS:

**Définition 1.1** [Fiorèse et Meinadier 2012] L'IS est une démarche méthodologique coopérative et interdisciplinaire, fondée sur la science et l'expérience, qui englobe l'ensemble des activités adéquates pour concevoir, développer, faire évoluer et vérifier un ensemble de produits, processus et compétences humaines apportant une solution économique et performante aux besoins des parties prenantes et acceptable par tous. Cet ensemble est intégré en un système, dans un contexte de recherche d'équilibre et d'optimisation sur tout son cycle de vie.

L'IS propose un processus de développement fondé sur plusieurs étapes. Une des étapes les plus importantes dans le cycle de développement d'un système, selon l'IS, est l'*ingénierie des exigences*. Une exigence est définie par :

**Définition 1.2** [Fiorèse et Meinadier 2012] Une exigence prescrit une propriété dont l'obtention est jugée nécessaire. Son énoncé peut être une fonction, une aptitude, une caractéristique ou une limitation à laquelle doit satisfaire un système, un produit ou un processus.

Le processus de l'ingénierie des exigences permet d'extraire les besoins des parties prenantes, de les analyser, de les spécifier et enfin, de les vérifier [Fiorèse et Meinadier 2012]. Nous nous intéressons, dans cette thèse, aux deux dernières étapes, à savoir : la spécification des exigences et la vérification.

## 1.2.1 La spécification des exigences

La spécification des exigences, dans un cycle de développement, consiste à documenter différents types d'exigences d'une façon cohérente, claire et précise [Alagar et Periyasamy 2011], dans le but de rendre ces exigences facilement compréhensibles par les parties prenantes [Wiegers et Beatty 2013]. Cet ensemble d'exigences est utilisé comme un référentiel qui suit le système durant tout son cycle de développement [Fiorèse et Meinadier 2012]. Dans l'étape de vérification, par exemple, ce référentiel est utilisé afin de s'assurer que le système respecte bien ses exigences. Le processus de spécification est défini comme :

**Définition 1.3** *IEEE-1233* [1998] Une spécification d'exigences de système (SES) est généralement considérée comme un document dans lequel sont énoncées les exigences fixées par le client, à l'intention de la communauté technique chargée de la conception et de la réalisation d'un système. Le recueil d'exigences qui forme la spécification et sa représentation sert de passerelle entre les deux parties ; il doit donc pouvoir être compris par chacune d'elles. Lors de la création d'un système, l'une des tâches les plus délicates est d'ailleurs de communiquer ces exigences, en un seul document, à tous les sous-ensembles de ces deux groupes. Cette opération requiert généralement l'utilisation de divers formalismes et langages.

La spécification doit inclure les activités suivantes :

L'élicitation des exigences, où toutes les exigences du système sont récoltées, en consultant les parties prenantes et les différentes documentations des systèmes (état de l'art technique, normes, contraintes, etc.).

- L'analyse des exigences et la négociation, où toutes les exigences sont analysées en détail et acceptées par les parties prenantes.

- La validation des exigences, où la cohérence et la complétude des exigences sont vérifiées.

Le processus de spécification produit les documents qui expriment les exigences fonctionnelles, non-fonctionnelles et également les contraintes que le système doit satisfaire. L'ensemble des exigences doit être complet et cohérent. En effet, la complétude signifie que le référentiel d'exigences doit contenir toutes les exigences nécessaires au développement i.e. qu'il ne doit pas omettre ou contenir des exigences inutiles ou superflues. Le référentiel des exigences doit aussi être cohérent, ce qui signifie qu'il ne doit pas contenir des exigences contradictoires. Sur le plan élémentaire, les exigences doivent présenter les critères de qualité suivants [Fiorèse et Meinadier 2012]:

- Unicité : l'exigence porte sur un seul sujet.

- Précision : l'exigence est bien écrite et claire.

- Non-ambiguïté : l'exigence doit avoir une seule interprétation.

- Pure prescription de résultat : l'exigence doit porter sur ce qui est attendu (le quoi ?), non sur la solution (le comment ?).

- Vérifiabilité : pour chaque exigence, une méthode de vérification est définie.

- Faisabilité : l'exigence peut être réalisée dans le contexte de l'état de l'art technologique et technique.

- Réalisme : l'exigence doit être satisfaite dans le contexte des contraintes et ainsi être réalisable.

Les exigences sont écrites généralement selon un dictionnaire (langage) compris par tous les intervenants. Ces langages sont connus sous le nom de "langages de spécification". Nous présentons, dans la section suivante, un aperçu des différents langages de spécification.

#### 1.2.1.1 Langages de spécification

Dans la littérature, plusieurs langages sont proposés pour la spécification des exigences. Les langages de spécification sont caractérisés par une syntaxe et une sémantique. Pour le langage naturel, comme le français par exemple, la syntaxe définit l'alphabet du langage et les règles grammaticales pour construire des phrases. La sémantique définit quant à elle, le sens des phrases construites. Les langages de spécification peuvent être classés, selon le caractère mathématique de leur sémantique, en trois classes : formels, semi-formels, ou naturels.

#### 1.2.1.1.1 Les langages formels

Les langages formels sont caractérisés par une syntaxe et une sémantique formelle [Bjørner et Havelund 2014]. Ces langages, basés généralement sur des notations mathématiques

précises, permettent la vérification automatique des exigences spécifiées. Mais, la manipulation des notations mathématiques requiert un savoir-faire et une forte expertise. C'est pour cela que l'utilisation des langages formels est modérée en industrie. Ces langages formels sont de deux types : langages orientés modèle et langages orientés propriété [Wing 1990].

Les langages orientés modèle permettent la spécification des différentes vues du système directement dans un modèle unique [Wing 1990], caractérisé par des types de données concrètes [Bjørner et Havelund 2014]. Parmi ces langages, on peut citer : les machines à état, les automates temporisés [Alur et Dill 1990], les réseaux de Petri [Petri 1966, Reisig 2013], Z <sup>1</sup> [Spivey et Abrial 1992], Alloy [Jackson 2002], VDM <sup>2</sup> [Jones 1986], Raise [George et al. 1992], la méthode B <sup>3</sup> [Abrial et Abrial 2005], B-évènementielle [Abrial 2010], ASM [Gurevich et al. 1995] et TLA+ <sup>4</sup> [Lamport 2002].

Les langages orientés propriété spécifient le système en un ensemble de propriétés souhaitées, dont le but est de définir un modèle qui satisfait l'ensemble des propriétés spécifiées. Ils sont caractérisés par des types de données abstraites [Bjørner et Havelund 2014]. Ces langages peuvent être axiomatiques ou algébriques [Wing 1990].

Dans les langages axiomatiques, les objets sont définis par des types. Les opérations, sur ces objets, sont écrites sous forme d'assertions en logique du premier ordre [Alagar et Periyasamy 2011]. Parmi eux, on peut citer : HOL<sup>5</sup> [Gordon et Melham 1993], PVS<sup>6</sup> [Owre et al. 1999], Coq [Bertot et Castéran 2013] et les logiques temporelles [Manna et Pnueli 2012] comme CTL<sup>7</sup> [Clarke et Emerson 1981].

Dans les langages algébriques, les objets et les processus sont définis en algèbre [Alagar et Periyasamy 2011]. Un objet est introduit comme un ensemble de définitions. Les opérations sur les objets sont définies par des équations. Les langages algébriques les plus connus sont : OBJ3 [Goguen et al. 1987], CafeOBJ [Diaconescu et Futatsugi 1998] et Maude [Clavel et al. 2002].

#### 1.2.1.1.2 Les langages semi-formels

Les langages semi-formels sont caractérisés par une syntaxe formelle bien précise. Cependant, leur sémantique présente des ambiguïtés d'interprétation dues à leur caractère *polysémique*. Un langage est dit polysémique s'il contient un symbole qui représente plus qu'un seul objet [Héon et al. 2010]. Par conséquent, les langages semi-formels sont plus expressifs que

- 1. Z:Zermelo

- 2. VDM: Vienna Development Method

- 3. B: Bourbaki

- 4. TLA: Temporal Logic of Actions

- 5. HOL: High Order Logic

- 6. PVS: Prototype Verification System

- 7. CTL: Computation Tree Logic

les langages formels. De plus, ils reposent souvent sur des notations graphiques ou textuelles qui les rendent d'un côté faciles à utiliser, mais d'un autre côté, difficiles à analyser. L'analyse de ces langages nécessite leurs transformations en langages formels. Parmi les langages semiformels, on peut citer : UML <sup>8</sup> [OMG 2015b], SysML <sup>9</sup> [OMG 2015a], OCL <sup>10</sup> [OMG 2014], SADT <sup>11</sup> [Dickover et al. 1977], etc.

UML est le langage semi-formel le plus utilisé pour la spécification des exigences. Il offre plusieurs diagrammes permettant de modéliser, à l'aide d'une syntaxe graphique, les différentes vues statiques ou dynamiques d'un système. Il est caractérisé par une syntaxe précise définie par un méta modèle et des contraintes OCL. Par contre, sa sémantique n'est pas formellement définie, malgré les efforts de l'OMG dans le projet F-UML [OMG 2016]. Bien qu'étant le langage le plus utilisé sur le plan académique et industriel, UML manque de précision dans sa sémantique. Ce qui le rend difficilement analysable par une machine.

Afin de vérifier automatiquement les langages semi-formels, plusieurs travaux proposent de les transformer en langages formels. Par exemple, différents diagrammes UML sont transformés en langages formels [Dong et al. 2001, Truong et Souquières 2004, Kim et Carrington 2000, Ng et Butler 2003].

#### 1.2.1.1.3 Les langages naturels

Les langages naturels, comme le français ou l'anglais, ont un pouvoir d'expression plus élevé que les langages semi-formels ou formels. Ils ont l'avantage aussi d'être compréhensibles par les différents intervenants du projet, une qualité très appréciée des industriels, qui continuent à les utiliser pour la spécification des exigences [Kudo et al. 2015]. En revanche, ces langages sont confus, ambigus et peuvent avoir plusieurs interprétations, ce qui les rend difficilement analysables par une machine et, par conséquent, ils peuvent être une source d'erreurs. Des erreurs, souvent introduites lors de la conception, résultent de mésinterprétations entre les différents concepteurs.

La norme SBVR <sup>12</sup> [OMG 2015c], du groupe OMG, propose un dictionnaire contrôlé pour la spécification des exigences. À la différence d'un langage purement naturel, ces langages contrôlés permettent aux exigences d'être automatiquement analysables.

Des travaux récents, comme ceux de Bajwa [2014], proposent de générer des notations formelles à partir des exigences spécifiées en Anglais. Dans leurs travaux, le langage naturel est parsé et normalisé selon la norme SBVR [OMG 2015c]. Une fois les spécifications normalisées, elles sont ensuite transformées en langages semi-formels comme OCL [Bajwa et al. 2010] ou formels comme Alloy [Bajwa et al. 2012]. D'autres travaux proposent d'utiliser les ontologies afin de transformer les contraintes, écrites en langage naturel, en un langage for-

- 8. UML: Unified Modeling Language

- 9. SysML: Systems Modeling Language

- 10. OCL : Object Constraint Language

- 11. SADT: Structured Analysis and Design Technique

- 12. SBVR: Semantic Business Vocabulary and Rules

mel [Sadoun et al. 2013].

Les exigences définies, lors de l'étape de spécification, doivent être vérifiées durant tout le cycle de développement d'un système. Nous présentons dans la section suivante la définition de la vérification ainsi que les différentes techniques de vérification.

#### 1.2.2 La vérification des exigences

Si le rôle de la spécification est la réécriture des besoins des clients d'une façon claire et précise. La vérification a pour rôle de vérifier que les exigences, résultantes de la spécification, sont respectées durant tout le cycle de développement. Son objectif est de détecter les erreurs introduites dans chaque étape de développement. La vérification répond à la question : "Faisons-nous le produit correctement?". Selon la norme ISO 9000, la vérification consiste à :

**Définition 1.4** [ISO 2000] La confirmation par des preuves tangibles que les exigences spécifiées ont été satisfaites.

A partir de cette définition, on peut constater que la vérification utilise des preuves tangibles, c.à.d. des méthodes, pour déterminer si les exigences sont satisfaites ou non. Nous présentons, dans la section suivante, un aperçu de la littérature des différentes méthodes de vérification.

#### 1.2.2.1 Les méthodes de vérification

Une méthode de vérification consiste à s'assurer que le système satisfait une exigence (propriété). Les méthodes de vérification les plus utilisées, dans la littérature, sont : le test, la simulation et les méthodes formelles.

#### 1.2.2.1.1 Le test

Le test permet de détecter les erreurs d'un système par rapport à un ensemble de scénarios définis antérieurement [Beizer 2003]. De ce fait, cette méthode est loin d'être exhaustive. Le test est pratiqué généralement après l'intégration du système, une fois que ce dernier est opérationnel. La correction des erreurs détectées à ce stade de développement (intégration), reste la plus coûteuse [Boehm et al. 1981]. Néanmoins, cette méthode de vérification reste la plus utilisée dans l'industrie [Bjørner et Havelund 2014], car elle peut être réalisée sur des systèmes de taille importante. Elle permet aussi de vérifier le système réel et pas seulement une abstraction de celui-ci, comme dans le cas de la simulation ou des méthodes formelles.

#### **1.2.2.1.2** La simulation

La simulation consiste à reproduire le comportement d'un système afin de vérifier son bon fonctionnement. Le comportement simulé est capturé sous forme de modèles abstraits qui sont, ensuite, exécutés sur des plateformes dédiées. La simulation consiste, alors, à faire des expérimentations sur des modèles abstraits [März et al. 2010]. En effet, l'analyste peut jouer des scénarios sur le simulateur afin de vérifier les performances du système.

Comme le test, la simulation peut être utilisée pour vérifier des systèmes de taille réelle, ce qui justifie son importante utilisation dans l'industrie. Mais, contrairement au test, la simulation peut être pratiquée dans des étapes en amont à l'implémentation et à l'intégration. Cela permet de détecter les erreurs avant que le système ne soit implémenté et ainsi réduire les coûts de correction. En revanche, la simulation souffre de plusieurs inconvénients comme le degré de réalisme ou granularité du simulateur. En effet, elle ne couvre pas la totalité du comportement du système, ce qui limite le nombre de scénarios vérifiables. De ce fait, la simulation n'est pas exhaustive.

#### 1.2.2.1.3 Les méthodes de vérification formelle

Les méthodes formelles, telle que définies par Bjørner et Havelund [2014], sont des techniques basées sur les mathématiques. Elles permettent de vérifier formellement des spécifications écrites en langages formels. Elles assurent que le système est correct en vérifiant un ensemble de propriétés. Elles donnent, ainsi, une cartographie des propriétés satisfaites et non satisfaites du système développé. Le caractère mathématique de ces méthodes, les rend plus précises et exhaustives comparées aux tests [Bennion et Habli 2014] et à la simulation. Ainsi, ces techniques sont de plus en plus utilisées pour la vérification des systèmes actuels. Mais leur adoption dans l'industrie souffre de plusieurs obstacles [Bjørner et Havelund 2014], malgré les résultats encourageants de certaines études [Bennion et Habli 2014]. Les méthodes formelles sont de deux types : le *Model-Checking* et le *Theorem-Proving*.

Le Model-Checking. [Schnoebelen et al. 1999, Baier et al. 2008] est une méthode formelle purement automatique, généralement supportée par un outil informatique "le Model-Checker". Elle consiste à vérifier automatiquement les propriétés souhaitées sur une spécification du système. Le système est généralement modélisé par des machines à états. Les propriétés à vérifier sont écrites dans une logique temporelle. Puis, sur la base des spécifications du système et des propriétés, le Model-Checker explore tout l'espace d'états. Il vérifie dans chaque état la satisfaction de la propriété désirée. Si la propriété est violée, le Model-Checker retourne un contre-exemple illustrant la trace de l'erreur, i.e, la succession d'états qui violent la propriété [Schnoebelen et al. 1999]. Cependant, pour les systèmes de taille importante, cette exploration exhaustive d'états peut dépasser la capacité des machines (ordinateurs), ce qui fait que la vérification échoue. Ce problème est connu sous le nom de l'explosion de l'espace des états.

Le *Model-Checking* est très utile pour la vérification des systèmes critiques complexes [Bennion et Habli 2014, Mesli-Kesraoui et al. 2016b;a]. En revanche, le problème de l'explosion de l'espace des états reste à ce jour, un vrai obstacle pour son adoption dans l'industrie. Afin d'évi-

ter cette explosion de l'espace des états, plusieurs techniques sont proposées dans la littérature comme : les BDD, les SAT, l'abstraction et la symétrie [Xin-feng et al. 2009].

UPPAAL [Larsen et al. 1997] <sup>13</sup> est un exemple de *Model-Checker*, utilisé pour la vérification formelle des systèmes temporisés. Le *Model-Checker* SPIN [Holzmann 2004] <sup>14</sup> est utilisé pour la vérification des systèmes concurrents. Roméo [Gardey et al. 2005] <sup>15</sup> est un *Model-Checker* pour la vérification des systèmes temps réel modélisés par des réseaux de Petri.