# Intégration dans un substrat PCB de composants à semi-conducteur grand gap pour le développement d'un convertisseur d'électronique de puissance à forte densité

Shuangfeng Zhang

## ► To cite this version:

Shuangfeng Zhang. Intégration dans un substrat PCB de composants à semi-conducteur grand gap pour le développement d'un convertisseur d'électronique de puissance à forte densité. Electronics. Université Paris Saclay (COmUE), 2018. English. NNT: 2018SACLS398. tel-02275807

# HAL Id: tel-02275807 https://theses.hal.science/tel-02275807v1

Submitted on 2 Sep 2019

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Wide Bandgap Semiconductor Components Integration in a PCB Substrate for the Development of a High Density Power Electronics Converter

Thèse de doctorat de l'Université Paris-Saclay

préparée à l'Université Paris-Sud

École doctorale n°575 : Electrical, Optical, Bio: Physics and Engineering (EOBE) Spécialité de doctorat: Génie électrique

Thèse présentée et soutenue à Gif-sur-Yvette de soutenance, le 30 Novembre 2018, par

# **Mme Shuangfeng ZHANG**

Composition du Jury :

| M. Cyril BUTTAY                                          |                    |

|----------------------------------------------------------|--------------------|

| Chargé de recherche CNRS, INSA de Lyon (Ampère)          | Rapporteur         |

| M. Yvan AVENAS                                           |                    |

| Maître de conférences, Grenoble INP (G2ELAB)             | Rapporteur         |

| M. Frédéric RICHARDEAU                                   |                    |

| Directeur de recherche CNRS, ENSEEIHT Toulouse (LAPLACE) | Président          |

| M. Zoubir KHATIR                                         |                    |

| Directeur de Recherche (IFSTTAR)                         | Examinateur        |

| M. Éric LABOURÉ                                          |                    |

| Professeur des universités, Université Paris-Sud (GeePs) | Directeur de thèse |

| M. Denis LABROUSSE                                       |                    |

| Maître de conférences, CNAM Paris (SATIE)                | Encadrant          |

| M. Stéphane LEFEBVRE                                     |                    |

| Professeur des universités, CNAM Paris (SATIE)           | Invité             |

ÉCOLE DOCTORALE Physique et ingénierie : électrons, photons, sciences du vivant (EOBE)

**Université Paris-Saclay** Espace Technologique / Immeuble Discovery Route de l'Orme aux Merisiers RD 128 / 91190 Saint-Aubin, France

**Titre :** Intégration dans un substrat PCB de composants à semi-conducteur Grand Gap pour le développement d'un convertisseur d'électronique de puissance à forte densité

**Mots clés :** Technologie de PCB, Gestion thermique, Modélisation 3D, Modélisation électrothermique

**Résumé :** Les nouveaux composants à semi-conducteur de type grand gap ont été développés pour des applications de conversion de puissance en raison de leurs hautes fréquences de commutation (de centaine kHz à quelques MHz) et pertes faibles. Afin de bien profiter ses avantages, la technologie des circuits imprimés (PCB) est intéressante pour une intégration à haute densité de puissance grâce à sa flexibilité et son faible coût. Cependant, à cause de la mauvaise conductivité thermique du matériau FR-4 utilisé pour le substrat PCB et la haute densité de puissance réalisée, il est primordial de trouver des solutions thermiques pour améliorer les performances thermique de la structure de PCB.

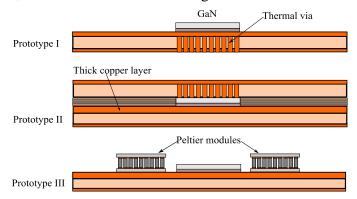

Dans cette thèse, trois solutions thermiques pour les structures de PCB ont été proposées, y compris des solutions avec des vias thermiques, de cuivre épais sur le substrat PCB ainsi que dispositifs refroidissement des de thermoélectrique (TEC). Nos études sont modélisation basées sur la électrothermique méthode et la d'éléments finis en 3D.

Tout d'abord, l'optimisation des paramètres des vias (diamètre, épaisseur de placage, surface formée par des vias, la distance entre des vias etc.) a été réalisée pour optimiser l'effet de refroidissement. Ensuite, on constate que les performances thermiques des strucutres de PCB peuvent être améliorées en utilisant cuivre épais sur le substrat de PCB. Cuivre épais augmente le flux thermique lateral dans la couche de cuivre. Les influnces de l'épaisseur de cuivre (35 à 500  $\mu$ m) ont été étudiées. Cette solution est facile à réaliser et peut être combinée à d'autres solutions de refroidissement.

Enfin, le dispositif thermoélectrique comme les modules Peltier est une technolgie de refroidissement local. Les influences des paramètres de Peltier (Propriétés du matériau thermoélectrique, nombre d'éléments Peltier, distance entre la source de chaleur et les dispositifs Peltier, etc.) ont été identifiées. Il est démonstré que des modules Peltier ont l'application potentielle pour le dévéloppement d'intégration de PCB attendu que son active contrôle des températures.

**Title :** Wide Bandgap Semiconductor Components Integration in a PCB Substrate for the Development of a High Density Power Electronics Converter

**Keywords :** PCB technology, Thermal management, 3D FE Modeling, Electrothermal modeling

Abstract : The emerging wide bandgap (WBG) semiconductor devices been developed for have power conversion applications instead of silicon devices due to higher switching frequencies (from few 100 kHz to several MHz) and lower on-state losses resulting in a better efficiency. In order to take full advantage of the WBG components, PCB technology is attractive for high power density integration thanks to its flexibility and low cost. However, due to thermal conductivity of poor the commonly used material Flame Retardant-4 (FR4), efficient thermal solutions are becoming a challenging issue in integrated power boards based on PCB substrates. So it is of the first importance to seek technological means in order to improve the thermal performances.

In this thesis, three main thermal management solutions for PCB structures have been investigated including thermal vias, thick copper thickness on the PCB substrate as well as thermoelectric cooling (TEC) devices. Our studies are based on the electrothermal modeling and 3D finite element (FE) methods.

Firstly, optimization of the thermal via parameters (via diameter, via plating thickness, via-cluster surface, via pattern, pitch distance between vias etc.) has been realized to improve their cooing performances. We presented and evaluated thermal performances of the PCB structures by analyzing the thermal resistance of the PCB substrate with different thermal vias.

Secondly, it is found that thermal performances of the PCB structures can be enhanced by using thick copper thickness on top of the PCB substrate, which increases the lateral heat flux along the copper layer. Influences of the copper thickness ( $35 \mu m$  to  $500 \mu m$ ) has been discussed. This solution is easy to realize and can be combined with other cooling solutions.

Thirdly, thermoelectric cooler like Peltier device is a solid-state cooling technology that can meet the local requirements. Influences of cooling (Thermoelectric Peltier parameters material properties, number of Peltier elements, distance between the heating source and the Peltier devices etc.) have been identified. All these analyses demonstrate the potential application of Peltier devices placed beside the heating source for PCB structures, which is a benefit for developing the embedding technology in such structures.

# **REMERCIEMENTS**

Sur cette page dédiée aux remerciements je souhaite m'adresser à toutes les personnes qui m'ont aidé à agrandir dans l'univers des sciences et des technologies durant ces trois années de thèse.

Je tiens tout d'abord à remercier l'ensemble des membres de mon jury de soutenance de thèse : **M. Frédéric RICHARDEAU** pour m'avoir fait l'honneur de présider ma soutenance ; **M. Cyril BUTTAY** et **M. Yvan AVENAS** d'avoir accepté d'être rapporteurs de mon travail de thèse et de me donner les conseils sur mes travaux ; **M. Zoubir KHATIR** d'avoir accepté de faire partie de ce jury en tant qu'examinateur.

J'adresse ma profonde reconnaissance et mes sincères remerciements à mes encadrants de thèse : **M. Éric LABOURÉ** et **M. Denis LABROUSSE**, d'une part pour leurs compétences scientifiques et d'autre part pour l'aide qu'ils m'ont apporté durant mes travaux de recherche et dans ma vie personnelle. Je m'oublierai jamais nos réunions au cours desquelles des propositions, des solutions et des idées ruisselaient telle une source inépuisable née par leur passion pour la recherche. C'est vraiment une grande joie de travailler avec eux. Merci !

Un grand merci à **M. Stéphane LEFEBVRE**, pour ses conseils, son aide, et son expérience sur la technologie PCB qu'il m'a bien voulu me faire partager.

Je voudrais adresser mes remerciements à toute le personnel du laboratoire GeePs-avec une mention spéciale pour mes amis : **Chengjiang, Qi, Man, Xiaotao, Zuqi, Xiang,** pour nos longues discussions, les pauses café, les repas au CESFO et les bons moments que nous avons passé ensemble.

Je souhaite aussi remercier toutes les personnes du laboratoire SATIE qui m'ont apporté des conseils ou de l'aide au cours de ma thèse-permanents, doctorants. Merci à mes collègues de SATIE : Yoann, Chabakata, Veronika, Alex, Salim, Adrien, Thomas, pour les discussions, pour leurs savoirs, conseils et aides qui m'ont fait également progresser.

Je voudrais remercier tous mes amis en France, qui m'ont accompagné pendant ces 6 ans de vie à l'étranger. Malgré mon éloignement de mon pays natal, grâce à vous je me suis entie à la maison.

Enfin, un très grand merci à toute ma famille qui m'a toujours encouragé et sans qui je ne serai pas arrivé à ce stade.

# **RÉSUMÉ EN FRANÇAIS**

# I- Contexte de l'étude

Au cours des dernières années, la technologie de l'électronique de puissance a connu une évolution rapide grâce au concept « plus électrique ». Récemment, de nombreuses applications de l'électronique de puissance se sont développées dans les environnements industriels, commerciaux, résidentiels, de transport, utilitaires, aérospatiaux et militaires en raison de la réduction des coûts, de la taille et de l'amélioration des performances [1].

Comme les caractéristiques des composants de puissance à base de Silicium ont atteint ou sont très proches leurs limites physiques, les composants à grand gap en Nitrure de Gallium (GaN) ou Carbure Silicium (SiC) ont récemment émergé. Ils permettent d'atteindre de plus hautes fréquences de commutation tout en offrant une plus faible résistance à l'état passant. La capacité de ces composants grand gap en matière de montée en fréquence est liée à leurs vitesse de commutation ce qui implique que des fronts d'onde *dv/dt* et *di/dt* extrêmement élevés sont générés. Les connexions de ces composants avec le reste du circuit et donc leur packaging sont donc des points cruciaux pour permettre de bénéficier pleinement des performances en vitesse de commutation. L'augmentation des performances électriques permet par ailleurs de réduire les dimensions de la partie active du composant grand gap pour un cahier des charges donné. Les contraintes thermiques découlant de la réduction de la surface de ces composants devient alors un problème important, d'autant plus si l'on souhaite travailler à plus haute température, ce que sont censés pouvoir permettre de tels composants.

L'augmentation de la densité de puissance et les avancées des semi-conducteurs à grand gap nécessitent des améliorations en matière d'intégration, de technologie d'assemblage ainsi que des solutions de gestion thermique. En effet, la plupart des technologies d'assemblage commerciales sont élaborées pour les composants à base de Silicium pour lesquels, la température de fonctionnement est en particulier plus faible. Or, dans de nombreuses applications, par exemple dans les domaines de l'aérospatiale et de l'aéronautique, une capacité de fonctionnement fiable dans des environnements difficiles (de  $-55 \ C \ a 250 \ C$ ) est fortement souhaitée. Les composants à grand gap offrent l'avantage de pouvoir fonctionner à plus haute température. Cependant, les technologies d'assemblage, les composants passifs, les composants périphériques disponibles, les matériaux de brasure, les considérations de fiabilité et les coûts limitent actuellement les températures de jonction à environ 175  $\ C$ , même si les semi-conducteurs à grand gap peuvent fonctionner principalement à températures de jonction beaucoup plus élevées [7-9].

Afin d'atténuer les effets induits par une plus grande rapidité de commutation et une densité de puissance plus importante, il est nécessaire de proposer et développer des solutions d'assemblage avancées avec des systèmes de refroidissement efficaces de manière à tirer pleinement avantage des composants à grand gap.

Parmi les technologies matures utilisées dans le domaine de l'électronique de puissance, la technologie des circuits imprimés (Printed Circuit Board : PCB) répond aux contraintes techniques pour les petites et moyennes puissances (quelques centaines de Watts jusqu'à quelques kW). La technologie DBC (Direct Bonded Copper) est pour sa part utilisée dans le cas de densité de puissance et de puissances élevées [10]. Entre autres avantages, la technologie PCB permet de réaliser l'intégration 3D des composants de puissance en supprimant l'utilisation des fils de bonding. Toutefois le substrat de PCB en matériau de FR- 4 a une mauvaise conductivité thermique (<1.5 W/mK), ce qui rend difficile la gestion des flux thermiques et la maîtrise de la température des composants.

Cette thèse est donc consacrée au développement de solutions de refroidissement destinées à des assemblages à base de PCB. Trois méthodes de refroidissement ont été étudiées :

- La première solution est basée sur le concept de vias thermiques créés dans le substrat PCB. L'objectif est pour cette partie de définir des règles de design permettant de choisir les paramètres des vias pour atteindre les performances thermiques souhaitées ;

- La seconde solution consiste à augmenter l'épaisseur de la couche de cuivre sur le dessus de substrat de PCB. Cette solution permet d'augmenter la diffusion latérale de la chaleur et ainsi d'augmenter la surface de dissipation thermique ;

- La troisième solution propose et analyse des solutions de refroidissement basées sur des technologies thermoélectriques (TEC).

Le mémoire de thèse est divisé en quatre parties, hors conclusion et perspectives, présentant successivement :

- Dans le premier chapitre, un bref aperçu du développement des systèmes électroniques de puissance et du contexte général de ce travail est présenté afin d'introduire les concepts de base de la gestion thermique, concepts utilisés tout au long de la thèse. Nous discuterons ensuite de l'état de l'art des techniques d'assemblage actuels utilisés en électronique de puissance et des différentes solutions de gestion des aspects thermiques. Ce chapitre sera également consacré à la comparaison des certaines méthodes de modélisation basées sur différents logiciels issues de la littérature ;

- Le deuxième chapitre présentera les aspects instrumentaux utilisés dans le banc d'essai destiné à la mesure des flux de puissance et des températures. Le banc d'essai est décrit ainsi que le processus d'étalonnage de certains dispositifs tels que les capteurs de température à résistance (RTD). Les principes de réalisation des échantillons sont également présentés ;

- Le troisième chapitre couvre deux méthodes de refroidissement : La solution de refroidissement par vias thermiques et par augmentation de l'épaisseur de cuivre du substrat PCB. Différentes méthodes de modélisation : analyse électrothermique en 1D et méthode d'éléments finis en 3D ont été utilisées pour analyser l'impact sur refroidissement des différents paramètres des vias, notamment le diamètre, le nombre des vias, l'épaisseur du cuivre, la distance entre deux vias, etc. ;

- Le quatrième chapitre, décrit et analyse une solution de refroidissement basée sur des modules thermoélectriques (TEC) utilisant l'effet Peltier. Dans ce chapitre, des modèles sont proposés et utilisés pour dimensionner et optimiser cette solution en fonction des propriétés thermiques recherchées.

# II- Les principaux résultats

♦ Optimisation des vias thermiques

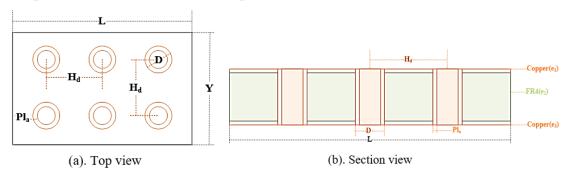

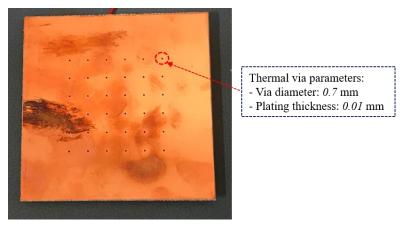

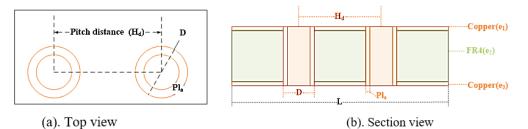

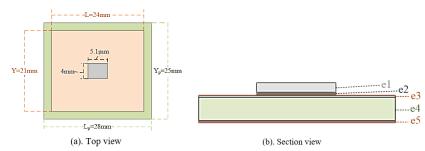

Figure 1: Vue de dessus (a) et vue en coupe (b) des vias thermiques créés dans un substrat PCB

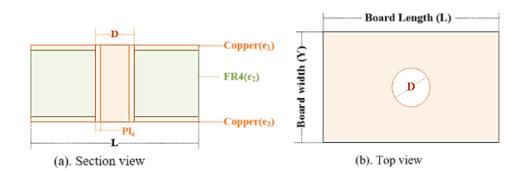

D'après l'hypothèse de conduction thermique en 1D, les paramètres des vias thermiques sont exprimés sous la forme de grandeurs adimensionnelles dans (1) et (2). Ces paramètres sont utilisés pour définir la résistance thermique d'une structure PCB avec vias thermiques.

$$R_{oa} = \frac{1}{1 + \pi \cdot R_{o1} \cdot R_{o2}^2 \cdot \left(\sigma_r \cdot \frac{R_{o3}}{R_{o2}} - \frac{1}{4}\right)}$$

(1)

$$R_{oa} = \frac{R_{a_N}}{R_{board}}, R_{o1} = \frac{N \cdot H_d^2}{S_1}, R_{o2} = \frac{D}{H_d}, R_{o3} = \frac{Pl_a}{H_d}$$

(2)

Avec

$R_{oa}$ : le rapport de la résistance thermique du substrat de PCB avec et sans N vias thermiques ;

$R_{a_N}$  (W/mK) : la résistance thermique du substrat de PCB avec N vias thermiques ;

*R*<sub>board</sub> (W/mK) : la résistance thermique du substrat de PCB sans vias thermiques ;

$R_{o1}$ : le rapport de la surface formée par des vias thermiques à la surface disponible ;

$R_{o2}$ : le rapport du diamètre du via thermique D (mm) à la distance entre deux vias  $H_d$  (mm);

$R_{o3}$ : le rapport de l'épaisseur de cuivre dans le via  $Pl_a$  (mm) à la distance entre deux vias  $H_d$  (mm);

$S_I$ : la surface normale à la direction de transfert de chaleur  $L \times Y$  (mm×mm);

$\sigma_r$ : le rapport de la conductivité thermique entre les matériaux : cuivre et FR-4 ;

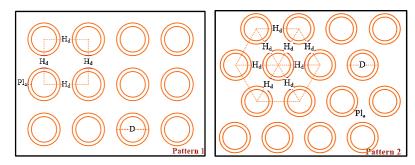

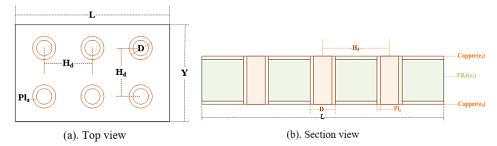

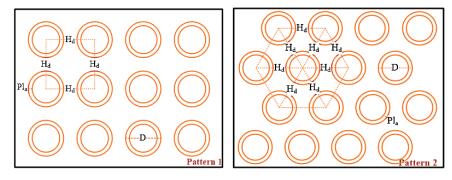

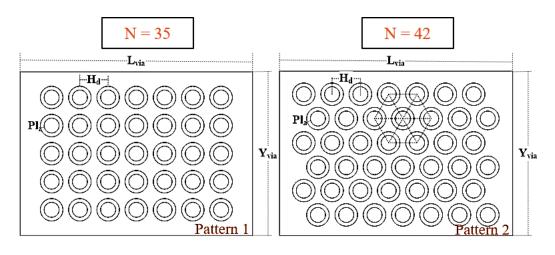

On a proposé deux motifs différents formés par des vias thermiques (Voir Figure 2). La différence entre les deux motifs réside dans le nombre des vias qu'on peut créer pour la même surface disponible.

Figure 2: Vue de dessus des deux motifs (Pattern\_1 et Pattern\_2) utilisés pour créer des vias thermiques dans un substrat PCB

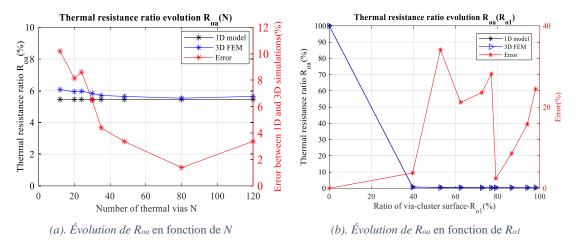

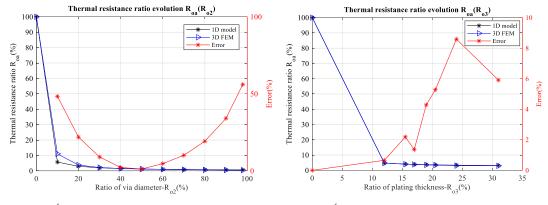

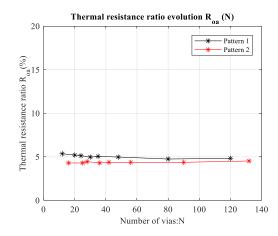

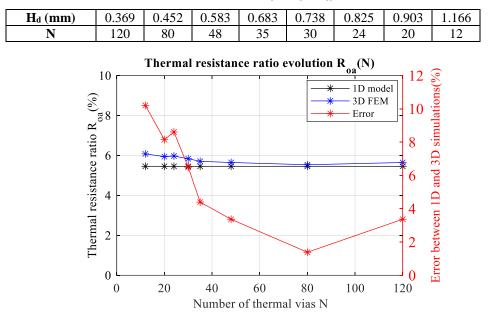

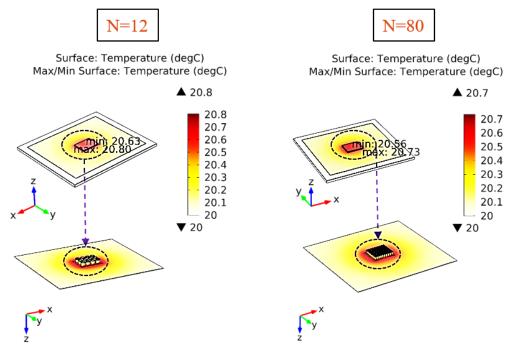

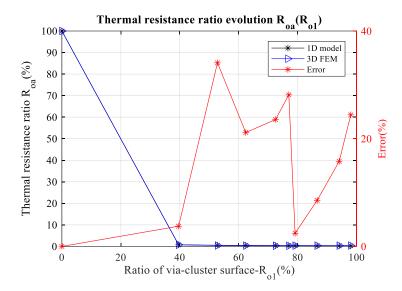

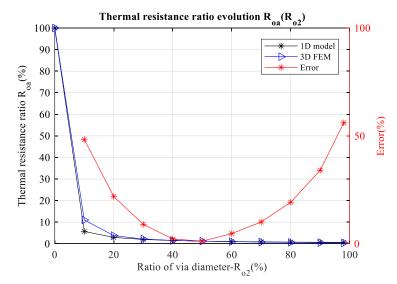

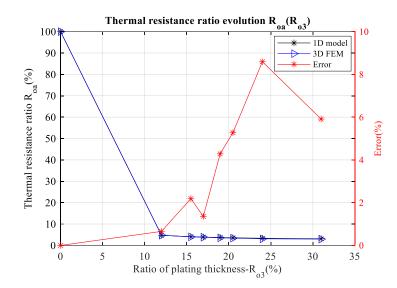

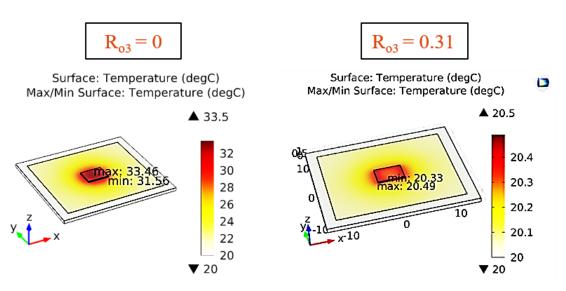

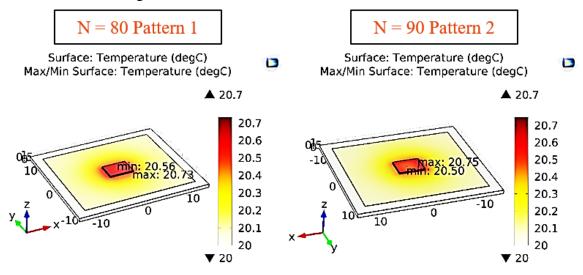

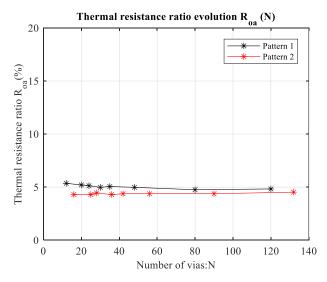

Les effets sur la résistance thermique du substrat des différents paramètres précédents (le nombre des vias N, le rapport de surface des vias  $R_{o1}$ , le rapport de diamètre du via  $R_{o2}$ , le rapport d'épaisseur de placage du via  $R_{o3}$  et le motif formé par des vias) sont résumées dans Figure 3, Figure 4 et Figure 5 :

Figure 3: Évolution du rapport de résistance thermique du substrat PCB avec des vias thermiques  $R_{oa}(N)$ ,  $R_{oa}(R_{o1})$

(a). Évolution de  $R_{oa}$  en fonction de N

(b). Évolution de Roa en fonction de Rol

Figure 4: Évolution du rapport de résistance thermique du substrat PCB avec des vias thermiques Roa (Ro2), Roa(Ro3)

Figure 5: Évolution de rapport de résistance thermique du substrat PCB avec des vias thermiques  $R_{oa}$  (N) pour deux motifs différents

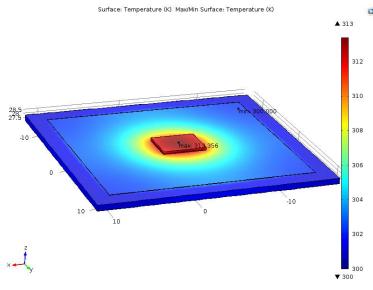

Les prédéterminations du comportement thermique de cette solution sont réalisées par simulation sur un modèle 1D en utilisant le logiciel Matlab Simulink. Les simulations 3D sont réalisées avec le logiciel COMSOL Multiphysics.

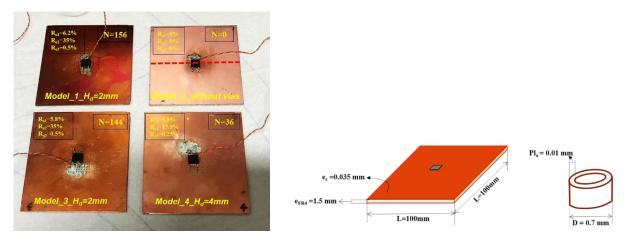

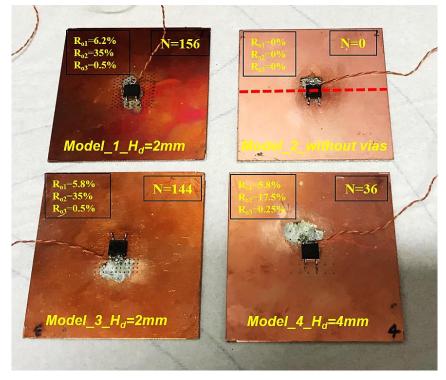

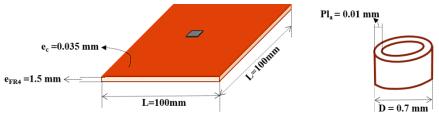

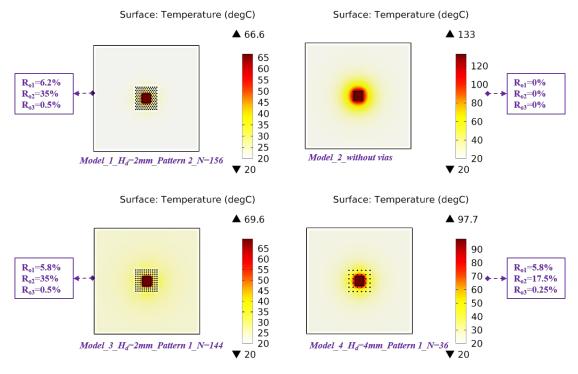

Figure 6: Les différents échantillons avec vias thermiques créés sur un substrat PCB. L'élément chauffant est une résistance brasée. les vias thermiques sont placés au-dessous de la résistance. Un thermocouple est soudé sur la semelle de la résistance pour mesurer sa température au plus près de l'élément chauffant

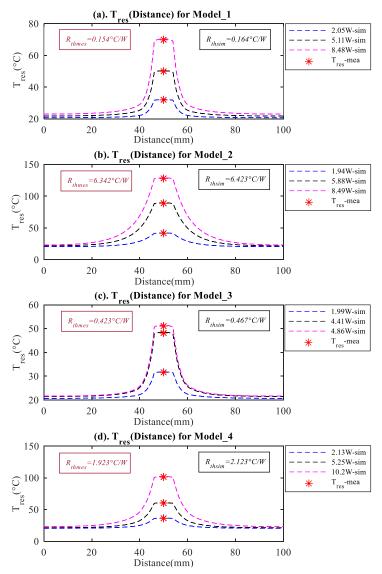

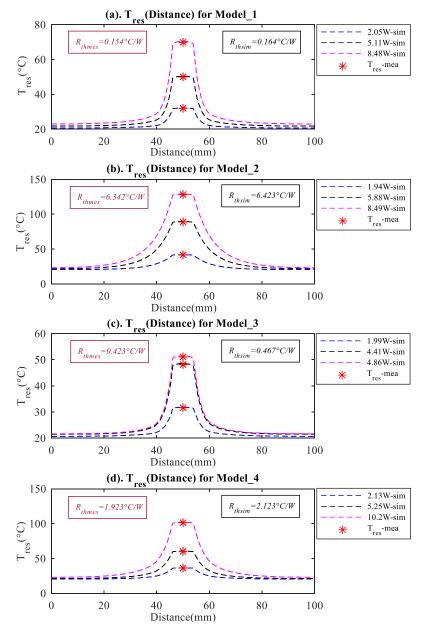

Figure 7: Comparaisons des résultats de simulation et des résultats d'expérimentation. Les températures au milieu de la surface de PCB sont obtenues par simulation thermique 3D. La température de l'élément chauffant est mesurée par thermocouple.

L'étude conduite a permis de relier la valeur de la résistance thermique du substrat aux valeurs des différents paramètres  $R_{o1}$ ,  $R_{o2}$ ,  $R_{o3}$ . De façon qualitative, la résistance thermique

diminue lorsque la valeur de ces paramètres augmente. Il est également démontré que le motif *Pattern\_2* donne de meilleurs performances à surface de PCB occupée identique.

Les résultats des températures obtenues par simulations et expérimentalement sont donnés à la Figure 6 et la Figure 7. Un bon accord entre les expérimentations et les simulations nous a permis de valider les modèles proposés et ainsi de valider ces modèles comme outil de conception de vias thermiques.

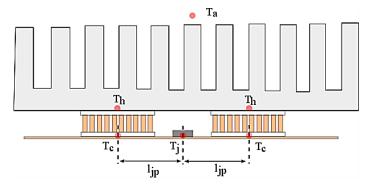

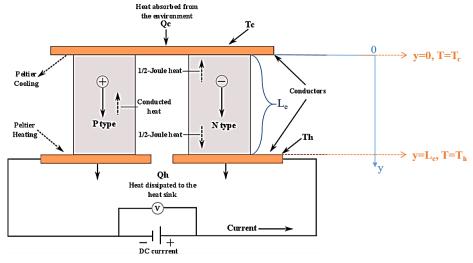

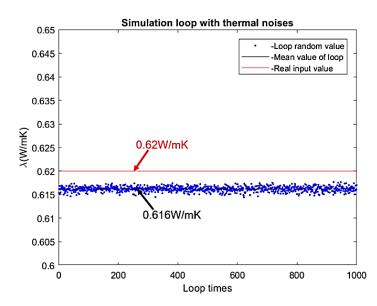

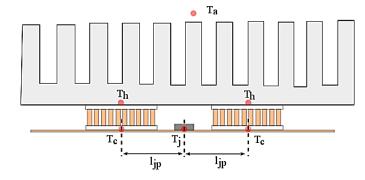

#### ♦ Refroidissement par des modules de Peltier

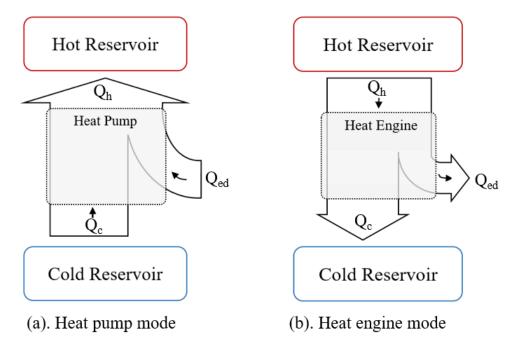

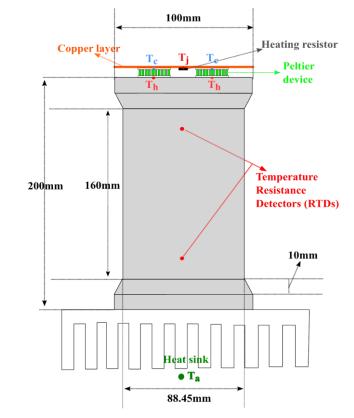

L'agencement du mode de refroidissement par modules thermoélectriques d'un assemblage sur PCB est proposé à la Figure 8. Cet agencement permet de drainer le flux de chaleur généré par l'élément chauffant en face avant via la couche supérieure de cuivre du PCB. Les modules de Peltier jouent le rôle de pompe à chaleur et absorbent le flux de chaleur de côté froid  $Q_c(W)$  pour l'évacuer côté chaud  $Q_h(W)$ .

Figure 8: Agencement du refroidissement d'un assemblage PCB par modules Peltier montés en face avant du PCB

L'un des avantages de cette solution réside dans le fait qu'elle permet de contrôler la température de jonction  $T_j(K)$  dynamiquement en fonction de la puissance à dissiper  $P_{heat}(W)$ . L'ajustement est réalisé par l'intermédiaire du courant électrique parcourant les modules Peltier et donc par modulation de la puissance électrique consommée. La puissance électrique nécessaire pour réaliser ce pompage d'énergie thermique est un point clé de ce mode de refroidissement. Le design de la solution doit être optimisé pour minimiser cette puissance.

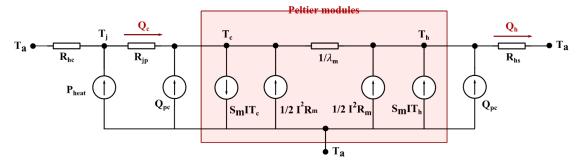

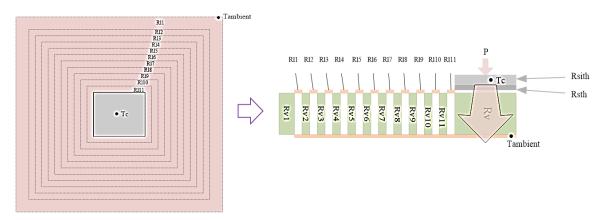

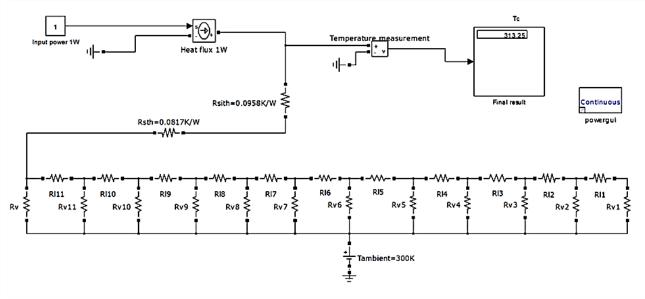

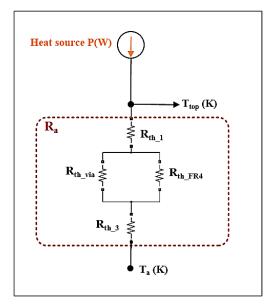

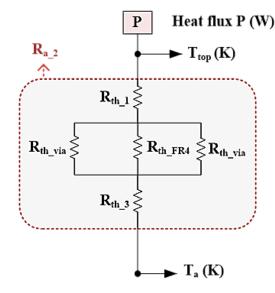

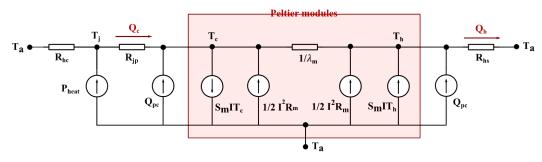

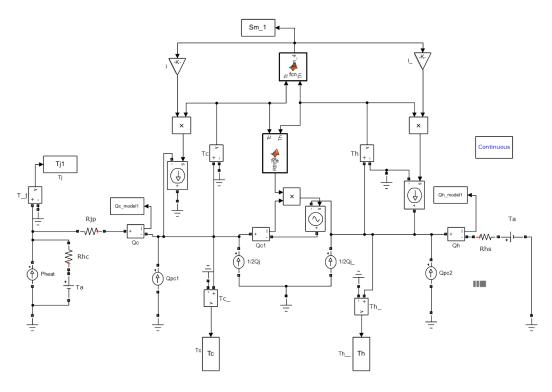

En considérant que le flux thermique est 1D dans l'essentiel de la structure, un modèle thermique simplifié a été proposé. Ce modèle intègre un modèle analytique des modules Peltier [161-166]. Le schéma électrique correspondant à ce modèle est donné ci-dessous :

Figure 9: Modèle électrothermique de la structure de refroidissement proposée.  $T_a(K)$  est la température ambiante ;  $T_j$ (K) représente la température de jonction ;  $R_{hc}(K/W)$  est la résistance thermique correspondant à l'effet de convection entre la source de chaleur et la périphérie ;  $R_{jp}(K/W)$  est la résistance thermique latérale entre les modules Peltier et la source de chaleur ;  $R_{hs}(K/W)$  est la résistance thermique du radiateur ;  $Q_{pc}(W)$  représente des pertes supplémentaires dans la structure. Les autres composants ( $Q_c$ ,  $S_m$ ,  $\lambda_m$  et  $R_m$ ,  $Q_h$ ) sont des paramètres du modèle des modules de Peltier.

Le modèle 1D proposé permet de prédire les performances thermiques de la structure de refroidissement de faire un bilan de puissance au niveau des modules Peltier. Ce modèle

léger permet de tester différentes options et d'évaluer le coefficient de performance  $(COP=Q_c/Q_{ed})$  de la structure étudiée.

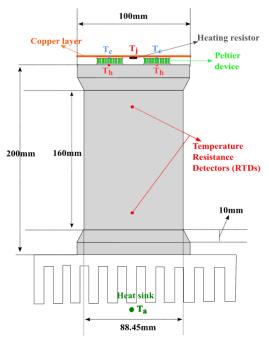

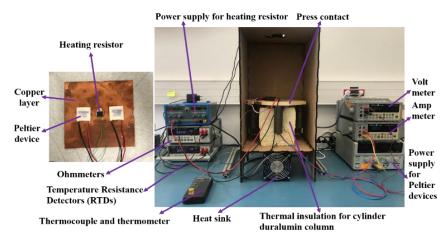

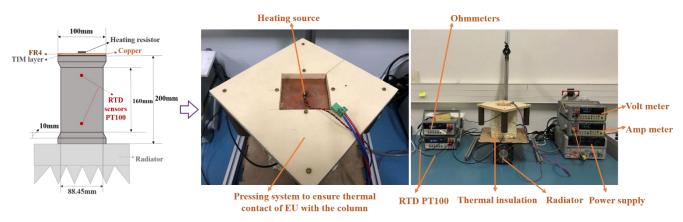

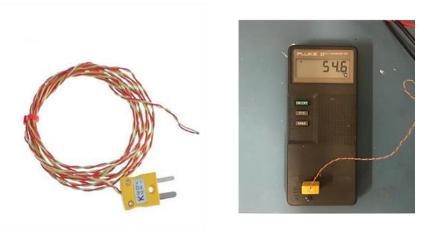

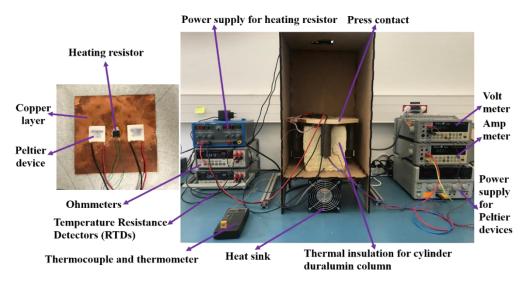

Le modèle 1D a été validé par des expérimentations en utilisant le banc d'essai montré à la Figure 10 et la Figure 11. La méthode calorimétrique mise en œuvre permet de mesurer le flux de chaleur total évacué par l'une des faces des modules Peltier  $Q_h(W)$ . Les modules Peltier CP39236 [188], CP30238 [189] et CP 60133 [190] testés dans ce travail expérimental sont distribués par CUI Inc.

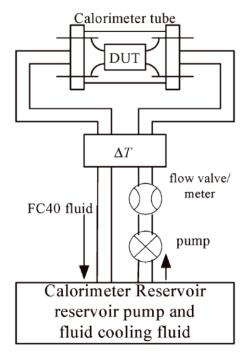

Figure 10: Schématique de principe du banc d'essai permettant la mesure de flux de chaleur par une méthode calorimétrique

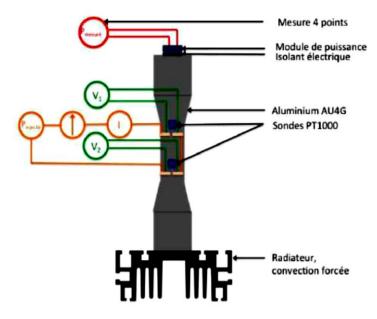

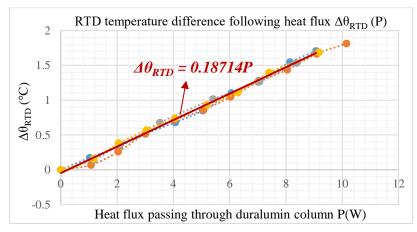

Dans notre travail expérimental, nous sommes assurés que la majorité des pertes de puissance générées par l'élément chauffant et par le module Peltier passe par la colonne de mesure. La température de l'élément chauffant est mesurée par un thermocouple et  $Q_h$  est obtenue via la mesure de la différence de température entre deux résistances Platine (La résistance thermique de la colonne en duralumin est de 0.187 K/W a été calibrée au préalable). Différents courants (variant de 0 à 2.5A pour les produits CP39236 et CP30238, de 0 à 4A pour le produit CP60133) sont injectés dans les modules Peltier afin d'évaluer les performances de refroidissement.

Figure 11: Banc d'essai permettant de mesurer le flux de chaleur par une méthode calorimétrique

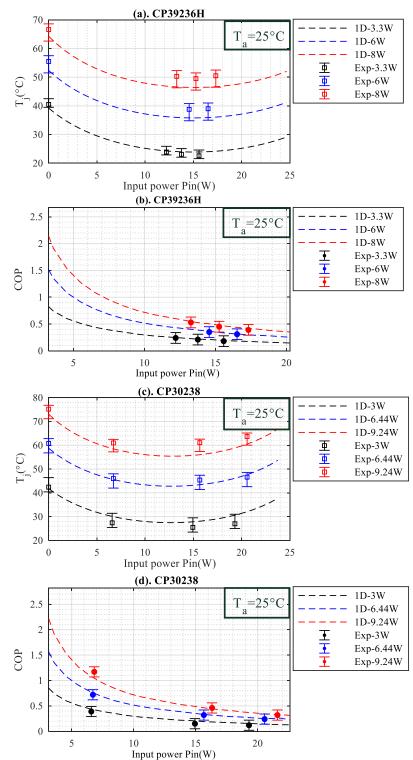

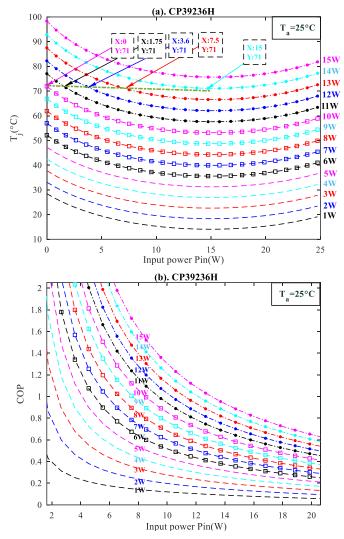

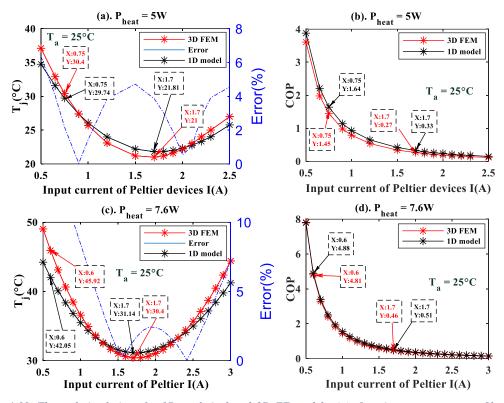

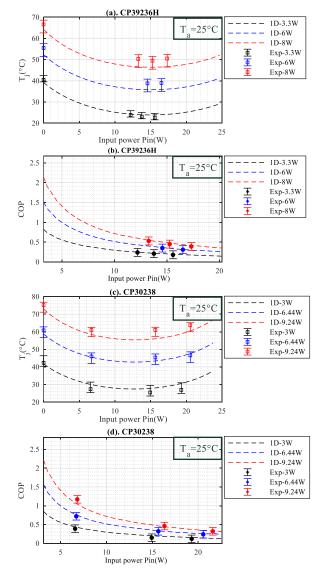

Tout d'abord, le modèle 1D proposé a été validé par comparaisons des résultats de simulation avec les résultats expérimentaux (Voit Figure 12).

Figure 12: Comparaisons des résultats des simulations avec les résultats expérimentations. (a). Évolution de la température de jonction  $T_j$  ( $P_{in}$ ) en utilisant des modules CP39236H; (b). Évolution du COP des modules Peltier CP39236H; (c). Évolution de la température de jonction  $T_j$  ( $P_{in}$ ) en utilisant des modules CP30238; (d). Évolution du COP des modules CP30238. La température ambiante  $T_a$  est de 25 °C.

Le modèle 1D est ensuite utilisé pour prédire les performances thermiques de la structure d'assemblage proposée. Comme montré dans Figure 13, l'effet de refroidissement des modules Peltier est lié à la puissance électrique  $P_{in}$  injectée et à la puissance thermique à

drainer. On peut donc montrer qu'il est possible de contrôler la température de jonction de l'élément chauffant et mettre en œuvre une stratégie permettant de maintenir la température de cet élément à une valeur fixe sur une certaine plage de puissance injectée. Il est également possible d'opter pour une stratégie limitant la température maximum et réduisant la consommation électriques des modules Peltier lorsque les flux de chaleur à dissiper sont faibles.

*Figure 13: Résultats prédits à partir du modèle 1D en utilisant les modules Peltier CP39236H. (a). Profil de la température de jonction*  $T_j(P_{in})$ ; *(b). Profil du COP (P<sub>in</sub>). La température ambiante*  $T_a$  *est de 25* °C.

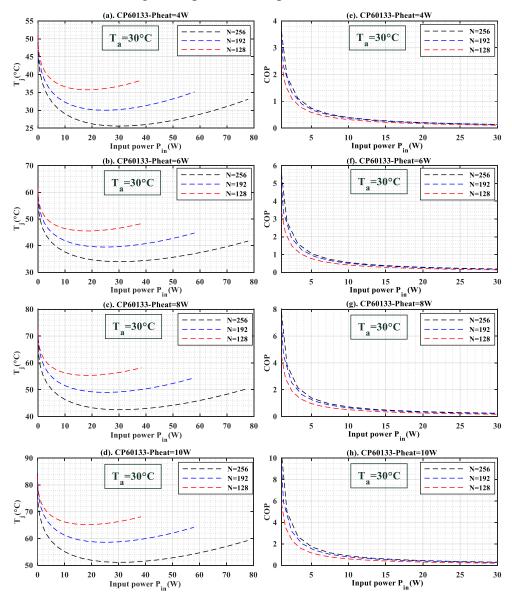

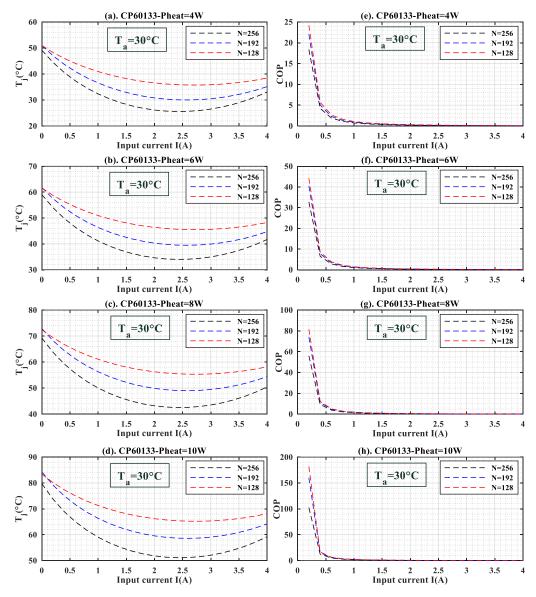

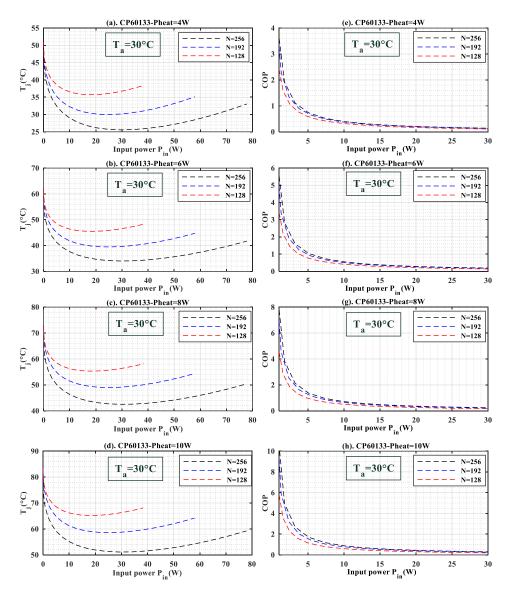

L'influence du nombre d'éléments des modules Peltier *N* a également été étudié comme montré dans la figure 14.

On constate que la puissance thermique soutirée par les modules augmente avec le nombre d'éléments. Pour illustrer ceci, la diminution maximale de la température  $\Delta T_{jmax}$  (°C) obtenue pour différents nombres d'éléments est donnée dans le tableau ci-dessous :

| Tableau I: La diminution maximale de la température $\Delta T_{jmax}$ (°C) des trois scénarios de refroi |

|----------------------------------------------------------------------------------------------------------|

|----------------------------------------------------------------------------------------------------------|

| Ν   | $P_{heat} = 4W$ | P <sub>heat</sub> = 6W | P <sub>heat</sub> = 8W | P <sub>heat</sub> = 10W |

|-----|-----------------|------------------------|------------------------|-------------------------|

| 128 | 15.2            | 16.1                   | 17.1                   | 18.3                    |

| 192 | 21              | 22.3                   | 23.9                   | 25.7                    |

| 256 | 23.6            | 25.1                   | 26.7                   | 28.7                    |

De plus, le COP est amélioré lorsqu'on augmente le nombre d'éléments des modules Peltier pour le même effet de refroidissement. Par exemple, pour une température de

l'élément chauffant souhaitée  $T_j$  de 55 °C, les valeurs des coefficients COPs sont indiquées dans le tableau ci-dessous :

| Pheat | СОР              |           |          |  |

|-------|------------------|-----------|----------|--|

| (W)   | N=128            | N=192     | N=256    |  |

| 4     | Infinity (Pin=0) | Infinity  | Infinity |  |

| 6     | 5.5              | 16.21     | Infinity |  |

| 8     | 0.26             | 1.27      | 3.84     |  |

| 10    | Inability        | Inability | 0.88     |  |

Tableau 2: Valeurs des coefficients COPs des trois scénarios pour maintenir  $T_j$  à 55 °C

Ce résultat démontre que l'efficacité du système de refroidissement s'accroit lorsque le nombre d'éléments Peltier augmente pour une température de l'élément chauffé donnée.

Figure 14: Résultats estimés par le modèle électrothermique pour les structures avec différents N. (a). Profil  $T_j(P_{in})$ pour évacuer 4 W de flux de chaleur ; (b). Profil  $T_j(P_{in})$  pour évacuer 6 W de flux de chaleur ; (c). Profil  $T_j(P_{in})$  pour évacuer 8 W de flux de chaleur ; (d). Profil  $T_j(P_{in})$  pour évacuer 10 W de flux de chaleur ; (e). Profil d'efficacité COP ( $P_{in}$ ) pour évacuer 4 W de flux de chaleur ; (f). Profil d'efficacité COP ( $P_{in}$ ) pour évacuer 6 W de flux de chaleur ; (g). Profil d'efficacité COP ( $P_{in}$ ) pour évacuer 8 W de flux de chaleur ; (h). Profil d'efficacité COP ( $P_{in}$ ) pour évacuer 10 W de flux de chaleur . La température ambient  $T_a$  est de 30 °C.

# **TABLE OF CONTENTS**

| Remerciem    | ents                                                      | I            |

|--------------|-----------------------------------------------------------|--------------|

| Résumé en    | français                                                  | Π            |

| List of figu | resXI                                                     | $\mathbf{V}$ |

| List of tabl | esXVI                                                     | Π            |

| General In   | troduction                                                | .1           |

| CHAPTER      | 1. State of The Art                                       | .3           |

| 1.1. Iı      | ntroduction                                               | .3           |

| 1.2. P       | ower Converters                                           | .3           |

| 1.2.1.       | Semiconductor Components                                  | .3           |

| 1.2.2.       | Multilevel Converters                                     | .6           |

| 1.3. P       | ower Packaging                                            | . 8          |

| 1.3.1.       | Introduction                                              | . 8          |

| 1.3.2.       | 2D Packaging with Direct Bonded Circuit (DBC) Technology  | . 8          |

| 1.3.3.       | 3D Packaging with Printed Circuit Board (PCB) Technology  | .9           |

| 1.3.4.       | Conclusion                                                | 11           |

| 1.4. T       | hermal Analysis of Power Electronics Systems              |              |

| 1.4.1.       | Introduction                                              | 11           |

| 1.4.2.       | Thermal Measurement Methods                               | 15           |

| 1.4.3.       | Thermal Management Solutions                              | 25           |

| 1.5. S       | ummary                                                    | 34           |

| CHAPTER      | 2. Thermal Instrumentations                               | 36           |

| 2.1. In      | ntroduction                                               | 36           |

| 2.2. T       | est Bench                                                 | 36           |

| 2.2.1.       | Establishment                                             | 36           |

| 2.2.2.       | RTD Sensor (PT 100) Calibration                           | 36           |

| 2.2.3.       | Thermal Conductivity of Duralumin $\lambda_{dura}$ (W/mK) | 38           |

| 2.2.4.       | Temperature Measurement Equipments                        | 39           |

| 2.2.5.       | Applied Softwares                                         | 40           |

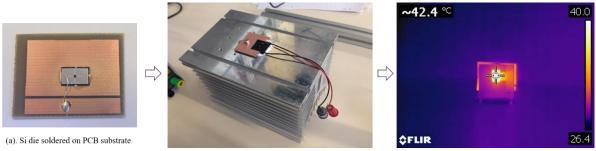

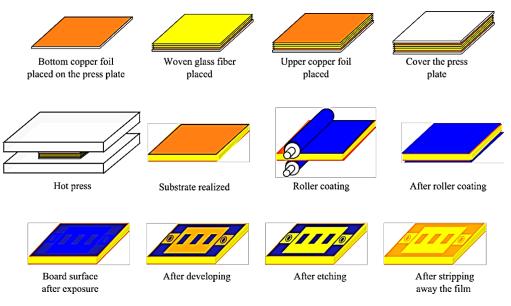

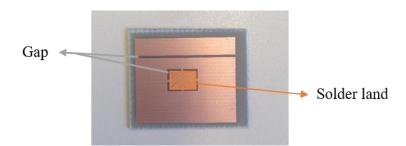

| 2.3. C       | Chip Attachment on The PCB Substrate                      | 43           |

| 2.3.1.       | Preparation of PCB Substrate                              | 43           |

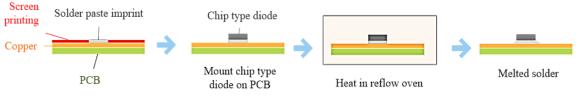

| 2.3.2.       | Chip Soldering                                            | 44           |

| 2.4. T       | hrough-Hole Electroplating                                | 45           |

| 2.5. S       | ummary                                                    | 45           |

| CHAPTER      | <b>3.</b> Optimization of thermal vias                    | 47           |

| 3.1. In      | ntroduction                                               | 47           |

| 3.2. A       | Analytical Analysis                                       | 47           |

| 3.2.1.   | PCB Substrate with One Individual Thermal Via        | 47  |

|----------|------------------------------------------------------|-----|

| 3.2.2.   | PCB Substrate with Two Thermal Vias                  | 48  |

| 3.2.3.   | PCB Substrate with Multiple Vias                     | 49  |

| 3.3.     | 3D FEM Analysis                                      | 51  |

| 3.3.1.   | Number of Thermal Vias N                             | 52  |

| 3.3.2.   | Via-Cluster Surface Ratio Rol                        | 53  |

| 3.3.3.   | Via Diameter Ratio R <sub>02</sub>                   | 54  |

| 3.3.4.   | Via Plating Thickness Ratio R <sub>03</sub>          | 54  |

| 3.3.5.   | Via Pattern                                          | 55  |

| 3.3.6.   | Copper Thickness on The PCB Substrate                | 57  |

| 3.4.     | Experimental Results and Discussions                 | 59  |

| 3.5.     | Conception of The Inverse Thermal Model              | 63  |

| 3.5.1.   | Introduction                                         | 63  |

| 3.5.2.   |                                                      |     |

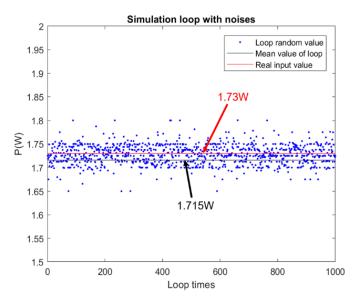

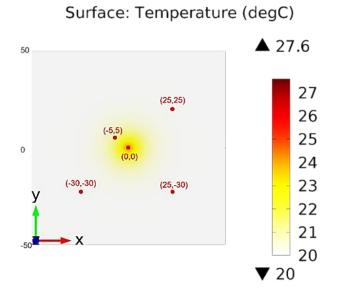

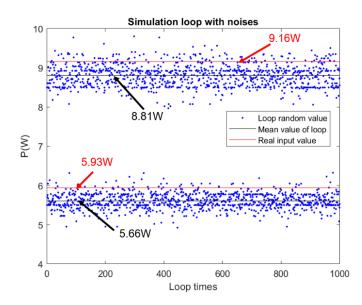

| 3.5.3.   | Dissipated Power Prediction                          | 65  |

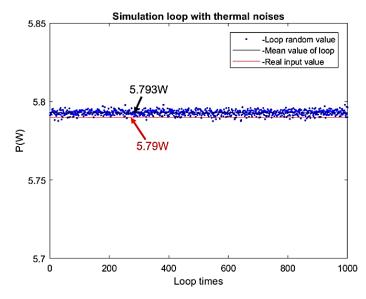

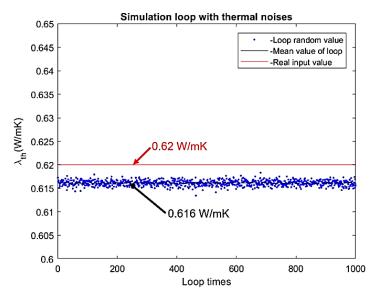

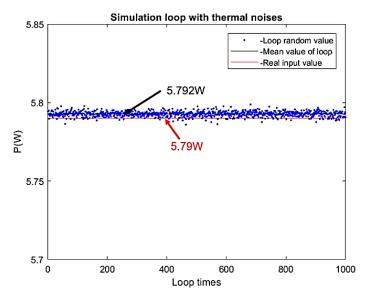

| 3.5.4.   | Dissipated Power and Thermal Conductivity Prediction | 67  |

| 3.6.     | Summary                                              | 69  |

| СНАРТЕ   | R 4. Thermoelectric Cooling                          | 71  |

|          | Introduction                                         |     |

| 4.2.     | 3D FEM Analysis                                      | 72  |

| 4.2.1.   | or r                                                 |     |

| 4.2.2.   |                                                      |     |

| 4.2.3.   |                                                      |     |

| 4.3.     | 1D Electro-Thermal Modeling                          | 80  |

| 4.3.1.   | 5 5                                                  |     |

| 4.3.2.   |                                                      |     |

|          | Experimental Validation                              |     |

| 4.4.1.   |                                                      |     |

| 4.4.2.   | Results and Discussions                              |     |

| 4.4.3.   |                                                      |     |

|          | Summary                                              |     |

|          | ons and Perspectives                                 |     |

|          | 25                                                   |     |

|          |                                                      |     |

|          |                                                      |     |

|          |                                                      |     |

| Annex D. |                                                      | 116 |

# **LIST OF FIGURES**

| Fig.1. Power density and costs evolution [2]1                                                                                                              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig.1-1. Summary of Si, SiC and GaN relevant material properties [14]                                                                                      |

| Fig.1-3. (a) Three-level NPC featuring IGCTs; (b) Three-level FC featuring MV-IGBTs; (c)                                                                   |

| Five-level CHB featuring LV-IGBTs [11]                                                                                                                     |

| Fig.1-4. Switching process of an IGBT with several commutation cycles [30]7                                                                                |

| Fig.1-5. Schematic view of a power module and example of 2D packaging inverter arm [10]                                                                    |

| Fig.1-6. Thin 60-W offline converter with PCB integrated transformer and capacitors [40]                                                                   |

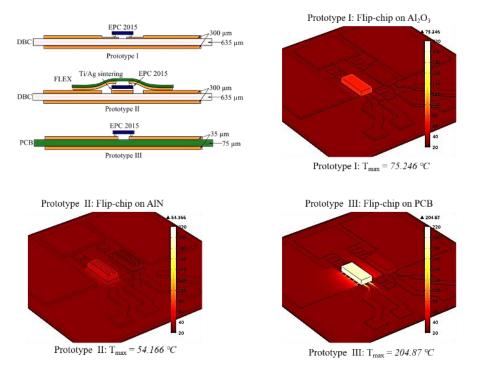

| Fig.1-7. Thermal simulation results for different GaN prototypes [10] 11                                                                                   |

| Fig.1-8. Bounded spatial thermal region                                                                                                                    |

| Fig.1-9. The Foster (top) and Cauer (bottom) canonic forms of thermal networks                                                                             |

| Fig.1-10. Calculation results for Si structures by Cauer modeling [48]                                                                                     |

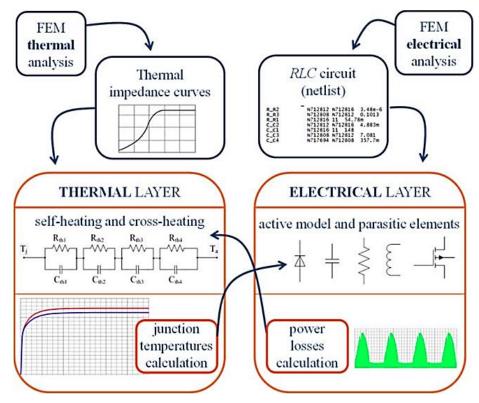

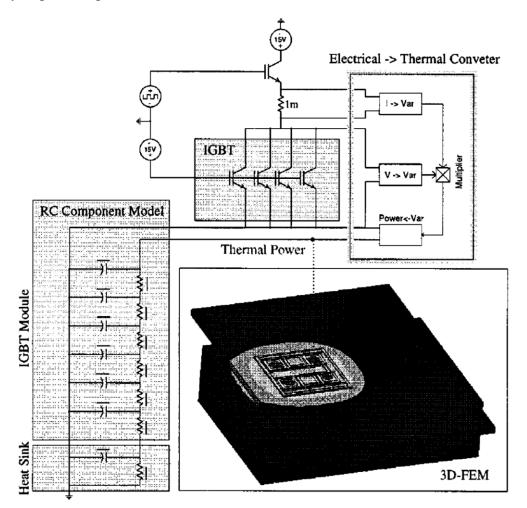

| Fig.1-11. Layered approach adopted for the electro-thermal modeling of integrated power electronics modules [49]                                           |

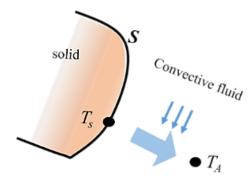

| Fig.1-12. Heat convection                                                                                                                                  |

| Fig.1-13. Heat radiation                                                                                                                                   |

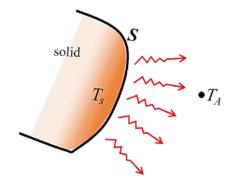

| Fig.1-14. Schematic of high power IGBT module modeled in ANSYS Icepak for FEM analysis [65]                                                                |

| Fig.1-15. Electro-thermal model in Saber [71]                                                                                                              |

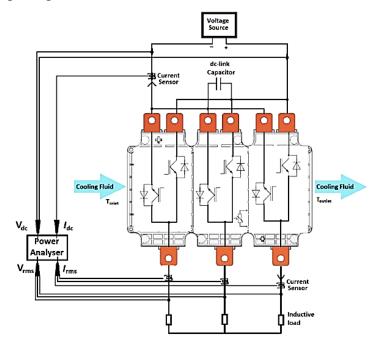

| Fig.1-16. Schematic for measurement of power losses with the electrical method [84]20                                                                      |

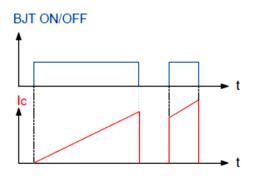

| Fig.1-17. Double pulse waveform [86]                                                                                                                       |

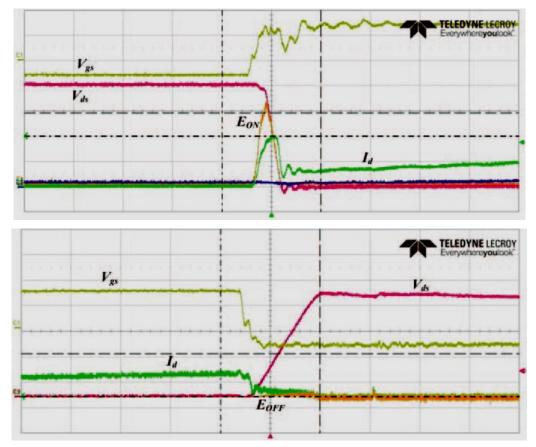

| Fig.1-18. SiC MOSFET switch on and switch off transient [88]21                                                                                             |

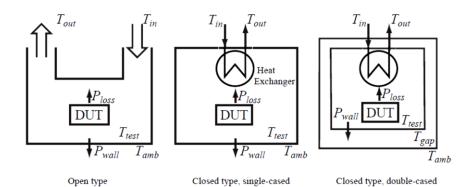

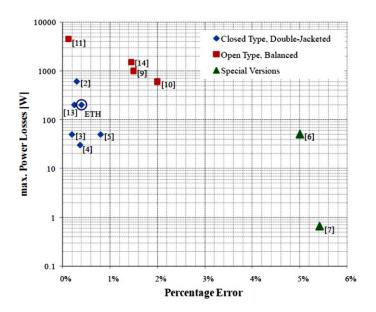

| Fig.1-19. Schematic open, single-cased closed and double cased closed type [107]23                                                                         |

| Fig.1-20. Overview of different implemented calorimeters and their reached accuracy [107]                                                                  |

|                                                                                                                                                            |

| Fig.1-21. Block diagram of calorimeter [95]                                                                                                                |

| Fig.1-22. Schematic of calorimetric method with heat-flux sensors PT100 [115]24                                                                            |

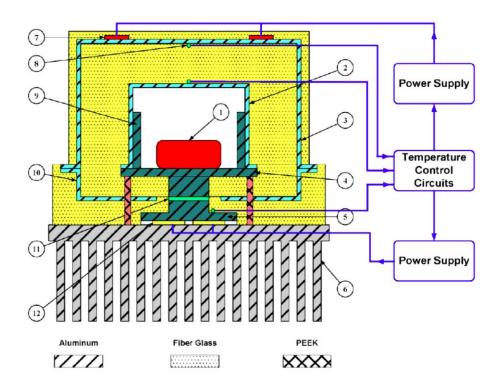

| Fig.1-23. Schematic of proposed apparatus.1: DUT; 2: Inner Al cover; 3: Outer Al cover; 4:                                                                 |

| Al base plate I; 5: Al base plate II; 6: Heat sink; 7: Heater; 8: Thermocouple; 9: Fins; 10: Insulated material; 11: Heat flux sensor; 12: TE module.[110] |

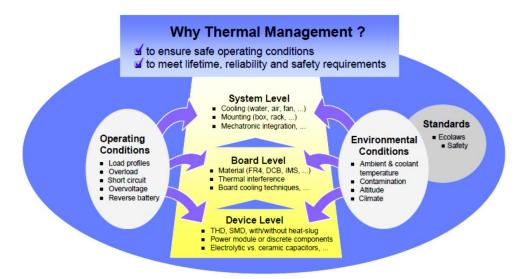

| Fig.1-24. Thermal management - a continuous process during system engineering [117]. 26                                                                    |

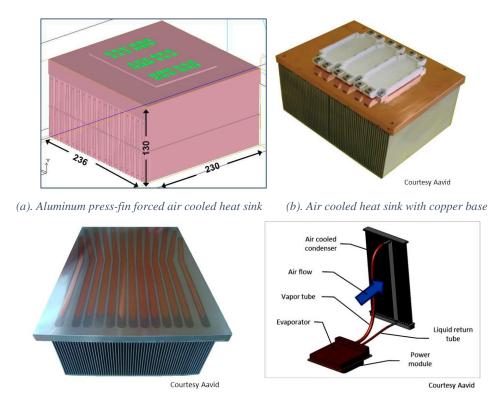

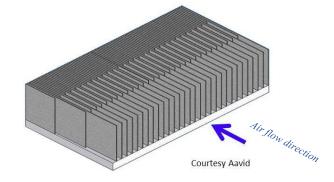

| Fig.1-25. Different air cooling systems design with heat sinks [119]27                                                                                     |

| Fig.1-26. Different liquid cooling solutions [122]                                                                                                         |

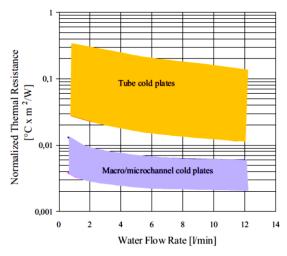

| Fig.1-27. Thermal resistance of commercial available cold plates as a function of water flow [124]                                                         |

| Fig.1-28. Section view of main heat transfer path for a 2 layer PCB with thermal vias [131]                                                                |

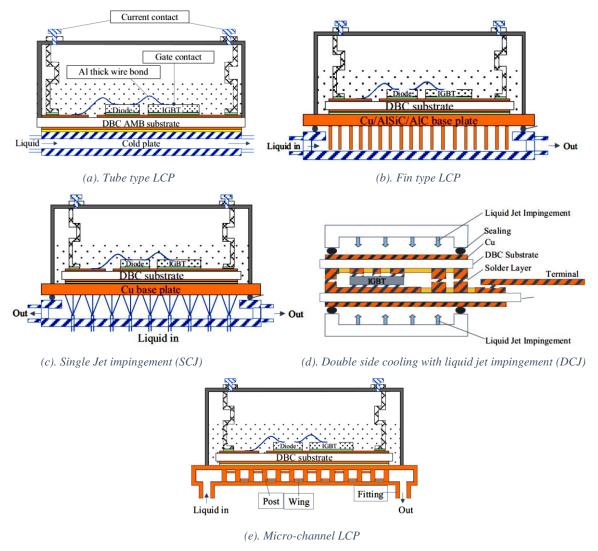

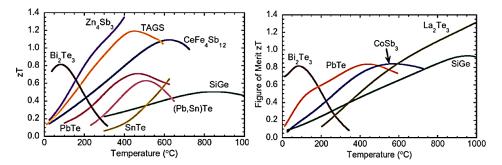

| Fig.1-29. Curves of ZT versus temperature for different materials [144]                                                                                    |

| Fig.1-30. Schematic of thermoelectric module operation in cooling mode                                                                                     |

| Fig.1-31. Pyrolytic graphite sheet from Panasonic PGS product datasheet [155]                                                                              |

| Fig.1-32. Hybrid solid- and liquid-cooling designs for IGBT isothermalization [116] 33                                                                     |

| Fig.1-33. Embedded thermal solutions for PCB structures using PGS and heat pipe                                                                            |

| techniques [126]                                                                                                                                           |

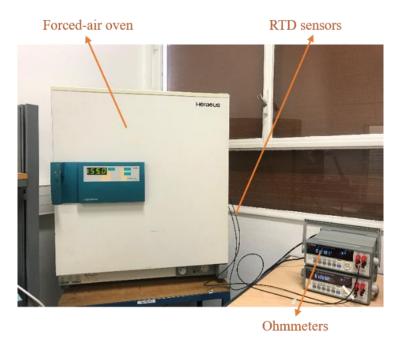

| Fig.2-1. Power loss measurement test bench                                                                           |        |

|----------------------------------------------------------------------------------------------------------------------|--------|

| Fig.2-2. RTD sensor PT 100 (Online source: flukecal.com)                                                             | . 37   |

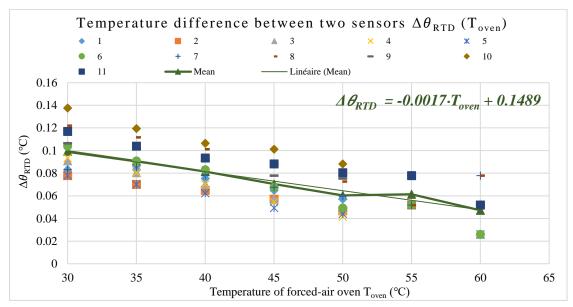

| Fig.2-3. Test bench for calibrating RTD sensors                                                                      | . 37   |

| Fig.2-4. Temperature differences between two RTDs following temperature of forced                                    | -air   |

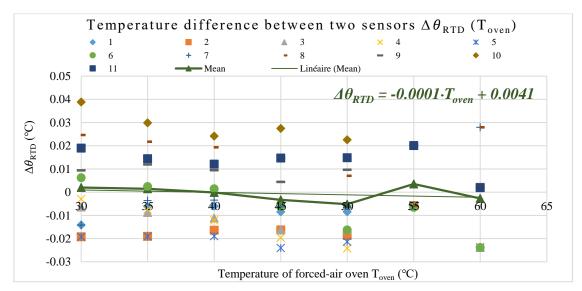

| oven                                                                                                                 | . 38   |

| Fig.2-5. Temperature differences between two RTDs after calibration                                                  | . 38   |

| Fig.2-6. Measured relationship between input power and temperature difference between                                |        |

| two RTDs                                                                                                             |        |

| Fig.2-7. Thermography camera FLIR T450sc [157]                                                                       | . 39   |

| Fig.2-8. Thermal imaging of a simple PCB structure                                                                   |        |

| Fig.2-9. K&T type thermocouple (ANSI MC96.1) [159] and thermometer                                                   |        |

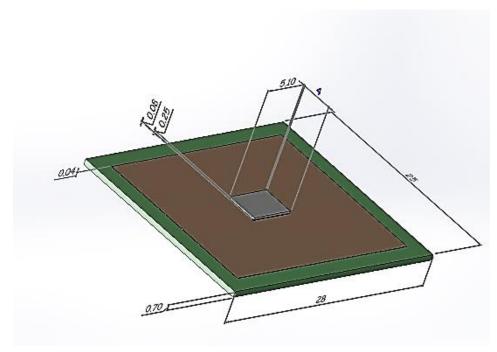

| Fig.2-10. 3D model of the PCB structure with soldered Si chip (dimensions in mm)                                     |        |

| Fig.2-11. Top and section view of lumped parameter model for the PCB structure                                       |        |

| Fig.2-12. Steady-state thermal network for the PCB structure                                                         |        |

| Fig.2-13. 3D Thermal simulation of the PCB structure                                                                 |        |

| Fig.2-14. Fabrication process of PCB [160]                                                                           |        |

| Fig.2-15. Prepared PCB substrate for chip soldering                                                                  | <br>44 |

| Fig.2-16. Chip soldering process                                                                                     |        |

| Fig.2-17. Electroplated vias in the standard PCB substrate                                                           |        |

| rig.2-17. Electropiated vias in the standard r CD substrate                                                          | . 45   |

| Fig.3-1. Typical PCB structure with a single thermal via                                                             | 17     |

|                                                                                                                      |        |

| Fig.3-2. Analytical model for one single via PCB structure                                                           |        |

| Fig.3-3. Top and Section view of the PCB substrate with two thermal vias                                             |        |

| Fig.3-4. Analytical thermal model for PCB structure with two thermal vias                                            |        |

| Fig.3-5. Top and section view of the PCB substrates with multiple thermal vias in patter                             |        |

| Fig.3-6. Two typical via-cluster patterns                                                                            |        |

| Fig.3-7. Top and Section view of the studied PCB assembly                                                            |        |

|                                                                                                                      |        |

| Fig.3-8. Evolution of thermal resistance ratio $R_{oa}$ following the number of vias                                 |        |

| Fig.3-9. 3D FEM simulations with different number of thermal vias but the same ratios $R_{01}$ , $R_{02}$ , $R_{03}$ |        |

|                                                                                                                      |        |

| Fig.3-10. Evolution of thermal resistance ratio R <sub>oa</sub> following the ratio of via-cluster surf              |        |

| $R_{ol}$                                                                                                             |        |

| Fig.3-11. Evolution of thermal resistance ratio $R_{oa}$ following the ratio of via diameter                         |        |

| Eig 2 12 Evolution of the mediator of matin D following the ratio of via alating thisks                              | . 54   |

| Fig.3-12. Evolution of thermal resistance ratio $R_{oa}$ following the ratio of via plating thickn                   |        |

| $R_{03}$                                                                                                             |        |

| Fig.3-13. 3D FEM simulations with different ratio of via plating thickness                                           |        |

| Fig.3-14. 3D FEM simulations with different via patterns                                                             |        |

| Fig.3-15. Arrangement of thermal vias in two patterns with the same available via-clus                               |        |

| surface                                                                                                              |        |

| Fig.3-16. Evolution of the average thermal resistance ratio in two patterns                                          |        |

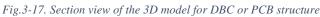

| Fig.3-17. Section view of the 3D model for DBC or PCB structure                                                      |        |

| Fig.3-18. Thermal resistance evolution following the copper thickness                                                |        |

| Fig.3-19. 3D thermal simulation results for PCB structures having 10kV breakdown volt                                | -      |

|                                                                                                                      |        |

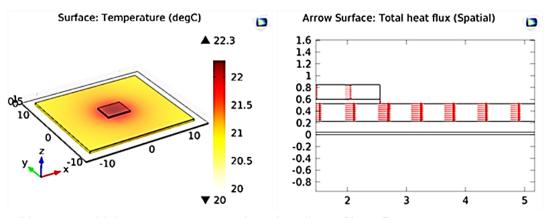

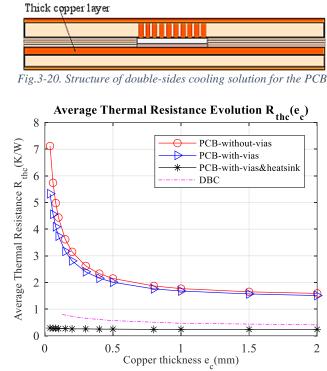

| Fig.3-20. Structure of double-sides cooling solution for the PCB                                                     |        |

| Fig.3-21. Thermal resistance evolution following the copper thickness for the sa                                     |        |

| breakdown voltage 10kV                                                                                               | . 59   |

| Fig.3-22. Four PCB structures with different via patterns                                                   | 59 |

|-------------------------------------------------------------------------------------------------------------|----|

| Fig.3-23. PCB dimensions and via parameters                                                                 |    |

| Fig.3-24. 3D FEM simulations for PCB structures with different via parameters                               | 60 |

| Fig.3-25. Temperature measurements of the heating source and comparisons with 3D FE                         | M  |

| simulations                                                                                                 |    |

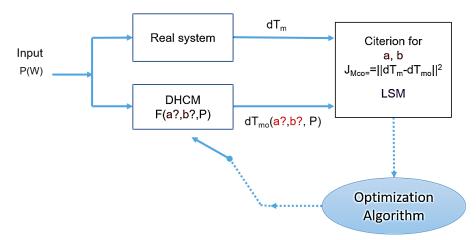

| Fig.3-26. PCB structure with embedded GaN chip                                                              | 64 |

| Fig.3-27. Parameters estimation step for DHCM                                                               | 64 |

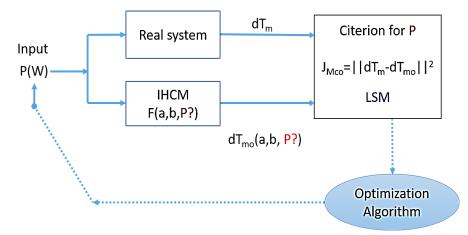

| Fig.3-28. Input power estimation step for IHCM                                                              | 64 |

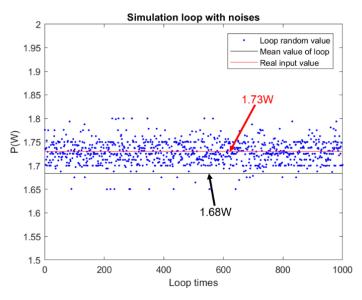

| Fig.3-29. Power prediction with 5 temperature sensors (Annex A)                                             |    |

| Fig.3-30. Power prediction with 10 temperature sensors (Annex B)                                            |    |

| Fig.3-31. Temperature measurements on the top surface of PCB structure by 3D FE                             |    |

| simulations                                                                                                 |    |

| Fig.3-32. Power predictions in 2 embedded GaN dies with 5 temperature sensors (Annex                        |    |

|                                                                                                             |    |

| Fig.3-33. Power prediction for IHCM with two unknown system parameters (Annex D).                           |    |

| Fig.3-34. Prediction of thermal conductivity of the PCB substrate for IHCM with tw                          |    |

| unknown system parameters (Annex D)                                                                         |    |

| Fig.3-35. Power prediction with less temperature sensors (Annex D)                                          |    |

| Fig.3-36. Thermal conductivity prediction with less temperature sensors (Annex D)                           | 69 |

|                                                                                                             |    |

| Fig.4-1. PCB structure with Peltier modules                                                                 |    |

| Fig.4-2. One element of a TEC device                                                                        |    |

| Fig.4-3. Working mode of the Peltier device                                                                 |    |

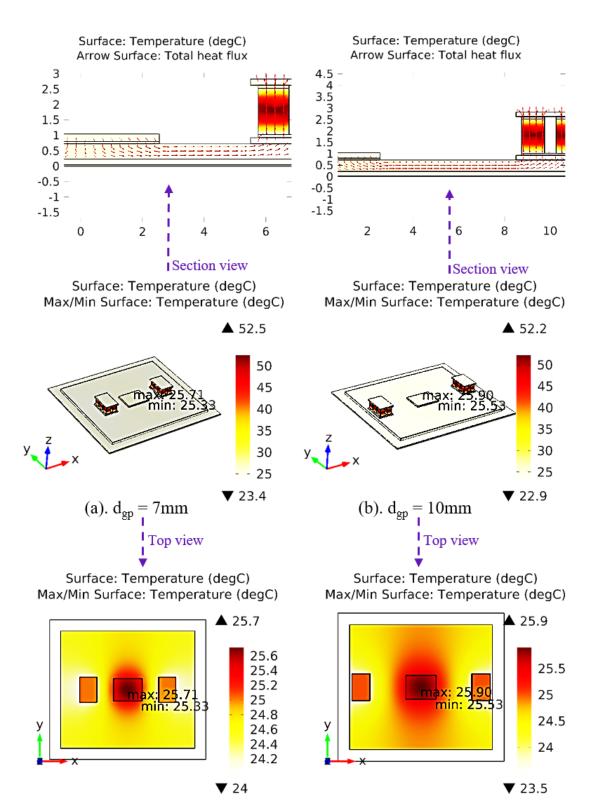

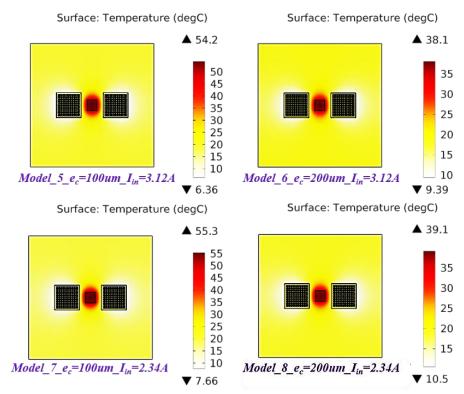

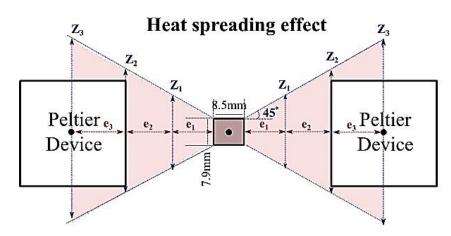

| Fig.4-4. Examples of 3D FEM simulations for PCB structures with different distant                           |    |

| between the chip and the Peltier devices. A heat dissipation of 1 W in the chip, an equivale                |    |

| convection heat-transfer coefficient of 15 W/( $m^2K$ ) from all external surfaces (except t                |    |

| bottom layer and the top TEC plate) to the ambient, a copper thickness $e_c$ of 500µm on t                  |    |

| top of the PCB substrate and an optimum input electric power of 0.4 V in the Peltier modul                  |    |

| are applied. The ambient temperature is at 25 $^\circ C$                                                    |    |

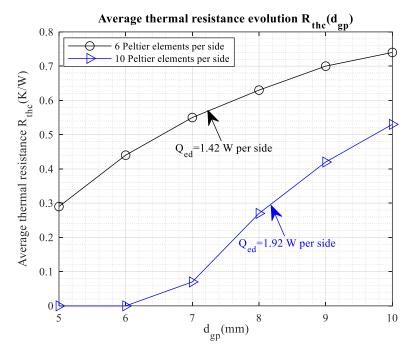

| Fig.4-5. Thermal resistance evolution following the distance $d_{gp}$ . A heat dissipation of 1             |    |

| in the chip, an equivalent convection heat-transfer coefficient of 15 $W/(m^2K)$ from                       |    |

| external surfaces (except the bottom layer and the top TEC plate) to the ambient and a copp                 | -  |

| thickness $e_c$ of 500µm on the top of the PCB substrate are applied. The ambient temperatu                 |    |

| is at 25 °C                                                                                                 |    |

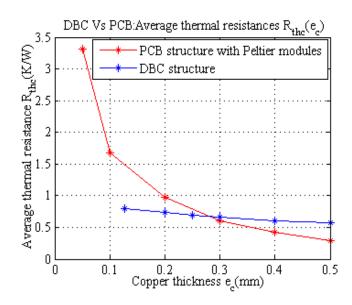

| Fig.4-6. Thermal performance comparison between PCB and DBC structures. A he                                |    |

| dissipation of 1 W in the chip, an equivalent convection heat-transfer coefficient of                       |    |

| $W/(m^2K)$ from all external surfaces (except the bottom layer and the top TEC plate) and                   |    |

| ambient temperature of 25 $^\circ\!\mathrm{C}$ are applied.                                                 |    |

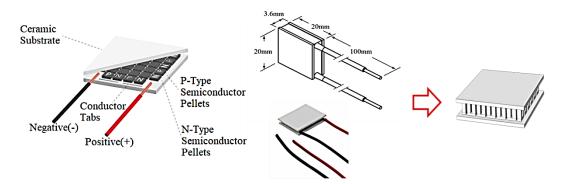

| Fig.4-7. 3D model of Peltier device CP39236H                                                                |    |

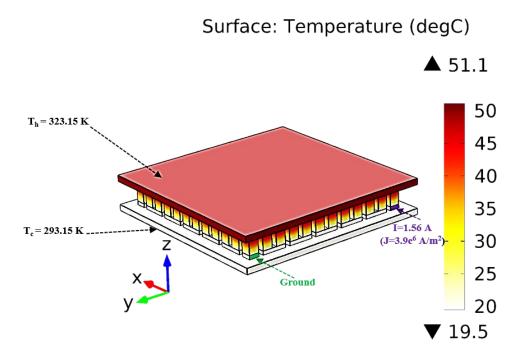

| Fig.4-8. A simulated example for the 3D FEM model of product CP39236H built                                 |    |

| COMSOL with the input current I equaling 1.56 A, the temperature of the cold side                           |    |

| equaling 20 $^\circ\! \mathbb{C}$ , the temperature of the hot side $T_h$ equaling 50 $^\circ\! \mathbb{C}$ |    |

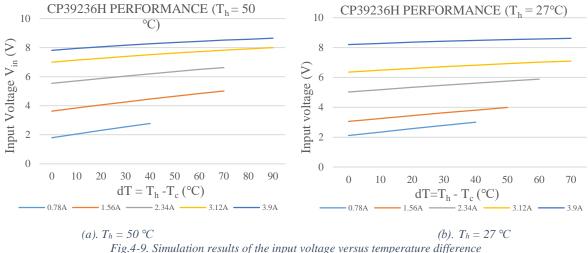

| Fig.4-9. Simulation results of the input voltage versus temperature difference                              |    |

| Fig.4-10. Simulation results of the heat absorbed versus temperature difference                             |    |

| Fig.4-11. Simulation results of the relationship between COP and input current                              |    |

| Fig.4-12. CP39236H performances from datasheet [172]                                                        |    |

| Fig.4-13. Cooling performances of Peltier modules for PCB structures                                        |    |

| Fig.4-14. Schematic of proposed cooling structure with Peltier devices beside the heati                     | -  |

| source                                                                                                      |    |

| Fig.4-15. Thermal resistance network of the studied structure                                               | 82 |

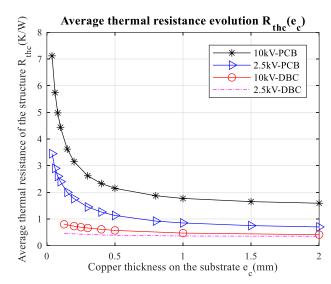

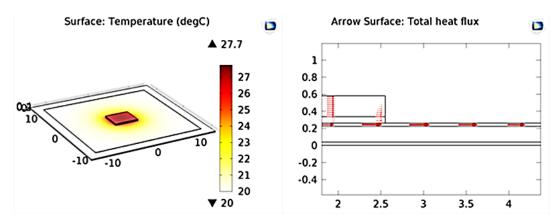

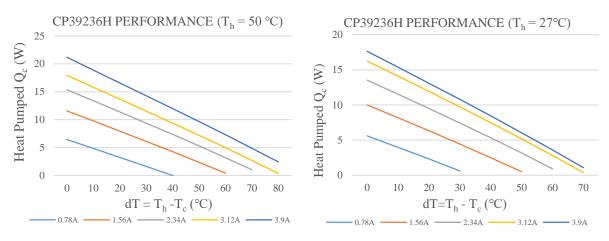

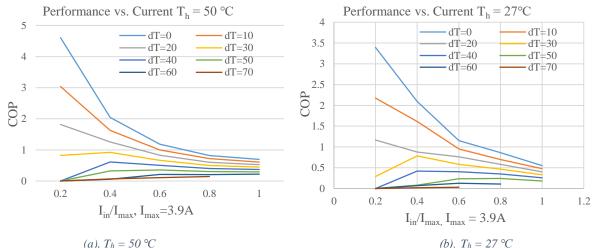

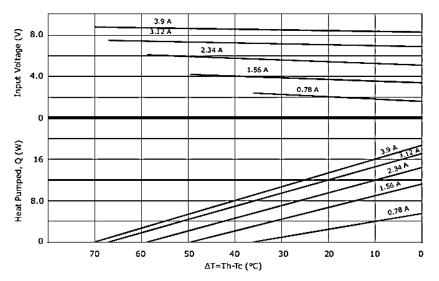

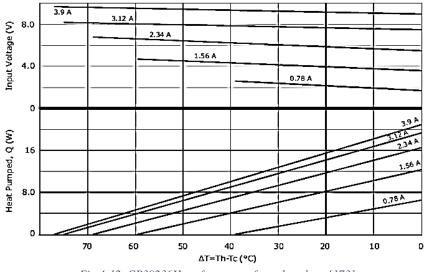

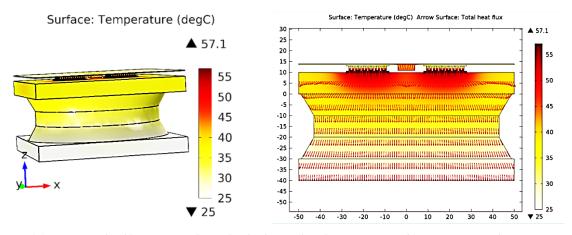

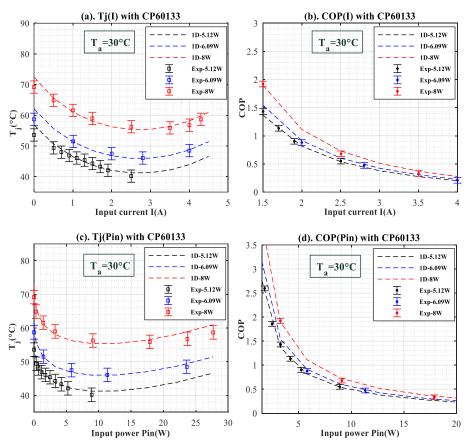

Fig.4-17. An example of 3D FEM simulation for the designed cooling structure and its section view. The PCB structure is put on a duralumin column for power loss measurement. The bottom side of the column is set at 25 °C. Heat power in the heat source  $P_{heat} = 7.6W$ Fig.4-18. 1D electro-thermal model of the cooling structure built by Matlab Simulink.....84 Fig.4-19. Thermal simulations for 1D analytical and 3D FE models. (a). Junction temperature profile  $T_i$  (I) when dissipating 5 W from the heating source; (b). Cooling efficiency profile COP (I) when dissipating 5 W from the heating source; (c). Junction temperature profile  $T_i$  (I) when dissipating 7.6 W from the heating source; (d). Cooling efficiency profile COP (I) when dissipating 7.6 W from the heating source. The ambient Fig.4-20. Test bench for validating the thermal models of the PCB structure with Peltier Fig.4-21. Power loss measurement based on calorimetric method with duralumin column86 Fig.4-22. Experimental and estimated results with Peltier devices CP39236H. (a). Junction temperature profile T<sub>i</sub> (I) when dissipating 5 W from the heating source; (b). Cooling efficiency profile COP (I) when dissipating 5 W from the heating source; (c). Junction temperature profile T<sub>j</sub> (I) when dissipating 7.6 W from the heating source; (d) Cooling efficiency profile COP (I) when dissipating 7.6 W from the heating source. The ambient Fig.4-23. Experimental and estimated results with Peltier devices CP39236H and CP30238. (a). Junction temperature profile Tj (Pin) with CP39236H; (b). Cooling efficiency profile COP (Pin) with CP39236H; (c). Junction temperature profile Tj (Pin) with CP30238; (d) Cooling efficiency profile COP (Pin) with CP30238. The ambient temperature is 25 °C..88 Fig.4-24. Estimated results with Peltier device CP39236H. (a). Junction temperature profile  $T_i$  (P<sub>in</sub>). (b). Cooling efficiency profile COP (P<sub>in</sub>). The ambient temperature is 25 °C...... 89 Fig.4-25. Experimental and estimated results with Peltier devices CP60133. (a). Junction temperature profile Tj (I); (b). Cooling efficiency profile COP (I); (c). Junction temperature profile T<sub>i</sub> (Pin); (d) Cooling efficiency profile COP (Pin). The ambient temperature is 30 °C. Fig.4-26. Estimated results with Peltier devices CP60133. (a). Junction temperature profile Tj (I) for dissipating 4 W; (b). Junction temperature profile Tj (I) for dissipating 6 W; (c). Junction temperature profile T<sub>i</sub> (I) for dissipating 8 W; (d). Junction temperature profile T<sub>i</sub> (I) for dissipating 10 W; (e). Cooling efficiency profile COP (I) for dissipating 4 W; (f). Cooling efficiency profile COP (I) for dissipating 6 W; (g) Cooling efficiency profile COP (I) for dissipating 8 W; (h). Cooling efficiency profile COP (I) for dissipating 10 W. The Fig.4-27. Estimated results with Peltier devices CP60133. (a). Junction temperature profile Tj (Pin) for dissipating 4 W; (b). Junction temperature profile Tj (Pin) for dissipating 6 W; (c). Junction temperature profile T<sub>i</sub> (Pin) for dissipating 8 W; (d). Junction temperature profile T<sub>i</sub> (Pin) for dissipating 10 W; (e). Cooling efficiency profile COP (Pin) for dissipating 4 W; (f). Cooling efficiency profile COP (Pin) for dissipating 6 W; (g) Cooling efficiency profile COP (Pin) for dissipating 8 W; (h). Cooling efficiency profile COP (Pin) for

# **LIST OF TABLES**

| Table 1.1. Physical characteristics of Si and main wide band gap semiconductors [13].     | 4     |

|-------------------------------------------------------------------------------------------|-------|

| Table 1.2. Ceramic materials used for DBC substrate [38]                                  | 9     |

| Table 1.3. Different loss-calculation models concerning IGBT devices in literatures [7]   | 3] 19 |

| Table 2.1. Thermal to electrical analogy                                                  | 41    |

| Table 3.1. Dimensions of the assembly and material properties                             | 51    |

| Table 3.2. Pitch distance and number of vias for different thermal models                 | 52    |

| Table 3.3. Via parameters used to create different 3D FE models                           | 53    |

| Table 3.4. Dimensions and thermal properties of each layer for the PCB structures         | with  |

| thermal vias                                                                              | 61    |

| Table 3.5. Comparisons between simulation and experimentation results                     | 62    |

| Table 4.1. Peltier element parameters                                                     | 73    |

| Table 4.2. Peltier element parameters and ceramic substrate dimensions of each side       | 76    |

| Table 4.3. Dimensions and calculated parameters of Peltier devices                        |       |

| Table 4.4. Thermoelectric material properties                                             |       |

| Table 4.5. Thermal to electrical analogy                                                  | 82    |

| Table 4.6. Maximum decrease of the junction temperature $\Delta T_{jmax}$ (°C)            | 91    |

| Table 4.7. COP values of the three cooling scenarios when keeping $T_j$ at 55 $^{\circ}C$ |       |

# **GENERAL INTRODUCTION**

# **GENERAL INTRODUCTION**

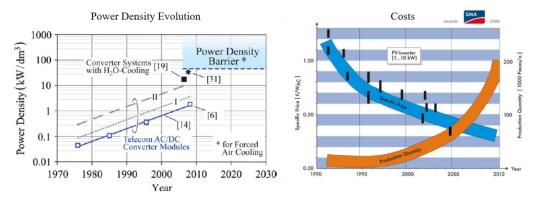

In last four decades, power electronics technology has gone through dynamic evolution due to the "more electric" concept. "*Recently, its applications are fast expanding in industrial, commercial, residential, transportation, utility, aerospace, and military environments primarily due to reduction of cost, size, and improvement of performance"* [1]. As shown in Fig.1 [2], power converters are constantly trending towards lower cost, higher efficiency, and higher power density.

Fig.1. Power density and costs evolution [2]

In addition, since characteristics of Si devices have reached its natural limitation, Wide Band Gap (WBG) components in Gallium Nitride (GaN) or Silicon Carbide (SiC) with lower on-state resistance ( $R_{on}$  ( $\Omega$ )) and higher switching frequency have recently emerged. Accompanied with the fast switching speed benefit of WBG devices, inevitably there is higher dv/dt and di/dt introduced at the same time, which can hardly be observed in comparatively slow Si Metal Oxide Semiconductor Field Effect Transistor (MOSFET). Current carrying capability is ultimately a thermal issue. In a power module, the package itself generates conduction losses in the metal interconnections, power terminals, wire bonds, and solder interfaces. Power semiconductors offer conduction losses as well as switching losses resulting from turn-on, turn-off, and diode reverse recovery energies. A well optimized system will work to reduce the magnitude of the generated losses as well as to provide an effective method for heat removal purpose [3-5].

Increased power density and advances in Wide Band Gap (WBG) semiconductors require improvements in the integration technology, packaging technology as well as thermal management solutions to adapt to their high temperature operation advantage. Today, in many applications such as aerospace and aircraft, desired reliable operating temperature is from -55 °C to 250 °C [6]. However, available packaging technologies, passives and peripheral components, solder materials, reliability considerations and cost presently limit the junction temperatures to ~175 °C even though the WBG semiconductor devices can, in principle, operate at much higher junction temperatures [7-9].

In order to mitigate these side effects and thus fully utilize the benefits of these unique devices, advanced module packaging and efficient cooling systems are needed.

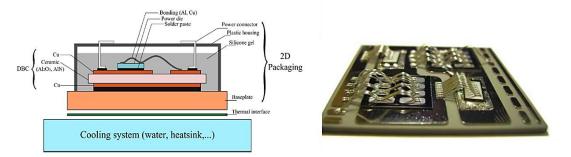

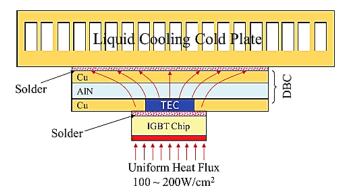

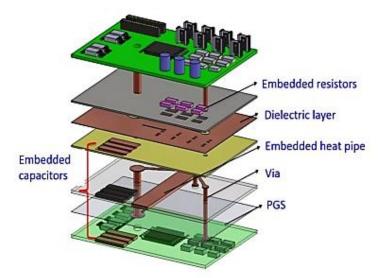

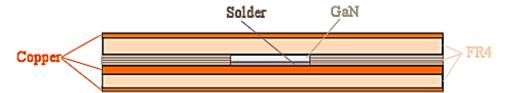

"Among the mature technologies used in power electronics domain, usually, the Printed Circuit Board (PCB) technology addresses today small and medium power (a few hundreds of Watts up to a few kW), and Direct Bonded Copper (DBC) based technology is used for medium and high power" [10]. To avoid the use of wire bondings, PCB technology is preferred to realize 3D integration of power components by embedding technologies. But

PCB substrate in material of FR4 has poor thermal conductivity (<1.5 W/mK), which brings us big challenges in thermal dissipation of the total structure.

Therefore, this research work will be devoted to develop cooling solutions for embedded PCB structures. Three different cooling methods have been studied.

- The first one allows to optimize the classical solution of creating thermal vias in the PCB substrates. The main goal here is to develop a referenced criterion of thermal via parameters for manufacturing.

- The second solution is to increase the thickness of copper layer on the top of the PCB substrate. This solution could enhance lateral heat spreading effect along the copper layer, thus increase the heat dissipation surface.

- The third one is a recent solution in use of thermoelectric cooling (TEC) devices. Compared to DBC structure with the same dielectric strength, this solution is dedicated to develop a competitive PCB structure in thermal aspects.

This thesis is organized as follows in five parts:

- In the first chapter, a brief overview concerning the development of power electronics systems and general context of this work will be presented to introduce basic concepts of thermal management needed throughout this thesis. Then, the state-of-art of power packaging, thermal measurement of the power systems as well as different thermal management solutions will be discussed. In particular, this chapter will be devoted to compare various modelling methods based on different softwares in literatures;

- The second chapter will present all used instrumentations in the process of establishing the test bench for temperature and power loss measurement. Schematic of the test bench, calibration process of some devices such as Resistance Temperature Detector (RTD) sensors, as well as chip soldering process will be introduced;

- The third chapter covers two cooling methods: the optimization of thermal vias and increasing the copper thickness of PCB. Different modeling methods: analytical and 3D Finite Element (FE) methods have been used to analyze the cooling effect of different via parameters including via diameter, number of vias, via pattern, plating thickness of copper and pitch distance between two vias etc.;

- In the fourth chapter, thermoelectric (TEC) cooling devices of Peltier modules based on Peltier effect will be described. Influences of different Peltier parameters will be discussed to optimize their thermal cooling performances.

- The last chapter dedicated to the general conclusion gives also some perspectives.

# **CHAPTER 1. STATE OF THE ART**

1.1. Introduction

- 1.2. Power Converters

- 1.3. Power Packaging

- 1.4. Thermal Analysis of Power Electronics Systems

- 1.5. Summary

# **CHAPTER 1.** STATE OF THE ART

#### **1.1. INTRODUCTION**

For completeness and better understanding of the reasons and recent advances in thermal management solutions, it is necessary to cover the concerned power converters' topologies. Firstly, different components of power converters and well-established packaging technologies for power converters will be briefly introduced and referred to existing literatures. Then, principle of different thermal management solutions will be discussed.

### **1.2. POWER CONVERTERS**

Generally, power converters consist of the totality of the equipments between source and load. The main objective is to convert currents form (AC, DC), or the voltage magnitude, or the frequency range, or a combination of that and also to control electromagnetic energy flow between an electric source and load.

Power converters are a combination of power devices which can be divided into active components and passive components. In a power converter, active components are made by association of a power transistor and its driver. By association of such elementary power switches many conversion functions can be achieved. This structure is a natural interface between digital controllers and the world of power conversion and play the role of amplifier to boost power. But they are mainly used in power converters to format the voltages and the currents by removing some unwanted frequency components. Basic passive components include capacitors and inductors.

#### 1.2.1. Semiconductor Components

Evolutions of the power converter topologies in order to improve power ratings, efficiency, reliability, performance and costs are directly related to the evolution of power semiconductor devices, which constitute the heart of power converters. In the last decades, Silicon (Si) devices (diodes, Insulated Gate Bipolar Transistors (IGBTs), MOSFETs, etc.) dominate the market because of its mature and well-established technology. However, Si devices approach theoretical limitations of the Si material. For example, Si-based device cannot sustain temperature higher than 200 °C as well as very high voltage (Si IGBT are limited to 6.6 kV). "Generally speaking, the medium-voltage range is considered in the power converter industry from 2.3 kV to 6.6 kV for high power in the range of 1-50 MW" [11]. So, Wide Band Gap (WBG) semiconductors like Gallium Nitride (GaN) and Silicon Carbide (SiC) have emerged because their intrinsic performances exceed those of Silicon [12, 13].

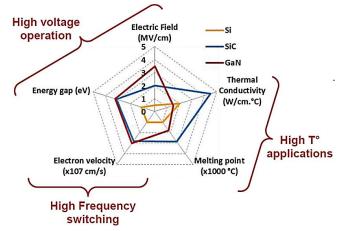

#### 1.2.1.1. Materials

Some of the main characteristics for WBG materials that can be compared to those of Si are shown in Fig.1-1 [14] and Table 1.1 [13]. These materials have superior electrical characteristics compared to Si. These properties lead to improve the power devices characteristics in several domains as they allow to lower the conduction and the switching losses. It is also possible to operate at a higher maximum junction temperature and, since the thermal properties of the WBG semiconductors are better than those of Si, the thermal management of the power dissipation can be facilitated.

These advantages allow to operate at higher frequencies and theoretically to higher ambient temperature. The emergence of new power electronics devices based on WBG semiconductor materials will result in substantial improvements in the performances of power systems in terms of faster switching speed, higher blocking voltages, higher efficiency, and higher reliability as well as higher temperature tolerance.

Fig.1-1. Summary of Si, SiC and GaN relevant material properties [14]

| Property                                                             | Si   | 6H-SiC | 4H-SiC | GaN  |

|----------------------------------------------------------------------|------|--------|--------|------|

| Bandgap, $Eg$ (eV)                                                   | 1.12 | 3.03   | 3.26   | 3.45 |

| Dielectric constant, $\varepsilon_r$                                 | 11.9 | 9.66   | 10.1   | 9    |

| Electric breakdown field, $E_c$ (kV/cm)                              | 300  | 2500   | 2200   | 2000 |

| Electron Mobility, $\mu_n$ (cm <sup>2</sup> / V.s)                   | 1500 | 500    | 1000   | 1250 |

| Thermal conductivity, $\lambda$ (W/m.K)                              | 150  | 490    | 490    | 130  |

| Saturate Electron Drift Velocity, $v_{sat}$ (x 10 <sup>7</sup> cm/s) | 1    | 2      | 2      | 2.2  |

Table 1.1. Physical characteristics of Si and main wide band gap semiconductors [13]

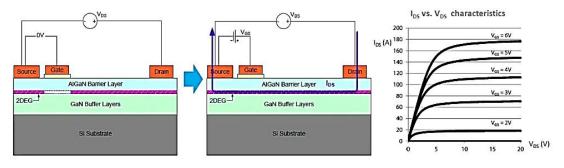

## 1.2.1.2. GaN Devices

GaN devices have a lateral structure because they are based on the high electron mobility transistor (HEMT) structure. As we can see in Fig.1-2 [15], a GaN HEMT is built on a silicon substrate, with a lateral two-dimensional electron gas (2DEG) channel formed on an AlGaN/GaN hetero-epitaxy structure [15, 16]. Like a Si MOSFET, a GaN transistor has source, drain and gate terminals, and the key figures of merit are  $R_{on}$  and the breakdown voltage.

Compared to Si devices, GaN devices have three main advantages:

- Lower Ron: theoretically about three orders of magnitude smaller than conventional Si devices because of the high critical electric field which allows to minimize the device length and the high concentration 2DEG with high carrier mobility [17], thus reducing a major source of static losses and inefficiency when at on-state.

- **Faster on/off switching:** switching hundreds of volts in nanoseconds, supporting the design of supplies that can switch large currents at rates of several megahertz (some latest-generation devices can operate in the hundreds of MHz) [15].

- Smaller die size: this gives us the potential to develop integrated circuits with high power density. For example, the eGaN transistor provided by EPC (40 V-33 A) has a very small die size of 4075 × 1602 × 685 μm [18].

There are two types of GaN transistors available on the market:

• Those operating in depletion mode: such GaN transistors are normally on. To turn them off, a negative voltage between the drain and the source electrodes is needed. To work around this apparent drawback (for the most popular power converters) and have it in a normally off configuration, they are often packaged

in a cascode configuration with a low-voltage Si MOSFET that reverses this situation [19].

• **Those operating in enhancement mode:** such GaN transistors are normally off (for example when the gate drive voltage is set to zero: left image in Fig.1-2) and are turned on when a positive voltage exceeding the threshold voltage is applied to the gate turned on by positive voltage applied to the gate (center and right images in Fig.1-2).

Fig.1-2. Normally-on GaN device built on a silicon substrate (Source: MOUSER ELECTRONICS [15])

## 1.2.1.3. SiC Devices

Those wide bandgap transistors are different from GaN devices. Indeed, the structure of SiC devices is usually vertical like Si power devices. Fast development of SiC technology in recent years is bringing solutions to the many barriers that Si devices have encountered. Besides the same advantages as GaN devices, authors in [20] have summarized following compelling advantages of SiC devices as following:

- Higher critical electrical field: It's ~8 times higher than that of Si, thus a SiC device is much thinner due to its high dielectric strength and is doped to a much higher level, leading to lower losses.

- Higher thermal conductivity: It's ~3 times higher than that of Si and heat dissipation by the losses can be conducted with a much lower temperature drop across the semiconductor material.

- *Higher operating temperature:* SiC devices can operate well over 400 °C (~150 °C for standard Si devices) which allows to increase the possible power density and enables applications in harsh environments.

Today, main commercial available SiC power devices are Schottky diodes, MOSFETs and Bipolar Junction Transistors (BJTs). Authors or manufacturers in [20-22] have characterized these SiC components. Advantages of these components have also been reviewed by authors in [20]:

- SiC Schottky Diode: It's the first successfully commercialized SiC power device and has extended the breakdown voltage of a Schottky diode above 1000 V, which had ever been limited below 200 V with Si technology [20].

- SiC MOSFET: It's attractive since it is voltage controlled and normally off. And it does not require continuous driving current to maintain the conduction state. Today several components from different manufacturers are available on the market for 1.2 and 1.7 kV and devices with higher breakdown voltage (until 10 kV) have been demonstrated.

• SiC BJT: It can provide the lowest specific R<sub>on</sub> that results in the smallest chip size and the smallest parasitic capacitance for a given voltage and current rating, allowing higher switching speed than other SiC switching devices. In addition, SiC BJT has no oxide layer and can operate at higher temperatures than the SiC MOSFET.

Compared to the best Si IGBTs, SiC devices will improve system efficiency up to 20 % and operate at 2-5 times the switching frequencies [2].

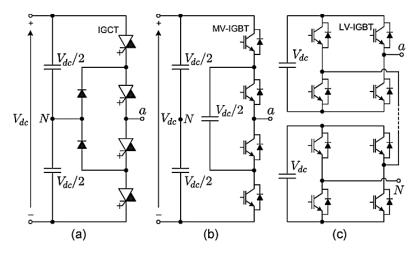

#### 1.2.2. Multilevel Converters

The converter topologies can be divided into two main groups: direct and indirect converters. Direct converters are topologies without any energy storage elements. Indirect converter is made of several stages with an energy storage link between them [23]. Besides, according to the nature of the dc link (inductive or capacitive, respectively), converters can be divided into Current Source Converters (CSCs) and Voltage Source Converters (VSCs). "In addition, VSCs can also be classified into two-level and multilevel converters depending on the number of voltage levels generated at the output" [23, 24].

Classic multilevel converter topologies (one phase) are shown in Fig.1-3 [11]. They are well established topologies namely the Neutral Point Clamped (NPC), the Cascaded H-Bridge (CHB) and the Flying Capacitor (FC). Operating principles, multilevel waveform generation, special characteristics, modulation schemes and more details as advantages and disadvantages related to the NPC, FC and CHB can be found in [25-29] and will not be covered in this thesis devoted to the present thermal management topics. Generally, multilevel converters have their own potential advantages thanks to their lower output harmonic distortion and also the lower device voltage rating requirements, which can provide a lighter, more efficient and more reliable power converter.

Fig.1-3. (a) Three-level NPC featuring IGCTs; (b) Three-level FC featuring MV-IGBTs; (c) Five-level CHB featuring LV-IGBTs [11]

#### 1.2.2.1. Power Losses Distribution

Power-supply efficiency is a critical criterion for power converters. The efficiency of the chosen power solutions relates to system power losses and thermal performances of switching cells and other components. An ideal switch implies zero losses, thus offering 100% efficiency. However, components are not ideal, and the topology of converters plays an important role in the power loss distribution as it defines the way the switches are operated [30]. For example, for a 2-level three-phase inverter, it is possible to apply eight different

switching states [31] and some of them give the same differential voltages on a starconnected load.

The losses in a device can be mainly classified as switching losses, conduction losses and reverse recovery losses (for diode).

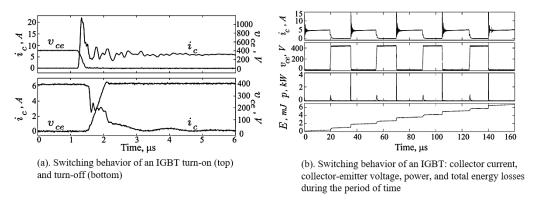

#### Switching Losses

Switching losses reduce the efficiency of power converters, particularly at low power ranges and force the designer to include large cooling devices. Typical switching losses are generated during the turn-on and turn-off transitions due to internal device capacitance, stored charges for bipolar components and stray inductances:

- **Device Capacitance:** It is the internal output capacitance (C<sub>oss</sub>) that comes in parallel with the switch such as IGBT and MOSFET when the switch comes in turning-on state. The energy stored by this capacitance in the off-state is vanished during the turning-on transition.

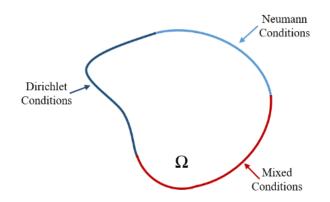

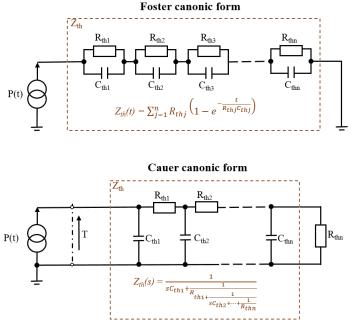

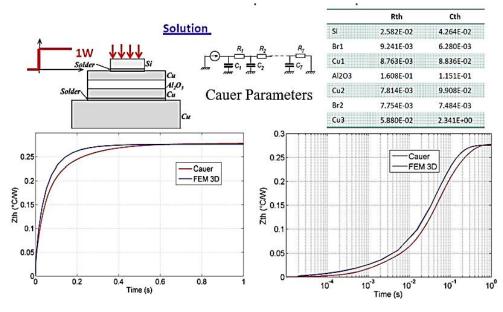

- **Stray Inductances:** These are inductances that appear effectively in series with the switch. The stored energy by these inductances during the on-state is vanished during the turn-off transition.