# Remote hardware attacks on connected devices

Joseph Gravellier

# ▶ To cite this version:

Joseph Gravellier. Remote hardware attacks on connected devices. Other. Université de Lyon, 2021. English. NNT: 2021LYSEM034. tel-03879252

# HAL Id: tel-03879252 https://theses.hal.science/tel-03879252v1

Submitted on 30 Nov 2022

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

N° d'ordre NNT: 2021LYSEM034

# THESE de DOCTORAT DE L'UNIVERSITE DE LYON

opérée au sein du Laboratoire Systèmes et Architectures Sécurisés et Thales

# **Ecole Doctorale N°488**

Science, Ingéniérie, Santé

Microélectronique / Systèmes Embarqués Sécurisés

Soutenue publiquement le 03/12/2021 par:

# Joseph Gravellier

# Remote Hardware Attacks on Connected Devices

Devant le jury composé de:

Edith KUSSENER, Professeur, ISEN

Présidente / Rapportrice

Régis LEVEUGLE, Professeur, Grenoble INP, Université Grenoble AlpesRapporteurJacques FOURNIER, Chef du laboratoire de sécurité, CEA-LetiExaminateurEmmanuel PROUFF, Chef adjoint de la division Produits et Services Sécurisés, ANSSIExaminateurLilian BOSSUET, Professeur, LaHC/Université Jean MonnetExaminateur

Jean-Max DUTERTRE, Professeur, *Mines St Etienne*Yannick TEGLIA, Ingénieur expert sécurité matérielle, *Thales*Philippe LOUBET MOUNDI, Manager expert sécurité matérielle, *Thales*

Directeur de thèse Encadrant

Encadrant

SCIENCES ET GENIE DES MATERIAUX MECANIQUE ET INGENIERIE GENIE DES PROCEDES SCIENCES DE LA TERRE SCIENCES ET GENIE DE L'ENVIRONNEMENT

Responsables :

K. Wolski Directeur de recherche S. Drapier, professeur F. Gruy, Maître de recherche B. Guy, Directeur de recherche

V.Laforest, Directeur de recherche

Spécialités doctorales

MATHEMATIQUES APPLIQUEES INFORMATIQUE SCIENCES DES IMAGES ET DES FORMES GENIE INDUSTRIEL MICROELECTRONIQUE

M. Batton-Hubert O. Boissier, Professeur JC. Pinoli, Professeur N. Absi, Maitre de recherche Ph. Lalevée, Professeur

Responsables

EMSE: Enseignants-chercheurs et chercheurs autorisés à diriger des thèses de doctorat (titulaires d'un doctorat d'Etat ou d'une HDR)

| MSE : Enseignants-cher | cheurs et chercheurs au | itorisés à diriger des thèses o | de doctorat (titulaires d'un doctorat d | l'État ou d'une |

|------------------------|-------------------------|---------------------------------|-----------------------------------------|-----------------|

| ABSI                   | Nabil                   | MR                              | Génie industriel                        | CMP             |

| AUGUSTO                | Vincent                 | MR                              | Génie industriel                        | CIS             |

| AVRIL                  | Stéphane                | PR                              | Mécanique et ingénierie                 | CIS             |

| BADEL                  | Pierre                  | PR                              | Mécanique et ingénierie                 | CIS             |

| BALBO                  | Flavien                 | PR                              | Informatique                            | FAYOL           |

| BASSEREAU              | Jean-François           | PR                              | Sciences et génie des matériaux         | SMS             |

| BATTON-HUBERT          | Mireille                | PR                              | Mathématiques appliquées                | FAYOL           |

| BEIGBEDER              | Michel                  | MA                              | Informatique                            | FAYOL           |

| BILAL                  | Blayac                  | DR                              | Sciences et génie de l'environnement    | SPIN            |

| BLAYAC                 | Sylvain                 | PR                              | Microélectronique                       | CMP             |

| BOISSIER               | Olivier                 | PR                              | Informatique                            | FAYOL           |

| BONNEFOY               | Olivier                 | PR                              | Génie des Procédés                      | SPIN            |

| BORBELY                | Andras                  | DR                              | Sciences et génie des matériaux         | SMS             |

| BOUCHER                | Xavier                  | PR                              | Génie Industriel                        | FAYOL           |

| BRUCHON                | Julien                  | PR                              | Mécanique et ingénierie                 | SMS             |

| CAMEIRAO               | Ana                     | PR                              | Génie des Procédés                      | SPIN            |

| CHRISTIEN              | Frédéric                | PR                              | Science et génie des matériaux          | SMS             |

| DAUZERE-PERES          | Stéphane                | PR                              | Génie Industriel                        | CMP             |

| DEBAYLE                | Johan                   | MR                              | Sciences des Images et des Formes       | SPIN            |

| DEGEORGE               | Jean-Michel             | MA                              | Génie industriel                        | Fayol           |

| DELAFOSSE              | David                   | PR                              | Sciences et génie des matériaux         | SMS             |

| DELORME                | Xavier                  | PR                              | Génie industriel                        | FAYOL           |

| DESRAYAUD              | Christophe              | PR                              | Mécanique et ingénierie                 | SMS             |

| DJENIZIAN              | Thierry                 | PR                              | Science et génie des matériaux          | CMP             |

| BERGER-DOUCE           | Sandrine                | PR                              | Sciences de gestion                     | FAYOL           |

| DRAPIER                | Sylvain                 | PR                              | Mécanique et ingénierie                 | SMS             |

| DUTERTRE               | Jean-Max                | PR                              | Microélectronique                       | CMP             |

| EL MRABET              | Nadia                   | MA                              | Microélectronique                       | CMP             |

| FAUCHEU                | Jenny                   | MA                              | Sciences et génie des matériaux         | SMS             |

| FAVERGEON              | Loïc                    | MR                              | Génie des Procédés                      | SPIN            |

| FEILLET                | Dominique               | PR                              | Génie Industriel                        | CMP             |

| FOREST                 | Valérie                 | PR                              | Génie des Procédés                      | CIS             |

| FRACZKIEWICZ           | Anna                    | DR                              | Sciences et génie des matériaux         | SMS             |

| GAVET                  | Yann                    | MA                              | Sciences des Images et des Formes       | SPIN            |

| GERINGER               | Jean                    | MA                              | Sciences et génie des matériaux         | CIS             |

| GONDRAN                | Natacha                 | MA                              | Sciences et génie de l'environnement    | FAYOL           |

| GONZALEZ FELIU         | Jesus                   | MA                              | Sciences économiques                    | FAYOL           |

| GRAILLOT               | Didier                  | DR                              | Sciences et génie de l'environnement    | SPIN            |

| GRIMAUD                | Frederic                | EC                              | Génie mathématiques et industriel       | FAYOL           |

| GROSSEAU               | Philippe                | DR                              | Génie des Procédés                      | SPIN            |

| GRUY                   | Frédéric                | PR                              | Génie des Procédés                      | SPIN            |

| HAN                    | Woo-Suck                | MR                              | Mécanique et ingénierie                 | SMS             |

| HERRI                  | Jean Michel             | PR                              | Génie des Procédés                      | SPIN            |

| ISMAILOVA              | Esma                    | MC                              | Microélectronique                       | CMP             |

| KERMOUCHE              | Guillaume               | PR                              | Mécanique et Ingénierie                 | SMS             |

| KLOCKER                | Helmut                  | DR                              | Sciences et génie des matériaux         | SMS             |

| LAFOREST               | Valérie                 | DR                              | Sciences et génie de l'environnement    | FAYOL           |

| LERICHE                | Rodolphe                | DR                              | Mécanique et ingénierie                 | FAYOL           |

| LIOTIER                | Pierre-Jacques          | MA                              | Mécanique et ingénierie                 | SMS             |

| MEDINI                 | Khaled                  | EC                              | Sciences et génie de l'environnement    | FAYOL           |

| MOLIMARD               | Jérôme                  | PR                              | Mécanique et ingénierie                 | CIS             |

| MOULIN                 | Nicolas                 | MA                              | Mécanique et ingénierie                 | SMS             |

| MOUTTE                 | Jacques                 | MR                              | Génie des Procédés                      | SPIN            |

| NAVARRO                | Laurent                 | MR                              | Mécanique et ingénierie                 | CIS             |

| NEUBERT                | Gilles                  | PR                              | Génie industriel                        | FAYOL           |

| NIKOLOVSKI             | Jean-Pierre             | Ingénieur de recherche          | Mécanique et ingénierie                 | CMP             |

| O CONNOR               | Rodney Philip           | PR                              | Microélectronique                       | CMP             |

| PICARD                 | Gauthier                | PR                              | Informatique                            | FAYOL           |

| PINOLI                 | Jean Charles            | PR                              | Sciences des Images et des Formes       | SPIN            |

| POURCHEZ               | Jérémy                  | DR                              | Génie des Procédés                      | CIS             |

| ROUSSY                 | Agnès                   | MA                              | Microélectronique                       | CMP             |

| SANAUR                 | Sébastien               | MA                              | Microélectronique                       | CMP             |

| SERRIS                 | Eric                    | IRD                             | Génie des Procédés                      | FAYOL           |

| STOLARZ                | Jacques                 | CR                              | Sciences et génie des matériaux         | SMS             |

| VALDIVIESO             | François                | PR                              | Sciences et génie des matériaux         | SMS             |

| VIRICELLE              | Jean Paul               | DR                              | Génie des Procédés                      | SPIN            |

| WOLSKI                 | Krzystof                | DR                              | Sciences et génie des matériaux         | SMS             |

| XIE                    | Xiaolan                 | PR                              | Génie industriel                        | CIS             |

| YUGMA                  | Gallian                 | MR                              | Génie industriel                        | CMP             |

|                        |                         | 2.22                            | ,                                       | C               |

#### **ABSTRACT**

To meet the ever-growing need for performance in silicon devices, integrated-circuit providers have been increasingly relying on software-hardware cooperation. By controlling hardware resources such as power or clock management from the software, developers earn the possibility to build more flexible and power efficient applications. Despite the benefits, these hardware components are now exposed to software code and can potentially be misused as open-doors to new types of attacks.

In this thesis we aim at evaluating software-based hardware attacks, a novel attack family that targets connected devices such as IoT products, smartphones or cloud datacenters. These attacks take advantage of hardware resources that can be directly accessed from software in complex integrated-circuits and use them to conduct fault injection and side-channel analysis exploits. Because they are triggered by software code, they can be launched remotely and on multiple victim devices regardless of their physical location. Through the evaluation of software-based hardware attacks we aim at assessing the level of threat they pose to connected devices security and at providing countermeasure guidelines for building resistant systems. The challenge is considerable since any connected device is potentially endangered.

This manuscript gathers the research work conducted during this thesis to identify attack vectors in FPGAs and complex SoC systems. Through our experiments we discovered generic software-based hardware attack vectors widely implemented in recent SoCs that could enable remote hardware attacks. We conducted FPGA-to-FPGA and FPGA-to-CPU attacks and demonstrated that remote power side-channel analysis was feasible. These new attack paths represent a serious threat for FPGA-based systems especially when applied to multi-user cloud FPGAs and heterogeneous SoCs. Then, we went further by proving that delay-line components, widely implemented in high-end SoCs, could be used for conducting fault injection and side-channel attacks. We built various scenarios such as CPU-to-CPU and CPU-to-MCU attacks on Linux-based operating systems and demonstrated that software-based hardware attacks could successfully break the logical isolation between processes and lead to the extraction of sensitive information.

Throughout the chapters, we precisely describe the methodology adopted to build and conduct the attacks along with countermeasure proposals to mitigate their impact. Finally, according to our experimentations results and to other works published recently, it appears that any door left open for malwares to gain access to hardware resources could lead to full disclosure of a target's stored secrets. Therefore, there is an urgent need to build on the lessons learned from this thesis and employ countermeasures to effectively mitigate remote hardware attacks.

# **TABLE OF CONTENTS**

| Abst  | ract        |            |                                                          | iii  |

|-------|-------------|------------|----------------------------------------------------------|------|

| Table | e of Conter | nts        |                                                          | X    |

| List  | of Figures  |            |                                                          | хi   |

| List  | of Tables   |            |                                                          | XV   |

| Gloss | sary        |            | x                                                        | vii  |

| Avan  | t Propos    |            | 3                                                        | xxi  |

| Résu  | mé          |            | XX                                                       | xiii |

| 1 I   | ntroductio  | n          |                                                          | 1    |

| 1.1   | Thesis C    | ontext     |                                                          | 2    |

| 1.2   | Thesis O    | bjectives  |                                                          | 3    |

| 1.3   | Roadmaı     | e: From F  | PGA to CPU exploits                                      | 3    |

| 1.4   | Contribu    | tions      |                                                          | 4    |

|       | 1.4.1       | Software   | e-based Power Analysis Attacks on FPGAs                  | 4    |

|       | 1.4.2       | Software   | e-based Power Analysis Attacks on Complex SoCs           | 5    |

|       | 1.4.3       | Software   | e-based Fault Injection on SoC External Memory Transfers | 5    |

| 1.5   | Outline .   |            |                                                          | 6    |

| 2 B   | ackground   | l          |                                                          | 7    |

| 2.1   | Introduct   | tion to Ha | rdware Attacks                                           | 8    |

|       | 2.1.1       | Origins    |                                                          | 8    |

|       | 2.1.2       | Attack C   | Classification                                           | 8    |

|       | 2.1.3       | Non-Inv    | asive Attack Setup                                       | 10   |

|       | 2.1.4       | Non-Inv    | asive Side-Channel Analysis Attacks                      | 11   |

|       |             | 2.1.4.1    | Power Analysis Attacks                                   | 11   |

|       |             | 2.1.4.2    | Electromagnetic Analysis Attacks                         | 12   |

|       |             | 2.1.4.3    | Other Side-Channels                                      | 13   |

|       | 2.1.5       | Non-Inv    | asive Fault Injection Attacks                            | 14   |

|       |             | 2.1.5.1    | Clock and Power Glitch Attacks                           | 14   |

|       |             | 2.1.5.2    | Electromagnetic Glitch Attacks                           | 15   |

| 2.2   | The Adv     | ent of Cor | nnected Devices                                          | 16   |

|      | 2.2.1      | Overview     | v                                                     | 16 |

|------|------------|--------------|-------------------------------------------------------|----|

|      | 2.2.2      | Applicat     | ions and Threats                                      | 16 |

|      | 2.2.3      | Hardwar      | e Attacks: No Future?                                 | 18 |

| 2.3  | Remote 1   | Hardware     | Attacks                                               | 18 |

|      | 2.3.1      | The Orig     | rins of Remote Hardware Attacks                       | 18 |

|      |            | 2.3.1.1      | The Increasing Complexity of Modern Devices           | 19 |

|      |            | 2.3.1.2      | The Adoption of Multi-User and Multi-Tasking Systems  | 20 |

|      |            | 2.3.1.3      | The Emergence of Integrated Security                  | 21 |

|      | 2.3.2      | Remote 1     | Hardware Attack Families                              | 24 |

|      |            | 2.3.2.1      | TEMPEST Attacks                                       | 24 |

|      |            | 2.3.2.2      | Timing and Microarchitectural Attacks                 | 25 |

|      |            | 2.3.2.3      | Software-based Hardware Attacks                       | 28 |

|      | 2.3.3      | Software     | -based Hardware Attack Taxonomy                       | 29 |

|      | 2.3.4      | Software     | -based Fault Injection Attacks                        | 30 |

|      |            | 2.3.4.1      | Overview & Categorization                             | 30 |

|      |            | 2.3.4.2      | Rowhammer-based Bit-flips Injection in DRAM Mem-      |    |

|      |            |              | ories                                                 | 30 |

|      |            | 2.3.4.3      | FPGA-based Power Glitch Injection                     | 32 |

|      |            | 2.3.4.4      | DVFS-based Power/Clock Glitch Injection               | 34 |

|      |            | 2.3.4.5      | Delay-Line-based Glitch Injection on Memory Transfers | 36 |

|      | 2.3.5      | Software     | -based Side-Channel Analysis Attacks                  | 37 |

|      |            | 2.3.5.1      | Overview & Categorization                             | 37 |

|      |            | 2.3.5.2      | FPGAs-based Power Side-Channel Attacks                | 37 |

|      |            | 2.3.5.3      | ADC-based Power Side-Channel Attacks                  | 39 |

|      |            | 2.3.5.4      | Delay-Line-based Power Side-Channel Attacks           | 41 |

|      |            | 2.3.5.5      | Intel RAPL-based Power Side-Channel Attacks           | 41 |

|      | 2.3.6      | Software     | based Hardware Attack Privileges                      | 42 |

| 2.4  | Conclusi   | on           |                                                       | 45 |

| 3 Sc | oftware-ba | sed Powe     | er Analysis Attacks on FPGAs                          | 47 |

| 3.1  | Chapter 1  | Introduction | on                                                    | 48 |

| 3.2  | Technica   | l Backgro    | und                                                   | 50 |

|      | 3.2.1      | FPGAs V      | Voltage Fluctuations                                  | 50 |

|      |            | 3.2.1.1      | Power Supply Fluctuations                             | 50 |

|      |            | 3.2.1.2      | Effect on Logic Propagation Delays                    | 51 |

|      | 3.2.2      | Delay Se     | ensors                                                | 51 |

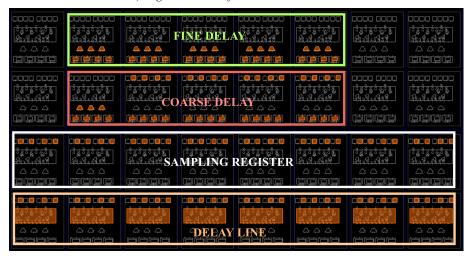

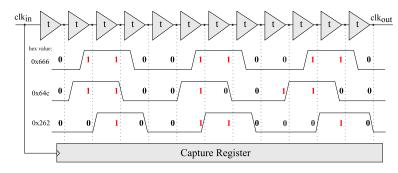

|      |            | 3.2.2.1      | Time-to-Digital Converter-based Sensor                | 52 |

|      |            | 3.2.2.2      | Ring-Oscillator-based Sensor                          | 53 |

|      | 3.2.3      | Threat M     | Iodel: FPGA-based Power SCA                           | 53 |

|      | 3.2.4      | Related V    | Works: Existing Scenarios (2018)                      | 54 |

| 3.3  | FPGA-to    | -FPGA -      | Designing High-Speed RO-based Sensors for FPGA-       |    |

|      | based SC   | CA           |                                                       | 55 |

|      | 3 3 1      | Introduct    | tion                                                  | 55 |

|     | 3.3.2   | Motivati  | on                                              | 56 |

|-----|---------|-----------|-------------------------------------------------|----|

|     | 3.3.3   | A Novel   | RO-based Sensor Design                          | 56 |

|     |         | 3.3.3.1   | RO-based Sensors Downsides                      | 56 |

|     |         | 3.3.3.2   | Designing a high frequency RO-based Sensor      | 57 |

|     |         | 3.3.3.3   | Number of RO-based sensors                      | 58 |

|     |         | 3.3.3.4   | Place and Route Influence                       | 59 |

|     | 3.3.4   | RO-sens   | or based Correlation Power analysis Attack      | 59 |

|     |         | 3.3.4.1   | Experimental Setup                              | 59 |

|     |         | 3.3.4.2   | Correlation Power Analysis Model                | 60 |

|     |         | 3.3.4.3   | JRO-based Sensor CPA Results                    | 61 |

|     | 3.3.5   | Further I | Results and Discussion                          | 62 |

|     |         | 3.3.5.1   | TDC & Electromagnetic Experimental Setup        | 62 |

|     |         | 3.3.5.2   | Side-Channel Results                            | 62 |

|     |         | 3.3.5.3   | Discussion                                      | 63 |

|     | 3.3.6   | Conclusi  | on                                              | 64 |

| 3.4 | FPGA-to | o-CPU - R | emote Side-Channel Attacks on Heterogeneous SoC | 66 |

|     | 3.4.1   | Introduc  | tion                                            | 66 |

|     | 3.4.2   | Presenta  | tion of the Side-Channel Setup                  | 67 |

|     |         | 3.4.2.1   | Side-Channel Targets                            | 67 |

|     |         | 3.4.2.2   | Xilinx Zynq Experimental Setup                  | 67 |

|     | 3.4.3   | FPGA-b    | ased attack on Hardware AES                     | 68 |

|     | 3.4.4   | FPGA-b    | ased attack on Software AES                     | 70 |

|     |         | 3.4.4.1   | Experiment 1: 8-bit Tiny AES                    | 70 |

|     |         | 3.4.4.2   | Experiment 2 : 32-bit OpenSSL AES               | 71 |

|     | 3.4.5   | EM Resi   | ults & Discussion                               | 73 |

|     |         | 3.4.5.1   | Electromagnetic Side-Channel Attack             | 73 |

|     |         | 3.4.5.2   | Attack feasibility                              | 74 |

|     |         | 3.4.5.3   | Countermeasures                                 | 74 |

|     | 3.4.6   | Conclusi  | on                                              | 75 |

|     | 3.4.7   | Appendi   | x                                               | 76 |

| 3.5 | SCAbox  | - A Fram  | ework for Evaluating the FPGA-based SCA Threat  | 77 |

|     | 3.5.1   | Introduc  | tion                                            | 77 |

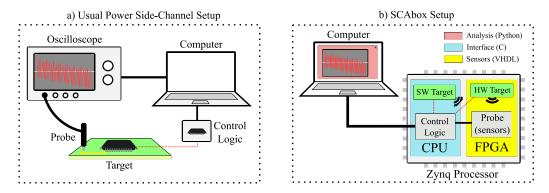

|     |         | 3.5.1.1   | Comparison with Usual Side-Channel Attacks      | 78 |

|     | 3.5.2   | Framewo   | ork Architecture                                | 79 |

|     |         | 3.5.2.1   | Overview                                        | 79 |

|     |         | 3.5.2.2   | Hardware Architecture (FPGA)                    | 79 |

|     |         | 3.5.2.3   | Software Architecture (Processor)               | 80 |

|     |         | 3.5.2.4   | SCA Automation Tool (Computer)                  | 80 |

|     | 3.5.3   | SCAbox    | User experience                                 | 81 |

|     |         | 3.5.3.1   | Use case: SCA Sensor & Setup                    |    |

|     |         | 3.5.3.2   | Use case: SCA Acquisition & Attack              |    |

|     |         | 3.5.3.3   | Discussion                                      |    |

|     | 3.5.4   | Conclusi  | ion                                             |    |

| 3.6 | Conclusi   | on on FP   | GA-based Power Analysis                                | 84  |

|-----|------------|------------|--------------------------------------------------------|-----|

|     | 3.6.1      | Results 1  | Reminder                                               | 84  |

|     |            | 3.6.1.1    | Main Contributions                                     | 84  |

|     |            | 3.6.1.2    | Some Numbers                                           | 84  |

|     | 3.6.2      | SbHA K     | nowledge: Demystifying On-Chip Power SCA               | 85  |

|     |            | 3.6.2.1    | On-Chip Power SCA can be conducted using digital logic | 85  |

|     |            | 3.6.2.2    | On-Chip Power SCA can be conducted with limited        |     |

|     |            |            | sensors                                                | 85  |

|     |            | 3.6.2.3    | On-Chip Power SCA can be conducted across the SoC      |     |

|     |            |            | boundaries                                             | 85  |

|     | 3.6.3      | SbHA K     | nowledge: Strengths and Challenges of On-Chip Power    |     |

|     |            | SCA        |                                                        | 86  |

|     |            | 3.6.3.1    | Challenge 1: Trace Synchronization                     | 86  |

|     |            | 3.6.3.2    | Challenge 2: Data Storage                              | 86  |

|     |            | 3.6.3.3    | Challenge 3: Data Export                               | 87  |

|     |            | 3.6.3.4    | Strength 1: Sensor Combination                         | 87  |

|     |            | 3.6.3.5    | Strength 2: Unlimited Attack Time                      | 87  |

|     | 3.6.4      | A Step 7   | Toward SoC Attacks                                     | 88  |

| 4 S | oftware-ba | ased Powe  | er Analysis Attacks on Complex SoCs                    | 89  |

| 4.1 | Chapter    | Introducti | on                                                     | 90  |

|     | 4.1.1      | Identifyi  | ng SbSCA Vectors                                       | 90  |

|     | 4.1.2      | Selecting  | g an SbSCA Vector                                      | 93  |

|     | 4.1.3      | Chapter    | Outline                                                | 94  |

| 4.2 | Technica   | l Backgro  | ound                                                   | 95  |

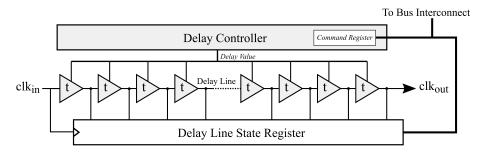

|     | 4.2.1      | Memory     | Controller Basics                                      | 95  |

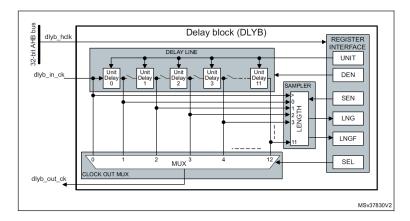

|     | 4.2.2      | Delay-L    | ine Blocks in Low-Bandwidth Memory Controllers         | 96  |

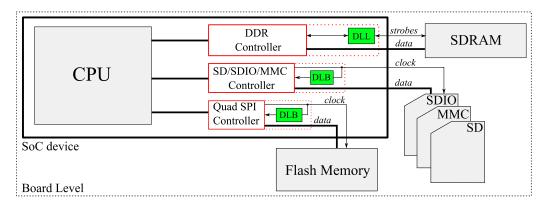

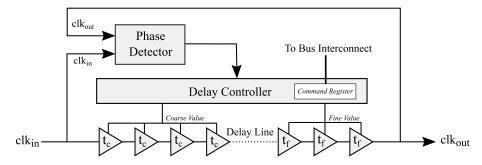

|     | 4.2.3      | DLLs in    | High-Bandwidth Memory Controllers                      | 97  |

| 4.3 | SideLine   | e: Delay-L | ine-based power SCA on complex SoCs                    | 99  |

|     | 4.3.1      | Introduc   | tion                                                   | 99  |

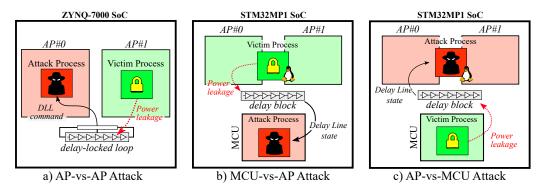

|     | 4.3.2      | Experim    | ental Setup                                            | 99  |

|     |            | 4.3.2.1    | Tested Devices                                         | 99  |

|     |            | 4.3.2.2    | OpenSSL AES Architecture                               | 100 |

|     |            | 4.3.2.3    | Threat Model                                           | 100 |

|     | 4.3.3      | DLL-bas    | sed Power Side-Channel Attack                          | 101 |

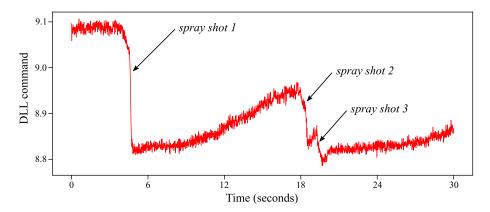

|     |            | 4.3.3.1    | Validating DLL Effectiveness: Monitoring Temperature   | 102 |

|     |            | 4.3.3.2    | Improving Sampling Rate and Synchronisation using      |     |

|     |            |            | DMA                                                    | 102 |

|     |            | 4.3.3.3    | Bare Metal OpenSSL AES Attack Setup                    | 103 |

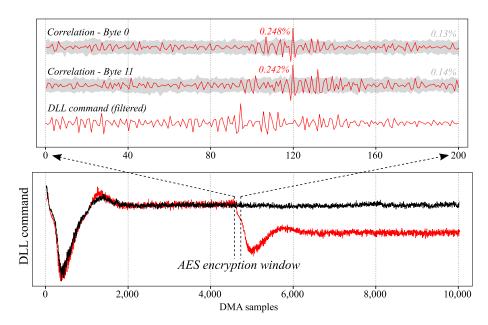

|     |            | 4.3.3.4    | DLL-based SCA Attack on Zynq-7000 SoC                  |     |

|     |            | 4.3.3.5    | Conclusion on DLL-based SCA                            | 106 |

|     | 4.3.4      | Delay-B    | lock-based Power Side-Channel Attack                   | 106 |

|     |            | 4.3.4.1    | From Delay-Block to TDC Sensor                         | 106 |

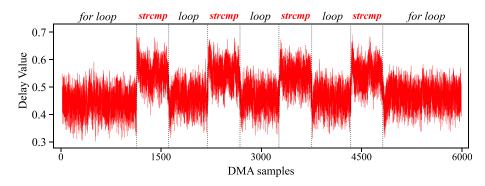

|     |            | 4.3.4.2 Validating Delay-Block Effectiveness: strcmp test | 107 |

|-----|------------|-----------------------------------------------------------|-----|

|     |            | 4.3.4.3 Linux-based OpenSSL AES Attack Setup              | 108 |

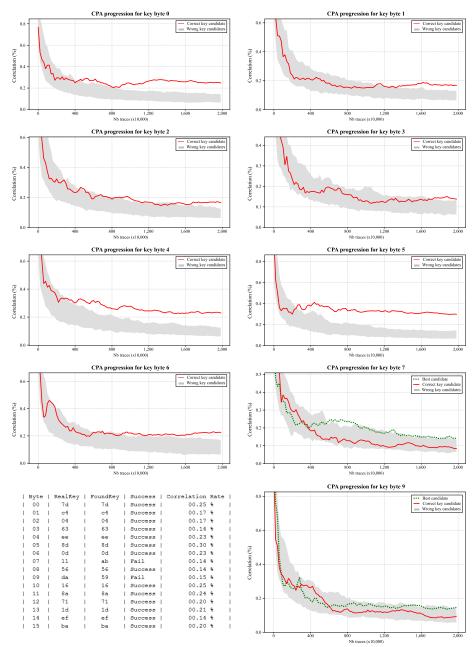

|     |            | 4.3.4.4 Delay-block-based SCA Attacks on STM32MP1 SoC .   | 109 |

|     | 4.3.5      | Discussion                                                | 111 |

|     |            | 4.3.5.1 Performance and Limitations of <i>SideLine</i>    | 111 |

|     |            | 4.3.5.2 Hardware & Software Mitigations                   | 112 |

|     | 4.3.6      | Conclusion                                                | 113 |

| 4.4 | Addition   | nal Results                                               | 115 |

|     | 4.4.1      | Covert Channels between processes                         | 115 |

|     | 4.4.2      | Simple Power Analysis on RSA                              | 117 |

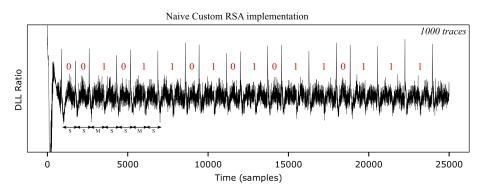

|     |            | 4.4.2.1 SPA on square and multiply RSA version            | 117 |

|     |            | 4.4.2.2 SPA on square and multiply always RSA version     | 118 |

|     |            | 4.4.2.3 SPA on Montgomery Powering Ladder RSA version     | 119 |

| 4.5 | Conclusi   | ion on Delay-Line-based Power Analysis                    | 120 |

|     | 4.5.1      | Results Reminder                                          | 120 |

|     |            | 4.5.1.1 Main Contributions                                | 120 |

|     |            | 4.5.1.2 Some Numbers                                      | 120 |

|     | 4.5.2      | SbHA Knowledge: SbHA Attack Vector Detection Methods      | 121 |

|     |            | 4.5.2.1 Listing OS user-exposed hardware controls         | 121 |

|     |            | 4.5.2.2 Searching registers in the target documentation   | 121 |

|     |            | 4.5.2.3 Reversing OS device drivers and boot code         | 122 |

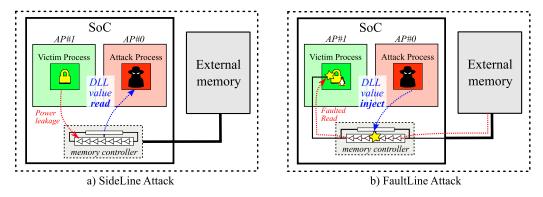

|     | 4.5.3      | From SideLine to FaultLine                                | 124 |

| 4.6 | Appendi    | ix                                                        | 125 |

| 5 S | oftware-ba | ased Fault Injection on SoC External Memory Transfers     | 129 |

| 5.1 | Chapter    | Introduction                                              | 130 |

| 5.2 | Technica   | al Background                                             | 131 |

|     | 5.2.1      | Monitoring Memory Transfers                               | 131 |

|     | 5.2.2      | Faulting Memory Transfers                                 | 131 |

|     | 5.2.3      | Threat Model                                              | 132 |

|     | 5.2.4      | Persistent Fault Analysis on AES                          | 132 |

| 5.3 | FaultLin   | e: Software-based Fault Injection on Memory Transfers     | 136 |

|     | 5.3.1      | Experimental Setup and Fault Parameters                   | 136 |

|     |            | 5.3.1.1 Experimental Setup                                | 136 |

|     |            | 5.3.1.2 Deeper View of the Fault Mechanism                | 137 |

|     |            | 5.3.1.3 Shaping the Glitch                                | 137 |

|     | 5.3.2      | FaultLine on a Bare-Metal Device                          | 138 |

|     |            | 5.3.2.1 Characterizing the Injected Faults                | 139 |

|     |            | 5.3.2.2 Differential Fault Analysis Attack on AES         | 140 |

|     |            | 5.3.2.3 Persistent Fault Analysis Attack on AES           | 141 |

|     |            | 5.3.2.4 Conclusion on Bare-Metal Results                  | 143 |

|     | 5.3.3      | FaultLine on a Device Running Linux                       | 143 |

|     |            | 5.3.3.1 Attack Setup                                      | 143 |

|        |            | 5.3.3.2    | Simple Data Byte Corruption                   | 144 |

|--------|------------|------------|-----------------------------------------------|-----|

|        |            | 5.3.3.3    | Persistent Fault Analysis Attack on AES       | 145 |

|        |            | 5.3.3.4    | Bellcore Attack on OpenSSL Signatures         | 145 |

|        |            | 5.3.3.5    | Conclusion on OS Results                      | 146 |

|        | 5.3.4      | Discussi   | on                                            | 146 |

|        |            | 5.3.4.1    | Related Works                                 | 146 |

|        |            | 5.3.4.2    | Advantages and Limitations over Prior Methods | 146 |

|        |            | 5.3.4.3    | Countermeasures                               | 147 |

| 5.4    | Conclus    | ion on Del | ay-Line based Fault Injection                 | 149 |

|        | 5.4.1      | Results 1  | Reminder                                      | 149 |

|        |            | 5.4.1.1    | Main Contributions                            | 149 |

|        |            | 5.4.1.2    | Some Numbers                                  | 149 |

|        | 5.4.2      | SbHA Ki    | nowledge: Toward Large Scale SbHAs            | 150 |

| 6 C    | Conclusion | and Pers   | pectives                                      | 153 |

| 6.1    | Manuscı    | ript Summ  | ary                                           | 154 |

| 6.2    | Conclus    | ion on SbI | HA                                            | 155 |

| 6.3    | Thesis I   | mpact      |                                               | 156 |

| 6.4    |            | _          | s                                             |     |

| Biblio | ography    | _          |                                               | 159 |

# LIST OF FIGURES

| 1    | Classification des attaques matérielles à distance x                | XV1 |

|------|---------------------------------------------------------------------|-----|

| 2    | Étude des attaques SbSCAs à base de FPGA                            | xix |

| 3    | Les trois scénarios d'attaques de SideLine                          | xii |

| 4    | De SideLine à FaultLine                                             | XXV |

| 1.1  | Thesis Roadmap                                                      | 4   |

| 2.1  | Proposed hardware attack classification                             | 9   |

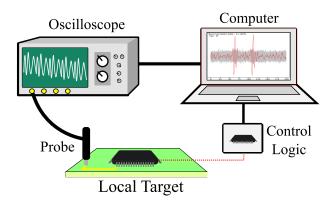

| 2.2  | Local Non-Invasive Attack Setup                                     | 10  |

| 2.3  | Simple Power Analysis on RSA                                        | 12  |

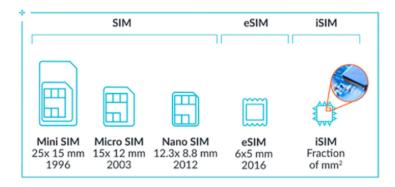

| 2.4  | Evolution of SIM                                                    | 22  |

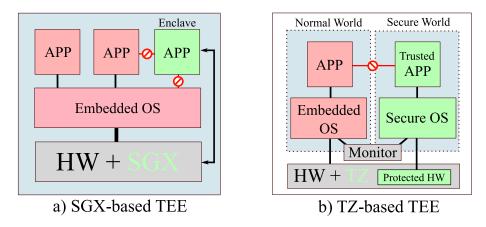

| 2.5  | SGX and TZ-based Trusted Execution Environments                     | 23  |

| 2.6  | Artist's representation of the TEMPEST attack threat                | 24  |

| 2.7  | Famous exploit names in the microarchitectural attack field         | 26  |

| 2.8  | Local hardware attack versus software-based hardware attack         | 28  |

| 2.9  | Artist's representation of the Rowhammer vulnerability              | 30  |

| 2.10 | Cloud FPGA fabrics shared between multiple users                    | 33  |

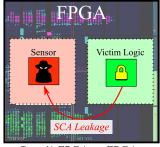

| 2.11 | FPGA-based power side-channel attack threat                         | 38  |

| 2.12 | SbHA paths and privilege levels                                     | 43  |

| 2.13 | Proposed attack classification                                      | 45  |

| 3.1  | Chapter contributions                                               | 48  |

| 3.2  | RLC parasitic elements in the PDN                                   | 50  |

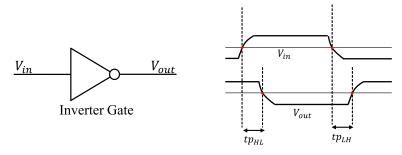

| 3.3  | Inverter gate propagation delay                                     | 51  |

| 3.4  | Functional schematic of a TDC-based sensor                          | 52  |

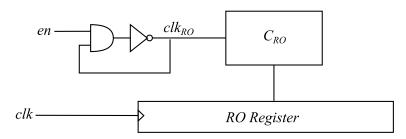

| 3.5  | Functional schematic of a RO-based sensor                           | 53  |

| 3.6  | Overview of FPGA-based Power Side-Channel Exploits                  | 54  |

| 3.7  | FPGA-to-FPGA attack                                                 | 55  |

| 3.8  | Schematic of the proposed JRO-based sensor design                   | 57  |

| 3.9  | Effect of the number of JRO-based sensors on the overall resolution | 58  |

| 3.10 | Xilinx Zynq Multi-User Experimental Setup                           | 60  |

| 3.11 | CPA Attack Results on AES                                           | 61  |

| 3 12 | CPA attack results using various sensing mechanisms                 | 63  |

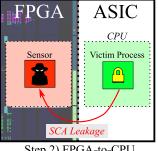

| 3.13       | FPGA-to-CPU attack                                                      | 66       |

|------------|-------------------------------------------------------------------------|----------|

| 3.14       | Xilinx Zynq experimental side-channel setup                             | 67       |

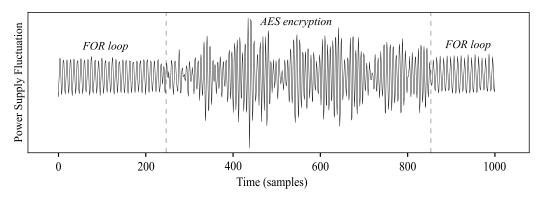

| 3.15       | Averaged AES power supply fluctuation                                   | 68       |

| 3.16       | Logical distance between sensors and target algorithm                   | 69       |

| 3.17       | Power supply fluctuation resulting from 100 Tiny AES encryptions        | 70       |

| 3.18       | Power supply fluctuation resulting from 100 OpenSSL AES encryptions .   | 71       |

| 3.19       | Correlation rate over the time                                          | 72       |

| 3.20       | XRAY picture and EM setup                                               | 73       |

| 3.21       | Logic schematic and implemented design of one TDC-based sensor instance | 76       |

| 3.22       | SCAbox Logo                                                             | 77       |

| 3.23       | Reducing SCA setup complexity                                           | 78       |

| 3.24       | SCAbox hardware (VHDL) and software (C) architecture                    | 80       |

| 3.25       | SCAbox CPA Results                                                      | 81       |

| 3.26       | From FPGA to SoC SbHA exploits                                          | 88       |

| 4.1        | Danchmanking the recovered available for voltage consing                | 91       |

| 4.1        |                                                                         | 91<br>92 |

| 4.2        |                                                                         | 92<br>95 |

| 4.3<br>4.4 |                                                                         | 93<br>96 |

| 4.4        | •                                                                       | 90<br>97 |

| 4.5<br>4.6 | An example of DLL used in DDR memory controllers                        |          |

|            |                                                                         |          |

| 4.7        | DLL response to sudden temperature drops                                |          |

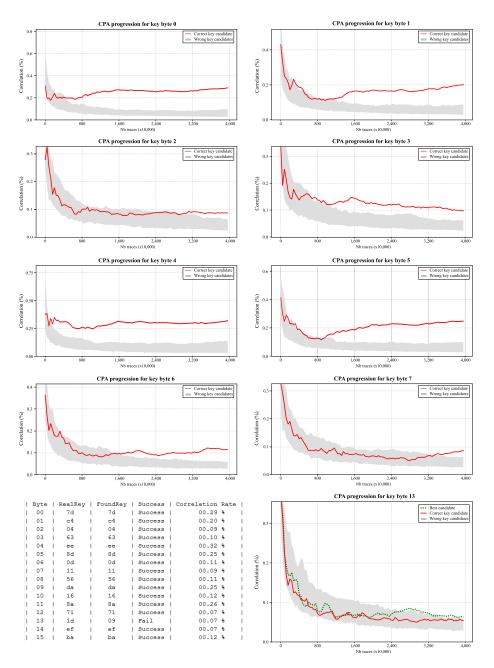

| 4.8        | DLL-based attack results                                                |          |

| 4.9        | Effect of on-chip voltage variations on the sampled delay values 10     |          |

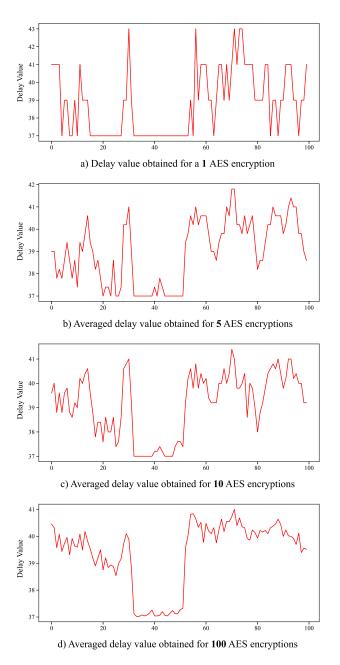

|            | Sampled delay values displayed on screen                                |          |

|            | strcmp test                                                             |          |

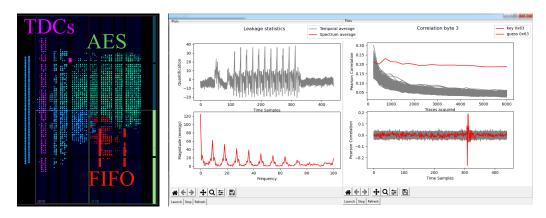

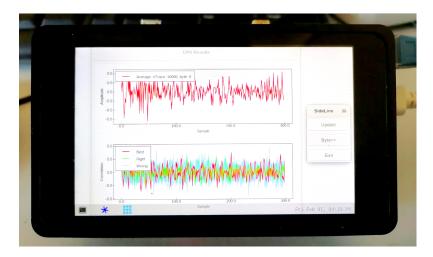

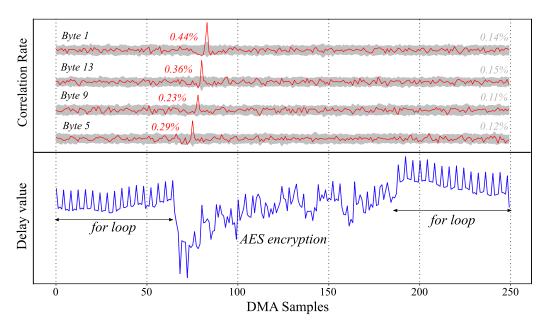

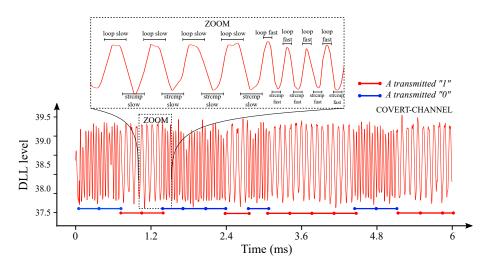

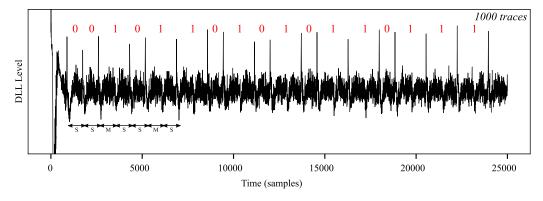

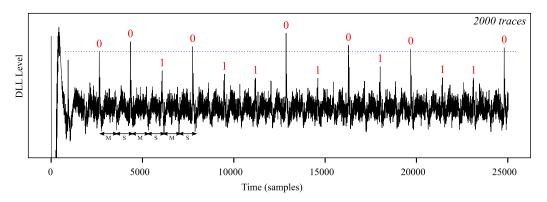

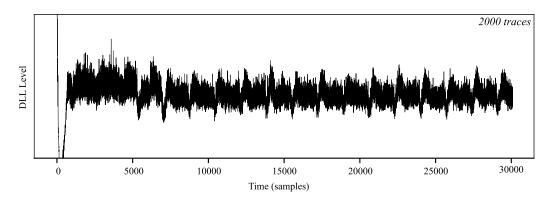

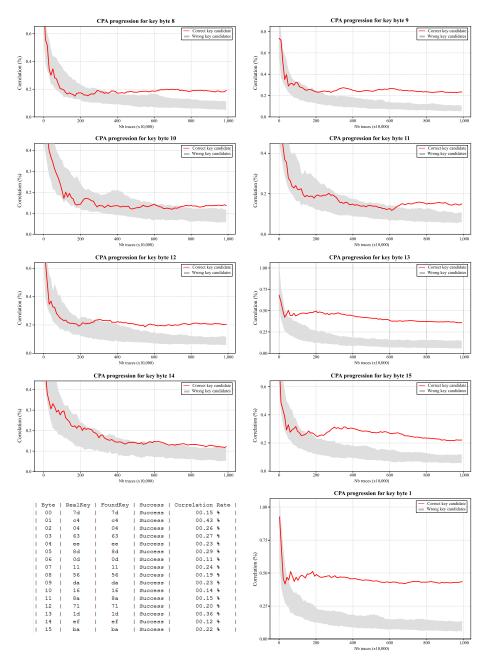

|            | SideLine CPA demonstration                                              |          |

|            | AP-vs-MCU attack results                                                |          |

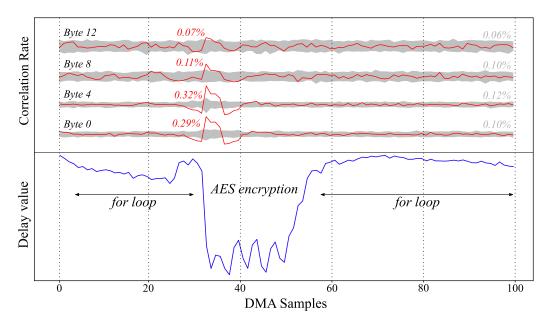

|            | Power fluctuation-based covert-channel captured using delay-lines 1     |          |

|            | Square and multiply RSA delay-line-based SPA                            |          |

|            | Square and multiply always RSA delay-line-based SPA                     |          |

|            | Montgomery powering ladder RSA delay-line-based SPA                     |          |

|            | •                                                                       |          |

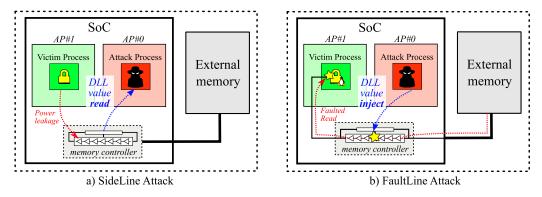

|            | From SideLine SbSCA to FaultLine SbFIA Exploits                         |          |

|            |                                                                         |          |

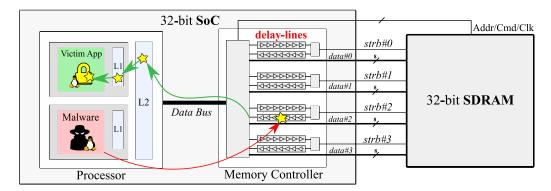

|            | STM32MP1 AP-vs-MCU attack scenario                                      |          |

|            | STM32MP1 MCU-vs-AP attack scenario                                      |          |

| 4 / 3      | DIVIDZIVIE I IVICU-VS-AP AHACK                                          | /.A      |

| 5.1 | Memory transfer organization between a SoC and an external SDRAM 13   |

|-----|-----------------------------------------------------------------------|

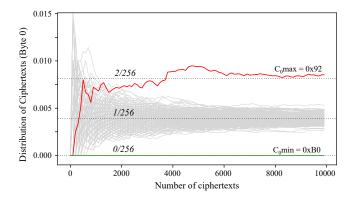

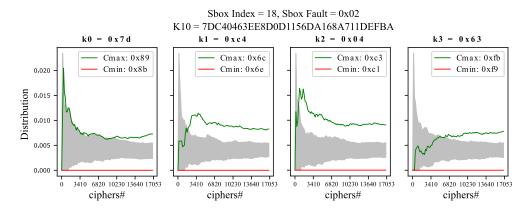

| 5.2 | PFA ciphertext byte 0 distribution                                    |

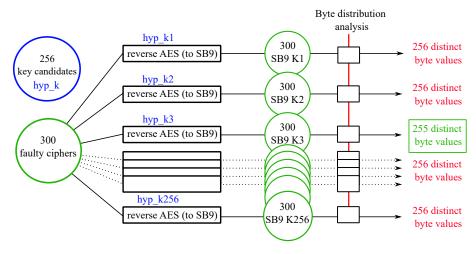

| 5.3 | Method for extracting the right PFA key candidate                     |

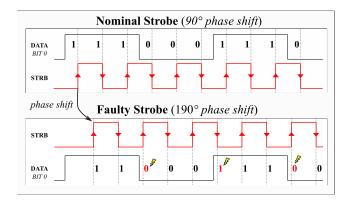

| 5.4 | Nominal vs faulty strobe phase-shifts                                 |

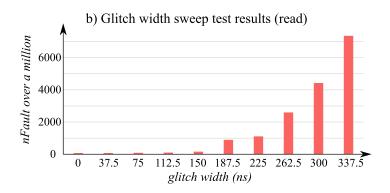

| 5.5 | stress and width characterization                                     |

| 5.6 | Progression of the PFA distribution over 17,053 faulty ciphertexts 14 |

# LIST OF TABLES

| 2.1 | The impact of 40 years of research in the semiconductor industry | 19  |

|-----|------------------------------------------------------------------|-----|

| 2.2 | Non-Exhaustive list of Rowhammer exploits                        | 31  |

| 2.3 | List of FPGA-based Power Glitch Injection exploits               | 34  |

| 2.4 | List of DVFS-based power glitch injection exploits               | 35  |

| 2.5 | List of delay-line-based glitch injection exploits               | 36  |

| 2.6 | List of FPGA-based power SCA exploits                            | 39  |

| 2.7 | List of ADC-based Power SCA exploits                             | 40  |

| 2.8 | List of Delay-line-based Power SCA exploits                      | 41  |

| 2.9 | List of RAPL-based power SCA exploits                            | 41  |

| 3.1 | Resource utilization for 1 RO-based sensor instance              | 57  |

| 3.2 | TDC optimization impact                                          | 69  |

| 3.3 | Number of traces required to retrieve an AES key byte            | 73  |

| 4.1 | On-chip SCA vector benchmark results                             | 93  |

| 4.2 | Overall delay-line-based power SCA results                       | 112 |

| 5.1 | Variations in faulty ciphertexts                                 | 141 |

### **GLOSSARY**

**ADC** Analog-to-Digital Converter

**AES** Advanced Encryption Standard

AI Artificial Intelligence

**AP** Application Processor

**API** Application Programming Interface

**ASIC** Application Specific Integrated Circuit

**AXI** Advanced eXtensible Interface

**CEMA** Correlation ElectroMagnetic Analysis

**CPA** Correlation Power Analysis

**CPU** Computer Processing Unit

**CRT** Chinese Remainder Theorem

**DDR** Double Data Rate

**DFA** Differential Fault Analysis

**DoS** Denial-of-Service

**DLB** Delay-Line Block

**DLL** Delay-Locked-Loop

**DMA** Direct Memory Access

**DPA** Differential Power Analysis

**DRAM** Dynamic Random-Access Memory

**DRM** Digital Right Management

**DUT** Device Under Test

**DVFS** Dynamic Voltage and Frequency Scaling

**ECC** Error-Correction Code

**EM** ElectroMagnetic

eSIM embedded SIM

**FIA** Fault Injection Attack

**FIFO** First In First Out

**FPGA** Field-Programmable Gate Array

**GPU** Graphic Processing Unit

**HPC** Hardware Performance Counters

IC Integrated Circuit

**IoT** Internet of Things

**IP** Intellectual Property

**iSIM** integrated SIM

**JRC** Johnson Ring-Counter

JRO Johnson Ring-Oscillator

MCU Microcontroller Unit

MMU Memory Management Unit

**NSA** National Security Agency

**NVM** Non-Volatile Memory

**OS** Operating System

**PCB** Printed Circuit Board

**PDN** Power Delivery Network

**PIN** Personal Identification Number

**PFA** Persistent Fault Attack

PHY Physical Layer

**PVT** Process Voltage Temperature

**RAM** Random-Access-Memory

**RAPL** Running Average Power Limit

**RHA** Remote Hardware Attack

**RNG** Random Number Generator

**RO** Ring-Oscillator

**RSA** Rivest–Shamir–Adleman

**SbHA** Software-based Hardware Attack

**SbSCA** Software-based Side-Channel Analysis

**SbFIA** Software-based Fault Injection Attack

**SCA** Side-Channel Analysis

**SDRAM** Synchronous Dynamic Random-Access Memory

**SEV** Secure Encrypted Virtualization

**SIM** Subscriber Identity Module

**SGX** Software Guard Extensions

**SoC** System-on-Chip

**SPA** Simple Power Analysis

**TDC** Time-to-Digital Converter

**TEE** Trusted Execution Environment

**TEMPEST** Telecommunications Electronic Material Protected from Emanating

**Spurious Transmissions**

TZ TrustZone

VCO Voltage-Controlled Oscillator

VM Virtual Machine

VRM Voltage Regulator Module

#### **AVANT PROPOS**

C'est à la fin de mon stage de fin d'étude dans l'entreprise Gemalto que Philippe Loubet Moundi m'a proposé une place en tant que doctorant dans l'équipe Hardware Lab. Pourtant, la période troublée que traversait Gemalto durant le rachat par Thales n'était pas forcément propice à ce recrutement. Philippe m'a fait confiance et je lui en suis reconnaissant.

Jean-Max Dutertre mon directeur de thèse à l'école des Mines de Saint-Étienne et Yannick Teglia mon encadrant Thales ont su par leurs conseils avisés et leurs observations habiles me mettre directement sur de bons rails. Une thèse c'est comme une maison, sans fondations solides ça s'effondre. J'ai eu la chance d'avoir un encadrement en béton armé.

Je voudrais remercier chaleureusement toutes les personnes que j'ai pu rencontrer durant de cette thèse. Ma pensée va à mes collègues du Centre Microélectronique de Provence à Gardanne et à l'équipe Security Lab de Thales à La Ciotat. Merci pour votre accueil et pour tous les échanges productifs (ainsi que non-productifs) que nous avons eu.

Je remercie ma famille Elina, Maman, Papa, Manon, Rémi, Adèle, Ugo, Lila et Robin pour leur soutien sans faille malgré la distance qui nous sépare.

Finalement je remercie les examinateurs Jacques Fournier, Lilian Bossuet, Emmanuel Prouff et les rapporteurs Edith Kussener et Régis Leveugle qui ont accepté de se livrer au jeu de la relecture et de la soutenance. Leurs questions et leurs remarques constructives ont contribué à l'aboutissement de ce manuscrit.

## **RÉSUMÉ**

#### Introduction

Durant l'année 1958, Jack Kilby et son équipe élaboraient le premier circuit intégré à transistor dans les laboratoires de Texas Instrument. À peine onze ans plus tard, les premiers ordinateurs de bord composés de plusieurs milliers de transistors nous amenaient sur la Lune. Depuis lors, l'industrie du semi-conducteur a conquis l'intégralité des aspects de la vie humaine : communication, travail, transports, etc. La loi de Moore prévoyant un doublement annuel du nombre de transistors dans les circuits intégrés a été satisfaite pendant 55 années consécutives et nos ordinateurs personnel sont maintenant composés de milliards de transistors.

Si la découverte des circuits intégrés a été une révolution instantanée, leur besoin en sécurité n'est devenu évident que 30 ans plus tard avec l'apparition de services aux consommateurs tels que : les ordinateurs personnels, la téléphonie mobile et l'avènement d'Internet. Pendant une longue période cependant, la structure interne des circuits intégrés a été considérée comme inviolable et la plupart des vulnérabilités ont été recherchées au niveau logiciel.

Les travaux menés par Van Eck [36], Biham [13] et Kocher [77] durant les années 80-90 ont prouvé que ce postulat était faux. Ces chercheurs ont participé à introduire de nouvelles techniques d'attaques telles que l'étude des canaux cachés, ou Side-Channel Analysis (SCA) en anglais, et l'injection de faute, ou Fault Injection Attack (FIA) en anglais, qui visent à exploiter des vulnérabilités physiques liées aux ressources matérielles qui composent les circuits intégrés.

Depuis plus de 30 ans, l'étude de la sécurité matérielle des circuits intégrés s'est montrée nécessaire afin d'implémenter des systèmes résistants aux attaques menées par des groupes de pirates informatiques. Les attaques matérielles utilisent des équipements tels que des lasers, des injecteurs électromagnétiques et des oscilloscopes pour injecter des erreurs dans les calculs d'un circuit ou pour espionner son fonctionnement. L'objectif à terme est d'en extraire les secrets comme par exemple le code source pour voler la propriété intellectuelle, les clés cryptographiques ou les données utilisateurs afin de les vendre au plus offrant. Les attaques matérielles visent une grande variété d'appareils comme les cartes à puce (cartes SIM, cartes bancaires, passeports), les processeurs (téléphones, ordinateurs, serveurs) et tous les autres objets pour lesquels l'extraction d'information fait sens (microcontrôleurs pour l'IoT, automobiles, consoles de jeu, drones, etc.).

Les attaques matérielles sont globalement utilisées sur des systèmes légers qui peuvent être volés et placés sur un banc d'attaque. À la différence des attaques logicielles,

elles nécessitent l'accès physique à la cible et ne permettent pas d'attaques à grande échelle sur des milliers d'appareils en simultané. Cependant, elles constituent une menace réelle et restent très étudiées car elles permettent, dans de nombreux cas, de révéler des secrets qu'une attaque logicielle ne pourrait pas obtenir. L'extraction de données secrètes contenues dans un appareil électronique peut avoir de grandes répercussions sur la crédibilité de gouvernements, sur la réputation et la rentabilité d'entreprises ainsi que sur la vie privée des consommateurs.

Récemment, plusieurs études menées sur des processeurs complexes ont montré que les attaques matérielles n'étaient plus nécessairement locales. Avec la multiplication et la complexification des objets connectés, il est devenu possible de mener ces attaques à distance.

Cette thèse propose d'étudier une nouvelle famille d'attaque communément nommée "attaque matérielle à base de logiciel", ou Software-based Hardware Attack (SbHA) en anglais, qui à travers l'exécution d'un programme malicieux vise à utiliser des composants intégrés dans un circuit cible afin de mener des attaques matérielles. Ces attaques ne requièrent aucun équipement externe à l'appareil ciblé et peuvent donc être menées à distance.

Le but de ce travail est tout d'abord d'étudier les risques découlant des attaques matérielles à distance, notamment au regard de l'adoption massive de la sécurité intégrée. Mais aussi d'évaluer de nouvelles vulnérabilités afin de mieux cerner l'étendue de la menace. Cette thèse contient des travaux variés allant d'attaques SCA embarquées sur des circuits intégrés reprogrammables de type Field-Programmable Gate Array (FPGA) à de l'attaque FIA sur des processeurs complexes de type System-on-Chip (SoC). Tous ces travaux ont été menés de façon à être reproductibles et réalisables à distance. Ils visent à préparer les différents acteurs de la sécurité intégrée à cette menace naissante et ainsi à éviter sa mise en exécution future sur des milliers d'appareils connectés à travers le monde.

Dans la suite de ce résumé, nous décrivons les grandes lignes de chaque chapitre composant ce manuscrit. Le chapitre 2 présente le sujet et l'état de l'art des attaques matérielles à distance. Les chapitres 3, 4 et 5 décrivent les expérimentations réalisées durant cette thèse. Finalement, le dernier chapitre conclut sur les résultats obtenus et revient sur l'impact des travaux menés et leurs perspectives futures.

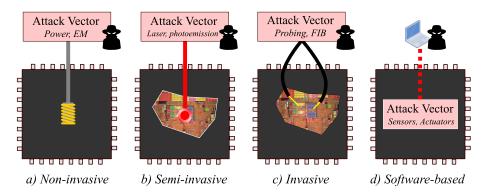

#### Les attaques matérielles à distance

Le chapitre 2 de ce manuscrit est dédié à la description du sujet de cette thèse : "les attaques matérielles à distance des objets connectés" et à la classification des travaux existants. Dans un premier temps, nous décrivons l'origine des attaques matérielles (Section 2.1.1) et procédons à leur répartition en 3 familles (Section 2.1.2) : les attaques invasives, les attaques semi-invasives et les attaques non-invasives comme proposé dans [125]. Il apparait que les attaques matérielles à distance ne s'intègrent dans aucune de ces familles qui nécessitent toutes des équipements et un accès physique à la cible. Nous proposons

donc d'en ajouter une appelée "attaque matérielle à base de logiciel" qui permettrait de classer ce nouveau type d'attaque.

La suite du chapitre présente l'origine et les enjeux derrière la multiplication des objets connectés. Dans la section 2.2, nous décrivons les mécanismes qui ont mené à l'adoption d'objets connectés dans tous les aspects de l'activité humaine (industrie, services publics, cloud, etc). Puis, nous décrivons les dangers qui découlent de l'utilisation de ces systèmes et comment des pirates tirent parti de certaines avancées pour extorquer, menacer et soudoyer des états, des entreprises ou des utilisateurs. Enfin, nous évoquons le futur des attaques matérielles dans la sous-section 2.2.3 et imaginons comment la sécurité matérielle évoluera face aux mutations des circuit intégrés et à la multiplication de services de calcul distant comme le cloud qui ne permettent pas de lancer des attaques matérielles locales classiques car inaccessibles. L'hypothèse de résistance aux attaques matérielles qu'apportent ces services de calcul distant est cependant remise en cause par l'introduction d'attaques matérielles à distance.

Dans la section 2.3, nous décrivons en quoi consiste une attaque matérielle à distance. Nous identifions tout d'abord trois mécanismes qui favorisent la multiplication de ces attaques. Le premier est lié à la complexification des circuits modernes. Les circuits de type SoC sont composés d'un processeur et de multiples ressources matérielles (mémoire, capteurs, régulateurs) sur la même puce de silicium. En rassemblant ces diverses fonctionnalités sur un même système, les concepteurs améliorent grandement les capacités de calcul et les performances énergétiques du circuit. Les ressources matérielles peuvent maintenant être accédées et programmées directement par un logiciel pour adapter par exemple la consommation du circuit à l'activité de l'utilisateur. La coopération matérielle-logicielle est plus que jamais représentée et permet d'obtenir des performances inégalées. Cependant, malgré les bénéfices, l'accès à des ressources matérielles par le logiciel pourrait être l'origine de nouvelles attaques. Notamment les attaques matérielles à distance.

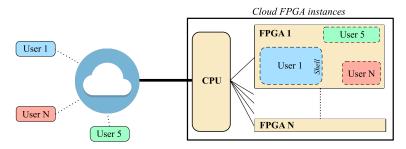

Le second mécanisme qui favorise l'émergence des attaques matérielles à distance est la démocratisation de systèmes comprenant plusieurs utilisateurs et/ou plusieurs niveaux de privilèges. Le partage de ressources matérielles entre plusieurs utilisateurs est devenu la référence avec l'avènement du cloud. L'isolation entre les processus est assurée par des mécanismes de protection mémoire et des niveaux de privilèges offerts par les systèmes d'exploitation, ou Operating System (OS) en anglais. Le fait de rassembler plusieurs utilisateurs avec différent niveaux de privilège sur un même système ouvre la porte à de nouvelles attaques où un utilisateur tente d'outrepasser l'isolation en place pour : espionner les autres utilisateurs, procéder à de l'escalade de privilège ou générer un déni de service. Les OS sont devenus si complexes qu'il en devient difficile d'en garantir la fiabilité sécuritaire. Pour cette raison, il est désormais commun d'intégrer des entités de sécurité matérielle afin d'assurer un niveau de sécurité supérieur dans les produits contenant des informations sensibles. L'intégration d'entités de sécurité prétendues résistantes aux attaques logicielles est le troisième mécanisme qui pourrait favoriser l'émergence d'attaques matérielles à distance.

Depuis les années 80, des cartes à puce telles que les cartes SIM assurent la sécurité des appareils connectés. Aujourd'hui des circuits intégrés effectuant les mêmes opérations sécuritaires mais pouvant être directement soudés sur un carte mère (eSIM) ou intégrés à l'intérieur d'un SoC (iSIM) remplacent peu-à-peu le format carte. Tant que les circuits sécuritaires étaient localisés en dehors du SoC, ils pouvaient difficilement être attaqués par un processus malicieux s'exécutant dans le processeur. Cependant, l'intégration de ces entités sécuritaires sur la même puce de silicium que le processeur applicatif ouvre la voie à de nouvelles vulnérabilités internes provenant du matériel. Ainsi, nous verrons que le risque de voir ces entités soumises à des attaques matérielles à distance augmente.

Un autre aspect de la sécurité intégrée est l'avènement des plateformes d'exécution sécurisées, ou Trusted Execution Environment (TEE) en anglais, renforcées par des entités matérielles conçues par des fabricants de processeurs majeurs tels que ARM, INTEL et AMD. Ces plateformes appelées TrustZone (TZ), Software Guard Extensions (SGX) et Secure Encrypted Virtualization (SEV) partent du principe que l'OS implémenté sur le processeur applicatif n'est pas forcément fiable et qu'il faut déléguer les opérations sécuritaire à une entité indépendante de l'OS. Ces entités assurent donc les opérations critiques telles que l'authentification ou le chiffrement à la place de l'OS et ajoutent une nouvelle couche de sécurité au-delà des privilèges administrateurs. Les attaques matérielles à distance pourrait préférentiellement s'attaquer à ces plateformes qui n'ajoutent que de la sécurité du point de vue logiciel et qui restent donc le plus souvent vulnérables aux attaques physiques.

Sur les facteurs favorisants les attaques matérielles à distance on retiendra : la complexification des circuits intégrés, l'avènement des systèmes multi-tâches/multi-utilisateurs à plusieurs niveaux de privilèges et l'intégration d'entités de sécurité dans les SoCs modernes.

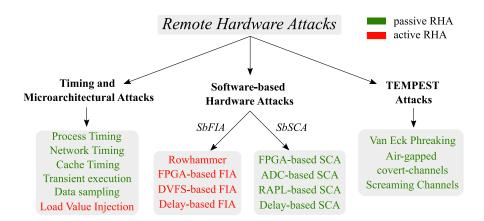

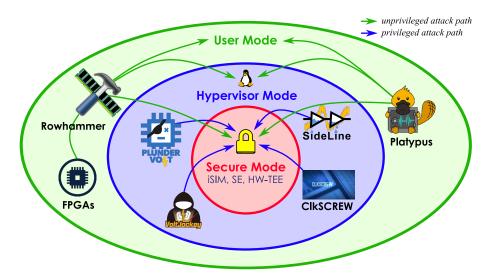

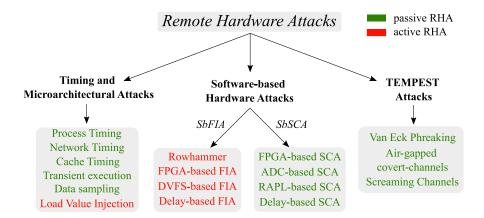

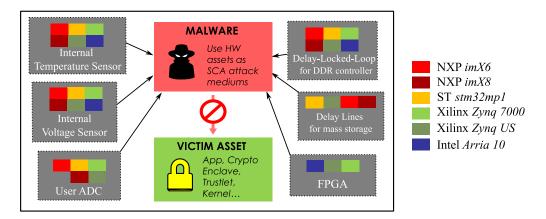

Dans la suite du chapitre 2, nous classons les attaques matérielles à distance en trois familles distinctes dont l'une d'elle sera le sujet d'étude de cette thèse. Ces trois familles ont pour point commun de rendre les attaques à distance possibles mais elles n'utilisent pas les mêmes moyens. Ces attaques sont classées dans la figure 1, nous les identifions dans la liste ci-dessous :

• Les attaques TEMPEST. L'étude des attaques TEMPEST remonte à la guerre froide. C'est un nom de code de la National Security Agency (NSA) [101] faisant référence à l'extraction d'informations contenues dans des appareils électroniques à travers des émanations physiques pouvant être mesurées à longue portée. Ce sont par exemple des émanations électromagnétiques générées par un appareil et pouvant être capturées à plusieurs mètres en utilisant une antenne radio. Elles avaient été introduites au grand public en 1985 dans un article de Wim van Eck [36] présentant l'extraction de l'image affichée par un écran d'ordinateur situé à l'intérieur d'un bâtiment à partir d'une antenne embarquée dans une camionette postée à l'extérieur (à une distance de 10 mètres).

**Figure 1** Classification des attaques matérielles à distance comme proposé dans le chapitre 2

Ces attaques ont récemment été remises au-devant de la scène par l'article Screaming Channel [22, 21] publié en 2018 qui vise des processeurs hétérogènes composés de logique analogique et digitale. Ces recherches ont prouvé que l'activité digitale génératrice de fuites par canaux-cachés pouvait se retrouver amplifiée par les modules intégrés analogiques de radio-fréquence (Wifi, Bluetooth) puis capturée à distance en utilisant une radio logicielle (SDR). En plus de capter l'activité électromagnétique induite par la cible, cet article va plus loin en démontrant la possibilité d'extraire des informations sur les processus exécutés par l'appareil espionné. Les chercheurs démontrent que l'empreinte side-channel d'un processus cryptographique s'exécutant dans la cible est détectable dans le signal radio et mènent une SCA permettant l'extraction de la clé secrète (à 15 mètres de la cible). Avec la prolifération des objets connectés qui intègrent de plus en plus souvent des modules radio, le champ d'application de ces attaques devrait s'élargir dans le futur. L'avantage ici pour l'attaquant est qu'il n'y plus de besoin d'accéder directement à la cible pour effectuer la SCA. Pour cette raison, nous considérons ces travaux comme des attaques matérielles à distance.

• Les attaques microarchitecturales et temporelles. Les attaques temporelles sur les processus cryptographiques et les protocoles réseaux sont connues depuis les travaux menés par Kocher [77] en 1996. Ces attaques peuvent être réalisées à distance puisqu'elles nécessitent seulement la mesure d'un temps d'exécution pour l'extraction des secrets. Aujourd'hui la plupart des processus cryptographiques sont protégés contre ce type d'attaque et utilisent des algorithmes à temps constant pour éviter toute fuite d'information liée à une clé cryptographique ou à un mot de passe.

Depuis le milieu des années 2000, de nouvelles attaques exploitant des vulnérabilités temporelles ont fait leur apparition : les attaques microarchitecturales. Ces menaces tirent parti du partage de certaines ressources matérielles entre plusieurs processus et utilisateurs pour mettre à mal l'isolation mémoire implémentée dans

ces systèmes. Par exemple, les attaques temporelles sur la mémoire cache exploitent le fait que des données provenant d'une application peuvent être stockées de manière transitoire dans la mémoire cache. En mesurant les temps d'accès à la mémoire, des processus espions peuvent déduire l'activité de programmes victimes et même établir des communications cachées entre processus [144, 58, 84]. Ces attaques sont considérées comme des attaques physiques car elles exploitent des vulnérabilités provenant du matériel et non de l'implémentation logicielle des programmes.

Plus récemment des attaques telles que *Spectre* [75] et *Meltdown* [86] ont visé des optimisations matérielles des processeurs telles que la prédiction de branchement ou l'exécution spéculative afin d'accéder à des données protégées.

Les attaques microarchitecturales sont à la frontière entre des attaques logicielles et des attaques matérielles. Elles sont menées à travers un programme malicieux mais exploitent des vulnérabilités matérielles. Elles s'inscrivent donc dans la liste des attaques matérielles à distance mais n'utilisent pas les mêmes outils et n'exploitent pas les mêmes vulnérabilités que les attaques matérielles locales.

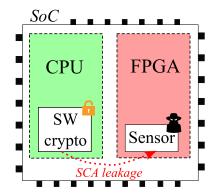

• Les attaques matérielles à base de logiciel (SbHA). Ces attaques sont le cas d'étude de cette thèse. Elles sont des reproductions pures des attaques matérielles classiques menées dans des laboratoires, à l'exception du fait qu'elles peuvent être réalisées à distance. C'est à dire qu'elles cherchent à induire des fautes ou à collecter une fuite side-channel de la même façon qu'une attaque matérielle classique mais sans utiliser d'équipement.

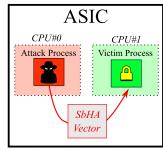

Les SbHA tirent parti de ressources matérielles directement implémentées dans les circuits cibles afin de mener des attaques. Elles profitent de la complexité des SoCs qui comportent des dizaines de composants matériels et dont l'accès et la calibration peut permettre l'implémentation d'attaques physiques. Dans la section 2.3.4 et 2.3.5 nous dressons un état de l'art complet de ces attaques qu'elles soient dédiées à la FIA ou à la SCA.

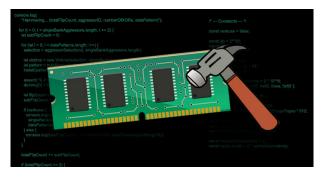

Du point de vue de la FIA, nous définissons les attaques réalisées sous le nom d'injection de faute à base de logiciel, ou Software-based Fault Injection Attack (SbFIA) en anglais. Les familles d'attaques décrites comportent la SbFIA sur mémoire DRAM ou *Rowhammer* introduite en 2014 par Kim et al [74], la FIA à base de régulateur tension-fréquence avec *ClkSCREW* [128], *VoltJockey* [111] et *Plundervolt* [100], les attaques sur FPGA telles que *FPGAhammer* [80] et enfin l'attaque *FaultLine* [51] découverte lors de cette thèse et décrite dans le chapitre 5.

Du point de vue de la SCA nous appelons ces attaques *analyse par canaux cachés* à base de logiciel, ou Software-based Side-Channel Analysis (SbSCA) en anglais. Nous intégrons plusieurs types d'attaques à la classification : les attaques SCA à base de capteurs FPGA [122] qui seront étudiées dans le chapitre 3 de ce manuscrit, les attaques à base de convertisseurs analogiques-numériques telles que *Leaky*

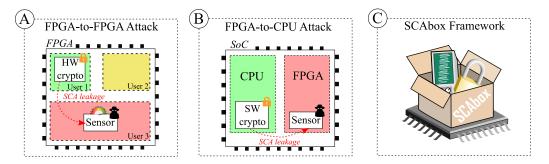

Figure 2 Étude des attaques SbSCAs à base de FPGA : Contributions du chapitre 3

*Noise* [46], les attaques à base de lignes à retard (delay-lines) menées dans cette thèse qui seront décrites au chapitre 4 (*SideLine* [51]) et enfin les attaques SCA menées sur des processeurs Intel dans l'article *Platypus* [85].

La section 2.4 conclut ce chapitre en proposant une vue globale des trois familles d'attaques matérielles à distance identifiées et des différents groupes de vecteurs d'attaques contenus dans chacune d'elles. La classification globale est illustrée dans la figure 1 de ce résumé.

#### Attaques par analyse de consommation à base de FPGA

En 2018, au début de cette thèse, plusieurs types de mécanismes permettant les SbHA tels que Rowhammer [74] ou les régulateurs tension/fréquence [128] avaient déjà été identifiés. Ces travaux précédents étaient, en grande majorité, dédiés à des attaques SbFIA. Seuls les travaux réalisés par Schellenberg et al. sur FPGA présentaient la menace des attaques SbSCA [122].

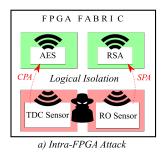

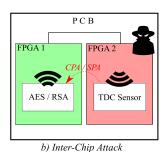

Il apparut rapidement que l'étude de ces travaux sur FPGA pourraient être un point de départ intéressant pour cette thèse. En étudiant des FPGAs qui permettent l'implémentation de n'importe quel type de bloc numérique, un banc d'expérimentation complet contenant un capteur de consommation intégré, la cible (un algorithme cryptographique) et le stockage des données pour les courbes SCA peut être mis en place. De plus avec l'adoption des FPGAs dans les SoC modernes [4] ainsi que dans les services cloud [24], le risque d'attaque lié à ces entités devient critique [131] et suscite l'intérêt de la recherche. L'implémentation de FPGA partagés entre plusieurs utilisateurs est déjà possible [24] et elle pourrait faire son apparition dans le cloud. Il y a donc un véritable enjeu sécuritaire à étudier ce type d'appareils au-delà de l'étude de faisabilité des attaques SbSCA.

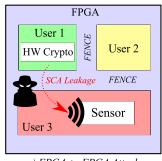

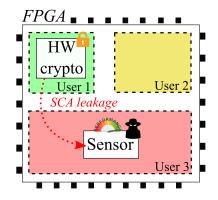

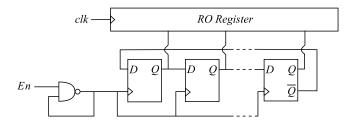

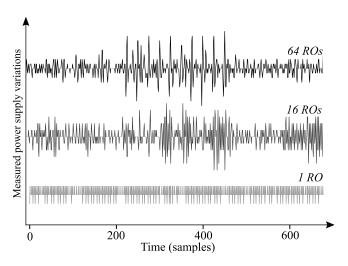

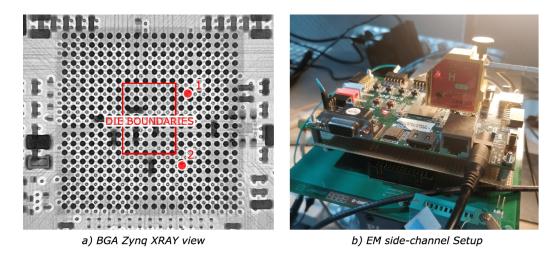

La figure 2 illustre trois travaux décrits dans le chapitre 3 de ce manuscrit. Tout d'abord, dans la section 3.3 nous étudions des capteurs de délai à base de Ring-Oscillators (ROs) permettant de capturer les variations de consommation électrique dans les FPGAs et menons des attaques SCA entre blocs logiques. Cette première partie étudie donc les attaques sur FPGA multi-utilisateurs où l'un des clients utilise sa logique reprogrammable pour espionner l'activité d'autres blocs logiques appartenant à d'autres clients (attaques

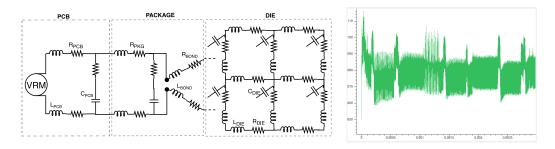

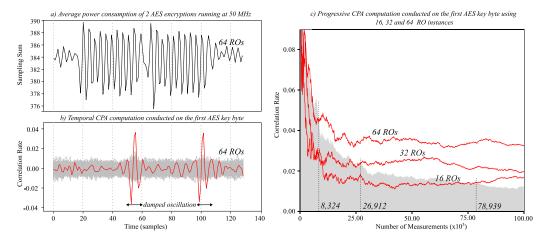

FPGA-to-FPGA dans la figure 2.A). À partir de capteurs digitaux optimisés pour la SCA nous lançons des attaques de type Correlation Power Analysis (CPA) [18] sur des cibles cryptographiques telles qu'un module Advanced Encryption Standard (AES) matériel [30]. Ainsi nous démontrons que la fuite de consommation liée à l'activité d'un module AES (implémenté dans une partie du FPGA) peut être collecté par des capteurs digitaux (implémentés dans une autre partie de FPGA). Cette étude confirme l'hypothèse que les variations de consommation électrique liées à l'activité des transistors se propagent dans toute la puce de silicium est peuvent être mesurées par une entité espacée physiquement de l'origine de la fuite. Il est donc possible de mener des attaques SbSCA entre des blocs matériels formant un FPGA ou un SoC (si tant est que l'attaquant trouve un moyen de collecter la fuite de consommation).

Une deuxième conclusion de cette étude est que les limitations en terme de fréquence des capteurs intégrés (ici 250 MHz) ne sont pas forcément rédhibitoires pour la mesure de la fuite de consommation. En effet, à travers nos expérimentations, nous remarquons que la fuite side-channel reste exploitable malgré l'augmentation de la vitesse d'exécution du module victime. Nous réalisons plusieurs tests sur le module AES en modifiant sa fréquence de fonctionnement de 10 MHz à 200 MHz et n'observons pas de réelle différence sur les corrélations relevées par la CPA. Ces résultats viennent confirmer que la fuite side-channel est essentiellement liée à la structure d'alimentation du circuit à sa finesse de gravure [31, 59] et non à la fréquence d'horloge du module ciblé [90]. Il sera donc possible d'attaquer des systèmes très rapides tels que des processeurs complexes cadencés au GHz avec des capteurs lents de l'ordre du MHz comme en témoignent les résultats du chapitre 4. Il est cependant important de prendre en compte qu'une trop grande limitation de la fréquence d'échantillonnage pourra s'avérer problématique pour la détection des points d'intérêts et ainsi la resynchronisation des courbes collectées.

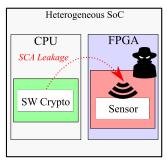

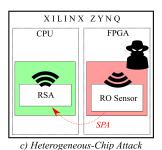

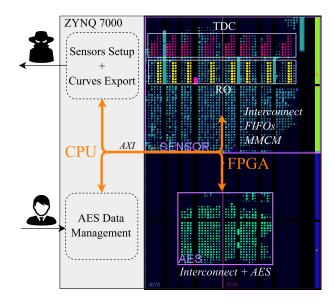

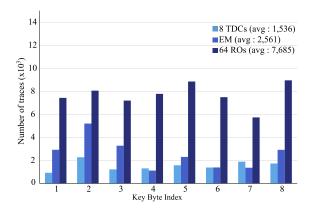

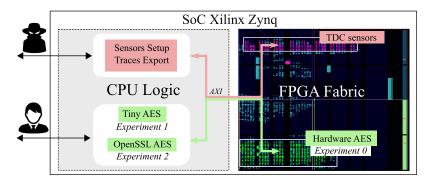

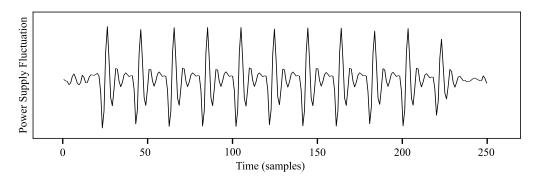

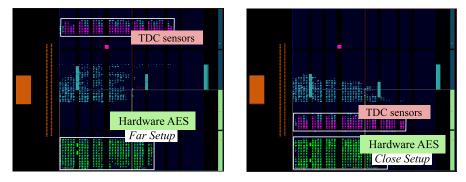

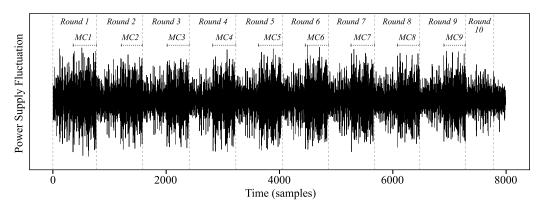

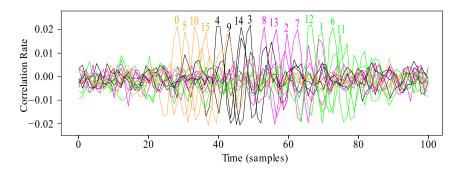

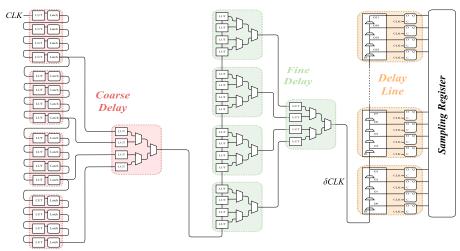

La section 3.4 du chapitre 3 étudie des systèmes hétérogènes composés à la fois d'un FPGA et d'un processeur (Attaques FPGA-to-Computer Processing Unit (CPU) dans la figure 2.B). L'objectif de cette section est de démontrer que des attaques SbSCA sont possibles d'un composant du SoC vers un autre. Ici, un SoC Xilinx Zynq 7000 [141] composé d'un processeur ARM Cortex-A et d'un FPGA est adopté pour mener des attaques du FPGA vers le CPU. C'est-à-dire, la collecte d'une fuite de consommation électrique induite par un algorithme cryptographique logiciel s'exécutant sur le CPU par des capteurs implémentés dans le FPGA. À travers l'implémentation de capteurs de type Time-to-Digital Converter (TDC) [151] dans le FPGA et la mise en place de plusieurs implémentations d'AES logiciels dans le CPU (OpenSSL AES [106] et Tiny AES [78]), nous lançons des attaques CPA du FPGA vers le CPU. Les résultats obtenus montrent que la fuite side-channel induite par le fonctionnement des AES s'exécutant dans le CPU est suffisamment importante pour être capturée par les capteurs et permet l'extraction des clés cryptographiques. Malgré la distance physique entre les capteurs (dans le FPGA) et l'algorithme (dans le CPU), le fait que les deux entités sont implémentées sur la même puce de silicium établit une canal d'information suffisant pour faire fonctionner l'attaque. Les attaques du FPGA vers le CPU nécessitent la collecte d'un plus grand nombre de courbes SCA (autour de 100,000 courbes) que les attaques FPGA vers FPGA (autour de 1,500 courbes) mais restent largement envisageables (moins de 15 minutes pour récupérer la clé secrète de l'AES OpenSSL dans notre preuve de concept).

Afin de comparer l'efficacité des attaques intégrées avec les techniques traditionnelles, une SCA électromagnétique est réalisée sur les mêmes AES cibles dans la section

3.4.5. Les résultats obtenus montrent que les capteurs FPGAs sont aussi efficaces que

l'analyse électromagnétique malgré les performances limitées des capteurs en terme de

vitesse d'échantillonnage et de résolution. L'avantage des TDCs dans cette configuration est leur proximité à la cible qui permet d'éviter toute perte d'information par effet

de dissipation de la fuite à travers le package et de limiter l'effet de filtrage induit par

les condensateurs de découplage externes. Il semble probable que dans certains SoC

complexes comportant des mémoires empilées, de multiples cœurs et de multiple mécanismes de régulation de tension, l'analyse interne de la consommation pourrait être plus

performante à terme que l'analyse externe.

La section 3.5 conclut la partie expérimentation du chapitre 3 en présentant un outil open-source permettant la mise en place d'attaques FPGA-vers-FPGA et FPGA-vers-CPU présentées dans les sections précédentes. Ce projet appelé *SCAbox* est disponible sur GitHub et vise à faciliter l'implémentation et l'évaluation de ces attaques [52]. Il intègre plusieurs modules de capteurs FPGA et fournit une méthode simple pour ajouter des algorithmes victimes et les évaluer. Cet outil est purement dédié à la recherche et se veut être utilisé comme plateforme d'initiation aux attaques matérielles à distance afin de mieux appréhender leur menace.

La conclusion du chapitre 3 revient sur les résultat des travaux menés sur FPGA qui ont donné lieu à la publication de deux articles de conférence pour les travaux d'attaque FPGA-vers-FPGA [50] et FPGA-vers-CPU [54] ainsi que la publication en ligne de l'outil *SCAbox* [52].

Nous revenons aussi sur l'impact des résultats obtenus pour l'avancée de cette thèse. L'objectif de celle-ci étant à terme de mener des attaques sur n'importe quel type de SoC implémentant ou non un FPGA. Au moment de clore ce chapitre, il semble désormais acquis que les attaques SbSCA peuvent être menées à partir de capteurs digitaux directement implémentés dans un SoC. Que les attaques SbSCA sont faisables même avec des capteurs moins performants que ceux utilisés pour les attaques matérielles locales. Enfin, que les attaque SbSCA brisent les frontières logicielles qui séparent normalement les différents blocs matériels formant un SoC (c'est à dire toutes les entités matérielles implémentées sur une même puce de silicium). Ceci ouvre la voie à des attaques FPGA-vers-CPU mais aussi à des attaques provenant de n'importe quel capteur (FPGA, Analog-to-Digital Converter (ADC), delay-line) vers n'importe quelle entité du SoC (CPU, Microcontroller Unit (MCU), élément sécurisé, iSIM, etc).

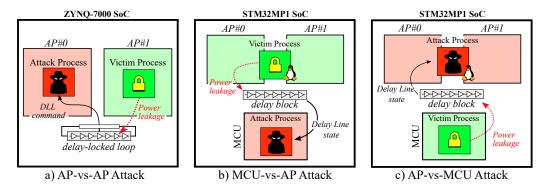

#### Attaques par analyse de consommation dans les SoC complexes